US008063432B2

# (12) United States Patent

# Ozawa

# (54) SEMICONDUCTOR DEVICE HAVING NITRIDE FILM BETWEEN GATE INSULATION FILM AND GATE ELECTRODE

- (75) Inventor: Yoshio Ozawa, Yokohama (JP)

- (73) Assignee: Kabushiki Kaisha Toshiba, Tokyo (JP)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: **12/805,620**

- (22) Filed: Aug. 10, 2010

# (65) **Prior Publication Data**

US 2010/0320522 A1 Dec. 23, 2010

#### **Related U.S. Application Data**

(62) Division of application No. 11/937,024, filed on Nov. 8, 2007, now Pat. No. 7,800,160.

# (30) Foreign Application Priority Data

Nov. 9, 2006 (JP) ..... 2006-304364

- (51) Int. Cl. *H01L 29/788* (2006.01) *H01L 29/792* (2006.01)

- (52) **U.S. Cl.** ..... **257/316**; 257/326; 257/E27.102; 257/E29.3

- (58) Field of Classification Search ...... 257/316, 257/326, E27.102, E29.3

See application file for complete search history.

#### (56) **References Cited**

#### U.S. PATENT DOCUMENTS

# (10) Patent No.: US 8,063,432 B2

# (45) **Date of Patent:** Nov. 22, 2011

| 6,228,717 B1*    | 5/2001  | Hazama et al 438/265 |

|------------------|---------|----------------------|

| 6,525,400 B2     | 2/2003  | Fujii et al.         |

| 2005/0153509 A1* | 7/2005  | Kwak 438/257         |

| 2006/0240619 A1  | 10/2006 | Ozawa et al.         |

| 2006/0270186 A1  | 11/2006 | Tsunomura et al.     |

| 2007/0241389 A1  | 10/2007 | Ozawa et al.         |

#### FOREIGN PATENT DOCUMENTS

| JP<br>JP | 61-147576<br>9-167807    | 7/1986<br>6/1997  |

|----------|--------------------------|-------------------|

| JP       | 11-3990                  | 1/1999            |

| JP<br>JP | 11-317463<br>2002-198446 | 11/1999<br>7/2002 |

| JP       | 2002-353343              | 12/2002           |

| JP       | 2005-197363              | 7/2005            |

# OTHER PUBLICATIONS

Notice of Reasons for Rejection issued by the Japanese Patent Office mailed on Mar. 29, 2011, for Japanese Patent Application No. 2006-304364 and English language translation thereof.

\* cited by examiner

Primary Examiner - Benjamin Sandvik

Assistant Examiner — Wensing Kuo

(74) Attorney, Agent, or Firm—Finnegan, Henderson, Farabow, Garrett & Dunner, L.L.P.

# (57) ABSTRACT

A semiconductor device includes a tunnel insulation film formed on a semiconductor substrate, a floating gate electrode formed on the tunnel insulation film, an inter-electrode insulation film formed on the floating gate electrode, a control gate electrode formed on the inter-electrode insulation film, a pair of oxide films which are formed between the tunnel insulation film and the floating gate electrode and are formed near lower end portions of a pair of side surfaces of the floating gate electrode, which are parallel in one of a channel width direction and a channel length direction, and a nitride film which is formed between the tunnel insulation film and the floating gate electrode and is formed between the pair of oxide films.

## 4 Claims, 19 Drawing Sheets

F I G. 2

FIG. 3

F I G. 4

FIG. 6

FIG. 7

FIG. 10

FIG. 12

FIG. 13B

FIG. 14B

FIG. 16B

F I G. 17B

FIG. 18A

FIG. 18B

FIG. 19B

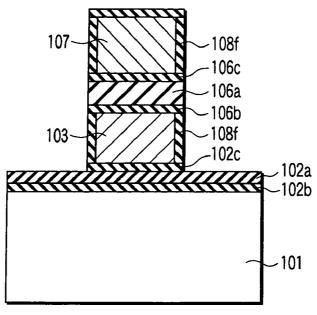

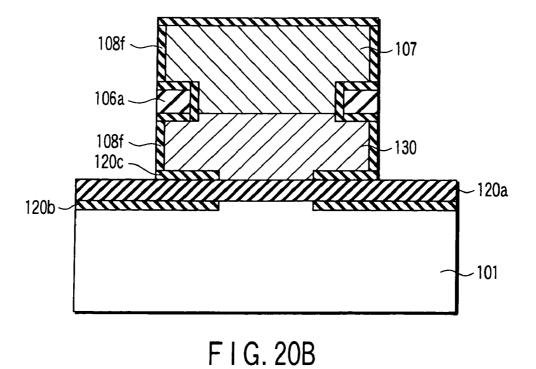

FIG. 20A

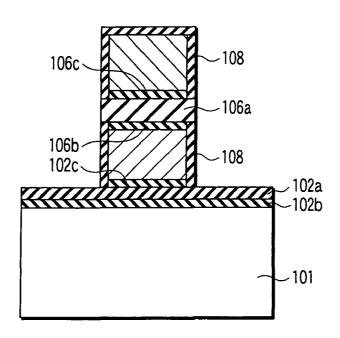

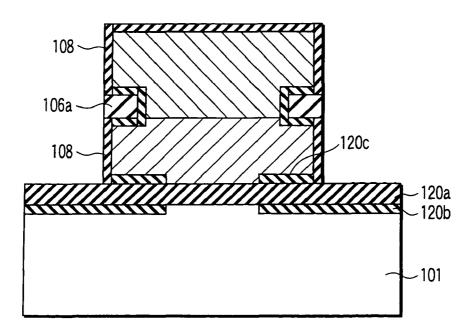

FIG. 21A

FIG. 21B

FIG. 25B

F I G. 26B

# SEMICONDUCTOR DEVICE HAVING NITRIDE FILM BETWEEN GATE INSULATION FILM AND GATE ELECTRODE

#### CROSS-REFERENCE TO RELATED APPLICATIONS

This application is a division of application Ser. No. 11/937,024, filed Nov. 8, 2007, now U.S. Pat. No. 7,800,160 and is based upon and claims the benefit of priority from prior Japanese Patent Application No. 2006-304364, filed Nov. 9, 2006, the entire contents of all of which are incorporated herein by reference.

# BACKGROUND OF THE INVENTION

1. Field of the Invention

The present invention relates to a semiconductor device.

2. Description of the Related Art

In recent years, nonvolatile memories, such as NAND flash memories, have widely been developed and manufactured. A memory cell transistor of the nonvolatile memory includes a tunnel insulation film formed on a semiconductor substrate, a floating gate electrode formed on the tunnel insulation film, 25 an inter-electrode insulation film formed on the floating gate electrode, and a control gate electrode formed on the interelectrode insulation film.

In normal cases, since a silicon oxide film is used for the tunnel insulation film, an oxidizing agent easily enters the <sup>30</sup> tunnel insulation film during a fabrication process. As a result, so-called bird's beak oxidation occurs, leading to an increase in operation voltage of the memory cell transistor and degradation in reliability.

It is possible to suppress progress of bird's beak oxidation <sup>35</sup> by providing nitride films on the upper and lower surfaces of the tunnel insulation film. Jpn. Pat. Appln. KOKAI Publication No. 2002-353343, for instance, discloses a structure in which oxinitride films are provided on the upper and lower surfaces of the tunnel insulation film. However, if nitride <sup>40</sup> films are provided, charge trap density and positive fixed charge density increase, leading to degradation in characteristics and reliability.

The above-described problem may similarly occur with respect to the inter-electrode insulation film of the memory <sup>45</sup> cell transistor. Furthermore, the above-described problem may similarly occur with respect to gate insulation films of a peripheral circuit transistor and a select gate transistor in a NAND flash memory.

As has been described above, in the prior art, no effective <sup>50</sup> solution to the problems with the bird's beak oxidation has been proposed, and it has been difficult to obtain a semiconductor device with excellent characteristics and reliability.

# BRIEF SUMMARY OF THE INVENTION

55

A first aspect of the present invention, there is provided a semiconductor device comprising: a tunnel insulation film formed on a semiconductor substrate; a floating gate electrode formed on the tunnel insulation film; an inter-electrode 60 insulation film formed on the floating gate electrode; a control gate electrode formed on the inter-electrode insulation film; a pair of oxide films which are formed between the tunnel insulation film and the floating gate electrode and are formed near lower end portions of a pair of side surfaces of the 65 floating gate electrode, which are parallel in one of a channel width direction and a channel length direction; and a nitride

film which is formed between the tunnel insulation film and the floating gate electrode and is formed between the pair of oxide films.

A second aspect of the present invention, there is provided 5 a semiconductor device comprising: a tunnel insulation film formed on a semiconductor substrate; a floating gate electrode formed on the tunnel insulation film; an inter-electrode insulation film formed on the floating gate electrode; a control gate electrode formed on the inter-electrode insulation film; a pair of first oxide films which are formed between the floating gate electrode and the inter-electrode insulation film and are formed near upper end portions of a pair of side surfaces of the floating gate electrode, which are parallel in a channel width direction; a first nitride film which is formed between the 15 floating gate electrode and the inter-electrode insulation film and is formed between the pair of first oxide films; a pair of second oxide films which are formed between the inter-electrode insulation film and the control gate electrode and are formed near lower end portions of a pair of side surfaces of the 20 control gate electrode, which are parallel in a channel width direction; and a second nitride film which is formed between the inter-electrode insulation film and the control gate electrode and is formed between the pair of second oxide films.

A third aspect of the present invention, there is provided a semiconductor device comprising: a gate insulation film formed on a semiconductor substrate; a gate electrode formed on the gate insulation film; a pair of oxide films which are formed between the gate insulation film and the gate electrode and are formed near lower end portions of a pair of side surfaces of the gate electrode, which are parallel in one of a channel width direction and a channel length direction; and a nitride film which is formed between the gate insulation film and the gate electrode films.

A fourth aspect of the present invention, there is provided a semiconductor device comprising: a memory cell transistor including: a tunnel insulation film formed on a semiconductor substrate; a floating gate electrode formed on the tunnel insulation film; an inter-electrode insulation film formed on the floating gate electrode; a control gate electrode formed on the inter-electrode insulation film; and a first nitride film which is formed between the tunnel insulation film and the floating gate electrode; and a peripheral circuit transistor including: a gate insulation film formed on the semiconductor substrate; a gate electrode formed on the gate insulation film; and a second nitride film which is formed between the gate insulation film and the gate electrode and includes a pair of portions which are formed near lower end portions of a pair of side surfaces of the gate electrode, which are parallel in one of a channel width direction and a channel length direction, the pair of portions being spaced apart from each other.

### BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWING

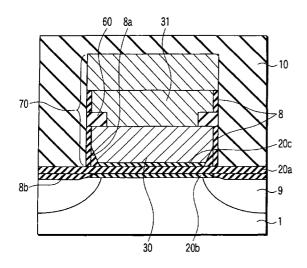

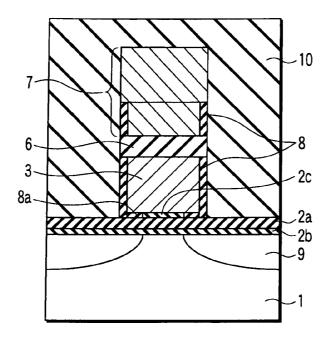

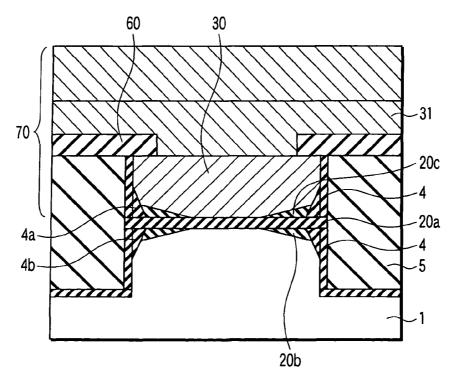

FIG. **1** is a cross-sectional view that schematically shows the structure of a semiconductor device according to a first embodiment of the present invention;

FIG. **2** is a cross-sectional view that schematically shows the structure of a semiconductor device according to a modification of the first embodiment of the invention;

FIG. **3** is a cross-sectional view that schematically shows the structure of a semiconductor device according to another modification of the first embodiment of the invention;

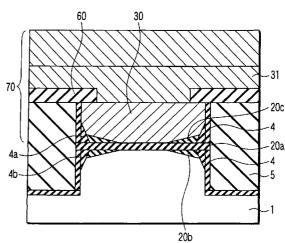

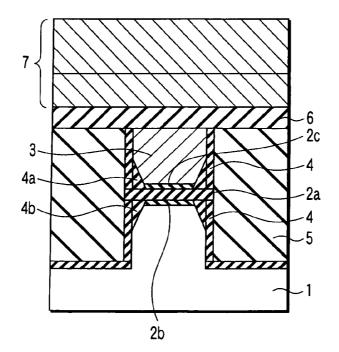

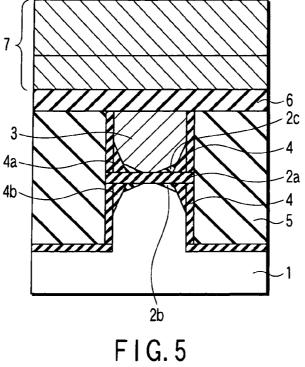

FIG. **4** is a cross-sectional view that schematically shows the structure of a semiconductor device according to a second embodiment of the present invention; FIG. **5** is a cross-sectional view that schematically shows the structure of a semiconductor device according to a modification of the second embodiment of the invention;

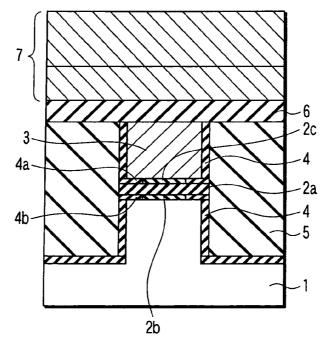

FIG. **6** is a cross-sectional view that schematically shows the structure of a semiconductor device according to another 5 modification of the second embodiment of the invention;

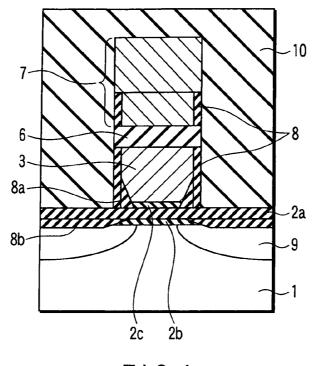

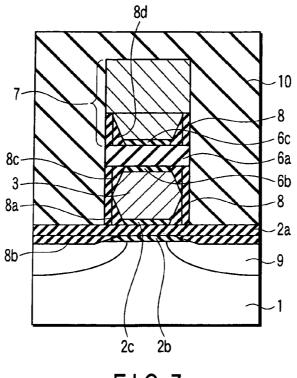

FIG. **7** is a cross-sectional view that schematically shows the structure of a semiconductor device according to a third embodiment of the present invention;

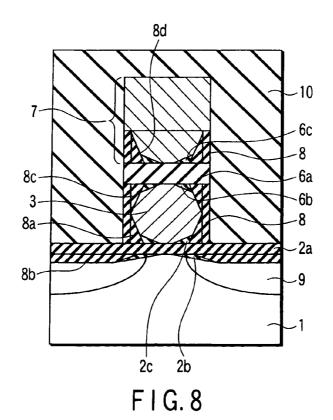

FIG. **8** is a cross-sectional view that schematically shows 10 the structure of a semiconductor device according to a modification of the third embodiment of the invention;

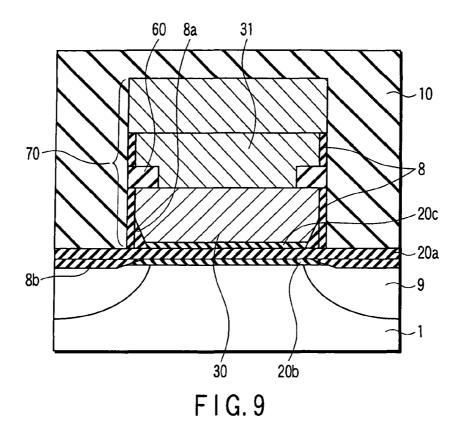

FIG. 9 is a cross-sectional view that schematically shows the structure of a semiconductor device according to a fourth embodiment of the present invention;

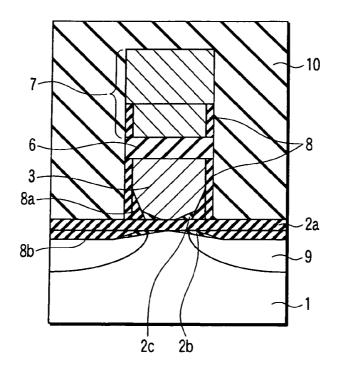

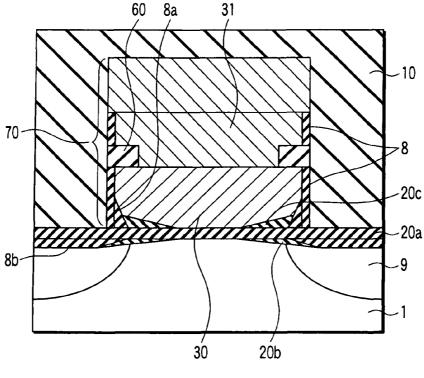

FIG. **10** is a cross-sectional view that schematically shows the structure of a semiconductor device according to a modification of the fourth embodiment of the invention;

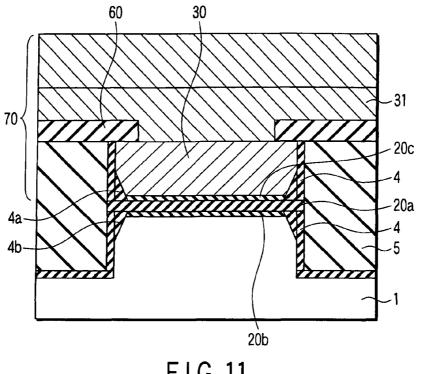

FIG. **11** is a cross-sectional view that schematically shows the structure of a semiconductor device according to a fifth 20 embodiment of the present invention;

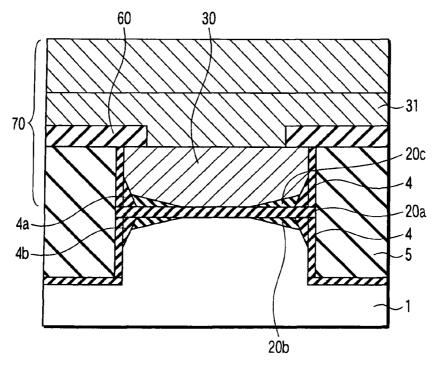

FIG. **12** is a cross-sectional view that schematically shows the structure of a semiconductor device according to a modification of the fifth embodiment of the invention;

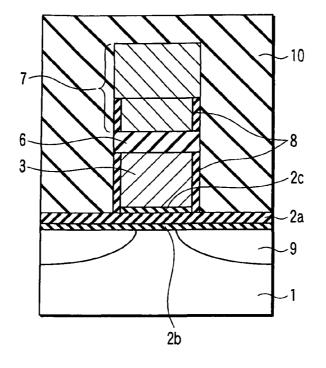

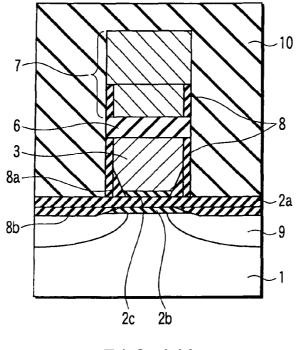

FIG. **13**A and FIG. **13**B are cross-sectional views that 25 schematically show the structure of a semiconductor device according to a sixth embodiment of the present invention;

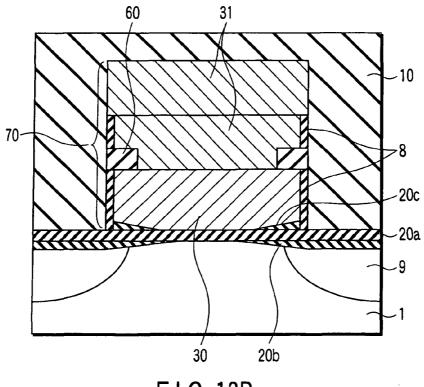

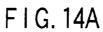

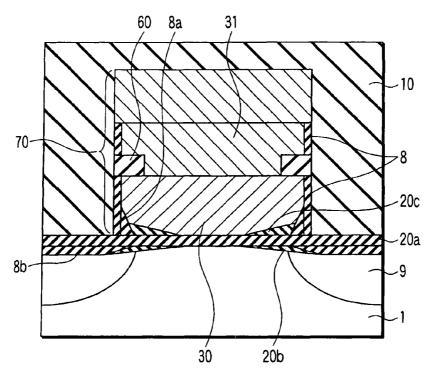

FIG. **14**A and FIG. **14**B are cross-sectional views that schematically show the structure of a semiconductor device according to a modification of the sixth embodiment of the 30 invention;

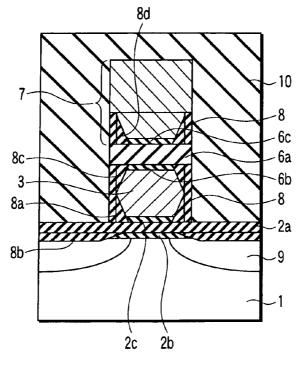

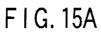

FIG. **15**A and FIG. **15**B are cross-sectional views that schematically show the structure of a semiconductor device according to another modification of the sixth embodiment of the invention;

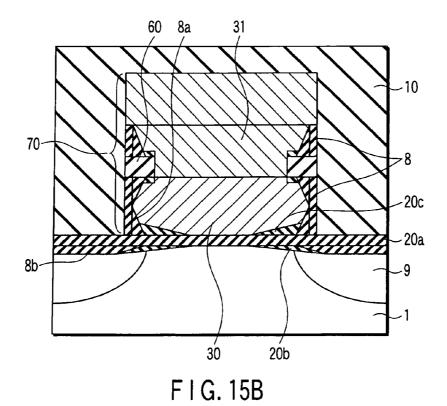

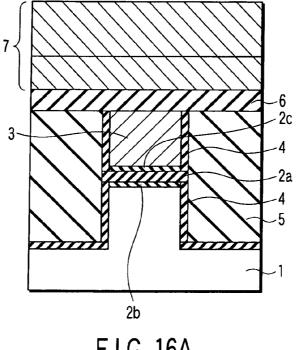

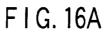

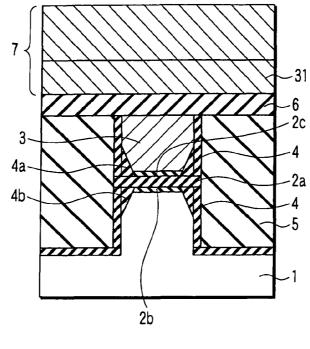

FIG. **16**A and FIG. **16**B are cross-sectional views that schematically show the structure of a semiconductor device according to a seventh embodiment of the present invention;

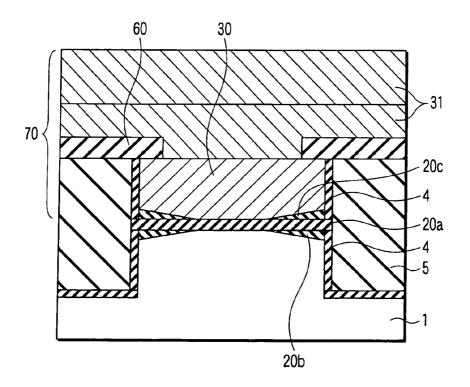

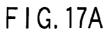

FIG. **17**A and FIG. **17**B are cross-sectional views that schematically show the structure of a semiconductor device 40 according to a modification of the seventh embodiment of the invention;

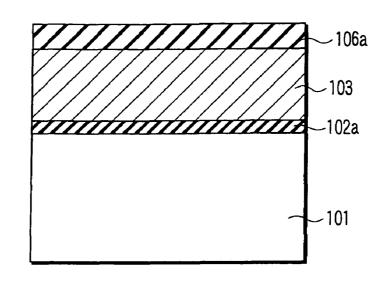

FIG. **18**A and FIG. **18**B are cross-sectional views that schematically show a fabrication step of a semiconductor device according to an eighth embodiment of the present 45 invention;

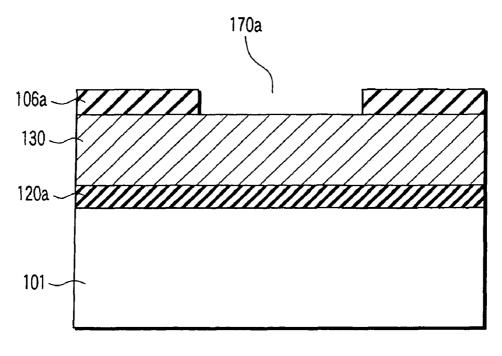

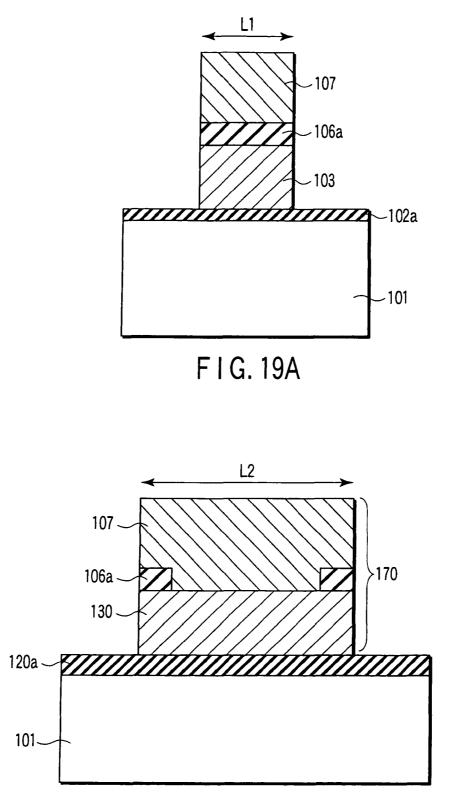

FIG. **19**A and FIG. **19**B are cross-sectional views that schematically show a fabrication step of the semiconductor device according to the eighth embodiment of the invention;

FIG. **20**A and FIG. **20**B are cross-sectional views that 50 schematically show a fabrication step of the semiconductor device according to the eighth embodiment of the invention;

FIG. **21**A and FIG. **21**B are cross-sectional views that schematically show a fabrication step of the semiconductor device according to the eighth embodiment of the invention; 55

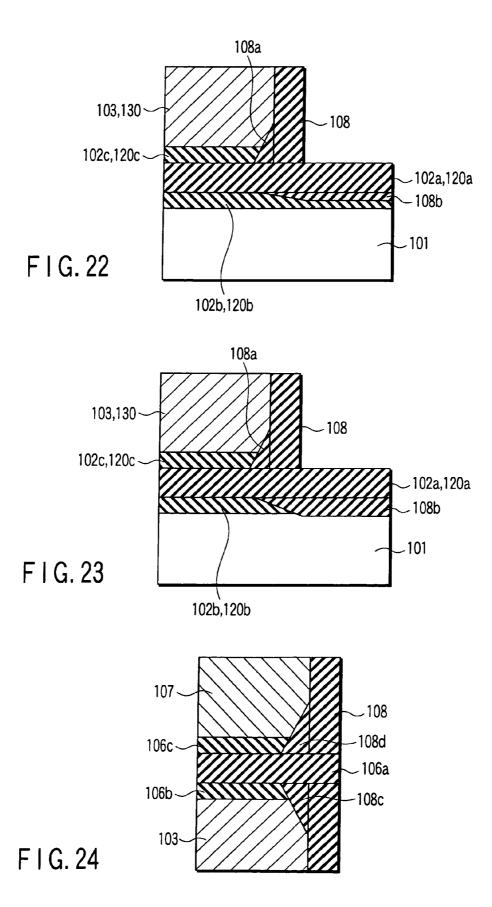

FIG. **22** is a view relating to the fabrication method of the semiconductor device according to the eighth embodiment of the invention, and shows a part of the structure in enlarged scale;

FIG. **23** is a view relating to the fabrication method of the <sup>60</sup> semiconductor device according to the eighth embodiment of the invention, and shows a part of the structure in enlarged scale;

FIG. **24** is a view relating to the fabrication method of the semiconductor device according to the eighth embodiment of 65 the invention, and shows a part of the structure in enlarged scale;

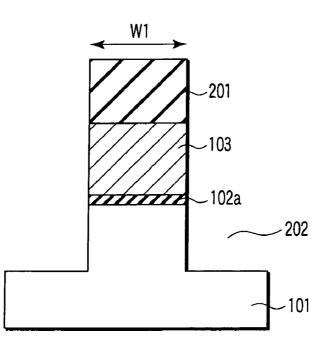

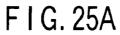

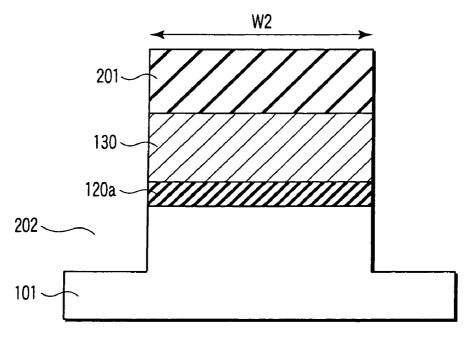

FIG. **25**A and FIG. **25**B are cross-sectional views that schematically show a fabrication step of a semiconductor device according to a ninth embodiment of the present invention;

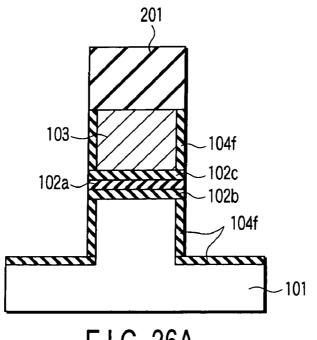

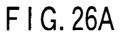

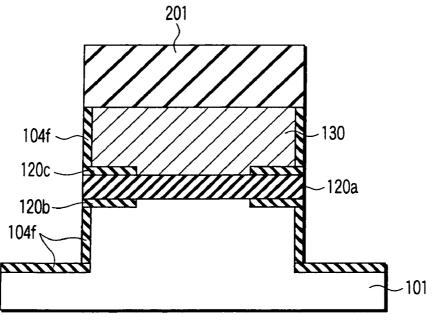

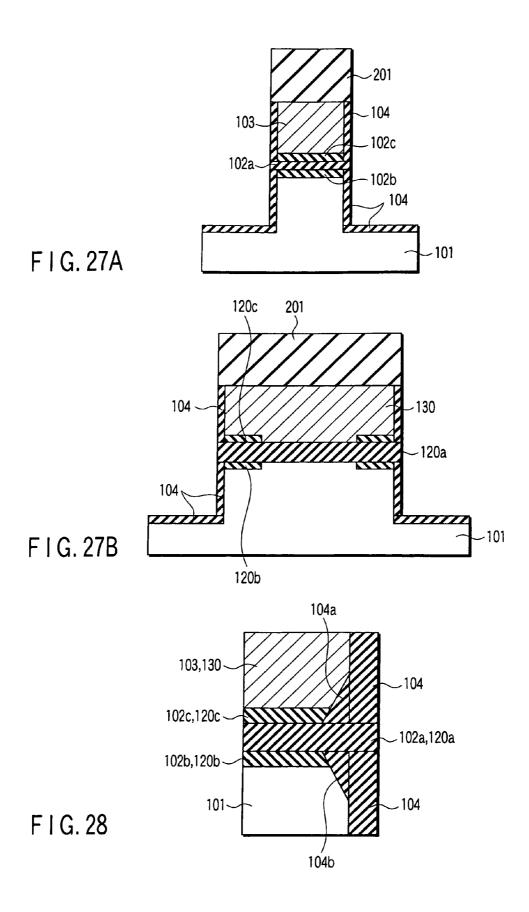

FIG. **26**A and FIG. **26**B are cross-sectional views that schematically show a fabrication step of the semiconductor device according to the ninth embodiment of the invention;

FIG. **27**A and FIG. **27**B are cross-sectional views that schematically show a fabrication step of the semiconductor device according to the ninth embodiment of the invention; and

FIG. **28** is a view relating to the fabrication method of the semiconductor device according to the ninth embodiment of the invention, and shows a part of the structure in enlarged scale.

# DETAILED DESCRIPTION OF THE INVENTION

Embodiments of the present invention will now be described with reference to the accompanying drawings. In the embodiments, nonvolatile memories, such as NAND flash memories, are exemplified as semiconductor devices.

#### Embodiment 1

FIG. 1 is a cross-sectional view that schematically shows the structure of a semiconductor device according to a first embodiment of the present invention. Specifically, FIG. 1 is a cross-sectional view taken along a channel length direction (bit line direction) of a memory cell transistor of a nonvolatile memory.

The memory cell transistor is formed in a device formation region which is surrounded by isolation insulation films (not shown). Specifically, the memory cell transistor includes a tunnel insulation film 2a formed on a semiconductor substrate 1, a floating gate electrode 3 formed on the tunnel insulation film 2a, an inter-electrode insulation film 6 formed on the floating gate electrode 3, and a control gate electrode 7 formed on the inter-electrode insulation film 6. A pair of impurity diffusion layers 9, which become source/drain regions, are formed in a surface region of the semiconductor substrate 1. A region between the pair of impurity diffusion layers 9 becomes a channel region. Electrode sidewall oxide films 8 are formed on sidewalls of the floating gate electrode 3 and on sidewalls of the control gate electrode 7. Further, the memory cell transistor is covered with an interlayer insulation film 10.

A pair of oxide films 8a is formed on inner sides of the electrode sidewall oxide films 8. The pair of oxide films 8a are formed between the tunnel insulation film 2a and the floating gate electrode 3 and are formed near lower ends of a pair of side surfaces of the floating gate electrode 3 (i.e. a pair of side surfaces which are parallel in the channel width direction). Each of the oxide films 8a has a wedge shape with a width gradually increasing from an upper side toward a lower side.

A nitride film 2c is formed on an upper surface of the tunnel insulation film 2a. The nitride film 2c is formed between the tunnel insulation film 2a and the floating gate electrode 3, and is formed between the pair of oxide films 8a.

A pair of oxide films 8b is formed on a lower surface of the tunnel insulation film 2a. A distal end of each of the oxide films 8b is positioned on the inside of an extension plane of the interface between the electrode sidewall oxide film 8 and the floating gate electrode 3. A nitride film 2b is formed on a lower surface of the tunnel insulation film 2a. The nitride film 2b is formed between the pair of oxide films 8b.

In this description, the film 2a is referred to as "tunnel insulation film". However, a stack film of the films 2a, 2b and 2c substantially functions as the tunnel insulation film.

A silicon substrate is used as the semiconductor substrate 1, and the floating gate electrode 3 is formed of a silicon film. 5 A lower layer portion of the control gate electrode 7 (i.e. a portion inside the electrode sidewall oxide films 8) is formed of a silicon film, and an upper layer portion of the control gate electrode 7 is formed of, e.g. a metal film.

The tunnel insulation film 2a is formed of a silicon oxide 10 film which contains silicon and oxygen as major components. Nitrogen may be contained in the silicon oxide film. The nitride film 2b and nitride film 2c are formed of silicon nitride films which contain silicon and nitrogen as major components. Oxygen may be contained in the silicon nitride films. 15 The nitride film 2b and nitride film 2c may be silicon oxynitride films having nitrogen concentration higher than oxygen concentration. The oxide films 8a, oxide films 8b and electrode sidewall oxide films 8 are formed of silicon oxide films which contain silicon and oxygen as major components. 20 Nitrogen may be contained in the silicon oxide films.

As has been described above, in the present embodiment, the nitride film 2c is formed on the upper surface of the tunnel insulation film 2a, and the nitride film 2b is formed on the lower surface of the tunnel insulation film 2a. Progress of 25 bird's beak oxidation during the fabrication process can be prevented by the nitride films 2b and 2c. Therefore, an increase of write/erase operation voltage can be suppressed, and degradation in reliability of the memory cell transistor can effectively be suppressed. 30

In the present embodiment, the oxide films 8a are formed at both end portions of the nitride film 2c. Specifically, in the vicinity of the lower end portions of the floating gate electrode 3, the oxide films 8a are present between the floating gate electrode 3 and the tunnel insulation film 2a, and the 35 nitride film 2c is not present between the floating gate electrode 3 and the tunnel insulation film 2a. Thus, in the vicinity of the lower end portions of the floating gate electrode 3, there is no charge trap state due to the nitride film 2c. Therefore, at the time of the rewriting operation which makes use of a 40 tunnel current or a hot carrier current, the charge trap amount can be reduced near the lower end portions of the floating gate electrode 3, and the reliability of the memory cell transistor can greatly be improved. Moreover, in the present embodiment, the oxide films 8b are formed at both end portions of the 45 nitride film 2b. Thereby, the charge trap amount near the lower end portions of the floating gate electrode 3 can further be reduced, and the reliability of the memory cell transistor can greatly be improved.

Therefore, the present embodiment can provide a memory 50 cell transistor with excellent characteristics and reliability, wherein the progress of bird's beak oxidation can be suppressed and the charge trap amount can be reduced.

Next, the outline of the fabrication process of the semiconductor device shown in FIG. 1 is described.

To begin with, a nitride film (silicon nitride film) 2b, a tunnel insulation film (silicon oxide film) 2a and a nitride film (silicon nitride film) 2c are successively formed on the surface of the semiconductor substrate 1. Subsequently, a phosphorus-doped polysilicon film is formed as a floating gate 60 electrode film on the nitride film 2c. Then, the floating gate electrode film, nitride film 2c, tunnel insulation film 2a, nitride film 2b and semiconductor substrate 1 are patterned, thereby isolation trenches (not shown) are formed. After isolation insulation films (not shown) are formed in the isolation 65 trenches, an inter-electrode film is formed on the inter-electrode

insulation film **6**. Subsequently, the control electrode film, inter-electrode insulation film **6** and floating gate electrode film are patterned, thereby a control electrode **7** and a floating gate electrode **3** are formed.

Thereafter, an oxidizing process is performed in an atmosphere containing oxygen radicals. Thereby, electrode sidewall oxide films 8 are formed on side surfaces of the electrodes. In addition, by this oxidizing process, oxide films 8a and oxide films 8b are formed. The oxygen radicals can not easily enter the silicon nitride films, but can easily enter the silicon oxide films. At this time, since the oxygen radicals and silicon oxide films react easily, the length of entrance is less than in cases of ordinary oxygen gas and water vapor, and is typically 10 nm or less. Since the oxygen radicals can transform the silicon nitride film surfaces into silicon oxide films, the silicon nitride films provided on the upper and lower sides of the region, where the oxygen radicals have entered, can easily be changed into silicon oxide films by choosing proper oxidizing process conditions. As a result, the oxide films 8aand oxide films 8b, as shown in FIG. 1, can be formed.

FIG. 2 is a cross-sectional view that schematically shows the structure of a semiconductor device according to a modification of the first embodiment. Specifically, FIG. 2 is a cross-sectional view taken along the channel length direction (bit line direction) of the memory cell transistor of the nonvolatile memory. The basic structure is the same as shown in FIG. 1. Thus, a detailed description of the parts common to those described with reference to FIG. 1 is omitted here.

In the modification shown in FIG. 2, the nitride films 2b and 2c are formed near lower end portions of the floating gate electrode 3, and are not formed near a central portion of the floating gate electrode 3. Specifically, the nitride film 2c includes a pair of portions which are formed near lower ends of a pair of side surfaces of the floating gate electrode 3 (i.e. a pair of side surfaces which are parallel in the channel width direction), and the pair of portions are spaced apart. Similarly, the nitride film 2b, like the nitride film 2c, includes a pair of portions which are spaced apart.

In this modification, too, the same advantageous effects as with the memory cell transistor shown in FIG. 1 can be obtained. In this modification, however, compared to the structure shown in FIG. 1, the effect of suppressing the bird's beak oxidation decreases. It is thus necessary to restrict process conditions, for example, to lower the process temperature in the oxidation step in the semiconductor device fabrication process. Instead, by virtue of the absence of the nitride film in the central region of the channel, scattering of carriers flowing in the cannel hardly occurs, which is considered to occur due to fixed charge that is present in the nitride film. As a result, the mobility of the carriers increases, and the oncurrent of the transistor can be increased. In addition, since the positive fixed charge density decreases, the threshold voltage of the transistor rises and the off-current of the transistor can be decreased.

Next, the outline of the fabrication process of the semiconductor device shown in FIG. **2** is described.

To begin with, a tunnel insulation film (silicon oxide film) 2a is formed on the surface of the semiconductor substrate 1. Subsequently, a phosphorus-doped polysilicon film is formed as a floating gate electrode film on the tunnel insulation film 2a. Then, the floating gate electrode film, tunnel insulation film 2a and semiconductor substrate 1 are patterned, thereby isolation trenches (not shown) are formed. After isolation trenches, an inter-electrode insulation film 6 is formed. Further, a control electrode film is formed on the inter-electrode insulation film 6. Subsequently, the control electrode film,

inter-electrode insulation film 6 and floating gate electrode film are patterned, thereby a control electrode 7 and a floating gate electrode 3 are formed.

Thereafter, a thermal nitriding process is performed in an atmosphere containing a nitriding gas such as nitric oxide gas, nitrous oxide gas or ammonia gas. In this thermal nitriding process, the process conditions are so set that the diffusion length of the nitriding gas in the silicon oxide film may become less than half the channel length. Thereby, the silicon nitride film 2b and silicon nitride film 2c, as shown in FIG. 2, 10 can be formed. At the same time, silicon oxinitride films or silicon nitride films are formed on sidewalls of the electrodes. Subsequently, an oxidizing process is performed in an atmosphere containing oxygen radicals. Thereby, oxide films 8a and  $\mathbf{8}b$  are formed. In addition, the silicon oxinitride films or 13silicon nitride films formed on the electrode sidewalls are transformed into silicon oxide films, and the electrode sidewall oxide films 8 are formed.

FIG. 3 is a cross-sectional view that schematically shows the structure of a semiconductor device according to another 20 modification of the first embodiment. Specifically, FIG. 3 is a cross-sectional view taken along the channel length direction (bit line direction) of the memory cell transistor of the nonvolatile memory. The basic structure is the same as shown in FIG. 1 and FIG. 2. Thus, a detailed description of the parts 25 common to those described with reference to FIG. 1 and FIG. 2 is omitted here.

In the modification shown in FIG. 2, each of the oxide films 8a has a wedge shape. In the modification shown in FIG. 3, each of the oxide films 8a has a rectangular shape.

In this modification, too, the same advantageous effects as with the memory cell transistors shown in FIG. 1 and FIG. 2 can be obtained. In the structures shown in FIG. 1 and FIG. 2, since the angles at lower end corners of the floating gate electrode 3 are large (typically, larger than 90 degree), the 35 concentration of electric field can be suppressed. In the structure shown in FIG. 3, since the angles at lower end corners of the floating gate electrode 3 are not large, there is a possibility that tunnel current may concentrate due to the concentration of electric field. However, since no nitride films are present at 40 the nitride film 2c is formed on the upper surface of the tunnel the regions where the current concentrates, a variation of the threshold voltage hardly occurs due to charge trap.

Next, the outline of the fabrication process of the semiconductor device shown in FIG. 3 is described.

To begin with, by the same method as described with 45 reference to FIG. 1, the control electrode 7 and floating gate electrode 3 are formed. Then, using a chemical such as hot phosphoric acid, the silicon nitride film 2c is selectively etched. At this time, the silicon nitride film 2c near lower end portions of the floating gate electrode 3 can be removed by 50 controlling the etching time and etching temperatures. Thereafter, a thermal oxidation process is performed in an atmosphere containing an oxidizing gas such as oxygen gas or water vapor. Thereby, electrode sidewall oxide films 8 are formed on side surfaces of the floating gate electrode 3 and 55 control electrode 7. In addition, by this oxidizing process, oxide films 8a are formed near lower end portions of the floating gate electrode 3.

#### Embodiment 2

60

FIG. 4 is a cross-sectional view that schematically shows the structure of a semiconductor device according to a second embodiment of the invention. Specifically, FIG. 4 is a crosssectional view taken along the channel width direction (word 65 line direction) of a memory cell transistor of the nonvolatile memory. The basic structure is the same as shown in FIG. 1.

Thus, a detailed description of the parts common to those described with reference to FIG. 1 is omitted here.

As shown in FIG. 4, the memory cell transistor is formed in a device formation region which is surrounded by isolation insulation films 5. The isolation insulation films 5 are buried in isolation trenches, and isolation trench sidewall insulation films 4 are formed on surfaces of the isolation trenches.

A pair of oxide films 4a and a pair of oxide films 4b are formed on inner sides of the isolation trench sidewall insulation films 4. The pair of oxide films 4a are formed between the tunnel insulation film 2a and floating gate electrode 3 and are formed near lower ends of a pair of side surfaces of the floating gate electrode 3 (i.e. a pair of side surfaces which are parallel in the channel length direction). Each of the oxide films 4a has a wedge shape with a width gradually increasing from an upper side toward a lower side. The pair of oxide films 4b are formed between the tunnel insulation film 2a and the device formation region of the semiconductor substrate 1, and are formed near upper ends of a pair of side surfaces of the device formation region (i.e. a pair of side surfaces which are parallel in the channel length direction). Each of the oxide films 4b has a wedge shape with a width gradually increasing from a lower side toward an upper side.

A nitride film 2c is formed on an upper surface of the tunnel insulation film 2a. The nitride film 2c is formed between the tunnel insulation film 2a and the floating gate electrode 3, and is formed between the pair of oxide films 4a. A nitride film 2bis formed on a lower surface of the tunnel insulation film 2a. The nitride film 2b is formed between the tunnel insulation film 2a and the device formation region of the semiconductor substrate 1, and is formed between the pair of oxide films 4b.

The materials of the tunnel insulation film 2a, nitride film 2b and nitride film 2c are the same as described in the first embodiment. The oxide films 4a, oxide films 4b and isolation trench sidewall insulation films 4 are formed of silicon oxide films which contain silicon and oxygen as major components. Nitrogen may be contained in the silicon oxide films.

As has been described above, in the present embodiment, insulation film 2a, and the nitride film 2b is formed on the lower surface of the tunnel insulation film 2a. Progress of bird's beak oxidation during the fabrication process can be prevented by the nitride films 2b and 2c. Therefore, an increase of write/erase operation voltage can be suppressed, and degradation in reliability of the memory cell transistor can effectively be suppressed.

In addition, in the present embodiment, the oxide films 4aare formed at both end portions of the nitride film 2c. Specifically, in the vicinity of the lower end portions of the floating gate electrode 3, the oxide films 4a are present between the floating gate electrode 3 and the tunnel insulation film 2a, and the nitride film 2c is not present between the floating gate electrode 3 and the tunnel insulation film 2a. Thus, in the vicinity of the lower end portions of the floating gate electrode 3, there is no positive fixed charge or charge trap state due to the nitride film 2c. Therefore, the off-current of the memory cell transistor can be reduced and malfunction can be prevented, and the reliability of the memory cell transistor can greatly be improved. Moreover, in the present embodiment, the oxide films 4b are formed at both end portions of the nitride film 2b. Therefore, the positive fixed charge and the charge trap state can further be reduced, and the reliability of the memory cell transistor can greatly be improved.

Therefore, the present embodiment can provide a memory cell transistor with excellent characteristics and reliability, wherein the progress of bird's beak oxidation can be suppressed and the fixed charge amount can be reduced.

Next, the outline of the fabrication process of the semiconductor device shown in FIG. **4** is described.

To begin with, a nitride film (silicon nitride film) 2b, a 5 tunnel insulation film (silicon oxide film) 2a and a nitride film (silicon nitride film) 2c are successively formed on the surface of the semiconductor substrate 1. Subsequently, a phosphorus-doped polysilicon film is formed as a floating gate electrode film on the nitride film 2c. Then, the floating gate 10 electrode film, nitride film 2c, tunnel insulation film 2a, nitride film 2b and semiconductor substrate 1 are patterned, thereby isolation trenches are formed.

Thereafter, an oxidizing process is performed in an atmosphere containing oxygen radicals. Thereby, isolation trench sidewall oxide films 4 are formed on side surfaces of the isolation trenches. In addition, by this oxidizing process, oxide films 4a and oxide films 4b are formed. The oxygen radicals can not easily enter the silicon nitride films, but can easily enter the silicon oxide films. At this time, since the 20 oxygen radicals and silicon oxide films react easily, the length of entrance is less than in cases of ordinary oxygen gas and water vapor, and is typically 10 nm or less. Since the oxygen radicals can transform the silicon nitride film surfaces into silicon oxide films, the silicon nitride films provided on the 25 upper and lower sides of the region, where the oxygen radicals have entered, can easily be changed into silicon oxide films by choosing proper oxidizing process conditions. As a result, the oxide films 4a and oxide films 4b, as shown in FIG. 4, can be formed. Thereafter, isolation insulation films 5 are 30 formed in the isolation trenches, and an inter-electrode insulation film and a control electrode film are formed. Further, the control electrode film, inter-electrode insulation film and floating gate electrode film are patterned, thereby a control electrode 7 and a floating gate electrode 3 are formed.

FIG. **5** is a cross-sectional view that schematically shows the structure of a semiconductor device according to a modification of the second embodiment. Specifically, FIG. **5** is a cross-sectional view taken along the channel width direction (word line direction) of the memory cell transistor of the 40 nonvolatile memory. The basic structure is the same as shown in FIG. **4**. Thus, a detailed description of the parts common to those described with reference to FIG. **4** is omitted here.

In the modification shown in FIG. 5, the nitride films 2b and 2c are formed near lower end portions of the floating gate 45 electrode 3, and are not formed near a central portion of the floating gate electrode 3. Specifically, the nitride film 2c includes a pair of portions which are formed near lower ends of a pair of side surfaces of the floating gate electrode 3 (i.e. a pair of side surfaces which are parallel in the channel length 50 direction), and the pair of portions are spaced apart. Similarly, the nitride film 2b, like the nitride film 2c, includes a pair of portions which are spaced apart.

In this modification, too, the same advantageous effects as with the memory cell transistor shown in FIG. **4** can be 55 obtained. In this modification, however, compared to the structure shown in FIG. **4**, the effect of suppressing the bird's beak oxidation decreases. It is thus necessary to restrict process conditions. Instead, by virtue of the absence of the nitride film in the central region of the channel, scattering of carriers 60 flowing in the channel hardly occurs. As a result, the mobility of the carriers increases, and the on-current of the transistor can be increased.

Next, the outline of the fabrication process of the semiconductor device shown in FIG. **5** is described.

65

To begin with, a tunnel insulation film (silicon oxide film) 2a is formed on the surface of the semiconductor substrate 1.

Subsequently, a phosphorus-doped polysilicon film is formed as a floating gate electrode film on the tunnel insulation film 2a. Then, the floating gate electrode film, tunnel insulation film 2a and semiconductor substrate 1 are patterned, thereby isolation trenches are formed.

Thereafter, a thermal nitriding process is performed in an atmosphere containing nitric oxide gas. In this thermal nitriding process, the process conditions are so set that the diffusion length of the nitric oxide gas in the silicon oxide film may become less than half the channel width. Thereby, the silicon nitride film 2b and silicon nitride film 2c, as shown in FIG. 5, can be formed. At the same time, silicon oxinitride films are formed on side surfaces of the isolation trenches. Subsequently, an oxidizing process is performed in an atmosphere containing oxygen radicals. Thereby, oxide films 4a and 4b are formed. In addition, the silicon oxinitride films which are formed on the side surfaces of the isolation trenches are transformed into silicon oxide films, and the isolation trench sidewall oxide films 4 are formed.

After isolation insulation films 5 are formed in the isolation trenches, an inter-electrode insulation film 6 is formed. Further, a control electrode film 7 is formed on the inter-electrode insulation film 6. Subsequently, the control electrode film 7, inter-electrode insulation film 6 and floating gate electrode film 3 are patterned, thereby a control electrode 7 and a floating gate electrode 3 are formed.

FIG. 6 is a cross-sectional view that schematically shows the structure of a semiconductor device according to another modification of the second embodiment. Specifically, FIG. 6

<sup>30</sup> is a cross-sectional view taken along the channel width direction (word line direction) of the memory cell transistor of the nonvolatile memory. The basic structure is the same as shown in FIG. 4 and FIG. 5. Thus, a detailed description of the parts common to those described with reference to FIG. 4 and FIG.

<sup>35</sup> 5 is omitted here.

In the modification shown in FIG. 5, each of the oxide films 4a and 4b has a wedge shape. In the modification shown in FIG. 6, each of the oxide films 4a and 4b has a rectangular shape.

In this modification, too, the same advantageous effects as with the memory cell transistors shown in FIG. 4 and FIG. 5 can be obtained. In the structures shown in FIG. 4 and FIG. 5, since the angles at lower end corners of the floating gate electrode 3 are large (typically, larger than 90 degree), the concentration of electric field can be suppressed. In the structure shown in FIG. 6, since the angles at lower end corners of the floating gate electrode 3 are not large, there is a possibility that the concentration of electric field may increase. However, since no nitride films are present at the regions where the electric field concentrates, an increase of off-current due to fixed charge hardly occurs.

The semiconductor device shown in FIG. 6 can be fabricated by a method similar to that shown in FIG. 3.

#### Embodiment 3

FIG. 7 is a cross-sectional view that schematically shows the structure of a semiconductor device according to a third embodiment of the present invention. Specifically, FIG. 7 is a cross-sectional view taken along a channel length direction (bit line direction) of a memory cell transistor of the nonvolatile memory. The basic structure is the same as that of the first embodiment shown in FIG. 1. Thus, a detailed description of the parts common to those described with reference to FIG. 1 is omitted here.

In the semiconductor device shown in FIG. 7, a pair of oxide films 8c is formed on inner sides of the electrode side-

wall oxide films 8. The pair of oxide films 8c are formed between the floating gate electrode 3 and inter-electrode insulation film 6a, and are formed near upper ends of a pair of side surfaces of the floating gate electrode 3 (i.e. a pair of side surfaces which are parallel in the channel width direction). 5 Each of the oxide films 8c has a wedge shape with a width gradually increasing from a lower side toward an upper side. In addition, a nitride film 6b is formed on a lower surface of the inter-electrode insulation film 6a. The nitride film 6b is formed between the floating gate electrode 3 and the inter- 10 electrode insulation film 6a, and is formed between the pair of oxide films 8c.

Besides, in the semiconductor device shown in FIG. 7, a pair of oxide films 8d is formed on inner sides of the electrode sidewall oxide films 8. The pair of oxide films 8d are formed 15 between the inter-electrode insulation film 6a and the control gate electrode 7, and are formed near lower ends of a pair of side surfaces of the control gate electrode 7 (i.e. a pair of side surfaces which are parallel in the channel width direction). Each of the oxide films 8d has a wedge shape with a width 20 gradually increasing from an upper side toward a lower side. In addition, a nitride film 6c is formed on an upper surface of the inter-electrode insulation film 6a. The nitride film 6c is formed between the inter-electrode insulation film 6a and the control gate electrode 7, and is formed between the pair of 25 oxide films 8d.

In this description, the film 6a is referred to as "interelectrode insulation film". However, a stack film of the films 6a, 6b and 6c substantially functions as the inter-electrode insulation film.

The nitride film 6b and nitride film 6c are formed of silicon nitride films which contain silicon and nitrogen as major components. Oxygen may be contained in the silicon nitride films. The nitride film 2b and nitride film 2c may be silicon oxynitride films having nitrogen concentration higher than 35 oxygen concentration. The oxide films 8c, oxide films 8d and electrode sidewall oxide films 8 are formed of silicon oxide films which contain silicon and oxygen as major components. Nitrogen may be contained in the silicon oxide films.

The inter-electrode insulation film 6a is formed of a silicon 40 oxide film which contains silicon and oxygen as major components. Nitrogen may be contained in the silicon oxide film. The inter-electrode insulation film 6a may be a stack film (silicon oxide film/silicon nitride film/silicon oxide film) in which a silicon nitride film is interposed between silicon 45 oxide films. Alternatively, the inter-electrode insulation film 6a may be a high dielectric constant oxide film such as an aluminum oxide film (alumina) or a hafnium oxide film (hafnia). In short, the inter-electrode insulation film 6a may be an oxide film or a stack film including an oxide film.

As has been described above, in the present embodiment, the nitride film 6c is formed on the upper surface of the inter-electrode insulation film 6a, and the nitride film 6b is formed on the lower surface of the inter-electrode insulation film 6a. Progress of bird's beak oxidation during the fabrica- 55 tion process can be prevented by the nitride films 6b and 6c. Therefore, non-uniformity in rewriting characteristics of the memory cell can be suppressed, and degradation in reliability of the memory cell transistor can effectively be suppressed.

In the present embodiment, the oxide films 8c are formed at 60 both end portions of the nitride film 6b, and the oxide films 8dare formed at both end portions of the nitride film 6c. Specifically, in the vicinity of the upper end portions of the floating gate electrode 3, the oxide films 8c are present between the floating gate electrode 3 and the inter-electrode 65 insulation film 6a, and the nitride film 6b is not present between the floating gate electrode 3 and the inter-electrode

insulation film 6a. Similarly, in the vicinity of the lower end portions of the control gate electrode 7, the oxide films 8d are present between the control gate electrode 7 and the interelectrode insulation film 6a, and the nitride film 6c is not present between the control gate electrode 7 and the interelectrode insulation film 6a. Thus, in the vicinity of the end portions of the floating gate electrode 3 and control gate electrode 7, there is no charge trap state due to the nitride films 6b and 6c. Therefore, at the time of the rewriting operation of the memory cell, the charge trap amount due to leakage current flowing in the end portions of the electrodes can be reduced, and the reliability of the memory cell transistor can greatly be improved.

Therefore, the present embodiment can provide a memory cell transistor with excellent characteristics and reliability, wherein the progress of bird's beak oxidation can be suppressed and the charge trap amount can be reduced.

Next, the outline of the fabrication process of the semiconductor device shown in FIG. 7 is described.

To begin with, a nitride film (silicon nitride film) 2b, a tunnel insulation film (silicon oxide film) 2a and a nitride film (silicon nitride film) 2c are successively formed on the surface of the semiconductor substrate 1. Subsequently, a phosphorus-doped polysilicon film is formed as a floating gate electrode film on the nitride film 2c. Then, the floating gate electrode film, nitride film 2c, tunnel insulation film 2a, nitride film 2b and semiconductor substrate 1 are patterned, thereby isolation trenches (not shown) are formed. After isolation insulation films (not shown) are formed in the isolation trenches, a nitride film (silicon nitride film) 6b, an interelectrode insulation film (silicon oxide film or alumina film) 6a and a nitride film (silicon nitride film) 6c are successively formed. Further, a control electrode film 7 is formed on the nitride film 6c. Subsequently, the control electrode film 7, nitride film 6c, inter-electrode insulation film 6a, nitride film 6b and floating gate electrode film 3 are patterned, thereby a control electrode 7 and a floating gate electrode 3 are formed.

Thereafter, an oxidizing process is performed in an atmosphere containing oxygen radicals. Thereby, electrode sidewall oxide films 8 are formed on side surfaces of the electrodes. In addition, by this oxidizing process, oxide films 8a and oxide films 8b, 8c and 8d are formed. The oxygen radicals can not easily enter the silicon nitride films, but can easily enter the oxide films such as silicon oxide films and alumina films. At this time, since the oxygen radicals and oxide films react easily, the length of entrance is less than in cases of ordinary oxygen gas and water vapor, and is typically 10 nm or less. Since the oxygen radicals can transform the silicon nitride film surfaces into silicon oxide films, the silicon nitride films provided on the upper and lower sides of the regions, where the oxygen radicals have entered, can easily be changed into silicon oxide films by choosing proper oxidizing process conditions. As a result, the oxide films 8c and oxide films 8d, as shown in FIG. 7, can be formed.

FIG. 8 is a cross-sectional view that schematically shows the structure of a semiconductor device according to a modification of the third embodiment. Specifically, FIG. 8 is a cross-sectional view taken along the channel length direction (bit line direction) of the memory cell transistor of the nonvolatile memory. The basic structure is the same as shown in FIG. 7. Thus, a detailed description of the parts common to those described with reference to FIG. 7 is omitted here.

In the modification shown in FIG. 8, the nitride film 6*b* is formed near upper end portions of the floating gate electrode 3, and is not formed near a central portion of the floating gate electrode 3. Specifically, the nitride film 6b includes a pair of portions which are formed near upper ends of a pair of side

30

surfaces of the floating gate electrode 3 (i.e. a pair of side surfaces which are parallel in the channel width direction), and the pair of portions are spaced apart. Besides, the nitride film 6c is formed near lower end portions of the control gate electrode 7, and is not formed near a central portion of the 5 control gate electrode 7. Specifically, the nitride film 6cincludes a pair of portions which are formed near lower ends of a pair of side surfaces of the control gate electrode 7 (i.e. a pair of side surfaces which are parallel in the channel width direction), and the pair of portions are spaced apart.

In this modification, too, the same advantageous effects as with the memory cell transistor shown in FIG. 7 can be obtained. In this modification, however, compared to the structure shown in FIG. 7, the effect of suppressing the bird's beak oxidation decreases. It is thus necessary to restrict process conditions. Instead, by virtue of the absence of the nitride film in the central region of the inter-electrode insulation film 6a, the electrical capacitance of the substantial inter-electrode insulation film comprising the films 6a, 6b and 6c can be increased. Therefore, the write/erase operation voltage of the 20 memory cell can greatly be decreased.

The semiconductor device shown in FIG. 8 can be fabricated by combining the fabrication method of FIG. 2 and the fabrication method of FIG. 7.

In the example shown in FIG. 8, each of the oxide films  $8c_{25}$ and 8d has a wedge shape. Alternatively, like the example shown in FIG. 3, each of the oxide films 8c and 8d may be formed in a rectangular shape.

#### Embodiment 4

FIG. 9 is a cross-sectional view that schematically shows the structure of a semiconductor device according to a fourth embodiment of the present invention. Specifically, FIG. 9 is a cross-sectional view taken along a channel length direction of 35 a peripheral circuit transistor of a nonvolatile memory. The peripheral circuit transistor in this embodiment includes select gate transistor.

The peripheral circuit transistor is formed in a device formation region which is surrounded by isolation insulation 40 films (not shown). Specifically, the peripheral circuit transistor includes a gate insulation film 20a formed on a semiconductor substrate 1, and a gate electrode 70 formed on the gate insulation film 20a. A pair of impurity diffusion layers 9, which become source/drain regions, are formed in a surface 45 region of the semiconductor substrate 1.

A region between the pair of impurity diffusion layers 9 becomes a channel region. Electrode sidewall oxide films 8 are formed on sidewalls of the gate electrode 70. Further, the peripheral circuit transistor is covered with an interlayer insu- 50 lation film 10.

A pair of oxide films 8a are formed on inner sides of the electrode sidewall oxide films 8. The pair of oxide films 8a are formed between the gate insulation film 20a and the gate electrode 70 and are formed near lower ends of a pair of side 55 surfaces of the gate electrode 70 (i.e. a pair of side surfaces which are parallel in the channel width direction). Each of the oxide films 8a has a wedge shape with a width gradually increasing from an upper side toward a lower side.

A nitride film 20c is formed on an upper surface of the gate 60 insulation film 20a. The nitride film 20c is formed between the gate insulation film 20a and the gate electrode 70, and is formed between the pair of oxide films 8a.

A pair of oxide films 8b are formed on a lower surface of the gate insulation film 20a. A distal end of each of the oxide 65 films 8b is positioned on the inside of an extension plane of the interface between the electrode sidewall oxide film 8 and

a lower-layer conductive portion 30 of the gate electrode 70. A nitride film 20b is formed on a lower surface of the gate insulation film 20a. The nitride film 20b is formed between the pair of oxide films 8b.

In this description, the film 20a is referred to as "gate insulation film". However, a stack film of the films 20a, 20b and 20c substantially functions as the gate insulation film.

The structure shown in FIG. 9 is an example of the case in which the peripheral circuit transistor is formed at the same time as the memory cell transistor (e.g. the memory cell transistor shown in FIG. 1). Specifically, the lower-layer conductive portion 30 of the gate electrode 70 is formed in the same fabrication step as the floating gate electrode. Insulation portions 60 are formed in the same fabrication step as the inter-electrode insulation film. An upper-layer conductive portion 31 of the gate electrode 70 is formed in the same fabrication step as the control gate electrode.

The gate insulation film 20a is formed of a silicon oxide film which contains silicon and oxygen as major components. Nitrogen may be contained in the silicon oxide film. The nitride film 20b and nitride film 20c are formed of silicon nitride films which contain silicon and nitrogen as major components. Oxygen may be contained in the silicon nitride films. The nitride film 2b and nitride film 2c may be silicon oxynitride films having nitrogen concentration higher than oxygen concentration. The oxide films 8a, oxide films 8b and electrode sidewall oxide films 8 are formed of silicon oxide films which contain silicon and oxygen as major components. Nitrogen may be contained in the silicon oxide films.

As has been described above, in the present embodiment, the nitride film 20c is formed on the upper surface of the gate insulation film 20a, and the nitride film 20b is formed on the lower surface of the gate insulation film 20a. Progress of bird's beak oxidation during the fabrication process can be prevented by the nitride films 20b and 20c. Therefore, an increase of a threshold voltage and a decrease of the transconductance of the peripheral circuit transistor can be suppressed, and degradation of characteristics of the peripheral circuit transistor can effectively be suppressed.

In the present embodiment, the oxide films 8a are formed at both end portions of the nitride film 20c. Specifically, in the vicinity of the lower end portions of the gate electrode 70, the oxide films 8a are present between the gate electrode 70 and the gate insulation film 20a, and the nitride film 20c is not present between the gate electrode 70 and the gate insulation film 20a. Thus, in the vicinity of the lower end portions of the gate electrode 70, there is no charge trap state due to the nitride film 20c. Therefore, it is possible to reduce the charge trap amount in the vicinity of lower end portions of the gate electrode 70 due to hot carriers at the time of the transistor operation, and to greatly increase the reliability of the peripheral circuit transistor. Moreover, in the present embodiment, the oxide films 8b are formed at both end portions of the nitride film 20b. Thereby, the charge trap amount in the vicinity of the lower end portions of the gate electrode can further be reduced, and the reliability of the peripheral circuit transistor can greatly be improved.

Therefore, the present embodiment can provide a peripheral circuit transistor with excellent characteristics and reliability, wherein the progress of bird's beak oxidation can be suppressed and the charge trap amount can be reduced.

Next, the outline of the fabrication process of the semiconductor device shown in FIG. 9 is described.

To begin with, a nitride film (silicon nitride film) 20b, a gate insulation film (silicon oxide film) 20a and a nitride film (silicon nitride film) 20c are successively formed on the surface of the semiconductor substrate 1. Subsequently, a gate electrode film, which is composed of, e.g. a phosphorusdoped polysilicon film, is formed, and the gate electrode film is patterned to form a gate electrode **70**.

Thereafter, an oxidizing process is performed in an atmosphere containing oxygen radicals. Thereby, electrode sidewall oxide films 8 are formed on side surfaces of the gate electrode 70. In addition, by this oxidizing process, oxide films 8a and oxide films 8b are formed. The oxygen radicals can not easily enter the silicon nitride films, but can easily 10enter the silicon oxide films. At this time, since the oxygen radicals and silicon oxide films react easily, the length of entrance is less than in cases of ordinary oxygen gas and water vapor, and is typically 10 nm or less. Since the oxygen radicals can transform the silicon nitride film surfaces into silicon oxide films, the silicon nitride films provided on the upper and lower sides of the region, where the oxygen radicals have entered, can easily be changed into silicon oxide films by choosing proper oxidizing process conditions. As a result, the oxide films 8a and oxide films 8b, as shown in FIG. 9, can be 20 formed.

FIG. **10** is a cross-sectional view that schematically shows the structure of a semiconductor device according to a modification of the fourth embodiment. Specifically, FIG. **10** is a cross-sectional view taken along the channel length direction <sup>25</sup> of the peripheral circuit transistor of the nonvolatile memory. The basic structure is the same as shown in FIG. **9**. Thus, a detailed description of the parts common to those described with reference to FIG. **9** is omitted here.

In the modification shown in FIG. 10, the nitride films 20b <sup>30</sup> and 20c are formed near lower end portions of the gate electrode **70**, and are not formed near a central portion of the gate electrode **70**. Specifically, the nitride film 20c includes a pair of portions which are formed near lower ends of a pair of side surfaces of the gate electrode **70** (i.e. a pair of side surfaces <sup>35</sup> which are parallel in the channel width direction), and the pair of portions are spaced apart. Similarly, the nitride film **20***b*, like the nitride film **20***c*, includes a pair of portions which are spaced apart.

In this modification, too, the same advantageous effects as <sup>40</sup> with the peripheral circuit transistor shown in FIG. **9** can be obtained. In this modification, however, compared to the structure shown in FIG. **9**, the effect of suppressing the bird's beak oxidation decreases. It is thus necessary to restrict process conditions. Instead, by virtue of the absence of the nitride <sup>45</sup> film in the central region of the channel, scattering of carriers flowing in the channel hardly occurs. As a result, the mobility of carriers increases, and the on-current of the transistor can be increased. In addition, since the positive fixed charge density decreases, the threshold voltage of the transistor rises and <sup>50</sup> the off-current can be decreased.

The semiconductor device shown in FIG. **10** can be fabricated by combining the fabrication method of FIG. **2** and the fabrication method of FIG. **9**.

In the example shown in FIG. 10, each of the oxide films 8a 55 and 8b has a wedge shape. Alternatively, like the example shown in FIG. 3, each of the oxide films 8a and 8b may be formed in a rectangular shape.

#### Embodiment 5

60

FIG. **11** is a cross-sectional view that schematically shows the structure of a semiconductor device according to a fifth embodiment of the invention. Specifically, FIG. **11** is a crosssectional view taken along the channel width direction of a 65 peripheral circuit transistor of the nonvolatile memory. The basic structure is the same as that of the fourth embodiment

shown in FIG. 9. Thus, a detailed description of the parts common to those described with reference to FIG. 9 is omitted here.

As shown in FIG. 11, the peripheral circuit transistor is formed in a device formation region which is surrounded by isolation insulation films 5. The isolation insulation films 5 are buried in isolation trenches, and isolation trench sidewall insulation films 4 are formed on surfaces of the isolation trenches.

A pair of oxide films 4a and a pair of oxide films 4b are formed on inner sides of the isolation trench sidewall insulation films 4. The pair of oxide films 4a are formed between the gate insulation film 20a and gate electrode 70 and are formed near lower ends of a pair of side surfaces of the gate electrode 70 (i.e. pair of side surfaces which are parallel in the channel length direction). Each of the oxide films 4a has a wedge shape with a width gradually increasing from an upper side toward a lower side. The pair of oxide films 4b are formed between the gate insulation film 20a and the device formation region of the semiconductor substrate 1, and are formed near upper ends of a pair of side surfaces of the device formation region (i.e. a pair of side surfaces which are parallel in the channel length direction). Each of the oxide films 4b has a wedge shape with a width gradually increasing from a lower side toward an upper side.

A nitride film 20c is formed on an upper surface of the gate insulation film 20a. The nitride film 20c is formed between the gate insulation film 20a and the gate electrode 70, and is formed between the pair of oxide films 4a. A nitride film 20bis formed on a lower surface of the gate insulation film 20a. The nitride film 20b is formed between the gate insulation film 20a and the device formation region of the semiconductor substrate 1, and is formed between the pair of oxide films 4b.

The structure shown in FIG. 11 is an example of the case in which the peripheral circuit transistor is formed at the same time as the memory cell transistor (e.g. the memory cell transistor shown in FIG. 4). Specifically, the lower-layer conductive portion 30 of the gate electrode 70 is formed in the same fabrication step as the floating gate electrode. The insulation portions 60 are formed in the same fabrication step as the inter-electrode insulation film. The upper-layer conductive portion 31 of the gate electrode 70 is formed in the same fabrication step as the control gate electrode.

The materials of the gate insulation film 20a, nitride film 20b and nitride film 20c are the same as described in the fourth embodiment. The oxide films 4a, oxide films 4b and isolation trench sidewall insulation films 4 are formed of silicon oxide films which contain silicon and oxygen as major components. Nitrogen may be contained in the silicon oxide films.

As has been described above, in the present embodiment, the nitride film 20c is formed on the upper surface of the gate insulation film 20a, and the nitride film 20b is formed on the lower surface of the gate insulation film 20a. Progress of bird's beak oxidation during the fabrication process can be prevented by the nitride films 20b and 20c. Therefore, an increase of the threshold voltage and a decrease of the transconductance of the peripheral circuit transistor can be suppressed, and degradation in characteristics of the peripheral circuit transistor can effectively be suppressed.

In addition, in the present embodiment, the oxide films 4a are formed at both end portions of the nitride film 20c. Specifically, in the vicinity of the lower end portions of the gate electrode 70, the oxide films 4a are present between the gate electrode 70 and the gate insulation film 20a, and the nitride film 20c is not present between the gate electrode 70 and the

55

gate insulation film **20***a*. Thus, in the vicinity of the lower end portions of the gate electrode **70**, there is no positive fixed charge or charge trap state due to the nitride film **20***c*. Therefore, the off-current of the peripheral circuit transistor can be reduced and malfunction can be prevented, and the reliability <sup>5</sup> of the peripheral circuit transistor can greatly be improved. Moreover, in the present embodiment, the oxide films **4***b* are formed at both end portions of the nitride film **20***b*. Therefore, the positive fixed charge and the charge trap state can further be reduced, and the reliability of the peripheral circuit transistor can greatly be improved.

Therefore, the present embodiment can provide a peripheral circuit transistor with excellent characteristics and reliability, wherein the progress of bird's beak oxidation can be suppressed and the fixed charge amount can be reduced.

The semiconductor device shown in FIG. **11** can be fabricated by a method similar to the fabrication method illustrated in FIG. **4**.

FIG. **12** is a cross-sectional view that schematically shows the structure of a semiconductor device according to a modi-<sup>20</sup> fication of the fifth embodiment. Specifically, FIG. **12** is a cross-sectional view taken along the channel width direction of the peripheral circuit transistor of the nonvolatile memory. The basic structure is the same as shown in FIG. **11**. Thus, a detailed description of the parts common to those described <sup>25</sup> with reference to FIG. **11** is omitted here.

In the modification shown in FIG. 12, the nitride films 20band 20c are formed near lower end portions of the gate electrode 70, and are not formed near a central portion of the gate electrode 70. Specifically, the nitride film 20c includes a pair <sup>30</sup> of portions which are formed near lower ends of a pair of side surfaces of the gate electrode 70 (i.e. a pair of side surfaces which are parallel in the channel length direction), and the pair of portions are spaced apart. Similarly, the nitride film 20b, like the nitride film 20c, includes a pair of portions which <sup>35</sup> are spaced apart.

In this modification, too, the same advantageous effects as with the peripheral circuit transistor shown in FIG. **11** can be obtained. In this modification, however, compared to the structure shown in FIG. **11**, the effect of suppressing the <sup>40</sup> bird's beak oxidation decreases. It is thus necessary to restrict process conditions. Instead, by virtue of the absence of the nitride film in the central region of the channel, scattering of carriers flowing in the channel hardly occurs. As a result, the mobility of carriers increases, and the on-current can be <sup>45</sup> increased.

The semiconductor device shown in FIG. **12** can be fabricated by a method similar to the fabrication method illustrated in FIG. **5**.

In the example shown in FIG. 12, each of the oxide films  $4a \, 50$  and 4b has a wedge shape. Alternatively, like the example shown in FIG. 6, each of the oxide films 4a and 4b may be formed in a rectangular shape.

## Embodiment 6

FIG. **13**A and FIG. **13**B are cross-sectional views which schematically show the structure of a semiconductor device according to a sixth embodiment of the invention. FIG. **13**A is a cross-sectional view taken along a channel length direction <sup>60</sup> of a memory cell transistor of the nonvolatile memory, and FIG. **13**B is a cross-sectional view taken along a channel length direction of a peripheral circuit transistor of the nonvolatile memory. The memory cell transistor shown in FIG. **13**A and the peripheral circuit transistor shown in FIG. **13**B are formed on the same substrate and constitute the same nonvolatile memory. A detailed description of the parts com-

mon to those described in the preceding embodiments is omitted here. The peripheral circuit transistor in this embodiment includes select gate transistor.

The basic structure of the memory cell transistor shown in FIG. **13**A is similar to that of the memory cell transistor shown in FIG. **1**. However, in the memory cell transistor of this embodiment, the oxide films 8a and 8b shown in FIG. **1** are not formed.

The basic structure of the peripheral circuit transistor shown in FIG. **13**B is similar to that of the peripheral circuit transistor shown in FIG. **10**. However, in the peripheral circuit transistor of this embodiment, the oxide films **8**a and **8**b shown in FIG. **10** are not formed.

The memory cell transistor shown in FIG. 13A and the peripheral circuit transistor shown in FIG. 13B are formed at the same time by using common fabrication steps. Specifically, the lower-layer conductive portion 30 of the gate electrode 70 of the peripheral circuit transistor is formed in the same fabrication step as the floating gate electrode 3 of the memory cell transistor. The insulation portion 60 of the peripheral circuit transistor film 6 of the memory cell transistor. The upper-layer conductive portion 31 of the gate electrode 70 of the peripheral circuit transistor is formed in the same fabrication step as the inter-electrode insulation film 6 of the memory cell transistor. The upper-layer conductive portion 31 of the gate electrode 70 of the peripheral circuit transistor is formed in the same fabrication step as the control gate electrode 7 of the memory cell transistor.

As shown in FIG. 13A, in the memory cell transistor, the nitride film 2c is formed on the entire lower surface of the floating gate electrode 3, and the nitride film 2b is formed on the entire lower surface of the tunnel insulation film 2a. By contrast, as shown in FIG. 13B, in the peripheral circuit transistor, the nitride film 20c is formed near lower end portions of the gate electrode 70, and is not formed near a central portion of the gate electrode 70. Specifically, the nitride film 20c includes a pair of portions which are formed near lower ends of a pair of side surfaces of the gate electrode 70 (i.e. a pair of side surfaces which are parallel in the channel width direction), and the pair of portions are spaced apart. Similarly, the nitride film 20b, like the nitride film 20c, includes a pair of portions which are spaced apart.

In the present embodiment, too, since progress of bird's beak oxidation can be suppressed by the nitride films, the problem resulting from the progress of the bird's beak oxidation can be prevented. Specifically, in the memory cell transistor, an increase of a write/erase operation voltage can be suppressed, and degradation in reliability of the memory cell transistor can effectively be suppressed. Moreover, in the peripheral circuit transistor, an increase of the threshold voltage and a decrease of the transconductance can be suppressed.

In the peripheral circuit transistor, since the nitride film is not provided in the central region of the channel, scattering of carriers flowing in the channel hardly occurs. As a result, the mobility of carriers increases, and the on-current can be increased. In addition, since the fixed charge density decreases, the threshold voltage of the transistor rises and the off-current can be decreased.

In the present embodiment, therefore, the problem resulting from the progress of the bird's beak oxidation can be prevented, and the on-current can be increased and the offcurrent can be decreased in the peripheral circuit transistor.

FIG. 14A and FIG. 14B are cross-sectional views which schematically show the structure of a semiconductor device according to a modification of the sixth embodiment. FIG. 14A is a cross-sectional view taken along the channel length direction of the memory cell transistor of the nonvolatile memory, and FIG. 14B is a cross-sectional view taken along the channel length direction of the peripheral circuit transistor of the nonvolatile memory. The basic structure is the same as that shown in FIGS. **13**A and **13**B. A detailed description of the parts, which have already been described, is omitted here.

As shown in FIG. **14**A, the memory cell transistor has the <sup>5</sup> same structure as the memory cell transistor shown in FIG. **1**. Therefore, the same advantageous effects as with the memory cell transistor shown in FIG. **1** can be obtained. As shown in FIG. **14**B, the peripheral circuit transistor has the same structure as the peripheral circuit transistor shown in FIG. **10**. Therefore, the same advantageous effects as with the peripheral circuit transistor shown in FIG. **10**. Therefore, the same advantageous effects as with the peripheral circuit transistor shown in FIG. **10** can be obtained. In addition, since the basic structure is the same as the above-described structure shown in FIGS. **13**A and **13**B, the same advantageous effects as with the structure described with reference to FIG. **13**A and FIG. **13**B can be obtained.

FIG. **15**A and FIG. **15**B are cross-sectional views which schematically show the structure of a semiconductor device according to another modification of the sixth embodiment. <sup>20</sup> FIG. **15**A is a cross-sectional view taken along the channel length direction of the memory cell transistor of the nonvolatile memory, and FIG. **15**B is a cross-sectional view taken along the channel length direction of the peripheral circuit transistor of the nonvolatile memory. The basic structure is <sup>25</sup> the same as that shown in FIGS. **13**A and **13**B. A detailed description of the parts, which have already been described, is omitted here.

As shown in FIG. **15**A, the memory cell transistor has the same structure as the memory cell transistor shown in FIG. **7**. <sup>30</sup> Therefore, the same advantageous effects as with the memory cell transistor shown in FIG. **7** can be obtained. As shown in FIG. **15**B, the structure of the peripheral circuit transistor is similar to the structure of the peripheral circuit transistor shown in FIG. **10**. Therefore, the same advantageous effects <sup>35</sup> as with the peripheral circuit transistor shown in FIG. **10** can be obtained. In addition, since the basic structure is the same as the above-described structure shown in FIGS. **13**A and **13**B, the same advantageous effects as with the structure described with reference to FIG. **13**A and FIG. **13**B can be <sup>40</sup> obtained.

#### Embodiment 7

FIG. **16**A and FIG. **16**B are cross-sectional views which 45 schematically show the structure of a semiconductor device according to a seventh embodiment of the invention. FIG. **16**A is a cross-sectional view taken along the channel width direction of the memory cell transistor of the nonvolatile memory, and FIG. **16**B is a cross-sectional view taken along 50 the channel width direction of the peripheral circuit transistor of the nonvolatile memory. The memory cell transistor shown in FIG. **16**A and the peripheral circuit transistor shown in FIG. **16**B are formed on the same substrate and constitute the same nonvolatile memory. A detailed description of the parts, 55 which have already been described in the preceding embodiments, is omitted here.

The basic structure of the memory cell transistor shown in FIG. **16**A is similar to the structure of the memory cell transistor shown in FIG. **4**. In the memory cell transistor of the  $_{60}$  present embodiment, however, the oxide films **4***a* and **4***b* shown in FIG. **4** are not formed.

The basic structure of the peripheral circuit transistor shown in FIG. **16**B is similar to the structure of the peripheral circuit transistor shown in FIG. **12**. In the peripheral circuit 65 transistor of the present embodiment, however, the oxide films 4a and 4b shown in FIG. **12** are not formed.

The memory cell transistor shown in FIG. 16A and the peripheral circuit transistor shown in FIG. 16B are formed at the same time by using common fabrication steps. Specifically, the lower-layer conductive portion 30 of the gate electrode 70 of the peripheral circuit transistor is formed in the same fabrication step as the floating gate electrode 3 of the memory cell transistor. The insulation portion 60 of the peripheral circuit transistor film 6 of the memory cell transistor. The upper-layer conductive portion 31 of the gate electrode 70 of the peripheral circuit transistor is formed in the same fabrication step as the inter-electrode insulation film 6 of the memory cell transistor. The upper-layer conductive portion 31 of the gate electrode 70 of the peripheral circuit transistor is formed in the same fabrication step as the control gate electrode 7 of the memory cell transistor.

As shown in FIG. 16A, in the memory cell transistor, the nitride film 2c is formed on the entire lower surface of the floating gate electrode 3, and the nitride film 2b is formed on the entire lower surface of the tunnel insulation film 2a. By contrast, as shown in FIG. 16B, in the peripheral circuit transistor, the nitride film 20c is formed near lower end portions of the gate electrode 70, and is not formed near a central portion of the gate electrode 70. Specifically, the nitride film 20c includes a pair of portions which are formed near lower ends of a pair of side surfaces of the gate electrode 70 (i.e. a pair of side surfaces which are parallel in the channel length direction), and the pair of portions are spaced apart. Similarly, the nitride film 20b, like the nitride film 20c, includes a pair of portions which are spaced apart.

In the present embodiment, too, since progress of bird's beak oxidation can be suppressed by the nitride films, the problem resulting from the progress of the bird's beak oxidation can be prevented. Specifically, in the memory cell transistor, an increase of a write/erase operation voltage can be suppressed, and degradation in reliability of the memory cell transistor can effectively be suppressed. Moreover, in the peripheral circuit transistor, an increase of the threshold voltage and a decrease of the transconductance can be suppressed.

In the peripheral circuit transistor, since the nitride film is not provided in the central region of the channel, scattering of carriers flowing in the channel hardly occurs. As a result, the mobility of carriers increases, and the on-current can be increased. In addition, since the positive fixed charge density decreases, the threshold voltage of the transistor rises and the off-current can be decreased.