(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4957925号

(P4957925)

(45) 発行日 平成24年6月20日(2012.6.20)

(24) 登録日 平成24年3月30日(2012.3.30)

|                       |                |

|-----------------------|----------------|

| (51) Int.Cl.          | F 1            |

| HO4N 5/341 (2011.01)  | HO4N 5/335 410 |

| HO4N 5/353 (2011.01)  | HO4N 5/335 530 |

| HO4N 5/3745 (2011.01) | HO4N 5/335 745 |

| HO1L 27/146 (2006.01) | HO1L 27/14 A   |

請求項の数 12 (全 22 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2009-19218 (P2009-19218)    |

| (22) 出願日  | 平成21年1月30日 (2009.1.30)        |

| (65) 公開番号 | 特開2010-178117 (P2010-178117A) |

| (43) 公開日  | 平成22年8月12日 (2010.8.12)        |

| 審査請求日     | 平成23年12月27日 (2011.12.27)      |

早期審査対象出願

|           |                                                  |

|-----------|--------------------------------------------------|

| (73) 特許権者 | 508261493<br>株式会社ブルックマンテクノロジ<br>静岡県浜松市中区大工町125番地 |

| (74) 代理人  | 100101454<br>弁理士 山田 卓二                           |

| (74) 代理人  | 100081422<br>弁理士 田中 光雄                           |

| (72) 発明者  | 渡辺 恭志<br>京都府木津川市相楽台9-15-39                       |

| 審査官       | 鈴木 肇                                             |

最終頁に続く

(54) 【発明の名称】 増幅型固体撮像装置

## (57) 【特許請求の範囲】

## 【請求項 1】

内部にメモリを有する単位画素が行列状に複数配置されてなる画素アレイと、該画素アレイを構成する各画素に対する動作制御を行う制御回路部とを備えた増幅型固体撮像装置において、

前記各画素は、

受光した光に応じた信号を生成して出力する光電変換部と、

該光電変換部から出力された信号がゲートに入力され、該ゲートに入力された信号を増幅して出力するMOSトランジスタからなる第1の増幅トランジスタと、

該第1の増幅トランジスタから出力された信号を記憶するための前記メモリをなす第1の容量と、

前記第1の増幅トランジスタから出力された信号に対して、該第1の容量への出力制御を行って該第1の容量への書き込み制御を行う第1の書き込みスイッチ部と、

前記第1の容量に書き込まれた信号がゲートに入力され、該ゲートに入力された信号を増幅して出力するMOSトランジスタからなる第2の増幅トランジスタと、

前記第1の容量に書き込まれた信号を所定の第1電圧に初期化する初期化トランジスタと、

をそれぞれ備え、

前記第1の増幅トランジスタは、前記第1の容量のみを負荷とし、前記第1の書き込みスイッチ部は、前記初期化トランジスタによって前記第1の容量に対する前記初期化が行

10

20

われた後、前記第1の増幅トランジスタが飽和領域動作からサブスレッショルド領域動作に移行して準安定状態になる期間、前記第1の増幅トランジスタから出力された信号を前記第1の容量へ出力して前記第1の容量への書き込みを行うことを特徴とする増幅型固体撮像装置。

【請求項2】

前記制御回路部は、前記画素アレイを構成する前記各画素に対して、同時に作動させて該各画素内の前記第1の容量に対する書き込み動作をそれぞれ行わせた後、所定の方法で前記各画素の前記第1の容量からの読み出しを順次行うことを特徴とする請求項1記載の増幅型固体撮像装置。

【請求項3】

前記画素アレイ内の各画素は、列単位で前記第1の増幅トランジスタが電源線に接続され、該電源線は列単位ごとにそれぞれ抵抗を介して所定の電源電圧に接続されることを特徴とする請求項2記載の増幅型固体撮像装置。

【請求項4】

前記画素アレイ内の各画素は、列単位で前記第1の増幅トランジスタが電源線に接続され、全列の該各電源線はそれぞれ接続部で接続され、該接続部は抵抗を介して所定の電源電圧に接続されることを特徴とする請求項2記載の増幅型固体撮像装置。

【請求項5】

前記制御回路部は、前記画素アレイから行ごとに順次読み出しを行う際、非選択行の各画素における前記初期化トランジスタに対して、前記第2の増幅トランジスタがそれぞれ不活性になるような前記第1電圧に初期化させることを特徴とする請求項1～4のうちのいずれか1つに記載の増幅型固体撮像装置。

【請求項6】

前記各画素は、

前記第1の増幅トランジスタから出力された信号を記憶するための前記メモリをなす1つ以上の第2の容量と、

前記第1の増幅トランジスタから出力された信号に対して、対応する該第2の容量への出力制御を行って該第2の容量への書き込み制御を行う1つ以上の第2の書き込みスイッチ部と、

前記第1の容量に書き込まれた信号に対して、前記第2の増幅トランジスタのゲートへの出力制御を行う第1の読み出しスイッチ部と、

対応する前記第2の容量に書き込まれた信号に対して、前記第2の増幅トランジスタのゲートへの出力制御を行う1つ以上の第2の読み出しスイッチ部と、

を備え、

前記第1の増幅トランジスタは、前記第1又は第2の容量のみを負荷とし、前記初期化トランジスタは、前記第2の容量に書き込まれた信号を前記所定の第1電圧に初期化し、前記第2の書き込みスイッチ部は、前記初期化トランジスタによって前記第2の容量に対する前記初期化が行われた後、前記第1の増幅トランジスタが飽和領域動作からサブスレッショルド領域動作に移行して準安定状態になる期間、前記第1の増幅トランジスタから出力された信号を前記第2の容量へ出力して前記第2の容量への書き込みを行うことを特徴とする請求項1～5のうちのいずれか1つに記載の増幅型固体撮像装置。

【請求項7】

前記各画素は、前記第1の増幅トランジスタのゲートを所定の第2電圧にリセットするリセットトランジスタをそれぞれ備え、前記第1及び第2の各書き込みスイッチ部は、前記第1及び第2の各容量に対して、ゲートが前記リセットされたときの前記第1の増幅トランジスタからの出力信号を一方の容量に書き込み、ゲートに前記光電変換部からの出力信号が入力されているときの前記第1の増幅トランジスタからの出力信号を他方の容量に書き込むことを特徴とする請求項6記載の増幅型固体撮像装置。

【請求項8】

前記各画素は、前記ゲートがリセットされたときに前記第1の増幅トランジスタの出力

10

20

30

40

50

端に所定の電圧を出力する制御スイッチ部をそれぞれ備えることを特徴とする請求項\_7記載の増幅型固体撮像装置。

【請求項 9】

前記第1の増幅トランジスタは、エンハンスマント型のMOSトランジスタであることを特徴とする請求項1～8のうちのいずれか1つに記載の増幅型固体撮像装置。

【請求項 10】

前記第2の増幅トランジスタは、デプレッション型のMOSトランジスタであることを特徴とする請求項9記載の増幅型固体撮像装置。

【請求項 11】

前記第1の容量は、少なくともその一部にMOS型容量を含むことを特徴とする請求項1～10のうちのいずれか1つに記載の増幅型固体撮像装置。 10

【請求項 12】

前記MOS型容量は、デプレッション型のMOS型容量であることを特徴とする請求項11記載の増幅型固体撮像装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画素内にメモリを有する増幅型固体撮像装置に関する。

【背景技術】

【0002】

一般に、増幅型固体撮像装置としては、増幅機能を持たせた画素部とその画素部の周辺に配置された走査回路とを有し、該走査回路によって前記画素部から画素データを読み出すものが普及している。

このような増幅型固体撮像装置の一例としては、画素部が周辺の駆動回路及び信号処理回路と一体化するのに有利なCMOS（コンプリメンタリ・メタル・オキサイド・セミコンダクタ）によって構成されたAPS（Active Pixel Sensor）型イメージセンサが知られている。このようなAPS型イメージセンサの中でも、近年は高画質が得られる4トランジスタ型が主流になりつつある。

【0003】

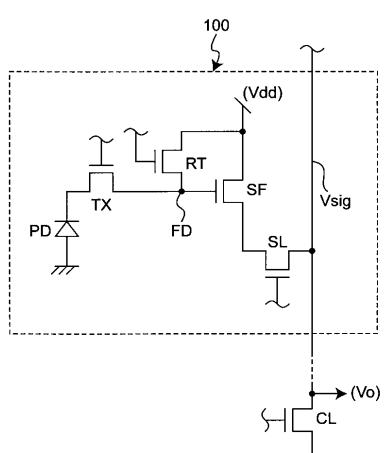

図16は、画素100内に4つのNMOSトランジスタを備えた、従来の4トランジスタ型の画素構成例を示した回路図である。 30

図16では、受光素子PDは通常埋め込みフォトダイオードで構成され、受光素子PDから接続部FDへは転送トランジスタTXによって信号電荷が転送される。接続部FDは、受光素子PDから信号電荷が転送される前に、リセットトランジスタRTによってリセットトランジスタRTのドレイン電圧である電源電圧Vddにリセットされる。次に、転送トランジスタTXがオンして、受光素子PDからの信号電荷が接続部FDに転送される。前記リセット後及び前記信号電荷転送後の接続部FDの電圧は、増幅トランジスタSFによって増幅され、選択トランジスタSLを介して読み出し信号線Vsigへ読み出される。読み出し信号線Vsigの一端には定電流負荷トランジスタCLが接続され、定電流負荷トランジスタCLのドレインから出力電圧V0が得られる。 40

【0004】

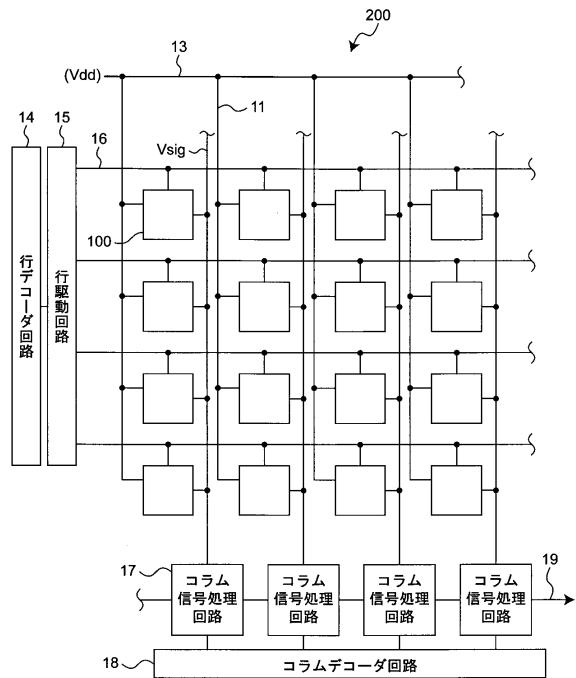

図17は、図16の画素100をマトリクス状に配置した画素アレイ200を含む増幅型固体撮像装置をなす2次元イメージセンサの構成例を示した図である。

図17において、11はリセットトランジスタRT及び増幅トランジスタSFの各ドレインに電源電圧Vddをそれぞれ印加するための電源線であり、電源線11は増幅型固体撮像装置全体の電源線13に直接接続されている。また、駆動線16は転送トランジスタ駆動線、リセットトランジスタ駆動線及び選択トランジスタ駆動線を1つにして示したものである。

各画素行では、行デコーダ回路14により特定の行が選択され、行駆動回路15を介して駆動線16へ駆動信号が与えられる。読み出し信号線Vsigからの信号は、コラム信 50

号処理回路 17 に入力され、コラム信号処理回路 17 でアナログ又はアナログとデジタルの信号処理が施される。この後、コラムデコーダ回路 18 によって、コラムごとの信号が水平信号線 19 へ読み出され、最終的に増幅型固体撮像装置外部に出力される。

#### 【0005】

図 17 で示した構成では、各画素は行ごとに順次読み出され、画素 100 では該読み出しが行われるときまで受光素子 PD に蓄積された信号を出力するため、各画素の信号は時間的に行ごとに順次ずれが生じ、動きのある被写体を撮像する場合には、動きに応じて像が歪んでいた。このような問題を解決するために、画素内にメモリを備え、すべての画素を同時に読み出して該メモリに書き込み、その後、該メモリ内の情報を順次読み出すようにした一括露光技術があった。しかし、この場合、受光素子からの信号を前記メモリに書き込んでから読み出すまでの間にノイズが増大し、S/N 比が低下するという問題があった。このようなことから、受光素子の信号を増幅してからメモリに書き込む技術があり、図 18 はこの一例を示した回路図である（例えば、特許文献 1 参照。）。

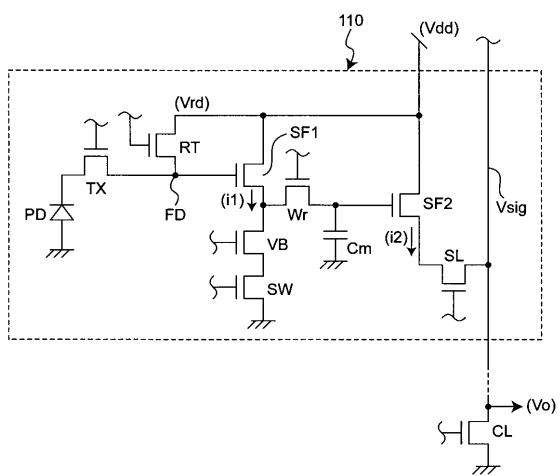

#### 【0006】

図 18 に示した画素 110 は、図 16 で示した画素 100 に、第 1 の増幅トランジスタ SF1、定電流負荷 VB、電流制御スイッチ SW、書き込みスイッチ Wr 及びメモリ Cm を追加した構成になっている。なお、図 18 では、第 2 の増幅トランジスタ SF2 が図 16 の増幅トランジスタ SF に相当しており、電流制御スイッチ SW は電源側に設けるようにしてもよい。

例えば、画素 110 を使用して図 17 に示した 2 次元イメージセンサを構成し、まず、すべての画素を一括動作させて、受光素子 PD からの信号をメモリ Cm に書き込むようする。即ち、電流制御スイッチ SW をオンさせた後、書き込みスイッチ Wr をオンさせ、第 1 の増幅トランジスタ SF1 によって増幅された受光素子 PD からの信号をメモリ Cm に書き込む。

#### 【0007】

この後、書き込みスイッチ Wr をオフさせ、次に電流制御スイッチ SW をオフさせて一括書き込み動作が終了する。読み出し動作は、行ごとに順次行われる。すなわち、メモリ Cm に保持された信号を、第 2 の増幅トランジスタ SF2 及び選択トランジスタ SL を介して読み出し信号線 Vsig へ読み出す動作を、行ごとに順次行われる。読み出し信号線 Vsig の一端には定電流負荷トランジスタ CL が接続され、出力電圧 Vo が行ごとに順次得られる。

#### 【先行技術文献】

#### 【特許文献】

#### 【0008】

#### 【特許文献 1】特開 2005-65074 号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0009】

しかしながら、図 18 の構成では下記 (a) ~ (d) の課題が伴っていた。

(a) すべての画素で第 1 の増幅トランジスタ SF1 が同時にオンするため、2 次元イメージセンサ素子全体では過大な電流が流れる。例えば、1 画素当り  $1 \mu A$  としても 10 万画素あれば、該素子全体で  $1 A$  にもなる。

(b) 1 画素当りの電流を抑圧するために、定電流負荷 VB のゲート電圧をしきい値 Vth 付近にすると、しきい値 Vth のばらつきによって電流値が画素ごとに大きく変動する。

(c) 1 画素内に定電流負荷 VB 及び電流制御スイッチ SW の 2 つのトランジスタ、並びに該各トランジスタへの制御信号線が必要になり、画素レイアウトが複雑化する。

#### 【0010】

(d) 第 1 の増幅トランジスタ SF1 と定電流負荷 VB によって構成されたソースフォロワ回路で発生するノイズは、下記 (1) 式のように表される。

10

20

30

40

50

$$\overline{V_{n,in}^2} = 4 \times k \times T \times \left(\frac{2}{3}\right) \times \frac{1}{gml} \times \left(1 + \frac{gm2}{gml}\right) \dots \dots \dots \quad (1)$$

前記(1)式では、 $k$ はボルツマン定数、 $T$ は絶対温度、 $g_{m1}$ 及び $g_{m2}$ は第1の増幅トランジスタ $SF1$ 及び定電流負荷 $VB$ の相互コンダクタンスをそれぞれ示している。画素領域内では、面積の制約から相互コンダクタンス $g_{m1}$ 及び $g_{m2}$ は同程度の値になるため、ノイズ電力は1トランジスタの場合と比較して2倍程度になる。

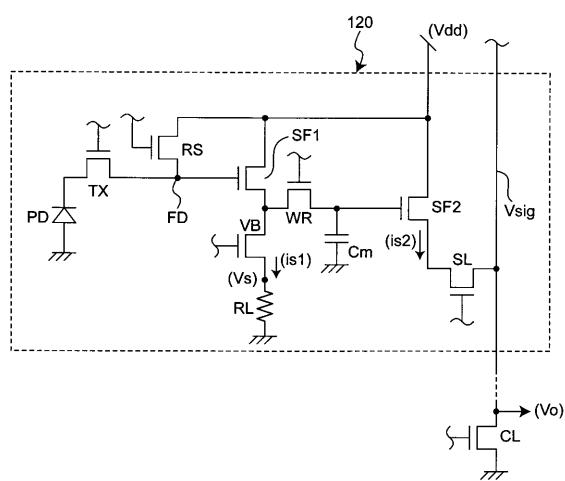

【 0 0 1 1 】

1画素当りの電流を安定して小さくする手法として、図19のような回路が考えられる。すなわち、図19では、定電流負荷VBのソース側に高抵抗RLが挿入され、MOSトランジスタのバックゲート効果によって、ゲート電圧をしきい値Vth以下のサブスレッショルド領域として電流を大幅に抑制しても、ソース電圧を安定して保つことができる。しかし、例えば100万画素で素子全体の電流を100mA以下にするためには、定電流負荷VBのソース電圧を1Vとし、 $RL = 10M$ とする必要があり、このような高抵抗値の抵抗を1画素内に形成するのは困難であった。

【 0 0 1 2 】

更に、図18及び図19で示したような、通常のソースフォロワ出力を容量値  $C_m$  のメモリに書き込む場合、ノイズ電力で表すと下記(2)式のような  $kTc$  ノイズが発生し、このような  $kTc$  ノイズは、前記ソースフォロワノイズに加算され、ノイズの増大を招いていた。

【 0 0 1 3 】

本発明は、このような問題を解決するためになされたものであり、簡単な回路構成で、メモリへの書き込み時における電流を抑圧することができ、安定した動作と高い性能を得ることができる増幅型固体撮像装置を得ることを目的とする。

## 【課題を解決するための手段】

【 0 0 1 4 】

この発明に係る増幅型固体撮像装置は、内部にメモリを有する単位画素が行列状に複数配置されてなる画素アレイと、該画素アレイを構成する各画素に対する動作制御を行う制御回路部とを備えた増幅型固体撮像装置において、

前記各画素は、

受光した光に応じた信号を生成して出力する光電変換部と、

該光電変換部から出力された信号がゲートに入力され、該ゲートに入力された信号を増幅して出力するMOSトランジスタからなる第1の増幅トランジスタと、

該第1の増幅トランジスタから出力された信号を記憶するための前記メモリをなす第1の容量と、

前記第1の増幅トランジスタから出力された信号に対して、該第1の容量への出力制御を行って該第1の容量への書き込み制御を行う第1の書き込みスイッチ部と、

前記第1の容量に書き込まれた信号がゲートに入力され、該ゲートに入力された信号を増幅して出力するMOSトランジスタからなる第2の増幅トランジスタと、

前記第1の容量に書き込まれた信号を所定の第1電圧に初期化する初期化トランジスタと、

をそれぞれ備え、

前記第1の増幅トランジスタは、前記第1の容量のみを負荷とし、前記第1の書き込みスイッチ部は、前記初期化トランジスタによって前記第1の容量に対する前記初期化が行

われた後、所定の期間、前記第1の増幅トランジスタから出力された信号を前記第1の容量へ出力して前記第1の容量への書き込みを行うものである。

【0015】

具体的には、前記第1の書き込みスイッチ部は、前記第1の増幅トランジスタが飽和領域動作からサブスレッショルド領域動作に移行して準安定状態になる期間、前記第1の増幅トランジスタから出力された信号を前記第1の容量へ出力して前記第1の容量への書き込みを行うようにした。

【0016】

また、前記制御回路部は、前記画素アレイを構成する前記各画素に対して、同時に作動させて該各画素内の前記第1の容量に対する書き込み動作をそれぞれ行わせた後、所定の方法で前記各画素の前記第1の容量からの読み出しを順次行うようにした。

10

【0017】

この場合、前記画素アレイ内の各画素は、列単位で前記第1の増幅トランジスタが電源線に接続され、該電源線は列単位ごとにそれぞれ抵抗を介して所定の電源電圧に接続されるようにした。

【0018】

また、前記画素アレイ内の各画素は、列単位で前記第1の増幅トランジスタが電源線に接続され、全列の該各電源線はそれぞれ接続され、該接続部は抵抗を介して電源電圧に接続されるようにしてもよい。

【0019】

また、前記制御回路部は、前記画素アレイから行ごとに順次読み出しを行う際、非選択行の各画素における前記初期化トランジスタに対して、前記第2の増幅トランジスタがそれぞれ不活性になるような前記第1電圧に初期化させるようにした。

20

【0020】

更に、前記各画素は、

前記第1の増幅トランジスタから出力された信号を記憶するための前記メモリをなす1つ以上の第2の容量と、

前記第1の増幅トランジスタから出力された信号に対して、対応する該第2の容量への出力制御を行って該第2の容量への書き込み制御を行う1つ以上の第2の書き込みスイッチ部と、

30

前記第1の容量に書き込まれた信号に対して、前記第2の増幅トランジスタのゲートへの出力制御を行う第1の読み出しスイッチ部と、

対応する前記第2の容量に書き込まれた信号に対して、前記第2の増幅トランジスタのゲートへの出力制御を行う1つ以上の第2の読み出しスイッチ部と、

を備え、

前記第1の増幅トランジスタは、前記第1又は第2の容量のみを負荷とし、前記初期化トランジスタは、前記第2の容量に書き込まれた信号を前記所定の第1電圧に初期化し、前記第2の書き込みスイッチ部は、前記初期化トランジスタによって前記第2の容量に対する前記初期化が行われた後、所定の期間、前記第1の増幅トランジスタから出力された信号を前記第2の容量へ出力して前記第2の容量への書き込みを行うようにしてもよい。

40

【0021】

この場合、前記第2の書き込みスイッチ部は、前記第1の増幅トランジスタが飽和領域動作からサブスレッショルド領域動作に移行して準安定状態になる期間、前記第1の増幅トランジスタから出力された信号を前記第2の容量へ出力して前記第2の容量への書き込みを行うようにした。

【0022】

また、前記各画素は、前記第1の増幅トランジスタのゲートを所定の第2電圧にリセットするリセットトランジスタをそれぞれ備え、前記第1及び第2の各書き込みスイッチ部は、前記第1及び第2の各容量に対して、ゲートが前記リセットされたときの前記第1の増幅トランジスタからの出力信号を一方の容量に書き込み、ゲートに前記光電変換部から

50

の出力信号が入力されているときの前記第1の増幅トランジスタからの出力信号を他方の容量に書き込むようにした。

【0023】

また、前記各画素は、前記リセット動作時に前記第1の増幅トランジスタの出力端に所定の電圧を出力する制御スイッチ部をそれぞれ備えるようにしてもよい。

【0024】

具体的には、前記第1の増幅トランジスタは、エンハンスメント型のMOSトランジスタである。

【0025】

また、前記第2の増幅トランジスタは、デプレッション型のMOSトランジスタである 10 ようにしてもよい。

【0026】

また、前記第1の容量は、少なくともその一部にMOS型容量を含むようにしてもよい 。

【0027】

この場合、前記MOS型容量は、デプレッション型のMOS型容量であるようにする。

【発明の効果】

【0028】

本発明の増幅型固体撮像装置によれば、画素内に定電流負荷を有さないため、書き込み時の電流を抑圧することができる。前記第1の増幅トランジスタの負荷となる前記第1の容量への書き込み動作を行うには、まず該第1の容量を所定の電圧、例えば接地電圧の 20 ような低い電圧に初期化し、この後、該第1の容量への充電電流によって書き込み動作を行うようにして、前記第1の書き込みスイッチ部によって該書き込み時間を制御することにより、安定した動作を行うことができる。

【0029】

また、前記第1の書き込みスイッチ部は、前記第1の増幅トランジスタが飽和領域動作からサブスレッショルド領域動作に移行して準安定状態になっている期間、前記第1の増幅トランジスタから出力された信号を前記第1の容量へ出力して前記第1の容量への書き込みを行うようにした。このことから、前記第1の増幅トランジスタがサブスレッショルド領域に移行して前記第1の容量における電圧の時間変化が極めて小さくなつた時点で前記書き込み動作を完了するようにしたため、より安定した動作を行うことができる。 30

【0030】

また、前記単位画素内には、前記第2の容量と前記第2の書き込みスイッチ部の組が1つ以上存在し、更に第1及び第2の各容量に対応して第1及び第2の各読み出しスイッチ部を備え、更に、前記単位画素内に、前記第1の増幅トランジスタのゲートをリセットするリセットトランジスタを備えるようにして、例えば、前記第1及び第2の各容量に対して、ゲートが前記リセットされたときの前記第1の増幅トランジスタからの出力信号を一方の容量に書き込み、ゲートに前記光電変換部からの出力信号が入力されているときの前記第1の増幅トランジスタからの出力信号を他方の容量に書き込むようにした。このことから、1画素当たりに複数の情報を記憶することができるため、例えば、前記第1の増幅トランジスタにおけるゲートのリセットレベルと前記光電変換部からの信号レベルを独立して保持することができる。したがつて、これらを第2の増幅トランジスタによって別々に信号線に読み出すようにすれば、その後段回路で該両レベルの電圧差を取ることにより、相關二重サンプリング(CDS)法を適用することができ、前記第1及び第2の各増幅トランジスタにおけるしきい値Vthのばらつきに起因する固定パターンノイズや、前記第1の増幅トランジスタにおけるゲートへのリセットノイズを抑制することができ、低ノイズの画像信号を得ることができる。 40

【0031】

また、前記画素アレイを構成する前記各画素に対して、同時に作動させて該各画素内の前記第1の容量に対する書き込み動作をそれぞれ行わせた後、所定の方法で前記各画素の 50

前記第1の容量からの読み出しを順次行うようにし、例えば、列単位で前記第1の増幅トランジスタを電源線に接続し、該電源線を列単位ごとにそれぞれ抵抗を介して電源電圧に接続するようにして、全画素を一括して同時に前記各容量に書き込む動作、及び前記各容量から順次読み出す動作を行なうことができる。例えば、各列の電源線に抵抗を直列接続するようすれば、全画素の情報を一括して書き込むときにも、前記容量を充電する過渡電流のピーク値を抑圧することができる。

【0032】

また、前記画素アレイから行順次で信号を読み出す際に、非選択行の前記第2の増幅トランジスタが不活性になるように、該第2の増幅トランジスタのゲート電圧を前記初期化トランジスタによって制御するようにしたことから、該第2の増幅トランジスタと前記信号線との間に選択トランジスタを設ける必要がなくなり、画素内の構成要素を削減することができ、受光部の面積の増大等の性能向上を図ることができる。10

【0033】

また、前記第1の増幅トランジスタにエンハンスマント型を使用するか又は、前記リセットトランジスタのドレイン電圧が電源電圧よりも小さくなるようにすることにより、前記第1の増幅トランジスタの出力レベルが該電源電圧よりも小さい値になり、前記第1の増幅トランジスタが飽和領域動作からサブスレッショルド領域動作に移行するまでの応答時間を短縮させることができ、書き込み動作全体の応答速度を速くすることができる。

【0034】

また、前記第2の増幅トランジスタにデブレッショングループを使用することにより、前記第1の増幅トランジスタをエンハンスマント型にして、該第2の増幅トランジスタの入力電圧が小さくなても、該第2の増幅トランジスタの動作マージンを十分に確保することができる。20

【0035】

また、前記第1の容量の少なくとも一部にMOS型容量を含むようにしたことから、限られた画素面積内で十分なメモリ容量値を確保することが容易になり、前記容量をデブレッショングループにすることにより、該容量値を確保することができる動作電圧範囲を低電圧側に拡大させることができる。

【図面の簡単な説明】

【0036】

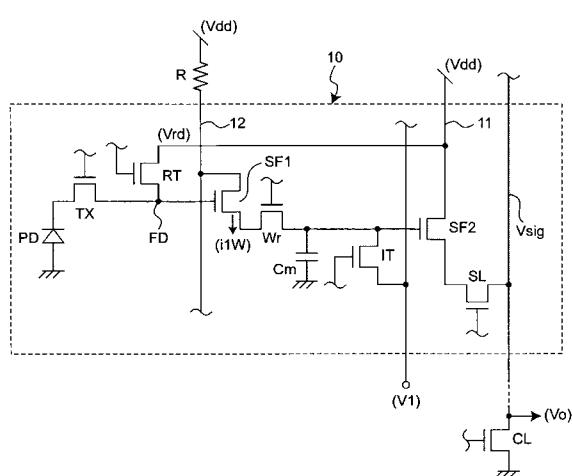

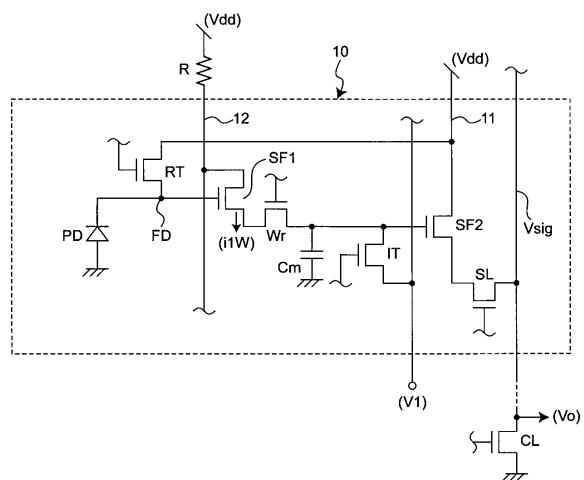

【図1】本発明の第1の実施の形態における増幅型固体撮像装置の画素構成例を示した図である。

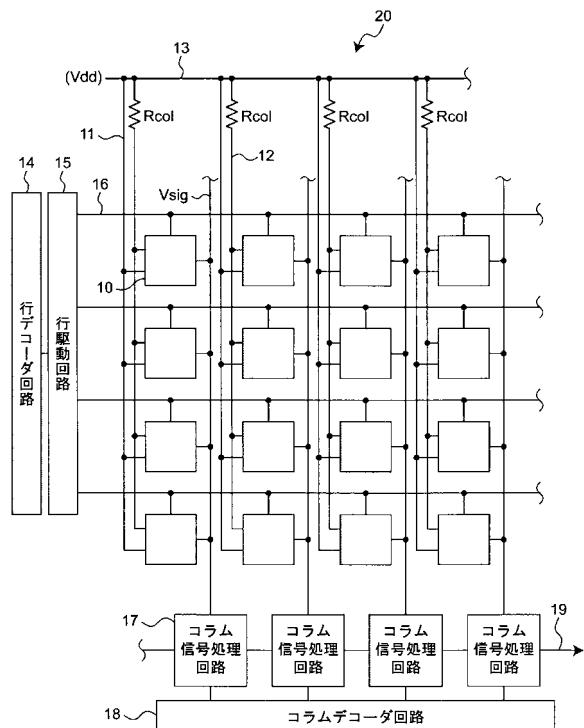

【図2】図1の画素10をマトリクス状に配置した画素アレイ20を含む2次元イメージセンサの構成例を示した図である。

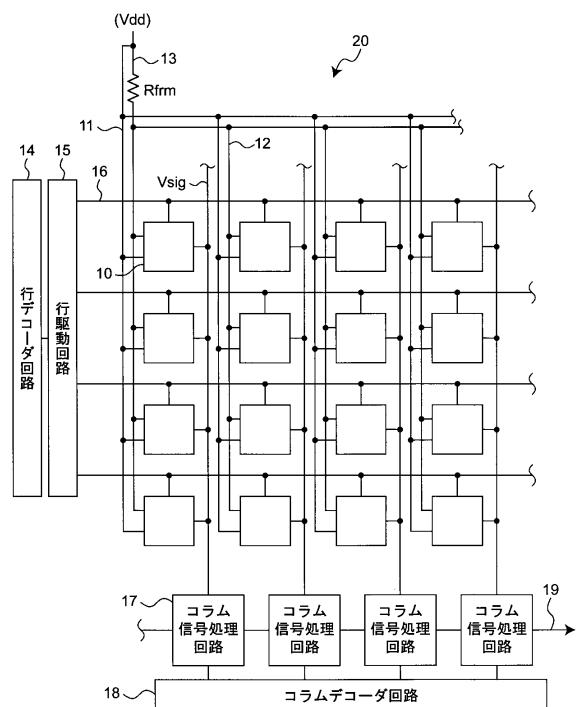

【図3】図1の画素10をマトリクス状に配置した画素アレイ20を含む2次元イメージセンサの他の構成例を示した図である。

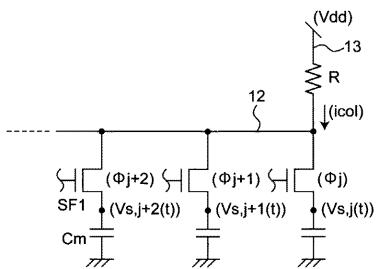

【図4】図1～図3で示した増幅型固体撮像装置における1列分の画素配列を抜き出した回路構成の一部を示した図である。

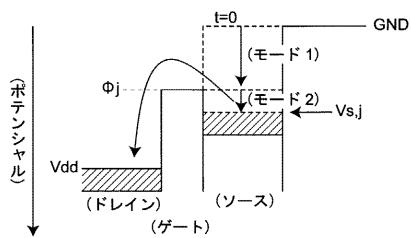

【図5】図4の回路構成の動作例をポテンシャルで示した図である。

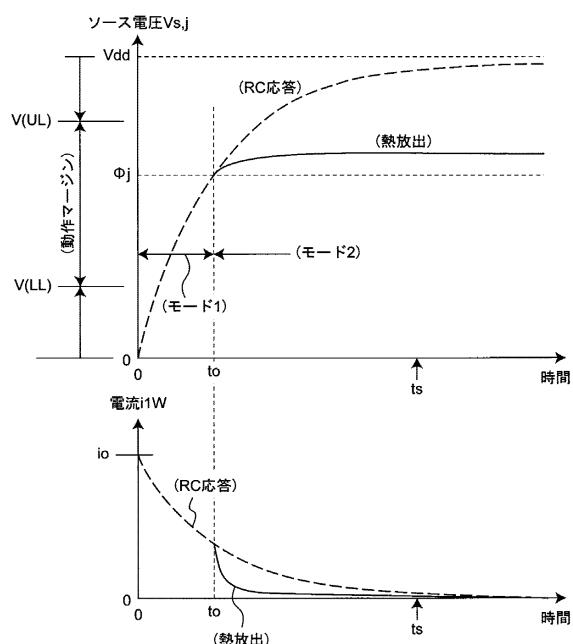

【図6】図4の回路構成の動作例を電位変化及び電流変化で示した図である。40

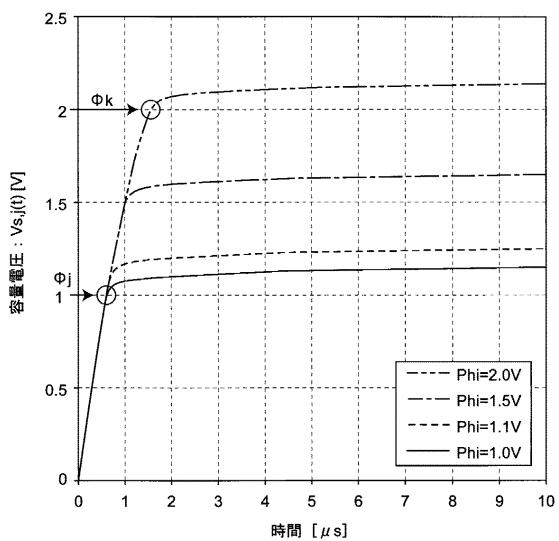

【図7】図4の回路構成の動作例を回路シミュレーションによって示した図である。

【図8】図1の画素構成における動作範囲例を示した図である。

【図9】本発明の第1の実施の形態における増幅型固体撮像装置の他の画素構成例を示した図である。

【図10】本発明の第2の実施の形態の増幅型固体撮像装置を画素構成例により示した図である。

【図11】図10で示した画素50の動作例を示したタイミングチャートである。

【図12】本発明の第2の実施の形態の増幅型固体撮像装置を他の画素構成例を示した図である。

【図13】図12の画素50における動作例を示したタイミングチャートである。50

【図14】本発明の第3の実施形態における増幅型固体撮像装置の画素構成例を示した図である。

【図15】図14で示した画素60の動作例を示したタイミングチャートである。

【図16】従来の増幅型固体撮像装置の画素構成例を示した図である。

【図17】図16の画素100をマトリクス状に配置した画素アレイを含む2次元イメージセンサの構成例を示した図である。

【図18】従来の増幅型固体撮像装置の他の画素構成例を示した図である。

【図19】従来の増幅型固体撮像装置の他の画素構成例を示した図である。

【発明を実施するための形態】

【0037】

10

次に、図面に示す実施の形態に基づいて、本発明を詳細に説明する。

第1の実施の形態。

図1は、本発明の第1の実施の形態における増幅型固体撮像装置の画素構成の例を示した図である。

図1において、画素10は、埋め込みフォトダイオードで構成された受光素子PD、転送トランジスタTX、リセットトランジスタRT、第1の増幅トランジスタSF1、選択トランジスタSL、第2の増幅トランジスタSF2、書き込みスイッチWr、容量からなるメモリCm及びメモリCmの端子電圧を初期化する初期化トランジスタITを備えている。転送トランジスタTX、リセットトランジスタRT、第1の増幅トランジスタSF1、選択トランジスタSL、第2の増幅トランジスタSF2、書き込みスイッチWr及び初期化トランジスタITは、それぞれNMOSトランジスタからなる。なお、受光素子PDは光電変換部を、書き込みスイッチWrは第1の書き込みスイッチ部を、メモリCmは第1の容量をそれぞれなす。

【0038】

20

受光素子PDのアノードは接地電圧に接続され、受光素子PDのカソードと第1の増幅トランジスタSF1のゲートとの間に転送トランジスタTXが接続されている。転送トランジスタTXと第1の増幅トランジスタSF1のゲートとの接続部をFDとすると、電源電圧Vddと接続部FDとの間にリセットトランジスタRTが接続されている。第1の増幅トランジスタSF1のドレインは抵抗Rを介して電源電圧Vddに接続され、第1の増幅トランジスタSF1のソースは、書き込みスイッチWrを介してメモリCmの一端に接続され、メモリCmの他端は接地電圧に接続されている。

30

【0039】

書き込みスイッチWrとメモリCmとの接続部は第2の増幅トランジスタSF2のゲートに接続され、該接続部と所定の電圧V1との間に初期化トランジスタITが接続されている。第2の増幅トランジスタSF2のドレインは電源電圧Vddに接続され、第2の増幅トランジスタSF2のソースと読み出し信号線Vsigとの間に選択トランジスタSLが接続されている。読み出し信号線Vsigの一端と接地電圧との間に定電流負荷トランジスタCLが接続され、定電流負荷トランジスタCLと読み出し信号線Vsigとの接続部から出力電圧Voが出力される。

【0040】

40

このように、第1の増幅トランジスタSF1の電源は、第2の増幅トランジスタSF1及びリセットトランジスタの各電源とは分離され、列単位で第1の増幅トランジスタSF1のドレインが電源線12に接続されており、電源線12は、抵抗Rを介して増幅型固体撮像装置全体の電源をなす電源電圧Vddに接続されている。初期化トランジスタITは、書き込み動作前にメモリCmの端子電圧の初期値を低電圧、例えば接地電圧である所定の電圧V1にリセットし、書き込み動作の開始と共に書き込みスイッチWrをオンにするとメモリCmに充電電流が流れることによって、第1の増幅トランジスタSF1の定電流負荷をなくしてもソースフォロワ動作を可能にしている。

【0041】

図2は、図1の画素10をマトリクス状に配置した画素アレイ20を含む増幅型固体撮

50

像装置をなす 2 次元イメージセンサの構成例を示した図である。

図 2 において、電源線 1 1 は、リセットトランジスタ R T 及び第 2 の増幅トランジスタ S F 2 の各ドレインに電源電圧 V d d をそれぞれ印加するための電源線であり、電源線 1 1 は増幅型固体撮像装置全体の電源線 1 3 に直接接続されている。また、各電源線 1 2 は、それぞれ抵抗 R c o 1 を介して電源線 1 3 に接続されており、各第 1 の増幅トランジスタ S F 1 のドレインにそれぞれ接続されている。駆動線 1 6 は、転送トランジスタ T X に対する駆動線、リセットトランジスタ R T に対する駆動線、書き込みスイッチ W r に対する駆動線、初期化トランジスタ I T に対する駆動線及び選択トランジスタ S L に対する駆動線を 1 つにして示したものであり、該各駆動線は、対応するトランジスタのゲートにそれぞれ接続されている。

10

#### 【 0 0 4 2 】

各画素行では、行デコーダ回路 1 4 により特定の行が選択され、行駆動回路 1 5 を介して駆動線 1 6 へ駆動信号が与えられる。読み出し信号線 V s i g からの信号は、コラム信号処理回路 1 7 に入力され、コラム信号処理回路 1 7 でアナログ又はアナログとデジタルの信号処理が施される。この後、コラムデコーダ回路 1 8 によって、コラムごとの信号が水平信号線 1 9 へ読み出され、最終的に増幅型固体撮像装置外部に出力される。なお、行デコーダ 1 4 、行駆動回路 1 5 、コラム信号処理回路 1 7 及びコラムデコーダ回路 1 8 は制御回路部をなし、行デコーダ 1 4 に入力される制御信号、及び該制御信号を生成する回路は省略している。

20

第 1 の増幅トランジスタ S F 1 の電源を、リセットトランジスタ R T 及び第 2 の増幅トランジスタ S F 2 の電源と分離し、列単位で抵抗 R c o 1 を介して増幅型固体撮像装置全体の電源線 1 3 に接続されており、抵抗 R c o 1 が図 1 の抵抗 R に相当する。なお、抵抗を列単位ではなく、すべての列で共通接続した後、抵抗 R f r m を介して増幅型固体撮像装置全体の電源電圧 V d d に接続するようにしてもよく、このようにした場合、図 2 は図 3 のようになる。

#### 【 0 0 4 3 】

このような構成において、メモリ C m への書き込みはすべての画素が一括して同時に行われる。まず、受光素子 P D から接続部 F D へは転送トランジスタ T X によって信号電荷が転送される。接続部 F D は、受光素子 P D から信号電荷が転送される前に、リセットトランジスタ R T によってリセットトランジスタ R T のドレイン電圧である電源電圧 V d d にリセットされる。次に、転送トランジスタ T X がオンして、受光素子 P D からの信号電荷が接続部 F D に転送される。前記リセット後及び前記信号電荷転送後の接続部 F D の電圧は、第 1 の増幅トランジスタ S F 1 によって増幅される。受光素子 P D からの信号をメモリ C m に書き込む際に書き込みスイッチ W r をオンさせ、第 1 の増幅トランジスタ S F 1 によって増幅された受光素子 P D からの信号をメモリ C m に書き込む。この後、書き込みスイッチ W r をオフさせて書き込み動作が終了する。

30

#### 【 0 0 4 4 】

読み出し動作は、行ごとに順次行われる。すなわち、メモリ C m に保持された信号を、第 2 の増幅トランジスタ S F 2 及び選択トランジスタ S L を介して読み出し信号線 V s i g へ読み出す動作を、行ごとに順次行われる。読み出し信号線 V s i g の一端には定電流負荷トランジスタ C L が接続され、定電流負荷トランジスタ C L のドレインから出力電圧 V o が行ごとに順次得られる。

40

#### 【 0 0 4 5 】

図 4 は、図 1 ~ 図 3 で示した増幅型固体撮像装置における 1 列分の画素配列を抜き出した回路構成の一部を示した図である。

図 4 で示すように、増幅型固体撮像装置全体の電源電圧 V d d に抵抗 R を介して電源線 1 2 が接続され、電源線 1 2 と接地電圧との間には、画素ごとに第 1 の増幅トランジスタ S F 1 とメモリ C m が直列に接続されている。

ここで、各画素内の第 1 の増幅トランジスタ S F 1 のチャネルポテンシャルをそれぞれ j で表し、図 4 の動作を説明するために、1 画素における第 1 の増幅トランジスタ S F

50

1 のポテンシャルの関係例を図 5 に示す。

【 0 0 4 6 】

図5では、第1の増幅トランジスタSF1において、ゲートのチャネルポテンシャルは $j$ であり、ドレイン電圧は電源電圧 $V_{dd}$ であり、ソースは時刻 $t = 0$ のときの初期値が初期化トランジスタITによるリセット動作によって接地電圧 $GND$ になっている。 $t > 0$ においては、最初に第1の増幅トランジスタSF1のゲートが飽和領域動作であるモード1になり、ソース電圧 $V_{s,j}$ は初期値の接地電圧 $GND$ から急速に $j$ まで上昇する。該ソース電圧 $V_{s,j}$ が $j$ を超えると、第1の増幅トランジスタSF1のゲートは、サブスレッショルド領域動作であるモード2になり、熱放出現象によって時間に対して対数的な変化となり、非常に緩慢な電圧変化になる。前記モード1の飽和領域動作では第1の増幅トランジスタSF1から出力された電流がメモリ $Cm$ の充電電流になり、該充電電流は、対象とする電流路での抵抗値 $Ra$ と負荷容量値 $Ca$ とで決まる時定数 $C_{R} = Ca \times Ra$ によって指数関数的に減衰する。このようなモード1の場合の、ソース電圧 $V_{s,j}$ の電圧変化を下記(3)式に示す。前記充電電流は開始点でピークになり、その値は $V_{dd} / Ra$ になる。

〔 0 0 4 7 〕

図 4 の回路では、抵抗  $R$  がコラムごとにある場合は、 $R_a = R_{col}$ 、 $C_a = n \times C_m$  になり、抵抗  $R$  が増幅型固体撮像装置全体で 1 か所にある場合は、 $R_a = R_{frm}$ 、 $C_a = n \times m \times C_m$  になる。なお、 $n$  は信号線 1 2 に接続される画素数、 $m$  はコラム数を示している。モード 2 での第 1 の増幅トランジスタ  $SF_1$  のソース電圧  $V_{s,j}$  の電圧変化は下記(4)式のように対数的な変化で表される。

$$\tau_{th} = \frac{Cm}{io} \times \frac{k \times T}{q}$$

なお、 $q$  は電子電荷を、 $i_0$  はモード 2 の開始点における前記充電電流をそれぞれ示している。

〔 0 0 4 8 〕

これらの関係を模式的に示すと、図 6 のようになる。

時刻  $t_0$  の前では前記モード 1 になって  $R_C$  の時定数で決まる指数関数応答になり、時刻  $t_0$  の後ではモード 2 になって熱放出で決まる対数関数応答になる。また、時刻  $t_0$  では、第 1 の增幅トランジスタ  $SF1$  のソース電圧  $V_{S,j}$  がチャネルポテンシャル  $\phi_j$  とほぼ一致する。これらのことから、モード 2 に移行して十分時間が経過した時刻  $t_s$  でサンプリングを行えば、ほぼ安定したメモリ  $Cm$  の出力レベルを読み取ることができる。また、メモリ  $Cm$  に流れる電流のピーク値は、抵抗  $R$  の抵抗値を適切に選ぶことによって抑制することができる。

[ 0 0 4 9 ]

ここで、図2と図3の場合についての相違点について説明する。

增幅型固体撮像装置全体での時定数  $C_R = C_a \times R_a$  を同じになるようにするには、 $R_{cool} = m \times R_{frm}$  の関係が成り立ち、抵抗  $R_{frm}$  よりも抵抗  $R_{cool}$  は大きな抵抗

抗値になる。図 6 で示したように、各画素で第 1 の増幅トランジスタ S F 1 のソース電圧  $V_{s,j}$  が  $j$  を超えると、第 1 の増幅トランジスタ S F 1 からの電流  $i_{1W}$  は急激に低下し（すなわち第 1 の増幅トランジスタ S F 1 の抵抗値が非常に大きくなり）、この状態をセミオフ状態と呼ぶ。各コラムには多数の画素が接続されているため、コラム単位で見るとソース電圧  $V_{s,j}$  の変化点、すなわち第 1 の増幅トランジスタ S F 1 のソース電圧  $V_{s,j}$  がチャネルポテンシャルを超えたときの電圧は該チャネルポテンシャルの値に応じた異なった値になる。仮に、大多数のコラムが前記セミオフ状態になり、少数のコラムだけがオン状態であるとすると、該少数のコラムにおいてのみ第 1 の増幅トランジスタ S F 1 の抵抗値が小さいまま残り、信号線 12 が、該少数のコラムの容量をなすメモリ C m に直結された状態になる。

10

## 【0050】

図 3 で示した場合では、直列に接続された抵抗  $R_{frm}$  の抵抗値が小さく、前記のような少数のコラムに大きな電流が流れる。これに対して、図 2 で示した場合では、コラムごとに比較的大きな抵抗値をなす抵抗  $R_{col}$  が電源に対して接続されているため、前記のような少数のコラムに大きな電流が流れることを回避することができる。しかし、特定のコラムに接続された大部分の画素において、第 1 の増幅トランジスタ S F 1 がオン状態になり、他のコラムに接続された大部分の画素で、第 1 の増幅トランジスタ S F 1 がセミオフ状態になることは、多数の画素からなる一般的なイメージセンサでは極めてまれである。したがって、簡易的に図 3 のような構成にしても、通常は問題になることはない。

20

## 【0051】

前記 (3) 式及び (4) 式を使用して計算した結果の例を図 7 に示す。図 7 では、画素数が  $1280 \times 1024 = 130$  万、電源電圧が 3.3 V、メモリ C m の容量が 40 fF、抵抗はコラムごとに  $R_{col} = 40$  k である場合を例にしており、チャネルポテンシャルの値は、1 ~ 2 V の範囲での結果を示している。

図 7 から明らかなように、サンプリング時間を  $5 \mu s$  以上にすれば、ほぼ安定したメモリ C m の電圧である容量電圧  $V_{s,j}(t)$  が得られる。また、このときの増幅型固体撮像装置全体でのピーク電流は 105 mA になり、画素内に従来のような例えれば 1  $\mu A$  の定電流負荷を持つ場合の値 1280 mA と比較して、十分に小さい値になる。

## 【0052】

本発明の更なる利点として、低ノイズ化に有利ということがある。前記 (1) 式で示したような、従来型の画素構成では避けられなかったソースフォロワ負荷側で発生するノイズが、本発明では本質的に回避されている。更に、本発明は、次のような低ノイズ化の要因がある。通常は、画素内のメモリ C m に信号を書き込む際、前記 (2) 式のようなノイズが発生し、このノイズは kTC ノイズと言われ、避けることができない。

30

## 【0053】

しかし、本発明においては、図 5 に示したように、書き込みの最終段階ではサブスレッショルド領域動作であるモード 2 になり、この場合にはノイズは下記 (5) 式で表されることが知られている。これはソフトリセットモードと呼ばれ、ノイズ電力が通常動作の 1/2 になる。

$$\overline{V_{n,kTC}^2} = \frac{k \times T}{2 \times Cm} \dots \dots \dots (5)$$

40

## 【0054】

図 1 において、第 1 の増幅トランジスタ S F 1 における出力レベルの最大値は、図 6 において  $V(U_L)$  で示したように、電源電圧  $V_{dd}$  に対してマージンを持つことが望ましい。ここで、 $V(U_L)$  の値は、第 1 の増幅トランジスタ S F 1 のしきい値及び接続部 F D の電圧に依存し、接続部 F D の電圧はリセットトランジスタ R T のドレイン電圧  $V_{rd}$  に依存する。図 1 に例示するように、 $V_{rd} = V_{dd}$  である場合には、第 1 の増幅トランジスタ S F 1 のしきい値をエンハンスメント型にすることにより、前記マージンを確保し

50

易くなる。又は、図示しないが、 $V_{rd} < V_{dd}$  である場合には、第1の増幅トランジスタ S F 1 のしきい値がデプレッション型であっても、前記マージンを確保することが容易になる。このようにして、図6におけるモード1の期間を短縮させることができ、書き込み動作全体の応答を早めることが可能になる。

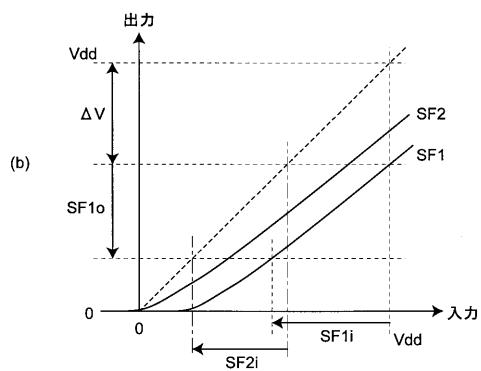

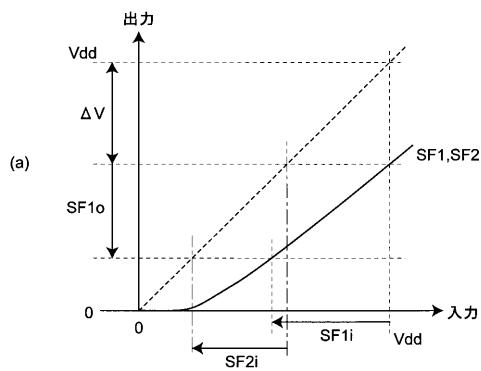

【0055】

図1において、前記のような手法により第1の増幅トランジスタ S F 1 における出力レベル、したがって第2の増幅トランジスタ S F 2 の入力レベルの最大値を電源電圧  $V_{dd}$  よりも低下させた場合、第2の増幅トランジスタ S F 2 がエンハンスメント型であるとすると、図8に示すように、直線性の良い動作領域が低下する。なお、図8で示した入力とはゲート電圧を示しており、図8で示した出力とはソース電圧を示している。図8(a)は、第1及び第2の各増幅トランジスタ S F 1, S F 2 が共にエンハンスメント型である場合の、第1及び第2の各増幅トランジスタ S F 1, S F 2 における入出力電圧の関係例を示している。

10

【0056】

S F 1 i で示した第1の増幅トランジスタ S F 1 の入力電圧、すなわちゲート電圧に対して、該出力電圧、すなわちソース電圧は S F 1 o になり、この電圧が第2の増幅トランジスタ S F 2 のゲート電圧である入力電圧 S F 2 i になる。図8(a)から明らかなように、第2の増幅トランジスタ S F 2 の動作領域の下限付近は直線性から外れた領域になっている。これに対して、図8(b)に示すように、第2の増幅トランジスタ S F 2 をデプレッション型にすることにより、第2の増幅トランジスタ S F 2 の入力電圧 S F 2 i が小さくなても、第2の増幅トランジスタ S F 2 の動作マージンを十分に確保することができる。

20

【0057】

また、図1において、メモリ C m の少なくとも一部をMOS型容量にすることにより、容量密度(単位面積当たりの容量)を高めることができるとなり、限られた画素面積内で十分なメモリ C m の容量値を確保し易くなる。更に、前記MOS型容量をデプレッション型にすればメモリ C m の容量値を確保することができる動作電圧範囲を低い側へ拡大させることができ、前記のように、第1の増幅トランジスタ S F 1 の出力電圧 S F 1 o が低下しても、一定のメモリ C m の容量値を確保しやすくすることができる。

30

【0058】

なお、図1において、転送トランジスタ T X を省略して3トランジスタ型の画素を構成するようにしてもよく、このようにした場合、図1は図9のようになる。図9のようにした場合においても、メモリ C m への書き込み、及びメモリ C m からの読み出しが、図1の場合と同様である。

【0059】

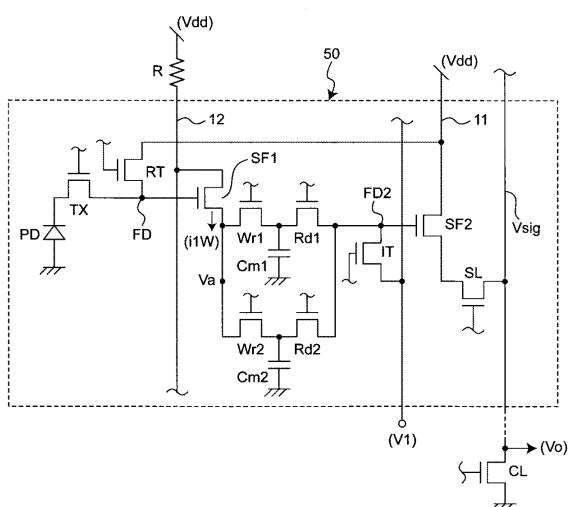

第2の実施の形態。

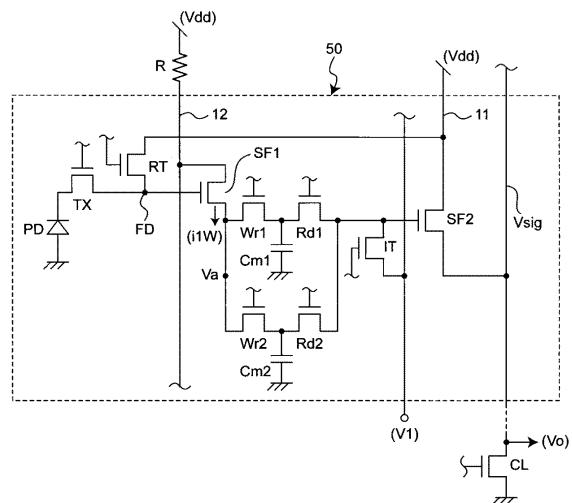

図10は、本発明の第2の実施の形態における増幅型固体撮像装置の画素構成の例を示した図である。なお、図10では、図1と同じもの又は同様のものは同じ符号で示し、ここではその説明を省略すると共に図1との相違点のみ説明する。

図10における図1との相違点は、画素内のメモリを C m 1 と C m 2 の2個にし、これに伴って2つの書き込みスイッチ W r 1, W r 2 と、2つの読み出しへスイッチ R d 1, R d 2 を備えたことにより、これらのことから図1の画素 1 0 を画素 5 0 にした。

40

【0060】

図10において、画素 5 0 は、受光素子 P D、転送トランジスタ T X、リセットトランジスタ R T、第1の増幅トランジスタ S F 1、選択トランジスタ S L、第2の増幅トランジスタ S F 2、第1及び第2の各書き込みスイッチ W r 1, W r 2、第1及び第2の各読み出しへスイッチ R d 1, R d 2、第1及び第2の各メモリ C m 1, C m 2 及び第1及び第2の各メモリ C m 1, C m 2 を初期化する初期化トランジスタ I T を備えている。第1及び第2の各書き込みスイッチ W r 1, W r 2、並びに第1及び第2の各読み出しへスイッチ R d 1, R d 2 は、それぞれNMOSトランジスタからなる。なお、メモリ C m 1 は第1

50

の容量を、メモリ C m 2 は第 2 の容量をそれぞれなし、第 1 の書き込みスイッチ W r 1 は第 1 の書き込みスイッチ部を、第 2 の書き込みスイッチ W r 2 は第 2 の書き込みスイッチ部を、第 1 の読み出しスイッチ R d 1 は第 1 の読み出しスイッチ部を、第 2 の読み出しスイッチ R d 2 は第 2 の読み出しスイッチ部をそれぞれなす。

#### 【 0 0 6 1 】

第 2 の増幅トランジスタ S F 2 のゲートと初期化トランジスタ I T との接続部を F D 2 10 とすると、第 1 の増幅トランジスタ S F 1 のソースと接続部 F D 2 との間に、第 1 の書き込みトランジスタ W r 1 及び第 1 の読み出しトランジスタ R d 1 の直列回路と、第 2 の書き込みトランジスタ W r 2 及び第 2 の読み出しトランジスタ R d 2 の直列回路が並列に接続されている。第 1 の書き込みトランジスタ W r 1 と第 1 の読み出しトランジスタ R d 1 との接続部と接地電圧との間に第 1 のメモリ C m 1 が接続され、第 2 の書き込みトランジスタ W r 2 と第 2 の読み出しトランジスタ R d 2 との接続部と接地電圧との間に第 2 のメモリ C m 2 が接続されている。

#### 【 0 0 6 2 】

なお、図 1 0 の画素 5 0 をマトリクス状に配置した画素アレイを含む 2 次元イメージセンサの構成例を示した図は、図 2 及び図 3 の画素 1 0 の符号を 5 0 に変える以外は同じであることから省略する。第 1 及び第 2 の各書き込みスイッチ W r 1 , W r 2 、並びに第 1 及び第 2 の各読み出しスイッチ R d 1 , R d 2 は、それぞれ信号線 1 6 を介して行駆動回路 1 5 から制御信号がゲートに入力される。

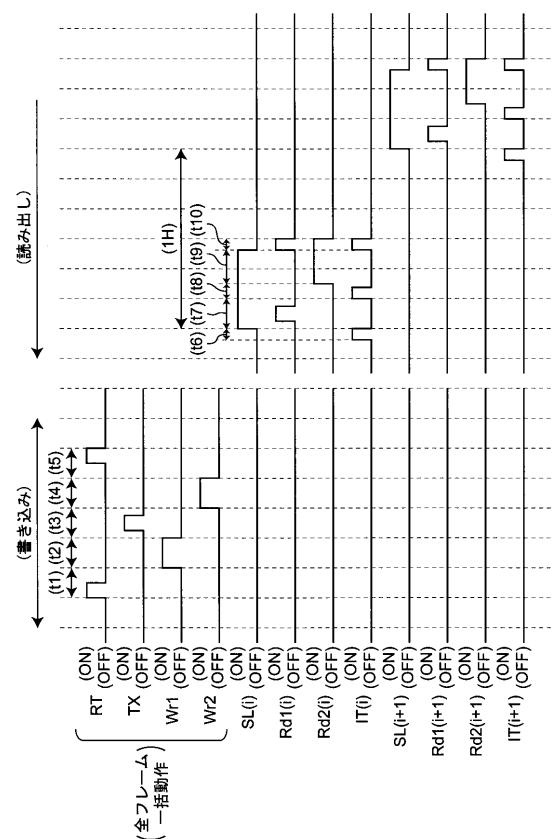

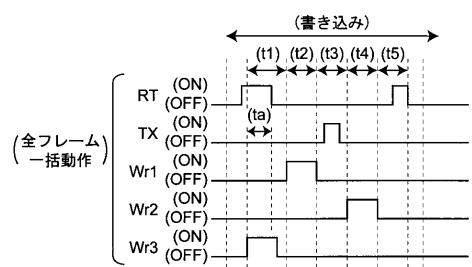

このような構成において、図 1 1 は、図 1 0 で示した画素 5 0 の動作例を示したタイミングチャートであり、図 1 1 を用いて図 1 0 の画素 5 0 の動作について説明する。 20

#### 【 0 0 6 3 】

書き込み動作は全行とも同時動作になる。図 1 1 において、まず期間 t 1 でリセットトランジスタ R T をオン / オフさせて接続部 F D の電圧をリセットし、次に、期間 t 2 において、第 1 の書き込みスイッチ W r 1 をオンさせ、このときの接続部 F D の電圧を前記図 4 から図 7 で説明した本発明の書き込み動作により、リセットレベル F R として第 1 のメモリ C m 1 に書き込む。

次に、期間 t 3 で、転送トランジスタ T X をオンさせて信号電荷を接続部 F D に転送し、期間 t 4 で、第 2 の書き込みスイッチ W r 2 をオンさせて該信号電荷によって変化した接続部 F D の電圧を信号レベル F S として、前記 t 2 の場合と同様の書き込み動作により第 2 のメモリ C m 2 に書き込む。最後に、期間 t 5 で、リセットトランジスタ R T を再度オン / オフさせて接続部 F D の信号電荷を排出して接続部 F D をリセットする。このようにして、各画素単位で、2 つのメモリ C m 1 及び C m 2 に、リセットレベル F R 及び信号レベル F S を独立に全行一括して書き込むことができる。 30

#### 【 0 0 6 4 】

各メモリ C m 1 及び C m 2 に書き込まれた信号の読み出しは行単位で順次行われる。例えば任意の i 行目について示すと次のようになる。なお、符号において、( i ) は i 行目のものであることを示し、( i + 1 ) は ( i + 1 ) 行目のものであることを示している。

まず、期間 t 6 で、初期化トランジスタ I T ( i ) をオン / オフさせて、2 段目のソースフォロワをなす第 2 の増幅トランジスタ S F 2 ( i ) のゲート電圧になる接続部 F D 2 ( i ) の電圧を接地電圧 V 1 に初期化する。 40

次に、期間 t 7 で、第 2 の増幅トランジスタ S F 2 ( i ) と読み出し信号線 V s i g の間の選択トランジスタ S L ( i ) をオンさせた後、読み出しスイッチ R d 1 ( i ) をオンさせて、第 1 のメモリ C m 1 ( i ) に保持されたリセットレベル F R を読み出す。

#### 【 0 0 6 5 】

次に、期間 t 8 で、初期化トランジスタ I T ( i ) を再度オン / オフさせて、先に読み出した信号を消去して接続部 F D 2 の電圧をリセットする。

期間 t 9 では、第 2 の読み出しスイッチ R d 2 ( i ) をオンさせて、第 2 のメモリ C m 2 ( i ) に保持された信号レベル F S を読み出す。

期間 t 1 0 では、選択トランジスタ S L ( i ) をオフさせ、初期化トランジスタ I T ( 50

$i$  ) をオンさせると共に第 1 及び第 2 の各読み出しスイッチ  $R d 1 ( i )$  ,  $R d 2 ( i )$  をそれぞれオンさせ、2 つの第 1 及び第 2 の各メモリ  $C m 1$  ,  $C m 2$  を同時に低電圧  $V 1$  にリセットし、次のフレームでの書き込み動作に備える。

#### 【 0 0 6 6 】

このようにして、読み出された 2 つの信号  $F R$  及び  $F S$  について、図示しないが後段の処理回路で両者の差分を取る相関二重サンプリング ( C D S ) 動作を行うことにより、接続部  $F D$  で発生するリセットノイズを除去することができるだけでなく、1 段目ソースフオロワをなす第 1 の増幅トランジスタ  $S F 1$  及び 2 段目ソースフオロワをなす第 2 の増幅トランジスタ  $S F 2$  のそれぞれにおいて、しきい値が画素間でばらつくことによって発生する、画素ごとの固定パターンノイズをも除去することができる。

10

#### 【 0 0 6 7 】

なお、図 1 0 において、選択トランジスタ  $S L$  を省略するようにしてもよく、このようにした場合、図 1 0 は図 1 2 のようになる。なお、図 1 2 の画素 5 0 をマトリクス状に配置した画素アレイを含む 2 次元イメージセンサの構成例を示した図においても、図 2 及び図 3 の画素 1 0 の符号を 5 0 に変える以外は同じであることから省略する。

このような構成において、図 1 3 は、図 1 2 の画素 5 0 における動作例を示したタイミングチャートであり、図 1 3 を用いて図 1 2 の画素 5 0 の動作について説明する。

#### 【 0 0 6 8 】

図 1 3 において、書き込み動作は図 1 1 と同じであるのでその説明を省略する。なお、図 1 3 においても、各メモリ  $C m 1$  及び  $C m 2$  に書き込まれた信号の読み出しは行単位で順次行われ、例えば任意の  $i$  行目について示すと次のようになる。図 1 3 の符号においても、(  $i$  ) は  $i$  行目のものであることを示し、(  $i + 1$  ) は(  $i + 1$  ) 行目のものであることを示している。

20

図 1 2 では、初期化トランジスタ  $I T$  をノーマリオン ( 読み出し動作時以外はオン ) にする。したがって、読み出し動作では、非選択行ではすべての初期化トランジスタ  $I T$  がオンしており、これらの画素では、接続部  $F D 2$  が接地電圧等の低電圧  $V 1$  に固定される。このため、ソースフオロワをなしている第 2 の増幅トランジスタ  $S F 2$  はオフする。

#### 【 0 0 6 9 】

読み出し行  $i$  においては、期間  $t 7$  と期間  $t 9$  においてのみ、初期化トランジスタ  $I T$  (  $i$  ) がオフし、接続部  $F D 2 ( i )$  はフローティング状態になる。期間  $t 7$  では、この間に第 1 の読み出しトランジスタ  $R d 1 ( i )$  がオンし、第 1 のメモリ  $C m 1 ( i )$  からリセットレベル  $F R$  が接続部  $F D 2 ( i )$  に読み出され、接続部  $F D 2 ( i )$  の電圧がこれに対応した大きい電圧になる。このため、このような行  $i$  のみ第 2 の増幅トランジスタ  $S F 2 ( i )$  はオンし、行  $i$  のリセットレベル  $F R$  が選択的に読み出される。

30

#### 【 0 0 7 0 】

同様に、期間  $t 9$  では、この間に第 2 の読み出しスイッチ  $R d 2 ( i )$  がオンし、第 2 のメモリ  $C m 2 ( i )$  から信号レベル  $F S$  が接続部  $F D 2 ( i )$  に読み出され、接続部  $F D 2 ( i )$  の電圧がこれに対応した大きい電圧になって、この行  $i$  の信号レベル  $F S$  が選択的に読み出される。動作範囲としては、 $F R < F S$  であることから、 $F S > V 1$  であれば非選択行の影響を受けずに読み出しを行うことができる。また、図示しない後段の処理回路で、リセットレベル  $F R$  と信号レベル  $F S$  の差分を取る C D S 動作を行うことも、図 1 0 及び図 1 1 の場合と同様である。

40

#### 【 0 0 7 1 】

第 3 の実施の形態 .

前記第 2 の実施の形態で示した画素構成の場合、期間  $t 1$  でリセットトランジスタ  $R T$  をオンさせて接続部  $F D$  をリセットする際、第 1 の増幅トランジスタ  $S F 1$  の出力側  $V a$  がフローティング状態になって電圧が不定になるため、接続部  $F D$  と出力側  $V a$  との間の容量  $C a$  に不定電圧情報がメモリされる。これは、次にリセットトランジスタ  $R T$  をオフさせて接続部  $F D$  をフローティング状態にすると、容量  $C a$  を介して接続部  $F D$  の電圧が前記不定電圧情報に影響され、誤差が生じる。このような誤差をなくすようにしたもの

50

本発明の第3の実施の形態とする。

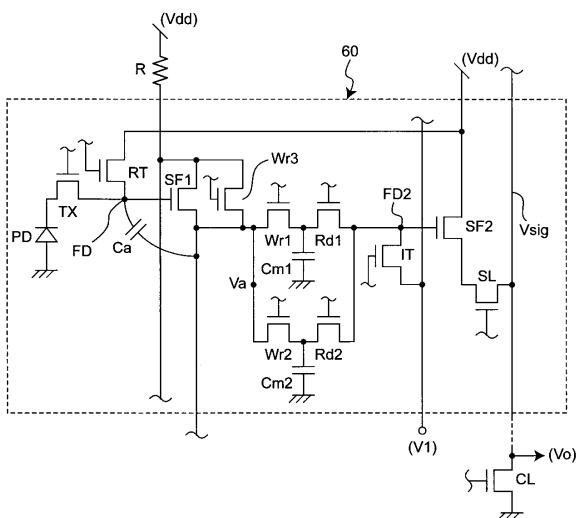

【0072】

図14は、本発明の第3の実施形態における増幅型固体撮像装置の画素構成の例を示した図である。なお、図14では、図10と同じもの又は同様のものは同じ符号で示し、ここではその説明を省略すると共に図10との相違点のみ説明する。

図14における図10との相違点は、第1の増幅トランジスタSF1に並列にNMOSトランジスタである制御スイッチWr3を接続したことにあり、これに伴って、図10の画素50を画素60にした。なお、制御スイッチWr3は制御スイッチ部をなす。

図14において、制御スイッチWr3がオンしているときには、第1の増幅トランジスタSF1の出力側Vaの電圧が電源電圧Vddになるように、制御スイッチWr3をデプレッション型のMOSトランジスタにすることが望ましい。あるいは、図示しないが、制御スイッチWr3のドレイン側を電源電圧Vddとは異なる所定のDC電圧としてもよい。

【0073】

図14において、画素60は、受光素子PD、転送トランジスタTX、リセットトランジスタRT、第1の増幅トランジスタSF1、選択トランジスタSL、第2の増幅トランジスタSF2、第1及び第2の各書き込みスイッチWr1, Wr2、第1及び第2の各読み出しスイッチRd1, Rd2、制御スイッチWr3、第1及び第2の各メモリCm1, Cm2及び第1及び第2の各メモリCm1, Cm2を初期化するための初期化トランジスタITを備えている。

なお、図14の画素60をマトリクス状に配置した画素アレイを含む2次元イメージセンサの構成例を示した図は、図2及び図3の画素10の符号を60に変える以外は同じであることから省略する。制御スイッチWr3は、信号線16を介して行駆動回路15からの制御信号がゲートに入力される。

【0074】

このような構成において、図15は、図14で示した画素60の動作例を示したタイミングチャートであり、図15を用いて図14の画素60の動作について説明する。

図15において、まず最初のリセット期間t1内の期間taにおいて、リセットトランジスタRTと制御スイッチWr3を同時にオンさせて、接続部FDをリセットすると共に出力側Vaの電圧を電源電圧Vddにすることにより、容量Caには確定した電圧情報が書き込まれる。この後、期間t2~t5では、図11で示した動作が誤差を生じることなく行われる。このような動作は、全画素一括して行われ、その後の読み出し動作は、図11の場合とまったく同じである。

【0075】

なお、前記第1から第3の各実施形態では、画素内の各MOSトランジスタがNMOS型である場合を例にして説明したが、これは一例であり、本発明はこれに限定するものではなく、PMOS型の場合についても、電圧、電流の極性を逆にすることによって同様に適用することができる。また、受光素子PDの信号電荷が電子である場合を例にして説明したが、正孔である場合においても信号蓄積による極性変化が逆になることで、同様に適用することができる。

【符号の説明】

【0076】

10, 50, 60 画素

PD 受光素子

TX 転送トランジスタ

RT リセットトランジスタ

SF1 第1の増幅トランジスタ

SF2 第2の増幅トランジスタ

Wr 書き込みスイッチ

SL 選択トランジスタ

10

20

30

40

50

I T 初期化トランジスタ

C m メモリ

W r 1 第1の書き込みスイッチ

W r 2 第2の書き込みスイッチ

W r 3 制御スイッチ

R d 1 第1の読み出しスイッチ

R d 2 第2の読み出しスイッチ

C m 1 第1のメモリ

C m 2 第2のメモリ

R , R c o l , R f r m 抵抗

10

C L 定電流負荷トランジスタ

11, 12, 13 電源線

14 行デコーダ回路

15 行駆動回路

16 駆動線

17 コラム信号処理回路

18 コラムデコーダ回路

19 水平信号線

20 画素アレイ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図15】

【図17】

【図18】

【図19】

---

フロントページの続き

(56)参考文献 特開2007-329722(JP,A)

特開2008-283593(JP,A)

特開2002-344809(JP,A)

特開2005-065074(JP,A)

特開2008-017288(JP,A)

特開2006-311515(JP,A)

特開2001-218112(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H01L 21/339

H01L 27/14 - 27/148

H01L 29/762