**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) Int. Cl.

H04N 5/46 (2006.01)

(45) 공고일자

2007년08월07일

(11) 등록번호

10-0746525

(24) 등록일자

2007년07월31일

(21) 출원번호 10-2000-0044005

(22) 출원일자 2000년07월29일

심사청구일자 2005년07월29일

(65) 공개번호 10-2001-0015474

(43) 공개일자 2001년02월26일

(30) 우선권주장 60/146,459 1999년07월30일 미국(US)

(73) 특허권자 톰슨 라이센싱

프랑스 92648 블로뉴 세데 께 알퐁스 르 갈로 46

(72) 발명자 데이스마이클스코트

미국인디아나주46077시온스빌인디안파이프레인1103

플리크너앤드류켄트

미국인디아나주46032카멜템퍼드라이브10243

(74) 대리인 김진희

김태홍

(56) 선행기술조사문현

KR100323661 B1 KR1019960002047 B1

KR1019960010496 B1 KR1019960013648 B1

**심사관 : 박진우**

전체 청구항 수 : 총 22 항

**(54) 디스플레이 프레임 레이트 적응화 방법 및 장치**

**(57) 요약**

수신기의 디스플레이 프레임 레이트를 수신 신호의 영상 프레임 레이트에 적응시키기 위한 본 발명의 방법은 수신 신호의 영상 프레임 레이트와 수신기의 디스플레이 프레임 레이트를 비교하는 단계와, 상기 비교 단계에 응답하여 표시되는 필드 당 라인수 및 프레임 당 라인수를 조절하는 단계 또는 상기 조절 단계에 응답하여 수신기에 대한 디스플레이 프레임 레이트 제어 신호를 발생하는 단계를 포함한다.

**대표도**

도 10

**특허청구의 범위**

## 청구항 1.

수신기의 디스플레이 프레임 레이트를 수신 신호의 영상 프레임 레이트에 적응시키기 위한 방법으로서, 수신 신호의 영상 프레임 레이트를 수신기의 디스플레이 프레임 레이트와 비교하는 비교 단계(92)와, 상기 비교 단계에 응답하여 표시되는 필드 당 라인수 또는 프레임 당 라인수를 조절하는 조절 단계(93)와, 상기 조절 단계에 응답하여 상기 수신기에 대한 디스플레이 프레임 레이트 제어 신호를 발생시키는 디스플레이 프레임 레이트 제어 신호 발생 단계(94)와, 상기 표시되는 필드 당 라인수 또는 프레임 당 라인수를 상기 영상 프레임 레이트와 평형시키기 위해 상기 디스플레이 프레임 레이트 제어 신호를 상기 비교 단계에 적용하는 단계를 포함하는 디스플레이 프레임 레이트 적응화 방법.

## 청구항 2.

제1항에 있어서, 상기 수신 신호가 아날로그 신호 포맷인 경우, 상기 비교 단계(92)는 상기 영상 신호 프레임 레이트를 나타내는 수직 동기 신호(NTSC Vsync)의 위상과, 상기 디스플레이 프레임 레이트 제어 신호로서의 수직 동기 신호(Vsync)의 위상을 비교하는 단계를 포함하는 것을 특징으로 하는 디스플레이 프레임 레이트 적응화 방법.

## 청구항 3.

제2항에 있어서, 상기 필드 당 라인수를 조절하는 단계(93)는 위상들이 서로 접근하도록 반복되는 것을 특징으로 하는 디스플레이 프레임 레이트 적응화 방법.

## 청구항 4.

제1항에 있어서, 상기 수신 신호가 디지털 신호(DS) 포맷인 경우, 상기 비교 단계는 상기 수신 신호의 타이밍 레퍼런스(PCR)와 상기 수신기의 로컬 타이밍 레퍼런스(local PCR)를 비교하는 단계를 포함하는 것을 특징으로 하는 디스플레이 프레임 레이트 적응화 방법.

## 청구항 5.

제1항에 있어서, 상기 비교 단계(92)는 상기 수신 신호의 프로그램 클록 레퍼런스(PCR)와 상기 수신기의 로컬 프로그램 클록 레퍼런스(local PCR)를 비교하는 단계를 포함하는 것을 특징으로 하는 디스플레이 프레임 레이트 적응화 방법.

## 청구항 6.

제4항에 있어서, 상기 조절 단계(93)는 상기 타이밍 레퍼런스(PCR)와 상기 로컬 타이밍 레퍼런스(local PCR)가 서로 접근하도록 반복되는 것을 특징으로 하는 디스플레이 프레임 레이트 적응화 방법.

## 청구항 7.

제1항에 있어서, 상기 디스플레이 프레임 레이트 제어 신호에 응답하여, 상기 수신 신호에 의해 표현되는 이미지가 보여지는 디스플레이 튜브에 대하여 수직 편향 신호를 발생시키는 수직 편향 신호 발생 단계를 더 포함하는 것을 특징으로 하는 디스플레이 프레임 레이트 적응화 방법.

### 청구항 8.

제7항에 있어서, 상기 수직 편향 신호 발생 단계는 상기 디스플레이 튜브에 DC 결합된 상기 수신 신호에 대해 일정 경사 수직 편향 신호를 발생시키는 단계를 포함하는 것을 특징으로 디스플레이 프레임 레이트 적응화 방법.

### 청구항 9.

제1항에 있어서, 상기 조절 단계는 상기 디스플레이 프레임 레이트의 평균치를 감소시키기 위해 상기 표시되는 필드 당 라인수를 추가하는 단계, 및 상기 디스플레이 프레임 레이트의 평균치를 증가시키기 위해 상기 필드 당 라인수를 줄이는 단계를 포함하는 것을 특징으로 하는 디스플레이 프레임 레이트 적응화 방법.

### 청구항 10.

제1항에 있어서, 상기 수신기는 DC 결합된 일정 경사 램프 수직 편향 시스템(500)을 포함하는 것을 특징으로 하는 디스플레이 프레임 레이트 적응화 방법.

### 청구항 11.

제1항에 있어서, 상기 조절 단계는 초당 29.97 프레임, 초당 30 프레임, 초당 59.94 프레임, 및 초당 60 프레임으로 구성된 그룹에서 선택된 평균 디스플레이 프레임 레이트에 대해 표시되는 필드 당 라인수를 변화시키는 단계를 포함하는 것을 특징으로 하는 디스플레이 프레임 레이트 적응화 방법.

### 청구항 12.

제1항에 있어서, 1080 개 비율 영상 라인인 경우, 상기 조절 단계는 1123 개, 1125 개 및 1127 개로 구성된 그룹 중에 하나가 선택되도록 표시되는 필드 당 라인수를 변화시키는 단계를 포함하는 것을 특징으로 하는 프레임 레이트 적응화 방법.

### 청구항 13.

제1항에 있어서, 프레임 당 540 개 순차 영상 라인인 2 개의 연속 프레임의 경우, 상기 조절 단계는 1124 개, 1126 개 및 1128 개로 구성된 그룹 중에 하나가 선택되도록 표시되는 필드 당 라인수를 변화시키는 단계를 포함하는 것을 특징으로 하는 디스플레이 프레임 레이트 적응화 방법.

### 청구항 14.

디스플레이 프레임 레이트를 수신 신호의 영상 프레임 레이트에 적응시키는 수신기로서,

DC 결합된 일정 경사 램프 수직 편향 시스템(106)과,

디스플레이 투브(107)를 구동시키기 위한 비디오 처리용 제1 신호와 상기 수신 신호의 영상 프레임 레이트를 나타내는 제2 신호를 제공하는 수신 신호용 신호 디코더(102, 103)와,

상기 제2 신호의 타이밍과, 상기 수신기의 디스플레이 프레임 레이트를 나타내는 타이밍 신호를 비교하기 위한 비교기(110, 112)와,

상기 타이밍 신호 및 상기 제2 신호의 필드 당 라인수 또는 프레임 당 라인수를 평형시키기 위하여 상기 비교기에 응답해, 상기 수신기에 의해 표시되는 필드 당 라인수 및 프레임 당 라인수를 조절하는 조절 수단(111, 113)과,

상기 표시되는 필드 당 라인수 또는 프레임 당 라인수를 조절하는 수단에 응답해서 수평 및 수직 편향 신호를 제공하여 상기 편향 시스템을 구동시키는 라스터 발생기(105)

를 포함하는 디스플레이 프레임 레이트 적응 수신기.

### 청구항 15.

제14항에 있어서, 상기 신호 디코더는 상기 수신 신호의 아날로그 형식을 디코딩하기 위한 것이고, 상기 제2 신호는 수직 동기 신호인 것을 특징으로 하는 디스플레이 프레임 레이트 적응 수신기.

### 청구항 16.

제14항에 있어서, 상기 신호 디코더(102)는 상기 수신 신호의 디지털 형식을 위한 디멀티플렉서이고, 상기 제2 신호는 타이밍 레퍼런스 신호인 것을 특징으로 하는 디스플레이 프레임 레이트 적응 수신기.

### 청구항 17.

제14항에 있어서, 상기 신호 디코더는 아날로그 신호 디코더(103) 및 디지털 신호 디멀티플렉서(102) 모두를 포함하고, 상기 제2 신호(103)는 상기 아날로그 신호 디코더에 의해 출력될 경우 수직 동기 신호이고, 상기 디멀티플렉서(102)에 의해 출력될 경우 프로그램 클록 레퍼런스인 것을 특징으로 하는 디스플레이 프레임 레이트 적응 수신기.

### 청구항 18.

제14항에 있어서, 상기 수신 신호가 아날로그 형식인 경우, 상기 비교기는 수직 동기 신호인 상기 제2 신호와, 제2 수직 동기 신호인 상기 타이밍 신호를 비교하는 위상 비교기(110)인 것을 특징으로 하는 디스플레이 프레임 레이트 적응 수신기.

### 청구항 19.

제14항에 있어서, 상기 수신 신호가 디지털 형식인 경우, 상기 비교기(112)는 상기 수신 신호의 프로그램 클록 레퍼런스인 상기 제2 신호와, 로컬 프로그램 클록 레퍼런스인 상기 타이밍 신호를 비교하는 것을 특징으로 하는 디스플레이 프레임 레이트 적응 수신기.

### 청구항 20.

제14항에 있어서, 1080 개 비율 영상 라인을 포함하는 수신 신호의 경우, 상기 조절 수단(111)은 1123 개, 1125 개 및 1127 개로 구성된 그룹 중 하나가 선택되도록 표시되는 필드 당 라인수를 변화시키는 것을 포함하는 것을 특징으로 하는 디스플레이 프레임 레이트 적응 수신기.

## 청구항 21.

제14항에 있어서, 프레임 당 540 개 순차 영상 라인인 2 개의 연속 프레임을 포함하는 수신 신호의 경우, 상기 조절 수단(111)은 1124 개, 1126 개 및 1128 개로 구성된 그룹 중에 하나가 선택되도록 표시되는 두 개의 프레임 당 라인수를 변화시키는 것을 포함하는 것을 특징으로 하는 디스플레이 프레임 레이트 적응 수신기.

## 청구항 22.

디스플레이 프레임 레이트를 수신 신호의 영상 프레임 레이트에 적응시키기 위한 수신기로서,

DC 결합된 일정 경사 램프 수직 편향 시스템(106)과,

디스플레이 튜브를 구동하기 위한 비디오 처리용 비디오 신호와, 아날로그 수신 신호용 제1 수직 동기 신호를 제공하는 아날로그 수신 신호용 아날로그 디코더(103)와,

상기 디스플레이 튜브(107)를 구동하기 위한 비디오 디코딩용 데이터 신호와 디지털 수신 신호용 제1 타이밍 레퍼런스 신호를 제공하는 디지털 수신 신호용 디지털 디코더(102)와,

상기 수직 동기 신호의 위상과, 상기 편향 시스템을 구동하기 위한 제2 수직 동기 신호의 위상을 비교하기 위한 제1 비교기(110)와,

상기 제1 타이밍 레퍼런스 신호와 상기 수신기의 제2 타이밍 레퍼런스 신호를 비교하기 위한 제2 비교기(112)와,

상기 제1 비교기에 응답하여 상기 수신기에 의해 표시되는 필드 당 라인수를 조절하기 위한 제1 수단(111)과,

상기 제2 비교기에 응답하여 상기 수신기에 의해 표시되는 필드 당 라인수를 조절하기 위한 제2 수단(113)과,

표시되는 필드 당 라인수를 조절하는 상기 제1 또는 제2 수단에 응답하여 상기 편향 시스템을 구동시키기 위해 수평 및 수직 편향 신호를 제공하는 라스터 발생기(105)

를 포함하는 디스플레이 프레임 레이트 적응 수신기.

### 명세서

#### 발명의 상세한 설명

##### 발명의 목적

##### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 일반적으로 텔레비전 수신기에 관한 것으로, 더욱 구체적으로는 DC 결합된 일정 경사 램프 수직 편향 시스템에서의 디스플레이 프레임 레이트 적응화(frame rate adaptation)에 관한 것이다.

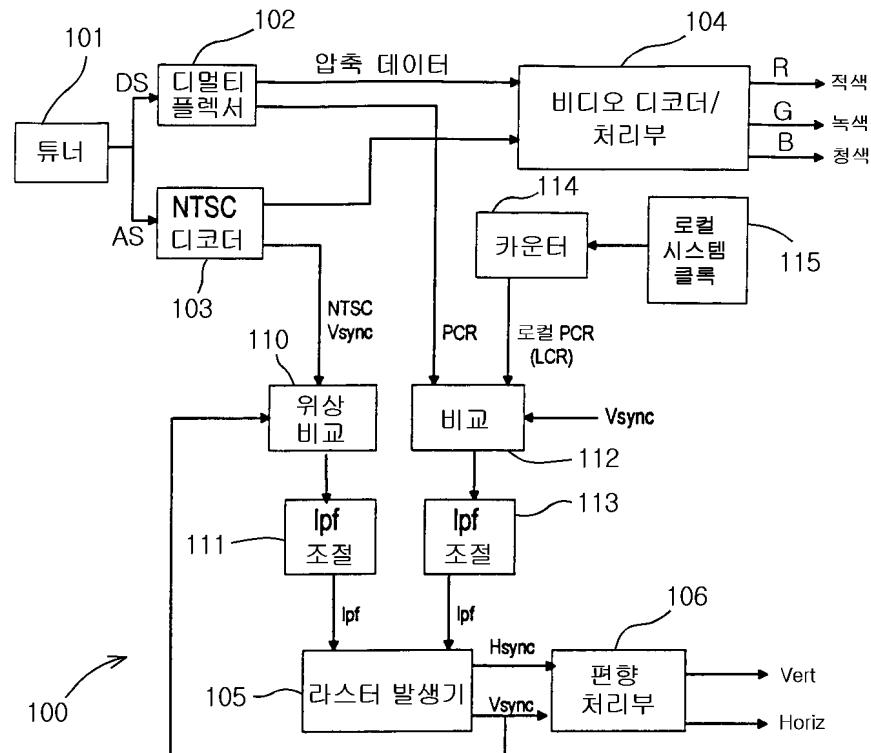

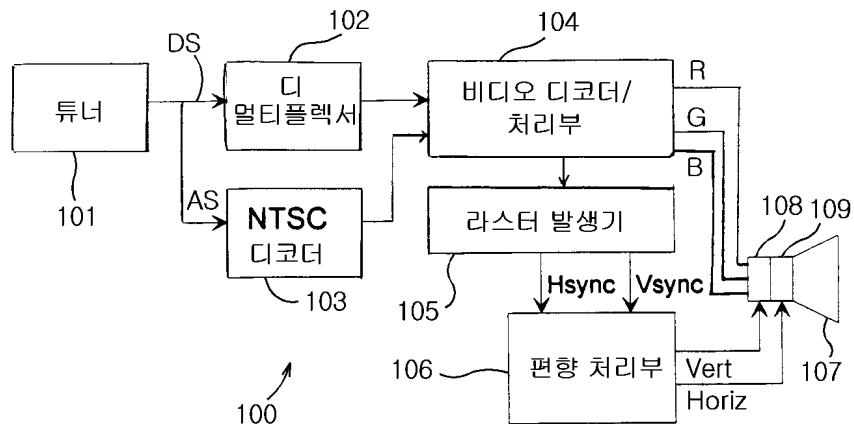

도 1은 아날로그 또는 디지털 포맷 신호 처리를 위한 예시적인 TV 수신기의 시스템 블록도(100)이다. 수신기(100)의 동작은 NTSC(National Television Systems Committee) 및 ATSC(Advanced Television Systems Committee) 신호 방식에서 논의될 것이다. 그러나 여기에서 다루는 본 발명의 실제적인 관점은 NTSC 및 ATSC 신호 방식에 한정되지 않는다. 튜너(101)로부터, 디지털 신호(DS)는 잘 알려진 디지털 디코더 형태인, 디멀티플렉서(102)에 공급되고, 디멀티플렉서(102)는 선택된 비디오 신호를 비디오 디코더/처리부(104)에 전달하고, 비디오 디코더는 적(R), 녹(G), 청(B) 컬러 성분 신호를 영상 튜브(107)에 제공한다. 튜너(101)로부터 수신된 아날로그 신호(AS)는 뒤따르는 비디오 처리부(104)에 선택적 비디오 신호를 제공하는 NTSC 디코더(103)에 공급되고, 비디오 디코더/처리부(104)는 영상 튜브(107)에 R, G, B 컬

러 성분 신호를 공급한다. 디코더(103)로부터 비디오 디코더/처리부(104)로 전달되는 NTSC 신호는 540 개 순차 활성 라인에서 변환된 포맷이다. 수평 및 수직 동기 신호(Hsync, Vsync)는 비디오 디코더/처리부(104)에 응답하여 라스터 발생기(105)에 의해 발생된다. 그리고 동기 신호는 편향 처리부(106)에 공급되고, 편향 처리부(106)는 편향 코일(108, 109)을 구동시키기 위한 수직 및 수평 편향 신호(Vert, Horiz)를 공급한다.

일반적으로, 라스터 발생기(105)는 영상 프레임이 비디오 신호와 함께 전송되는 레이트와 동일한 레이트에서 표시되도록 수신 신호에 동기를 맞추어야 한다. 프레임의 드롭 또는 반복은 퀄리티 TV 수신기(quality TV receiver)로 움직임을 묘사하는데 바람직하지 못하다. 일시적인 아티팩트의 생성을 피하기 위해 TV 수신기가 입력 프레임을 추적할 수 있는 합리적인 방법이 필요하다. 60 Hz, 30 Hz 및 24 Hz의 프레임 레이트에 기초하여, ATSC 방식에 의해 지원되는 18 개의 영상 주사 포맷과 프레임 레이트가 있다. 그러나, 만약 ATSC 및 NTSC 양쪽 모두의 동시 방송 기간 중에 NTSC 신호의 비디오 수신을 가능하게 하는, 59.94 Hz, 29.97 Hz 및 23.97 Hz의 NTSC 방식에 따른 레이트를 고려할 때, 총 36 개의 영상 포맷이 존재한다. ATSC 영상 포맷의 수만 고려하는 경우, 좁은 주파수 범위에서 동작하기 적합한 TV 편향 시스템 설계가 목적이라면 입력 비디오 영상 프레임 레이트를 추적하기 어렵다.

### 발명이 이루고자 하는 기술적 과제

수신기의 디스플레이 프레임 레이트를 수신 신호의 영상 프레임 레이트에 적응시키기 위한 본 발명의 방법은, 수신 신호의 영상 프레임 레이트와 수신기의 디스플레이 프레임 레이트를 비교하는 단계와, 상기 비교 단계에 응답하여 표시되는 필드 당 라인수 또는 프레임 당 라인수를 조절하는 단계 및 상기 조절 단계에 응답하여 수신기에 대해 디스플레이 프레임 레이트 제어 신호를 발생하는 단계를 포함한다.

디스플레이 프레임 레이트를 수신 신호의 영상 프레임 레이트에 적응시키기 위한 본 발명의 수신기는 DC 결합 일정 경사 램프 수직 편향 시스템과, 디스플레이 투브를 구동시키는 비디오 처리를 위한 제1 신호와 수신 신호의 영상 프레임 레이트를 나타내는 제2 신호를 제공하는 수신 신호용 신호 디코더와, 제2 신호와 수신기의 디스플레이 프레임 레이트를 나타내는 타이밍 신호를 비교하는 비교기를 구비한다. 수신기는 또한 비교기에 응답하여 수신기가 표시하는 필드 당 라인수 또는 프레임 당 라인수를 조절하는 수단과, 표시되는 필드 당 라인수 또는 프레임 당 라인수를 조절하는 수단에 응답하여 편향 시스템을 구동하기 위해 수평 및 수직 편향 신호를 제공하는 라스터 발생기를 포함한다.

### 발명의 구성

일반적으로, 프레임은 전송된 것과 동일 레이트로 표시되어야만 한다, 즉 프레임을 드롭하거나 반복해야 한다. 프레임 드롭 또는 부가가 허용되지 않으므로, TV 수신기가 입력 프레임을 추적할 수 있는 바람직한 방법이 필요하다. ATSC 영상 포맷수를 고려하는 경우, 이것은 협대역의 주파수 상에서 동작하도록 최적화된 TV 편향 시스템에서 어려워진다.

표시되는 필드 당 라인수를 조절함으로써, 다중 영상 프레임 디코드 포맷용 디스플레이 포맷 컨버터와 함께 사용될 때, 수직 레이트를 약간만 가변시키고, 수평 라인 주파수를 일정하게 유지하는 방법을 제공한다. 본 발명의 방법에 의해 허용된 수직 레이트의 변화는 수신기 대 송신기 시간축 간의 모든 프레임 레이트와, 다양한 ATSC 영상 포맷의 포맷 변환에서 기인하는 출력 프레임 레이트의 변화를 추적하기에 충분하다.

본 발명의 디스플레이 프레임 레이트 적응화의 기본요소는, TV 수신기에서 사용될 수 있는 것으로서, DC 결합 수직 편향 시스템, 수직 편향 램프에 대해 일정한 경사 및 평균 프레임 레이트를 느리게 하기 위한 더 많은 수평 라인의 디스플레이 출력 필드 또는 평균 프레임 레이트를 빠르게 하기 위한 더 적은 수평 라인의 디스플레이 출력 필드를 포함한다. 드롭되거나 부가될 수평 라인수는 그 라인이 수직 블랭킹 구간(수직 퀀텀 소거 구간) 동안에 발생되므로 영상 라스터에 단순히 표시되지 않는다.

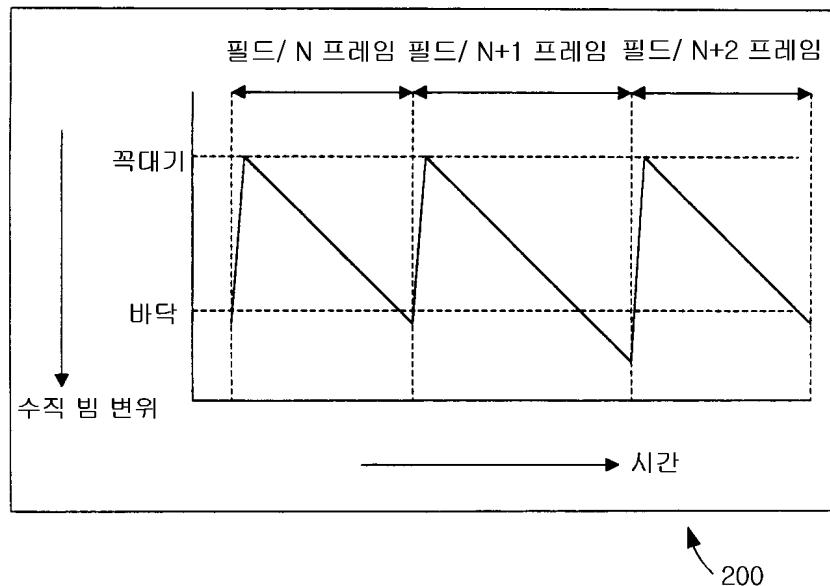

이상의 구성요소의 상호 작용은 도 2에 그림으로 예시되고, 이 도면에서 "꼭대기"에 해당하는 램프 부분은 연속 프레임에서 영상의 상단, 예컨대 라인 1을 나타내고, "바닥"은 활성 디스플레이 라인의 바닥을 나타낸다, "바닥" 아래에 있는 램프의 일부는 비활성, 즉 디스플레이 불능 라인을 나타내고, "꼭대기"와 "바닥" 사이 부분은 활성, 즉 디스플레이 가능 라인을 나타낸다. 이 예시에서, 프레임 당 활성(디스플레이 가능) 및 비활성(디스플레이 불능) 라인수는 다음과 같다. N 개의 프레임은 M+1 개의 수평 라인을 갖고, N+1 개의 프레임은 M+2 개의 수평 라인을, N+2 개의 프레임은 M+1 개의 수평 라인을 갖는다.

M+2 개의 프레임에 대한 M+1 개의 프레임의 상대 수는 시간에 따라 평균한 값으로서 전체의 프레임 레이트를 조절한다. 시간이 경과함에 따라, 평균 프레임 레이트는 임의적으로 정확해진다. 유일한 요건은 시스템이 공칭보다 더 낮은 순간 프

레임 레이트와 공칭보다 더 높은 순간 프레임 레이트 사이에서 디더링(dithering)해야만 한다는 것이다. 일반적으로 디더링은 순차 디스플레이 시스템에서는 프레임마다 또는 비월 시스템에서는 필드마다 불과 1 개 또는 2 개 이상씩 수평 라인의 총수를 가변시켜야 한다. 사실상, "꼭대기" 위에도 디스플레이 불능 라인이 있을 수 있지만, 이점은 이 실시예에서는 중요하지 않다.

도 2는 표시된 주사 라인이 프레임마다 드롭되거나 부가될 때, 수직 변위의 평균 값이 프레임마다 변하는 것을 도시한다. AC 결합 수직 편향 시스템은 꼭대기 위와 바닥 아래에서 라인수가 동일하도록 평균 수직 변위를 탐색하는 경향이 있다. 이것은 활성 디스플레이의 제1 및 그 다음의 수직 부분을 변하게 하는 결과를 초래하므로, 영상은 이 평균 레벨이 변할 때 위 아래로 이동할 것이다. 한편, DC 결합 편향 시스템은 표시된 제1 라인의 수직 부분을 기준인 꼭대기에 강제 유지시킴으로써, 영상은 CRT 면의 특정 위치에 고정된다. 수직 램프의 일정 경사는 "바닥"에서 최종 디스플레이 가능 라인의 수직 위치에 고정된다.

DC 결합 편향은 "꼭대기"에서 제1 라인에 고정되고 일정 경사는 "바닥"에 최종 디스플레이 가능 라인에 고정되므로, 표시된(활성) 영상 사이즈 및 위치에 영향을 끼치지 않고 "바닥" 아래에 라인을 추가할 수 있다. 또한, 이미지는 공간 일관성으로 표시되어 단지 프레임만 영향을 받는다.

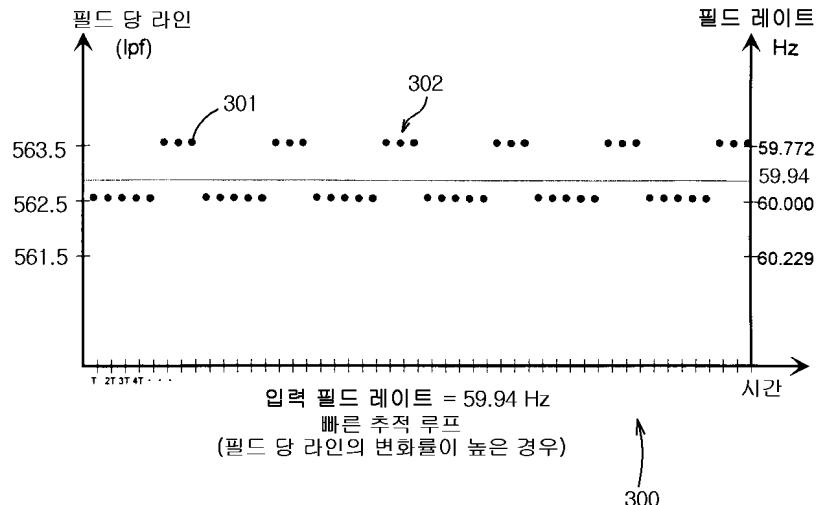

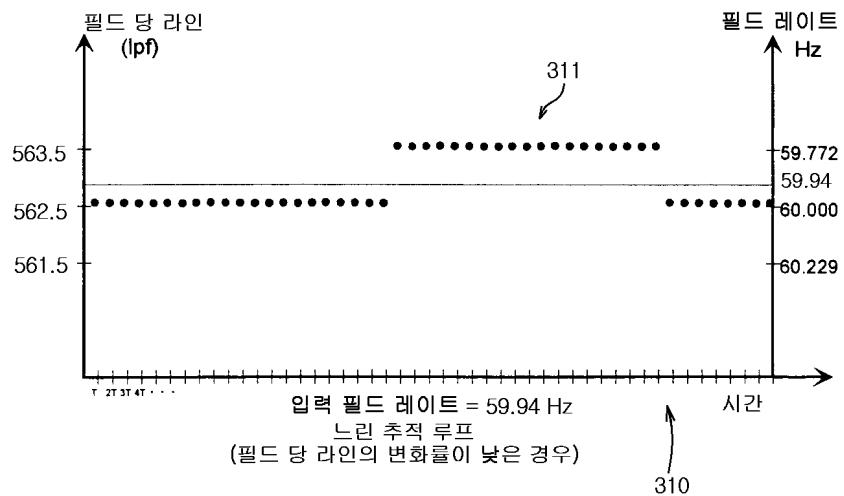

라스터 발생기(105)가 필드 당 562.5 개의 라인에서 60Hz의 공칭 필드 레이트에 대해 구성되는 경우를 고려한다. 도 3a는 입력 비디오의 필드 레이트가 59.94Hz인 상황을 나타낸다. 라스터 발생기(105)의 시스템 클록이 일정하므로, 필드(301) 당 라인수는 59.94Hz의 평균 출력 필드 레이트를 발생시키기 위해 수시로 변한다. 이 특정 예에 있어서, 8 개의 필드 중 매 3 개(302)는 공칭적인 562.5 개의 라인 대신에 563.5 라인이 필요하다.

출력 라스터에서 필드 당 라인수를 조절하는 추적 루프의 다이내믹을 고려하는 것이 중요하다. 루프 응답은 빠르거나 느릴 것이다. 도 3a의 그래프(300)는 상대적으로 짧은 시간 동안 평균 필드 레이트를 유지함으로써 추적 루프가 빨라진 경우를 도시한다. 도 3b의 그래프(310)는 더 느린 추적 루프를 나타내며, 평균 필드 레이트는 장시간 동안 유지되고, 40 개의 필드 중 19 개(311)는 필드 당, 공칭 562.5 개 라인 대신에 563.5 개 라인(단위는 lpf(lines per field)임)을 갖는다.

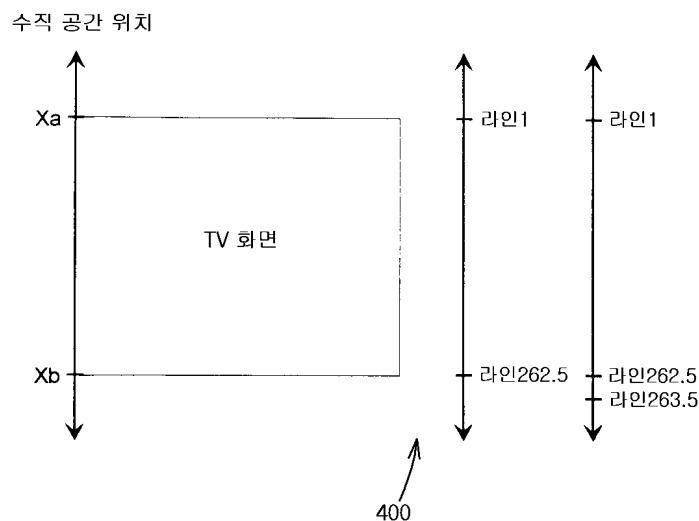

필드 당 라인수의 동적인 변화는 수직 편향 처리에 일부 제약을 부과한다. 필드 당 라인수를 조절하는 시스템에서, 수직 편향 시스템 설계에 대한 표준적 접근법은 DC 결합 및 일정 경사 램프를 부과하는 것이다. 직류 결합 요건은 비디오의 제1 라인을 TV 화면 상에 항상 동일한 수직 위치에서 시작하게 하는 것이다. 도 4의 도식(400)에 있어서, 라인 1은 수직 위치(Xa)에서 도시되고, 포인트 Xb는 TV 화면의 바닥을 나타낸다. DC 결합 수직 시스템에 있어서, 라인 1은 항상 포인트 Xa에서 발생한다. 일정 경사 요건은 출력 라스터에서의 라인수에 관계없이, 라인 562.5을 항상 위치 Xb에 발생시키는 것이다.

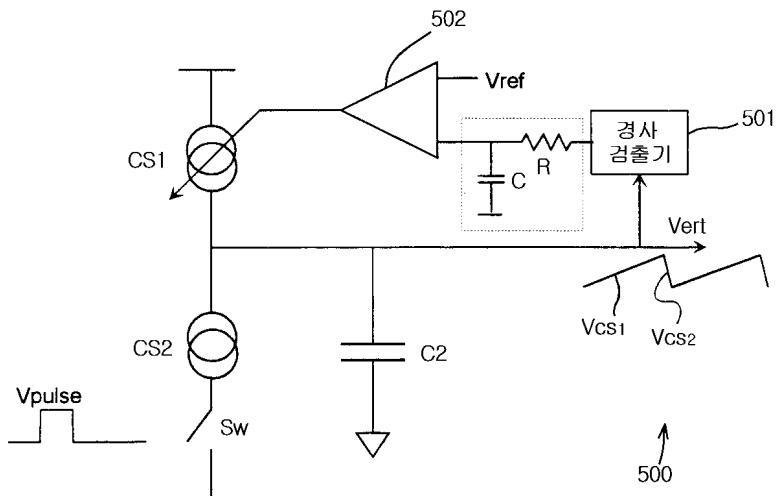

도 5는 예시적인 일정 경사 수직 편향 신호(Vert) 발생기에 대한 개략도를 나타낸다. 수직 램프 편향 전압(Vert)은 수직 트레이스 전압 경사(VCS1) 및 수직 리트레이스 전압 경사(VCS2)를 포함한다. 도시된 바와 같이, 스위치(SW)가 개방되면, 저항(R)과 커패시터(C) 네트워크를 통해, 수직 편향 전압(Vert)과 기준 전압(Verf)을 비교하는 차동 증폭기에 출력되는 수직 편향 전압(Vert)의 일부가 경사 검출기(501)에 피드백된다. 정진류원(CS1)의 동작 전류 레벨은 차동 증폭기(502)의 출력에 의해 변화되어 커패시터(C2)를 충전시키고 수직 램프 트레이스 전압(Vcs1)을 공급한다. 스위치(SW)가 폐쇄될 경우, 전류원(CS1)은 커패시터(C2)를 충전하여 리트레이스 전압(VCS2)을 발생시키는 전류원(CS2)으로 끌려진다. 일정 경사 수직 편향 발생기는 기술적으로 잘 알려져 있다. 수직 추적 레이트는 경사 검출기(501)의 출력과 차동 증폭기(502)의 입력 사이에 연결된 RC 네트워크의 시정수에 영향을 받는다는 것에 주목해야 한다.

본 발명의 디스플레이 프레임 레이트 적응화는 디지털 위성 시스템(DSS) 및 ATSC 지상 전송에서 디지털 오디오 및 비디오를 디코딩하고 표시하기 위해 설계된 오디오/비디오(A/V) 디코더 보드에 적용될 수 있다. A/V 디코더 보드에 의해 공급되는 아날로그 비디오는 최대 81MHz인 고정 주파수에서 클록킹되는 디지털 아날로그(D/C) 컨버터에서 출력된다. 이 클록의 각 사이클에서 출력되는 것이 1 픽셀이다. 표시될 모든 영상은 업(up)-샘플될 것이고, 필요하다면, 수평 라인 당 1920 개의 활성 픽셀로 업샘플된다. 라인 당 비활성 픽셀수는 라인 당 총 2400 개의 픽셀에 대해 480 개 이상에 고정될 것이다. 활성 라인수는, 비월 디스플레이 경우, 초 당 29.97 개의 프레임(초당 프레임 수:fps) 또는 30 fps에서 1080 개가 된다. 순차 디스플레이 경우, 활성 라인수는 59.94 fps 또는 60 fps에서 540 개가 된다.

도 6의 표에서, 4 가지 예는 라스터 상에서 표시되는 라인수가 상이한 디스플레이 프레임 레이트를 달성하기 위해 필드 단위 또는 프레임 단위로 얼마나 감소되고 증가될 수 있는지를 도시한다. 라인 당 192 개의 픽셀과 1080 개 비월 수직 라인의 제1 경우(601)에서, 매 10 개의 필드에 대해 562.5 개 라인이 필드 1~4, 6~8 및 10에 표시되고, 주사 라인이 하나 추가되어 필드 5에 표시되며, 주사 라인이 하나 감소되어 필드 9에 표시되어 30 fps(601)의 평균 필드 레이트를 제공한다.

라인 당 1920 개의 픽셀과 1080 개 비율 수평 라인의 제2 경우(602)에 있어서, 매 10 개의 필드에 대해 563.5 개의 주사 라인이 필드 1, 3, 5, 7~8 및 10에 표시되고, 주사 라인이 하나 감소되어 필드 2, 4, 6 및 9에 표시되어 29.97 fps의 평균 필드 레이트를 제공한다.

라인 당 1920 개의 픽셀과 540 개 순차 수평 라인의 제1 경우(603)에 있어서, 10 개의 필드마다 562 개의 주사 라인이 필드 1, 3 및 7~9에 표시되고, 주사 라인이 하나 추가되어 필드 2, 4~6 및 10에 표시되어 60 fps의 평균 필드 레이트를 제공한다. 라인 당 1920 개의 픽셀과 540 개 순차 수평 라인의 제2 경우(604)에 있어서, 매 10개 필드마다 563 개의 주사 라인이 필드 1~7 및 9~10에 표시되고 주사 라인이 하나 추가되어 필드 8에 표시되어 59.94 fps의 평균 프레임 레이트를 얻게 된다.

상이한 디스플레이 및 영상 포맷에 대한 상세한 동기 및 타이밍도를 이용하여 본 발명의 디스플레이 프레임 레이트 적응화 구현을 설명한다. 이들 도면은 이전의 활성 영상 라인의 완료 후에, 주사된 디스플레이 라인수를 감소시키면 활성 영상 라인의 프레임 사이에 있는 수직 블랭킹 구간에서 수직 플라이백 펄스가 더 일찍 시작되어야 한다는 것을 나타낸다. 이전의 활성 영상 라인의 완료 후에, 주사된 디스플레이 라인수를 증가시킬려면 활성 영상 라인의 프레임 사이에 있는 수직 블랭킹 구간에서 수직 플라이백 펄스가 늦게 시작되어야 한다.

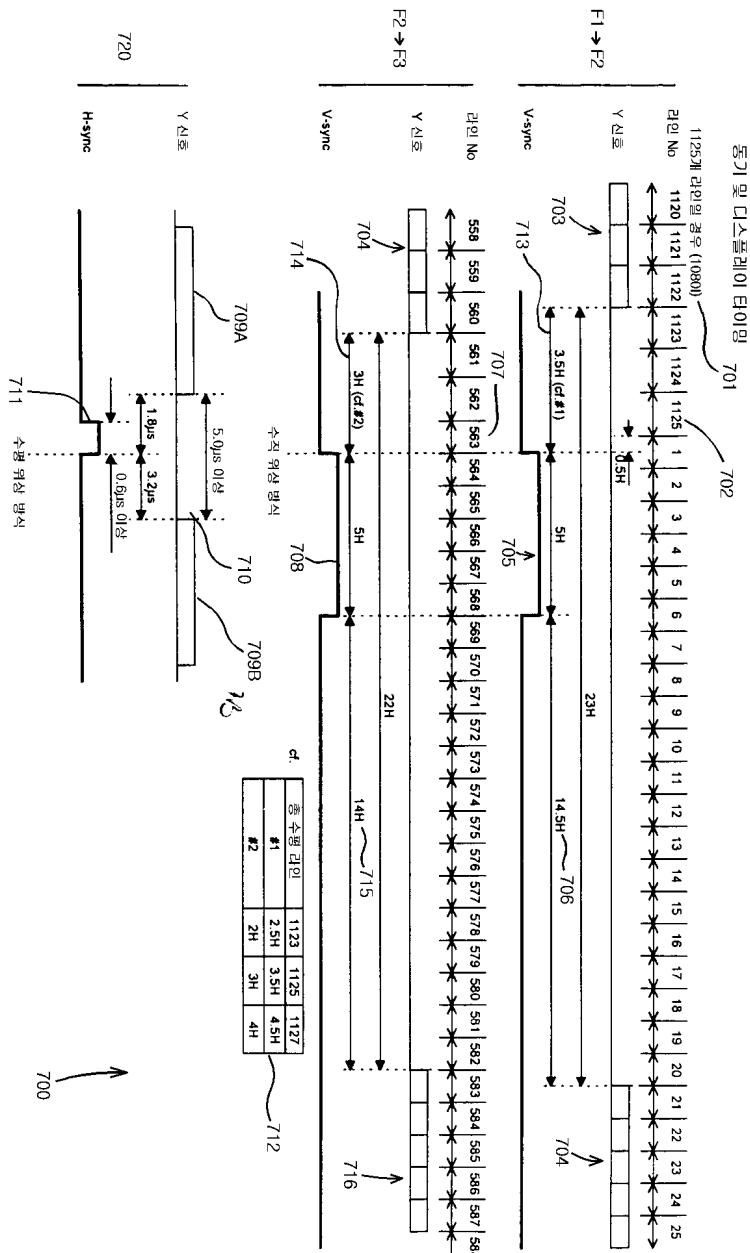

도 7은 1080 개 비율 영상 라인에 대해서 1125 개의 디스플레이 라인의 디스플레이 포맷에 관한 동기 및 타이밍 조절을 나타낸다. Y 신호 영상 라인의 주어진 필드(703)에서 Y 신호 영상 라인의 다음 필드(704)까지의 트랜지션을 나타내는 상단의 동기 및 타이밍도(F1-F2)가 도시하는 바와 같이, 활성 Y 신호 영상 라인(703)은 디스플레이 주사 라인(1122)과, 비활성 Y 신호 영상 라인의 그 다음 필드(704)가 다음 프레임 주사의 디스플레이 주사 라인(21)에서 시작된다. 수직 동기 과형(V-sync)은 최종 디스플레이 주사 라인(1125)로부터 1/2 수평 주사 라인 기간(0.5 H)만큼 오프셋된 플라이백 펄스(705)의 상승 엣지에서, 즉 디스플레이 주사 라인(1122)으로부터 총 3.5 H 수평 라인 기간(713) 후에 플라이백을 시작한다. 플라이백 펄스(705)의 5H 수평 라인 기간 후에, 수직 블랭킹은 다음의 활성 Y 신호 영상 라인(704)이 시작할 때까지 14.5 H 수평 디스플레이 라인 기간(706) 동안 계속된다.

Y 신호 영상 라인의 다음 필드(704)에서 Y 신호 영상 라인의 연속 필드(716)로의 트랜지션(F2-F3) 중에, 수직 블랭킹은 디스플레이 라인의 이전 필드의 디스플레이 주사 라인(561~563)과 동시에 발생하여 3 H 수평 라인 기간(714) 동안 계속되며, 수직 플라이백 펄스(708)는 디스플레이 라인(564)과 동시에 시작되어 5 H 수평 라인 기간(715) 동안 계속된다. 수직 블랭킹은 플라이백(708)에 이어 14 H의 수평 라인 기간(175) 동안 계속된다.

하단의 타이밍도(720)를 참조하면, Y 신호 영상 라인인, 도시된 예시적 영상 라인(709A, 709B) 사이에 있는 수평 블랭킹 구간(710)에서, 수평 플라이백 펄스(711)의 상승 엣지는 이전의 Y 신호 영상 라인(709A)의 하강 엣지보다 1.2 ms(도면에 도시된 1.8보다 0.6 더 작음)만큼 늦게 시작된다.

본 발명의 디스플레이 프레임 레이트 적응화를 달성하기 위한 동기 및 타이밍의 조절은 디스플레이 프레임 레이트를 높여서 디스플레이 라인을 1125 개에서 1123 개로 용이하게 감소하기에 앞서 수직 플라이백 펄스(705, 708)를 시작함으로써 이루어진다. 디스플레이 라인을 1125 개에서 1127 개로 증가시킬려면, 블록(712)에 나타낸 바와 같이, 수직 플라이백 펄스(705, 708)의 시작이 지연되어야 한다. 1123 개 디스플레이 라인의 경우, 수직 플라이백 펄스(705, 708)는 각각, 이전의 Y 신호 영상 라인(703, 704)에서부터 최종 영상 라인 후에 2.5 H 및 2 H 수평 라인 기간에서 시작된다. 1127 개 디스플레이 라인의 경우, 수직 플라이백 펄스(705, 708)은 각각 이전 Y 신호 영상 라인(703, 704)으로부터 최종 영상 라인 후에 4.5 H 및 4 H 수평 라인 기간에서 시작된다. 요약하면, 1125 개에서 1123 개로 디스플레이 라인을 감소시킬려면 플라이백 펄스의 상승 엣지를 1 수평 기간(1H) 일찍 시작하는 것이 필요하고, 1125 개에서 1127 개로 디스플레이 라인을 증가시킬려면 수직 플라이백 펄스(705, 708)의 상승 엣지를 1 수평 라인 기간(1H)만큼 지연시켜야 한다.

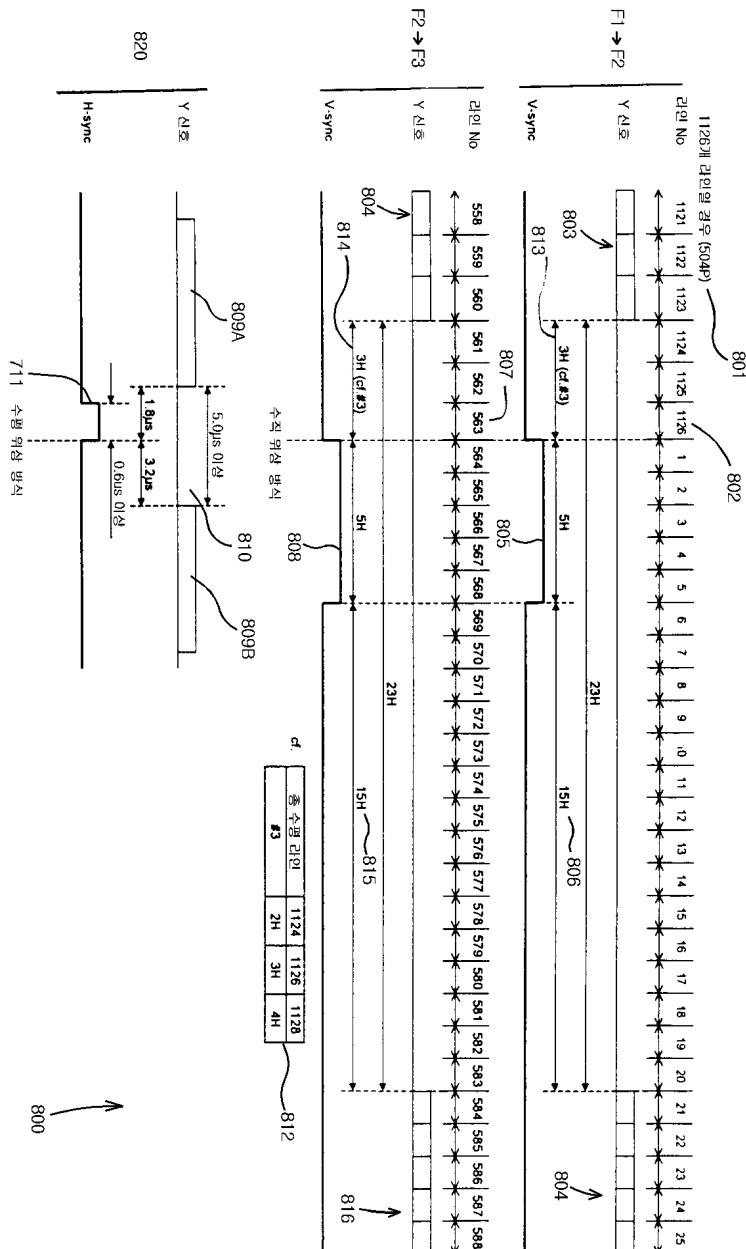

도 8은 프레임 당 540 개 순차 영상 라인인 2 개의 연속 프레임에 대해, 1126 개의 디스플레이 라인의 디스플레이 및 영상 포맷에 대한 동기 및 타이밍 조절을 나타낸다. 비록 563 개 디스플레이 라인만이 활성 영상 라인의 각 프레임마다 발생되지만, 도 7의 동기 및 타이밍도와 쉽게 비교하기 위해 프레임 당 540 개 순차 영상 라인인, 2 개 프레임에 대한 1126 개 디스플레이 라인을 나타낸다.

Y 신호 영상 라인의 주어진 필드(803)에서부터 Y 신호 영상 라인의 그 다음 필드(804)까지의 트랜지션을 나타내는 상단의 동기 및 타이밍도(F1-F2)가 나타내는 바와 같이, 활성 Y 신호 영상 라인(803)은 디스플레이 주사 라인(1123)과, 비활성 Y 신호 영상 라인의 이어지는 수직 블랭킹의 23 개 수평 라인 기간(23H)으로 끝난다. 수직 블랭킹의 완료 후에 Y 신호 영상 라인의 다음 필드(804)가 다음 프레임 주사의 디스플레이 주사 라인(21)으로 시작된다. 수직 동기 과형(V-sync)은 다

음의 활성 Y 신호 영상 라인에 대한 디스플레이 프레임의 처음 디스플레이 주사 라인(1)과 함께 플라이백 펄스(805)의 상승 엣지에서, 즉 디스플레이 주사 라인(1123)의 종단에서 총 3 H의 수평 라인 기간(813) 후에 플라이백을 시작한다. 플라이백 펄스(805)의 5H 수평 라인 기간 후에, 수직 블랭킹은 다음의 활성 Y 신호 영상 라인(804)이 시작할 때까지 15 H 수평 디스플레이 라인 기간(806) 동안 계속된다.

Y 신호 영상 라인의 그 다음 필드(804)에서 Y 신호 영상 라인의 후속 필드(816)로의 트랜지션(F2-F3) 중에, 수직 블랭킹은 디스플레이 라인의 이전 필드의 디스플레이 주사 라인(561-563)과 동시에 발생하여 3 H 수평 라인 기간(814) 동안 계속되며, 수직 플라이백 펄스(808)는 디스플레이 라인(564)과 동시에 발생하여 5 H 수평 라인 기간 동안 계속된다. 수직 블랭킹은 수직 플라이백 펄스(808) 후에 14 H의 수평 라인 기간(815) 동안 계속된다.

하단의 타이밍도(820)를 참조하면, Y 신호 영상 라인, 즉 도시된 예시적 영상 라인(809A, 809B) 사이에 있는 수평 블랭킹 구간(810) 동안, 수평 플라이백 펄스(811)의 상승 엣지는 이전의 Y 신호 영상 라인(809A)의 하강 엣지로부터 단지 1.2 ms(도면에 도시된 1.8보다 0.6 더 작음)에서 시작된다.

본 발명의 디스플레이 프레임 레이트 적응화를 달성하기 위한 동기 및 타이밍의 조절은 디스플레이 프레임 레이트를 높여 디스플레이 라인을 1125 개에서 1124 개로 용이하게 감소하기에 앞서 수직 플라이백 펄스(805, 808)를 일찍 시작함으로써 이루어진다. 디스플레이 라인을 1126 개에서 1128 개로 증가시킬려면 블록(812)에 도시된 바와 같이, 수직 플라이백 펄스(805, 808)의 시작이 지연되어야 한다. 1124 개 디스플레이 라인의 경우, 수직 플라이백 펄스(805, 808)는 각각, 이전 Y 신호 영상 라인(803, 804)에서 최종 영상 라인 후 2 H 수평 라인 기간에서 시작된다. 1128 개의 디스플레이 라인의 경우에, 수직 플라이백 펄스(805, 808)는 이전의 Y 신호 영상 라인(803, 804)에서 최종 영상 라인 후 4 H 수평 라인 기간에서 시작된다. 요약하면, 1126 개에서 1124 개로 디스플레이 라인을 감소시키기 위해 플라이백 펄스의 상승 엣지를 1 수평 기간(1H) 일찍 시작하는 것이 필요하고, 1126 개에서 1127 개로 디스플레이 라인을 증가시킬려면 수직 플라이백 펄스(805, 808)의 상승 엣지를 1 수평 라인 기간(1H)만큼 지연시켜야 한다.

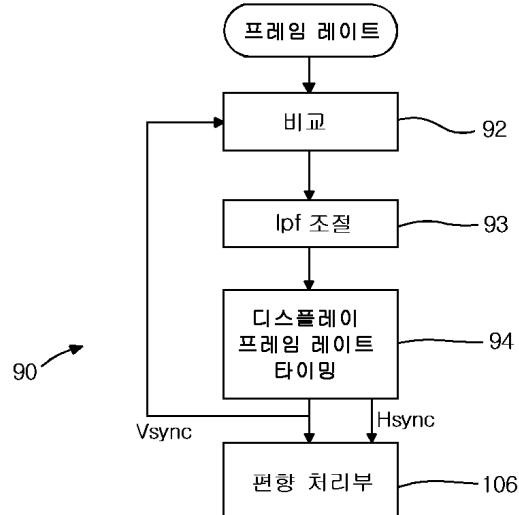

본 발명인 디스플레이 프레임 레이트 적응화를 구현하기 위한 기본 단계가 도 9에 표시된다(90). 수신된 영상 신호(91)의 프레임 레이트는 수신기의 디스플레이 프레임 레이트(94)과 비교된다(92). 영상 신호 프레임 레이트와 디스플레이 프레임 레이트 간의 임의의 차이에 응답하여, 표시되는 필드 당 라인수(lpf)가 조절된다(93). 조절되는 필드 당 라인수는 디스플레이 프레임 레이트 타이밍(94)을 변경하고, 디스플레이 프레임 레이트를 나타내는 신호를 출력하여 편향 처리부(106) 등의 디스플레이 제어 처리부(95)를 구동시킨다. 디스플레이 프레임 레이트 신호는 양 신호 간의 차이가 매우 작거나 "제로"가 될 때까지 영상 신호 프레임 레이트와 반복 비교되도록 계속적으로 피드백된다.

본 발명의 디스플레이 프레임 레이트 적응화를 구현하기 위한 예시적인 수신기(100)가 도 10에 도시된다. 비록 도시된 예시적인 수신기(100)는 이중 신호 처리 경로, 즉 아날로그 신호 처리를 위한 경로 및 디지털 신호 처리를 위한 경로를 구비한 것으로 도시하지만, 본 발명의 디스플레이 프레임 레이트 적응화는 단지 아날로그 전용 또는 디지털 전용 수신기에서도 실시될 수 있다.

수신기(100)에 있어서, 라스터 발생기(105)는 필드 당 라인수(lpf) 파라미터를 입력으로서 채택하고 적합한 수직 및 수평 동기 신호(Vert, Horiz)를 제공한다. 필드 당 라인수(lpf)의 계산은 필드 단위로 행해진다. 수직 동기(Vsync)가 라스터 발생기(104)에서 매 lpf 라인마다 발생하므로, 수시로 lpf 조절은 도 7 및 도 8에서 전술한 바와 같이, 플라이백 펄스의 상승 엣지를 일찍 또는 나중에 시작함으로 이루어진다.

NTSC 포맷의 아날로그 신호(AS)의 경우, NTSC 디코더(103)는 또한 NTSC-Vsync 신호를 초당 60 필드의 포맷으로 출력하는데, 이 신호의 위상은 라스터 발생기(105)로부터 초당 60 프레임의 포맷으로, 발생된 수직 동기 신호(Vsync)의 위상과 비교된다(110). 라스터 발생기(105)로의 필드 당 라인수(lpf) 입력은 라스터 발생기(105)에서 NTSC-Vsync 신호와 Vsync 신호 간의 위상 에러가 매우 적거나 제로가 될 때까지 조절된다(111). 이때 위상 에러 제로는 디스플레이 프레임 레이트 및 비디오 신호의 전송된 프레임 레이트 간의 프레임 동기를 위한 조건이 된다.

MPEG-2 포맷의 디지털 신호(DS)의 경우, 디멀티플렉서, 즉 DEMUX(102)는 두개의 압축된 신호를 비디오 디코더/처리부(104)에 전달하고 비교기(112)에 프로그램 클록 레퍼런스(PCR)를 전달한다. 프로그램 클록 레퍼런스(PCR)는, 예컨대 타이밍 레퍼런스와 같은 타임스탬프, 즉 통신 링크의 전송측에서 인코더 클록을 복구 또는 추적하면서 비디오 디코더(104)를 동기 위해 MPEG-2 인코더에 의해 트랜스포트 스트림 내에 삽입되는 것이다. PCR은 로컬 시스템 클록(115)에 의해 구동되는 카운드(114)로부터 출력된 로컬 프로그램 클록 레퍼런스(LCR)와 비교된다. PCR은 전송측에서 인코딩 시스템 클록에 의한 카운터 구동기의 출력 샘플이라는 것을 주목해야 한다.

필드 당 라인수(lpf)는 라스터 발생기(104)에 의해 출력된 수직 동기 신호(Vsync)에 동기를 맞춘 LCR 및 PCR의 비교(112)에 응답하여 조절되고(113), lpf는 LSR 및 PCR 간의 차이가 "제로"에 근접하거나 거의 "제로"일 때까지 조절된다. 이것은 이전의, PCR 및 LCR간의 차이가 매우 작거나 거의 "제로"일 때까지 로컬 시스템 클록 주파수를 조절하기 위해 비교기(112)로부터의 출력을 이용하는 클록 복구 구성과 상당히 다르다.

당업자에게 가능한 전술한 것들의 변형, 조합 및 치환은 본 발명의 기술 사상 및 범주 내에 포함된다.

### 발명의 효과

다중 영상 프레임 디코드 포맷을 위한 디스플레이 포맷 컨버터와 함께 사용할 경우, 표시되는 필드 당 라인수를 조절하여 수직 레이트를 약간만 가변시키고, 수평 라인 레이트를 일정하게 유지하는 방법을 제공한다. 본 발명의 방법에 의해 허용된 수직 레이트의 변화는 수신기 대 송신기 시간축 간의 모든 프레임 레이트 주파수와, 다양한 ATSC 영상 포맷의 포맷 변환에서 기인하는 출력 프레임 레이트의 변화를 추적하기에 충분하다.

### 도면의 간단한 설명

도 1은 디지털 및 아날로그 비디오 신호 양쪽 모두를 위한 예시적인 TV 수신기의 시스템 블록도.

도 2는 라스터 출력으로 표시된 라인수의 변화와 DC 결합 일정 경사 수직 편향간의 관계를 개략적으로 나타내는 도면.

도 3a은 필드 당 라인수의 상대적으로 높은 변화률로 표시되는 필드 당 라인수의 적응화를 도시하는 도면.

도 3b는 필드 당 라인수의 상대적으로 낮은 변화률로 표시되는 필드 당 라인수의 적응화를 도시하는 도면.

도 4는 수평 라스터 라인의 수직 공간 위치 지정을 도시하는 도면.

도 5는 일정 경사 수직 램프 발생기의 개략적인 도면.

도 6은 디스플레이 프레임 레이트를 디코딩된 프레임 레이트에 동기를 맞추기 위해 조절된 필드 당 라인수를 나타내는 예시적인 표.

도 7은 1125 개의 디스플레이 라인과 1080 개 비율 영상 라인의 경우에 대한 동기화 및 디스플레이 타이밍도.

도 8은 프레임 당 540 개 순차 영상 라인인 2 개의 연속 프레임에 대한 1126 개의 디스플레이 라인의 경우에 대한 동기화 및 디스플레이 타이밍도.

도 9는 디스플레이 프레임 레이트를 입력 영상 프레임 레이트에 적응시키는 본 발명에 대한 필수 단계도.

도 10은 본 발명의 디스플레이 프레임 레이트 적응화를 구현하기 위한 특징을 포함하기 위해 변형된 도 1의 시스템 블록도.

<도면의 주요 부분에 대한 부호의 설명>

101 : 튜너

102 : 디멀티플렉서

103 : NTSC 디코더

104 : 비디오 디코더/처리부

105 : 라스터 발생기

106 : 편향 처리부

107 : 영상 투브

108, 109 : 편향 코일

도면

도면1

도면2

도면3a

도면3b

도면4

도면5

도면6

디스플레이 레이트 : 1920 x 1080 @ 30 fps (ave)

| 601 | 필드 수     | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     | 9     | 10    | ... |

|-----|----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-----|

| 601 | 필드당 총 라인 | 562.5 | 562.5 | 562.5 | 562.5 | 562.5 | 562.5 | 562.5 | 562.5 | 561.5 | 562.5 | ... |

디스플레이 레이트 : 1920 x 1080 @ 29.97 (ave)

| 602 | 필드 수     | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     | 9     | 10    | ... |

|-----|----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-----|

| 602 | 필드당 총 라인 | 563.5 | 562.5 | 563.5 | 562.5 | 563.5 | 562.5 | 563.5 | 563.5 | 562.5 | 563.5 | ... |

디스플레이 레이트 : 1920 x 540P @ 60 ips

| 603 | 필드 수      | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | ... |

|-----|-----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 603 | 프레임당 총 라인 | 562 | 563 | 562 | 563 | 563 | 563 | 563 | 562 | 562 | 563 | ... |

디스플레이 레이트 : 1920 x 540P @ 59.94 ips

| 604 | 필드 수      | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | ... |

|-----|-----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 604 | 프레임당 총 라인 | 563 | 563 | 563 | 563 | 563 | 563 | 563 | 564 | 563 | 563 | ... |

도면7

## 도면 8

도면9

도면10