(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5335791号

(P5335791)

(45) 発行日 平成25年11月6日(2013.11.6)

(24) 登録日 平成25年8月9日(2013.8.9)

(51) Int.Cl.

F 1

G 11 C 16/02 (2006.01)

G 11 C 16/06 (2006.01)G 11 C 17/00 601 Q

G 11 C 17/00 632 A

請求項の数 5 (全 12 頁)

(21) 出願番号 特願2010-520026 (P2010-520026)

(86) (22) 出願日 平成20年6月25日 (2008.6.25)

(65) 公表番号 特表2010-536115 (P2010-536115A)

(43) 公表日 平成22年11月25日 (2010.11.25)

(86) 國際出願番号 PCT/US2008/068091

(87) 國際公開番号 WO2009/020718

(87) 國際公開日 平成21年2月12日 (2009.2.12)

審査請求日 平成23年6月16日 (2011.6.16)

(31) 優先権主張番号 11/833,545

(32) 優先日 平成19年8月3日 (2007.8.3)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 テキサス州 78735

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100142907

弁理士 本田 淳

(72) 発明者 チョイ、ジョン エス.

アメリカ合衆国 78735 テキサス州

オースティン メンラー ドライブ 7

624

最終頁に続く

(54) 【発明の名称】高電圧メモリ擾乱を防止する方法及び回路

## (57) 【特許請求の範囲】

## 【請求項 1】

メモリアレイを有する回路を動作させる方法であつて：

ロジック電源ドメインを使用してメモリ制御ロジックを動作させること；

発振器の発振に応答して、前記ロジック電源ドメインの電圧よりも高い電圧を生成すること；

前記高い電圧を使用して前記メモリアレイを動作させること；

前記ロジック電源ドメインが第1レベル以上にあるとき、前記メモリ制御ロジックによつて前記発振器の動作を制御すること；

前記ロジック電源ドメインが前記第1レベルよりも低下したとき、低電圧インジケータ信号をアサートすること；

前記低電圧インジケータ信号がアサートされたことに応答して発振器制御回路によつて前記発振器をディセーブルにすること

を備え、前記発振器制御回路は、前記ロジック電源ドメインと、前記高い電圧よりも低い値であるが前記ロジック電源ドメインよりも高い値を有するメモリ電源ドメインとによつて電源供給される、方法。

## 【請求項 2】

第1出力及び第2出力を有し、ロジック電源ドメインによって電源が供給されるメモリ制御ロジックと；

前記ロジック電源ドメインに接続され、出力を有する低電圧インジケータ回路と；

10

20

前記低電圧インジケータ回路の出力に接続される第1入力と、前記メモリ制御ロジックの第1出力に接続される第2入力と、出力とを有する発振器制御回路と；

前記発振器制御回路の出力に接続される制御入力と、発振器出力とを有する発振器と；

前記発振器の発振器出力に接続され、前記ロジック電源ドメインよりも大きい絶対値を有する高電圧を供給する複数の電圧乗算器と；

前記複数の電圧乗算器及び前記メモリ制御ロジックの第2出力に接続されるアレイ制御ロジックと；

前記アレイ制御ロジックに接続されるメモリアレイと

を備え、前記発振器制御回路は、前記ロジック電源ドメインと、前記高電圧の絶対値よりも低い値であるが前記ロジック電源ドメインよりも高い値を有するメモリ電源ドメインと

によって電源供給される、回路。

【請求項3】

前記発振器制御回路は：

前記メモリ制御ロジックの第1出力に接続される入力と、出力とを有する第1レベルシフタと；

前記低電圧インジケータ回路の出力に接続される入力と、出力とを有する第2レベルシフタと；

前記第1レベルシフタの出力に接続される入力と、前記第2レベルシフタの出力に接続される第2入力と、前記発振器の制御入力に接続される出力とを有する論理ゲートと

を含む、請求項2に記載の回路。

【請求項4】

前記アレイ制御ロジックは、前記メモリ制御ロジックの第2出力に応答して前記メモリアレイへの前記高電圧の印加を制御する手段を含み、前記メモリ制御ロジックの第2出力がマルチ信号である、請求項2に記載の回路。

【請求項5】

書き込み及び消去に高電圧を必要とするセル群により構成されるメモリアレイと；

ロジック電源ドメインによって電源供給され、読み出し動作、書き込み動作、及び消去動作の実行を指示する信号を供給するメモリ制御手段と；

前記ロジック電源ドメインが所定のレベルよりも低いことを通知する低電圧インジケータと；

少なくともメモリ電源ドメインによって電源供給され、出力を有する発振器と；

前記ロジック電源ドメインが前記所定のレベルより低いことを前記低電圧インジケータが示すとき前記発振器をディセーブルにし、前記ロジック電源ドメインが前記所定のレベル以上のとき前記メモリ制御手段により前記発振器を制御可能にする発振器制御手段であって、前記低電圧インジケータに接続された第1レベルシフタと、前記メモリ制御手段に接続された第2レベルシフタと、前記第1レベルシフタ、前記第2レベルシフタ、及び前記発振器に接続された論理ゲートとを含む発振器制御手段と；

前記発振器の出力に接続された複数の電圧乗算器であって、少なくとも前記メモリ電源ドメインによって電源供給され、前記メモリ電源ドメインよりも高い値を有する高電圧を供給する複数の電圧乗算器と；

前記複数の電圧乗算器及び前記メモリ制御手段に接続され、前記メモリ制御手段による実行の指示に従って書き込み及び消去を行う際に、前記高電圧を前記メモリアレイに印加するためのアレイ制御手段と

を備える回路。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、概して半導体に関し、特に半導体データ記憶素子に関する。

【背景技術】

【0002】

10

20

30

40

50

集積回路内に他のタイプの回路と共に埋め込まれる半導体メモリは通常、動作のために2つの異なる電源電圧を必要とする。第1電源電圧は、メモリの制御回路に電源を供給するために使用される。このような制御回路は、多くは論理ゲートで実現され、比較的低い電源電圧で駆動される。第2電源電圧は、メモリの書き込みや消去といったメモリ動作に必要な電源を供給するために使用される。

【発明の概要】

【発明が解決しようとする課題】

【0003】

特にフラッシュメモリなどのメモリにおけるこのような電圧は通常、論理回路に必要な電源よりもはるかに高い。このため、電源電圧が低下し、論理回路を駆動するために必要な臨界値を下回ってしまうと、誤った論理信号が生成される可能性がある。このように論理値に誤りがあると、通常チャージポンプまたは電圧乗算器によって生成される高電源電圧がメモリアレイのビットセルに誤って印加されるおそれがある。高電圧がメモリセルに誤って印加されると、メモリセルの電気的特性が変化する。その結果、変化した電気的特性によって、誤ったデータが生成され、それによって、動作の信頼性が損なわれることになる。

10

【図面の簡単な説明】

【0004】

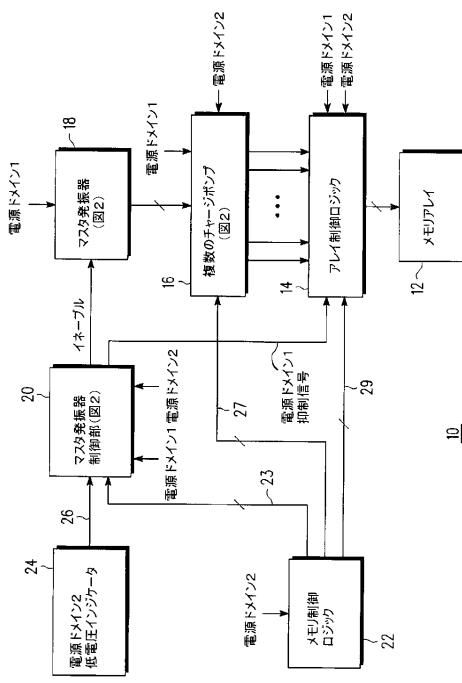

【図1】本発明による高電圧メモリ擾乱を防止するメモリを示すブロック図である。

【図2】図1に利用されるマスタ発振器、及び同発振器の制御部の1つの形態を示す部分模式図である。

20

【図3】本発明によるメモリ内の高電圧メモリ擾乱を防止する方法を示すフローチャートである。

【図4】図1のメモリに関連する種々の電圧信号を示すタイミング図である。

【発明を実施するための形態】

【0005】

本発明の一例を添付の図に示す。しかしながら、本発明は添付の図によって制限されない。図中、同様の参照記号は同様の構成要素を示している。図中の構成要素は、簡略化と分かり易さを目的として示されており、必ずしも寸法通りには描かれていない。

【0006】

30

図1は、電圧擾乱保護機構を有するメモリ10を示す。電圧擾乱保護は、メモリアレイの電気特性を不所望に変化させ得る高電圧がメモリアレイ12のメモリビットセルに意図せずに印加されることを防止する。メモリアレイ12は複数のメモリビットを有し、これらのメモリビットは、アレイ制御ロジック14により制御される。アレイ制御ロジック14は、2つの異なる電源電圧の電源下で動作する。第1電源電圧は、電源ドメイン1またはメモリ電源ドメインと表記される。電源ドメイン1は、メモリアレイ12内のメモリビットに対する書き込み及び消去を可能にする十分な大きさの電圧を生成するために、複数のチャージポンプによって使用される電源電圧である。第2電源電圧は電源ドメイン2と表記され、ロジック電源ドメインである。第2電源電圧は第1電源電圧よりも低く、かつ論理ゲート及び論理回路の駆動を可能にする少なくともトランジスタ動作電圧よりも高い値を有する。従って、第1電源電圧及び第2電源電圧のいずれも、メモリビットに対する書き込みまたは消去を行なうほどの十分な大きさの値ではない。アレイ制御ロジック14は、複数のチャージポンプ16から電源供給される。複数のチャージポンプの各々は、電圧乗算回路またはチャージポンプ回路として実現される。複数のチャージポンプ16は、電源ドメイン1及び電源ドメイン2の両方の電源電圧で動作する。複数のチャージポンプ16の入力は、单一のマスタ発振器18の出力に接続される。单一のマスタ発振器18は、全てのチャージポンプ16をクロッキングするために使用される共有の共通発振器である。单一のマスタ発振器18は、電源ドメイン1のメモリ電源電圧で動作し、マスタ発振器制御部20の出力に接続される入力を有する。マスタ発振器制御部20は、電源ドメイン1のメモリ電源電圧、及び電源ドメイン2のロジック電源電圧で動作する。マスタ発振

40

50

器制御部 20 の第 1 入力は、電源ドメイン 2 低電圧インジケータ 24 の出力に接続され、低電圧インジケータ (Low Voltage Indicator: LVI) 信号 26 を受信する。マスタ発振器制御部 20 の第 2 入力は、メモリ制御ロジック 22 の第 1 出力に接続されている。メモリ制御ロジック 22 は、電源ドメイン 2 のロジック電源電圧で動作する。メモリ制御ロジック 22 の第 2 出力は、複数のチャージポンプ 16 の制御入力に接続され、制御信号 27 を供給する。メモリ制御ロジック 22 の第 3 出力は、アレイ制御ロジック 14 の第 2 制御入力に接続され、制御信号 29 をアレイ制御ロジック 14 に供給することにより、メモリアレイ 12 との種々の相互作用を制御する。マスタ発振器制御部 20 の第 2 出力は、アレイ制御ロジック 14 の第 2 入力に接続される。

## 【0007】

10

動作状態において、メモリ 10 は、アレイ制御ロジック 14 による制御の下でデータを記憶するように機能する。図示の都合上、メモリアレイ 12 に至るデータパスは図示されないが、構造及び動作に関しては従来通りである。メモリ 10 は、ロジック電源ドメイン (電源ドメイン 2) を使用して図示の論理回路に対して、ロジックトランジスタの確実な切り替えを可能にする十分な高さの論理電圧レベルの電源供給を行なうように動作する。この電圧はプロセスによって変わり、現時点では、1 ボルト程度、またはそれよりも低い電圧である。これとは異なり、メモリ電源ドメイン (電源ドメイン 1) を使用して、書き込み動作または消去動作のような特定のメモリ動作に必要な電源を供給する。1 つの形態において、メモリアレイ 12 がフラッシュメモリとして実現されると仮定する。この形態では、電源ドメイン 1 を実現するために使用される電圧は通常、3 ボルト以上である。この電圧もプロセスによって変わり、将来では、更に小さくなる可能性がある。いずれにしても、電源ドメイン 1 電圧は、電源ドメイン 2 電圧よりもはるかに高い。

## 【0008】

20

メモリ 10 を携帯電子機器に用いる多くの用途では、携帯用バッテリを使用して電源ドメイン 1 電源電圧、及び電源ドメイン 2 電源電圧の両方の電源を供給する。メモリ 10 に関連する論理動作は、論理動作よりも高い電圧のメモリ動作よりもはるかに頻繁に使用されるので、電源ドメイン 2 電圧を電源供給するために使用されるバッテリは、電源ドメイン 1 に関して使用されるバッテリが切れる前に切れてしまう恐れがある。電源ドメイン 2 低電圧インジケータ 24 を使用して、電源ドメイン 2 電圧が、論理回路に確実に電源供給するために必要な所定の最小電圧値または最低電圧レベルを下回る時点を通知する。マスタ発振器制御部 20 への低電圧インジケータ信号 26 は、電源ドメイン 2 電圧が極めて低くなるときにアサートされる。低電圧インジケータ信号 26 に応答して、マスタ発振器制御部 20 は、単一のマスタ発振器 18 に既に供給されているイネーブル信号をアサートしなくなる。低電圧インジケータ信号 26 がアサートされない場合、メモリ制御ロジック 22 は、正しい電圧で動作しており、制御信号 23 をマスタ発振器制御部 20 に供給している。この状態では、メモリ 10 は、正常回路動作で機能しており、制御情報をマスタ発振器制御部 20 に供給して、単一のマスタ発振器 18 を正しく制御している。マスタ発振器 18 が今度は、クロック信号を正しいタイミングで生成して、電源ドメイン 1 信号を選択的に昇圧する複数のチャージポンプ 16 を作動させる。メモリ制御ロジック 22 は制御信号 27 を供給して、アレイ制御ロジック 14 との複数のチャージポンプ 16 の接続を制御する。複数のチャージポンプ 16 は電源ドメイン 2 を使用して、複数のチャージポンプ 16 内のロジックインターフェース回路に電源供給することにより、メモリ制御ロジック 22 が使用するロジック電源ドメインと複数のチャージポンプ 16 が使用するメモリ電源ドメインとのインターフェースを行なう。アレイ制御ロジック 14 は昇圧電圧を複数のチャージポンプ 16 から受信し、昇圧電源電圧がメモリアレイ 12 内の正しい位置に印加されるようにする。

## 【0009】

30

電源ドメイン 2 低電圧インジケータ 24 が、電源ドメイン 2 電圧が低くなり過ぎて、メモリ制御ロジック 22 内の論理回路、及びメモリ 10 の他の論理回路を確実に動作させることができないと判断する場合、低電圧インジケータ信号 26 がアサートされる。低電圧

40

50

インジケータ信号 26 がアサートされると、マスタ発振器制御部 20 が無効になる。その結果、マスタ発振器 18 へのイネーブル信号が、マスタ発振器制御部 20 によりアサートされなくなる。更に、マスタ発振器制御部 20 は、アレイ制御ロジック 14 への電源ドメイン 1 抑制信号をアサートする。別の形態では、イネーブル信号はまた、マスタ発振器 18 への電源供給を完全に停止するように機能し、更に、イネーブル信号によってメモリ 10 における電力を節約することができる。マスタ発振器 18 が再度有効になり、マスタ発振器に電源供給される場合、メモリ動作に関連する同期問題が生じなくなる。いずれの形態においても、マスタ発振器制御部 20 により供給されるイネーブル信号は、マスタ発振器 18 から出力されるクロック信号を制御するように機能する。電源ドメイン 1 抑制信号に応答して、アレイ制御ロジック 14 は、電源ドメイン 1 電源電圧が、メモリアレイ 12 10 内のビットセルのノードに供給されるのを阻止する。従って、マスタ発振器制御部 20 は、低電圧インジケータ信号がアサートされるときに複数の昇圧電圧が複数のチャージポンプ 16 から生成されることを阻止するように機能する。単一のマスタ発振器 18 を直接制御して複数のチャージポンプ電圧の生成を回避することにより、更なる電力の削減が達成される。

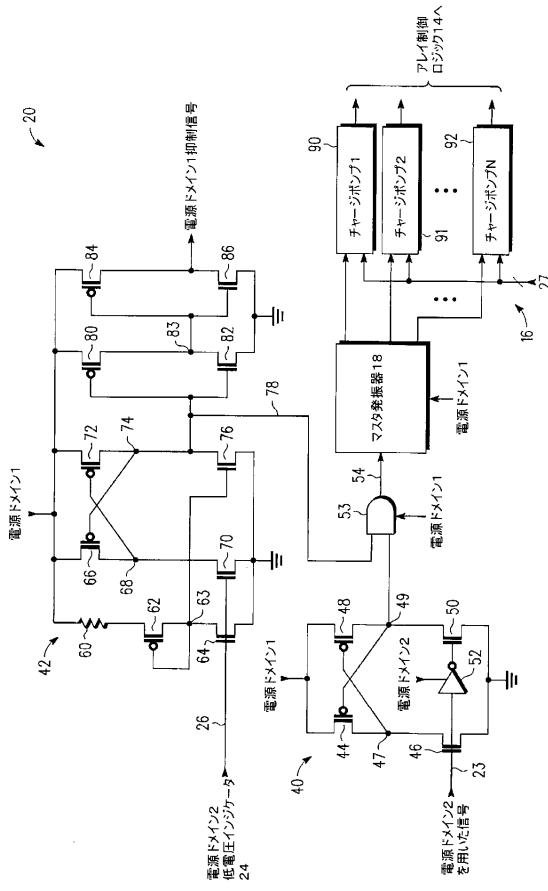

#### 【 0010 】

図 2 に示すのは、マスタ発振器 18 及び複数のチャージポンプと組み合わせたマスタ発振器制御部 20 の 1 つの形態である。マスタ発振器制御部 20 については、非常に多くの従来型発振器回路のいずれをも使用することができるので、詳細に説明することはしない。更に、特定の詳細は、図 2 のチャージポンプに関しては、非常に多くの従来型チャージポンプ回路のいずれをも使用することができるので提示していない。図示の形態では、マスタ発振器制御部 20 は、レベルシフタ回路 40 及びレベルシフタ回路 42 を有する。レベルシフタ回路 40 内には、電源ドメイン 1 (メモリ電源ドメイン) の電源電圧を入力する端子に接続されるソースを有する P チャネルトランジスタ 44 が設けられる。トランジスタ 44 のドレインはノード 47 に接続され、かつ N チャネルトランジスタ 46 のドレインに接続される。トランジスタ 46 のゲートは、電源ドメイン 2 を使用する図 1 の制御信号 23 に接続される。制御信号 23 は、電源ドメイン 2 の電源電圧が、動作を確実にするために十分高い場合に、マスタ発振器 18 をマスタ発振器制御部 20 を介して制御するために使用される制御信号である。制御信号 23 は更に、ロジック電源ドメインまたは電源ドメイン 2 で電源供給されるインバータ 52 の入力に接続される。インバータ 52 の出力は、N チャネルトランジスタ 50 のゲートに接続される。トランジスタ 46 及びトランジスタ 50 の各トランジスタのソースは、グランド基準を入力する端子に接続される。P チャネルトランジスタ 48 は、トランジスタ 44 のソースに接続されて電源ドメイン 1 電圧を入力するソースを有する。トランジスタ 48 のゲートはノード 47 に接続される。トランジスタ 44 のゲートはノード 49 に、かつトランジスタ 50 のドレインに接続される。レベルシフタ回路 40 は、第 1 及び第 2 電源ドメインの両方の電源ドメインで電源供給される。

#### 【 0011 】

レベルシフタ回路 42 は、電源ドメイン 1 電圧を入力する端子に接続される第 1 端子を有する抵抗 60 を有する。抵抗 60 の第 2 端子は P チャネルトランジスタ 62 のソースに接続される。トランジスタ 62 のゲートは、当該トランジスタのドレインにノード 63 で接続される。N チャネルトランジスタ 64 は、トランジスタ 62 のドレインにノード 63 で接続されるドレインを有する。トランジスタ 64 のゲートは、電源ドメイン 2 低電圧インジケータ 24 からの低電圧インジケータ信号 26 に接続される。P チャネルトランジスタ 66 は、電源ドメイン 1 電圧を入力する端子に接続されるソースを有する。トランジスタ 66 のドレインはノード 68 において、N チャネルトランジスタ 70 のドレインに接続される。トランジスタ 70 のゲートは、トランジスタ 64 のゲートに、かつ電源ドメイン 2 低電圧インジケータ 24 からの低電圧インジケータ信号 26 に接続される。トランジスタ 64 及びトランジスタ 70 の各トランジスタのソースは、グランド基準電圧端子に接続される。P チャネルトランジスタ 72 は、電源ドメイン 1 電圧を入力する端子に接続され 40 50

るソースを有する。トランジスタ 7 2 のゲートはノード 6 8 に接続される。トランジスタ 6 6 のゲートはノード 7 4 に接続され、このノード 7 4 は、トランジスタ 7 2 のドレインに接続される。N チャネルトランジスタ 7 6 のドレインはノード 7 4 に接続される。トランジスタ 7 6 のゲートはノード 6 3 に接続され、トランジスタ 7 6 のソースはグランド基準電圧端子に接続される。P チャネルトランジスタ 8 0 は、電源ドメイン 1 電圧を入力する端子に接続されるソースを有する。トランジスタ 8 0 のゲートは、N チャネルトランジスタ 8 2 のゲートにノード 7 4 で接続される。トランジスタ 8 0 のドレインはトランジスタ 8 2 のドレインにノード 8 3 で接続される。トランジスタ 8 2 のソースはグランド基準電圧端子に接続される。P チャネルトランジスタ 8 4 は、電源ドメイン 1 電圧を入力する端子に接続されるソースを有する。トランジスタ 8 4 のゲートは、N チャネルトランジスタ 8 6 のゲートにノード 8 3 で接続される。トランジスタ 8 4 のドレインはトランジスタ 8 6 のドレインに接続され、かつ電源ドメイン 1 抑制信号を供給する。トランジスタ 8 6 のソースはグランド基準電圧端子に接続される。

#### 【 0 0 1 2 】

AND ゲート 5 3 の第 1 入力はノード 4 9 に接続される。AND ゲート 5 3 の第 2 入力はノード 7 4 に接続される。AND ゲート 5 3 の出力 5 4 は、マスタ発振器 1 8 の入力に接続される。マスタ発振器 1 8 は、図 1 に示したように、電源ドメイン 1 で電源供給される。マスタ発振器 1 8 は複数の出力を有し、これらの出力はそれぞれ、複数のチャージポンプ 1 6 のうちの所定の 1 つのチャージポンプの入力に接続される。複数のチャージポンプ 1 6 は、第 1 チャージポンプ 9 0 と、第 2 チャージポンプ 9 1 と、N を整数とした場合の第 N チャージポンプ 9 2 のような追加チャージポンプと、を含む。チャージポンプ 9 0 ~ 9 2 の各チャージポンプは、アレイ制御ロジック 1 4 に接続されるそれぞれの出力を有する。

#### 【 0 0 1 3 】

動作状態では、レベルシフタ回路 4 0 は、電源ドメイン 2 で電源供給されながらデジタル信号を受信し、制御信号 2 3 と同じデジタル値（すなわち、論理状態）である値を有する出力ビットをノード 4 9 に伝送する。しかしながら、レベルシフタ回路 4 0 の出力の電圧レベルは、相対的に低い電源ドメイン 2 から、相対的に高い電源ドメイン 1 に変換される。レベルシフタ回路 4 2 内では、信号 7 8 はまた、電源ドメイン 2 低電圧インジケータ 2 4 と同じ論理値を有する。レベルシフタ回路 4 0 の場合と同じように、レベルシフタ回路 4 2 の出力の電圧レベルは、相対的に低い電源ドメイン 2 から相対的に高い電源ドメイン 1 に変換される。しかしながら、レベルシフタ回路 4 2 内の回路の全ては、電源ドメイン 1 で電源供給される。従って、レベルシフタ回路 4 2 の出力が正確になるのに対し、レベルシフタ回路 4 0 の出力は、電源ドメイン 2 に関連する電圧が低下して閾値レベルを下回る場合には正確ではなくなる可能性がある。レベルシフタ回路 4 0 の出力、及びレベルシフタ回路 4 2 の出力が共に有効にならない限り、相対的に高い電源ドメイン 1 電源電圧で電源供給される AND ゲート 5 3 によって、マスタ発振器 1 8 が有効になることはない。従って、レベルシフタ回路 4 2 は、低電圧インジケータ信号 2 6 がアサートされる場合にマスタ発振器が有効にならないことを保証するように機能する。

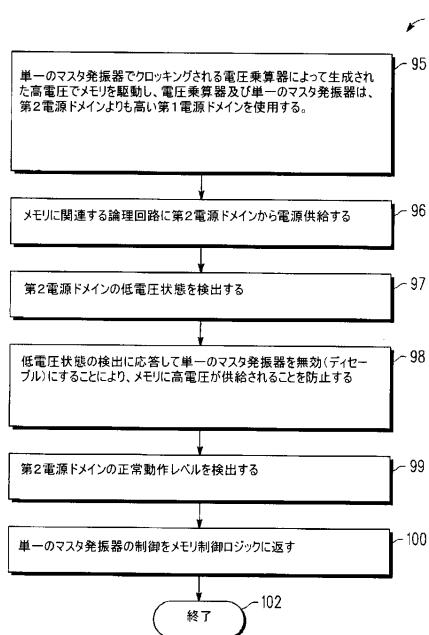

#### 【 0 0 1 4 】

図 3 に示すのは、高電圧メモリ擾乱を防止する方法 9 4 のフローチャートである。ステップ 9 5 では、メモリに高電圧で電源供給し、この高電圧は、単一のマスタ発振器によってクロッキングされる電圧乗算器により生成される。本明細書で「高電圧」という用語は、相対的な用語であり、論理機能を実行するために接続されるトランジスタに電源供給するために使用される電圧よりも高い値の電圧を意味する。このような高電圧は通常、FLASH メモリのようなメモリを動作させて書き込み動作、及び消去動作を行なうために必要とされる。電圧乗算器及び単一のマスタ発振器は、第 2 電源ドメインよりも電圧絶対値が大きい第 1 電源ドメインを使用する。ステップ 9 6 では、メモリに関連する論理回路に、第 2 電源ドメインで電源供給する。ステップ 9 7 では、第 2 電源ドメインの低電圧状態を検出する。この状態は、第 2 電源ドメイン電圧が低下して所定の閾値を下回る場合に発

10

20

30

40

50

生する。ステップ 9 8 では、単一のマスタ発振器 1 8 を、第 2 電源ドメインの低電圧状態の検出に応答して無効にする。マスタ発振器 1 8 を無効にすることにより、高電圧がメモリアレイ 1 2 に供給されるのを防止する。ステップ 9 9 では、第 2 電源ドメインが正常動作レベルに戻るのを検出する。この検出は、第 2 電源ドメイン電圧が、所定の閾値に所定期間に亘って達する、または所定の閾値を所定期間に亘って上回る場合に行なわれる。ステップ 1 0 0 では、単一のマスタ発振器 1 8 の制御を解除する、またはメモリ制御ロジック 2 2 に返す。ステップ 1 0 2 では、方法 9 4 は、メモリ制御ロジック 2 2 がメモリ 1 0 を制御して、電源ドメイン 2 が正確な動作、及び確実な動作を実現するために十分大きい絶対値を有することを示唆する場合に終了する。

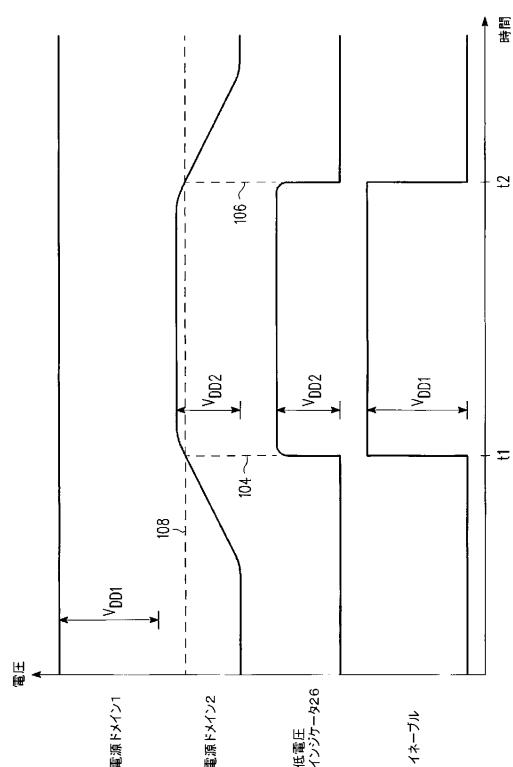

【 0 0 1 5 】

10

図 4 に示すのは、図 1 及び図 2 に関連して先に説明した種々の信号に関して電圧を時間に対してプロットした波形である。電源ドメイン 1 信号は、図示の時間全体に亘って一定値  $V_{DD1}$  を有するものとして示されている。電源ドメイン 2 信号は、ゼロと  $V_{DD2}$  との間で変化するものとして示されている。時刻  $t_1$  の前では、電源ドメイン 2 の電圧  $V_{DD2}$  は、所定の閾値 1 0 8 を下回っている。従って、負論理信号として示される低電圧インジケータ信号がアサートされる。低電圧状態が発生している場合、マスタ発振器 1 8 は、イネーブル信号が論理ゼロになることにより示されるように無効になる。時刻  $t_1$  では、電源ドメイン 2 の値が所定の値 1 0 8 を超え、電源ドメイン 2 値は、ほぼ時刻  $t_2$  まで  $V_{DD2}$  の電源電圧値になっている。この時間区間では、低電圧インジケータ信号 2 6 は、 $V_{DD2}$  の値を探る負論理インスタンス生成値により示されるようにアサートされない。動作を確実にするための十分高い電源ドメイン 2 電圧のこの時間区間では、マスタ発振器 1 8 は  $V_{DD1}$  信号によって有効になる。時刻  $t_2$  では、電源ドメイン 2 の電圧が所定の値 1 0 8 を満たさなくなり、低電圧インジケータ信号 2 6 が再度アサートされる。更に、マスタ発振器 1 8 のイネーブル信号はアサートされず、マスタ発振器 1 8 から複数のチャージポンプ 1 6 へのクロックは供給されない。これらの波形は、電源ドメイン 2 の電圧が変化して所定の値 1 0 8 を上回り、下回るときに動作が途切れないことを示している。電圧が変化して、メモリアレイ 1 2 のビットセルに書き込まれている電気特性を阻害することは許容されない。

【 0 0 1 6 】

20

以上の説明から、メモリに使用される複数の電源電圧のうちの 1 つの電源電圧が低くなり過ぎて確実な動作を確保できないことにより生じるビットセル擾乱を最小にする方法及びメモリ回路が提供される。不揮発性メモリビットセルが、より小さい寸法で実現され続けると、これらのビットセルは、ビットセルの記憶状態を劣化させる電圧擾乱またはメモリ擾乱の影響を受け易くなる。1 つの形態では、論理レベル信号が無効になる場合にアクティブになるパワーオンリセット信号が、機能を追加するために使用される。論理電圧レベルになっている電圧レベルを有するパワーオンリセット信号を、相対的に高い電圧レベルに変換し、イネーブル信号として使用してメモリシステムの複数のチャージポンプを無効にする。複数のチャージポンプは、複数のチャージポンプを制御するマスタ発振器または共通発振器を無効にすることにより無効になる。システムのマスタ発振器が機能していない場合、電源ドメイン 2 の電圧が高くなることにより、ビット擾乱がメモリアレイ内で生じないことを保証することができる。複数のチャージポンプの動作は、電源ドメイン 1 の電圧が低下して閾値を下回る場合に選択的に無効になるので、アレイ制御ロジックの回路内のドレイン電流が流れなくなり、これにより、メモリアレイに対するソフトホットキャリア注入 (hot carrier injection: H C I ) 摆乱の可能性を無くすことができる。ここに説明する方法により、電圧乗算器またはチャージポンプにより生成される内部生成電圧に対する不揮発性メモリにおけるビット擾乱を効果的に回避することができる。

【 0 0 1 7 】

40

1 つの形態において、メモリアレイを有する回路を動作させる方法が提供される。メモリ制御ロジックは、ロジック電源ドメインを使用して動作する。ロジック電源ドメインの電圧よりも高い電圧が、発振器の発振に応答して生成される。この高電圧を使用してメモ

50

リアレイが動作する。ロジック電源ドメインが少なくとも第1レベルにあるとき、発振器の動作がメモリ制御ロジックを用いて制御される。ロジック電源ドメインが第1レベルよりも低いとき、発振器が無効（ディセーブル）にされる。別の形態では、高電圧を生成することは更に、発振器の発振に応答する電圧乗算器を使用することを含む。別の形態では、高電圧を生成することは更に、この高電圧よりも低いメモリ電源ドメインを用いて電圧乗算器に電源を供給することを含む。更に別の形態では、高電圧を使用することは更に、アレイ制御ロジックを使用して高電圧をメモリアレイに印加することを含む。別の形態では、高電圧を使用することは更に、メモリ電源ドメインを用いて、アレイ制御ロジックに電源を供給することを含む。更に別の形態では、発振器を無効にすることは更に、ロジック電源ドメインが第1レベルよりも低下したときに低電圧インジケータ信号をアサートすることを含む。低電圧インジケータ信号がアサートされると発振器が無効にされる。別の形態では、発振器の動作を制御することは更に、メモリ制御ロジックを使用して、発振器制御回路への発振器イネーブル信号をアサートすることを含む。発振器制御回路の出力は、発振器を有効（イネーブル）にする第1論理状態で発振器に接続される。更に別の形態では、低電圧インジケータ信号をアサートすることは更に、発振器を無効にする第2論理状態で発振器に発振器制御回路の出力を供給するように発振器制御回路を動作させる論理状態で、低電圧インジケータ信号をアサートすることを含む。更に別の形態では、低電圧インジケータ信号をアサートすることは更に、低電圧インジケータ信号をレベルシフトすることを含む。レベルシフトされた低電圧インジケータ信号は論理ゲートに供給される。論理ゲートの出力は発振器に接続される。

10

## 【0018】

別の形態では、回路は、第1出力及び第2出力を有するロジック電源ドメインによって電源供給されるメモリ制御ロジックを含む。低電圧インジケータ回路は、出力を有するロジック電源ドメインに接続される。発振器制御回路は、低電圧インジケータ回路の出力に接続される第1入力と、メモリ制御ロジックの第1出力に接続される第2入力と、出力とを有する。発振器は、発振器制御回路の出力に接続される制御入力と、発振器出力とを有する。複数の電圧乗算器は、発振器の発振器出力に接続され、ロジック電源ドメインよりも高い絶対レベルを有する高電圧を供給する。アレイ制御ロジックは、複数の電圧乗算器及びメモリ制御ロジックの第2出力に接続される。メモリアレイは、アレイ制御ロジックに接続される。別の形態では、発振器制御回路は、ロジック電源ドメインより高いレベルであるが上記高電圧の絶対値よりも低いレベルを有するメモリ電源ドメインによって電源供給される。別の形態では、発振器制御回路は、メモリ制御ロジックの第1出力に接続される入力と、出力とを有する第1レベルシフタを含む。第2レベルシフタは、低電圧インジケータ回路の出力に接続される入力と、出力とを有する。論理ゲートは、第1レベルシフタの出力に接続される入力と、第2レベルシフタの出力に接続される第2入力と、発振器の制御入力に接続される出力とを有する。1つの形態では、第2レベルシフタは、低電圧インジケータ回路の出力に接続されるゲートと、グランド端子に接続されるソースと、ドレインとを有するトランジスタを含む。抵抗素子及びダイオード接続トランジスタは、トランジスタのドレインとメモリ電源ドメインとの間に直列に接続される。メモリ電源ドメインで電源供給されるレベルシフト回路は、低電圧インジケータ回路の出力に接続される第1入力と、第1トランジスタのドレインに接続される第2入力と、第2レベルシフタの出力としての出力とを有する。ロジック電源ドメインが所定の電圧レベルよりも低いとき、低電圧インジケータ回路は論理ローの出力を供給する。アレイ制御ロジックは、メモリ制御ロジックの第2出力に応答してメモリアレイに対する高電圧の印加を制御する回路を含み、ここでメモリ制御ロジックの第2出力はマルチ信号である。別の形態では、メモリアレイは、書き込み及び消去を行なうために高電圧を必要とする不揮発性メモリセルを含む。アレイ制御ロジックは、この高電圧を使用して書き込み及び消去を制御する。アレイ制御ロジックは、第2電源ドメイン及び第1電源ドメインを使用する。ロジック電源ドメインが所定の電圧レベルよりも低いとき、低電圧インジケータ回路は、発振器制御回路によって発振器を無効にする。

20

30

40

50

## 【0019】

別の形態では、書き込み及び消去を行なうために高電圧を必要とするメモリセルアレイを有する回路が提供される。メモリ制御回路は、ロジック電源ドメインから電源供給され、読み出し動作、書き込み動作、及び消去動作の実行を指示する信号を供給する。低電圧インジケータは、ロジック電源ドメインが所定の電圧レベルよりも低いことを通知する。発振器は、少なくともメモリ電源ドメインによって電源供給される。ロジック電源ドメインが所定のレベルよりも低いことを低電圧インジケータが通知すると、発振器制御回路は発振器を無効にし、ロジック電源ドメインが所定のレベル以上のとき、発振器制御回路は、メモリ制御回路によって発振器を制御可能にする。複数の電圧乗算器は、発振器の出力に接続されている。これら複数の電圧乗算器は、少なくともメモリ電源ドメインによって電源供給され、メモリ電源ドメインよりも高いレベルを有する高電圧を供給する。アレイ制御回路は、複数の電圧乗算器及びメモリ制御回路に接続されており、メモリ制御回路による実行の指示に従って書き込み及び消去を行う際に高電圧をメモリアレイに印加する。メモリ制御回路は、複数の電圧乗算器を制御する。1つの形態では、発振器制御回路は、低電圧インジケータに接続される第1レベルシフタを含む。第2レベルシフタは、メモリ制御回路に接続される。論理ゲートは、第1レベルシフタ、第2レベルシフタ、及び発振器に接続される。

10

## 【0020】

本発明を特定の導電型または電位極性に関して説明したが、導電型及び電位極性は逆でもよい。更に、上記の説明及び請求項で用いられている場合、「前方」「後方」「上部」「下部」「以上」「以下」「上方」「下方」等の用語は全て、表現上の目的で使用されており、必ずしも恒久的な相対位置を表わすために使用されていない。このように使用するこれらの用語は適切な状況の下では入れ替え可能であり、本明細書に記載された本発明の実施形態は、例えば例示の配置以外の他の配置でも、あるいは本明細書に記載された配置以外の配置でも動作可能である。本明細書において使用する「備える」「備えている」という用語、またはこれらの用語の他の全ての変形語は包括的な意味で適用されるものであり、一連の要素を備えるプロセス、方法、製品、または装置がこれらの要素のみを含むのではなく、明示的に列挙されていないもしくはそのようなプロセス、方法、製品、または装置に固有の他の要素も含むことができる。本明細書において使用する「1つの」という用語は、「1つ」または「1つ以上」として定義される。特に断らない限り、「第1の」「第2の」のような用語は、このような用語によって記述される要素群を任意に区別するために使用される。従って、これらの用語は、必ずしも要素群の時間的な優先度、または他の優先度を指すために使用されていない。

20

## 【0021】

本明細書において使用する「複数の」という用語は、「2つ」または「2つ以上」として定義される。本明細書において使用する「別の」という用語は、「少なくとも2番目以降の」として定義される。本明細書において使用する「含む」及び/又は「有する」という用語は、「備える」(すなわち、広義語)として定義される。本明細書において使用する「結合される」という用語は、「接続される」として定義されるが、必ずしも直接的ではなく、また必ずしも機械的にでもない。

30

## 【0022】

本発明を特定の実施形態を参照して説明したが、本発明の範囲から逸脱しない限り種々の変形及び変更が可能である。例えば、トランジスタ以外の他の半導体素子が形成されていてもよい。例えば、ダイオード及びフューズが搭載されていてもよい。また、本明細書において列挙される材料の他に種々の半導体材料を使用することができる。また、複数のメモリアレイが搭載される場合、各メモリアレイが、共通発振器によりクロッキングされる複数のチャージポンプにより制御されてもよい。更に、複数のチャージポンプのグループ分けは、各グループが单一の発振器またはマスタ発振器により制御されるように実行することができる。本明細書において特定の実施形態に関して説明したいずれの効果、利点、または問題解決法も、本発明に必須の、必要な、または基本的な特徴または要素である

40

50

と解釈されるべきではない。従って、本明細書及び図面は制限的な意味ではなく例示として捉えられるべきであり、あらゆる変更が、本発明の範囲に包含されるべきである。

【 図 1 】

【 図 2 】

【図3】

【図4】

---

フロントページの続き

(72)発明者 ワン、ヤンツォ

アメリカ合衆国 78733 テキサス州 オースティン マヤン ウェイ 1105

審査官 堀 拓也

(56)参考文献 特開平05-109291 (JP, A)

特開平11-096800 (JP, A)

特開平03-046198 (JP, A)

国際公開第2006/036443 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

G11C 16/02

G11C 16/06