(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4940965号

(P4940965)

(45) 発行日 平成24年5月30日(2012.5.30)

(24) 登録日 平成24年3月9日(2012.3.9)

(51) Int.Cl.

F 1

|                |              |                  |

|----------------|--------------|------------------|

| <b>G 0 1 D</b> | <b>5/245</b> | <b>(2006.01)</b> |

| <b>H 0 1 L</b> | <b>43/06</b> | <b>(2006.01)</b> |

| <b>H 0 1 L</b> | <b>43/08</b> | <b>(2006.01)</b> |

|        |       |   |

|--------|-------|---|

| GO 1 D | 5/245 | H |

| GO 1 D | 5/245 | R |

| HO 1 L | 43/06 | Z |

| HO 1 L | 43/08 | Z |

請求項の数 7 (全 14 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2007-17986 (P2007-17986)    |

| (22) 出願日  | 平成19年1月29日 (2007.1.29)        |

| (65) 公開番号 | 特開2008-185406 (P2008-185406A) |

| (43) 公開日  | 平成20年8月14日 (2008.8.14)        |

| 審査請求日     | 平成21年12月7日 (2009.12.7)        |

|           |                                          |

|-----------|------------------------------------------|

| (73) 特許権者 | 000004260<br>株式会社デンソー<br>愛知県刈谷市昭和町1丁目1番地 |

| (74) 代理人  | 100068755<br>弁理士 恩田 博宣                   |

| (74) 代理人  | 100105957<br>弁理士 恩田 誠                    |

| (72) 発明者  | 大平 聰<br>愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内        |

審査官 真岩 久恵

最終頁に続く

(54) 【発明の名称】回転センサ及び回転センサ装置

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板に作り込まれ、半導体基板の表面に平行な磁界を検出する縦型ホール素子と、前記縦型ホール素子を作り込んだ前記半導体基板上に形成され、半導体基板の表面に平行な磁界の強さにより抵抗値が変化する磁気抵抗素子と、を備え、前記縦型ホール素子の出力信号と前記磁気抵抗素子により得られる信号とを用いて被検出体の回転を検出する回転センサにおいて、

前記縦型ホール素子として前記被検出体の回転位置を検出する单一の縦型ホール素子を設け、前記磁気抵抗素子として前記被検出体の回転方向を検出する单一の磁気抵抗素子を設けた

ことを特徴とする回転センサ。

## 【請求項 2】

前記磁気抵抗素子は NiFe の薄膜よりなることを特徴とする請求項 1 に記載の回転センサ。

## 【請求項 3】

前記磁気抵抗素子は NiCo の薄膜よりなることを特徴とする請求項 1 に記載の回転センサ。

## 【請求項 4】

前記縦型ホール素子は、

第 1 導電型の半導体基板に形成した第 2 導電型のウェル領域内において当該第 2 導電型

のウェル領域よりも浅い第1導電型のウェル領域が前記第2導電型のウェル領域を分割するように形成され、前記第2導電型のウェル領域の表層部において前記第1導電型のウェル領域を挟んで電流供給対を構成するコンタクト用の第2導電型の不純物拡散領域が形成されるとともに電圧出力対を構成するコンタクト用の第2導電型の不純物拡散領域が形成されてなる

ことを特徴とする請求項1～3のいずれか1項に記載の回転センサ。

【請求項5】

前記半導体基板には周辺回路が形成されていることを特徴とする請求項1～4のいずれか1項に記載の回転センサ。

【請求項6】

被検出体としてのマグネットロータは有底円筒状をなすロータボディを有しており、前記ロータボディの内面にはS極永久磁石とN極永久磁石とが対向して配置されているとともに、前記ロータボディの内部における前記S極永久磁石と前記N極永久磁石とが対向する部位には請求項1～5のいずれか一項に記載の回転センサが配置されている

回転センサ装置。

10

【請求項7】

被検出体としての磁性体からなるギアに対し、その外周側の近傍にセンサチップが配置されるとともに、さらにその外周側には永久磁石からなるバイアス磁石が配置され、前記センサチップに請求項1～5のいずれか一項に記載の回転センサが作り込まれている

回転センサ装置。

20

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、回転センサ及び回転センサ装置に関するものである。

【背景技術】

【0002】

回転センサとして磁気抵抗素子を複数用いたものが知られている（特許文献1，2参照）。特許文献1においては2つの磁気抵抗素子ブリッジをバイアス磁界の磁気的中心に対し対称に配置する技術が開示されている。特許文献2においては2つの磁気抵抗素子を被検出体であるギヤに対し並設して2つの磁気抵抗素子から出力される位相差をもった信号（パルス信号）の立上りエッジによりギヤの回転方向を検知する技術が開示されている。

30

【特許文献1】特開2001-153683号公報

【特許文献2】特開平10-332725号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

近年、センサの小型・高精度化の要求が増している。特に、回転センサにおいて小型化、360°検出、0.1%FS等の厳しい要求がX-by-Wireの進展とともに増えている。

【0004】

40

本発明は、このような背景の下になされたものであり、その目的は、小型化に優れた回転センサ及び回転センサ装置を提供することにある。

【課題を解決するための手段】

【0005】

上記の課題を解決するために、請求項1に記載の発明では、半導体基板に作り込まれ、半導体基板の表面に平行な磁界を検出する縦型ホール素子と、前記縦型ホール素子を作り込んだ前記半導体基板上に形成され、半導体基板の表面に平行な磁界の強さにより抵抗値が変化する磁気抵抗素子と、を備え、前記縦型ホール素子の出力信号と前記磁気抵抗素子により得られる信号とを用いて被検出体の回転を検出する回転センサにおいて、前記縦型ホール素子として前記被検出体の回転位置を検出する単一の縦型ホール素子を設け、前記

50

磁気抵抗素子として前記被検出体の回転方向を検出する单一の磁気抵抗素子を設けたことを要旨とする。

【0006】

請求項1に記載の発明によれば、磁気抵抗素子に比べて小さな縦型ホール素子を用いることにより小型化に優れた回転センサを提供することができる。

請求項2に記載のように、請求項1に記載の回転センサにおいて、前記磁気抵抗素子はNiFeの薄膜よりなるとよい。また、請求項3に記載のように、請求項1に記載の回転センサにおいて、前記磁気抵抗素子はNiCoの薄膜よりなるとよい。

【0009】

請求項4に記載のように、請求項1～3のいずれか1項に記載の回転センサにおいて、前記縦型ホール素子は、第1導電型の半導体基板に形成した第2導電型のウェル領域内において当該第2導電型のウェル領域よりも浅い第1導電型のウェル領域が前記第2導電型のウェル領域を分割するように形成され、前記第2導電型のウェル領域の表層部において前記第1導電型のウェル領域を挟んで電流供給対を構成するコンタクト用の第2導電型の不純物拡散領域が形成されるとともに電圧出力対を構成するコンタクト用の第2導電型の不純物拡散領域が形成されてなると、ウェル領域を用いることによりコスト的に有利な構成とすることができます。

請求項5に記載の発明では、請求項1～4のいずれか1項に記載の回転センサにおいて、前記半導体基板には周辺回路が形成されていることを要旨とする。

請求項6に記載の発明では、回転センサ装置として、被検出体としてのマグネットロータは有底円筒状をなすロータボディを有しており、前記ロータボディの内面にはS極永久磁石とN極永久磁石とが対向して配置されるとともに、前記ロータボディの内部における前記S極永久磁石と前記N極永久磁石とが対向する部位には請求項1～5のいずれか一項に記載の回転センサが配置されていることを要旨とする。

請求項7に記載の発明では、回転センサ装置として、被検出体としての磁性体からなるギアに対し、その外周側の近傍にセンサチップが配置されるとともに、さらにその外周側には永久磁石からなるバイアス磁石が配置され、前記センサチップに請求項1～5のいずれか一項に記載の回転センサが作り込まれていることを要旨とする。

【発明を実施するための最良の形態】

【0010】

(第1の実施形態)

以下、本発明を具体化した第1の実施形態を図面に従って説明する。

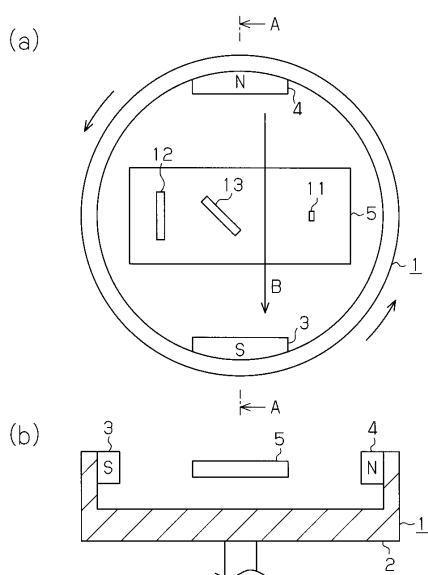

図1には本実施形態の回転センサの全体図を示す。図1(a)は回転センサの平面図であり、図1(b)は図(a)でのA-A線での断面図である。

【0011】

図1に示すように、被検出体としてマグネットロータ1を用いている。マグネットロータ1はロータボディ2を有し、ロータボディ2は有底円筒状をなしている。有底円筒状のロータボディ2の内面にはS極永久磁石3とN極永久磁石4とが対向して配置されている。有底円筒状のロータボディ2の内部におけるS極永久磁石3とN極永久磁石4とが対向する部位にはセンサチップ5が永久磁石3,4と離間して配置されている。永久磁石3,4によりセンサチップ5に磁界が印加される。

【0012】

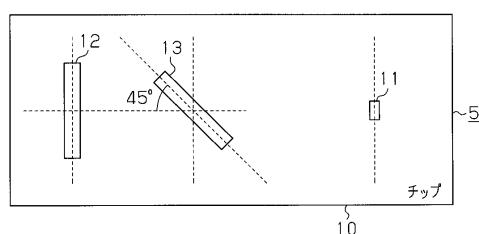

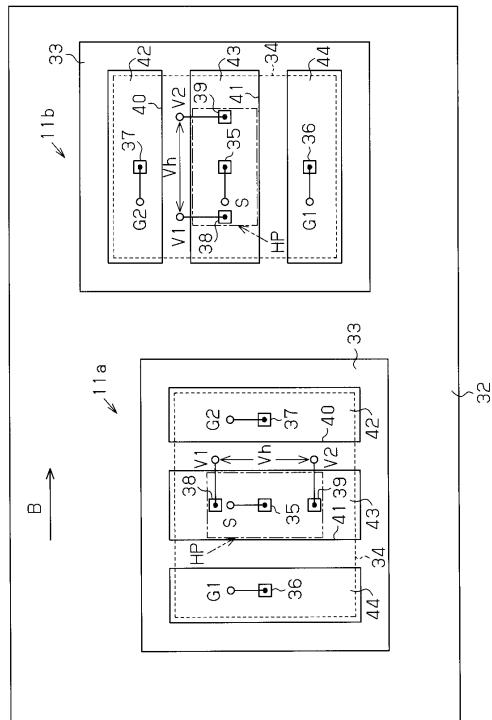

図2には、センサチップ5の詳細を示す。

図2において、半導体基板10に縦型ホール素子11が作り込まれている。また、半導体基板10上に磁気抵抗素子12,13が形成されている。磁気抵抗素子12,13はNiFeの薄膜よりなる。このように、同一基板(同一チップ)に2つの磁気抵抗素子12,13と縦型ホール素子11が並べて配置されている。

【0013】

縦型ホール素子11は、感磁面(ホール電圧が一番大きくなるホールプレートの面の方向、または磁界の入射方向に対し垂直にホールプレートが配置される方向)が磁気抵抗素

10

20

30

40

50

子 1 2 の長手方向（磁界に対して N i F e では抵抗値が一番低くなる方向）に合わせて配置されている。このときの磁界はセンサチップ 5 の表面に平行な磁界である。このように、縦型ホール素子 1 1 は半導体基板 1 0 の表面に平行な磁界を検出することができるようになっている。また、磁気抵抗素子 1 2 , 1 3 は半導体基板 1 0 の表面に平行な磁界の強さにより抵抗値が変化する。そして、各磁気抵抗素子 1 2 , 1 3 から、抵抗値に応じたレベルの信号が出力される。磁気抵抗素子 1 2 , 1 3 は帯状をなし、第 1 の磁気抵抗素子 1 2 に対し第 2 の磁気抵抗素子 1 3 はその延設方向が 4 5 ° 傾かせて配置されている。これにより、一方の磁気抵抗素子 1 3 は、他方の磁気抵抗素子 1 2 に対して、マグネットロータ 1 の回転に伴う抵抗値変化に 4 5 ° の位相差をもつ。

## 【 0 0 1 4 】

10

なお、隣り合う磁気抵抗素子 1 2 , 1 3 は、センサチップ 5 内でも、できるだけ近いところに配置した方がよい。また、同一チップ内に周辺回路（演算や補正などが可能な回路）を集積化することも可能である。

## 【 0 0 1 5 】

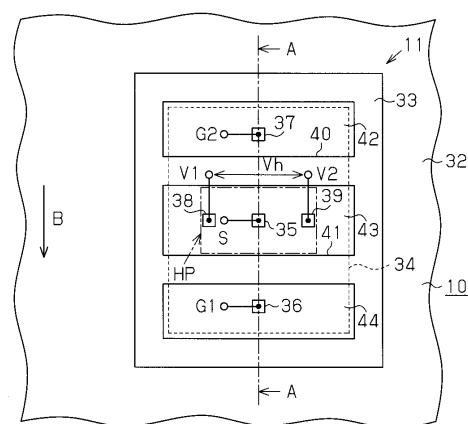

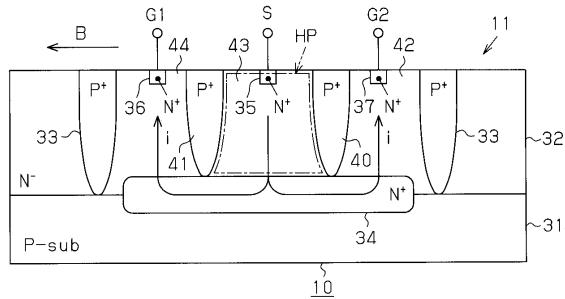

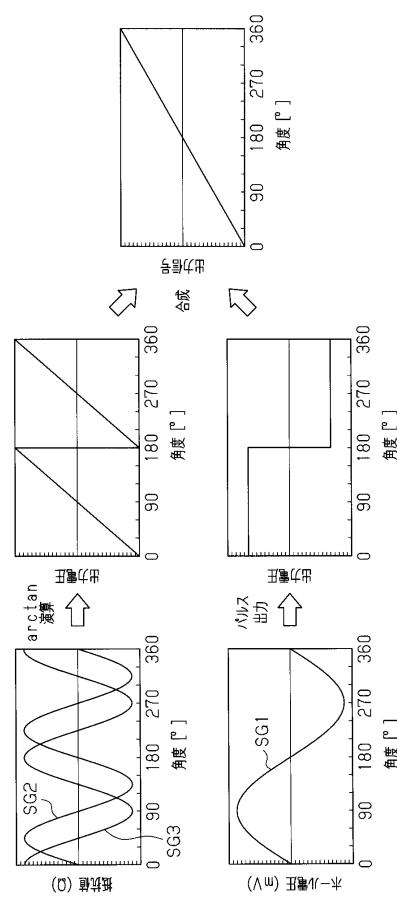

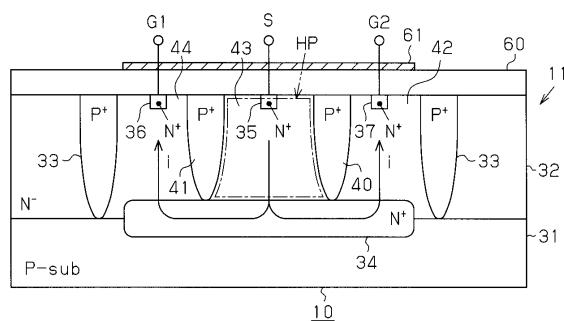

図 3 , 4 には、センサチップ 5 に形成した縦型ホール素子 1 1 の具体的構成を示す。

図 3 はホール素子 1 1 の平面構造を模式的に示す平面図、図 4 は図 3 の A - A 線に沿った断面図である。

## 【 0 0 1 6 】

20

図 4 に示すように、P 型シリコン基板 3 1 の上に N 型シリコン層 3 2 がエピタキシャル成長法により形成されている。P 型シリコン基板 3 1 と N 型シリコン層 3 2 により半導体基板が構成されている。また、N 型シリコン層 3 2 において素子分離用の P 型不純物拡散領域 3 3 が、その平面構造として図 3 に示すように、四角環状に、かつ、縦断面構造として図 4 に示すように P 型シリコン基板 3 1 に達するように形成されている。N 型シリコン層 3 2 において P 型不純物拡散領域 3 3 にて囲まれた領域がホール素子形成領域となっている。このホール素子形成領域において N 型の埋込層 3 4 が形成されている。

## 【 0 0 1 7 】

ホール素子形成領域の N 型シリコン層 3 2 の表層部には、N<sup>+</sup> コンタクト領域 3 5 , 3 6 , 3 7 , 3 8 , 3 9 が形成されている。これらコンタクト領域 3 5 , 3 6 , 3 7 , 3 8 , 3 9 には、図示しない配線を介して、それぞれ端子 S , G 1 , G 2 , V 1 , V 2 と電気的に接続されている。コンタクト領域 3 6 および 3 7 は、それぞれコンタクト領域 3 5 と対をなし、電流供給対が構成されている。コンタクト領域 3 8 および 3 9 により、電圧出力対が構成されている。

30

## 【 0 0 1 8 】

図 4 に示すように、N 型シリコン層 3 2 において P 型不純物拡散領域 4 0 , 4 1 が、その平面構造として図 3 に示すように、ホール素子形成領域を 3 つの領域 4 2 , 4 3 , 4 4 に分割するように形成され、かつ、縦断面構造として図 4 に示すように N 型埋込層 3 4 に達するように形成されている。そして、領域 4 3 において、コンタクト領域 3 5 , 3 8 , 3 9 が一直線上に配置されている。また、領域 4 2 のコンタクト領域 3 7 と領域 4 3 のコンタクト領域 3 5 と領域 4 4 のコンタクト領域 3 6 とが一直線上に配置されている。ここで、コンタクト領域 3 5 , 3 8 , 3 9 が位置する直線とコンタクト領域 3 7 , 3 5 , 3 6 が位置する直線とは直交している。

40

## 【 0 0 1 9 】

領域 4 3 においてコンタクト領域 3 8 および 3 9 にて挟まれる領域が磁気検出部（ホールプレート）H P となり、ここに印加される磁界に対応するホール電圧信号を生じさせることになる。

## 【 0 0 2 0 】

端子 S から端子 G 1 へ、また端子 S から端子 G 2 へそれぞれ一定の駆動電流 i を流すと、その電流 i は、基板表面に形成されたコンタクト領域 3 5 から下方に向かい、磁気検出部 H P 、埋込層 3 4 、さらに埋込層 3 4 内を横方向に進み、コンタクト領域 3 6 , 3 7 の下方位置から上方に向かい、コンタクト領域 3 6 , 3 7 へとそれぞれ流れれる。このとき、

50

磁気検出部HPには、基板表面(チップ表面)に垂直な成分を含む電流*i*が流れるため、この駆動電流を流した状態において、基板表面(チップ表面)に平行な成分を含む磁界(例えば図3,4中に矢印Bで示される磁界)が磁気検出部HPに印加されると、ホール効果によって端子V1と端子V2との間にその磁界に対応するホール電圧V<sub>h</sub>が発生し、端子V1, V2を通じてその発生したホール電圧信号を検出することで、検出対象とする磁界成分(基板の表面に平行な磁界成分)が求められる。

#### 【0021】

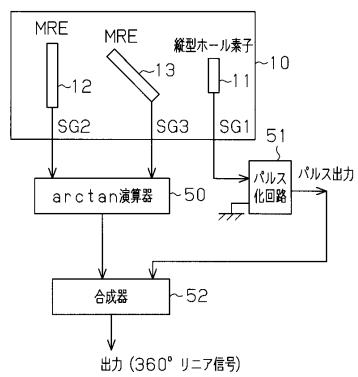

次に、回転センサの電気的構成を、図5に基づいて説明する。

図5に示すように、縦型ホール素子11、磁気抵抗素子12, 13に対する周辺回路としてarctan演算器50とパルス化回路51と合成器52が設けられている。arctan演算器50において磁気抵抗素子12, 13により得られる信号(抵抗値に応じたレベルの信号)SG2, SG3に対しarctan演算が行われる。縦型ホール素子11にはパルス化回路51が接続されている。パルス化回路51において縦型ホール素子11の出力信号SG1がパルス化された信号に変換される。arctan演算器50とパルス化回路51は合成器52に接続されている。合成器52において、arctan演算器50の出力信号とパルス化回路51の出力信号とが合成される。この合成器52の出力信号は360°リニア信号となっている。

#### 【0022】

次に、回転センサの作用について説明する。

図6は、磁気抵抗素子12, 13により得られる信号SG2, SG3およびホール素子11の出力信号SG1から、リニアな出力を得るために処理内容を説明するための波形図である。

#### 【0023】

図6に示すように、2つの磁気抵抗素子12, 13により得られる信号SG2, SG3は、角度に対して抵抗値が変化することによりsin、cosの曲線となる。つまり、一方の出力信号SG2と他方の出力信号SG3とは45°位相差をもつ。

#### 【0024】

また、磁気抵抗素子12, 13の抵抗値は永久磁石3, 4のN極、S極に対する判別ができるない(磁界の強さによって抵抗値が変わる)。そのため、図1のマグネットロータ1の回転に伴い、磁界を印加させている磁石3, 4が回転すると、図6のように、sin、cosの曲線は、0~360°回転する間に2回の周期で出力される。

#### 【0025】

一方、ホール素子11は、永久磁石3, 4のN極、S極の判別ができる素子である。そのため、ホール素子11の出力信号SG1は、0~360°の回転に対して1回の周期で出力される。

#### 【0026】

磁気抵抗素子12, 13により得られる信号SG2, SG3は図5のarctan演算器50において、arctanの演算が行われる。これにより、図6に示すように、出力がつなぎ合わされて180°周期で直線的にレベルが変わることで得られる。

#### 【0027】

また、ホール素子11の出力信号SG1が図5のパルス化回路51においてパルス信号に変換されて出力される。これにより、図6に示すように、180°周期でH(ハイ), L(ロー)のレベルが変わる出力が得られる。

#### 【0028】

図5の合成器52において、磁気抵抗素子12, 13により得られる信号SG2, SG3についてのarctanの演算後の信号と、ホール素子11の出力信号SG1についてのパルス出力後の信号が合成されて、つなぎ合わされる。これにより、図6に示すように、0~360°のリニア出力が得られる。つまり、ホール素子11の出力信号SG1がプラスのときの磁気抵抗素子により得られる信号SG2, SG3と、ホール素子11の出力信号SG1がマイナスのときの磁気抵抗素子により得られる信号SG2, SG3とが区別

10

20

30

40

50

できるため、得られる出力をさらに合成し、つなぎ合わせることで、0～360°のリニア出力を得ることができる。

#### 【0029】

以上のように、ホール素子11と磁気抵抗素子12, 13とを磁界の感度で比較すると磁気抵抗素子12, 13の方が大きいため、磁気抵抗素子12, 13により得られる信号をリニア出力の信号として利用することにより、高精度なセンサが構成できる。また、永久磁石の強度（磁界の大きさ）が小さいものでも使えるため、永久磁石のコストを下げることができる。一方、素子サイズに関して、磁気抵抗素子の寸法は1mm程度であり、ホール素子の縦横寸法は100μm程度あり、素子サイズが1/10程度に小さく、ホール素子11を、パルス出力を得る素子として利用する。これによりチップ面積を小さく構成でき、小型化を図ることができる。このようにして、小型・高精度化に優れた回転センサを提供することができる。10

#### 【0030】

詳しく説明する。

360°の範囲を検出すべく図7のようにした場合において、縦型ホール素子11a, 11bを90°位相差をもつように基板上にレイアウトし、得られる2つの信号をarc tanの演算をすることで、リニアな360°の出力を得ることができるセンサを1チップ上に構成することができる。しかし、この方法ではホール素子11a, 11bの感度が小さいために、得られる信号成分が小さい。すると、ノイズなどの影響によりセンサの精度が悪くなる。これに対し本実施形態では、磁気抵抗素子を用いることにより感度を大きくでき、得られる信号成分を大きくでき、ノイズなどによるセンサの精度の悪化を回避することができる。20

#### 【0031】

また、この信号成分を強めるために、磁界の強い磁石を用いる方法がある。しかし、磁界の強い磁石を用いることで、磁石のコストがアップしてしまう。これに対し本実施形態では、磁気抵抗素子を用いることにより信号成分を大きくでき、磁界が強い磁石を用いなくてよい。

#### 【0032】

また、ホール素子は一般的に使われている素子は横型ホール素子であるために、感磁面がチップ表面に対して垂直な方向であった（チップ表面に垂直な磁場に対する回転を検出するために使われている）。よって、磁界を検出する方向が磁気抵抗素子と90°ずれているために、同一チップに配置しても、所望の出力は得られない。これに対し本実施形態では、縦型ホール素子を用いることで磁界の検出方向を一致させることができる。30

#### 【0033】

上記実施形態によれば、以下のような効果を得ることができる。

(1) 回転センサの構成として、半導体基板10に作り込まれ、半導体基板10の表面に平行な磁界を検出する縦型ホール素子11と、縦型ホール素子11を作り込んだ半導体基板10上に形成され、半導体基板10の表面に平行な磁界の強さにより抵抗値が変化する磁気抵抗素子12, 13と、を備え、縦型ホール素子11の出力信号SG1と磁気抵抗素子12, 13により得られる信号SG2, SG3を用いて被検出体としてのマグネットロータ1の回転（回転位置）を検出するようにした。よって、1方向からの磁界に対してそれぞれの素子にて同時に検出することとなり、磁気抵抗素子に比べて小さな縦型ホール素子を用いることにより小型化に優れた回転センサを提供することができる。40

#### 【0034】

(2) 従来、磁気抵抗素子は磁界の強度のみを判別し、N極、S極の判別ができない素子であるために、回転に対し180°の周期で出力されるという特徴があり、そのため、45°の位相差をもつように配置した磁気抵抗素子で得られる出力をarc tanの演算をすることによりリニア出力に変換した場合、最大0～180°の範囲でしか角度の検出ができなかった。これに対し本実施形態においては、磁気抵抗素子は、マグネットロータ50

1の回転に伴う抵抗値変化に位相差をもつ第1および第2の磁気抵抗素子12, 13からなり、縦型ホール素子11の出力信号SG1と磁気抵抗素子12, 13により得られる信号SG2, SG3を用いて被検出体としてのマグネットロータ1の回転を検出する手段として、第1の磁気抵抗素子12により得られる信号SG2と第2の磁気抵抗素子13により得られる信号SG3をarctanの演算をするarctan演算手段としてのarctan演算器50と、縦型ホール素子11の出力信号SG1をパルス化するパルス化手段としてのパルス化回路51と、arctan演算器50によるarctanの演算をして得た信号と、パルス化回路51による縦型ホール素子11の出力信号SG1をパルス化した信号を合成して0~360°の角度においてリニアな出力を得る合成手段としての合成器52と、を備える。よって、簡単な構成にて0~360°の角度においてリニアな出力を得ることができる。10

#### 【0035】

(3) 磁気抵抗素子12, 13はNiFeの薄膜よりなるので、微弱な磁界を検知することができる。

なお、チップ5(基板10)の材料はシリコン以外にも化合物半導体(GaAs, InAs, InSb)でもよい。

#### 【0036】

また、ホール素子11は基板の中に拡散層として構成し、磁気抵抗素子12, 13は薄膜のため基板上に構成することができるため、図8に示すように、磁気抵抗素子61の下にホール素子11を重ねて配置してもよい。なお、図8において符号60はシリコン層32と磁気抵抗素子61とを絶縁分離するためのシリコン酸化膜等の絶縁膜である。このように、半導体基板10において磁気抵抗素子61の下に縦型ホール素子11を重ねて配置すると、より小型化することができる。20

#### 【0037】

また、ホール素子11のパルス出力の数(図5のパルス化回路51からのパルス数)をカウントすれば、多回転の(360°以上の)検出が可能である。

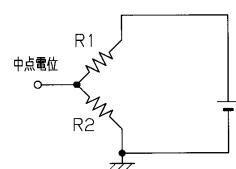

また、磁気抵抗素子12, 13の部分はゲージで構成してもよい。つまり、磁気抵抗値を読むのではなく、図9に示すように、磁気抵抗素子12, 13(図9での抵抗R1, R2)を直列に接続し、その中点電位を取り出すようにしてもよい。

#### (第2の実施形態)

次に、第2の実施形態を、第1の実施形態との相違点を中心に説明する。

#### 【0038】

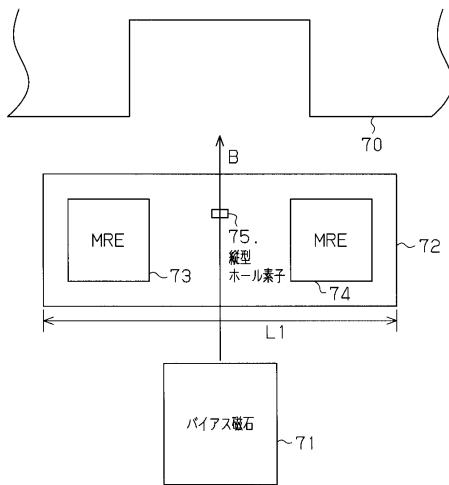

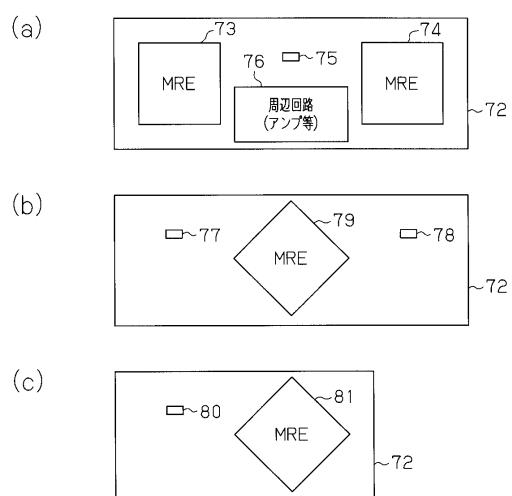

図10には、本実施形態における回転センサの平面図を示す。

図10において、被検出体としてのギヤ70に対し、その外周側の近傍にチップ72が配置されるとともに、さらにその外周側にはバイアス磁石(永久磁石)71が配置されている。チップ72においては左右方向の中央部に縦型ホール素子75が配置され、その両側に磁気抵抗素子73, 74が配置されている。縦型ホール素子75は、図3, 4で示した構造をなし、磁気抵抗素子73, 74に対して位相差をもつように配置されている。このようにして、チップ72(同一基板上)に、2つの磁気抵抗素子73, 74と、縦型ホール素子75が配置されている。即ち、縦型ホール素子75が半導体基板(チップ72)に作り込まれ、半導体基板(チップ72)の表面に平行な磁界を検出し、また、半導体基板(チップ72)上に磁気抵抗素子73, 74が形成され、半導体基板(チップ72)の表面に平行な磁界の強さにより抵抗値が変化する。40

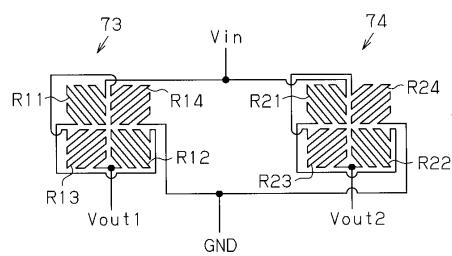

#### 【0039】

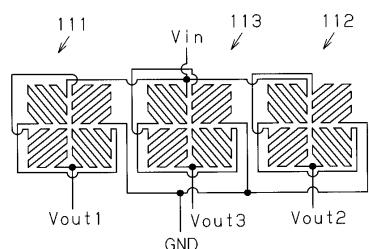

図11には2つの磁気抵抗素子73, 74の結線状態を示す。図11において、磁気抵抗素子73はフルブリッジ回路が組まれるとともに磁気抵抗素子74もフルブリッジ回路が組まれている。つまり、磁気抵抗素子73の構成として、電源電圧Vinとグランド(GND)間にいて4つの抵抗R11, R12, R13, R14が直列に接続され、この直列回路での抵抗R12, R13間の電位(中間電位)が出力電位Vout1となっている。同様に、磁気抵抗素子74の構成として、電源電圧Vinとグランド(GND)間に50

おいて4つの抵抗R21, R22, R23, R24が直列に接続され、この直列回路での抵抗R22, R23間の電位(中間電位)が出力電位Vout2となっている。

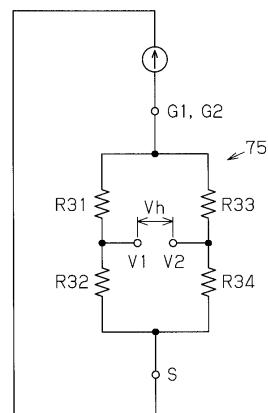

#### 【0040】

図3, 4で示した縦型ホール素子75の等価回路を図12に示す。図12において、ホール素子は抵抗ブリッジとして近似できる。つまり、2つの抵抗R31, R32が直列に接続されるとともに、2つの抵抗R33, R34が直列に接続され、両直列回路における中間電位の差がホール電圧(出力電位)Vhとなる。

#### 【0041】

そして、磁気抵抗素子73, 74にて得られる信号よりギヤ70の回転位置が検出される。また、縦型ホール素子75の出力信号と、いずれかの磁気抵抗素子73, 74にて得られる信号により、ギヤ70の正・逆の回転方向が検出される。つまり、縦型ホール素子75と、磁気抵抗素子73, 74との位相差を利用して、磁気抵抗素子73, 74により得られる信号と縦型ホール素子75の出力信号におけるパルス波形の立ち上がりの違いを利用してギヤ70の正・逆の回転方向が検出される。10

#### 【0042】

詳しくは、縦型ホール素子75の出力信号の2値化後の信号をA相信号とし、磁気抵抗素子73(又は磁気抵抗素子74)の出力信号の2値化後の信号をB相信号としたときにおいて、A相信号の立上りエッジにおけるB相信号のレベルを判定する。A相信号の立上りエッジにおけるB相信号のレベルがHレベルならば正回転であると判定し、また、A相信号の立上りエッジにおけるB相信号のレベルがLレベルならば逆回転であると判定する20。

#### 【0043】

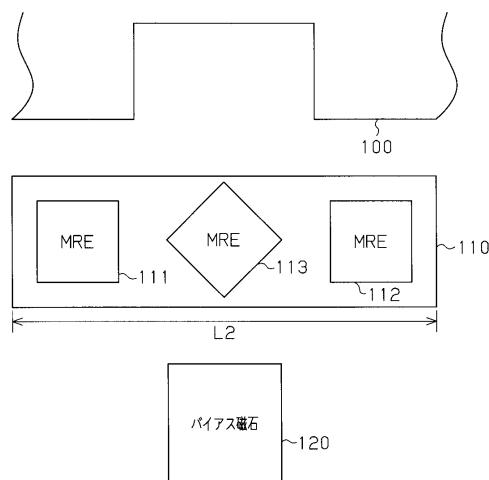

このようにして、縦型ホール素子75を回転方向検出用の素子として用いている。これにより、チップサイズを小さくすることができる。具体的には、図13でのチップ110と図10でのチップ72を比較したとき、横方向のサイズは、図13の寸法L2に比べて図10の寸法L1を小さくすることができる( $L_1 < L_2$ )。

#### 【0044】

以下、図13, 14の場合と、本実施形態とを比較して、詳しく説明する。

図13に示すように、ギヤ100に対しチップ110が離間して配置されるとともにチップ110の背面側にバイアス磁石(永久磁石)120が配置され、チップ110において磁気抵抗素子111, 112, 113が左右方向に並設されている。左右の磁気抵抗素子111, 112に対し中央の磁気抵抗素子113が位相差をもつように配置されている。また、各磁気抵抗素子111, 112, 113での結線として、図14に示すようにブリッジ回路が組まれている。そして、チップ110において両サイドに配した磁気抵抗素子111, 112でギヤ100の回転位置を検出する。また、チップ110において中央部に配した磁気抵抗素子113を用いてギヤ100の正・逆の回転方向を検出する。この際、位相差を利用して中央の磁気抵抗素子113と両サイドの磁気抵抗素子111, 112とのパルスの波形の立ち上がりの違いを利用して正逆の回転方向を検出することができる。しかし、この磁気抵抗素子111, 112, 113でブリッジを構成した場合、ホール素子に比べて検出素子が大きくなり(チップサイズが大きくなり)、コストがアップしてしまう。3040

#### 【0045】

これに対し、図10の本実施形態では回転方向検出用の素子として縦型ホール素子75を用いることによりチップサイズを小さくすることができる。つまり、図13の回転方向検出用の磁気抵抗素子113を縦型ホール素子75に置き換えることによりチップサイズを小さくすることができる。

#### 【0046】

図10に代わりに、図15(a)に示すように、空いたスペースなどに周辺回路76を集積化することも可能であり、この場合、センサシステム全体のコストダウンにもつながる。逆に、図13における位置検出用の磁気抵抗素子111, 112を、図15(b)に50

示すように縦型ホール素子 77, 78 に置き換えて、回転方向の検出のみを磁気抵抗素子 79 で行うことも可能である。このようにすることでも、チップサイズを小さくすることができます。

#### 【0047】

また、縦型ホール素子は、等価回路で考えると、図12に示すように、素子1つで（ホールプレート1つで）ブリッジが構成できているため、位置検出用として使用してもよく、この場合、図15(c)に示すように磁気抵抗素子81に加えて縦型ホール素子80を一つ使用することでもセンサの構成が可能である。このようにしても磁界をピンポイントでより正確に検出できるとともにチップサイズを小さくすることができる。

#### 【0048】

また、磁気抵抗素子はNiFeの薄膜以外にも、NiCoの薄膜を用いてもよい。

また、縦型ホール素子の構成として、図3, 4に代わり、図16あるいは図17に示す構成としてもよい。

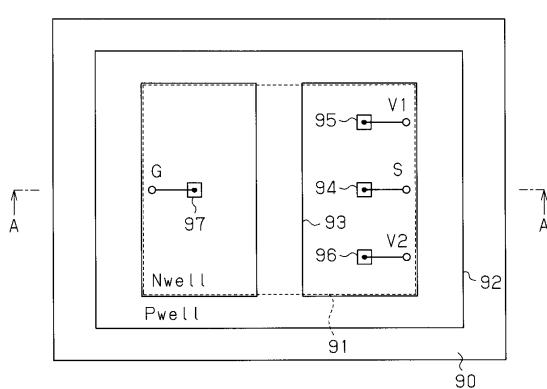

#### 【0049】

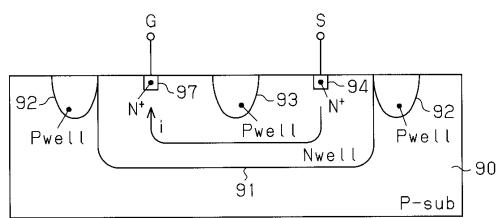

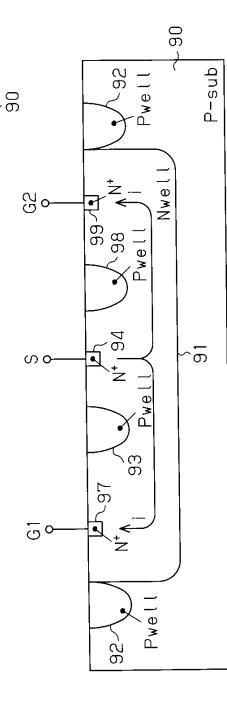

図16において、P型シリコン基板90にNウェル領域91が形成され、Nウェル領域91を囲むようにPウェル領域92が四角環状に形成されている。また、Nウェル領域91内においてPウェル領域93がNウェル領域91を二分割するように形成されている。Pウェル領域92, 93はNウェル領域91より浅い。二分割したNウェル領域91の一方の領域において表層部にN<sup>+</sup>領域94, 95, 96が一直線上に並ぶように形成され、また、二分割したNウェル領域91の他方の領域において表層部にN<sup>+</sup>領域97が形成されている。N<sup>+</sup>領域94～97はPウェル領域92, 93より浅い。N<sup>+</sup>領域94, 97が電流供給対を構成するコンタクト領域であり、N<sup>+</sup>領域95, 96が電圧出力対を構成するコンタクト領域である。

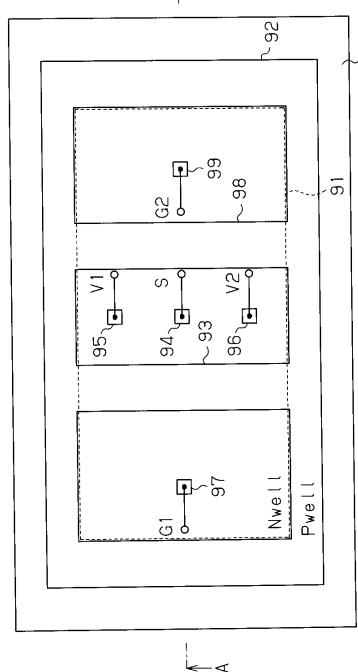

#### 【0050】

図17においては図16の構成に対し、さらに、Nウェル領域91においてPウェル領域98が形成され、これによりNウェル領域91が三分割されている。このNウェル領域91での追加した領域(3番目の分割領域)において表層部にN<sup>+</sup>領域99が形成され、N<sup>+</sup>領域99を電流供給対を構成するコンタクト領域として用いている。

#### 【0051】

この図16, 17の構成においては、CMOS工程で作成しており、バイポーラ工程でないためバイポーラ工程で作成する縦型ホール素子よりもコスト的に有利である。

以上のように、縦型ホール素子は、第1導電型の半導体基板としてのP型シリコン基板90に形成した第2導電型のウェル領域としてのNウェル領域91内においてウェル領域91よりも浅い第1導電型のウェル領域としてのPウェル領域93(98)がウェル領域91を分割するように形成され、ウェル領域91の表層部においてウェル領域93(98)を挟んで電流供給対を構成するコンタクト用の第2導電型の不純物拡散領域としてのN<sup>+</sup>領域94, 97(99)が形成されるとともに電圧出力対を構成するコンタクト用の第2導電型の不純物拡散領域としてのN<sup>+</sup>領域95, 96が形成されている。これによって、ウェル領域を用いることによりコスト的に有利な構成とすることができます。

#### 【図面の簡単な説明】

#### 【0052】

【図1】(a)は第1の実施形態における回転センサの平面図、(b)は(a)のA-A線での断面図。

【図2】センサチップの平面図。

【図3】縦型ホール素子の平面図。

【図4】図3のA-A線での縦型ホール素子の断面図。

【図5】回転センサの電気的構成図。

【図6】回転センサの波形図。

【図7】比較のためのセンサチップの平面図。

【図8】別例のセンサチップの断面図。

10

20

30

40

50

【図9】別例の磁気抵抗素子の構成を示す回路図。

【図10】第2の実施形態における回転センサの平面図。

【図11】第2の実施形態における回転センサの回路構成図。

【図12】縦型ホール素子の等価回路図。

【図13】比較のための回転センサの平面図。

【図14】比較のための磁気抵抗素子の回路図。

【図15】(a), (b), (c)は別例のセンサチップの平面図。

【図16】(a)は別例の縦型ホール素子の平面図、(b)は(a)のA-A線での縦断面図。

【図17】(a)は別例の縦型ホール素子の平面図、(b)は(a)のA-A線での縦断面図。 10

#### 【符号の説明】

##### 【0053】

10 ... 半導体基板、11 ... 縦型ホール素子、12 ... 磁気抵抗素子、13 ... 磁気抵抗素子

、50 ... arctan演算器、51 ... パルス化回路、52 ... 合成器、72 ... センサチップ

、73 ... 磁気抵抗素子、74 ... 磁気抵抗素子、75 ... 縦型ホール素子、77 ... 縦型ホール

素子、78 ... 縦型ホール素子、79 ... 磁気抵抗素子、80 ... 縦型ホール素子、81 ... 磁気

抵抗素子、90 ... P型シリコン基板、91 ... Nウェル領域、92 ... Pウェル領域、93 ...

Pウェル領域、94 ~ 97 ... N<sup>+</sup>領域、98 ... Pウェル領域、99 ... N<sup>+</sup>領域。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図12】

【図11】

【図13】

【図15】

【図14】

【図16】

(a)

(b)

【図17】

(a)

(a)

(b)

---

フロントページの続き

(56)参考文献 特表2000-515639(JP,A)

特開平01-251763(JP,A)

特開2006-128400(JP,A)

特開2001-159542(JP,A)

特開平11-094512(JP,A)

国際公開第2005/111546(WO,A1)

特開2006-275764(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 01 D 5 / 00 - 5 / 252

G 01 D 5 / 39 - 5 / 62

H 01 L 43 / 06

H 01 L 43 / 08