(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7489118号

(P7489118)

(45)発行日 令和6年5月23日(2024.5.23)

(24)登録日 令和6年5月15日(2024.5.15)

(51)国際特許分類

A 61 B 8/14 (2006.01)

F I

A 61 B

8/14

請求項の数 26 (全73頁)

|                   |                                  |          |                                                                                          |

|-------------------|----------------------------------|----------|------------------------------------------------------------------------------------------|

| (21)出願番号          | 特願2021-539864(P2021-539864)      | (73)特許権者 | 520342725<br>エコー イメージング、インク。<br>アメリカ合衆国カリフォルニア州 950<br>54, サンタクララ, パートン・ドライ<br>ブ 4201    |

| (86)(22)出願日       | 令和2年1月14日(2020.1.14)             | (74)代理人  | 100118902<br>弁理士 山本 修                                                                    |

| (65)公表番号          | 特表2022-517774(P2022-517774<br>A) | (74)代理人  | 100106208<br>弁理士 宮前 徹                                                                    |

| (43)公表日           | 令和4年3月10日(2022.3.10)             | (74)代理人  | 100196508<br>弁理士 松尾 淳一                                                                   |

| (86)国際出願番号        | PCT/US2020/013530                | (72)発明者  | ハク, ユースフ<br>アメリカ合衆国 94065 カリフォル<br>ニア州 レッドウッドシティ ブリッジ・<br>パークウェイ 3600 スイート 102<br>最終頁に続く |

| (87)国際公開番号        | WO2020/150253                    |          |                                                                                          |

| (87)国際公開日         | 令和2年7月23日(2020.7.23)             |          |                                                                                          |

| 審査請求日             | 令和5年1月13日(2023.1.13)             |          |                                                                                          |

| (31)優先権主張番号       | 62/792,821                       |          |                                                                                          |

| (32)優先日           | 平成31年1月15日(2019.1.15)            |          |                                                                                          |

| (33)優先権主張国・地域又は機関 | 米国(US)                           |          |                                                                                          |

(54)【発明の名称】 超音波イメージングシステムのための合成レンズ

## (57)【特許請求の範囲】

## 【請求項1】

超音波イメージングシステムであって、該超音波イメージングシステムは、

a) 複数の p M U T トランスデューサ素子を含む超音波トランスデューサであって、前記複数の p M U T トランスデューサ素子のそれぞれが 2 つ以上の端子を有する、超音波トランスデューサと、

b) 前記複数の p M U T トランスデューサ素子に接続された 1 つ以上の回路であって、前記 1 つ以上の回路は、

i) 前記超音波トランスデューサから超音波パルスを送信すること、

i i) 前記超音波トランスデューサで反射された超音波信号を受信すること、および

i i i) 前記超音波パルス、または前記反射された超音波信号を、仰角方向に集束させるために構成された電子制御とを、可能にするために電子的に構成される、

回路と、

\_を含む、超音波イメージングシステムにおいて、

\_パルス送信および反射された超音波信号の受信は、反射された超音波信号を、第 1 のビームフォーマーを使用してアジマス方向に集束させるために使用され、および仰角焦点は、第 2 のビームフォーマーを使用して達成され、

\_仰角方向の焦点は、遅延をデジタル方式で適用することによって受信器で達成される、

\_超音波イメージングシステム。

## 【請求項2】

前記複数のトランステューサ素子は、1つ以上の行および1つ以上の列に配置され、

前記複数のトランステューサ素子は、上部セクション、中央セクション、および下部セクションを含み、それらのそれぞれは、パルス送信および反射された超音波信号の受信のための多くの行および多くの列を含み、

前記複数のp M U Tトランステューサ素子のうちの2つは、ともにアドレスされ、前記2つの素子は、前記1つ以上の行の1つの行上で隣接する、

請求項1に記載の超音波イメージングシステム。

【請求項3】

前記複数のトランステューサ素子は、1つ以上の行および1つ以上の列に配置され、トランステューサ素子の2次元アレイを構成し、

10

前記複数のp M U Tトランステューサ素子の1つ以上は、その異なる部分上で2つの方向に分極され、分極の強度は、行上の前記複数のp M U Tトランステューサ素子の1つ以上の素子の位置に応じて変動し、および前記複数のp M U Tトランステューサ素子の1つ以上のそれぞれは、少なくとも3つの端子を含む、

請求項1に記載の超音波イメージングシステム。

【請求項4】

分極の強度は、中心の行の方が強く、外側の行の方が弱く、それによって仰角方向にアポダイゼーションが作成される、請求項3に記載の超音波イメージングシステム。

【請求項5】

前記1つ以上の回路は、送信ドライバ回路、受信増幅器回路、および制御回路の1つ以上を含む、請求項1に記載の超音波イメージングシステム。

20

【請求項6】

前記電子制御は、リアルタイムで行われる、請求項1に記載の超音波イメージングシステム。

【請求項7】

前記複数のトランステューサ素子の上部で配置される外部レンズであって、前記仰角方向において追加焦点を提供するように構成される外部レンズをさらに含む、請求項1に記載の超音波イメージングシステム。

【請求項8】

前記仰角焦点および仰角アポダイゼーションは、イメージングされる標的における運動誤差を最小限に抑えるために電子的に実行され、前記1つ以上の回路は、仰角方向へのアポダイゼーションの電子制御を可能にするように電子的に構成される、請求項1に記載の超音波イメージングシステム。

30

【請求項9】

列上の各トランステューサ素子は、前記1つ以上の回路によって生成される多値パルスによって駆動される、請求項2に記載の超音波イメージングシステム。

【請求項10】

前記多値パルスの大きさ、幅、形状、パルス周波数、またはそれらの組み合わせは、電気的にプログラム可能である、請求項9に記載の超音波イメージングシステム。

【請求項11】

多値パルスのパルス開始の遅延、または、多値パルスのシーケンスのパルス数は、電気的にプログラム可能である、請求項9に記載の超音波イメージングシステム。

40

【請求項12】

前記送信ドライバ回路は、列上の前記複数のp M U Tトランステューサ素子の1つ以上を駆動するように構成され、かつ送信チャネルからの信号によって駆動され、前記送信チャネルの信号は、異なる列上の複数のp M U Tトランステューサ素子の他の1つ以上を駆動する他の送信チャネルに適用される遅延に関連して電子的に遅延される、請求項5に記載の超音波イメージングシステム。

【請求項13】

列上の前記複数のp M U Tトランステューサ素子の1つ以上は、実質的に同一の遅延、

50

または異なる遅延で作動する、請求項 1 2 に記載の超音波イメージングシステム。

【請求項 1 4】

前記制御回路は、列上の前記複数の p M U T トランステューサ素子の 1 つ以上のための相対的遅延を決定するように構成され、および前記制御回路は、相対的遅延のために粗遅延をセットするように構成される粗遅延回路と、相対的遅延のために細密遅延をセットするように構成される細密遅延回路と、を含む、請求項 1 3 に記載の超音波イメージングシステム。

【請求項 1 5】

前記送信チャネルおよび追加送信チャネルは、隣接する列間の相対的遅延を電気的に制御するように構成され、および前記制御回路は、同じ行にある第 1 の数のトランステューサ素子が、開始行の第 2 の数のトランステューサ素子と実質的に同様の相対的遅延を共有するように、列上の第 1 の数のトランステューサ素子のための相対的遅延をセットするように構成される、請求項 1 2 に記載の超音波イメージングシステム。

10

【請求項 1 6】

前記送信チャネルおよび追加の送信チャネルは、隣接する列間の相対的遅延を電子的に制御するように構成され、および前記制御回路は、同じ行にある第 1 の数のトランステューサ素子が、他の列の同じ行の第 2 の数のトランステューサ素子と比較して独立した遅延を有するように、列上のトランステューサ素子の相対的遅延をセットするように構成される、請求項 1 2 に記載の超音波イメージングシステム。

20

【請求項 1 7】

前記制御回路は、列の中心行にあるトランステューサ素子に対して対称的になるように列の相対的遅延を電気的に制御するように構成される、請求項 1 6 に記載の超音波イメージングシステム。

【請求項 1 8】

前記制御回路は、列内で直線的に増大するように、相対的遅延を電気的に制御し、それによって、超音波ビームを仰角方向に導くように構成される、請求項 5 に記載の超音波イメージングシステム。

【請求項 1 9】

前記制御回路は、相対的遅延を電気的に制御し、それによって、仰角方向にスライス厚を制御するように構成される、請求項 5 に記載の超音波イメージングシステム。

30

【請求項 2 0】

前記制御回路は、相対的遅延を、列で区分線形的に増加するまたは減少するように電気的に制御し、区分線形遅延セグメントの数は、2 以上の整数であるように構成される、請求項 5 に記載の超音波イメージングシステム。

【請求項 2 1】

前記制御回路は、列に沿った相対的遅延を、線形遅延と任意の細密遅延の和となるように電気的に制御するように構成される、請求項 5 に記載の超音波イメージングシステム。

【請求項 2 2】

B モードを使用してイメージングするために、受信チャネルは、行上の 2 つのトランステューサ素子、上部セクションの 2 つの素子のうちの一方の素子、下部セクションの 2 つの素子のうちの他方の素子に割り当てられ、および、別のチャネルは、中央セクションの 2 つのトランステューサ素子に割り当てられる、請求項 2 に記載の超音波イメージングシステム。

40

【請求項 2 3】

2 N の受信チャネルは、N の列にアドレスするために使用される、請求項 2 2 に記載の超音波イメージングシステム。

【請求項 2 4】

前記複数のトランステューサ素子のすべては、送信動作において仰角焦点を有する圧力を生成するために作動され、および受信動作において、前記複数のトランステューサ素子のすべては、アジマス方向および仰角面に集束する画像を復元するために使用される、請

50

求項 2 2 に記載の超音波イメージングシステム。

**【請求項 2 5】**

送信アポダイゼーションは、仰角面において使用される、請求項 2 2 に記載の超音波イメージングシステム。

**【請求項 2 6】**

前記仰角焦点は、動的であり、仰角面において導かれる、請求項 2 2 に記載の超音波イメージングシステム。

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

関連出願の相互参照

本出願は、2019年1月15日に出願された、米国仮出願シリアル番号第62/792,821号の利益を主張し、本明細書で全体として参照により組み込まれる。

**【背景技術】**

**【0 0 0 2】**

超音波イメージングについては、トランスデューサは、イメージングされる標的へ超音波ビームを送信するために使用され、および反射された波形は、トランスデューサによって受信され、受信された波形は、電気的信号に変換され、さらなる信号処理で、超音波画像が作成される。慣例的に、2次元の(2D)イメージングについては、超音波トランスデューサは、超音波ビームの発射のために1次元(1D)トランシーバーアレイを含む。アレイ上に位置する機械的レンズは、超音波波形を仰角面に集束させる。一旦構築されると、構造的特性、および、したがって、アレイおよび機械的レンズの対応する機能的特性は、変更することができない。

**【発明の概要】**

**【0 0 0 3】**

圧電センサは、20年間以上医療用イメージングに使用されている。これらは、典型的にバルク圧電フィルムを使用して、構築される。これらのフィルムは、アジマス方向に列に沿って配置される圧電素子を形成する。各列は、送信ドライバによって駆動され得る。連続の列上で様々な時間遅延を使用することによって、送信されたビームをアジマス方向に集束させることは可能である。

**【0 0 0 4】**

圧電素子のアレイの仰角配置は、アレイのビームが仰角面でナロービームへと電子的に集束することを可能にすることができます。トランシーバーアレイの圧電素子の単一の行は、2D超音波画像の仰角または厚さ次元での電子集束を可能にしない。従来の2D超音波画像は、仰角方向にある厚さを有するアジマス面にある(すなわち、薄い画像スライスにビームを制限するための従来の技術は、ビームを、この次元で圧電素子の輪郭を作るまたは各素子をレンズ効果させること(lensing)によって、この横また仰角的次元で機械的に集束させるためである)。さらに最近では、この次元で素子の圧電特性の制御によって、仰角的集束を達成することができることは示された。シェ-デッド分極として知られているこの技術では、グレードつけられた強電界は、圧電素子が中心に最も強く分極され、仰角方向における素子の各末端へとより劣った程度に分極されるように、圧電素子の分極を次第に減らすために、各素子に均一に適用される。技術は、各圧電素子の音響透過率を、アレイの縦の中央線に沿ってより大きく、かつ各仰角側面へと少なくなるために形成し得る。この技術の著しい短所は、分極シェーディングの規模およびグラジエントを正確に制御することの困難さである。他の既存の技術は、仰角焦点を達成するためにアレイの一部のためにより小さな電圧駆動が使用されてもよいが、短所も有する。例えば、米国特許第特許2005/0075572A1は、仰角焦点で促進するために機械的レンズを使用する。

**【0 0 0 5】**

他の方法は、トランスデューサを複数の行に整列する。例えば、1.5次元の(1.5

10

20

30

40

50

D)、1.75次元(1.75D)のトランステューサは、複数の送受信を使用し、および受信ビームフォーミングを、例えば、二段階ビームフォーマーを使用して、実行して、仰角焦点上である程度の制御を可能にする場合がある。しかしながら、これらの方法は、複数の送受信の必要性のため、仰角焦点の制限的程度、および画像の低フレームレートのみを可能にし得る。さらに、さらなる計算が必要とされ、それによって、通常電力がバッテリーから供給される低コストのポータブル装置に望ましくない電力およびコストが高まる場合がある。

#### 【0006】

一態様では、本明細書に開示されるのは超音波イメージングシステムであって、該超音波イメージングシステムは、a)複数のpMUTトランステューサ素子を含む超音波トランステューサであって、複数のpMUTトランステューサ素子の各々が2つ以上の端子を有する、超音波トランステューサと、b)複数のpMUTトランステューサ素子に接続された1つ以上の回路であって、前記1つ以上の回路は、i)超音波トランステューサから超音波パルスを送信することと、ii)超音波トランステューサで反射された超音波信号を受信することと、iii)超音波パルス、または反射された超音波信号を、仰角方向に集束させるために構成された電子制御と、を可能にするために電子的に構成される、回路と、を含む。いくつかの実施形態では、複数のトランステューサ素子は、トランステューサ素子のアレイを含む。いくつかの実施形態では、アレイは2次元である。いくつかの実施形態では、アレイは、長方形、正方形、環状形状、橢円形、放物線形状、螺旋形状、または任意の形状から選択された形状を含む。いくつかの実施形態では、複数のトランステューサ素子は、1つ以上の行および1つ以上の列に配置される。いくつかの実施形態では、列上の各トランステューサ素子は、1つ以上の回路によって生成される多値パルスによって駆動される。いくつかの実施形態では、列上の各トランステューサ素子は、前記1つ以上の回路によって生成される多値パルスのシーケンスによって駆動される。いくつかの実施形態では、多値パルスのパルス振幅、幅、形状、パルス周波数、またはそれらの組み合わせは、電気的にプログラム可能である。いくつかの実施形態では、パルス開始の遅延は、電気的にプログラム可能である。いくつかの実施形態では、パルスシーケンスのパルスの1つ以上は、電気的にプログラム可能である。いくつかの実施形態では、多値パルスの形状は、正弦曲線、デジタル正方形、または任意の形状である。いくつかの実施形態では、複数のpMUTトランステューサ素子の1つ以上の第1の端子は、前記1つ以上の回路に接続され、および第2の、随意に追加端子は、バイアス電圧に接続される。いくつかの実施形態では、複数のpMUTトランステューサ素子の1つ以上は、その異なる部分上で2つの方向に分極され、分極の強度は、列上で前記複数のpMUTトランステューサ素子の1つ以上の素子の位置に応じて変動し、および前記複数のpMUTトランステューサ素子の1つ以上の各々は、少なくとも3つの端子を含む。いくつかの実施形態では、複数のpMUTトランステューサ素子の1つ以上は、1つの方向のみに分極され、および前記複数のpMUTトランステューサ素子の1つ以上の各々は、2つの端子のみを含む。いくつかの実施形態では、分極の強度は、中心行のためにより強く、外側行のためにより弱く、それによって仰角方向にアポダイゼーションが作成される。いくつかの実施形態では、1つ以上の回路は、送信駆動回路、受信増幅器回路、および制御回路の1つ以上を含む。いくつかの実施形態では、送信駆動回路は、列上で前記のpMUTトランステューサ素子の1つ以上を駆動するように構成され、かつ送信チャネルからの信号によって駆動され、前記送信チャネルの信号は、異なる列上で他のpMUTトランステューサ素子の1つを駆動する他の送信チャネルに適用される遅延に関連して電子的に遅延される。いくつかの実施形態では、列上で複数のpMUTトランステューサ素子の1つ以上は、実質的に同一の遅延、または異なる遅延で作動する。いくつかの実施形態では、制御は、リアルタイムに行われる。いくつかの実施形態では、複数のトランステューサ素子の各々は、第1のリードおよび第2のリードを含み、第1のリードは、1つ以上の回路に電子的に接続され、および第2のリードは、前記複数のトランステューサ素子の他のトランステューサ素子の対応リードに接続される。いくつかの実施形態では、複数のトランステューサ素子の上で配

10

20

30

40

50

置される外部レンズをさらに含み、外部レンズは、仰角方向においてさらなる焦点を提供するように構成される。いくつかの実施形態では、制御回路は、同じ列に位置するトランステューサ素子のための駆動パルス間の相対的な遅延を電気的に制御するために構成される。いくつかの実施形態では、送信チャネルおよび追加送信チャネルは、隣接列間の相対的な遅延を電気的に制御するために構成され、および制御回路は、同じ行にある第1の数のトランステューサ素子が、開始行の第2の数のトランステューサ素子と実質的に同様の相対的な遅延を共有するように、列上でトランステューサ素子の第1の数のための相対的な遅延をセットするために構成される。いくつかの実施形態では、送信チャネルおよび追加送信チャネルは、隣接列間の相対的に電気的に制御するために構成され、および制御回路は、同じ行にある第1の数のトランステューサ素子が、他の列の同じ行の第2の数のトランステューサ素子と比較して独立した遅延を有するように、列上でトランステューサ素子の相対的な遅延をセットするために構成される。いくつかの実施形態では、制御回路は、列の中心行でトランステューサ素子に対して対称的な列の相対的な遅延を電気的に制御するように構成される。いくつかの実施形態では、制御回路は、相対的な遅延を、それらが列で直線的に増大して、それによって、仰角方向に超音波ビームを導くように、電気的に制御するために構成される。いくつかの実施形態では、制御回路は、相対的な遅延を電気的に制御するために構成され、それによって、仰角方向にスライス厚を制御する。いくつかの実施形態では、複数のトランステューサ素子は、上部分、中央部分、および下部分を含み、それらの各々は、パルス送信および反射された超音波信号の受信のための行数および列数を含み、それらの部からのパルス送信および反射された超音波信号の受信は、反射された超音波信号を、第1のビームフォーマーを使用してアジマスに集束させるために使用され、および仰角焦点は、第2のビームフォーマーを使用して達成される。いくつかの実施形態では、部分からのスキャンラインは、次の列のスキャンに進行する前に全列のスキャンを完成することによって、イメージングされる標的における運動誤差を最小限に抑えるために同期される。いくつかの実施形態では、仰角方向の焦点距離は電子的にプログラムされる。いくつかの実施形態では、上部セクションおよび下部セクションのパルス送信および反射信号の受信は、同時に実行される。いくつかの実施形態では、イメージングされる対照における運動誤差は、スキャンラインを現像するために並列のビームフォーミングを実行することによって最小限に抑えられる。いくつかの実施形態では、仰角焦点および仰角アポダイゼーションは、運動誤差を最小限に抑えるために電子的に実行される。いくつかの実施形態では、多値パルスは、外部列のためにより低い振幅駆動、および中央列のために高い振幅駆動を使用することによって、アポダイゼーションを電子的に実施するために使用される。いくつかの実施形態では、上部セクション、中央セクション、および下部セクションは、1より多くのサブセクションを含み、そのサブセクションの各々は、パルス送信および反射信号の受信のために列数および列数を含む。いくつかの実施形態では、複数のトランステューサ素子は、5つのセクションを含み、ここで、アジマス角に集束されるビームを送受信する2つの外部のセクションは、アジマス角に集束されるビームを送受信する2つの内部のセクション、およびアジマス角に集束されるビームを送受信する中央セクションに従い、第1レベルのビームフォーマーを使用してスキャンラインを形成し、および第2レベルのビームフォーマーを使用して仰角焦点を達成する。いくつかの実施形態では、アポダイゼーションは、仰角方向に電子的に実施される。いくつかの実施形態では、超音波トランステューサは、機械的レンズの欠損によって引き起こされる信号欠損によって物質的に制限されていない帯域幅を示す。いくつかの実施形態では、複数のpMUTトランステューサ素子のうちの2つは、ともにアドレスされ、2つの素子は、1つ以上の行の同行上で隣接し、および複数のトランステューサ素子は、上部セクション、中央セクション、および下部セクションを含み、そのセクションの各々は、超音波パルス送信および反射された超音波信号の受信のために行の第1の数および列の第2の数を含み、セクションからの超音波パルス送信および反射超音波信号の受信は、第1のビームフォーマーを使用して、反射超音波信号をアジマス方向に集束させるために使用され、および仰角焦点は、第2のビームフォーマーを使用して、達成され、およびBモードを

10

20

30

40

50

使用してイメージングするために、受信チャネルは、同行上で効率的に組み合わせられる 2 つのトランステューサ素子に割り当てられ、ここで、2 つの素子が 1 つの有効な素子として動作し、かつそれらの組み合わせられる素子を含む上と下からの行の一部はともに接続され、および、別のチャネルは、少数の行から成る中央セクションの 2 つのトランステューサ素子に割り当てられる。いくつかの実施形態では、2 N 受信チャネルは、N 列にアドレスするために使用される。いくつかの実施形態では、複数のトランステューサ素子のすべては、送信作動における仰角焦点で圧力を生成するために作動され、および受信作動における、前記複数のトランステューサ素子のすべては、アジマス方向および仰角面に集束することを用いて画像を復元するために使用される。いくつかの実施形態では、送信アポダイゼーションは仰角面において使用される。いくつかの実施形態では、仰角焦点は動的であり、仰角面において導かれる。いくつかの実施形態では、機械的レンズは使用されない。いくつかの実施形態では、p M U T トランステューサ素子の 1 つ以上は、同時の送受信作動のために構成可能な複数のサブ素子を含む。いくつかの実施形態では、p M U T トランステューサ素子の 1 つ以上は、複数のサブ素子を含み、ここで、前記複数のサブ素子は、様々な共振周波数応答を有する。いくつかの実施形態では、複数の p M U T トランステューサ素子の各々は、少なくとも 2 つの端子を有する。いくつかの実施形態では、制御回路は、列上でトランステューサ素子のための相対的遅延を決定するために構成され、およびここで、制御回路は、粗遅延をセットするために構成される粗遅延回路と、細密遅延をセットするために構成される細密遅延回路を含む。いくつかの実施形態では、ビームの導きは、粗遅延回路を使用して達成され、および、仰角焦点は、細密遅延回路を使用して達成される。いくつかの実施形態では、列のための細密遅延は、他の列上の細密遅延に依存しない。いくつかの実施形態では、制御回路は、相対的遅延が、列で区分線形的に増大するまたは減少することを電気的に制御するために構成され、および区分線形遅延セグメントの数は、2 以上の整数である。いくつかの実施形態では、制御回路は A S I C 上で実行される。いくつかの実施形態では、制御回路は、列に沿った相対的遅延を、線形遅延と任意の細密遅延の加重であるように電気的に制御するために構成される。いくつかの実施形態では、列の線形遅延および任意の細密遅延は、超音波トランステューサの他の列の他の線形遅延および任意の細密遅延から独立しており、それによって、3 つの次元における任意の導きおよび集束が可能になる。いくつかの実施形態では、複数の p M U T トランステューサ素子の各々は、多数の振動モードを示、ここで、1 つの振動モードは、入力刺激が、前記 1 つまたは唯一の振動モードに隣接している複数の振動モードの他のものの周波数未満であるように帯域制限されるときに引き起こされる。いくつかの実施形態では、複数の p M U T トランステューサ素子の各々は、複数の振動モードを示し、ここで、第 1 の複数の振動モードから生成された周波数は、第 2 の複数の振動モードからの周波数と重複する。いくつかの実施形態では、複数の p M U T トランステューサ素子の各々は、複数の振動モードの中心周波数を含む広帯域周波数入力によって駆動される時に複数の振動モードを同時に示す。いくつかの実施形態では、1 つ以上の回路は、仰角方向にアポダイゼーションの電子制御を可能にするために電子的に構成される。いくつかの実施形態では、複数の p M U T トランステューサ素子の各々は、同じ半導体ウエハ基板上で製作され、かつそれに隣接中の回路を感知、駆動、および制御するために接続される。

#### 【 0 0 0 7 】

いくつかの実施形態では、1 つ以上の回路は、1 つの作動中にアジマス面における B モードイメージングを開発するために電子的に構成され、ここで、送信ビームフォーマーの遅延は、選択された素子にアジマス方向に適用され、および、受信アパーチャ技術を使用して、2 つの直交軸上で形成される 2 方向画像を表示するために、後の作動中に仰角方向に遅延を調節するために送信ビームフォーマーを使用することによって、直交面における B モードイメージングを開発するために、さらに構成される。いくつかの実施形態では、アジマス面におけるイメージングするとき、列上の素子上に追加遅延を追加することによって仰角焦点が達成され、および仰角面で画像を形成するとき、アジマス面におけるさらなる焦点を可能にために、行上の素子上にアジマス軸上で追加遅延を追加する。

10

20

30

40

50

## 【0008】

他の態様では、本明細書に開示されるのは、本明細書の超音波イメージングシステムを使用して、3Dイメージングを実行する方法であって、該方法は、a) 前記複数のpMUTトランスデューサ素子によって超音波パルスを送信する工程であって、該工程は、i) 第1の複数の遅延を、同じ列上の複数のpMUTトランスデューサ素子の1つ以上に適用された第2の複数の遅延によって制御される、仰角方向に特定の導きの角度を有する送信のセットのためにアジマス方向に適用することと、ii) a) の各反復のために仰角方向にさらなる導きの角度を用いて設定数回a) を繰り返すことと、を含む工程と、b) 前記複数のpMUTトランスデューサ素子によって反射された超音波信号を受信する工程と、c) 前記複数のpMUTトランスデューサ素子からの受信された反射された超音波信号を使用して、画像を復元する工程と、を含む。いくつかの実施形態では、第1の複数の遅延内の遅延の規模は等しく、および第2の複数の遅延内の遅延の規模は等しい。いくつかの実施形態では、第1の複数の遅延を適用することは、a) アジマスに沿った第1の複数の遅延内の1つ以上の遅延の規模を変動することによってアジマス面にa) 集束させることと、b) 特定の列に沿った複数のpMUTトランスデューサ素子の1より多くのために第2の複数の遅延内の1つ以上の遅延の規模を変動することによって、仰角方向にビームを集束させるまたは導くことと、をさらに含む。いくつかの実施形態では、送信のセットは特定の焦点を有する。いくつかの実施形態では、画像は3次元であり、容積を表わす。いくつかの実施形態では、第1の複数の遅延内の遅延の規模は、すべて等しくなく、および第2の複数の遅延内の遅延の規模は、すべて等しくない。いくつかの実施形態では、設定数は100未満である。いくつかの実施形態では、設定数は1000以上である。

10

20

30

## 【0009】

## 引用による組み込み

本明細書で言及される全ての刊行物、特許、及び特許出願は、あたかも個々の刊行物、特許、又は特許出願が引用によって組み込まれるよう具体的且つ個別に示されるかのように、同じ程度まで引用により本明細書に組み込まれる。

## 【図面の簡単な説明】

## 【0010】

本主題の特徴と利点のより良い理解は、例証的な実施形態と添付の図面を説明する以下の詳細な記載を参照することによって得られる。

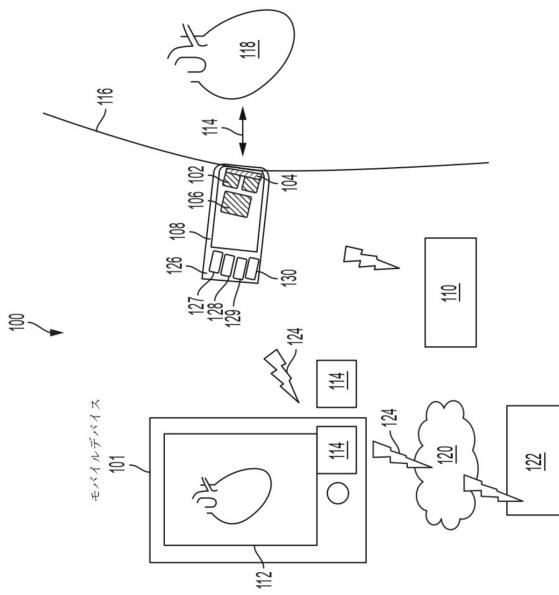

【図1】は、本明細書の超音波システムの例示的な概略図を示し、該システムは、超音波ビームを送受信するために使用されるpMUTアレイを備えたトランスデューサと、pMUTアレイを制御するためのエレクトロニクス、他の計算、制御、および通信エレクトロニクス、ディスプレーユニットおよび記録ユニットを含み、pMUTアレイはイメージングされる標的に向けられている。

40

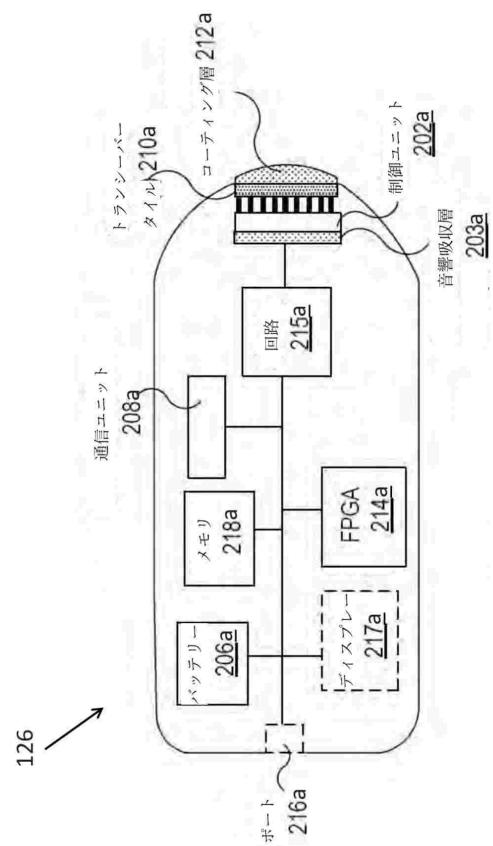

【図2】は、本明細書の超音波トランスデューサの例示的な概略図を示す。

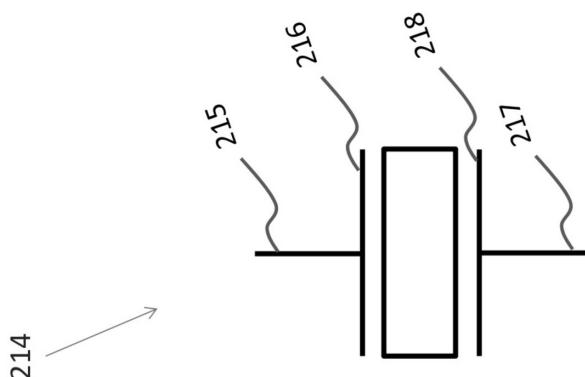

【図3A】は、2つの伝導体を備えた圧電マイクロマシントラスデューサ(pMUT)素子の例示的な概略図を示す。

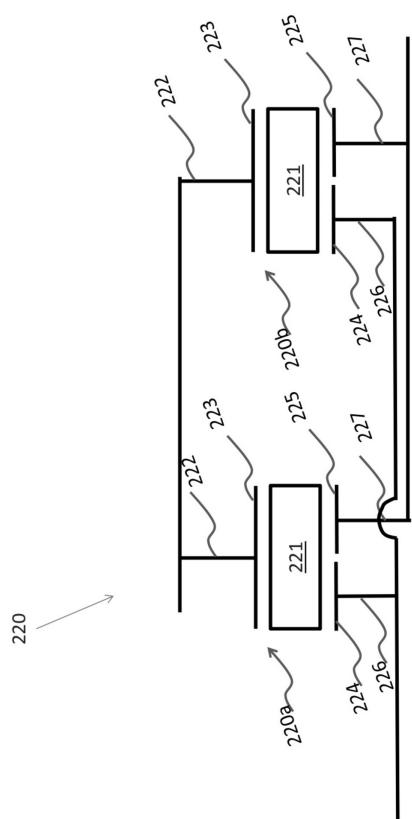

【図3B】は、2つのサブ素子を含むpMUT素子の例示的な概略図を示し、各サブ素子は、2つ以上の電極を有する。

【図3C】は、2つのサブ素子を含むpMUT素子の例示的な概略図を示し、各サブ素子は、2つの電極を有し、ここで、第1のサブ素子の第1の電極は、第2の素子の電極の1つに接続され、および第1の素子の第2の電極は、第2のサブ素子の残りの電極に接続される。

【図4】は、本明細書の超音波トランスデューサシステムのpMUTアレイの例示的な図を示す。

【図5A】は、本明細書のpMUTアレイの圧電素子の例示的な断面を示す。

【図5B】は、図5Aの圧電素子の例示的な象徴的表象を示す。

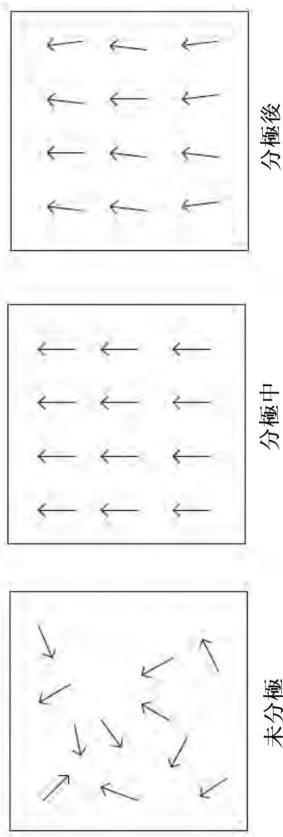

【図6】は、本明細書の圧電素子における分極されていない状態、および分極中に、および分極後の双極子方向づけを示す。

50

【図 7】は、象徴的な接続構成を有する受信モード中の、低ノイズ増幅器（LNA）への本明細書の圧電素子の例示的な接続を示す。

【図 8 A】は、電気的に調節可能な線トランスデューサのために 1 つの共通の接地電極またはバイアス電極を有する pMUT の 2D アレイの例示的な実施形態を示し、該トランスデューサの線は、垂直または水平方向にあってもよく、および線のサイズ（例えば、線における pMUT 素子の数）は、電気的にプログラム可能である。

【図 8 B】は、バイアス電圧に示される接続を有する pMUT の 2D アレイの例示的な実施形態を示し、はおよび／または活潑に駆動される端子。

【図 9】は、pMUT 素子当たり差別的な分極方向を可能にするために複数の接地電極およびバイアス電極を示す線トランスデューサの例示的な実施形態を示す。

【図 10 A】は、ピエゾ材料制御膜および 1 行当たりに異なる分極強度のために異なる分極方向を使用する性能を有する各圧電素子上に複数の膜を備える例示的な pMUT アレイを示す。

【図 10 B】は、分極作動後のバイアス接続が示された、図 10 A の例示的な実施を示す。

【図 11 A】は、送信と受信のドライバを牽制する ASIC および他の機能への、2 つの pMUT 素子の相互連結の例示的な概略図を示す。

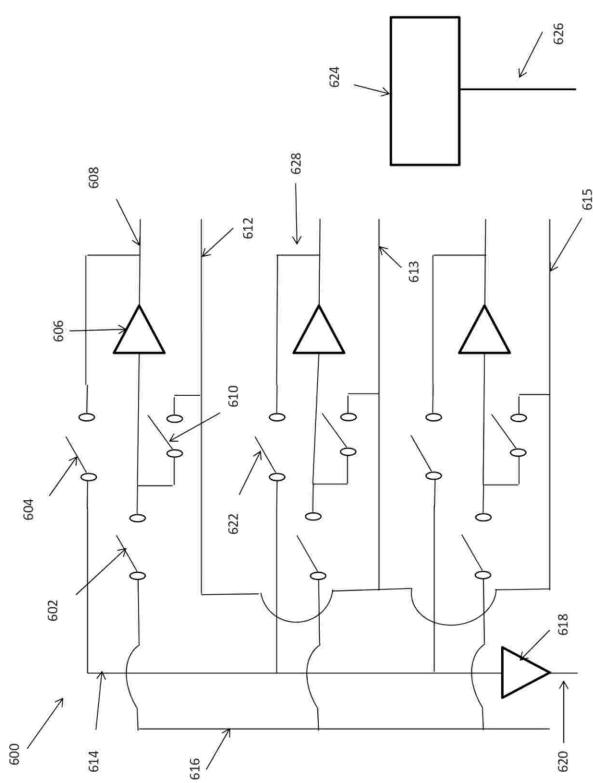

【図 11 B】は、図 11 A の ASIC の例示的な概略図を示し、その概略図では、1 つのエレクトロニクスの列は、混成より大きなトランスデューサ素子を構成するために pMUT の 1 列と直接に相互動作する。

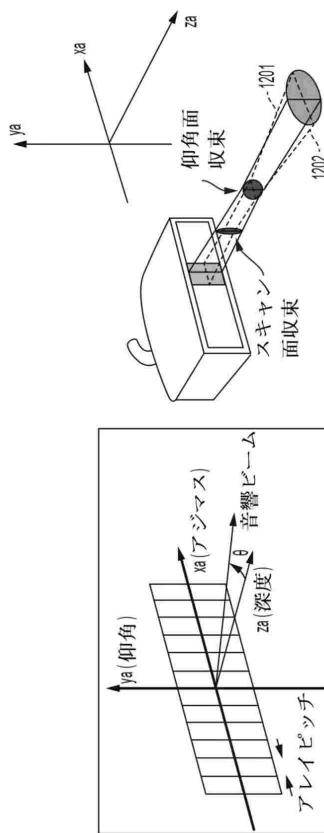

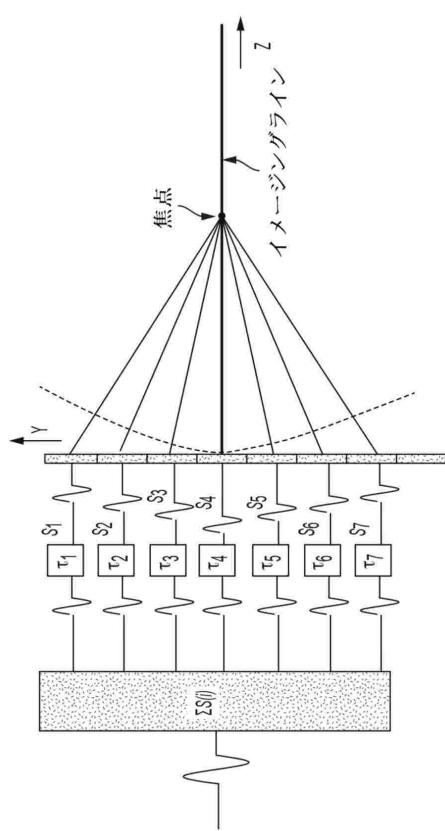

【図 12 A】は、本明細書に開示される仰角方角に集束する超音波トランスデューサの例示的な概略図を示す。

【図 12 B】は、本明細書に開示される仰角方角に集束する超音波トランスデューサの例示的な概略図を示す。

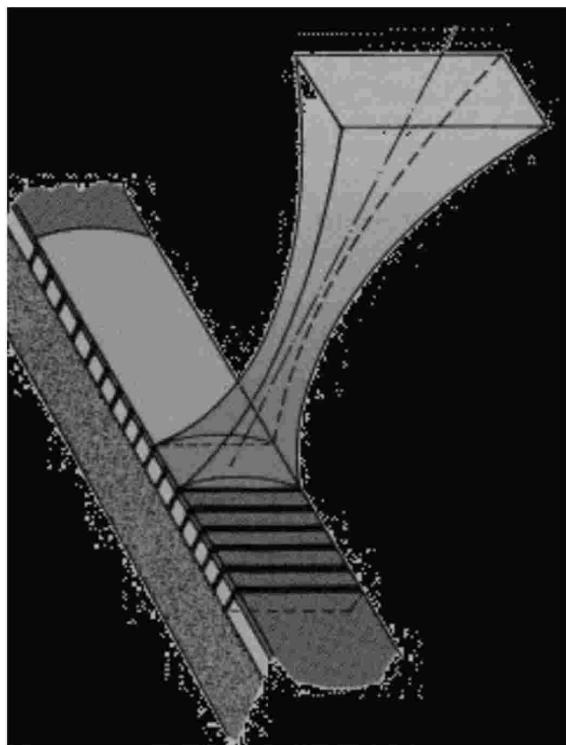

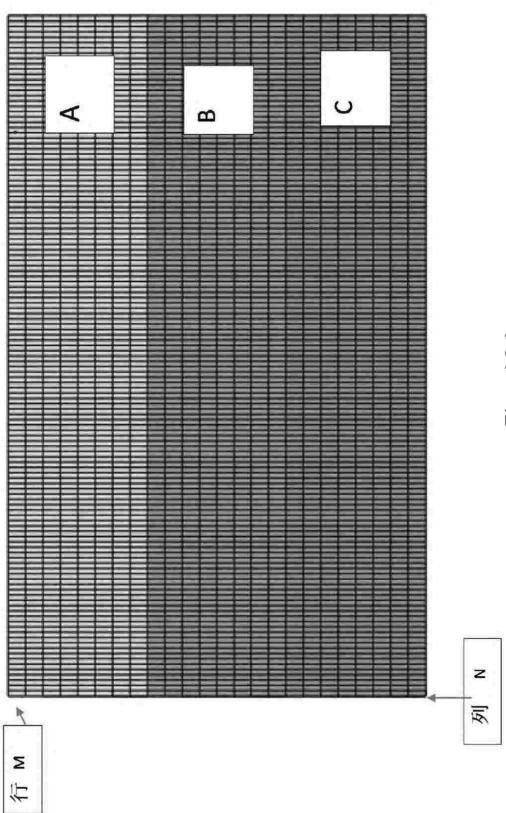

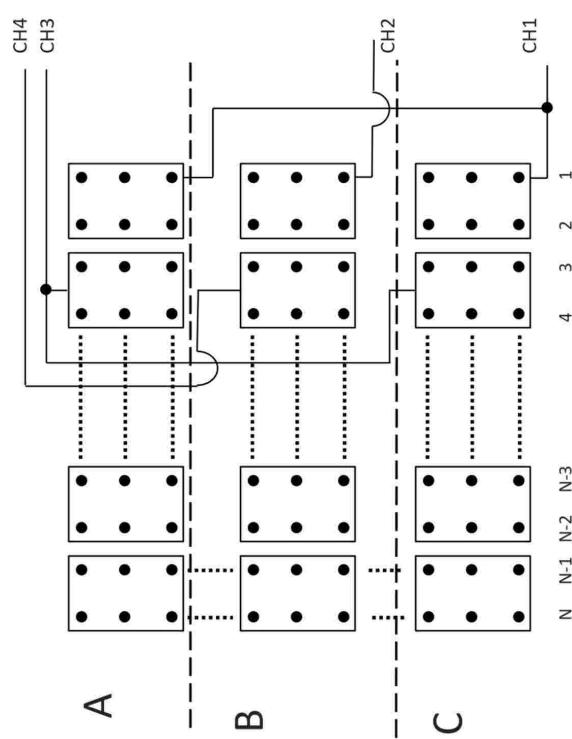

【図 13 A】は、超音波トランスデューサの例示的な概略図を示し、そのトランスデューサ素子は M 行と N 列の上で整列され、トランスデューサは、行および／または列を含む 3 つのストリップから成り、ストリップの各々は個別に駆動されるように選択され得、および各ストリップ中の列は送信ドライバによる同じ駆動を共有する。

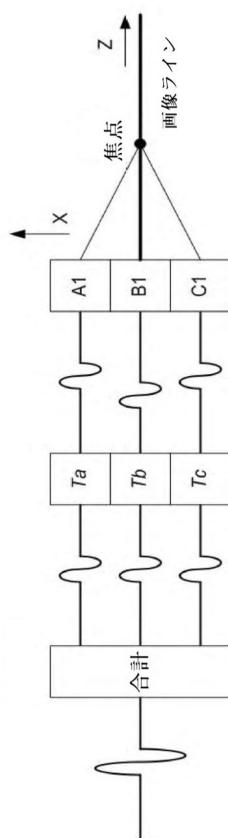

【図 13 B】は、行と列に整列されるトランスデューサ素子を有する超音波トランスデューサの例示的な概要を示し、行上の 2 つの素子は、送受信の目的のために有効的にともに組み合わせられ、トランスデューサは、行および／または列のトランスデューサ素子の 3 つの部分を含み、トランスデューサの上部および下部の部分は、送信および／または受信作動のために 1 つのチャネルによって駆動され得る一方、中央部分は、送信および／または受信作動のために異なるチャネルによって駆動され得る。

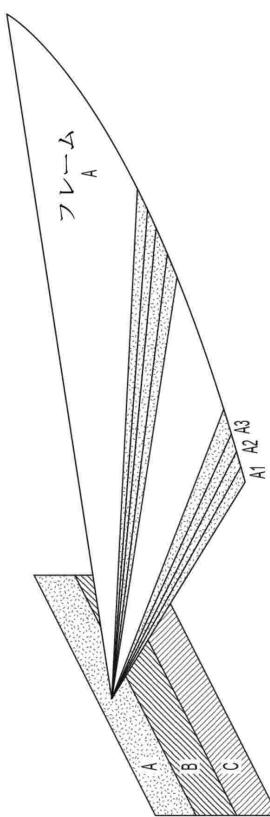

【図 14】は、超音波画像フレームを構築するスキャンライン数の例示的な概略図を示す。

【図 15】は、図 14 のスキャンラインを取得することの例示的な概略図を示す。

【図 16】は、様々なストリップに適用される遅延を使用して、仰角焦点を取得することの例示的な概略図を示す。

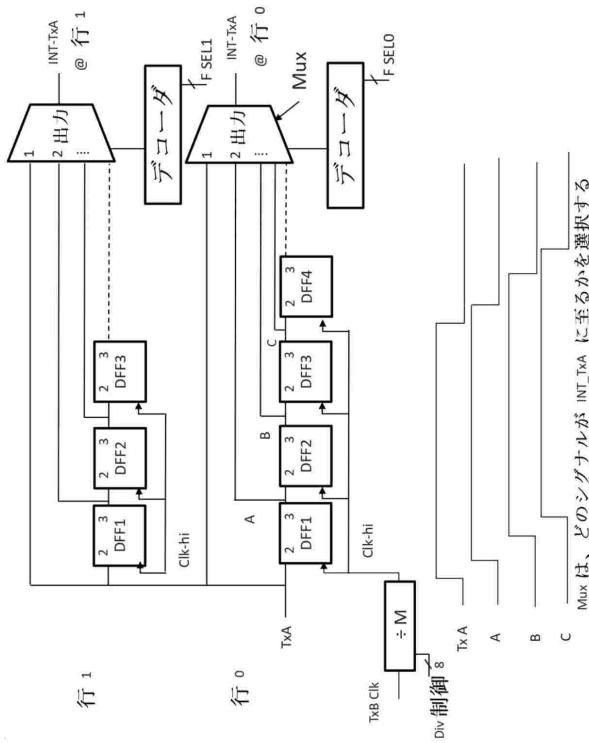

【図 17 A】は、列上で素子に粗遅延を提供する、複数のフリップフロップを有する本明細書の遅延回路の例示的な概略図を示す。

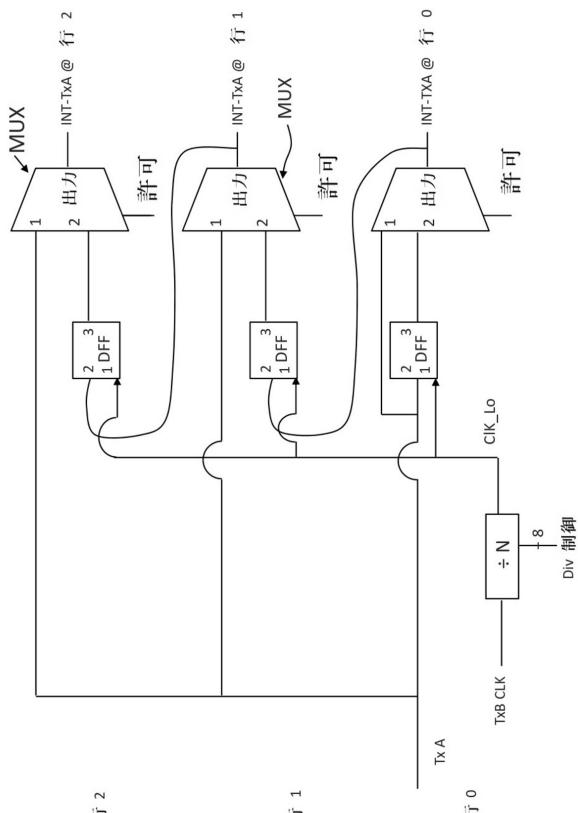

【図 17 B】は、列上で素子に細密遅延を提供する、本明細書の遅延回路の例示的な概略図を示す。

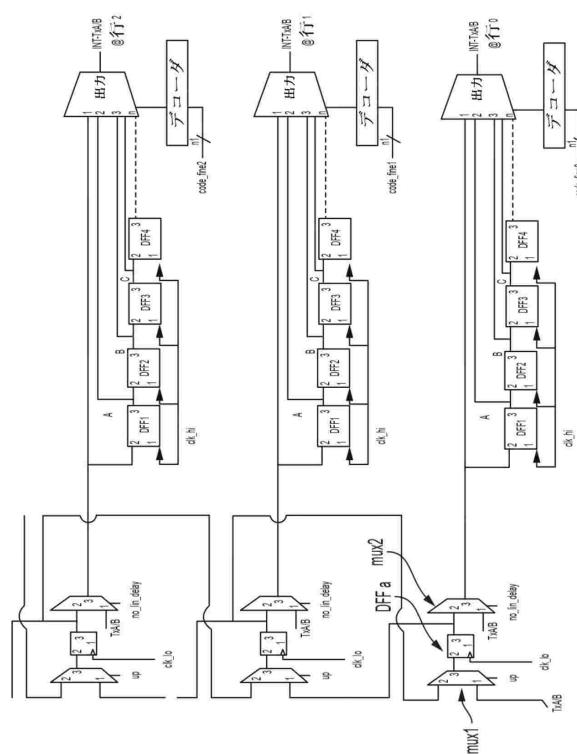

【図 17 C】は、列上で素子に粗遅延および／または細密遅延を提供する遅延回路の例示的な概略図を示す。

【図 17 D】は、図 17 C の追加回路の詳細を示す。

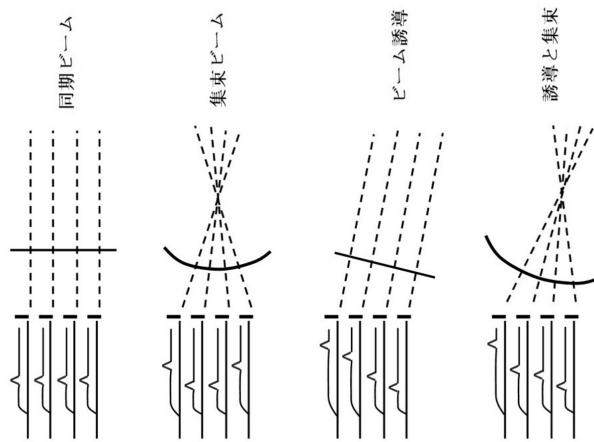

【図 18 A】は、送信チャネルからのアジャス方向での遅延を使用して、アジャス方向でのビーム誘導またはビーム集束を有する図を示す。

【図 18 B】は、トランスデューサ素子およびそれらの遅延の例示的な概略図を示し、遅延は電子的にプログラムされることができ、トランスデューサ素子の 1 より多くの列に実質的に類似し得る。

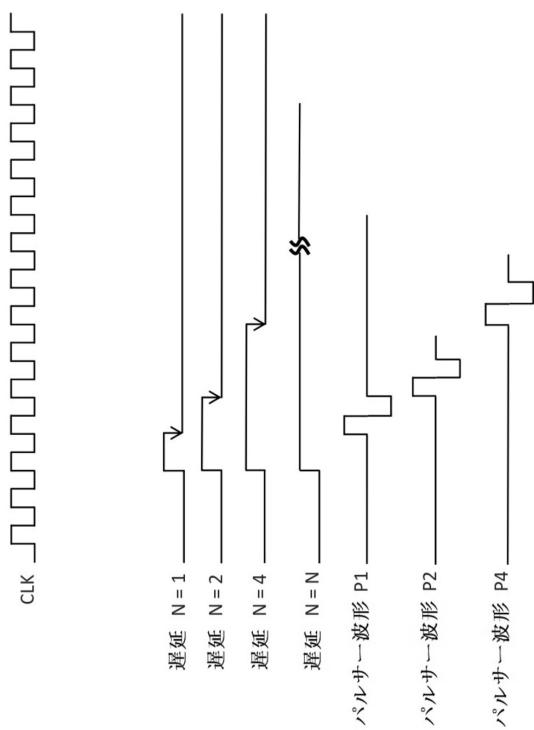

【図 19】は、送信駆動パルスの例示的な概略図を示し、トランスデューサ素子の列の遅延回路を示す。

延は、中央素子のまわりに遅延相称を有する。

【図 2 0】は、様々な列のトランステューサ素子のための遅延を有する送信駆動パルスの例示的な概略図を示す。

【図 2 1】は、内部カウンター信号を使用して、様々な遅延を生成することの例示的な概略図を示す。

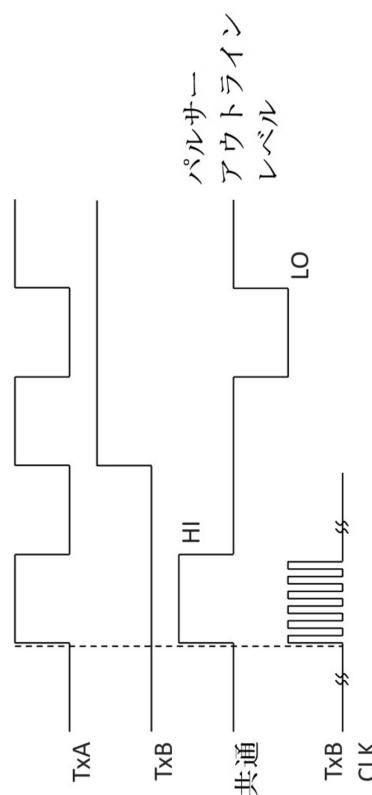

【図 2 2】は、送信駆動パルスとして出力を生成する、2つのデジタル入力を有するパルサーの例示的な概略図を示す。

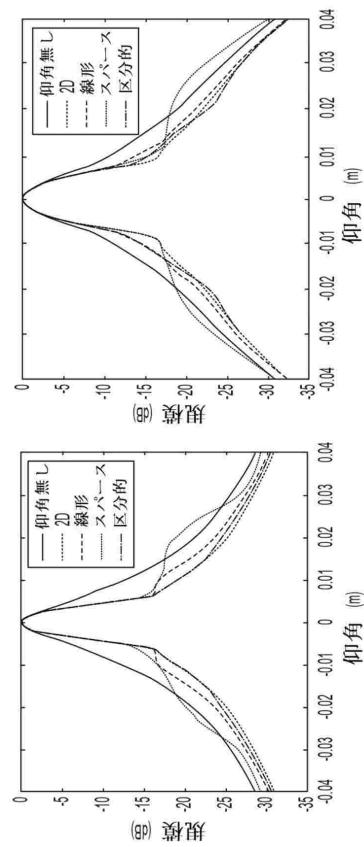

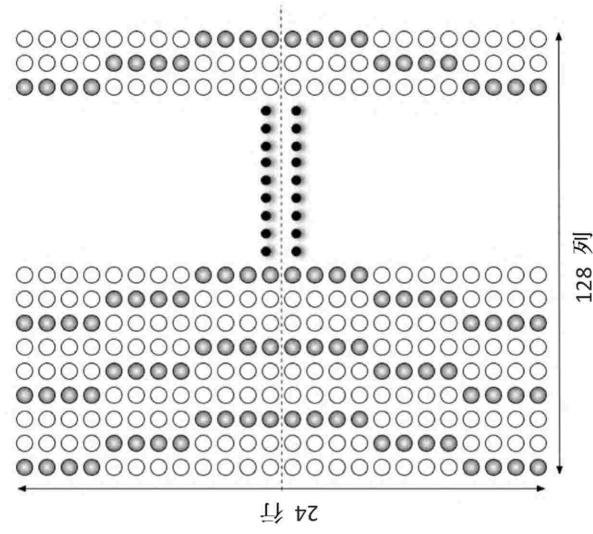

【図 2 3 A】は、0度の外側の誘導（左パネル）および45度の外側の誘導（右パネル）を有するトランステューサ素子のシミュレートされた $24 \times 128$ マトリックスアレイの例示的な仰角ビームプロット（beam plots）を示し、それは、仰角方向の集束されないと比較して、仰角方向に集束を提供することの複数の方法の違いを示す。10

【図 2 3 B】は、トランステューサ素子の $24 \times 128$ の2Dアレイで送信仰角集束を可能にする例示的なスパース送信スキームを示し、それでは、暗くなった円は、1列当たりのトランステューサ素子になり得、（仰角対称面に沿って集束することを仮定して）仰角相称は使用されることができる。この送信スキームは、すべての $24 \times 128$ 能動素子を使用する場合よりおよそ1/3の少ない圧力を出力することができる。

【図 2 4 A】は、本開示の実施形態に係る、イメージングアセンブリの概略図を示す。

【図 2 4 B】は、基板に配置されたトランステューサと、別の基板上のASICと、相互連結の手段との例示的な実施形態を示す。

【図 2 5】は、本開示の実施形態に係る2および3次元イメージングを実行可能な圧電素子アレイの概略図を示す。20

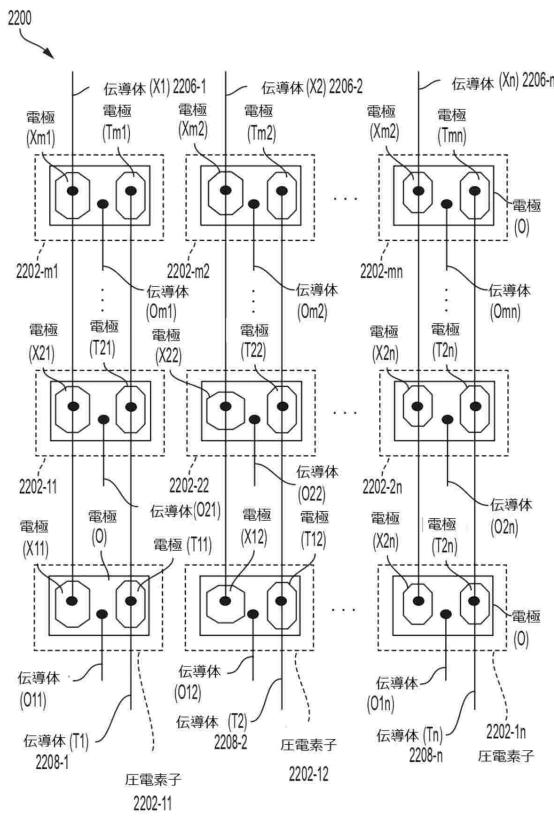

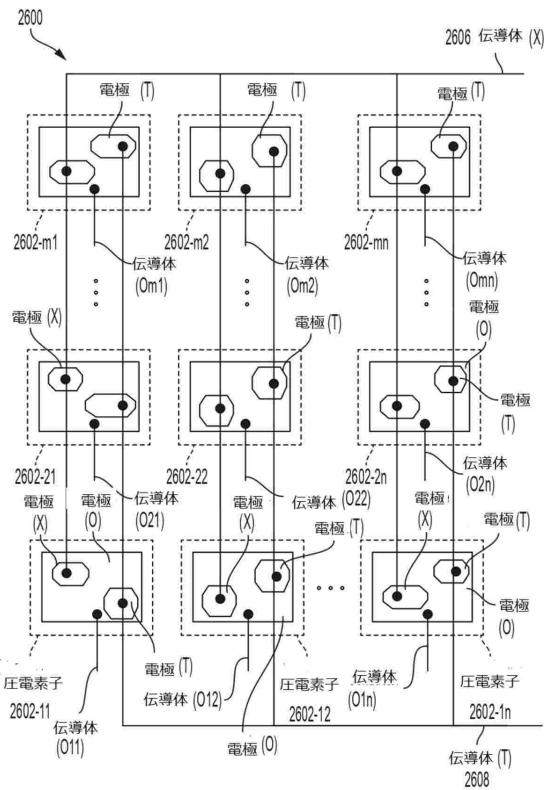

【図 2 6】は、本開示の実施形態に係る圧電素子アレイの概略図を示す。

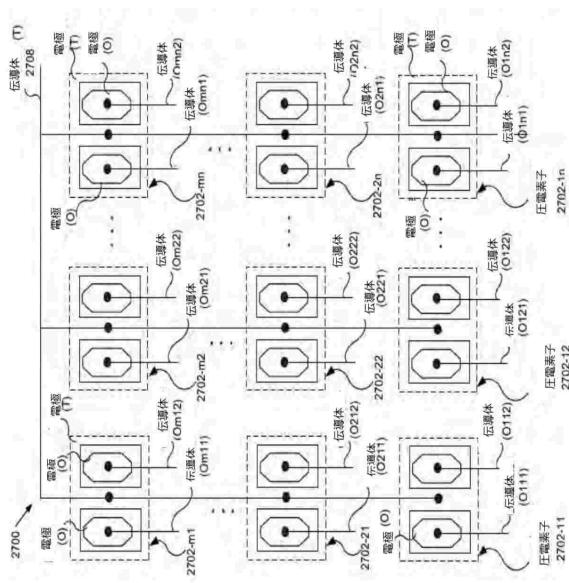

【図 2 7】は、本開示の実施形態に係る圧電素子アレイの概略図を示す。

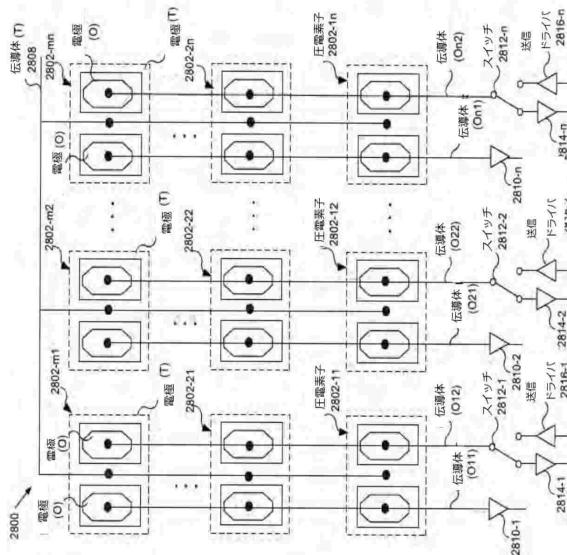

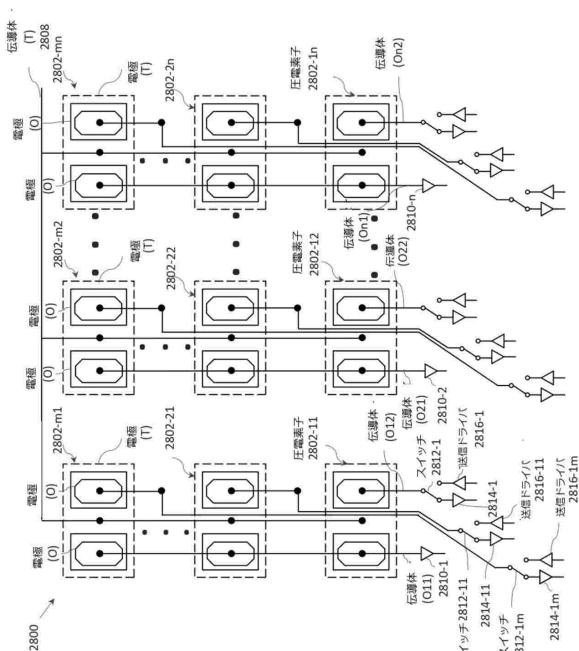

【図 2 8】は、本開示の実施形態に係る圧電素子アレイの概略図を示す。

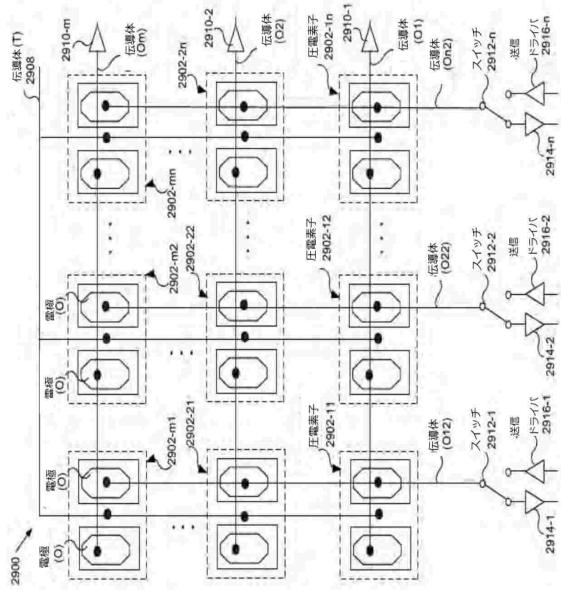

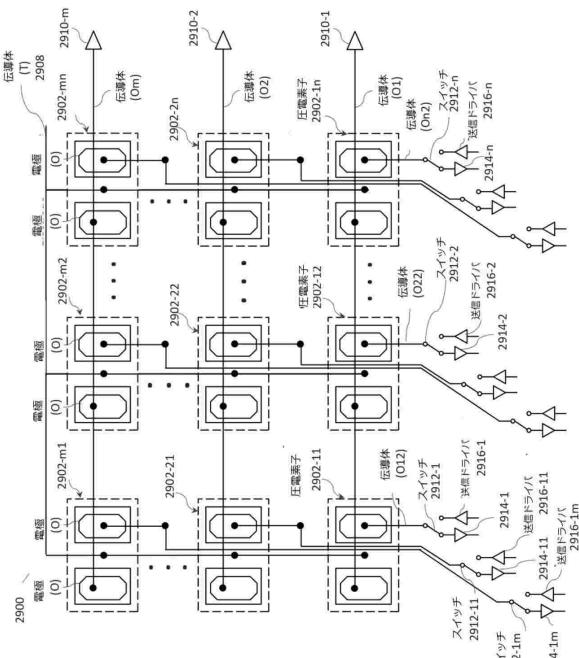

【図 2 9】は、本開示の実施形態に係る圧電素子アレイの概略図を示す。

【図 3 0】は、本開示の実施形態に係る圧電素子アレイの概略図を示す。

【図 3 1】は、本開示の実施形態に係る圧電素子アレイの概略図を示す。

【図 3 2】は、本開示の実施形態に係る圧電素子アレイの概略図を示す。

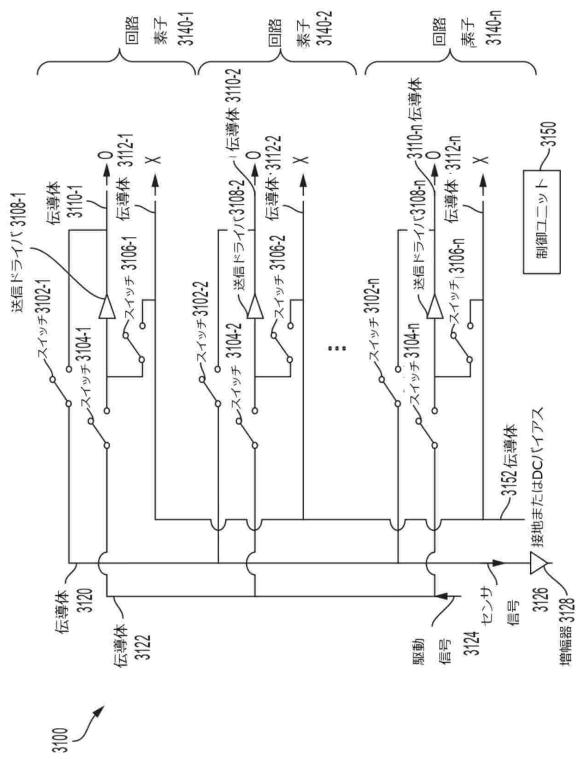

【図 3 3 A】は、本開示の実施形態に係る、列上の圧電素子のための有線接続を有するイメージングシステムの概略図を示す。30

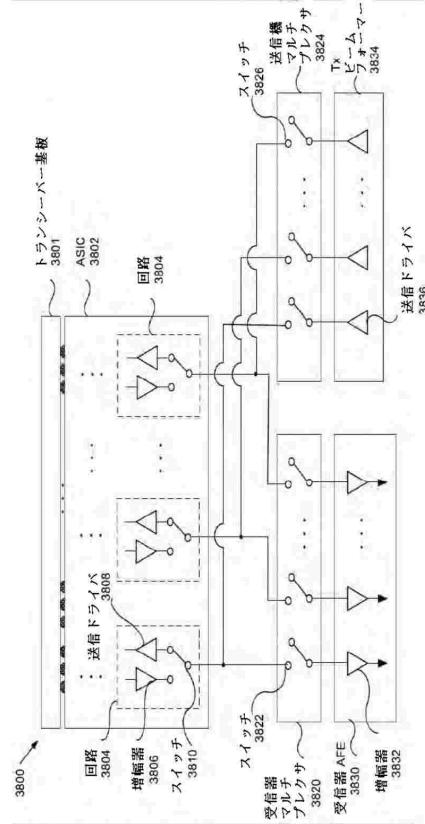

【図 3 3 B】は、本開示の実施形態に係る、列上の圧電素子のためのプログラム可能な送受信機能を有するイメージングシステムの概略図を示す。

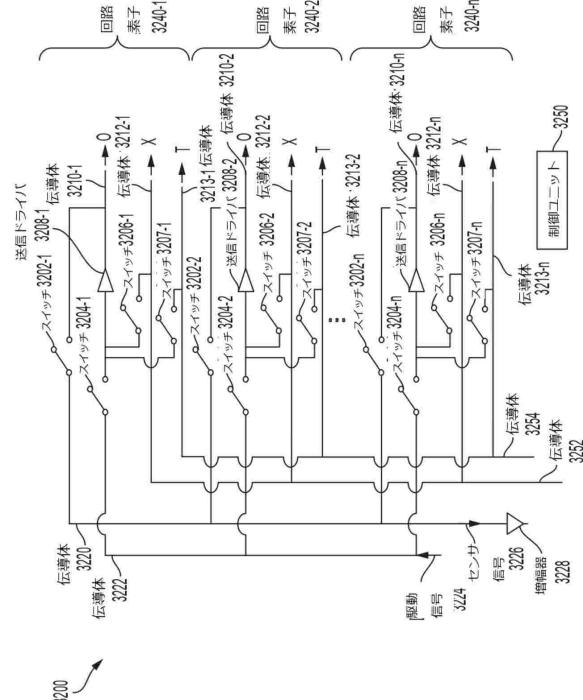

【図 3 4 A】は、本開示の実施形態に係る、列上の有線圧電素子を有するイメージングシステムの概略図を示す。

【図 3 4 B】は、本開示の実施形態に係る、列上の圧電素子のプログラム可能な送受信機能を有するイメージングシステムの概略図を示す。

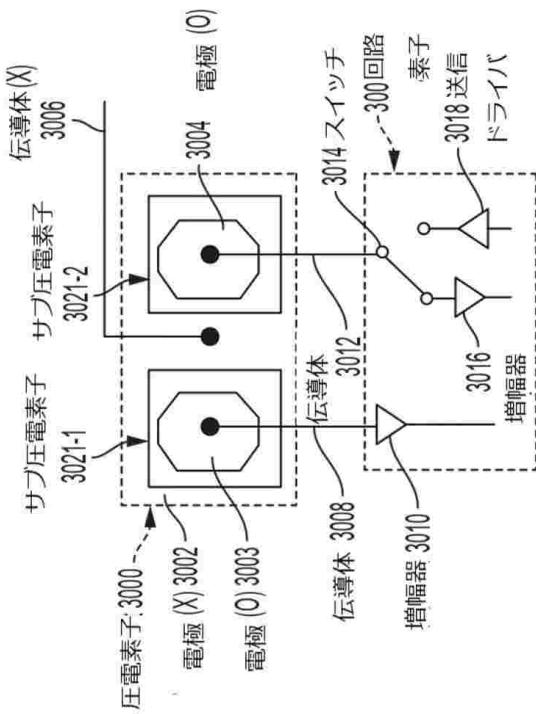

【図 3 5 A】は、本開示の実施形態に係る、回路素子に結合された圧電素子の実施形態を示す。

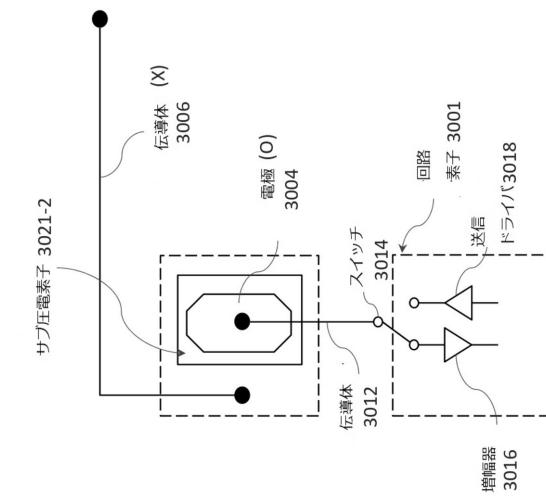

【図 3 5 B】は、圧電素子が、プログラム可能な送受信機能を有する、本開示の実施形態に係る、回路素子に結合された圧電素子の例示的な実施形態を示す。

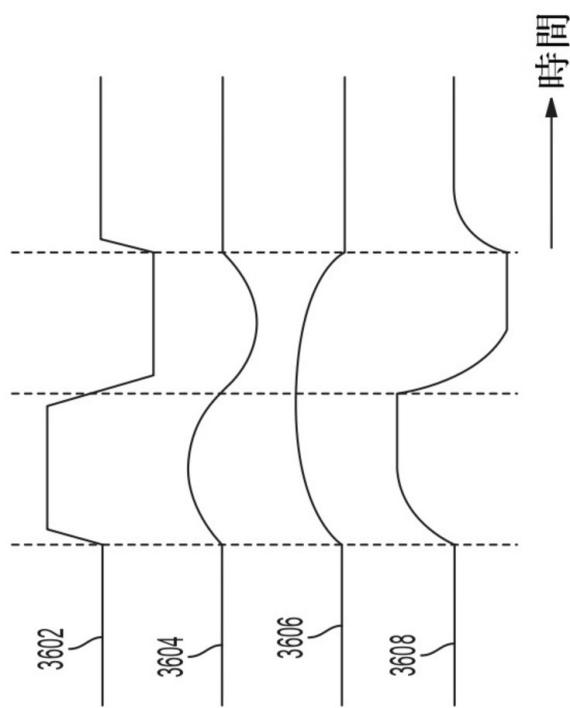

【図 3 6】は、本開示の実施形態に係る、複数の圧電素子を制御するための回路を示す。

【図 3 7】は、本開示の実施形態に係る、複数の圧電素子を制御するための回路を示す。

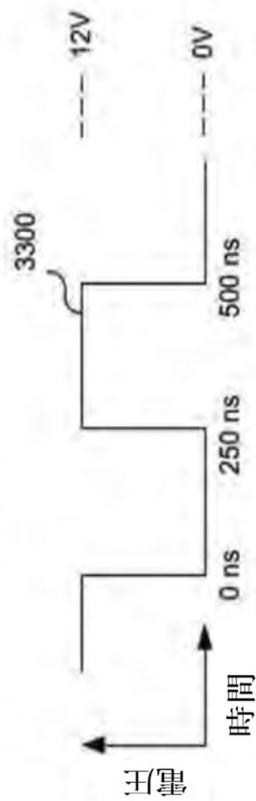

【図 3 8】は、本開示の実施形態に係る、送信駆動信号波形を示す。

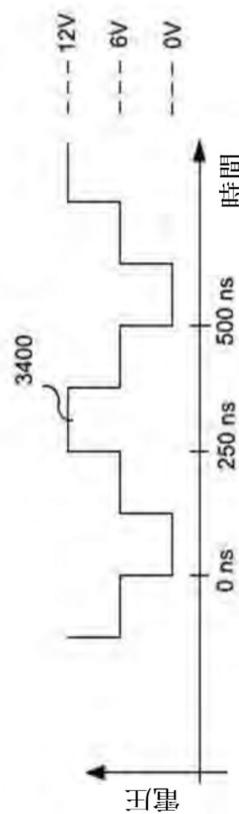

【図 3 9 A】は、本開示の実施形態に係る、送信駆動信号波形を示す。

【図 3 9 B】は、本開示の実施形態に係る、送信駆動信号波形を示し、ここで、T × B C L Kは、送信チャネルのためにパルス出力のために生成されるT × AおよびT × B波形を生成するために使用することができる高速クロックである。

【図 4 0】は、本開示の実施形態に係る、送信駆動信号波形を示す。

【図 4 1】は、本開示の実施形態に係る、イメージングアセンブリにおける様々な回路の入力 / 出力信号を示す。

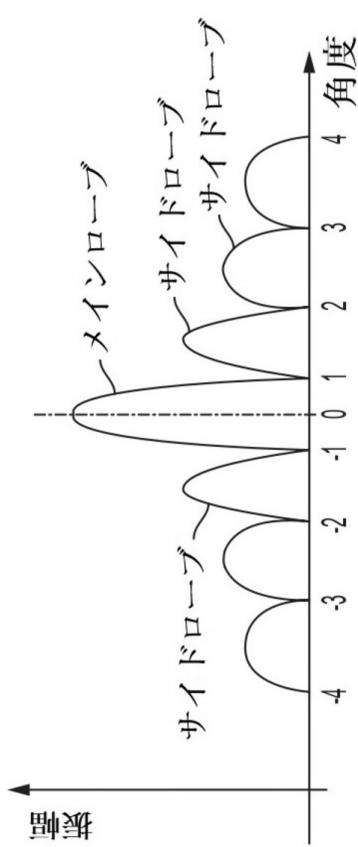

【図42A】は、本開示の実施形態に係る、角度の関数として送信圧力波の振幅のプロットを示す。

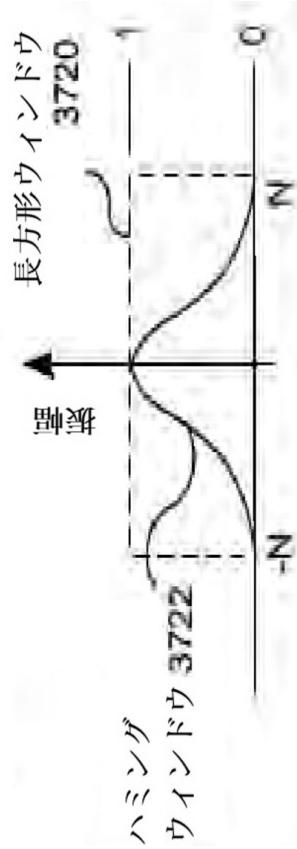

【図42B】は、本開示の実施形態に係る、アポダイゼーションプロセスのためのウィンドウを示す。

【図43】は、本開示の実施形態に係る、イメージングアセンブリの概略図を示す。

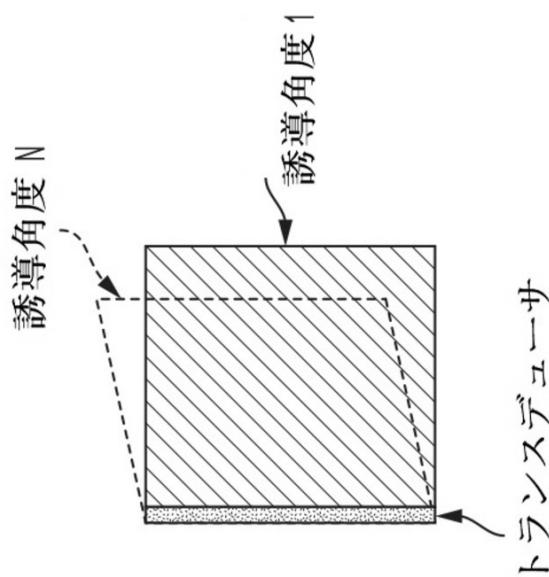

【図44】は、本開示の実施形態に係る、トランスデューサの特定の誘導角度を示す。

【発明を実施するための形態】

【0011】

従来、2D超音波画像は、*Fredrik Lingvall Lingvall, F. , 2004. Time-domain Reconstruction Methods for Ultrasonic Array Imaging: A Statistical Approach*によって記載されたものなどの様々なアルゴリズムの使用によって作成することができる。[[http://www.signal.uu.se/Publications/pdf/fredrik\\_thesis.pdf](http://www.signal.uu.se/Publications/pdf/fredrik_thesis.pdf)を参照]この1つの例は、信号を圧電素子の列に沿ってアジマス方向に駆動するために相対的な遅延を使用することである。アジマス方向の様々な列の信号に適用される、電子的にプログラム可能な遅延を変更することによってビームをアジマス方向に電子的に集束させることができる。しかしながら、アジマス方向に垂直の方向（例えば、仰角方向）における焦点は、典型的に機械的レンズの使用によって達成される。機械的レンズは、一度にわずか1つの焦点を可能とすることができる、したがって、様々な仰角焦点には、レンズの様々な設計が必要となる場合がある。さらに、固定された機械的レンズは、3D超音波イメージングに必要な焦点を提供しない。

10

20

20

【0012】

3D超音波イメージングは、既存のポータブル超音波イメージングシステムで実施するには、あまりに複雑で、高価であり、大量の電力を消費する。いくつかの実施形態において本明細書に開示されるのは、2Dおよび3Dの両方の超音波イメージングように低コストで、低電力で、ポータブル高解像度超音波トランスデューサおよび超音波イメージングシステムを実現するために構成されたシステムおよび方法である。これらの低コスト高性能システムの実現は、高量半導体プロセスと同様に、高量および低コストで半導体ウエハ上で製造可能なpMUTの使用に左右される場合がある。例示的な実施形態では、そのようなpMUTは、2Dアレイに配置され、ここで、アレイにおける各素子は電子回路に接続され、pMUTアレイおよび回路アレイは様々なウエハ上で一体的に整列され、かつタイルを形成するために一体的に統合され、各圧電素子は制御回路素子に接続され、各圧電素子は図3Bと図3Cに示されるように2つ以上の端子を有する。これらのpMUTは、さらに、高帯域を示すことができ、そうすることで、従来のピエゾ容積トランスデューサと異なり、前述のトランスデューサを広帯域のイメージングに適切なものにする。従来のトランスデューサの帯域幅は、制限されており、様々なトランスデューサを様々な周波数範囲で求められる場合がある。このため、1つのトランスデューサが1MHzから12MHz以上などの広範囲の周波数をカバーすることで、患者を診察時に、ユーザにとってより大きな利便性を提供することができ、この場合ユーザは、多種多様な周波数を必要とする様々な臓器を検査する際に、異なるトランスデューサに切り替える必要がない場合もある。この結果、コストは削減することができる。広帯域挙動は、少なくとも2つの異なる方法で本開示のpMUTにおいて達成することができる。いくつかの実施形態では、トランスデューサ素子は、2つ以上のサブ素子を含んでもよく、各サブ素子は、異なる中心周波数で共振する。さらに、複合体として一体化した場合、この合成素子は、より大きな帯域をカバーすることができる（例として図28を参照）。他の実施形態では、1つの膜において複数の共振モードを支持することができるよう、膜を設計することができる。共振は、共振が一定の周波数で生じる初期モードを呈することができる。他の共振、例えば、第2の共振、第3の共振も、膜に存在してもよい。これらの共振は、調和して関連づけられることもまたは関連づけられないこともある。これらの共振のまわりの帯域幅は、他

30

40

50

の共振のまわりの帯域幅と重複する場合があり、それによって、全体的な広帯域幅を可能にする。p M U Tへの入力信号が、例えば、1つの共振に帯域制限されると、他の共振は生じない場合がある。トランスデューサ素子は、様々な共振の中心周波数を含む広帯域周波数入力によって駆動されると、複数の振動モードを同時に呈することができる。

#### 【 0 0 1 3 】

加えて、仰角集束に機械的レンズを利用する既存のトランスデューサは、さらにレンズにおける減衰欠損という問題を抱える場合があり、それによって、画質が低下する。本明細書の例示的な合成レンズでは、機械的レンズは不要である。時に、深焦点でわずかに曲線した弱いレンズを使用してもよく、または代わりに、トランスデューサの上部に平らで薄いインピーダンス整合層が使用することができる。これにより、減衰欠損は大幅に改善することができる。

10

#### 【 0 0 1 4 】

固定された機械的レンズを使用する代わりに、本明細書に開示されるイメージングシステムは、固定された焦点距離を有する機械的レンズを構築する必要性を都合よく排除する電子レンズを使用する。さらに、本明細書に開示される電子レンズは、仰角面における焦点距離を変更可能な大きな適応性を可能にするとともに、および深さに応じた動的な焦点を可能にする。さらに、アポダイゼーションにより、仰角方向にあるサイドローブを、抑制することができ、これにより仰角スライス厚みの良好な調節が可能となる。仰角制御におけるアポダイゼーションの電子リアルタイム制御により、仰角方向でのサイドローブの電子的な抑制を都合よく可能にする場合がある。

20

#### 【 0 0 1 5 】

本明細書に開示されるのは、いくつかの実施形態では、仰角方向に集束するように構成可能な超音波イメージングシステムである。本明細書に開示されるのは、いくつかの実施形態では、列および／または行に沿ったプログラム可能な遅延による電子仰角制御を可能にするように構成可能な超音波イメージングシステムである。いくつかの実施形態では、電子制御は、プログラム可能な遅延が、列上で個々の素子を駆動する送信駆動回路に挿入されるときに生じる。

#### 【 0 0 1 6 】

本明細書に開示されるのは、いくつかの実施形態では、トランスデューサ素子（例えば、p M U T素子）であり、したがって、トランスデューサ素子の圧電素子は、2つの次元で複数の行（各行はアジマス方向に沿っている）および列（各列は仰角方向に沿っている）へと整列される。いくつかの実施形態では、行の中央セクションのまわりに1つまたは複数の行を含むセクションが、アジマス方向に沿って集束される場合がある。1回の送受信で、このセクションから生成したデータをアジマス方向に集束させて、中間データを生成することができる。さらなる送受信では、複数のセクションのデータを、仰角方向に集束させることができる。このプロセスにより、仰角方向におけるスライス厚みを改善することができる。いくつかの実施形態では、超音波パルスのアポダイゼーションの適用ことでそのようなプロセスを補助することができる。

30

#### 【 0 0 1 7 】

##### 特定の定義

特に定義されていない限り、本明細書で使用されるすべての専門用語、本発明特定事項が属する技術の通常の当業者によって一般に理解されるものと同じ意味を有する。

40

#### 【 0 0 1 8 】

本明細書で使用されるように、単数形「a」、「a n」、および「t h e」は、文脈が明確に指定していない限り、複数の基準を含む。「または」への任意の言及は、別段の定めがない限り、「および／または」を包含することを意図している。

#### 【 0 0 1 9 】

本明細書で使用されるように、「約」との用語は、その増分を含む、約10%、5%、または1%によって明示される量に近い量を指す。

#### 【 0 0 2 0 】

50

いくつかの実施形態では、本明細書の撮像装置（本明細書では「トランステューサ」と交換可能）は、Aスキャンとして知られている1Dイメージング、Bスキャンとして知られている2Dイメージング、1.5Dイメージング、1.75Dイメージング、3Dおよびドップラーイメージングを実行するために使用することができるが、これらの実行に限定されるものではない。さらに、本明細書中の撮像装置は、あらかじめプログラムされる様々なイメージングモードに切り替えることができる。さらに、本明細書のトランステューサを使用して2方向イメージングモードを実行してもよい。

#### 【0021】

いくつかの実施形態では、本明細書のトランステューサ素子（例えば、pMUT素子）は、トランシーバー素子、圧電素子およびピエゾ素子と交換可能である。いくつかの実施形態では、本明細書のトランステューサ素子は、基板、基板上にある膜、膜に配置される下部電極、下部電極に配置される圧電層、および、は圧電層に配置される1つ以上の上部電極、のうち1つ以上を含む。

#### 【0022】

図1は、本明細書に開示される超音波イメージングシステム（100）の例示的な実施形態を示す。この実施形態では、画像システムは、ポータブルデバイス（101）、ディスプレーユニット（112）を有するポータブルデバイス（101）、通信インターフェースによりネットワーク（120）との接続を可能とされるデータ記録ユニット（114）、および電子カルテなどの外部データベース（122）を含む。そのように外部データソースへの接続することで、医療費請求、データ交換、問い合わせ、または他の医療用関連情報通信が容易になる場合がある。この実施形態では、システム（100）は、超音波撮像装置アセンブリ（本明細書では「タイルアセンブリ」として交換可能）（108）を含む超音波撮像装置（本明細書では「プローブ」として交換可能）プローブ（126）を含み、ここで、超音波タイルは、基板上に作り上げられたpMUTアレイ（102）を有する。pMUTアレイ（102）は、電子制御ユニット、例えば、撮像装置上に位置する特定用途向け集積回路（ASIC）（106）および他の制御ユニット（110）の下で超音波の波形を放射し受け取るように構成される。

#### 【0023】

この特定の実施形態では、ディスプレーユニット（112）および/または、少なくとも電子通信制御ユニット（110）の一部は、アセンブリ（108）に位置され得る。いくつかの実施形態では、制御ユニット（110）のディスプレーまたは部分は、撮像装置の外部にあるが、超音波撮像装置アセンブリ（108）およびその内の素子と有線通信インターフェースおよび/または無線通信インターフェース（124）で接続され得る。いくつかの実施形態では、ディスプレー（112）は、ユーザ相互動作を単純化するために、入力装置、例えば、タッチスクリーン、ユーザフレンドリーなインターフェース、例えば、グラフィカルユーザインターフェース（GUI）を有してもよい。

#### 【0024】

同じ実施形態では、pMUTアレイ（102）は、別の基板に、およびpMUTアレイ（102）に近接して位置する特定用途向け集積回路（ASIC）（106）に結合される。アレイは、pMUTアレイ上に置かれることができる様々なインピーダンス材料および/またはインピーダンス整合材料（104）にも結合されてもよい。いくつかの実施形態では、撮像装置（126）は、再充電可能な電源（127）および/または外部電源との接続インターフェース（128）を含み、例えば、USB2またはUSB3などの他のUSB基準のシグナリングプロトコルと適合するUSB Power Deliveryインターフェースを使用する。いくつかの実施形態では、再充電方法はワイヤレスである。いくつかの実施形態では、撮像装置（126）は、スキャンをECGパルスと同期させるためにECG信号のための入力インターフェース（129）を含む。いくつかの実施形態では、撮像装置（126）は、ユーザガイダンスを支援するために慣性センサ（130）を備えている。

#### 【0025】

10

20

30

40

50

矢印(114)は、身体部分(116)およびボリュームエレメント(118)のイメージングを標的とする撮像装置アセンブリ(108)からの超音波送信ビームを示す。送信ビームは、イメージングされている標的によって反射され、矢印(114)によって示されるように撮像装置アセンブリ(108)に入る。ASIC(106)に加えて、イメージングシステム(100)は、他の電子制御、通信および計算の回路(110)を含み得る。超音波撮像装置(108)は、図1に示されるような1つの内蔵ユニットであり得、または、それは、電子制御ユニット(110)の一部などの物理的に別個だが電気的にまたは無線で接続された素子を含み得ることは理解されるであろう。この例は、図2に示される。

#### 【0026】

図2は、本開示の実施形態に係る撮像装置(126)の概略図を示す。図2に描かれるように、撮像装置(126)は、圧力波を送受信するためのトランシーバータイル(210a)と、圧力波の伝搬方向を導く、および/または圧力波を集束させるためのレンズとして作動する、またはトランシーバーアレイと人体との間のインピーダンスインターフェースとしても機能するコーティング層(212a)であって、レンズ(212)は、トランスデューサを出る、さらにトランスデューサに入る信号の減衰をさらに引き起こす場合があり、したがって、これを最小限に抑えることはさらに望ましく、仰角制御が電子の場合、このレンズは必要とされなくともよく、欠損が最小限のみである、薄い保護インピーダンス整合層のみと取り替えられることができる、コーティング層と、トランシーバータイル(210a)を制御するために突起によってトランシーバータイル(210a)に連結したASICチップ(または、短縮してASIC)などの制御ユニット(202a)と、を含んでもよい。それに接続されたASICを有するトランシーバーアレイの組み合わせは、タイルと呼ばれる。撮像装置(126)の成分を制御するためのフィールドプログラマブルゲートアレイ(FPGA)(214a)、信号の処理/コンディショニングのためのアナログ・フロント・エンド(AFE)などの回路(215a)、トランシーバータイル(210a)によって生成され、回路(215a)の方へ伝搬する波を吸収するための音響吸収層(203)と、ある実施形態では、音響吸収層はトランスデューサとASICの間に位置し、ある実施形態では、これらの音響吸収層は不要であり、1つ以上のポート(216a)を通じて装置(101)等の外部装置とデータを通信するための通信ユニット(208a)と、データを記憶するためのメモリ(218a)と、撮像装置の構成部分に電力を供給するためのバッテリー(206a)と、そして随意に、標的器官の画像を表示するためのディスプレイ(217a)と、を備えていてもよい。

#### 【0027】

作動中に、ユーザは、インターフェース材料(104)に覆われるpMUT(102)表面に、超音波がイメージングされる標的(118)の方へ送信される身体部分領域と接触させてもよい。撮像装置は、イメージング標的から反射された超音波ビームを受信し、それらを処理し、または画像処理および/または再構成のために外部処理装置に、およびその後、画像を表示するためにポータブルデバイス(101)に送信する。他のデータも、収集され、計算され、引き出されがあり、およびユーザにディスプレー上に表示されてもよい。

#### 【0028】

図1は、画像プローブ(本明細書にトランスデューサとして交換可能)(126)を含む本明細書のポータブルな超音波イメージングシステム(100)の例示的な実施形態を示す。プローブは、電子ユニット、例えば、図2の制御ユニット(202a)に接続されるpMUT撮像装置アセンブリ(108)を含んでもよい。プローブ(102)は、通信インターフェースおよび手段(124)を使用して、外部ディスプレーユニット(204)と通信する。

#### 【0029】

この通信手段は、ケーブルまたは無線接続になり得る。有線接続部のために、USB2、ライトニングおよびその他などのデータ交換のためのプロトコルの多くが使用され得る

10

20

30

40

50

。同様に、無線通信のために、802.11または他のプロトコルなどの一般的に使用されるプロトコルが使用され得る。同様に、データ記録ユニット(114)は、さらにプローブの外部に存在し得、無線通信または有線通信手段を使用して、プローブ(126)とさらに通信し得る。

#### 【0030】

撮像装置を使用するとき、例えば、ヒトまたは動物の身体部分をイメージングするため、送信された超音波波形は標的へと方向付けられる。身体との接触は、一般的にゲルが身体に適用され、および撮像装置がゲル上に置かれた後で撮像装置を身体の隣接に抱えることによって達成され、それは、超音波の優れたインターフェースが身体に入るため放電され、および超音波の波形が撮像装置を再び入れるために標的から反射されることを可能にし、反射された信号は、身体部分の画像を作成するために使用され、および結果は、様々なフォーマットの身体部分の画像を有して、またはその画像なしで示されるグラフ、プロット、統計を含んでスクリーンに表示される。

10

#### 【0031】

プローブ(126)は、物理的に分離して、かつケーブルを通じて、または無線で接続される特定の部分を有して開発され得ることが注目されるべきである。例として、この特定の実施形態では、pMUT集合体とASICと制御および通信関連のエレクトロニクスは、しばしばプローブと呼ばれるユニット中に存在することができた。身体部分と接触する装置の部分またはプローブは、pMUT集合体を含有する。

20

#### 【0032】

図3Aは、従来の圧電素子(214)の概略図の断面を示す。この実施形態では、圧電素子は、2つの電極を有しており、第1の電極(216)は、信号伝導体(215)に接続され、および第2の電極(218)は、第2の伝導体(217)に接続され、共通的に接地または他の直流電位に接続され得る。

#### 【0033】

圧電素子は、超音医療医用イメージングのために数十年間使用されている。しかしながら、圧電素子は、例えば、約 $100\mu\text{m}$ に接近して、厚くなり得、典型的に医療用イメージングを可能にする十分な強度の超音波の圧力波を作成するために、+100V~-100Vの交流(AC)がそれを横切って駆動することを必要とする場合がある。このAC駆動信号の周波数は、圧電気構造の共振周波数のまわりであってもよく、医療用イメージング適用のために1MHz以上であり得る。

30

#### 【0034】

いくつかの実施形態では、圧電素子を駆動中に消散された電力は、 $C \cdot V^2$ に比例し、ここで、Cがピエゾ素子の静電容量であり、Vが圧電層にわたる最大電圧である。送信するとき、多数の圧電素子は、ビームを集束させるまたはビームを導くために、多少異なる遅延とともに駆動され得る。多数の素子の同時駆動は、素子の表面で温度を上昇させる場合がある。イメージングされている被験体を傷つけないために、閾値温度を超過しないことが非常に望ましいまたは要求される。したがって、この閾値温度は、駆動され得る素子の数、およびそれらが駆動され得る期間を制限する。

40

#### 【0035】

本明細書に開示される、いくつかの実施形態では、圧電素子は、従来のバルクピエゾ素子の $100\mu\text{m}$ 厚さと比較して、大分薄く、典型的には $5\mu\text{m}$ またはそれ以下の厚さである。そのような厚さの大規模な減少は、従来の素子と同様の電界の強さを維持するために圧電素子に低電圧駆動信号の使用を可能にし得る。例えば、本明細書に開示される圧電素子は、ピークとピークの間の約5V~40V電圧を駆動してもよい。

#### 【0036】

ピエゾ素子の静電容量は、特定の圧電材料の厚さの縮小によって増大させられる場合がある。したがって、例として、 $\times 10$ 倍薄いフィルムを駆動する際に、駆動電圧が100Vから10Vになると、静電容量は、より薄い圧電材料には $\times 10$ 倍に増大し得、電力消散は10の因数で減少され得る。この電力消散の減少は、さらにイメージングプローブ中

50

の発熱および温度上昇を低減することができる。したがって、より低い駆動電圧を使用すると、p M U T 表面の温度は低下され得る。

#### 【 0 0 3 7 】

いくつかの実施形態では、所与の温度には、低電圧 p M U T を使用する場合、より多くの p M U T 素子がより大きな領域を照らすために駆動され得る。これは、特に画像を形成するために全体の標的をスキャンするために複数の放射が必要な場合、標的をより速くスキャンすることを可能にする。しばしば、標的領域は、様々な操縦角を使用して、複数の放射でスキャンされてもよく、および画像データは、より高い画質を取得するために組み合わせられる。

#### 【 0 0 3 8 】

高いフレームレートでイメージングすることも望ましい場合がある。フレームレートは、標的が 1 分当たり何回イメージングされるか測定する。画像ぶれなしで標的が移動していることを観察するために、組織運動が関与されている場合、高いフレームレートでイメージングすることは望ましい。いくつかの実施形態では、より多くの圧電素子を駆動する性能は、1 つの放射当たりのトランステューサアーチャのより多くの適用範囲を可能にし得、それによって全体アーチャをカバーするために必要とされる放射数を最小限に抑えられ、したがって、フレームレートを増大させられる。

#### 【 0 0 3 9 】

いくつかの実施形態では、画質は、複数の画像フレームを、結果として生じた 1 つのより低いノイズのフレームへと混成することによって改善され得る。しかしながら、これはフレームレートを減少し得る。従来のピエゾフィルムのフレームレートと比較して、より高いフレームレートの低電力の p M U T を使用する場合、p M U T 温度の所与の上昇には、この平均法は、より低い電力を有する低電圧 p M U T のために使用することができ、したがって、本質的により高い開始フレームレートを可能にする。いくつかの実施形態では、超音波イメージングの開口合成法は、画像の混成を可能にするために使用され得る。

#### 【 0 0 4 0 】

いくつかの実施形態では、一度により多くの圧電素子を駆動する性能は、信号対ノイズ比 ( S N R ) を改善し、再構成像のより良い画質を可能にする。

#### 【 0 0 4 1 】

さらに、図 1 に示されるように、A S I C ( 1 0 6 ) は、p M U T ( 1 0 2 ) に結合される。A S I C は低ノイズ増幅器 ( L N A ) を含み得る。p M U T は、スイッチを通して受信モードにおける L N A に接続される。L N A は、反射された超音波ビームが p M U T に対する発揮する圧力によって生成された p M U T での電荷を、低ノイズの増幅された電圧信号に変換する。受信信号の信号対ノイズ比は、再構成されている画像の画質を決定する主要因の一つであり得る。したがって、L N A 自体における本来の雑音を減少させることは望ましい。これは、L N A の入力段階の相互コンダクタンスを増大させることによって達成することができる。これは、例えば、入力段階でより多くの電流を使用することによって達成することができる。より多くの電流は、電力消費および熱の増強を引き起こし得る。しかしながら、隣接中の A S I C では、低電圧 p M U T が使用される場合、低電圧 p M U T によって節約された電力は、高電圧で作動しているトランステューサと比較された時許容できる所与の合計温度上昇に L N A における雑音を低下させるために利用することができる。

#### 【 0 0 4 2 】

図 3 B は、本明細書に開示される p M U T 素子 ( 2 2 0 ) の概略図を示す。この実施形態では、p M U T 素子 ( 2 2 0 ) は、2 つのサブ素子 ( 2 2 0 a )、( 2 2 0 b ) を含む。いくつかの実施形態では、各 p M U T 素子は、それぞれ 1 つ以上のサブ素子を含む。各サブ素子は、この実施形態では、第 1 の伝導体 ( 2 2 2 ) に接続された第 1 の電極 ( 2 2 3 )、および第 2 の伝導体 ( 2 2 7 ) に接続された第 2 の電極 ( 2 2 5 )、および第 3 の伝導体 ( 2 2 6 ) に接続された第 3 の電極 ( 2 2 4 ) を有する圧電層 ( 2 2 1 ) を有しており、すべてのサブ素子の第 1 の伝導体はともに接続され、およびすべてのサブ素子の第

10

20

30

40

50

2の伝導体はともに結ばれたコネクタであり、およびすべてのサブ素子のすべての第3の伝導体はともに接続される。

【0043】

ある実施形態では、pMUT素子(220)は、各pMUT素子が2つの端子を有する2つのサブ素子(220a)、(220b)を含む。例えば、(220a)は、第1の伝導体(222)に接続された第1の電極(223)、および第2の端子(227)に接続された第2の電極(225)を有しており、および(220b)は、第1の伝導体(222)に接続された第1の電極(223)、および第2の端子(227)に接続された第2の電極(225)を有する。

【0044】

ある実施形態では、各pMUT素子が2つの端子が有する、pMUT素子(220)は1つのサブ素子(220a)を含む。例えば、(220a)は、第1の伝導体(222)に接続された第1の電極(223)、および第2の端子(227)に接続された第2の電極(225)を有する。

【0045】

いくつかの実施形態では、サブ素子(220a)は、複数のサブ素子を有し得、サブ素子は2つの電極を有し、すべての第1の電極は、第1の伝導体に接続され、すべての第2の電極は、第2の伝導体に接続される。

【0046】

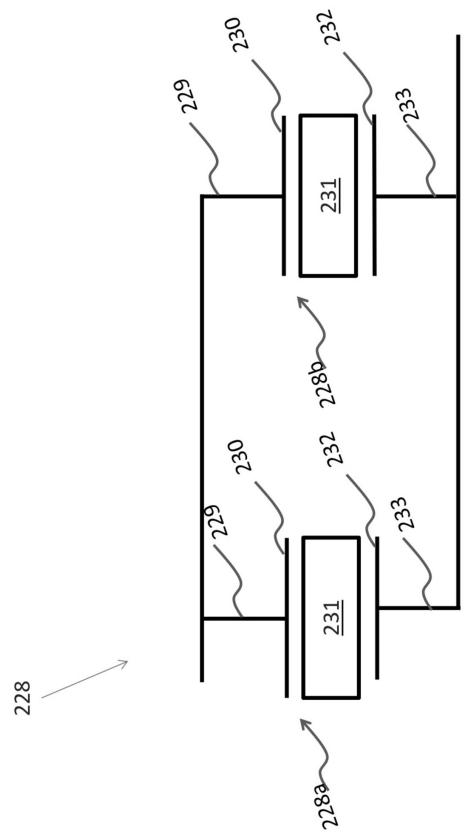

図3Cは、2つのサブ素子(228a)、(228b)を有するpMUT素子(228)の概略図である。いくつかの実施形態では、各pMUT素子は、1つ以上のサブ素子を含む。各サブ素子は、この実施形態では、第1の伝導体(229)に接続された第1の電極(230)、および、第2の伝導体(233)に接続された第2の電極(232)を有する圧電層(231)を有しており、ここで、すべてのサブ素子の第1の伝導体はともに接続され、およびすべてのサブ素子の第2の伝導体がともに結ばれたコネクタである。

【0047】

いくつかの実施形態では、サブ素子(228a)、(228b)は、複数のサブ素子を有することができ、素子に2つのサブ素子がある場合、各サブ素子は2つの電極を有しており、第1のサブ素子の第1の電極は、伝導体を有する第2のサブ素子の別の電極に接続され、および第1のサブ素子の第2の電極は、第2のサブ素子の残りの電極に接続される。

【0048】

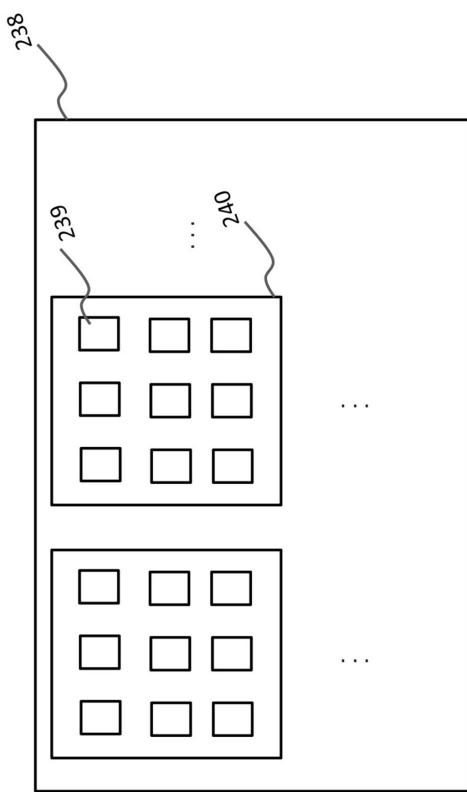

図4は、複数の圧電マイクロマシン超音波トランステューサ(pMUT)アレイ素子(239)が、その上で配置される基板(238)を示す。この実施形態では、1つ以上のアレイ素子は、トランシーバーアレイ(240)を形成し、および1より多くのトランシーバーアレイは、基板(238)上に含まれる。

【0049】

従来のトランステューサアレイは、個々のピエゾ素子を形成するために、圧電材料、例えば、バルクPZTのブロックをダイシングすることによって形成されたジルコン酸チタン酸鉛(PZT)を使用する。これらは、高価になりがちである。これに対して、本明細書に開示されるpMUTアレイは、基板(例えば、ウエハ)上で配置される。ウエハは、様々な形状および/またはサイズであり得る。例として、本明細書のウエハは、集積回路の構築のために使用される半導体プロセスでのウエハのサイズおよび形状になり得る。そのようなウエハは、高い容量、および低コストで产生することができる。例示的なウエハサイズは、直径6、8および12インチである。

【0050】

いくつかの実施形態では、多数のpMUTアレイが低コストでバッチ製造され得る。さらに、集積回路は、典型的に、pMUTと通信するために必要とされる接続が、互いに整列させるように、およびpMUTアレイ(図1の102)が、整合集積回路(106)に隣接で、典型的に垂直に下、または例えば、約25μm~100μmの距離でアレイに隣接して接続することができるよう、寸法を有するために設計され得る。いくつかの実施

10

20

30

40

50

形態では、図 1 に示されるように、102、104 と 106 との組み合わせは、画像化アセンブリ (108) またはタイルとして参照される。例えば、アセンブリ (108) の 1 つの例示的な実施形態は、1024 の圧電素子のために送受信機能の適切な数を有する整合 ASIC に接続される、1024 の pMUT 素子を有してもよい。いくつかの実施形態では、アレイサイズは 1024 に制限されていない。それは更に小さく、または更に大きくなり得る。pMUT 素子のより大きなサイズは、複数の整合 ASIC (106) に加えて、複数の pMUT アレイ (102) を使用し、それらを互いに隣接して組み立て、およびそれらをインピーダンス整合材料 (104) の適切な量でカバーすることによって達成することができる。交互に、単一のアレイは、pMUT 素子の数が 1000 未満 ~ 10,000 に範囲内にある、長方形アレイまたは他の形状に配置される pMUT 素子の多数を有し得る。pMUT アレイおよび複数の pMUT 素子は、整合 ASIC に接続され得る。

#### 【0051】

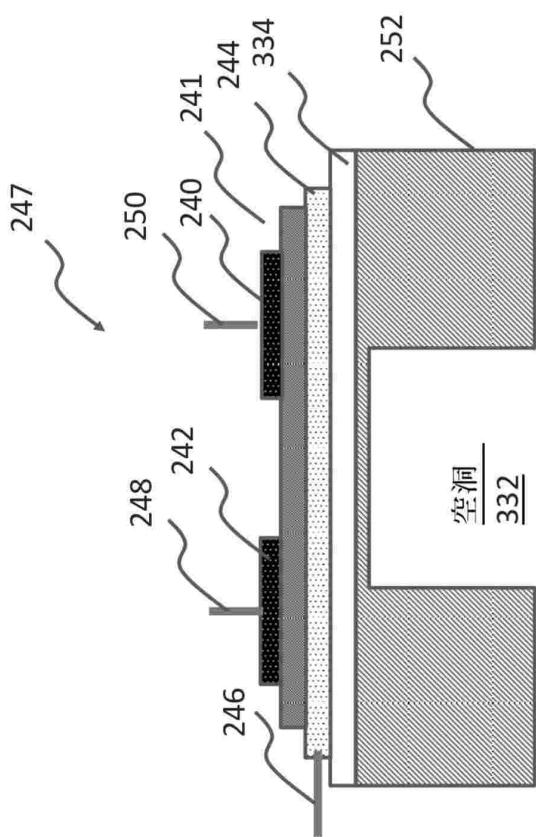

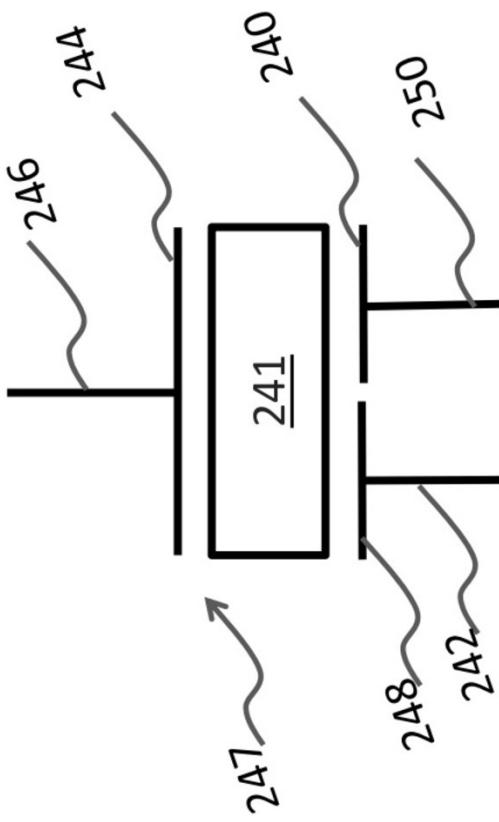

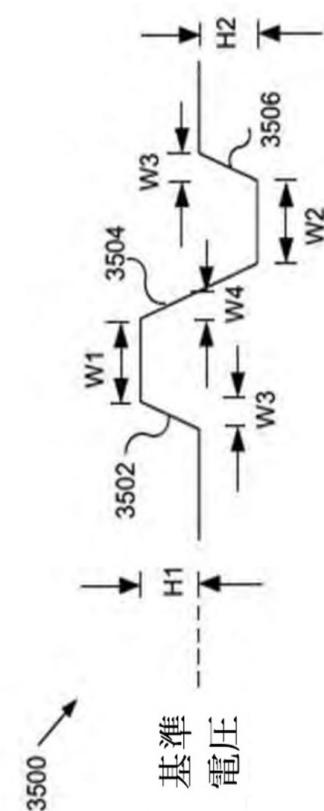

図 5A は、圧電素子 (247) の例示的な実施形態の断面図を示す。この実施形態では、素子 (247) は、基板 (252) に配置される薄い圧電フィルム (241) を有する。圧電フィルムは、信号伝導体 (246) に接続される、第 1 の電極 (244) を有する。この電極は、典型的に SiO<sub>2</sub> が成長する基板に配置される。PZT が跳ね飛ばされる、または、PZT ゾルゲルが適用される、プラチナが後に配置される TiO<sub>2</sub> の層は、圧電フィルム (241) として PZT の薄層を発達させる。これおよび第 1 の金属電極は、所望の形状に腐食動作によってパターン化される。信号伝導体 (246) は、第 1 の電極に接続される。第 2 の電極 (240) は、薄フィルム (241) 上に成長し、第 2 の伝導体 (250) に接続される。第 3 の電極 (242) は、第 2 の電極に隣接しているが、電気的に単離されるように成長させられる。第 3 の伝導体 (248) は、第 3 の電極に接続される。示された電極の実際のレイアウトは、電極が別のものを囲む、正方形から長方形、橢円その他の隣接電極、または環状電極に変動することができる。圧電フィルムは、様々な形状を有し得、基板および空洞上である部分で存在し得る。

#### 【0052】

図 5B は、図 5A の圧電素子の象徴的表示である。いくつかの実施形態では、第 1 の伝導体 (246) は、第 1 の電極 (244) に電気的に接続される。そのような接続は、金属、ピア、層間絶縁膜 (ILD) を使用してもよく、それらは簡潔性のために示されない。第 1 の電極は、圧電層 (241) と接する。第 2 の伝導体は、第 1 の電極に関して、圧電層の反対側に堆積させられる、または成長させられる。第 2 の電極 (248) は、第 2 の伝導体 (242) に接続される。第 3 の電極 (240) は、電極 (248) に隣接して位置し、第 3 の伝導体 (250) がそれに接続する。第 1 の電極 (244) は、「O」電極としても呼ばれる。第 2 の電極は、「X」の電極と呼ばれ、第 3 の電極は「T」電極と呼ばれる。簡易性のために、ピア、層間絶縁膜 (ILD) および他の金属層の使用などの電極に導体を接続する接続手段は、すべての図で示されない、または詳細に説明されないことが理解されるであろう。これらの詳細は、最先端技術に熟達したものに公知である。さらに、根本的な膜を示すことなどの他の詳細は示されない。

#### 【0053】

PZT の結晶構造の非相称のため、電気的分極性が電気双極子を作成して発達する。巨視的結晶構造では、双極子は、図 6 の左側に示されるように、デフォルトでランダムに配向されると認められる。材料が機械的ストレスにさらされるとき、各双極子は、その本来の配向から双極子に蓄積された全体的な電気的および力学的エネルギーを最小限に抑える方向へと回転することができる。すべての双極子が最初にランダムに配向される（すなわち、零点のネット分極）場合、それらの回転は、材料の巨視的ネット分極を大幅に変更することなく、従って、示された圧電効果は無視可能であり得る。したがって、ほとんどの双極子が多少同じ方向に配向され得るように、材料における初期状態を作成することは重要である。そのような初期状態は、材料を分極することによって材料に与えることができる。双極子が整列する方向は、分極方向として知られる。分極中の、および分極の後の双極子の配向は、図 6（中間パネルと右パネル）に示される。

10

20

30

40

50

## 【0054】

したがって、圧電の薄フィルムは、使用される前に最初に分極される必要があるかもしれない。これは、典型的に高温（例えば、175°C）で暫くの間（例えば、1-2分以上）フィルムにわたって高電圧をかけることによって行うことができる。図3のピエゾ素子では、pMUTは、2つの端子を備えて構築することができ、高電圧は、例えば、(216)と(218)にわたってかけることができる。この高電圧は、1μmの厚さのピエゾフィルム用に約15Vであり得る。そのような電圧は、分極に十分である。

## 【0055】

典型的に従来pMUTまたはバルクPZTからの他のピエゾ素子は2つの電極を有する。本明細書に開示されるように、圧電素子は2つ（図3において）、または図5Aおよび図5Bに示されるように、2つ以上の電極を有してもよい。図5Aおよび図5Bでは、分極中に第1の伝導体は、接地電位に結び付けられることができる一方、第2の伝導体は、負電位に、1μmの厚さのPZT膜のために-15Vと言い、結び付けられ、および第3の電極は+15Vで高温でしばらくの間結び付けられる。これは、PZT膜にわたって、第1と第2の伝導体間のフィルム対第1と第3の伝導体間のピエゾフィルムのために反対の2つの分極方向を作成することができる。分極が完了した後、送信または受信作動中に、第2および第3の伝導体は、接地またはバイアス電圧に接続され得る一方、第1の伝導体は、送信作動中に送信ドライバによって駆動されるためにASICに接続されるか、または受信作動中にスイッチを通してLNAに接続される。第2および第3の伝導体は、0でないDCバイアスに結び付けることができ、バイアス値は異なることができる。

10

## 【0056】

例示的な実施形態での圧電素子は、横歪を利用し、それによって膜の動作を作成する、または膜の動作を電荷に変換するためにPZT横歪定数d31、圧電率、を利用する。送信作動中でフィルムへの直交分極方向を有する図5Aおよび図5BのPZT素子は、図3Aおよび図3Cで示されるフィルムのために唯一の分極方向を有する構造と比較して、所与の駆動には膜の動作を増幅させる。したがって、送信感度は、改善され得、適用された送信駆動の1ボルト当たり膜のより大きな動作を可能にする。

20

## 【0057】

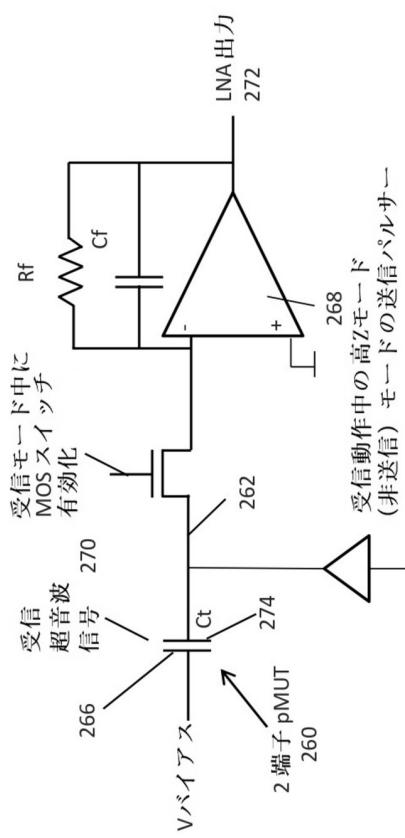

受信モードでは、直交分極方向は、LNAによってより多くの電荷が感知される状況を作成してもよい。LNA接続は、図7に象徴的に示される。LNAにピエゾ素子を接続する経路中のすべての素子は、簡易さのために示されるとは限らない。圧電素子(260)は、ある実施形態では、伝導体(262)によって接続されるLNA(268)連続してスイッチに接続される第1の電極を有する。(260)の第2の電極は、(266)であり、0V(接地)を含むDCバイアスに接続されてもよい。(270)は、pMUT素子(260)を突き当り、および電極(266)と(274)をわたって電荷を作成する、反射された超音波ビームを表わす。LNAは、電圧または電荷モードで作動するために設計され得ることが注目されるべきである。pMUTは、大きな静電容量を有する傾向があり得、電荷の所定量のために、トランスデューサ上で電圧が増幅される場合、電圧感知が使用されると、トランスデューサにわたって、はるかに小さな静電容量を有するPZTバルク素子のためよりも低電圧を作成する。LNAの入力での電圧が小さいので、出力はより騒々しい。電荷増幅は、特にpMUTが受信モードにおける所与の入力圧力のためにより多くの電荷出力を生成する時、電圧モード作動と比較して、pMUT素子の高容量のため、LNAの出力で改善した信号対ノイズ比を提供することができる。これは、Ctによって受信された任意の電荷は、はるかに小さなキャパシターCfにわたって転送され、LNAの出力でより大きな電圧を作成することが、図7に説明される。これらのLNAは、それらが迅速に（例えば、1μsec未満で）電力を上げるまたは電力を落とすように、設計することができる。

30

## 【0058】

従来の2Dイメージングは、高い長方形形状で設計されている素子の列を使用して行われる。交互に、これは列で配置された多くのより小さな素子を使用することによって達成

40

50

され得る。個々のアレイ素子は、列を作るために、単一のより大きな 1 D アレイ素子として動作するために組み合わせられ得る。これは、1 つの信号伝導体および共通接地伝導体を有するより大きな素子を作成するために、これらの個々の素子を配線で接続することによって達成される。駆動を送信する、感知と制御を受信することは、この1 つの組み合わせられるより大きな2 リードの p M U T のために実施される。

#### 【 0 0 5 9 】

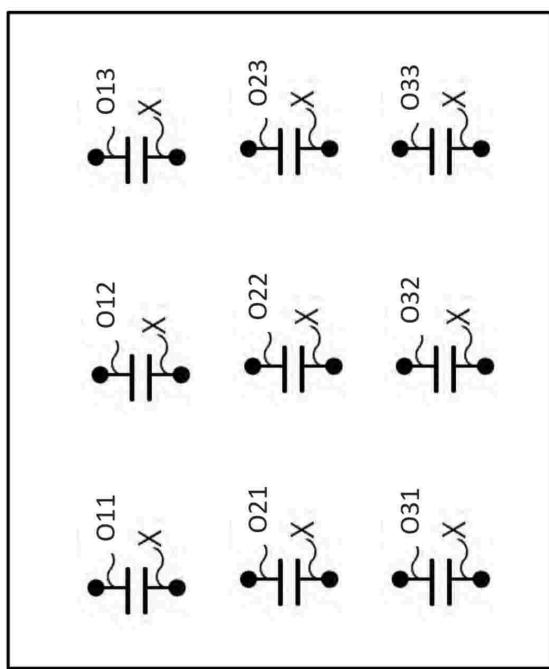

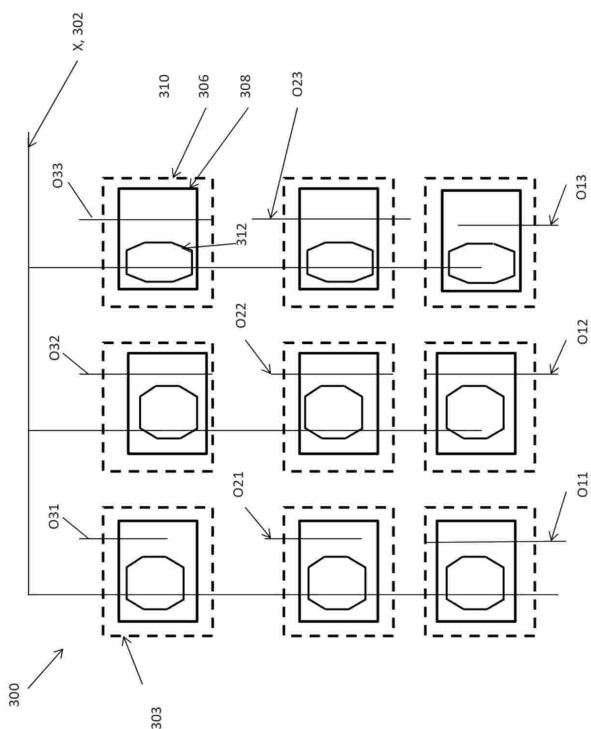

図 8 A は、本明細書のトランステューサの超音波イメージングアレイ ( 3 0 0 ) の例示的な実施形態の概略図を示す。アレイは、実例の目的で3 つの行と3 つの列、または3 対3 に配置される、9 つの p M U T 素子を有して示される。実際上、アレイサイズが、より大きなまたはより小さな様々なサイズになりえることは理解されるであろう。サイズの非限定的な例は、3 2 対3 2 、3 2 対6 4 、3 2 対1 9 4 、1 2 対1 2 8 、2 4 対1 2 8 、3 2 対1 2 8 、6 4 対1 2 8 、6 4 対3 2 、6 4 対1 9 4 を ( 列対行または行対裂 ) を含む。

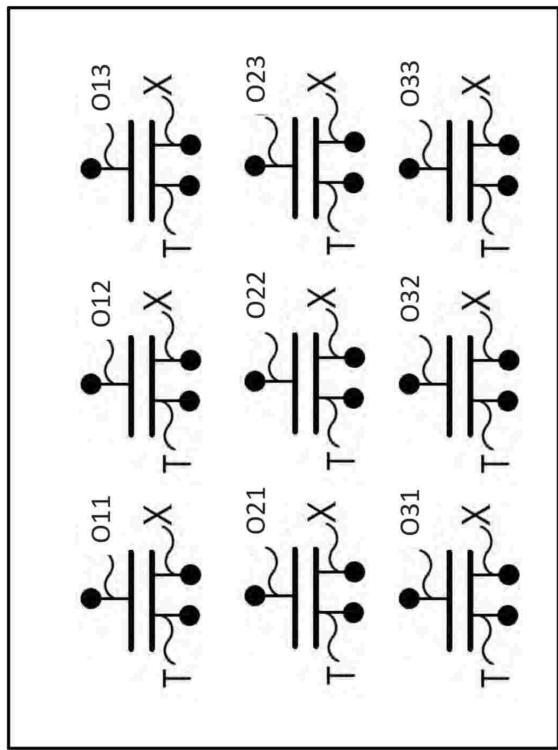

#### 【 0 0 6 0 】

図 5 B で使用されるような象徴的表示は、ここでこの p M U T のアレイに使用される。各圧電素子の伝導体は、図 8 B で電極に接続され、O x y と指名され、x が1 ~ 3 の範囲内であり、y が1 ~ 3 の範囲内である。各圧電素子の第1 の伝導体は、第1 の電極に接続され、O 1 1 と指名される。さらに、電子的に設定可能な撮像装置のためのすべての素子は、別のウエハに位置する対応するエレクトロニクスに接続されるそれらのリードを有する。X と呼ばれる各素子の第2 の電極はすべて、伝導体 ( 3 0 2 ) によって他の素子のための他のX 電極に接続される。伝導体O は、信号伝導体である一方、X は接地またはバイアスの線である。図 8 B で示されるこの実施形態では、O 電極は、p M U T が配置される基板に近接で A S I C に接続される。3 2 対3 2 の p M U T のアレイがある例示的な場合では、1 0 2 4 のピエゾ素子がある。p M U T ダイス以下に典型的に位置した A S I C への1 0 2 4 の「O 」鉛接続部がある場合がある。これらの1 0 2 4 O 線の各々は、送信作動中に送信ドライバに、および受信作動中に L N A の入力に接続され、送信ドライバは受信モードにおけるハイインピーダンス状態になる。

#### 【 0 0 6 1 】

図 9 は、3 × 3 素子を備えるトランステューサアレイの例示的な実施形態を示し、各素子は、3 つのリード / ノード、すなわち、O 、X 、T を有する。O ノードは、O x y として示され、x は1 ~ 3 の範囲内であり、およびY は1 ~ 3 範囲内である。これらのO ノードは、A S I C でエレクトロニクスを駆動し感知するために接続され得、ここで、X ノードは、バイアス電源または接地にともに接続され得、およびT ノードは、別のバイアス電源または接地にともに接続され得る。

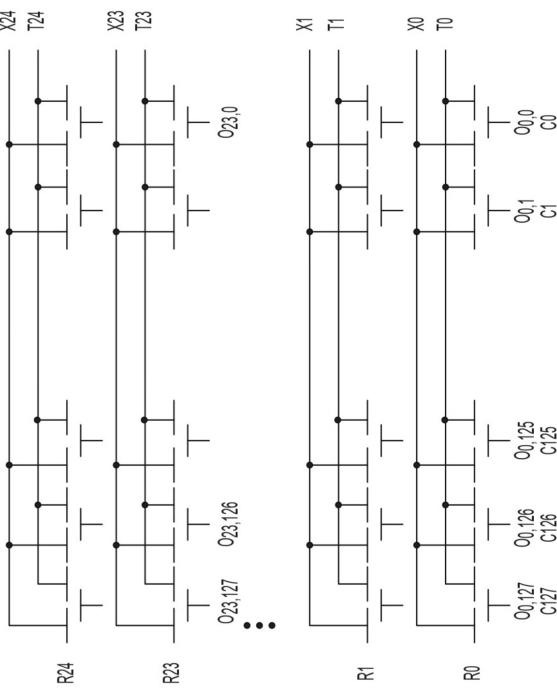

#### 【 0 0 6 2 】

図 10 A は、各 p M U T 素子が3 つの端子を有する例示的な p M U T アレイを示す。この実施形態では、アレイは、2 4 行を有し、各行は、1 2 8 の素子から構成される。同様に、同じ実施形態では、各列は、2 4 の素子から構成され得、すべての素子は、O 、X とT という名の3 つの端子を有し得る。例えば、低左角の素子のO 電極は、O 0 , 1 2 7 と標識される。この素子は、2 つの他の電極、すなわちX とT を有し得る。行上のすべての素子は、伝導体 X 0 に接続され得、すべてのT 端子は、T 0 に接続され得る、と注目されるであろう。分極作動中に、すべてのO 端子は、0 V に接続されることができ、すべてのX 端子は、負電位 - V 0 に接続されることができ、および、すべてのT 端子は、陽電位 + V 0 に接続されることができる。次の行のために、行1 の電位は、最大電圧が電圧 V 1 1 、- V 1 1 で行 R 1 1 に適用されるまでに、X 1 により高い - V 1 、およびT 1 により高い + V 1 になり得る。行の上部半分の電圧は、下部半分に対称的になり得る。これらのバイアス条件下では、回路は、約1 7 5 C の高温で分極されてもよい。図 10 B は、イメージング使用のための分極の後、すべてのX 端子は、ともに接続され、バイアス電圧に接続されてもよく、さらにすべてのT 端子のためにも同様であることを示す。X とT のためのバイアス電圧は異なり得ることに注目されるであろう。本構成では、列に沿った差別的な分

10

20

30

40

50

極のため、アポダイゼーションは、サイドロープ漏出が仰角面で最小限に抑えられ手も多い、仰角方向に達成することができる。いくつかの実施形態では、トランステューサアレイは、さらに素子当たり2つの端子のみを含み得る、例えば、X端子とO端子、T端子は使用されない場合がある。

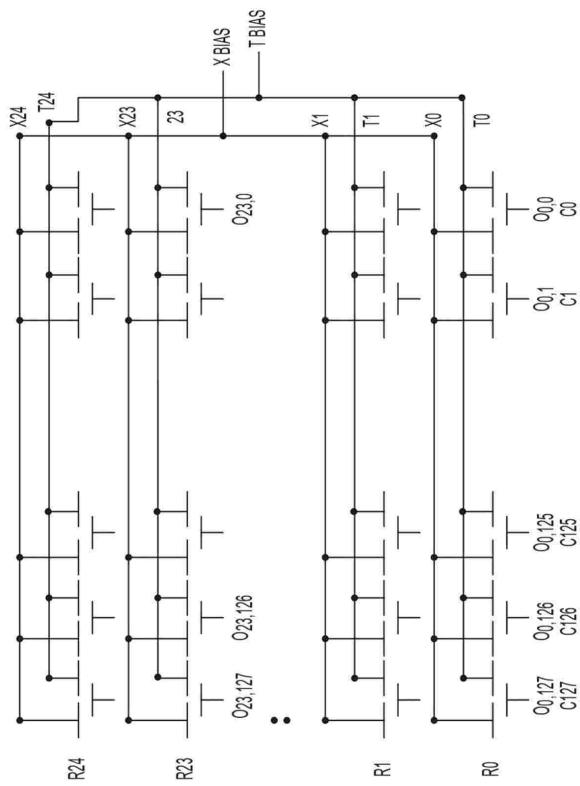

#### 【0063】

図11Aは、2つのトランステューサ素子のASIC(500)への相互連結の略図である。ある実施形態では、2つのトランステューサ素子(502)は、1つの基板(504)上に存在し、送受信および他の機能を含む別の基板(512)上のASICにある。LNA(516)の入力は、それをトランステューサの信号の伝導体に接続するリード(510)、Oリードにスイッチ(514)によって接続される。いくつかの実施形態では、バイアス伝導体(506)は、ASICへと接続され、後で接地または他のバイアス電圧に接続するためにASICから出て来る。これらはトランステューサのXリードであり、トランステューサおよびASICで他のXリードとともに接続されてもよい。(520)によって示されるように、送信ドライバ(518)は、基板(512)上でASICの外部の通信によって制御される場合がある。さらに、それは、送信モードにおけるスイッチ接続を示す、スイッチ(514)に接続される場合がある。図11Aを示されるように、LNAの出力および送信ドライバの入力は、2つの異なるリードを必要とする場合がある。(514)に類似するマルチプレクサースイッチの使用によって、1つのリードを使用することは可能である。いくつかの実施形態では、LNA出力への接続は、受信モードにおける外部のエレクトロニクスに提供され得、送信ドライバへの入力は送信モードで提供され得る。

10

20

#### 【0064】

図11Bは、エレクトロニクスの1列のASICにおける機能のうちのいくつかの略図を示す。機能的に、エレクトロニクスの1列は、混成のより大きな線素子に構成するためには、pMUTの1列へ直接接続してもよい。ASICが、他の行または列のための回路を含んでもよく、示されていない他のサポート回路を含んでもよいことは理解されるであろう。最先端技術に熟知している当業者にとって明白であると考えられる、異なる回路トポロジーで望まれる実際の機能を達成することはさらに理解されるであろう。示された描写は、単に観念自体を説明することである。

30

#### 【0065】

図11Bは、ASIC(600)の1列の例示的な概略図を示す。ある実施形態では、伝導体(608)は、図8A-8Bの、O31のpMUTアレイでの素子のための対応信号伝導体に接続される。同様に、図8A-8BのO21は、図11Bの(628)に接続される。送信ドライバ(606)は、図11Bの伝導体(608)に接続され得る。このドライバ606はその入力にスイッチ602を接続することがあり、616(線素子のための信号の伝導体)をリードするために接続する、それは他のものの入力に接続する、その列上のスイッチを通してその列のドライバを送信する。スイッチは、制御ユニット(624)によって制御され得、制御ユニットは、どのスイッチを付けるべきか外部制御装置との通信によって決定してもよい。信号伝導体(616)は、さらにエレクトロニクスに接続し、送信ビームフォーマーを実行する場合がある。O伝導体(608)は、さらにスイッチ(604)に接続され得、スイッチ(604)の反対側は、その列(例えば、(622))の同様のスイッチに接続する場合がある。線(614)は、低ノイズ増幅器(LNA)(618)の入力に接続する場合がある。各線素子(または列)のために、1つのLNAのみが必要とされる場合がある。LNAは、受信モードにおける制御ユニット(624)によって活性化され得、該制御ユニットは、他のスイッチ(例えば、(602))を止める際に、さらにスイッチ(例えば、(604))を付ける。これは、pMUTの信号電極を(接続(608)を通して)LNAに接続する場合があり、LNAは、受信される信号を増幅し、低付加雑音を有する電圧出力(620)へ変換する場合がある。受信モードにおける、制御装置は、送信ドライバを、受信信号を妨げないように、それらの出力インピーダンスが非常に高くなる無効モードにさらに行かせる場合がある。送信モードに

40

50

おける、ピエゾ素子が送信することになっていないとき、スイッチ (610) は、正味 0 ボルトが、送信モード中に信号を送信することになっていない素子のために pMUT 信号とバイアス電極にわたって駆動することを確保するために、スイッチ (602) および (604) が止めた状態で、付けられ得る。X 線も ASIC に接続される。図 8A - 8B では、1 つのみのバイアス電極 X が示されることに注目されるべきである。しかし、複数のバイアス電極は存在し得る。例えば、図 9 は、X および T の 2 つのバイアス電極での実施を示す。原則として、全アレイには、T および X の電極に接続するために 2 つの接続のみが必要であるが、高品質イメージングを達成するためにさらに多くのを有することは望ましい。ASIC と pMUT と間の T および X のための接続数を増大させることは、接地またはバイアス源と平行して接続されるとき、X および T の伝導体におけるインピーダンスを減少させ、それは、クロストークを減少させる。クロストークは、干渉および画質低下を引き起こす、イメージング素子から別の素子まで信号の結合である。偽の電気的結合は、X および T の線で流れる電流に起因していずれかの電圧降下が、その電圧に理想的にさらされるべきでないピエゾ素子にわたって現われるとときに引き起こされ得る。ピエゾ素子が電子制御下で送信していないまたは受信していないとき、X、T および O 電極は局部的に短絡される。

#### 【0066】

簡単性のため、図 11B は、2 つのバイアス伝導体のうちの 1 つ（図 8A および 8B の X）のみとの接続を示す。しかし、X および T 端子の両方を接続するための手段が、図 9 に示されるものと類似の pMUT アレイを支持するために、さらに存在することは理解されるであろう。

#### 【0067】

いくつかの実施形態では、図 11B の伝導体 (612) は、図 8B の (302)、X に接続され得る。いくつかの実施形態では、図 11B の伝導体 (613) も、X (302) に、ただし (613) に近い位置で、接続され得る。これらの追加相互連結 (613) および (615) は、不可欠ではない一方、少なくとも 1 つの接続 ((612)、(613) または (615) のいずれか) が必要であることに注目して頂きたい。図 11B は、図 9 の T 電極に接続するために必要とされる回路も示さない。必要とされる回路は、X 電極への接続のために使用されるものに類似し得る。

#### 【0068】

図 11B は、受信出力 (620) および送信入力 (616) が、2 つのリードを必要とし得ることを示す。しかし、マルチプレクサを使用すると、1 つのリードもこの目的に使用され得る。

#### 【0069】

本明細書の線撮像装置は、複数のピエゾ素子列を含んでもよく、各列は、少なくとも信号およびバイアスリードによって制御装置に接続される。適切な周波数のパルスは、線を駆動する。他の線は、このパルスの遅延されたバージョンで駆動される。特定の線のための遅延の量は、ビームフォーミングとして知られている作動で、結果として生じた送信されたビームを角度で操縦されるか、または特定の深さで集束されるように可能にするものである。

#### 【0070】

図 8 および図 9 の線撮像装置は、電子的に設定可能である。1 つの方向に 24 の素子、および直交方向（この例のためにアジマス方向）に 64 の素子を有して配置されるピエゾ素子のアレイの例を使用すると、各線が最大 24 の素子からなる、64 線撮像装置を構築することができる。しかしながら、サイズは、任意の線のために 0 ~ 24 の素子に電子的に調節することができ、アジマスで最大 64 線の任意の数も活性化することができる。

#### 【0071】

2D または 3D の撮像装置における、図 12A 及および図 12B に示されるように、仰角面の薄いスライスをイメージングすることは望ましい。この特定の実施形態では、仰角方向は左パネル上の ya 軸にある。仰角面 (1201) は、ya - za 面内にある。同じ

実施形態では、アジマス面（1202）は、本明細書のスキャニング面でも、仰角面に対して直交である。図12Bを参照して、機械的レンズは、ビームを仰角面に集束させ、ビームを、仰角面におけるより厚いスライスを形成するために追い払い続け、受信信号の一部になる望まれない反射を有するより厚い仰角スライスで他の対象を打ち、信号に散乱（cluttering）を加え、画質を低下させる。

#### 【0072】

ビームが意図されたスライス厚を越えて広がると、それは場合によって所望の範囲外の標的を打ち得、それらの反射は再構成画像に散乱を引き起す。トランステューサ表面上で形成される機械的レンズは、図12Bで見られるように、仰角面のビームを固定された仰角スライス厚まで集束させることができ、ここで、厚さは、図12Bで見られるように、仰角焦点ポイントで最小限であり、および仰角面焦点ポイントとして図12Aの上でさらに示される。2Dイメージングのための電子焦点は、時間関数としての動的受信焦点によって、仰角面の改善された焦点を可能にする。ここで、仰角での焦点距離は、ビームが標的へと下がりより優れた画像をもたらすとともに、変動される。3D画像化については、その特定の仰角切片を導くことができないか、所望の量以上掃くことができないので、固定された機械的レンズは働かない。したがって、電子的に制御される仰角焦点は望ましい。

10

#### 【0073】

いくつかの実施形態では、これはトランステューサを多くの様々なストリップに分割することによって達成される。図13Aを参照して、特定の実施形態では、複数のトランステューサ素子を有するトランステューサは、N列で整列され、ここで、各列は、トランシーバー素子の最大M行を有する。素子の行は、第1の数の行を含むAストリップであって、ストリップAは最大N列を有する、ストリップAと、行の中央セクションにある第2の数の行を含むストリップBであって、各行は、最大N列を有する、ストリップBと、最大N列の行の下部セクションを含むストリップCと、に分割することができる。いくつかの実施形態では、各ストリップは、個別に駆動されるために、および各ストリップの列が送信ドライバによって同じ駆動を共有するように、選択され得る。ストリップA、BおよびCは、隣接するストリップと重複しないことになり得る。代替的に、ストリップは、その隣接するストリップと多くの行および列に重複する場合がある。いくつかの実施形態では、ストリップは、ともにトランステューサ素子のすべてのN列とM行をカバーする。いくつかの実施形態では、電気的にプログラムされた時、ストリップのすべては、トランステューサのM対Nアレイの一部のみをカバーする場合がある。

20

#### 【0074】

いくつかの実施形態では、上部セクションAは、そのセクションのすべての素子が、素子がある列に意図される送信ドライバによって駆動されるように、構成される。この実施形態では、送信動作では、N混成列各混成列は、ストリップAまたはBまたはCの行の素子を含んでもよいを駆動する特有の遅延を有するN送信ドライバは、超音波ビームをアジマス面（1202）に集束させるために使用される。受信動作中に、セクションAに衝突する反射された信号は、図14に示されるように、スキャンラインA1、A2、A3などを形成するためにビーム形成される。図14を参照して、PMUTの3つのストリップは、A、BおよびCとして標識される。これらのストリップは、列上の素子が共通送信ドライバによって駆動されるPMUTの行を含む場合、N列のためにNドライバ（すなわち、N列の各々のために異なるドライバ）を有する。スキャンラインA1、A2等は、ストリップAを使用して送信と受信によって形成することができる。スキャンラインB1、B2等は、セクションBから形成され、およびスキャンラインC1、C2等は、セクションCから形成される。そうすると、3つのセクションのスキャンデータを使用して、別の焦点、今度仰角方向では、列ドライバに沿った遅延を使用してビームをアジマス面に集束するために前に使用された同様の方法で、セクションA、BおよびCのデータに特有の遅延を使用して実行される。このプロセスは、2段階ビームフォーマーと見なされてもよく、ここで、第1の段階は、A、B、Cのスキャンラインの現像からなり、第2の段階は、

30

40

50

そのデータを仰角面で焦点を展開するために使用する。仰角の焦点は、遅延をデジタル方式で適用することによって受信器で達成される。この技術は、仰角面で焦点を可能にするのみならず、焦点が動的であることを可能にする。この場合、焦点距離は、仰角焦点が超音波ビームとともに移動することを可能にするために、時間の関数として調節することができます。

#### 【 0 0 7 5 】

図 1 3 A と図 1 4 に記載されるプロセスは、3 つの送受信を必要としても、セクション A および C からの第 1 と第 2 の送受信は、1 つの動作に組み合わせられ得る。いくつかの実施形態では、トランステューサの上部および下部の両方の送信は、同時に実施されることができ、ここで、列の上部および下部の上の遅延は同一である。第 2 の送信は、第 1 のおよび / または第 2 の送信に使用されるものとは異なる遅延を有する中央部からである。

10

#### 【 0 0 7 6 】

いくつかの実施形態では、上部セクション、中央セクション、および / または下部セクションは 1 つ以上のサブセクションに分割されることができ、その各サブセクションは、パルス送信および信号受信のための多くの行を含む。いくつかの実施形態では、各サブセクションは、本明細書に開示されるものと類似した複数のスキャンラインを形成するために使用され得る。

#### 【 0 0 7 7 】

いくつかの実施形態では、トランステューサ素子アレイは、3 つ以上のストリップ、例えば、4、5、6、7 などに分割され得る。いくつかの実施形態では、各ストリップのスキャンラインは、順次にまたは同時に実行され得る。いくつかの実施形態では、同時送信では、中央ストリップに対称的なストリップのスキャンラインは取得される。いくつかの実施形態では、同じ列の素子の遅延は、同時に動作されるセクションのものと同一である。

20

#### 【 0 0 7 8 】

仰角焦点は、トランステューサの残存部分に対してトランステューサの 2 つの外側のセクションの一部の電圧のより低い振幅をさらに使用することによって促進され得る。

#### 【 0 0 7 9 】

いくつかの実施形態では、仰角方向に沿った特有のプログラム可能な遅延は、すべての列の各素子のために実施される。すべての N 列が、互いにに対して遅延される駆動信号を受信すると仮定する。さらなる遅延は、列素子に沿ったさらなる遅延を追加するために生成され得、列に沿った各素子は、同じ列上のその隣接素子に対する異なって遅延されることができる。遅延プロフィールの例は、図 1 8 B で示される。仰角方向に沿ったすべての列素子の遅延は類似し得る。1 つの実施形態では、遅延は対称的であり、中心素子で仰角面の焦点のために最大である。外側および中央の素子間の遅延差の量は、焦点距離を決定する。

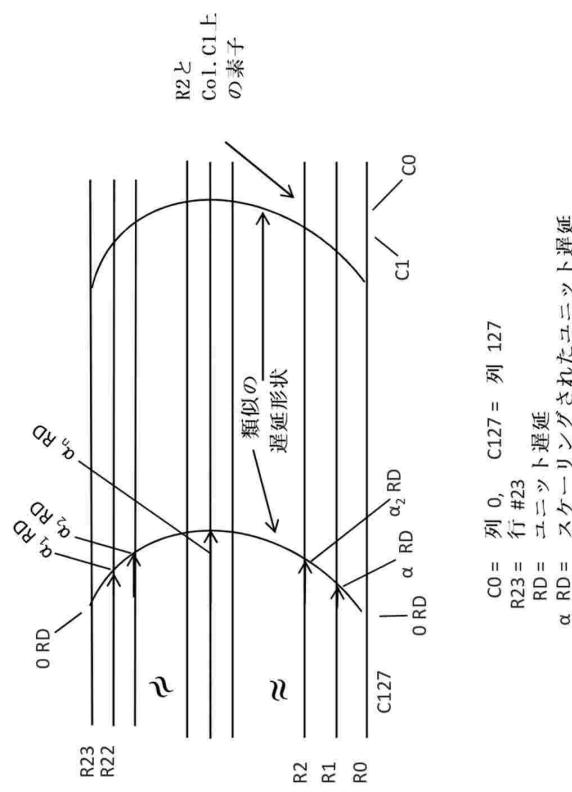

30

#### 【 0 0 8 0 】

いくつかの実施形態では、遅延プロフィールは、図 1 8 B に示され、ここで、列の端素子での相対的な遅延は、 $0 \times R D$  または  $0 \text{ n s}$  であってもよい。行 1 および R 2 2 の上の素子については、行 0 での遅延に対する遅延は、対称な遅延が中央素子のまわりで望ましい場合、図 1 8 B で示されるように、アルファ  $1 \times R D$  などでありえる。遅延  $R D$  は、アルファ 1、アルファ 2 等と同様にプログラム可能である。したがって、遅延プロフィールは、列に沿って構築され得、ここで、遅延は、列の端にある遅延に相対的であり得る。相対的な遅延プロフィールは、他の列の素子のために同一である得ることが注目されるべきである。他の実施形態では、遅延プロフィールは、中央素子のまわりで対称的でない場合があり、任意にプログラムされ得る。いくつかの実施形態では、遅延は、 $25 \text{ n s} \sim 1000 \text{ n s}$  の範囲内である。いくつかの実施形態では、遅延は、 $10 \text{ n s} \sim 5000 \text{ n s}$  の様々な範囲を有し、プログラム可能である。いくつかの実施形態では、遅延は、 $50 \text{ n s} \sim 500 \text{ n s}$  の範囲内である。

40

#### 【 0 0 8 1 】

いくつかの実施形態では、本明細書のシステムおよび方法を使用して、スキャンライン

50

を取得する手順は、図15に示される。いくつかの実施形態では、反射された信号は、トランステューサによって受信され、信号は、電圧に変換され、アナログ・デジタル・コンバーター（A D C）によって増幅され、デジタル化される。これらの受信信号は、R F信号としても知られている。これらのR F信号は、n（例えば、1、2、3、4…）によって遅延され、図14のスキャンライン、例えば、A1、A2などを形成するために合計化され得る。いくつかの実施形態では、信号は、遅延されてそして係数で重み付けされ、その後、スキャンラインを形成するために合計化される。

#### 【0082】

いくつかの実施形態では、受信方向にビームを集束させることは、アジマス方向（Y）に沿って1つを超えるR F信号、例えば、S1、S2などを利用し、それらはR F信号として知られているデジタル化された出力サンプルである。いくつかの実施形態では、R Fサンプルは、例えば、Y方向に沿った遅延プロフィールで遅延され、結果として生じる信号は、スキャンラインを形成するために重み付けられ、合計化され得る。

10

#### 【0083】

図14に示されるように、連続の送受信イベントで、スキャンラインA1、A2および追加スキャンラインは、セクションAを使用して取得され得る。いくつかの実施形態では、画像フレームは、イメージングされる標的領域の細密スキャンを達成するために100またはそれ以上などの多くのスキャンラインを含んでもよい。同様の手順は、セクションBおよびセクションCを使用してスキャンラインを取得するために使用され得る。セクションA、BおよびCのスキャンラインは、第1のレベルビームフォーマーを使用して展開され、ビームフォーマーは、アルゴリズムを使用して、スキャンラインを作成し、記載された実施形態では、アルゴリズムがすでに記載された信号遅延および合計化の方法を使用した。合成アパーチャ、第2のレベルのビームフォーマーは、その後、図16で示されるように、仰角面において集束を達成するために使用される。いくつかの実施形態では、これらの送信は、単一の仰角角度（0度、10度、20度、30度など）に集束され、それによって、仰角面内にない面散乱を減少させ、改善された画像を取得する。

20

#### 【0084】

特定の実施形態では、図16を参照して、2段の集束／ビームフォーマーは、A1、B1およびC1、A2、B2およびC2、A3、B3およびC3等からのビームデータ（すなわち、スキャンラインデータ）を使用し、それは、最終ビーム出力を形成するために、遅延され、重み付けされ、合計化され、仰角面集束を可能にする。この実施形態では、Xは仰角軸である。

30

#### 【0085】

機械的レンズと異なり、合成レンズについて本明細書に開示されるように、焦点距離は、ビームフォーマーに電子的にプログラムされ得る。いくつかの実施形態では、そのプロセスは、トランステューサの任意のセクション、例えば（A、BおよびCセクション）からスキャンラインを形成するために多くの送受信（例えば、スキャンラインA1を形成するためにNラインから1つの送受信）を必要とする場合がある。フレームを形成するために、Rスキャンラインはイメージングされる全領域をスキャンすることが必要とされる。さらに、この場合、3つの別個のフレームA、BおよびCが必要である。いくつかの実施形態では、画像に高いフレームレートを有することは望ましい。フレームは、多くのスキャンラインを含んでもよい。しかしながら、同数のスキャンラインを展開させることができ一方で送受信の数を減少することができれば、フレームレートが増加するであろう。いくつかの実施形態では、増加したフレームレートは、2つのセクション（例えば、AとC）からの送受信を組み合わせることによって達成することができる。これらの領域は中央領域に対して対称的であるので、例えば、図15に示されるような必要とされる遅延は、領域AおよびCには同一であり得る。これらの2つの領域を、信号を送受信するために組み合わせられた1つの領域に組み合わせることによって、フレームレートは、150%増加し得る。中央部分Bは、領域AおよびCのための第1の送信で使用された遅延と異なる遅延を必要とする場合がある。いくつかの実施形態では、スキャンラインA1、B1、

40

50

C 1 などはアジマス面に沿って形成される。第 2 のビームフォーミング動作は、第 1 レベルのビームフォーマーからのデータを使用し得、および図 1 5 および図 1 6 で示されるような同様の技術を使用して集束は仰角面において達成され得る。いくつかの実施形態では、2 D スキャンはストリップの片側、例えば、N 列からスタートすることができ、もう一方の末端、例えば、列 1 で完成する。したがって、フレーム A は、ビーム A 1、A 2、A N … のために順番でスキャンすることによって取得することができる。フレーム A に対する時間のシーケンスフレームであるフレーム B のこのシーケンスを追従することによって、標的は移動したかもしれない。運動アーチファクトの影響を最小限に抑えるために、ビームフォーミングは、A 1、B 1、C 1、A 2、B 2、C 2 などの様々なフレームのためにスキャンラインをインターリーブすることによって行うことができる。A と C は、送信および受信がともになされ得るように組み合わせられると、組み合わせられた A、C 領域は、D として指定され得、およびスキャンラインは D 1、D 2 などとして指定され得る。非限定的な例示的スキャンシーケンスは、D 1、B 1、D 2、B 2 などになり得る。これは、イメージングされている標的の運動に対する感度を最小限に抑えることを可能にし得る。

#### 【 0 0 8 6 】

いくつかの実施形態では、A、B、C を形成するために使用される列の数はプログラム可能である。列の数は、イメージングされている解剖学的構造に応じて調整され得、および、例えば、解剖学的構造または患者情報に基づいて事前セットを使用してユーザインタフェースで設定することができる。

#### 【 0 0 8 7 】

いくつかの実施形態では、電子合成レンズは、動的集束および動的アパー チャを提示する。例えば、近距離場では、A と C のための重みは、最小限で、深度に応じて徐々に増加することができ、アパー チャの変化を引き起こす。

#### 【 0 0 8 8 】

いくつかの実施形態では、セクション（例えば、A および C）は、送受信中にアポダイズされる。アポダイゼーションは、送信（T x）駆動波形のパルス幅変調（P W M）によって達成され得る。アポダイズされないパルス駆動は、標準パルス幅を有する。パルス幅が変更される、例えば、減少させられる場合、p M U T からの圧力出力は減少され得る。いくつかの実施形態では、アポダイゼーションは、素子がトランスデューサの中心から端に行くにつれて、素子のために重みを先細りさせる。これはサイドロープを減少させ、より高画質の画像を作成することができる。記載された手順にアポダイゼーションを適用することによって、信号の仰角面の外側への漏れを減少させ得る。図 1 0 A - 図 1 0 B は、p M U T アレイを用いた仰角方向のアポダイゼーション実装の例示的な実施形態を示す。アレイにおける各 p M U T は、3 つの端子を有する。この実施形態では、p M U T は、変更する分極強度でプログラムされ得る。例えば、図 1 0 A における、p M U T アレイは、膜および 1 行当たりの様々な分極強度を制御するピエゾ材料のために様々な分極方向を使用して分極される場合がある。図 1 0 B は、分極動作後のアレイの例示的なバイアス接続を示す。いくつかの実施形態では、本明細書の同じ原理は、2 つの端子のみ、例えば、O 端子および X 端子を使用する p M U T に当てはまる。

#### 【 0 0 8 9 】

いくつかの実施形態では、アポダイゼーションは、マルチレベル送信駆動、例えば、3、5 または 7 レベルを使用することによって達成され得る。この駆動信号の様々なレベルを選ぶことによって、アポダイゼーションは、トランスデューサの中心より端に近い素子のためにより低い振幅の送信駆動信号を変化させる振幅を適用することによって作成され得る。この例では、中央の行と比較して外側の行上のすべての素子は、より低い駆動電圧を有し得、およびデジタル復号および選択によって特定の駆動レベルは、マルチレベル出力を形成するために利用可能であり得る。3 レベルの復号の例は、図 2 2 に示される。

#### 【 0 0 9 0 】

いくつかの実施形態では、アポダイゼーションは、トランスデューサアパー チャの中心

10

20

30

40

50

のそれと比較して端でより小さなサイズの圧電素子を使用することによって実施される。

【0091】

いくつかの実施形態では、トランスデューサ素子は、図13Aで示されるように、上部セクション、A、下部セクション、C、および中間セクション、Bで、配置される。図13Bで示されるように、これらの各セクション、すなわち、セクションA、BおよびCでは、行上の2つの隣接する素子は、送信および/または受信動作において電気的に一体化して接続され、Nライン（本明細書では列に等しい）トランスデューサをN/2ライントトランスデューサに本質的に変換する。送信動作中に、各ラインの上部および下部のセクションは、チャネルに接続され得、および中間セクションは、別のチャネルに接続され得る。したがって、Nチャネルは、N/2ラインを処理するのに必要とされる。送信動作中に、すべての素子がオンに操作され得、そしてトランスデューサすべての素子を利用するこ<sup>10</sup>とによって最大の送信圧力を生成することができる。アジャマス方向に集束することは、ラインまたは列の間の相対的遅延を変更する送信チャネルによって達成され得る。受信動作中に、素子は、図13Bで示されるように接続され得、アジャマス方向に集束され得る。仰角集束は、図13Aで議論されるように、第1レベルのビームフォーマーの結果を使用して、ビームフォーミングを使用して実行され得る。図13Bで示されるように接続され<sup>20</sup>ているトランスデューサ素子を使用する送受信の動作は、最大の信号対ノイズ比および速いフレームレートのために、トランスデューサ全体を使用して1つの送受信動作という利点を有し得る。信号対ノイズ比は、図13Aで示されるような場合より高くなり得、その場合では、各ストリップは個別に駆動されるために選択され得、およびすべてのトランスデューサ素子が使用されるので、各ストリップの列は、送信ドライバによる同じ駆動を共有する。さらに、運動アーチファクトは、図13Aで示されるようなトランスデューサを使用するより、図13Bで示されるようなトランスデューサを使用して減少され得る。

【0092】

いくつかの実施形態では、プログラム可能な遅延は、1つ以上の列に仰角方向に沿って生成され得る。いくつかの実施形態では、すべてのN列が、互いに対しても遅延される駆動信号を受信する場合、追加遅延は、同じ列に沿った素子のためにさらなる遅延を加えるために生成され得る。いくつかの実施形態では、列に沿った各素子は、同じ列上のその隣接する素子に対して異なって遅延され得る。遅延プロフィール例は、図18Bで示される。アレイ素子 $e_1 e_i, j$ のための有効な遅延は、以下のように、グループ列遅延、 $j$ 、および個々の行遅延、 $i$ 、の和であり得る：<sup>30</sup>

【0093】

【数1】

$$\tau_{i,j} = \tau_j + \tau_i \quad (1)$$

【0094】

ここで、いくつかの実施形態では、遅延 $j$ 、 $i$ は、以下によって決定され得る：

【0095】

【数2】

$$\tau_j = \sqrt{(x - x_j)^2 + z^2} / c \quad (2)$$

【0096】

【数3】

$$\tau_i = \sqrt{(y - y_i)^2 + z^2} / c \quad (3)$$

【0097】

10

20

30

40

50

等式(1) - (3)では、送信時の焦点は、位置(x, y, z)あり、遅延は、位置x<sub>j</sub>、y<sub>i</sub>での素子のために独立して計算され得る。可変数cは、伝搬媒質における仮定の音速である。完全で分離不可能集束の場合、トランスマッテューサ素子、e<sub>1</sub>e<sub>i</sub>,<sub>j</sub>、のための遅延は、以下のように計算され得る。

【0098】

【数4】

$$\tau_{i,j} = \sqrt{(x - x_j)^2 + (y - y_i)^2 + z^2} / c \quad (4)$$

10

【0099】

いくつかの実施形態では、アジマスおよび仰角における遅延の可分性仮定は、完全ではなく、遅延プロフィールにおける最大の誤差は、集束アーチャの外側の素子上で生じることに注目されたい。しかしながら、小さな誘導角度および/または大きなf/数(ここで、f/数はアーチャ直径対焦点距離の比である)を有する実施形態については、この可分性仮定は、満足な結果を提供し得、電子実施を容易にし得る。

【0100】

仰角(例えば、同じ行)に沿ったすべての列素子のための遅延は、類似し得る。遅延は、仰角面の集束のために中心に最大を有して対称的になり得る。遅延の量は、焦点距離を決定してもよい。

20

【0101】

いくつかの実施形態では、すべての列のための仰角方向に沿ったプログラム可能な遅延が、実施されてもよい。すべてのN列は、互いに遅延される駆動信号を受信すると仮定する。追加遅延は、列素子に沿ったさらなる遅延を追加するために生成され得、ここで、列に沿った各素子は、同じ列上のその隣接する素子に対して異なって遅延され得る。列上の中央素子に関する非対称的な遅延も達成され得る。ある実施形態では、仰角面においてビームを導くことは望ましく、および列上の素子のための遅延は、列の各素子がその隣接素子に対して固定された遅延インクリメントを有するように、生成される。

【0102】

いくつかの実施形態では、仰角方向に沿ったプログラム可能な遅延が、実施され得、ここで、仰角遅延は、2つの遅延、例えば、粗線形遅延、および細密で任意の遅延の和になり得る。列に沿った素子のための粗線形遅延は、ビーム誘導のためにも有用であり得る。ビームを傾けるために、列の下部の素子は、列の上部の素子から横方向の遅延を有してもよく、ここで、その間の素子は、直線的に補極される遅延を有する。遅延は、より大きな誘導角度が大きくなればより大きくなる。さらに、列の素子に沿った細密遅延は、仰角方向にビームを集束させるのに有用であり得る。例えば、遅延がラインの中央素子でより大きく、かつ遅延が、中央素子の両側で対称的に減少する場合、ビームは集束し得る。小さな遅延値は、より大きな焦点距離(例えば、何十ns)を有するビームという結果をもたらし、および大きな遅延値は、より短い焦点距離(例えば、数百nsec ~ μsec)を有するビームという結果をもたらす。いくつかの実施形態では、すべてN列が互いに遅延される駆動信号を受信する場合、仰角遅延は、列素子に沿ったさらなる遅延を追加するために生成され得、ここで、列に沿った各素子は、2つの遅延、例えば粗遅延および細密遅延によって遅延され得、ここで、粗遅延は、隣接する素子間で線形的になり得、細密遅延は、隣接する素子間で任意であり得る。列素子に沿った線形的遅延は、列によって異なり得ると同様に、列素子に沿った細密遅延は列によって異なり得る。したがって、アレイ素子e<sub>1</sub>e<sub>i</sub>,<sub>j</sub>のための有効な遅延は、以下のように、グループ列遅延、<sub>j</sub>、線形的粗行遅延(linear coarse row delay)、<sub>i</sub>、coarse、と細密行遅延(fine row delay)、<sub>i</sub>、fineの和でありえる:

30

【0103】

【数5】

40

50

$$\tau_{i,j} = \tau_j + \tau_{i,coarse} + \tau_{i,fine} \quad (5)$$

## 【0104】

ここで、 $j$ 、 $i$ 、`coarse`、および、 $i$ 、`fine`は、以下のように計算され得る：

## 【0105】

## 【数6】

$$\tau_j = (\sqrt{(x - x_j)^2 + (y - y_{min})^2 + z^2} - \sqrt{x^2 + y^2 + z^2})/c \quad 10$$

(6)

## 【0106】

## 【数7】

$$\tau_{i,j,coarse} = \Delta\tau y_i$$

$$\tau_{i,j,fine} = (\sqrt{(x - x_j)^2 + (y - y_i)^2 + z^2})/c - \tau_j - \tau_{i,j,coarse} \quad 20$$

(7)

## 【0107】

等式(5) - (7)では、送信時の焦点は、位置( $x$ 、 $y$ 、 $z$ )にあり、遅延は、位置 $x_j$ 、 $y_i$ での素子のために独立して計算され得る。変数 $c$ は、伝搬媒質における仮定の音速である。等式(6)では、 $y_{min}$ パラメータは、2Dトランステューサ面上に、焦点( $x$ 、 $y$ 、 $z$ )を投影すること、および投影された焦点への最小距離を有するトランステューサ行位置を計算することによって計算され得る。粗遅延( )のスロープは、細密遅延が、完全な2D遅延の十分な近似値を与えるために使用され得るように計算され得る。

## 【0108】

遅延を計算するための上記の方法は、前述されたX-Yの分離可能な遅延と比較して、等式(4)の2Dの焦点の遅延にはるかに良い近似値を与えることは当業者に明白であろう。改善された遅延計算は、列ベースで列上の様々な遅延を実施するために、粗遅延クロック、細密遅延クロック、およびさらなるいくつかのレジスタービットを必要とすることになり得る。しかしながら、この方法は、細密クロック遅延および個々の素子ルーティングでの2次元における完全な任意の遅延よりも、集積回路中で実施するのに簡単である。

## 【0109】

いくつかの実施形態では、カスケード化された一連のフリップフロップは、適切な遅延を有するT×ビームフォーマーからの列に到達クロックをゲート制御する。その後、この遅延は、異なるクロックによって列において伝播され得、この異なるクロックの周波数はプログラム可能であるが、様々な列ドライバのためのドライバのための遅延を生成したT×クロックに同期される。列上の中央素子のまわりの対称的な遅延については、遅延を生成するフリップフロップチェーンは、列の中央素子で停止し、ここで、遅延プロフィールが、図19に示されるように、中心のまわりで対称的になり得る。フリップフロップによって生成された遅延は、行0の素子が最後の行上の素子と同じ遅延を有し、第2の行上の素子は、上側で最後から2番目の行上の素子と類似の遅延を有するように、適切な位置へ送られることができる。

## 【0110】

いくつかの実施形態では、列の隣接する素子間の遅延は、線形的であり得る。表1の結果および図23Aでの仰角ビームプロット(`beamplot`)は、放物線のプロフィー

ルと比較して、仰角における線形的遅延プロフィールを使用する効果を示す。表1の結果は、図23Aの一方方向のビームプロットのビーム幅（-3dBおよび-10dB）を定量化する。図23Aで示されるように、特定の実施形態では、仰角集束の5つの異なる実施：1) 仰角集束なし、2) 完全な2D集束、3) 線形的遅延、4) 区分上線形的遅延、5) スペースアポダイゼーションが、2dトランスデューサアレイのために調査される。線形的遅延の例については、列に沿った隣接する素子間の遅延は、互いに固定され得、この条件は必須ではないが、仰角遅延プロフィールは、アレイの中心のまわりで対称的であり得る。区分上線形的遅延については、遅延プロフィールは、少なくとも3つのセグメントに分離され得、所与のセグメントの隣接する素子は、互いに固定された遅延を有する。この方法は、複数の線形的遅延セグメントを含むことによって放物線の遅延プロフィールのよりよい近似値を可能にし得る。スペースアポダイゼーション方法は、他の方法と比較して、アレイを送信時に1.5Dアレイと同様に動作させるために、素子をオンおよびオフすることによって、能動素子の数を減少させることができる。このスペースアポダイゼーション方法の1つの例は、図23Bで示される。このアプローチでは、完全なアーチャと比較して、出力圧力が減少され得ることに注目されたい。トランスデューサの様々な誘導角度の例は、図44に示される。

#### 【0111】

表1の結果は、アジマスにおける0度の誘導を有する仰角ビームプロットの-3dBおよび-10dBのビーム幅を示す。結果は、線形的遅延方法が仰角集束を使用しない場合よりも良く、完全な2D集束法に類似し得ることを示す。区分上線形的遅延方法は、線形的方法よりさらに良いビーム幅性能を予想通りに達成する。スペースアポダイゼーション方法は、達成可能なビーム幅の観点から仰角集束がない場合よりもよいが、線形的方法ほど良好ではない。スペースアポダイゼーション方法が標準以下である理由は、スペースアレイの「行」に沿ったピッチが、他の方法と比較して減少されているという事実のために最も可能性がある。図23Aの仰角ビームプロットの結果は、線形的および区分上線形的遅延ビームプロットが-15dBまで2D集束ビームプロットと同様であることを示す。スペースアポダイゼーション方法は、行の横方向のオフセットにより非対称的なビームプロットを有し、この方法はさらに調査されたすべての方法の中で最大のサイドローブを示す。方法はさらにオフ軸（図23Aの右パネル）から離れて横方向に導くときに安定性を示す。これらの結果は、前述の電子仰角遅延方法が、低コストの、バッテリーで動作される超音波システムにおける位相アレイおよび線形的アレイイメージングに対する適切な代替手段であることを示唆する。

#### 【0112】

##### 【表1】

| 集束方法          | -3dB ビーム幅 (mm) | -10dB ビーム幅 (mm) |

|---------------|----------------|-----------------|

| 仰角集束なし        | 6.08           | 15.98           |

| 完全な2D集束       | 5.35           | 9.23            |

| 線形的遅延         | 5.38           | 9.25            |

| 区分上線形的        | 5.35           | 9.25            |

| スペースアポダイゼーション | 5.50           | 9.65            |

#### 【0113】

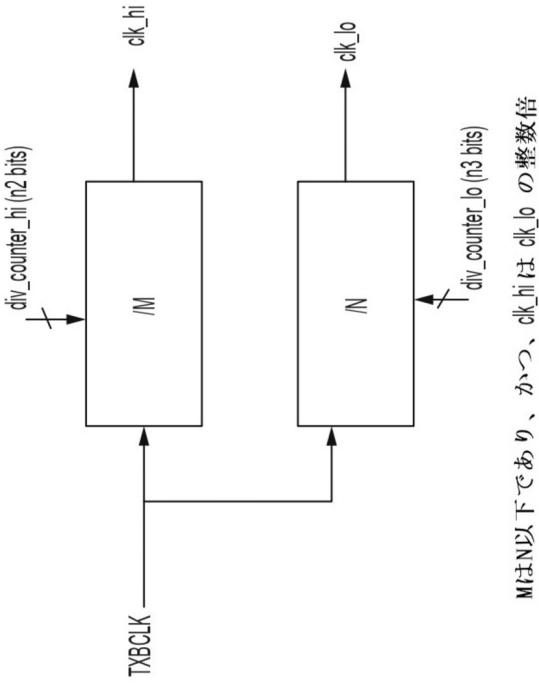

表1は、様々な遅延プロフィールを使用し、または集束を使用せずに、仰角集束の影響を示す。これらの結果は、図23Aの0度のアジマスの誘導ビームプロットの結果を定量化する。いくつかの実施形態では、列上の各素子は、専用の送信ドライバを有する。いくつかの実施形態では、各素子ドライバは、クロック、例えば、TxB C1kによって駆動されるデジタル遅延回路を含む。1つの実施形態の遅延回路は、図17Aで示されるよう

10

20

30

40

50

に複数のフリップフロップを含む。フリップフロップ（例えば、DFF1、DFF2、DFF3、DFF4等）は、列の下部、例えば、列0からスタートするデジタル入力を有する。いくつかの実施形態では、TXAは、送信ビームフォーマーから生成されたデジタルビットである。送信ビームフォーマーは、1つのチャネル当たり複数のデジタルビットを提供する回路を含んでもよい。図17Aで示されるように、1つのチャネル当たり2つのビットが使用される。TXAは1つのデジタルビットであり得る。TXBは別のビットであり得る。例えば、図17Aのような、TXAに取り付けられたものと同一の回路は、TXBまたは任意の追加ビットのために使用され得る。これらの2つのビットは、図39Bで示されるように、送信ドライバのための電圧駆動レベルを決定するために復号され得る。ここで、TXAおよびTXbは、TXドライバの出力レベルを決定するために復号され得るデジタル信号である。例えば、TXA、TXBは両方とも0である、または、出力レベルは共通である、または時に、信号グラウンドの場合；TXA=1ならば、TXB=0、その出力はHIである。これは、5Vまたは10Vまたは求められるような他の値の正電圧であり得る。TXA=0の場合、TXB=1、例えば、共通が0Vである場合、出力は、LOまたは-5V 0.5 - 1.0Vになる。TXAおよびTXBは、TXBCLKと呼ばれる高速クロックを使用して、TXビームフォーマーにおいて作成され得る。好ましい例では、これは200MHzのクロックにおいてあり得る。TXパルサー出力の遅延された出力信号は、図18Aで示されるように超音波ビームを導く、または集束させるために使用され得る。ここで、ライン撮像装置は、同じ遅延を共有するライン上のすべての素子と仮定される。各ライン素子は、TXビームフォーマーによって2つのビット（例えば、TXA、TXB）を送ることができる。次のラインのビットは、異なり、ビームを導くまたは集束させる必要に応じて遅延され得る。TXビームフォーマーによって適用されるこれらの遅延は、アジマス軸に沿ってあり得、アキシアル方向でビームを導くまたは集束させることができる。しかしながら、遅延は、仰角面においてビームを導くまたは集束させるために、仰角方向に沿っても必要になり得る。これは、列上の素子のために分離された遅延を必要とする場合がある。図17Aは例示的な実施形態を示す。TXA、TXBビットは、列でTXビームフォーマーから到着する。Nが1～16または32あるいは求められるように大きい場合、フリップフロップDFF1～DFFNは、各行に位置する。DFF1の入力ピン1は、TXAまたはTXBに接続することができる。フリップフロップのピン1は、c1k\_hiという名のクロックに接続することができ、それはその入力としてTXBクロックでデジタルディバイダーによって生成される。分割はMによるものであり、ここで、Div Controlと標識されたデジタル入力バスは、非限定的な例として8ビットのバスとしてここで示され、M値を決定するために使用され得る。フリップフロップDFF1～DFFN、TXA/TXB入力信号の作成された遅延は、図17Aで示される通りであり、ここで、A、B、C、は、TXA、TXBの遅延されたバージョンである。これらの出力は、これらの入力のうちの1つを自分の出力として選択するMUXに接続され得、選択は、これらがFビットを含むことができる、SEL0、SEL1などによって制御されたDECODERを使用して、行われることができる。例えば、行0については、Fビットがすべて0である場合、1と標識されたポート上の入力はMUXの出力であるように選択されている。その場合、TXAは出力であるように選択される。Fの値は二元性の1だった場合、1と標識されたポートは選択され、およびAはMUXの出力に接続されるであろう。これらのデジタル出力、この場合に素子当たり2つは、図22に示されるように、その後、復号され得、パルサー出力を駆動するために使用される。この回路は、列上の素子のためにTXA、TXBビット上の入力の遅延に対して細密遅延を提供し得る。さらに、これらの遅延は、列上の素子のために特有のものであり得る。図17Bは、列上の素子に粗遅延を追加し得る例示的な実施形態を示す。ここで、Nによって分割する、別のディバイダーは含まれ得る。MがNより小さく、または等しい、および整数である入力c1kTXBは含まれ得る。このディバイダーの出力、c1k\_1oは、図17Bで示されるDFFのc1k入力に接続されてもよい。ここで、TXAまたはDFFの出力（それはTXAの遅延されたバージョンである）は、MUXに接続され得、遅延され

10

20

30

40

50

ないバージョンが選ばれる場合、それは行 0 の素子に適用される。その後、これは、行 1 の D F F のピン 2 に接続され得る。行 1 素子が遅延を必要とする場合、遅延されたバージョン ( D F F のピン 3 出力 ) は、行 1 の M U X によって選択され得る。これは次の素子のために反復され得る。ここで、遅延は、行 0 上の素子を除いて、列上のすべての素子に追加され得る。列上の素子に適用されたこの線形的遅延は、ビームを導くように支援する場合がある。図 17 A および図 17 B の回路は、列上のすべての素子に細密遅延および粗遅延を与えるために組み合わせられることができる。例えば、これは、回路を I N T \_ T X A @ R o w 0 および他の列上の同様のノードに追加することによって行うことができ、ここで、図 17 A の細密遅延回路は、粗遅延生成器によって既に遅延されていたこれらの出力に細密遅延を追加するために挿入され得る。図 17 C は、列上の各素子に粗遅延および細密遅延を実施するために好ましい実施形態を示す。T x A または T x B のビットは、T x A / B が m u x 1 のピン 1 に接続するところで示される。この入力が U P によって示される制御によって選択されている場合、T x A / B が m u x 1 の出力に現われる。その後、この信号は、c l k \_ l o を使用する D F F によって遅延され得る。その後、フリップフロップの出力は、m u x 2 に利用可能になってもよく、この入力が m u x 2 ( n o \_ 1 i n \_ d e l a y 制御を使用して ) によって選択されている場合、その後、m u x 2 の出力は、図 17 A のものと類似する D F F 1 - N に接続する。この回路は、細密遅延を提供してもよい。D F F a の出力に続き、m u x 1 と同様であるが、次の行のための m u x に行く。その後、この信号は、それに接続された D F F により遅延され得る。同じプロセスは、他の行に垂直に進行して反復され得る。これは、列上の素子を直線的に、例えば、行 0 から他の行まで、上の信号を遅延させ得る。各行上では、D F F 1 - N は、希望に応じて、列上のすべての素子に細密遅延を追加してもよい。m u x 1 の第 2 の入力およびすべての行の同様の m u x は、上部の最小の遅延および下部の遅延 ( 行 0 ) から始めて、信号を直線的に遅延させるために使用し得る。これの T x A / B は、さらに最後の行上の m u x 1 のクローンのピン 2 に接続してもよい。このように、M U X 1 上の U P 制御 ( および他の行上のその等価物 ) を使用して、遅延は、下部から上部まで増加し得、またはその逆でもあり得る。

#### 【 0 1 1 4 】

図 21 は、パルサー波形を示し、すなわち、遅延および仰角焦点のための復号後の送信ドライバ出力は、P 1 が、1 つの遅延単位を有する素子 1 の送信ドライバの出力を表わし、P 2 が、素子 2 に適用された 2 つの遅延単位であり、および P 4 が、4 つの遅延を有する送信ドライバ素子 4 の出力であるとき、完了する。この場合、この図面で、列上の粗遅延のみが示され、細密遅延は示されない。

#### 【 0 1 1 5 】

図 18 B は、列上の素子の相対的な遅延を示す。いくつかの実施形態では、遅延の量は焦点距離を決定する。いくつかの実施形態では、すべての列の開始遅延は、アジマス軸に沿って集束する必要性に応じてセットされ、異なることができる。仰角軸に沿った遅延は任意であり得る。例えば、遅延は、下部行からトランスデューサの上部の行に行って直線的に増加し得る。この場合、ビームは、仰角方向に導かれることができる。遅延が中央素子のまわりで対称的である場合、焦点は仰角面にある。他の様々な遅延プロフィールも可能であり、仰角スライスの焦点および誘導を可能にし得る。

#### 【 0 1 1 6 】

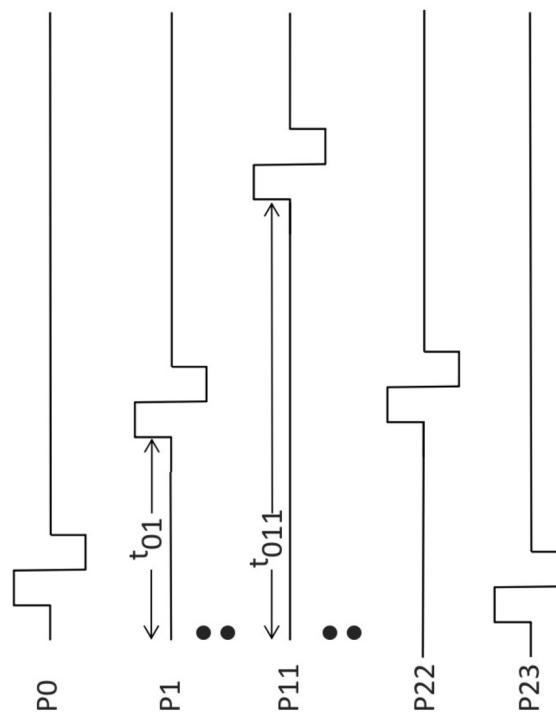

図 19 は、トランスデューサの列に沿った圧電素子に適用される送信ドライバパルスの非限定的、例示的な波形を示す。この実施形態では、トランスデューサは、列上で 24 の圧電素子を有する。P 0 は、行 0 上で特定の列 ( 例えば、列 1、2、3、4、5、6、7、8、9、10、11 など ) 上の圧電素子であり、P 1 は、P 0 と同じ列だが、行 1 上の圧電素子である、P 11 は、同じ列だが、行 11 上の、P 22 は行 22 上の、P 23 は行 23 上のものである。この実施形態では、素子 P 0 に特定の周波数の 1 つのパルスが適用される。同じパルスは、素子 P 1 に適用されるが、P 0 に対して t 01 によって遅延される。同様に、同じパルスは、遅延 t 01 より長い遅延 t 011 を有して P 11 に到着する

10

20

30

40

50

。この実施形態では、遅延は、中央素子 P 1 1 のまわりで対称性を有する。これは、図 1 9 に示されるように、P 2 3 と P 0 でのパルスタイミングは実質的に同一であり、P 1 、 P 2 2 のパルスタイミングは実質的に同一であるなどを意味する。いくつかの実施形態では、本明細書のパルス（幅、規模、形状、および / または周波数）は、同じ列のすべての素子に対して同じである。いくつかの実施形態では、本明細書のパルス相対的遅延および周波数は、列の 2 つの行上のすべての素子に対して同じであり、列上の第 1 の素子上の初期の遅延は、異なる列上の同様の素子と異なることができる。いくつかの実施形態では、本明細書のパルスは、様々な形状を有し、波形は複数のパルスを有してもよい。パルスの非限定的、例示的な形状は、方形状パルス、ガウスのパルス、および正弦波パルスの 1 つ以上を含む。いくつかの実施形態では、遅延、例えば、t 0 1 、 t 0 2 、 t 0 3 、 ... 、 t 0 1 1 は、すべての選択された列上のすべての素子のために電子的にプログラムされ、制御される。

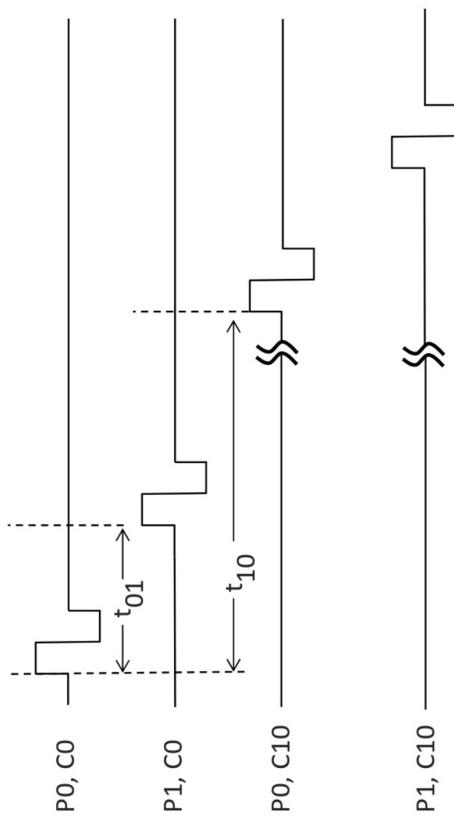

#### 【 0 1 1 7 】

図 2 0 は、列間の遅延関係を示す。この特定の実施形態では、遅延は、送信ビームフォーマーチャネル遅延によって決定される。例えば、t 1 0 は、列 0 上の素子 0 と列 1 0 上の素子 0 との間の遅延である。これらの遅延は、送信ビームフォーマーにおいてプログラムされ、図 1 2 A の x a - z a 面で示されるように、アジマス面においてビームを集束させることを促進するために電気的に調節可能である。いくつかの実施形態では、列上の素子間の遅延は、図 1 2 A の x a - z a 面で示されるように、仰角面においてビームを集束させる、またはビームを傾けるために別々にプログラムされる。t 0 1 は、同じ列上の素子（例えば、列 0 の素子 0 および 1 と、列 1 0 上の素子 0 および 1 ）間の例示的な遅延である。いくつかの実施形態では、列上の素子の遅延は、そのチャネルのために送信ビームフォーマーによって決定される、開始遅延に対するものである。いくつかの実施形態では、開始遅延は、送信ビームフォーマーによって予め決められてもよく、または送信ビームフォーマーによって調整可能であってもよい。

#### 【 0 1 1 8 】

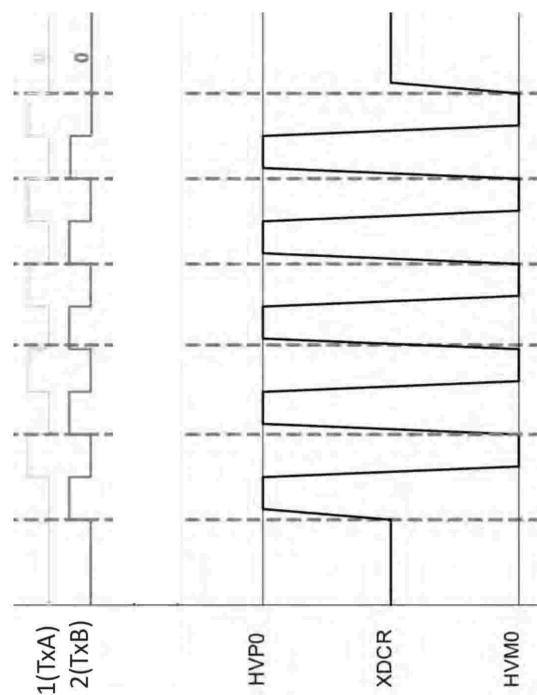

特定の実施形態では、図 2 2 を参照して、パルサー機能の一例が示される。この実施形態では、2 つのデジタル入力、すなわち、 I N 1 （例えば、図 1 7 A - 1 7 D の T x A ） 、 I N 2 （例えば、図 1 7 A - 1 7 D の T x B ）は、パルサーの電圧出力レベルを制御する。これらの 2 つの入力のロジックレベルに基づいて、 H V P 0 が正高電圧であり、 H V M 0 は負低電圧であり、および X D C R は有効な接地レベルまたは 0 V である、 3 レベルの出力結果は生成され得る。この実施形態では、同一のパルス波形の 5 つのサイクルは、出力結果として生成される。いくつかの実施形態では、 I N 1 、 I N 2 のパターンおよび / またはパターンの周波数の変更によって、出力結果のパターン、周波数、および / またはパルス数は変更され得る。いくつかの実施形態では、本明細書のロジックレベルまたはロジックコード化は、1 つ以上入力のデジタル論理動作を含み得る。いくつかの実施形態では、論理動作は、 A N D 、 N O T 、 O R 、 N A N D 、 X O R 、 N O R 、 X N O R から選択される 1 つ以上の論理オペレーター、または 1 つ以上の入力、または任意の他の論理動作を使用することを含む。

#### 【 0 1 1 9 】

いくつかの実施形態では、フリップフロップのカスケードにされたシリーズ / チェーンは、適切な予め定義された、または予めプログラムされた遅延を有する、その列のための送信ドライバから 1 つ以上の列に到着する送信クロックをゲート制御する。いくつかの実施形態では、この遅延は、その後、その周波数がプログラム可能である異なるクロックによって列で広められるが、様々な列ドライバのためのドライバに遅延を生成する送信クロックと同期される。いくつかの実施形態では、遅延を生成するフリップフロップチェーンは、列の中央素子で止まり、ここで遅延プロフィールは図 1 9 のように中心のまわりで対称的である。フリップフロップによって生成される遅延は、したがって、行 0 の素子は、最後の行上に素子と同じ遅延を有し、第 2 の行上の素子は、上部の側から 2 番目の素子と同様の遅延を有するように、1 つ以上の列の適切な位置に転送され得る。

10

20

30

40

50

## 【0120】

実施形態では、仰角焦点は様々な遅延プロフィールを使用して達成される。遅延が列の下から上へ単調に増加するまたは減少するように、仰角方向において線形的遅延プロフィールを使用することは、仰角方向にビームを導く場合がある。その上に、曲率が列の末端に0である、ビームへのさらなる曲率は、ビーム誘導に加えて集束を可能にする場合がある。理論的な遅延の線形的近似値は、誘導および集束を提供し、かつ本明細書の実施形態に記載される経済的実施を可能にするために十分に正確であり得る。

## 【0121】

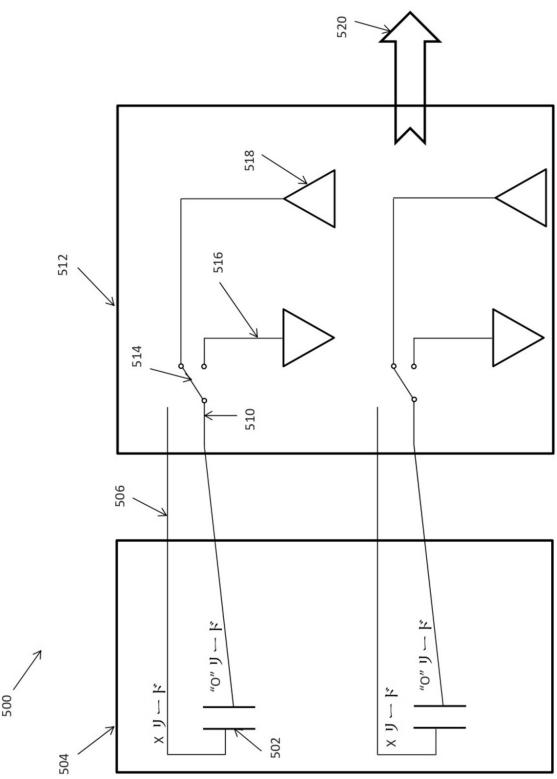

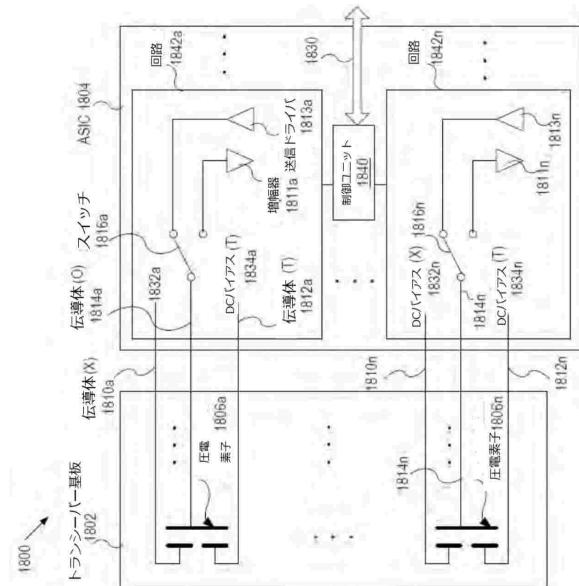

図24Aは、本明細書の超音波イメージングシステム(1800)を示す。描写されているように、イメージングシステムは、トランシーバー基板(1802)と、トランシーバー基板に電気的に結合されるASICチップ(1804)と、を含んでもよい。実施形態では、トランシーバー基板(1802)は、1つ以上の圧電素子(1806)を含んでもよく、各圧電素子は1つ以上の膜で配置されてもよい。実施形態では、1より多くの圧電素子は、1つの膜で配置されてもよい。

10

## 【0122】

実施形態では、圧電素子(1806a) - (1806n)の各々は、2つ以上の電極を有してもよく、これらの電極は、ASICチップ(1804)に収容される駆動/受信エレクトロニクスに接続されてもよい。実施形態では、各圧電素子(例えば、(1806a))は、伝導体(O)(例えば、(1814a))に電気的に接続される上部伝導体、および伝導体(X、T)(例えば、(1810a)と(1812a))に電気的に接続される2つの下部電極を含んでもよい。実施形態では、伝導体(1810a)は、DCバイアス(X)(1832a)、または接地に電気的に結合されてもよく、伝導体(T)(1812a)は、DCバイアス(T)(1834a)または接地に結合されてもよい。

20

## 【0123】

実施形態では、ASICチップ(1804)は、1つ以上の回路(1842a) - (1842n)であって、それらの各々は、1つ以上の圧電素子(1806a) - (1806n)に電気的に結合される回路と、回路(1842a) - (1842n)を制御するための1つの制御ユニット(1840)と、を含んでもよい。実施形態では、各回路(例えば、(1842a))は、送信ドライバ(1813a)、受信増幅器(例えば、(1811a))、伝導体(O)(1814a)に電気的に結合されるスイッチ(例えば、(1816a))、および結合された1つの端子、および送信ドライバ(1813a)と増幅器(1811a)に結合される2つの伝導体間に切り替える別の端子を含んでもよい。送信(Tx)モード/プロセス中に、スイッチ(1816a)は、信号が圧電素子(1806a)の上部電極に送信されるように、圧電素子(1806a)に送信ドライバ(1813a)を接続してもよい。受信(Rx)モード/プロセス中に、スイッチ(1816a)は、信号が圧電素子(1806a)の上部電極から増幅器(1811a)に送信されるように、増幅器(1811a)を圧電素子(1806a)に接続してもよい。

30

## 【0124】

いくつかの実施形態では、送信ドライバ(1813a)は様々な電気コンポーネントを含んでもよい。しかしながら、簡潔さのため、送信ドライバ(1813a)は、1つのドライバによって表わされる。しかし、それは、送信ドライバが多くの機能を有するより複雑なドライバを含む場合があるということは、当業者に明白であるはずである。たとえ図24Aで1つの増幅器(1811a)のみが示されても、受信される信号を処理するための電気コンポーネントは、増幅器(1811a)に接続される場合がある。実施形態では、増幅器(1811a)は、低ノイズ増幅器(LNA)であってもよい。実施形態では、回路(1842n)は、回路(1842a)と同じまたは類似の構造であってもよい。実施形態では、DCバイアス(X)(1832a) - (1832n)のすべては、同じDCバイアスまたは接地に接続されてもよく、すなわち、伝導体(X)(1810a) - (1810n)のすべては、単一のDCバイアスまたは接地に接続されてもよい。

40

## 【0125】

50

同様に、DCバイアス(X)(1834a) - (1834n)のすべては、同じDCバイアスまたは異なるDCバイアスに接続されてもよく、すなわち、伝導体(T)(1812a) - (1812n)のすべては、単一のDCバイアスまたは接地に接続されてもよい。

#### 【0126】

実施形態では、伝導体(X、TおよびO)(1810)、(1812)および(1814)は、相互接続技術 - 例えば、銅柱相互に連結接続、または突起(図24Bの(1882)などの)を使用して、矢印(1880)によって示されるように、ASIC(1804)に接続される場合がある。実施形態では、ASICチップ(1804)の回路部品は、相互接続(1830)を使用して、ASICチップ(1804)の外側で通信する場合がある。実施形態では、相互接続((1830)は、ASICチップ(1804)上のパッドからASICチップの外側の別のパッドまでのボンディングワイヤーを使用して実行される場合がある。実施形態では、ASICチップ(1804)上の突起パッドまたは再分布突起などの相互接続の他のタイプは、ワイヤー結合されたパッドに加えて使用してもよい。

10

#### 【0127】

実施形態では、回路(1842)に含まれるLNA(1811)は、受信アナログフロントエンド(AFE)の一部などの、ASICチップ(1804)の外側で実施される場合がある。実施形態では、LNAは、ASICチップ(1804)および別のLNAに呈してもよく、プログラム可能な利得増幅器(PGA)は、AFEに呈してもよい。各LNA(1811)の利得は、リアルタイムでプログラムされてもよく、それによって、LNAが撮像装置に必要とされる時間利得補償機能(TGC)になることができる。

20

#### 【0128】

実施形態では、LNA(1811)は、低電圧トランジスター技術を使用して、構築されてもよく、それによって、それらが従来のトランステューサが必要とする高電圧にさらされると、破損される場合がある。したがって、従来システムでは、高電圧伝送/受信スイッチは、高送信電圧を、低電圧受信回路から離間するために使用される。そのようなスイッチは、大きくて高価であり、高電圧(HV)プロセスを使用し、LNAに送られる信号を劣化させる場合がある。これに対して、実施形態では、低電圧が使用されてもよく、これによって、従来システムの高電圧コンポーネントは不要になる場合がある。さらに、実施形態では、従来のHVスイッチの除去により、従来のHVスイッチによって引き起こされる性能劣化が回避される場合がある。

30

#### 【0129】

実施形態では、圧電素子(1806)は、スイッチ(1816)によって受信モード中にLNA(1811)に接続されてもよい。LNA(1811)は、圧電素子に発揮する圧力を振る反射圧によって生成された圧電素子(1806)の電荷を、低ノイズを有する増幅された電圧信号に変換する場合がある。受信される信号の信号対ノイズ比は、改造される画像の画質を決定する主要因の一つになる場合がある。したがって、LNA自体の内部ノイズを減少させることは望ましい。実施形態では、ノイズを、入力段階でより多くの電流の使用などの、LNA(1811)の入力段階のトランスクンダクタンスを増加させることによって減少させてもよい。電流の増加は、動力消費および熱を上昇させる場合がある。実施形態では、pMUT(1806)は、低電圧で動作され、ASICチップ(1804)に近接する場合があり、これによって、低電圧pMUT(1806)によって節約される電力は、LNA(1811)におけるノイズを、所与の合計温度が、高電圧で動作される従来のトランステューサと比較して、容認可能なように上昇するために、低下させるために利用されてもよい。

40

#### 【0130】

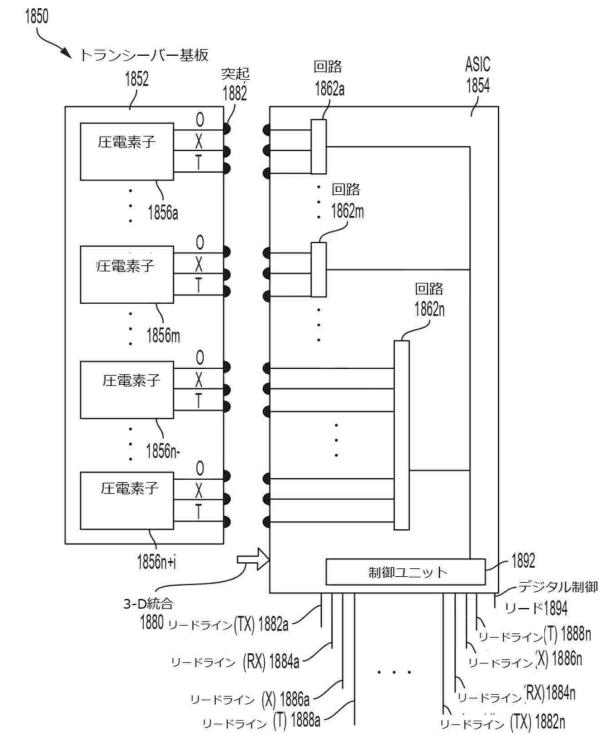

図24Bは、本開示の実施形態のイメージングセンブリ(1850)の概略図を示す。実施形態では、トランシーバー基板(1852)およびASICチップ(1854)は、トランシーバー基板(1802)およびASICチップ(1804)のそれぞれに類似する場合がある。従来システムでは、圧電トランステューサを駆動するためのエレクトロ

50

ニクスは、典型的に圧電トランステューサからはるかに遠く位置し、かつ同軸ケーブルを使用して、圧電トランステューサに接続される。一般的に、同軸ケーブルは、エレクトロニクスへさらなる付加容量などの寄生負荷を増加させ、および付加容量は、ノイズの増大および信号電力の損失などの重大なパフォーマンスパラメータの損害を引き起こす。これに対して、図 24 B で描かれるように、送信ドライバまたはドライバ（または等価に回路）(1862a) - (1862n) は、Cu ピラーまたはハンダバンプ (1882) またはウエハボンディングまたは、同様のアプローチ、またはそのような技術の組み合わせなどの低いインピーダンス 3 次元 (3D) 相互接続メカニズムを使用して（矢印 (1880) によって示されるように）、圧電素子（または等価にピクセル）(1856a) - (1856n+i) に直接接続される場合がある。実施形態では、トランシーバー基板 (1852) を ASIC チップ (1854) へ統合させる際、回路 (1862) は、圧電素子 (1856) から 100 μm 未満の垂直に（またはその程度）遠ざけて位置してもよい。実施形態では、ドライバ回路 (1862) と圧電素子 (1856) 間のインピーダンス整合のための任意の従来の機器は不要とされる場合があり、それによって、イメージングアセンブリ (1800) の設計はさらに簡易化され、および電力効率は増加する。回路 (1862) のインピーダンスは、圧電素子 (1856) の要件を満たすように設計されてもよい。

### 【0131】

実施形態では、図 24 A では、圧電素子 (1806a) - (1806n) の各々は、ASIC チップ (1804) に位置する対応する回路 (1842a) - (1842n) の 1 つに電気的に接続されてもよい。送信ドライバ (1813a) - (1813n) の入力の信号は、例えば、図 17 A - D で示されるが、図 24 A および図 24 B で明白に示されていない回路を使用して、生成され得る。実施形態では、この配置により、撮像装置は 3 次元画像を生成することができる。同様に、図 24 B では、圧電素子 (1856a) - (1856m) の各々は、X、T および O に表示される 3 つのリードを有してもよい。各圧電素子のリードは、相互接続手段 (1882) によって ASIC チップ (1854) に位置する、対応する回路 (1862a) - (1862m) の 1 つに電気的に接続される場合がある。加えて、実施形態では、(1856n) - (1856n+i) などの圧電素子のラインは、1 つの共通回路 (1862n) に電気的に結合される場合がある。実施形態では、送信ドライバ回路 (1862n) は、1 つの送信ドライバで実施される場合がある。代替的な実施形態では、送信ドライバ回路 (1862n) は、様々なイメージングモードを促進するために多層ドライバで実施される場合がある。

### 【0132】

ASIC チップ (1854) が、回路 (1862n) に類似する回路の任意の適切な数を有してもよいことは、当業者に明白であろう。実施形態では、制御ユニット (1892) は、圧電素子を 2 次元のピクセルアレイに水平または垂直に構成し、それらの長さを構成し、およびそれらを送信モード、または受信モード、または分極モード、またはアイドルモードに置く性能を有する。実施形態では、送信ドライバ回路 (1813) は、図 22 および図 39 で示されるように、多層ドライバで実施される場合があり、ここで、送信ドライバ出力は、2 を上回る出力レベルを有する場合がある。図 39 A は、出力レベルが 0 V または 6 V、または 12 V であってもよい実施形態を示す。これらの電圧が、様々で、例えば、-5 V、0 V および +5 V であり得ることは理解されるであろう。送信ドライバは、さらに、図 38 に示されるように、駆動信号を有する 2 レベルのドライバになり得る。

### 【0133】

実施形態では、リードライン (1882a) - (1882n) は、圧電素子 (1856) の電極 (O) にパルスを適用するために使用される信号伝導体であってもよい。同様に、リードライン (1884a) - (1884n)、(1886a) - (1886n) および (1888a) - (1888n) は、信号を圧電素子 (1856a) - (1856n+i) と通信させるために使用されてもよい。他の適切な数のリードラインが、信号 / データをイメージングアセンブリ (1800) と通信させるために、使用されてもよいことは

10

20

30

40

50

注目されたい。

【0134】

実施形態では、リードライン( X ) ( 1886 ) およびリードライン( T ) ( 1888 ) の各々は、接地またはDCバイアス端子に接続されてもよい。実施形態では、デジタル制御リード( 1894 )は、デジタル制御バスであってもよく、イメージングアセンブリ( 1850 )での様々な機能を制御し取り組むために必要な1つ以上のリードを含んでもよい。これらのリードは、例えば、シリアル・ペリフェラル・インターフェース( SPI )または他のプロトコルなどの通信プロトコルを使用して、ASICチップ( 1854 )のプログラム可能性を可能にする場合がある。

【0135】

実施形態では、圧電素子( 1806 ) ( または( 1856 ) ) および制御エレクトロニクス/回路( 1842 ) ( または( 1862 ) ) は、同じ半導体ウエハ上で展開される場合がある。代替的な実施形態では、トランシーバー基板( 1802 ) ( または( 1852 ) ) およびASICチップ( 1804 ) ( または( 1854 ) ) は、個別に製造され、突起( 1882 )を使用する金属相互接続技術などの3D相互接続技術によって互いに組み合わせられる場合がある。実施形態では、相互接続技術は、製造コストを低下させ、かつ成分の収率を独立して最大化するために低収率増加効果を除去する場合がある。

10

【0136】

実施形態では、リードライン( 1862a ) - ( 1862n ) は、圧電素子( 1806 )の電極( O )にパルスを適用するために使用される信号伝導体であってもよい。同様に、リードライン( 1864a ) - ( 1864n )、( 1866a ) - ( 1866n ) および( 1868a ) - ( 1868n )は、信号を圧電素子( 1806a ) - ( 1806n )と通信させるために利用されてもよい。他の適切な数のリードラインが、信号/データをイメージングアセンブリ( 1800 )と通信させるために使用されてもよいことは注目されたい。

20

【0137】

上に議論されるように、LNA( 1811 )は、電荷感知モードで動作してもよく、および各々は、利得代償を提供するためにリアルタイムで構成されてもよいプログラム可能な利得を有する。

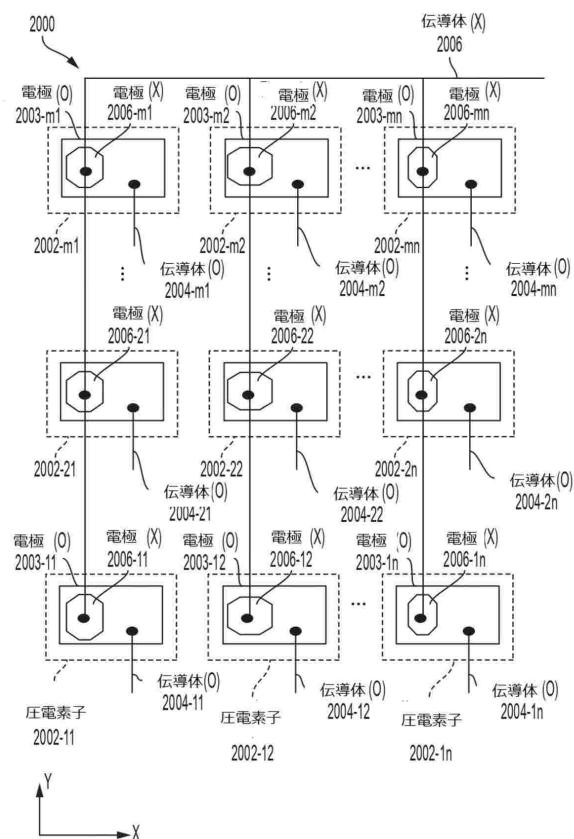

【0138】

30

図25は、本開示の実施形態に係る、圧電素子( 2002 - 11 ) - ( 2002 - mn )のm × nアレイ( 2000 )の概略図を示す。描写されているように、各圧電素子は、( 図3Aの圧電素子( 214 )などの ) 2端子圧電素子であってもよく、伝導体( O ) ( 例えば、2004 - 11 )に電気的に結合される電極( O ) ( 例えば、2003 - 11 )、および共通伝導体( X ) ( 2006 )を介して接地またはDCバイアス電圧に電気的に接続される電極( X )を有してもよい。実施形態では、各信号伝導体( O )は、回路素子によって独立して管理されてもよい。実施形態では、各伝導体( O ) ( 例えば、( 2004 - mn ) )は、回路素子の送信ドライバに電気的に結合されてもよい一方、圧電素子アレイのX電極( ( 2006 - 11 ) - ( 2006 - mn ) )のすべては、共通伝導体( X ) ( 2006 )に接続されてもよい。実施形態では、アレイ( 2000 )は、トランシーバー基板に配置され、m × n + 1突起などの相互接続メカニズムによってASICチップに電気的に結合されてもよい。より具体的には、m × n伝導体( O ) ( 2004 - 11 ) - ( 2004 - mn )は、m × n突起によってASICチップのm × nドライバに結合されてもよく、および共通伝導体( X ) ( 2006 )は、1つの突起によってASICチップに結合されてもよい。実施形態では、ここで記載されるような例示的な構成は、3Dイメージングを実施するために使用され、ここで、少なくとも1つのサブ圧電素子を含む各圧電素子は、アレイにおける特有の情報を提供することができる。実施形態では、各圧電素子は、1つ以上の膜を備えてもよく、膜の複数のモードおよび周波数で振動してもよい。実施形態では、各圧電素子( 2002 )は、図38および図39の電圧プロファイル( 3300 )および( 3400 )を有するパルスによって駆動されてもよい。

40

50

## 【0139】

実施形態では、各列のO電極（例えば、(2003-11)-(2003-m1)）は、共通伝導体に電気的に結合されてもよい。例えば、各列のO電極が互いに電気的に結合されるように、ASICチップの回路素子は、電子的に制御されてもよい。そのような構成では、各列のO電極は、共通送信ドライバによって、または送信モード中に同一の電気的駆動信号を有する複数のドライバにつき同じ電気パルスを受信する場合がある。同様に、各列のO電極は、受信モード中に共通増幅器に同時に電荷を送信する場合がある。言い換えると、各列の圧電素子は、ラインユニット（または等価にライン素子）として動作される場合がある。

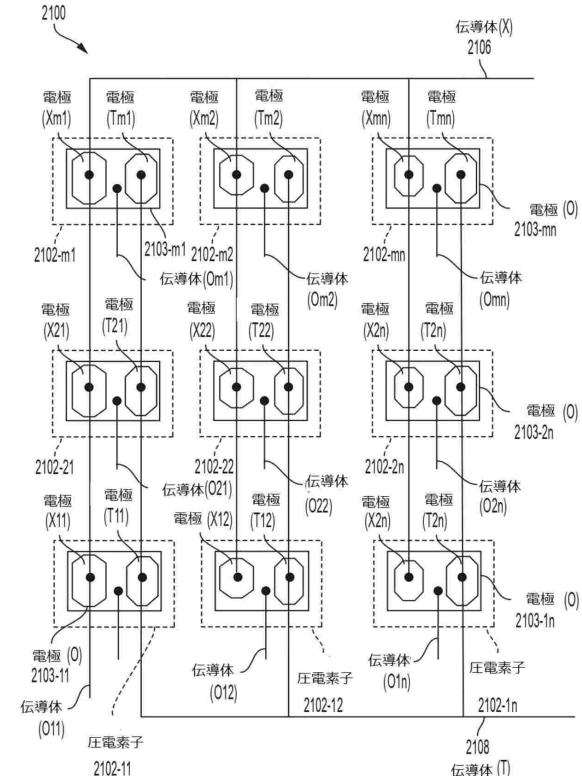

## 【0140】

図26は、本開示の実施形態に係る、圧電素子(2102-11)-(2012-mn)のn×nアレイ(2100)の概略図を示す。描写されているように、各圧電素子は、3端子圧電素子であってもよく、電極O、XおよびTを含んでもよい。実施形態では、X電極（例えば、X11、X21、…、Xm1）は、連続的に列方向に接続されてもよく、X電極(X11～Xmn)のすべては、共通伝導体(X)(2106)に電気的に結合されてもよい。実施形態では、T電極（例えば、T11、T21、…、Tm1）は、連続的に列方向に接続されてもよく、T電極(T11～Tmn)のすべては、共通伝導体(T)(2108)に電気的に結合されてもよい。(2102-11)、(2102-21)-(2102-m1)などの素子の列は、実施形態に記載されるように一体的に接続される時に、ライン素子または列を構築する。実施形態では、O電極(2103-11)-(2103-mn)の各々は、伝導体(O11)-(0mn)のうちの1つを介してASICチップの対応する回路素子の送信ドライバに電気的に結合されてもよい。実施形態では、アレイ(2100)は、トランシーバー基板に配置され、m×n+1突起などの相互接続メカニズムによってASICチップに電気的に結合されてもよい。ASICでは、O電極に接続される送信ドライバは、図22に示されるように、多層出力を生成するために復号されるパルスを受信することができる。これらのパルスは、（図17A-17Dで示されたように）列に沿った素子のために遅延されてもよい。さらに、遅延は、（例えば、図19で示されるように）列に沿って作成され得る。

## 【0141】

実施形態では、各列のO電極（例えば、(2003-11)-(2103-m1)）は、共通伝導体に電気的に結合されてもよい。そのような配置では、各列のO電極は、送信モード中に共通送信ドライバを通じて同じ電気パルスを受信してもよい。同様に、各列のO電極は、受信モード中に共通増幅器に同時に電荷を送信する場合がある。言い換えると、各列の圧電素子はラインユニットとして動作される。実施形態では、列のO電極の各々は、専用送信ドライバに接続されてもよく、ここで、列のすべての素子のための送信ドライバの入力信号は同一であり、したがって、送信動作中にすべての圧電素子に現われるために実質的に同一の送信ドライバ出力を生成する。そのようなライン素子は、各素子が特有の送信ドライバを有するため、素子当たりのベースで電子的に制御される。これは、大きな容量性ライン素子を駆動することにおいて有益であり、ここで、各素子はより小さな容量を有し、タイミングの遅延は、列上の素子のために最小限に抑えられることができる。実施形態では、受信モード中に、列のすべての素子の電荷は、2Dイメージングによって行われるように、LNAにそれを接続することによって感知されることができる。3Dイメージングでは、各素子の電荷は、受信モード動作中にLNAに各素子のO電極を接続することによって感知される。

## 【0142】

図27は、本開示の実施形態に係る、圧電素子(2002-11)-(2202-mn)のm×nアレイ(2200)の概略図を示す。描写されているように、アレイ(2200)は、アレイ(2100)に類似してもよいが、列のX電極（例えば、(X12)-(Xm2)）が共通伝導体（例えば、(2206-1)）に接続され、および列のT電極（例えば、(T12)-(Tm2)）は、共通伝導体（例えば、(2208-1)）に接続

10

20

30

40

50

されてもよいという違いを有する。したがって、同じ列の X 電極（または T 電極）は、動作中に同じ電位を有する場合がある。実施形態では、O 電極の各々は、伝導体（O 1 1）-（O m n）のうちの 1 つを介して ASIC チップの対応する回路素子の送信ドライバに電気的に結合されてもよい。実施形態では、アレイ（2 2 0 0）は、トランシーバー基板に配置され、 $m \times n + 2 n$  突起などの相互接続メカニズムによって ASIC チップに電気的に結合されてもよい。

#### 【0 1 4 3】

アレイ（2 1 0 0）と比較して、アレイ（2 2 0 0）は、ASIC チップに T 電極および X 電極を接続するためにより多くの突起を使用する場合がある。一般的に、ASIC チップと圧電アレイとの間の T および X の接続数の増加は、接地または DC バイアス源と平行して接続される時、X 伝導体および T 伝導体におけるインピーダンスを減少させ、クロストークを減少させる場合がある。クロストークは、イメージング素子から別の素子までの信号の結合を指し、干渉を引き起こし、画質を低下させる場合がある。X および T のラインを流れる電流によるいすれかの電圧降下は、その電圧に理想的にさらされるべきでない圧電素子をわたって現われる際に、偽性の電気的結合が作成される場合がある。実施形態では、圧電素子が電子制御の下で送信または受信していない場合、X、T および O 電極は、所局的に短絡される場合がある。代替的に、アイドル電極は、O 電極をアースさせ、X 電極をアレイの他の X 電極に接続し、T 電極をアレイの他の T 電極に接続する。

#### 【0 1 4 4】

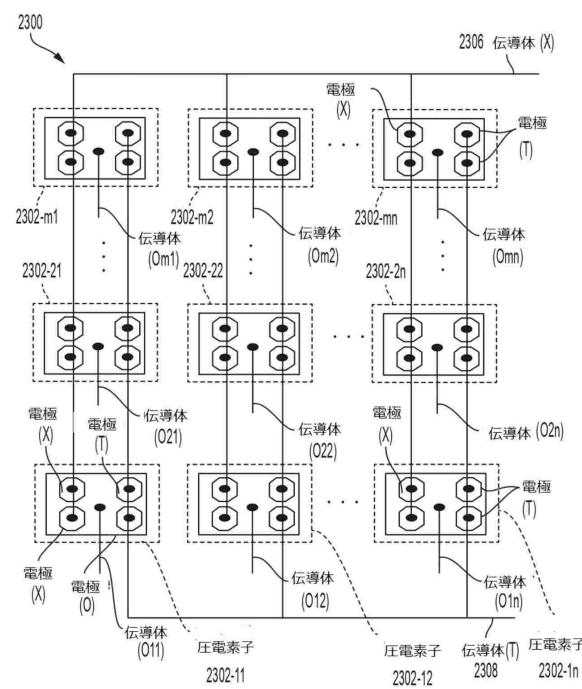

図 28 は、本開示の実施形態に係る、圧電素子（2 3 0 2 - 1 1）-（2 3 0 2 - m n）の $m \times n$  アレイ（2 3 0 0）の概略図を示す。描写されているように、アレイ（2 3 0 0）は、アレイ（2 1 0 0）に類似してもよいが、各圧電素子が、5 端子圧電素子であってもよく、すなわち、各圧電素子は、1 つの下部電極（O）および 4 つの上部電極（2 つの X 電極および 2 つの T 電極）を含んでもよい。実施形態では、各圧電素子の 2 つの X 電極は、連続的に列方向に接続されてもよく、 $2 m \times n$  の X 電極のすべては、共通伝導体（X）（2 3 0 6）に電気的に結合されてもよい。同様に、各圧電素子の 2 つの T 電極は、連続的に列方向に接続されてもよく、 $2 m \times n$  の X 電極のすべては、共通伝導体（T）（2 3 0 8）に電気的に結合されてもよい。実施形態では、O 電極の各々は、伝導体（O 1 1）-（O m n）のうちの 1 つを介して ASIC チップの対応する回路素子の送信ドライバに電気的に結合されてもよい。ASIC は、O ノードに接続する送信ドライバを含んでもよく、送信ドライバへの入力は、本明細書で例えば、図 17 A - D で議論される技術および回路を使用して遅延されてもよい。実施形態では、アレイ（2 3 0 0）は、トランシーバー基板に配置され、 $m \times n + 2$  突起などの相互接続メカニズムによって ASIC チップに電気的に結合されてもよい。

#### 【0 1 4 5】

図 28 を参照して、この例示的な実施形態では、2 つのサブ素子は X 電極に接続され、他の 2 つのサブ素子は T 電極に接続される。X 電極および T 電極は、DC 電圧源に接続されるバイアス電極になり得る。X 電極に接続される 2 つの素子は、様々な共振周波数で挙動する。これらの 2 つのサブ素子は、一体として、単独で各サブ素子より幅広い帯域幅を示す場合がある。T 電極に接続される 1 つの端子を有する 2 つのサブ素子は、両方とも、素子が X 電極に接続されると同様の共振周波数挙動を示す。例えば、X 電極に接続される 1 つのサブ素子、および T 電極に接続される 1 つのサブ素子は、2 MHz の共振周波数または中心周波数を有してもよく、残りのサブ素子は、4 MHz の中心周波数を示してもよい。これらの 2 つのサブ素子を組み合わせることにより、合成素子の帯域幅はより広くなる。X 電極および T 電極の使用は、さらにサブ素子において様々な分極方向を可能にし、素子の感度を増大させることができる。しかしながら、原則として、広帯域素子は、図 30 に示されるように、X 電極または T 電極のみを使用して設計されることもできる。

#### 【0 1 4 6】

図 32 に示される別の例示的な実施形態では、素子は、まだ 2 つのサブ素子を使用するが、この場合、サブ素子の各々は 2 つの「O」端子有する場合がある。各サブ素子は、様

10

20

30

40

50

々な挙動を示すことができ、および各サブ素子は特有の制御可能な駆動端子、O電極を有するので、それらは電子的に独立して駆動されることがある。

#### 【0147】

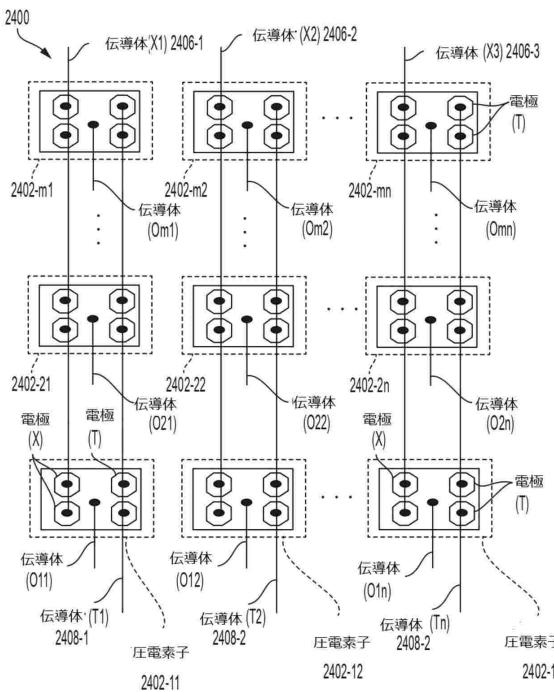

図29は、本開示の実施形態に係る、圧電素子(2402-11)-(2402-mn)のm×nアレイ(2400)の概略図を示す。描写されているように、アレイ(2400)は、アレイ(2200)に類似してもよいが、各圧電素子が、5端子圧電素子であつてもよく、1つの下部電極(O)および4つの上部電極(2つのX電極および2つのT電極)をであつてもよい。実施形態では、各圧電素子の2つのX電極は、列方向に伝導体(例えば、(2406-1))に電気的に接続されてもよく、および各圧電素子の2つT電極は、列方向に共通伝導体(例えば、(2408-1))に電気的に接続されてもよい。実施形態では、O電極の各々は、伝導体(O11)-(0mn)のうちの1つを介してASICチップの対応する回路素子の送信ドライバに電気的に結合されてもよい。実施形態では、アレイ(2400)は、トランシーバー基板に配置され、m×n+2n突起などの相互接続メカニズムによってASICチップに電気的に結合されてもよい。

10

#### 【0148】

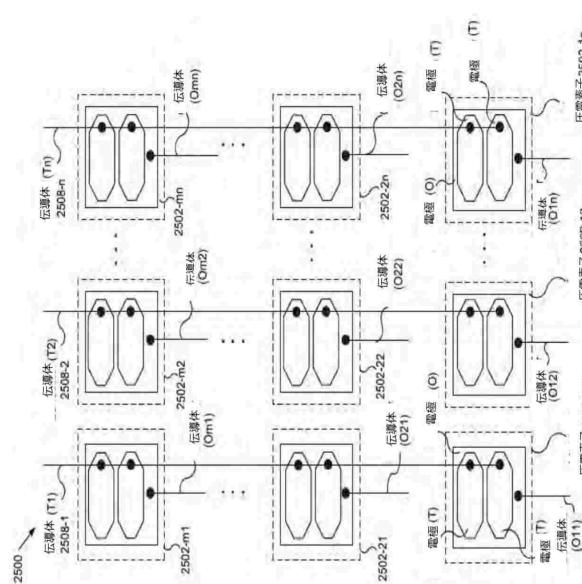

図30は、本開示の実施形態に係る、圧電素子(2502-11)-(2502-mn)のm×nアレイ(2500)の概略図を示す。描写されるように、アレイ(2500)は、各圧電素子が1つの下部電極(O)および2つの上部電極(T)を有するアレイ(2100)に類似してもよいが、列に沿った圧電素子(例えば、(2502-11)-(2502-m1))の2つの上部電極(T)のすべてが、共通伝導体(例えば、(2508-1))に電気的に接続されてもよいという相違点がある。実施形態では、O電極の各々は、伝導体(O11)-(0mn)のうちの1つを介してASICチップの対応する回路素子の送信ドライバに電気的に結合されてもよい。実施形態では、アレイ(2500)は、トランシーバー基板に配置され、m×n+n突起などの相互接続メカニズムによってASICチップに電気的に結合されてもよい。

20

#### 【0149】

図31は、本開示の実施形態に係る圧電素子(2602-11)-(2602-mn)のm×nアレイ(2600)の概略図を示す。描写されるように、アレイ(2600)は、アレイ(2100)と同様の電気的接続を有していてもよく、つまり、圧電素子のX電極の全ては、共通の伝導体(2606)に電気的に結合されていてもよく、そして圧電素子のT電極の全ては、共通の伝導体(2608)に電気的に結合されていてもよい。アレイ(2600)は、1つの圧電素子(例えば(2602-11))の上部の電極(X、T)が、別の圧電素子(例えば(2602-21))の上部の電極(X、T)と同じ、または異なる幾何学的形状を有し得る点で、アレイ(2100)とは異なるかもしれない。

30

#### 【0150】

圧電素子アレイ(2000)-(2500)については、各圧電素子アレイの圧電素子は互いに同じ、または異なっていてもよい。例えば、1つの圧電素子(2202-11)の2つの上部の電極の投影領域は、別の圧電素子(2202-n1)の2つの上部の電極の投影領域と同じ、または異なる形状を有していてもよい。

40

#### 【0151】

図32は、本開示の実施形態に係る圧電素子(2702-11)-(2702-mn)のm×nアレイ(2700)の概略図を示す。描写されるように、各圧電素子は、2つの信号電極(O)と、1つの共通の電極(X)とを含んでいてもよい。実施形態では、各信号電極(O)は、ASICチップの対応する回路素子の送信ドライバに、電気的に結合されていてもよい。例えば、圧電素子(2702-11)は、ASICチップの2つの回路素子にそれぞれ電気的に結合され得る、2つのシグナル伝導体(O111)と(O112)とを含んでいてもよく、ここで、各信号電極は、受信モード中に電荷を展開してもよい。実施形態では、アレイ(2700)は、トランシーバー基板上に配置されていてもよく、そして、2m×n+1突起などの相互接続メカニズムによって、ASICチップに電気的に結合されてもよい。実施形態では、アレイ(2700)のT電極の全ては、共通の伝

50

導体 (T) (2708) を介して、接地、またはDCバイアス電圧に電気的に結合されていてもよい。

#### 【0152】

実施形態では、例えば、図25-32の、アレイの信号伝導体(O)は、回路素子に電気的に結合されていてもよく、ここで、回路は、図24Aのスイッチ(1816)に類似するトランジスタスイッチを含んでいてもよく、つまり、該スイッチは、送信モード中と受信モード中に送信ドライバと増幅器との間でそれぞれ切り替わってもよく、その結果、O電極は送信モード中に圧力波を生成し、かつ受信モード中に電荷を展開してもよい。

#### 【0153】

図33Aは、本開示の実施形態に係る、イメージングシステム(2800)の例示的な実施形態を示す。描写されるように、イメージングシステム(2800)は、圧電素子のアレイ(2802-11)-(2802-mn)と、アレイを制御する/アレイと通信するための回路素子とを含んでいてもよい。実施形態では、圧電素子(2802-11)-(2802-mn)の各々は、3つの電極、第1の信号O電極と第2の信号O電極、およびT電極、を含んでいてもよい。(説明を目的として、各圧電素子の第1のO電極と第2のO電極とは、図33の中の各圧電素子の左のO電極と右のO電極とを指す。)実施形態では、アレイ(2800)のT電極の全ては、伝導体(T)(2808)を介して、接地、またはDCバイアス電圧に電気的に結合されていてもよい。実施形態では、列の圧電素子の第1のO電極は共通の伝導体(例えばO11)に電気的に結合されていてもよく、そして、同じ列の圧電素子の第2のO電極は別の共通の伝導体(例えばO12)に電気的に結合されていてもよい。この実施形態では、電子的な仰角の誘導は可能ではないかもしれない、というのは、例えば、(2802-11)から(2802-m1)のための全ての右のO電極は、O12を使用して一緒に接続されているかもしれない、そしてその後に1つのTxドライバ、またはRx受信器に接続されてもよい(2816-1)と(2814-1)。O12を使用して列の各素子のONノードをハード接続する代わりに、その列上の各ONノードを対応するTxドライバに接続することができ、そしてその後に、送信された信号の遅延を、列上の素子が異なる遅延を有するように制御することができ、そのようにして、電子集束がこの列の仰角軸において達成されてもよい。このことは図33Bに示され、この実施形態では、スイッチ(2812-11)は、pMUT素子(2802-21)に接続し、そしてスイッチ(2812-1m)が(2802-m1)のO端子に接続する。Txドライバ(2816)の入力は、図17A-17Dに示されるように、素子間の望ましい遅延を作り出す回路に接続される。個別のTxドライバ、増幅器、および/またはスイッチは、電子集束が望ましい場合に、素子のあらゆるO電極のために必要とされるかもしれない。この例では、合成の仰角集束を必要とする他のpMUT素子はまた、個別の送信エレクトロニクスと受信エレクトロニクスと共に示される。それらの表示は、図33Bに簡易形態で示されるが、信号を送受信するための機能的必要性を表わすように意図されている。この例では、(O11)-(On1)上の素子が電子集束を必要としない場合、それらは、示されるように有線接続することができる。実施形態では、受信モード中に、第1の信号O電極と第2の信号O電極の各々は、対応する回路によって処理され得る電荷を展開してもよい。

#### 【0154】