(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-294828

(P2005-294828A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

H01L 29/786

H01L 21/8238

H01L 27/08

H01L 27/092

F 1

H01L 29/78 613A

H01L 27/08 331A

H01L 27/08 331E

H01L 27/08 321B

H01L 29/78 620

テーマコード(参考)

5FO48

5F110

審査請求有 請求項の数 39 O L (全 23 頁) 最終頁に続く

(21) 出願番号 特願2005-85789 (P2005-85789)

(22) 出願日 平成17年3月24日 (2005.3.24)

(31) 優先権主張番号 10/708907

(32) 優先日 平成16年3月31日 (2004.3.31)

(33) 優先権主張国 米国(US)

(71) 出願人 390009531

インターナショナル・ビジネス・マシーンズ・コーポレーション

INTERNATIONAL BUSINESS MACHINES CORPORATION

アメリカ合衆国10504 ニューヨーク

州 アーモンク ニュー オーチャード

ロード

(74) 代理人 100086243

弁理士 坂口 博

(74) 代理人 100091568

弁理士 市位 嘉宏

(74) 代理人 100108501

弁理士 上野 剛史

最終頁に続く

(54) 【発明の名称】集積回路構造及び形成方法(高移動度平面CMOS SOI)

## (57) 【要約】

【課題】特定のデバイスに最適な性能を与える異なる結晶方位を有する1つの基板上に形成された集積半導体デバイスを提供する。

【解決手段】少なくとも2つのタイプの結晶方位を有する基板を備える集積回路構造を開示する。第1のタイプの結晶方位を有する該基板の第1の部分の上に、第1のタイプのトランジスタ(例えばN F E T)を形成し、第2のタイプの結晶方位を有する該基板の第2の部分の上に、第2のタイプのトランジスタ(例えばP F E T)を形成する。この基板の第1の部分のうちのいくつかの部分は非浮遊基板部分を含み、基板の第1の部分の残りと全ての第2の部分とが、浮遊基板部分を含む。

【選択図】図7

**【特許請求の範囲】****【請求項 1】**

少なくとも 2 つのタイプの結晶方位を有する基板と、

第 1 のタイプの結晶方位を有する前記基板の第 1 の部分の上に形成された第 1 のタイプのトランジスタと、

第 2 のタイプの結晶方位を有する前記基板の第 2 の部分の上に形成された第 2 のタイプのトランジスタとを含む集積回路構造であって、

前記基板の前記第 1 の部分のうち選択された部分が、非浮遊基板部分を含み、

前記基板の前記第 1 の部分の残りの部分と前記第 2 の部分の全てとが、浮遊基板部分を含む、集積回路構造。

10

**【請求項 2】**

前記浮遊基板部分が、シリコン・オン・インシュレータ (S O I) 構造を含む、請求項 1 に記載の構造。

**【請求項 3】**

前記非浮遊基板部分が、前記基板の下の層によってバイアスされる、請求項 1 に記載の構造。

**【請求項 4】**

前記浮遊基板部分の下に完全な絶縁層をさらに含む、請求項 1 に記載の構造。

**【請求項 5】**

前記非浮遊基板部分の下に不完全な絶縁層をさらに含む、請求項 1 に記載の構造。

20

**【請求項 6】**

前記非浮遊基板部分と前記浮遊基板部分の間に浅いトレンチ分離 (S T I) 領域をさらに含む、請求項 1 に記載の構造。

**【請求項 7】**

前記基板の前記第 2 の部分がそれぞれ複数の浮遊基板部分を含む、請求項 1 に記載の構造。

**【請求項 8】**

少なくとも 2 つのタイプの結晶方位を有する基板と、

第 1 のタイプの結晶方位を有する前記基板の第 1 の部分の上に形成された N 型トランジスタと、

第 2 のタイプの結晶方位を有する前記基板の第 2 の部分の上に形成された P 型トランジスタとを含む集積回路構造であって、

30

前記基板の前記第 1 の部分のうち選択された部分が、非浮遊基板部分を含み、

前記基板の前記第 1 の部分の残りの部分と前記第 2 の部分の全てとが、浮遊基板部分を含む、集積回路構造。

**【請求項 9】**

前記浮遊基板部分が、シリコン・オン・インシュレータ (S O I) 構造を含む、請求項 8 に記載の構造。

**【請求項 10】**

前記非浮遊基板部分が、前記基板の下の層によってバイアスされる、請求項 8 に記載の構造。

40

**【請求項 11】**

前記浮遊基板部分の下に完全な（全て絶縁体の）絶縁層をさらに含む、請求項 8 に記載の構造。

**【請求項 12】**

前記非浮遊基板部分の下に不完全な絶縁層をさらに含む、請求項 8 に記載の構造。

**【請求項 13】**

前記非浮遊基板部分と前記浮遊基板部分の間に浅いトレンチ分離 (S T I) 領域をさらに含む、請求項 8 に記載の構造。

**【請求項 14】**

50

前記基板の前記第2の部分がそれぞれ複数の浮遊基板部分を含む、請求項8に記載の構造。

【請求項15】

集積回路構造を形成する方法であって、

第1の基板構造上に絶縁層を形成するステップと、

前記絶縁層に第2の基板構造を接合して、前記絶縁層の下に位置する第1の結晶方位を有する第1の基板および前記絶縁層の上に位置する第2の結晶方位を有する第2の基板を備える積層構造を形成するステップと、

前記第2の基板に、前記絶縁層まで延びる第1の開口を形成するステップと、

前記第1の開口より小さい第2の開口を前記第1の開口を貫通して前記絶縁層に形成して前記第1の基板を露出させるステップと、

前記第2の開口を貫通して前記第1の基板上に追加の材料を成長させて前記第1の開口を充填し、前記積層構造の上部に、前記第1のタイプの結晶方位を有する第1の部分および前記第2のタイプの結晶方位を有する第2の部分を備える表面を形成するステップと、

前記表面の前記第1の部分の上に第1のタイプのトランジスタを形成するステップと、

前記表面の前記第2の部分の上に第2のタイプのトランジスタを形成するステップとを含み、

前記表面の前記第1の部分のうち前記絶縁層の前記第2の開口の上に形成された部分が、非浮遊基板部分を含み、

前記表面の前記第1の部分の残りの部分と前記第2の部分の全てとが、浮遊基板部分を含む、方法。

【請求項16】

前記追加の材料が、前記第1の基板と同じ結晶方位を有する、請求項15に記載の方法。

【請求項17】

前記第1の開口を形成する前記ステップの前に、前記第2の基板を覆う保護キャップを形成するステップをさらに含み、前記第1の開口が、前記保護キャップおよび前記第2の基板を貫通して形成される、請求項15に記載の方法。

【請求項18】

前記第1の開口を形成した後に、前記第1の開口によって露出した前記第2の基板の側壁に沿って分離材料を形成するステップをさらに含む、請求項15に記載の方法。

【請求項19】

前記追加の材料を成長させる前記ステップの後に、前記第1の部分および前記第2の部分に浅いトレンチ分離(S T I)構造を形成して前記第1の部分および前記第2の部分を細分割するステップをさらに含む、請求項15に記載の方法。

【請求項20】

前記第2の開口が前記浅いトレンチ分離構造の間の距離よりも小さくすることにより、前記第2の開口のそれぞれが隣接する2つの浅いトレンチ分離構造の間に位置するようになっている、請求項15に記載の方法。

【請求項21】

1タイプの結晶方位を有する材料を含む基板であって、第1の部分および第2の部分を含み、前記第1の部分の結晶構造が前記第2の部分の結晶構造に対して回転している基板と、

前記基板の前記第1の部分の上に形成された、第1のタイプのフィン型電界効果トランジスタ(F i n F E T)と、

前記基板の前記第2の部分の上に形成された第2のタイプのフィン型電界効果トランジスタとを含む集積回路構造であって、

前記第1のタイプのフィン型電界効果トランジスタが、前記第2のタイプのフィン型電界効果トランジスタのフィンと平行なフィンを有する、集積回路構造。

【請求項22】

10

20

30

40

50

前記基板が浮遊基板を含む、請求項 2 1 に記載の構造。

【請求項 2 3】

前記第 1 のタイプのフィン型電界効果トランジスタおよび前記第 2 のタイプのフィン型電界効果トランジスタが、シリコン・オン・インシユレータ ( S O I ) 構造を含む、請求項 2 2 に記載の構造。

【請求項 2 4】

前記浮遊基板の下に完全な絶縁層をさらに含む、請求項 2 2 に記載の構造。

【請求項 2 5】

前記基板の前記第 1 の部分と前記基板の前記第 2 の部分の間に、浅いトレンチ分離 ( S T I ) 領域をさらに含む、請求項 2 2 に記載の構造。 10

【請求項 2 6】

集積回路構造を形成する方法であって、

第 1 の基板構造上に絶縁層を形成するステップと、

前記絶縁層に第 2 の基板構造を接合して、前記第 1 の基板構造と前記第 2 の基板構造の間に前記絶縁層を有する積層構造を形成するステップであって、前記第 1 の基板構造および前記第 2 の基板構造が同じタイプの結晶方位を有し、前記第 1 の基板構造の結晶構造が前記第 2 の基板構造の結晶構造に対して回転しているステップと、

前記第 1 の基板構造に、前記第 2 の基板構造まで延びる開口を形成するステップと、

前記開口を貫通して前記第 2 の基板構造上に材料を成長させて前記開口を充填して、前記積層構造の上部に、第 1 の部分および第 2 の部分を有する表面を形成するステップであって、前記第 1 の部分の結晶構造が前記第 2 の部分の結晶構造に対して回転しているステップと、 20

前記表面の前記第 1 の部分の上に第 1 のタイプのフィン型電界効果トランジスタを形成するステップと、

前記表面の前記第 2 の部分の上に第 2 のタイプのフィン型電界効果トランジスタを形成するステップとを含む方法。 20

【請求項 2 7】

前記開口を形成するステップの後に、前記開口の側壁に沿って分離材料を形成するステップをさらに含む、請求項 2 6 に記載の方法。 30

【請求項 2 8】

前記材料を成長させる前記ステップの後に、前記第 1 の部分および前記第 2 の部分に浅いトレンチ分離 ( S T I ) 構造を形成して前記第 1 の部分および前記第 2 の部分を細分割するステップをさらに含む、請求項 2 6 に記載の方法。 30

【請求項 2 9】

集積回路構造を形成する方法であって、

第 1 の基板構造上に絶縁層を形成するステップと、

前記絶縁層に第 2 の基板構造を接合して、前記第 1 の基板構造と前記第 2 の基板構造の間に前記絶縁層を有する積層構造を形成するステップであって、前記第 1 の基板構造および前記第 2 の基板構造が同じタイプの結晶方位を有し、前記第 1 の基板構造の結晶構造が前記第 2 の基板構造の結晶構造に対して回転しているステップと、 40

前記第 2 の基板に、前記絶縁層まで延びる第 1 の開口を形成するステップと、

前記第 1 の開口より小さい第 2 の開口を前記第 1 の開口を貫通して前記絶縁層に形成して前記第 1 の基板構造を露出させるステップと、

前記第 2 の開口を貫通して前記第 1 の基板構造上に材料を成長させて前記第 1 の開口を充填して、前記積層構造の上部に、第 1 の部分および第 2 の部分を有する表面を形成するステップであって、前記第 1 の部分の結晶構造が前記第 2 の部分の結晶構造に対して回転しているステップと、

前記表面の前記第 1 の部分の上に第 1 のタイプのフィン型電界効果トランジスタ ( F i n F E T ) を形成するステップと、

前記表面の前記第 2 の部分の上に第 2 のタイプのフィン型電界効果トランジスタを形成 50

するステップとを含み、

前記表面の前記第1の部分のうち前記絶縁層の前記第2の開口の上に形成された部分が、非浮遊基板部分を含み、

前記表面の前記第1の部分の残りの部分と前記第2の部分の全てとが、浮遊基板部分を含む、方法。

【請求項30】

前記第1の開口を形成する前記ステップの前に、前記第2の基板構造を覆う保護キャップを形成するステップをさらに含み、前記第1の開口が、前記保護キャップおよび前記第2の基板を貫通して形成される、請求項29に記載の方法。

【請求項31】

前記第1の開口を形成するステップの後に、前記第1の開口によって露出した前記第2の基板の側壁に沿って分離材料を形成するステップをさらに含む、請求項29に記載の方法。

【請求項32】

前記材料を成長させる前記ステップの後に、前記第1の部分および前記第2の部分に浅いトレンチ分離(STI)構造を形成して前記第1の部分および前記第2の部分を細分割するステップをさらに含む、請求項29に記載の方法。

【請求項33】

前記第1の基板が、前記第2の基板に対して45°回転している、請求項29に記載の方法。

【請求項34】

集積回路構造を形成する方法であって、

第1の結晶方位を有する第1の基板構造上に絶縁層を形成するステップと、

第2の結晶方位を有する第2の基板構造を前記絶縁層に接合して、積層構造を形成するステップと、

前記第1の基板構造および前記絶縁層に開口を形成して、前記第2の基板構造の一部分を露出させるステップと、

前記第2の基板構造の露出部分の上にシリコン・ゲルマニウム層を形成するステップと、

前記開口を貫通して前記シリコン・ゲルマニウム層の上に材料を成長させて前記開口を充填し、前記積層構造の上部に、前記第1の結晶方位を有する第1の部分および前記第2の結晶方位を有する第2の部分を有する表面を形成するステップと、

前記第1の部分および前記第2の部分をパターン形成して第1のタイプのフィンおよび第2のタイプのフィンを形成するステップであって、前記第1のタイプのフィンは前記第1の結晶方位を有し、かつ前記絶縁層によって前記第2の基板から絶縁され、前記第2のタイプのフィンは前記第2の結晶方位を有し、かつ前記シリコン・ゲルマニウム層の上に位置するステップと、

前記シリコン・ゲルマニウム層を絶縁層に変化させるステップとを含む方法。

【請求項35】

前記シリコン・ゲルマニウム層を形成するステップの前に、さらに追加の絶縁層を用いて、前記開口内の前記第1の基板の露出した側壁部分を保護するステップをさらに含む、請求項34に記載の方法。

【請求項36】

前記シリコン・ゲルマニウム層を絶縁層に変化させる前記ステップが、前記シリコン・ゲルマニウム層の全厚にわたってを酸化することを含む、請求項34に記載の方法。

【請求項37】

前記シリコン・ゲルマニウム層を絶縁層に変化させる前記ステップが、

前記第1のタイプのフィンおよび前記第2のタイプのフィンについて選択的に前記シリコン・ゲルマニウムを除去するステップと、

前記第2の基板構造上に前記絶縁層を形成するステップとを含む、請求項34に記載の

10

20

30

40

50

方法。

【請求項 3 8】

前記第1の基板構造および前記第2の基板構造が、同じタイプの結晶方位を有し、前記第1の基板構造の結晶構造が、前記第2の基板構造の結晶構造に対して回転している、請求項3 4に記載の方法。

【請求項 3 9】

前記第1の基板構造および前記第2の基板構造が、異なるタイプの結晶方位を有する、請求項3 4に記載の方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、半導体デバイスに関する。さらに詳細には、本発明は、シリコン・オン・インシュレータ(SOI)デバイスや相補型金属酸化膜半導体(CMOS)デバイスなど、ハイブリッド結晶方位基板上に形成される集積半導体デバイスに関する。特に、本発明は、N F E TおよびP F E Tなど、少なくとも2種類の半導体デバイスを、異なる結晶方位を有する接合基板上に集積する手段を提供する。接合基板上の各デバイスの位置は、特定の結晶方位における当該デバイスの性能によって決まる。例えば、本発明では、(100)面にN F E Tを形成し、(110)面にP F E Tを形成する。(100)結晶面はN F E Tに高い性能を与える、(110)結晶面はP F E Tに高い性能を与える。

【背景技術】

【0 0 0 2】

現在の半導体技術では、N F E TやP F E TなどのCMOSデバイスは、通常、S iなど単一の結晶方位を有する半導体ウェハ上に作製される。特に、今日の半導体デバイスは、(100)結晶方位を有するS iの上に構築されるものがほとんどである。

【0 0 0 3】

電子の移動度は、(100)S i面方位で高いことが分かっており、一方、正孔の移動度は、(110)面方位で高いことが分かっている。すなわち、(100)S iにおける正孔の移動度の値は、この結晶方位での対応する電子移動度より約1/4倍から1/2倍の低さとなる。この不一致を補償するために、通常、P F E Tは、そのプルアップ(pull-up)電流をN F E Tのプルダウン電流(pull-down)と釣り合わせて一様な回路スイッチングを実現するために、幅を広くして設計される。幅の広いN F E Tは、かなりのチップ領域を占めるので望ましくない。

【0 0 0 4】

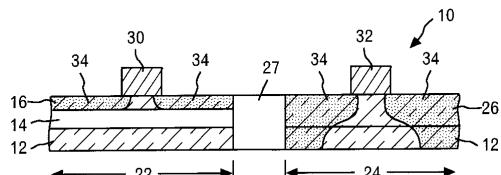

一方、(110)S iにおける正孔の移動度は、(100)S iにおける移動度の2倍である。したがって、P F E Tを(110)面に形成すると、(100)面に形成したP F E Tより大幅に大きな駆動電流を示す。残念ながら、(110)S i面における電子の移動度は、(100)S i面に比べるとかなり低下している。(110)S i面における電子移動度の低下の一例を、図1に示す。図1において、実線は電子の移動度を示し、破線は正孔の移動度を示している。

【0 0 0 5】

上記の説明と図1から推察されるように、(110)S i面は、正孔の移動度が高いのでP F E Tデバイスには最適であるが、この結晶方位はN F E Tデバイスには全く不向きである。逆に、(100)S i面は、電子が移動しやすいのでN F E Tデバイスに最適である。

【特許文献1】米国特許出願第10/708586号

【発明の開示】

【発明が解決しようとする課題】

【0 0 0 6】

上記の内容に鑑みて、特定のデバイスに最適な性能を与える異なる結晶方位を有する1つの基板上に形成された集積半導体デバイスを提供することが必要とされている。すなわ

10

20

30

40

50

ち、1つの基板でありながら、ある種類のデバイス（例えばP F E T）を有する結晶面（例えば（110）面）に形成する一方で別の種類のデバイス（例えばN F E T）を別の結晶面（例えば（100）面）に形成することができる基板を作製することに絶大なる要望がある。

【課題を解決するための手段】

【0007】

本発明は、集積回路構造を形成する方法を提供する。この方法では、最初に、第1の基板構造上に絶縁層を形成し、第2の基板構造を該絶縁層に接合して、第1の結晶方位を有する第1の基板を該絶縁層の下に有し、第2の結晶方位を有する第2の基板を該絶縁層の上に有する積層構造を形成する。次に、本発明では、この積層構造に絶縁層まで延びる第1の開口を形成し、第1の開口を貫通して絶縁層に第2の開口を形成する。第2の開口は、第1の開口より小さい。本発明では、第2の開口を貫通して第1の基板上に追加の材料を成長させて第1の開口を充填し、積層構造の上部に、第1のタイプの結晶方位を有する第1の部分および第2のタイプの結晶方位を有する第2の部分を備える表面を形成する。本発明では、次に、基板の第1の部分の上に第1のタイプのトランジスタ（例えばN F E T）を形成し、基板の第2の部分の上に第2のタイプのトランジスタ（例えばP F E T）を形成する。基板の第1の部分のうち絶縁層の第2の開口の上に形成されている部分は、非浮遊（non-floating）基板部分を含み、基板の第1の部分の残りの部分および全ての第2の部分は、浮遊（floating）基板部分を含む。

【0008】

第1および第2の開口を貫通して成長させる追加の材料は、第1の基板と同じ結晶方位を有する。第1の開口を形成する前に、本発明では、第2の基板を覆う保護キャップを形成する。第1の開口は、保護キャップおよび第2の基板を貫通して形成される。第1の開口を形成した後で、本発明では、第1の開口によって露出した第2の基板の側壁に沿って分離材料を形成する。上記追加の材料を成長させた後で、本発明では、第1の部分および第2の部分に浅いトレンチ分離（S T I）構造を形成して、第1の部分および第2の部分を細分割する。第2の開口は、浅いトレンチ分離構造の間の距離より小さくすることにより、第2の開口のそれぞれが、隣接する2つの浅いトレンチ分離構造の間に位置するようになっている。

【0009】

この方法では、少なくとも2タイプの結晶方位を有する基板を有する集積回路構造を作製する。第1のタイプのトランジスタ（例えばN F E T）は、第1のタイプの結晶方位を有する基板の第1の部分の上に形成され、第2のタイプのトランジスタ（例えばP F E T）は、第2のタイプの結晶方位を有する基板の第2の部分の上に形成される。基板の第1の部分のいくつかは非浮遊基板部分を含み、基板の第1の部分の残りの部分および全ての第2の部分は、浮遊基板部分を含む。

【0010】

浮遊構造は、シリコン・オン・インシュレータ（S O I）構造を含み、非浮遊構造は、バイアス（biased）基板構造またはバルク基板構造を含む。非浮遊基板部分は、基板の下の層によって電気的にバイアスされる。絶縁層は、浮遊基板部分の下に位置し、これらの領域を全て絶縁体からなる完全な絶縁層により基板の下の層から電気的に分離する。小さな第2の開口があるので、実際に非浮遊基板部分の下にあるのは不完全な絶縁体からなる絶縁層である。非浮遊基板部分と浮遊基板部分の間には、浅いトレンチ分離（S T I）領域がある。前記基板の第2の部分はそれぞれ、複数の浮遊基板部分を含む。

【0011】

本発明の1つの独特な態様は、小さな第2の開口があるために、非浮遊基板部分の下にある絶縁層が、実際には不完全な絶縁体である点である。この実施形態の別の独特な態様は、基板の第1の部分のいくつかが非浮遊基板部分を含み、基板の残りの第1の部分（および全ての第2の部分）が、浮遊基板部分を含む点である。したがって、本発明によれば、1つの結晶方位タイプの基板群内で、どのトランジスタをS O Iトランジスタにし、ど

10

20

30

40

50

のトランジスタをバルク・トランジスタにするかを、設計者が選択することができる。

**【0012】**

本発明の上記その他の態様および目的は、以下の説明と添付の図面とを併せて考察すれば、より深く認識され理解されるであろう。ただし、本発明の好ましい実施形態とその具体的な多数の詳細を示す以下の説明は、限定を目的としたものではなく、例示を目的としたものであることを理解されたい。多くの変更および改変を、本発明の趣旨を逸脱することなく本発明の範囲内で行うことができ、本発明はこのような改変を全て包含する。

**【0013】**

本発明は、図面を参照して以下の詳細な説明を読むことによってより理解されるであろう。

10

**【発明を実施するための最良の形態】**

**【0014】**

本発明ならびにその様々な特徴および利点は、添付の図面に図示し以下の説明で詳述する非限定的な実施形態に関連してより完全に説明される。図面で図示した各要素は、必ずしも寸法の比率どおりに描いたものではないことに留意されたい。本発明が無用に曖昧になるのを避けるために、周知の構成要素および処理技術についての説明は省略する。本明細書で用いる例は、単に本発明の実施方法の理解を助け、さらに当業者が本発明を実施できるようにするためのものである。したがって、これらの例は、本発明の範囲を限定しないものと理解されたい。

**【0015】**

以下、異なる結晶面を有する1つの接合基板上にN F E TやP F E Tなど異なる半導体デバイスを形成する方法について、本願に添付の図面を参照しながらより詳細に説明する。添付の図面では、同じか、または対応する要素は、同じ参考番号で示してある。

20

**【0016】**

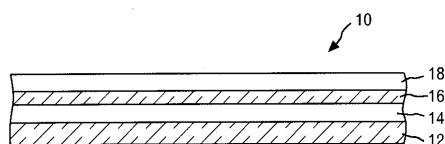

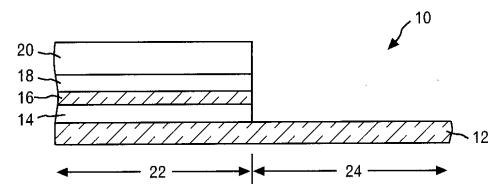

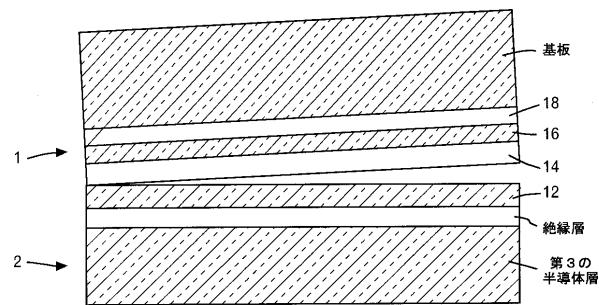

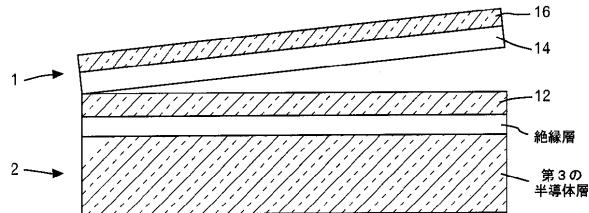

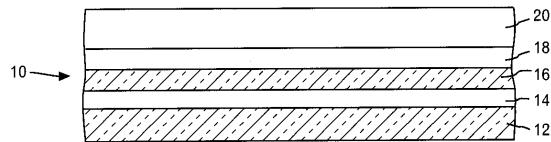

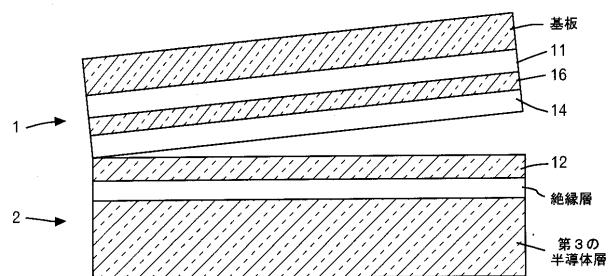

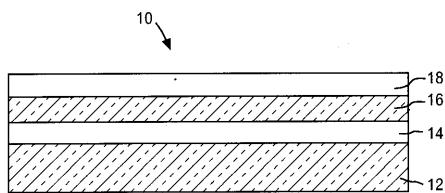

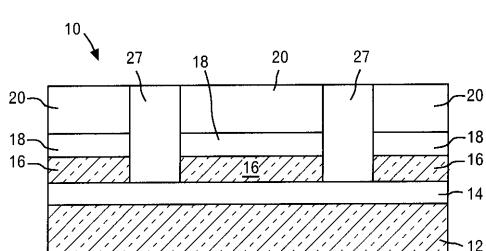

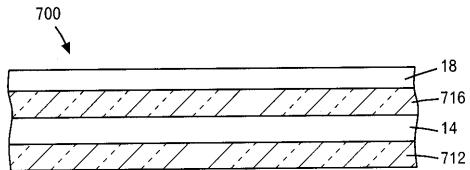

図2は、本発明で利用することができる接合基板10、すなわちハイブリッド基板を示す図である。図示のように、接合基板10は、表面誘電体層18、第1の半導体層16、絶縁層14、および第2の半導体層12を含む。必要なら、接合基板10は、第2の半導体層12の下に位置する第3の半導体層（図示せず）をさらに含むこともできる。その場合の接合基板では、絶縁層をもう1つ設けて、第2の半導体層12を（任意選択の）第3の半導体層から分離する。

30

**【0017】**

接合基板10の表面誘電体層18は、接合前に初期ウェハの1つに既に形成されていたか、あるいはウェハ接合後に熱プロセス（すなわち酸化、窒化もしくは酸窒化）または堆積によって第1の半導体層16の上に形成した、酸化物、窒化物、酸窒化物または他の絶縁層である。表面誘電体層18は、その由来に関わらず、約3nmから約500nmの厚さを有する。より好ましくは、約5nmから約20nmの厚さを有する。

**【0018】**

第1の半導体層16は、例えばSi、SiC、SiGe、SiGeC、Ge合金、GaAs、InAs、InP、および他のII-V族化合物半導体またはII-VI族化合物半導体など、任意の半導体材料から構成される。また、第1の半導体層16は、予備形成したSOI基板からなるSOI層、または例えばSi/SiGeなどの層状半導体を含むこともできる。また、第1の半導体層16は、好ましくは(110)である第1の結晶方位を有することも特徴とする。好ましい結晶方位は(110)であるが、第1の半導体層16は、(111)結晶方位または(100)結晶方位を有することもできる。

40

**【0019】**

第1の半導体層16の厚さは、接合基板10を形成するために使用する初期のウェハによって、変えることができる。ただし、通常は、第1の半導体層16は、約5nmから約500nmの厚さを有し、約5nmから約100nmの厚さであることがより好ましい。

**【0020】**

第1の半導体層16と第2の半導体層12の間に位置する絶縁層14は、接合基板10

50

の作製に使用した初期のウェハによって決まる可変の厚さを有する。ただし、通常は、絶縁層14は、約1nmから約500nmの厚さを有し、約5nmから約100nmの厚さであることがより好ましい。絶縁層14は、接合前のウェハの一方または両方に形成した、酸化物またはその他の同様の絶縁材料である。

#### 【0021】

第2の半導体層12は任意の半導体材料で構成され、その材料は、第1の半導体層16と同じであっても別のものであってもよい。したがって、第2の半導体層12は、例えば、Si、SiC、SiGe、SiGeC、Ge合金、GaAs、InAs、InP、およびその他のII-V族化合物半導体、またはII-VI族化合物半導体などを含むことができる。また、第2の半導体層12は、予備形成したSOI基板からなるSOI層、または例えばSi/SiGeなどの層状半導体を含むこともできる。また、第2の半導体層12は、第1の結晶方位とは異なる第2の結晶方位を有することも特徴とする。FETトランジスタを備えた構造を形成するときには、異なる結晶方位を有する材料を使用するのではなく、同じ材料の基板を使用して、接合プロセス中に一方の基板60を他方の基板64に対して45°回転させて異なる結晶方位をもたらすことができる。第1の半導体層16は(110)面であることが好ましいので、第2の半導体層12の結晶方位は(100)であることが好ましい。好ましい結晶方位は(100)であるが、第2の半導体層12は、(111)結晶面または(110)結晶面構造を有することもできる。

#### 【0022】

第2の半導体層12の厚さは、接合基板10を形成するために使用する初期のウェハによって、変えることができる。ただし、通常は、第2の半導体層12は、約5nmから約200nmの厚さを有し、約5nmから約100nmの厚さであることがより好ましい。

#### 【0023】

必要に応じて第3の半導体層を設けた場合には、第3の半導体層を構成する材料は、第2の半導体層12と同じ半導体材料であっても別の半導体材料であってもよい。第3の半導体層の結晶方位は、通常は第2の半導体層と同じであるが、必ず同じになるわけではない。第3の半導体層は、一般に第2の半導体層12より厚い。第3の層を設けた場合には、絶縁層を設けて、第3の半導体層を第2の半導体層から分離する。

#### 【0024】

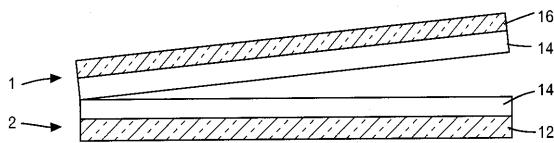

図2に示す接合基板10は、共に接合された2枚の半導体ウェハで構成されている。接合基板10の作製に使用する2枚のウェハは、一方のウェハ(参照番号1で示す)が第1の半導体層16を含み、もう一方のウェハ(参照番号2で示す)が第2の半導体層12を含む2枚のSOIウェハである場合(図8参照)、1枚のSOIウェハ(参照番号2)と1枚のバルク半導体ウェハ(参照番号1)である場合(図9参照)、それぞれが絶縁層14を有する2枚のバルク半導体ウェハ(参照番号1および2)である場合(図10参照)、または1枚のSOIウェハ(参照番号2)と、接合中に少なくとも一方のウェハの一部分を分割するために使用することができる水素(H<sub>2</sub>)注入領域などのイオン注入領域11を含む1枚のバルク・ウェハ(参照番号1)である場合(図11参照)などがある。

#### 【0025】

接合は、最初に2枚のウェハを互いに密着させ、必要ならこれらの接触させたウェハに外力を加え、次いで、これら2枚の接触したウェハを互いに接合できる条件下で加熱することによって行う。加熱ステップは、外力を加えて行うこと、加えずに行うこともある。加熱ステップは、通常は、約200から約1050の温度で、約2時間から約20時間、不活性雰囲気中で行う。より好ましくは、接合は、約200から約400の温度で、約2時間から約20時間行う。「不活性雰囲気」という用語は、本発明では、HeやAr、N<sub>2</sub>、Xe、Krまたはそれらの混合物などの不活性ガスをその中に含む雰囲気を意味している。接合プロセス中に使用される好ましい雰囲気は、N<sub>2</sub>である。

#### 【0026】

2枚のSOIウェハを使用する実施形態では、接合後に、少なくとも一方のSOIウェハのいくつかの材料層を、化学機械的研磨(CMP)や研削(grinding)およびエッテン

グなどの平坦化プロセスによって除去することができる。平坦化プロセスは、表面誘電体層 18 に達したときに終了する。

#### 【0027】

一方のウェハがイオン注入領域を含む実施形態では、接合中にイオン注入領域が多孔性 (porous) 領域を形成し、これにより当該ウェハのイオン注入領域の上の部分が分離され、例えば図 2 に示すような接合ウェハが残る。注入領域は、通常は、当業者には周知のイオン注入条件を利用してウェハ表面に注入された水素イオンから構成される。

#### 【0028】

接合するウェハがいずれも誘電体層を含まない実施形態では、表面誘電体層 18 は、酸化などの熱プロセス、または化学的気相堆積 (CVD)、プラズマ増強 CVD、原子層堆積、化学溶液付着およびその他の同様の堆積プロセスなどの従来の堆積プロセスによって、接合したウェハの上に形成することができる。

#### 【0029】

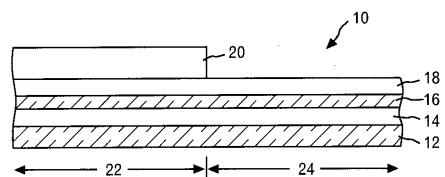

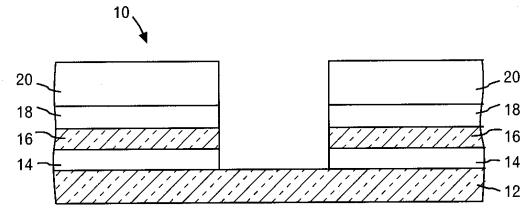

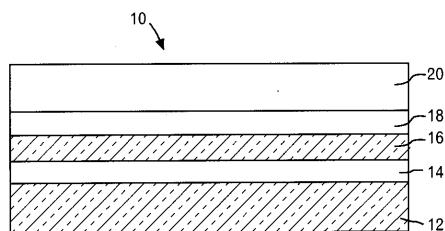

次いで、接合基板 10 の一部分を保護し、別の部分を保護しない状態で残すように、図 2 の接合基板 10 の所定部分の上にマスク 20 を形成する。接合基板 10 の保護された部分は、この基板の第 1 のデバイス領域 22 を画定し、保護されない部分は、第 2 のデバイス領域 24 を画定する。一実施形態では、マスク 20 は、フォトレジスト・マスクを接合基板 10 の表面全体に塗付することによって、表面誘電体層 18 の所定部分に形成される。フォトレジスト・マスクを塗付した後で、リソグラフィによってマスク・パターンを形成する。リソグラフィは、フォトレジストを放射光パターンで露光するステップと、レジスト現像装置を用いてこのパターンを現像するステップとを含む。こうして得られた接合基板 10 の所定部分にマスク 20 が形成された基板の例を、図 3 に示す。

#### 【0030】

別の実施形態では、マスク 20 は、リソグラフィおよびエッチングを利用して形成およびパターン形成した窒化物または酸窒化物の層である。窒化物または酸窒化物のマスク 20 は、第 2 の半導体デバイスの領域を画定した後で除去することもできる。

#### 【0031】

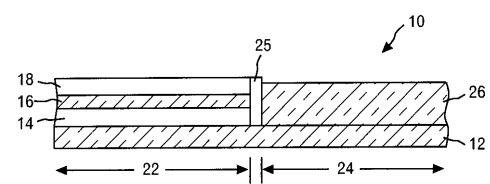

接合基板 10 にマスク 20 を形成した後で、第 2 の半導体層 12 の表面が露出するよう、この基板に 1 回または複数回のエッチング・ステップを施す。詳細には、本発明のこの時点で用いる 1 回または複数回のエッチング・ステップでは、表面誘電体層 18 の保護されていない部分、ならびにその下に位置する第 1 の半導体層 16 の部分、および第 1 の半導体層 16 を第 2 の半導体層 12 から分離する絶縁層 14 の一部分を除去する。エッチングは、1 回のエッチング・ステップで行ってもよいし、あるいは複数のエッチング・ステップを利用してもよい。本発明のこの時点で用いるエッチングとしては、反応性イオン・エッチングやイオン・ビーム・エッチング、プラズマ・エッチング、レーザ・エッチングなどのドライ・エッチング・プロセス、または化学エッチング液を利用するウェット・エッチング・プロセス、あるいはそれらの任意の組合せを利用することができます。本発明の好みの実施形態では、第 2 の半導体デバイス領域 24 内の表面誘電体層 18、第 1 の半導体層 16 および絶縁層 14 の保護されていない部分を選択的に除去する際に、反応性イオン・エッチング (RIE) を使用する。エッチング・ステップを行った後で得られる構造の一例を、図 4 に示す。このエッチング・ステップの後では、保護されている第 1 のデバイス領域 22、すなわち表面誘電体層 18、第 1 の半導体層 16、絶縁層 14 および第 2 の半導体層 12 の側壁が露出していることに留意されたい。図示のように、層 18、16 および 14 の露出した側壁は、マスク 20 の最も外側の縁部と位置合わせされている。

#### 【0032】

次いで、従来のレジスト剥離プロセスを用いて図 4 に示す構造からマスク 20 を除去し、次いで露出した側壁上にライナ (liner) またはスペーサ 25 を形成する。ライナまたはスペーサ 25 は、堆積およびエッチングによって形成される。ライナまたはスペーサ 25 は、例えば酸化物などの絶縁材料で構成される。

10

20

30

40

50

## 【0033】

ライナまたはスペーサ25を形成した後で、露出した第2の半導体層12の上に半導体材料26を形成する。本発明によれば、半導体材料26は、第2の半導体層12の結晶方位と同じ結晶方位を有する。これにより得られる構造の一例を、図5に示す。

## 【0034】

半導体材料26は、Siや歪Si、SiGe、SiC、SiGeCまたはそれらの組合せなど、選択的エピタキシャル成長法によって形成することができる任意のSi含有半導体を含むことができる。いくつかの好ましい実施形態では、半導体材料26はSiで構成される。別の好ましい実施形態では、半導体材料は、緩和SiGe合金層の上に位置する歪Si層である。本発明では、半導体材料26を再成長(regrown)半導体材料と呼ぶこともある。

10

## 【0035】

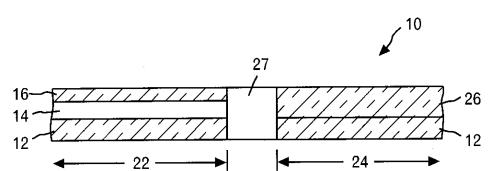

次に、半導体材料26の上面が第1の半導体層16の上面とほぼ同一面(同一平面)になるように、図5に示す構造に化学機械的研磨(CMP)または研削などの平坦化プロセスを施す。表面誘電体層18のそれまで保護されていた部分が、この平坦化プロセスの間に除去されることに留意されたい。

## 【0036】

実質的に平坦な表面を準備した後で、通常は、浅いトレンチ分離(shallow trench isolation)領域などの分離領域27を形成して、第1の半導体デバイス領域22を第2の半導体デバイス領域24から分離する。分離領域27は、例えばトレンチを画定しエッチングするステップと、必要なら拡散バリヤでトレンチの内側を覆う(lining)ステップと、酸化物などのトレンチ誘電体でトレンチを充填するステップとを含む、当業者には周知の処理ステップを利用して形成される。トレンチ充填後に、この構造を平坦化することができ、必要なら高密度化(densification)プロセス・ステップを行ってトレンチ誘電体を高密度化することもできる。

20

## 【0037】

こうして得られた、分離領域27を含むほぼ平坦な構造の一例を、図6に示す。図示のように、図6の構造は、第1の結晶方位を有する露出した第1の半導体層16と、第2の半導体層12と同じ結晶方位を有する露出していない再成長半導体材料26とを含む。

30

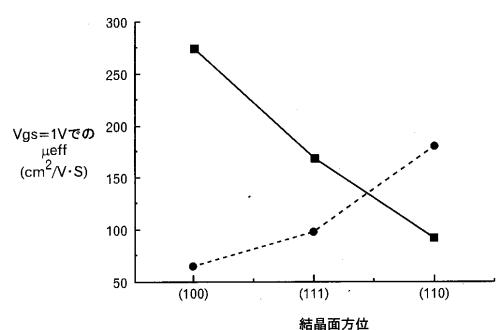

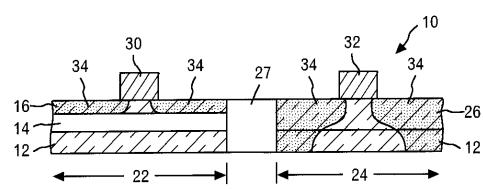

## 【0038】

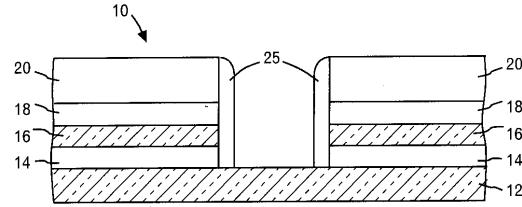

図7は、第1の半導体層16の一部の上に第1の半導体デバイス30を形成し、再成長半導体材料26の上に第2の半導体デバイス32を形成した後で形成される集積構造を示す図である。各デバイス領域に存在する半導体デバイスは1つずつしか示していないが、本発明では、それぞれのデバイス領域に各タイプのデバイスを複数形成することも考えられる。本発明によれば、第1の半導体デバイスが第2の半導体デバイスと異なること、および高性能デバイスとなる結晶方位でそれぞれのデバイスが作製されることを条件として、第1の半導体デバイスをPFETまたはNFETにし、第2の半導体デバイスをNFETまたはPFETにすることができる。PFETおよびNFETは、当業者には周知の標準的なCMOS処理ステップを利用して形成される。各FETは、ゲート誘電体、ゲート導体、ゲート導体の上に配置される任意選択のハード・マスク、少なくともゲート導体の側壁に位置するスペーサ、およびソース/ドレイン拡散領域を含む。拡散領域は、図7では参照番号34で示してある。PFETは(110)または(111)方位を有する半導体材料の上に形成され、NFETは(100)または(111)方位を有する半導体表面の上に形成されることに留意されたい。

40

## 【0039】

上記説明および図2乃至図7は、異なる2つの結晶方位を有する接合基板の提供、マスキング、エッチング、再成長、平坦化およびデバイス形成を含む、本発明の基本概念を説明するものである。図12乃至図21を参照して行う以下の説明では、(100)結晶面に形成された2つのNFETと、これらのNFETの間に位置する、(110)結晶面に形成された1つのPFETとを含む高性能半導体デバイスを形成する際に使用される処理

50

ステップを例示する。

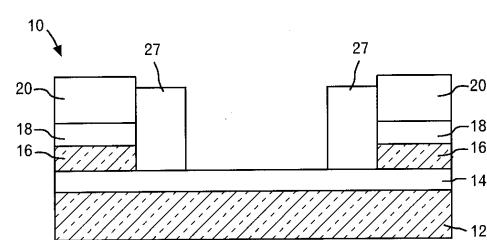

【0040】

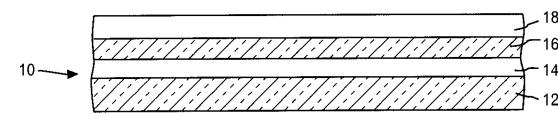

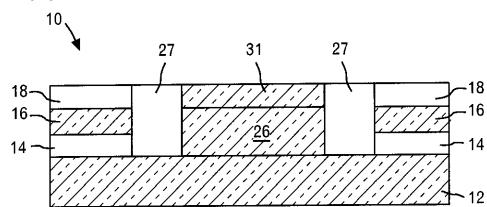

図12は、本発明のこの実施形態で使用することができる接合基板10を示す図である。接合基板10は、表面誘電体層18、第1の半導体層16、絶縁層14、および第2の半導体層12を含む。必要なら、第3の半導体層を、第2の半導体層12の下に配置することもできる。そのような実施形態では、新たに絶縁層を設けて、第2の半導体層を第3の半導体層から分離する。

【0041】

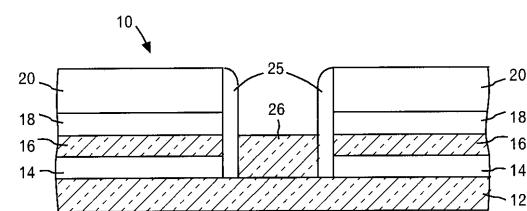

図13は、表面誘電体層18の上に窒化物マスク20を形成した後の構造を示している。窒化物マスク20は、CVDなど、従来の堆積プロセスを利用して形成される。

10

【0042】

窒化物マスク20を形成した後で、パターン形成したフォトレジスト・マスクを使用してエッチングを行ってマスクにパターン形成し、次いで、もう一度エッチング・プロセスを行ってこのパターンを窒化物マスクから構造に転写する。このエッチングは、第2の半導体層12の上側表面層に達するまで行う。この2回目のエッチング・プロセスのエッチングでは、表面誘電体層18、第1の半導体層16および絶縁層14の一部を除去する。接合基板10にパターンを転写する際には、1回または複数回のエッチング・プロセスを行う。こうして得られたパターン転写後の構造を、図14に示す。

【0043】

次に、図15に示すように、露出した側壁にスペーサ25を形成する。スペーサ25は、例えば酸化物などの絶縁材料で構成される。保護された第1のデバイス領域の側壁に配置されたスペーサ25は、堆積およびエッチングによって形成される。

20

【0044】

スペーサ25を形成した後で、第2の半導体層12の露出表面上に半導体材料26を形成して、例えば図16に示す構造を形成する。次いで、図16に示す構造を平坦化して、図17に示すほぼ平坦な構造を形成する。平坦化ステップでは、それまでにエッチングで除去されなかった窒化物マスク20および表面誘電体層18を除去して、第1の半導体層16が露出し、かつ再成長半導体材料26が露出した構造を形成することに留意されたい。露出した第1の半導体層16は、N F E Tなど第1の半導体デバイスを形成するための領域であり、半導体材料26の露出表面は、P F E Tなどの第2の半導体デバイスを形成するための領域である。

30

【0045】

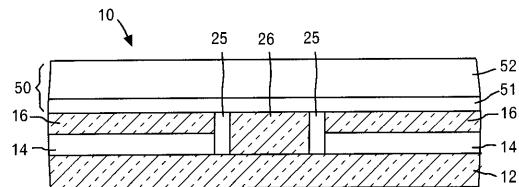

次に、図18に示すように、図17に示すほぼ平坦な構造の上に、パッド酸化物51およびパッド窒化物52を含む材料スタック50を形成する。材料スタック50のパッド酸化物51は、熱酸化プロセスまたは堆積によって形成され、パッド窒化物52は、熱窒化プロセスまたは堆積によって形成される。パッド窒化物52は、通常は、その下にあるパッド酸化物51より厚い。

【0046】

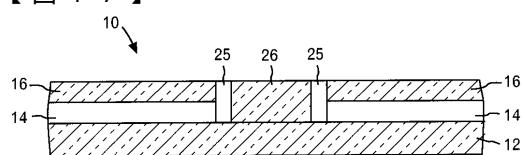

材料スタック50は、分離領域27用のトレンチ開口の画定に使用される。図19は、図18に示す構造にトレンチ開口29を形成した後の構造を示す図である。トレンチ開口29は、リソグラフィおよびエッチングによって形成される。

40

【0047】

トレンチ開口29を画定した後で、トレンチ開口29を、酸化物などのトレンチ誘電体で充填し、第1の半導体層16および再成長半導体材料26に合わせて平坦化する。図20は、トレンチ充填および平坦化を行った後の構造を示す図である。図20に示す構造は、3つのデバイス領域を含む。そのうちの2つを、第1の半導体デバイス30を形成するための第1のデバイス領域22と呼び、3つ目の領域を、第2の半導体デバイス32を形成するための第2のデバイス領域24と呼ぶ。

【0048】

図21は、第1の半導体デバイス30を第1の半導体層16の一部分の上に形成し、第

50

2 の半導体デバイス 3 2 を再成長半導体材料 2 6 の上に形成した後の集積構造を示す図である。各デバイス領域に存在する半導体デバイスは 1 つずつしか示していないが、本発明では、それぞれのデバイス領域に各タイプのデバイスを複数形成することも考えられる。本発明によれば、第 1 の半導体デバイスを P F E T ( または N F E T ) とし、第 2 の半導体デバイスを N F E T ( または P F E T ) とすることができます。P F E T および N F E T は、当業者には周知の標準的な C M O S 処理ステップを用いて形成する。各 F E T は、ゲート誘電体、ゲート導体、ゲート導体の上に配置される任意選択のハード・マスク、少なくともゲート導体の側壁に配置されるスペーサ、およびソース / ドレイン拡散領域を含む。P F E T は ( 1 1 0 ) または ( 1 1 1 ) 方位を有する表面の上に形成され、N F E T は ( 1 0 0 ) または ( 1 1 1 ) 方位を有する表面の上に形成されることに留意されたい。図 2 1 に示す構造では、N F E T は S O I 類似のデバイスであり、P F E T はバルク状の半導体デバイスである。第 2 の半導体層 1 2 の下に第 3 の半導体層が存在する場合には、3 つのデバイスが全て S O I 類似のデバイスとなる。

10

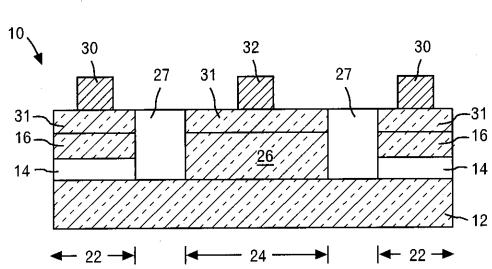

## 【 0 0 4 9 】

図 2 2 乃至図 2 8 は、( 1 0 0 ) 結晶面に形成された 2 つの N F E T と、それらの N F E T の間に位置する、( 1 1 0 ) 結晶面に形成された 1 つの P F E T とを含む高性能半導体デバイスを形成する際に使用される代替の処理方法を示す図である。この代替方法では、最初に、図 2 2 に示す接合基板を形成する。接合基板 1 0 は、少なくとも、表面誘電体層 1 8 、第 1 の半導体層 1 6 、絶縁層 1 4 および第 2 の半導体層 1 2 を含む。必要なら、第 2 の半導体層の下に第 3 の半導体層を配置することもできる。

20

## 【 0 0 5 0 】

次に、接合基板 1 0 上に窒化物マスク 2 0 を形成して、図 2 3 に示す構造を形成する。接合基板 1 0 上に窒化物マスク 2 0 を形成した後で、窒化物マスク 2 0 と表面誘電体 1 8 とを合わせてエッティング・マスクとして利用して、分離領域 2 7 を形成する。分離領域 2 7 は、窒化物マスク 2 0 の表面にフォトレジストを塗布し、フォトレジストをパターン形成し、このパターンをフォトレジストから窒化物マスク 2 0 に転写し、次に表面誘電体層 1 8 に転写することによって、第 1 の半導体層 1 6 が露出する。次いで、露出した第 1 の半導体層 1 6 を、絶縁層 1 4 の上面に達するまでエッティングする。次いで、このエッティング・ステップで形成されたトレンチをトレンチ誘電体で充填し、窒化物マスク 2 0 の上面に合わせて平坦化する。図 2 4 は、トレンチ充填および平坦化を行った後の構造を示す図である。特に、分離領域 2 7 を図 2 4 に示す。

30

## 【 0 0 5 1 】

次いで、分離領域と分離領域の間の材料を除去して、図 2 5 に示す構造を形成する。詳細には、分離領域と分離領域の間の材料の除去は、この構造の第 1 の半導体デバイスを形成するための部分を保護するブロック・マスクを形成し、窒化物マスク 2 0 、表面誘電体層 1 8 および第 1 の半導体層 1 6 の保護されていない部分を、絶縁層 1 4 に達するまでエッティングすることによって行う。

## 【 0 0 5 2 】

次いで、酸化物などの絶縁材料を選択的に除去するエッティング・ステップを利用して絶縁層 1 4 の露出部分を除去し、例えば図 2 6 に示す構造を形成する。このエッティング・ステップでは、分離領域 2 7 の高さも低くなることに留意されたい。このエッティング・ステップは、第 2 の半導体層 1 2 の上面に達したところで停止する。次いで、残りの窒化物マスク 2 0 をこの構造から剥離し、第 2 の半導体材料 1 2 の露出した表面上に半導体材料 2 6 を再成長させて、例えば図 2 7 に示す構造を形成する。この特定の実施形態では、再成長半導体材料 2 6 は、上側歪 S i 層 3 1 を含む。

40

## 【 0 0 5 3 】

次いで、図 2 7 に示す構造から酸化物を剥離し、第 1 の半導体層 1 6 の露出部分の上に歪 S i 層 3 1 を形成する。歪 S i 層を形成した後で、C M O S デバイス 3 0 および 3 2 を、それぞれ高性能デバイスを与える結晶方位で形成する。こうして得られた歪 S i 層の上に形成された N F E T および P F E T を含む構造の一例を、図 2 8 に示す。

50

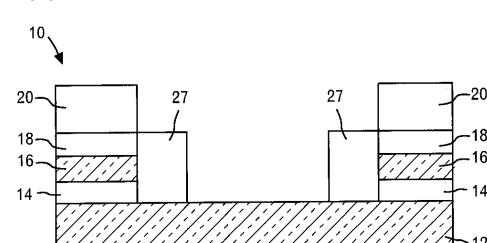

## 【0054】

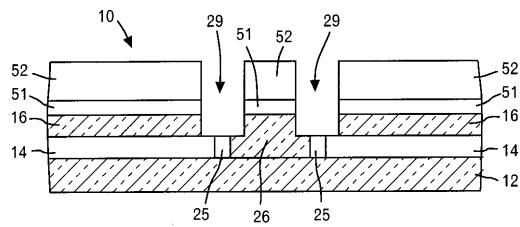

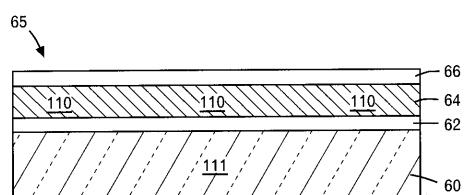

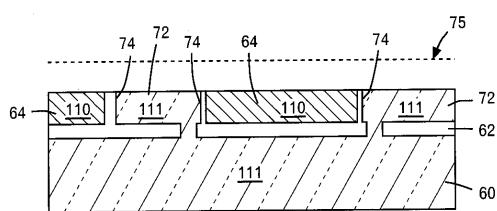

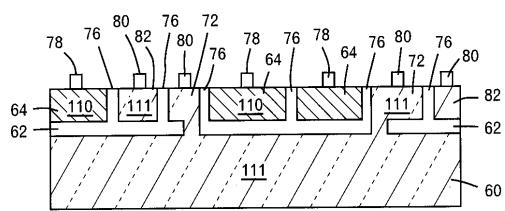

図29乃至図33は、選択的な浮遊基板および非浮遊基板を備えた集積回路構造を形成する方法を提供するさらに別の実施形態を示す図である。図29に示すように、この方法では、最初に、上述の方法および材料のいずれかを使用して、第1の基板60の構造上に絶縁層62を形成し、第2の基板64の構造を絶縁層62に接合して、積層構造65を形成する。上述のように、第1の基板60は第1の結晶方位を有することができ、第2の基板64は第2の結晶方位を有することができ、上述した基板のいずれかを含むことができる。本発明では、接合プロセスの前または後に、第2の基板64の上に保護キャップ66(例えば窒化物エッチング・トップ層など)を形成することができる。

## 【0055】

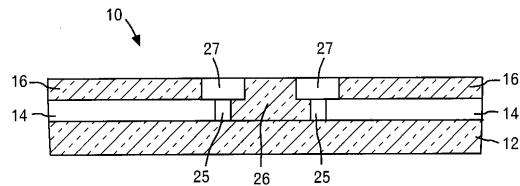

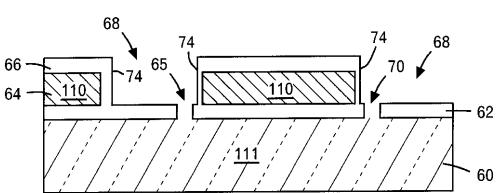

次に、図30に示すように、本発明では、絶縁層62まで下向きに延びる第1の開口68を積層構造65内に形成し、第1の開口68を貫通して、絶縁層62内に第2の開口70を形成する。第1の開口68は、保護キャップ66および第2の基板64を貫通して形成する。第2の開口70は、第1の開口68より小さい。第1の開口68を形成した後で、本発明では、第1の開口68によって露出した第2の基板64の側壁に沿って、分離材料74(例えば酸化物など)を形成する。

## 【0056】

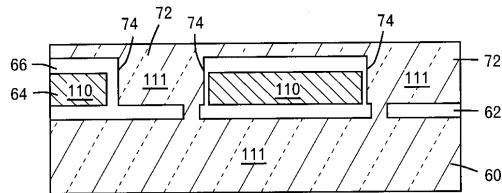

図31に示すように、本発明では、第2の開口70を通して追加の材料72をエピタキシャル成長させ(第1の基板60をシード材料として用いる)、少なくとも第1の開口68を充填する。第1の開口68および第2の開口70を通して成長させたこの追加の材料72は、第1の基板60から(これをシード材料として用いて)成長させた(例えばエピタキシャル・シリコン成長)ものであるので、第1の基板60と同じ結晶方位を有する。この構造を、図32に示すように平坦化して、積層構造65の上部に、第1のタイプの結晶方位を有する第1の部分72および第2のタイプの結晶方位を有する第2の部分64を有する基板表面75を形成する。

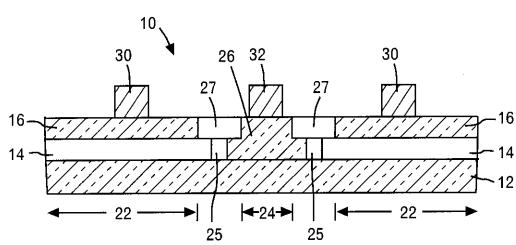

## 【0057】

次に、図33に示すように、本発明では、(例えば周知のパターン形成プロセスおよび絶縁層堆積/成長プロセスを用いて)第1の部分72および第2の部分64に浅いトレンチ分離(STI)構造を形成し、第1の部分72および第2の部分64をさらに細分割する。第2の開口70は、各浅いトレンチ分離構造76の間の距離よりも小さいので、第2の開口70のそれぞれが、隣接する2つの浅いトレンチ分離構造の間に位置するようになっている。

## 【0058】

基板の第1の部分72のうち、絶縁層62の第2の開口70の上に形成された部分は非浮遊基板部分72として残り、残りの第1の部分72は浮遊部分82となる(STI構造76の絶縁する働きによってその下にある基板60から分離される)。この基板の全ての第2の部分64は、浮遊基板部分として残る。

## 【0059】

したがって、これらのSOI構造76は、その下にある基板60から電気的に分離され(その上で浮遊する)シリコン・オン・インシュレータ(SOI)構造を含む「浮遊」構造82を形成し、その下にある基板60から分離されない(その上で浮遊していない)バイアス基板構造またはバルク基板構造を含むいくつかの「非浮遊」構造72を形成する。したがって、非浮遊基板部分72は、基板60(および基板60の下の層)によってバイアスされる。浮遊基板部分64、82の下の絶縁層62は、これらの領域を基板60から電気的に分離している。浅いトレンチ分離(STI)領域は、非浮遊基板部分72と浮遊基板部分64、82との間に存在する。

## 【0060】

本発明では、基板の第1の部分72の上に第1のタイプのトランジスタ80(例えばN-FET)を形成し、基板の第2の部分64の上に第2のタイプのトランジスタ78(P-FET)を形成する。したがって、この集積回路構造は、少なくとも2つのタイプの結晶方

位を有する基板表面 7 5 を有する。第 1 のタイプのトランジスタ（例えば N F E T（または P F E T））8 0 は、基板の第 1 の部分 7 2、8 2（第 1 のタイプの結晶方位、例えば 1 1 1 を有する）の上に形成され、第 2 のタイプのトランジスタ（例えば P F E T（または N F E T））7 8 は、第 2 のタイプの結晶方位（例えば 1 1 0 や 1 0 0 など）を有する基板の第 2 の部分 6 4 の上に形成される。これらのトランジスタとしては、水平相補型金属酸化膜半導体（C M O S）トランジスタまたはフィン型電界効果トランジスタ（F i n F E T）などがある。

#### 【 0 0 6 1 】

F i n F E T トランジスタを備えた構造を形成するときには、異なる結晶方位を有する材料を使用するのではなく、同じ材料の基板を使用して、接合プロセス中に一方の基板を他方の基板に対して 45° 回転させて異なる結晶方位をもたらすことができる。例えば、図 3 4 に示すように、F i n F E T を形成するときには、結晶方位の異なる様々な基板を利用する図 2、図 8、図 1 2、図 2 2 および図 2 9 に示す構造から開始するのではなく、本発明では、結晶方位が同じタイプである（例えば両方とも 1 1 0 または 1 1 1 である）同じ材料の基板 7 1 2 および 7 1 6 を有するが、一方の基板 7 1 2 の結晶構造が他方の基板 7 1 6 の結晶構造に対して角度をなしている（45° 回転している）構造 7 0 0 を利用することができる。F i n F E T を基板上に形成するときには、この構造を、図 2 から図 3 3 に示したのと全く同じ処理技術に適用することができる。本発明のこの態様の 1 つの利点は、全てのフィンを互いに平行に形成し、その上全てのフィンの結晶方位を異なる向きにすることである。

#### 【 0 0 6 2 】

本発明のこの実施形態の、前述の実施形態に比べて独特な点は、小さな第 2 の開口があることにより、非浮遊基板部分 7 2 の下にある絶縁層が、実際には不完全な絶縁体であるということである。この実施形態のもう 1 つの独特な点は、この基板の第 1 の部分 7 2 のいくつかの部分が非浮遊基板部分を含み、この第 1 の部分 7 2 の残りの部分（および全ての第 2 の部分 6 4 ）が、浮遊基板部分を含むことである。したがって、本発明によれば、1 つの結晶方位タイプの基板群内でどのトランジスタを S O I トランジスタにし、どのトランジスタをバルク・トランジスタにするかを設計者が選択することが可能になる。

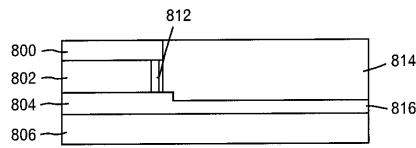

#### 【 0 0 6 3 】

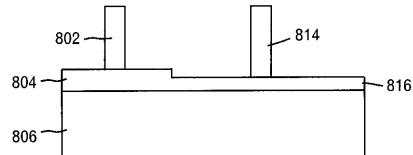

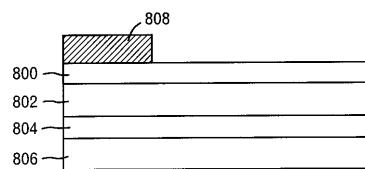

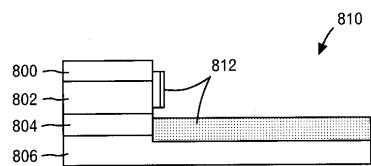

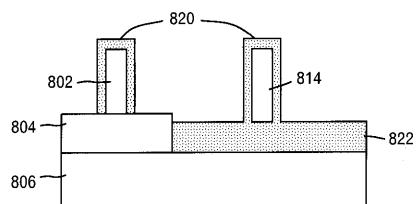

集積回路構造を形成する別の方法を図 3 5 から図 4 2 に示す。この実施形態は、異なる結晶方位を有する F i n F E T トランジスタの形成に関する。図 3 5 に示すように、この実施形態では、最初に、第 1 の結晶方位を有する第 1 の基板構造 8 0 2 に第 1 の絶縁層 8 0 4 を形成する。次に、本発明では、第 2 の結晶方位を有する第 2 の基板構造 8 0 6 を第 1 の絶縁層 8 0 4 に接合して、図 3 5 に示す積層構造を形成する。このプロセス中の任意の時点でさらに別の絶縁層 8 0 0 を形成することができる。

#### 【 0 0 6 4 】

第 1 の基板構造 8 0 2 および第 2 の基板構造 8 0 6 は、同じタイプの結晶方位を有することができるが、第 1 の基板構造 8 0 2 の結晶構造は第 2 の基板構造 8 0 6 の結晶構造に対して（例えば 45°）回転している。あるいは、第 1 の基板構造 8 0 2 および第 2 の基板構造 8 0 6 を、異なるタイプの結晶方位を有するように形成することもできる。

#### 【 0 0 6 5 】

次に、本発明では、積層構造の上でマスク 8 0 8 をパターン形成し、第 1 の基板構造 8 0 2 および絶縁層 8 0 4 に開口 8 1 0 を形成して、第 2 の基板構造 8 0 6 の一部分を露出させる（図 3 6 参照）。その後、本発明では、開口 8 1 0 内の第 1 の基板構造 8 0 2 の露出した側壁部分を保護する。方向性エッチング・プロセスを用いて絶縁層 8 1 2 の水平部分を除去し、絶縁層 8 1 2 の垂直部分のみが適所に残って、その後の処理中に第 1 の基板構造 8 0 2 の側壁部分を保護するようとする。

#### 【 0 0 6 6 】

図 3 7 に示すように、本発明では、次いで、第 2 の基板構造 8 0 6 の露出部分の上に直接シリコン・ゲルマニウム層 8 1 6 を形成する。次いで、本発明では、シリコン・ゲルマ

10

20

30

40

50

ニウム層 816 の上に開口 810 を通してシリコン材料 814 を成長（例えばエピタキシャル成長）させて開口 810 を充填し、図 37 に示す構造を形成する。シリコン材料 814 は、そのシード材料である材料 806 と同じ結晶方位を有することになる。ゲルマニウム濃度が十分に低く（例えば 10 ~ 15 %）、厚さが薄く保たれている（例えば < 1 μm）場合には、格子構造が維持され、歪み状態となる。Ge の濃度が高くなる、または厚さが厚くなると、格子欠陥が生じることになる。

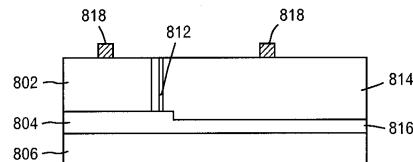

#### 【0067】

図 38 で、積層構造を平坦化して絶縁層 800 を除去し、水平な表面にする。より詳細には、平坦化後、積層構造の上部の表面は、第 1 の結晶方位を有する第 1 の部分 802 と、第 2 の結晶方位を有する第 2 の部分 814 とを有する。

10

#### 【0068】

図 38 に示す構造の上にマスク 818 を形成し、第 1 の部分 802 および第 2 の部分 814 をパターン形成して、図 39 に示すように第 1 のタイプのフィン 802 および第 2 のタイプのフィン 814 を形成する。第 1 のタイプのフィン 802 は、第 1 の結晶方位を有し、絶縁層 804 によって第 2 の基板 806 から絶縁されている。第 2 のタイプのフィン 814 は、第 2 の結晶方位を有し、シリコン・ゲルマニウム層 816 の上に配置されている。

#### 【0069】

第 2 のタイプのフィン 814 を第 2 の基板 806 から絶縁するために、本発明では、シリコン・ゲルマニウム層を絶縁層に変化させる。これは、図 40 に示すように、単純にシリコン・ゲルマニウム層 816 を酸化して酸化物層 822 にすることにより行うことができる。SiGe 層は、厚くすることもあり、必ずしも全体を酸化するとは限らない。要は、フィンを基板から分離するために、フィンの下の SiGe を酸化すればよい。その下がシリコンである一部の SiGe は、酸化されないまま残っていてもよい。

20

#### 【0070】

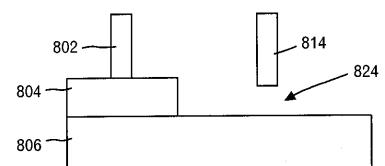

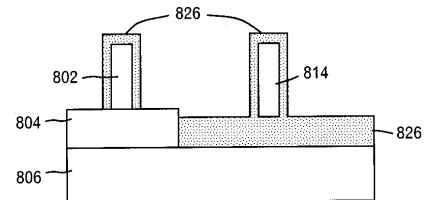

シリコン・ゲルマニウム層 816 の酸化は、シリコン・フィン 802 および 814 よりはるかに速く進行することになる。したがって、このシリコン・ゲルマニウム層 816 を酸化する酸化プロセスでは、フィン 802 および 814 は完全には酸化せず、フィン 802 および 814 の外側に酸化物 820 が生成されることになる。必要なら、この酸化物 820 を FinFET ドラフトランジスタのゲート酸化物として使用することもできる。あるいは、図 41 および図 42 に示すように、シリコン・ゲルマニウム層 816 を除去して、酸化物で置き換えることもできる。より詳細には、図 41 に示すように、選択的エッチング・プロセスを使用して、シリコン・フィン 802 および 814 にはほとんど影響を及ぼさず、シリコン・ゲルマニウム層 816 を除去することができる。この場合、第 2 のタイプのフィン 814 の下に隙間 824 が形成される。第 2 のタイプのフィン 814 は開口の 3 次元の側壁（図 35 から図 42 の概略断面図には図示せず）に接続されているので、このプロセスでは第 2 のタイプのフィン 814 が除去されないように留意されたい。その後、図 42 に示すように、本発明では、露出したシリコンの上に酸化物 826 を形成し、これが第 2 のタイプのフィン 814 と第 2 のタイプの基板 806 の間の絶縁層となる。この場合も、絶縁層 826 は、後続の処理中にゲート酸化物として使用することができる。

30

#### 【0071】

次いで、フィンの端部にドーピングを行ってソース領域およびドレイン領域を形成し、これらのフィンの中央部分の上にゲート導体を形成する。FinFET 技術の当業者には周知のように、この構造の上に様々な絶縁層を形成し、この絶縁層はソース、ドレイン、ゲート導体などに接触する。したがって、このプロセスでは、結晶方位の異なる複数のフィンを有し、それらのフィンがその下の基板から絶縁された FinFET ドラフトランジスタも同時に形成される。

40

#### 【0072】

好みしい実施形態に関連して本発明について説明したが、添付の特許請求の範囲の趣旨および範囲内で様々な修正を加えて本発明を実施することができることを、当業者なら理

50

解するであろう。

【図面の簡単な説明】

【0073】

【図1】Si基板のV<sub>g</sub>s = 1Vにおけるμeffを結晶方位に対してプロットした図である。

【図2】接合基板の結晶方位の異なる面上に集積CMOSデバイスを形成する際に本発明で用いる基本的な処理方法の1ステップを示す断面図である。

【図3】接合基板の結晶方位の異なる面上に集積CMOSデバイスを形成する際に本発明で用いる上記基本的な処理方法の1ステップを示す断面図である。

【図4】接合基板の結晶方位の異なる面上に集積CMOSデバイスを形成する際に本発明で用いる上記基本的な処理方法の1ステップを示す断面図である。 10

【図5】接合基板の結晶方位の異なる面上に集積CMOSデバイスを形成する際に本発明で用いる上記基本的な処理方法の1ステップを示す断面図である。

【図6】接合基板の結晶方位の異なる面上に集積CMOSデバイスを形成する際に本発明で用いる上記基本的な処理方法の1ステップを示す断面図である。

【図7】接合基板の結晶方位の異なる面上に集積CMOSデバイスを形成する際に本発明で用いる上記基本的な処理方法の1ステップを示す断面図である。

【図8】互いに接合することができる、図2から図7で説明した方法で使用することができる様々なウェハを示す断面図である。

【図9】互いに接合することができる、図2から図7で説明した方法で使用することができる様々なウェハを示す断面図である。 20

【図10】互いに接合することができる、図2から図7で説明した方法で使用することができる様々なウェハを示す断面図である。

【図11】互いに接合することができる、図2から図7で説明した方法で使用することができる様々なウェハを示す断面図である。

【図12】(100)結晶面に形成された2つのN-FETと、これらのN-FETの間に位置する(110)結晶面に形成された1つのP-FETとを含む高性能半導体デバイスを形成する際に本発明で用いる基本的な処理方法の1ステップを示す断面図である。 30

【図13】(100)結晶面に形成された2つのN-FETと、これらのN-FETの間に位置する(110)結晶面に形成された1つのP-FETとを含む高性能半導体デバイスを形成する際に本発明で用いる上記基本的な処理方法の1ステップを示す断面図である。

【図14】(100)結晶面に形成された2つのN-FETと、これらのN-FETの間に位置する(110)結晶面に形成された1つのP-FETとを含む高性能半導体デバイスを形成する際に本発明で用いる上記基本的な処理方法の1ステップを示す断面図である。

【図15】(100)結晶面に形成された2つのN-FETと、これらのN-FETの間に位置する(110)結晶面に形成された1つのP-FETとを含む高性能半導体デバイスを形成する際に本発明で用いる上記基本的な処理方法の1ステップを示す断面図である。

【図16】(100)結晶面に形成された2つのN-FETと、これらのN-FETの間に位置する(110)結晶面に形成された1つのP-FETとを含む高性能半導体デバイスを形成する際に本発明で用いる上記基本的な処理方法の1ステップを示す断面図である。 40

【図17】(100)結晶面に形成された2つのN-FETと、これらのN-FETの間に位置する(110)結晶面に形成された1つのP-FETとを含む高性能半導体デバイスを形成する際に本発明で用いる上記基本的な処理方法の1ステップを示す断面図である。

【図18】(100)結晶面に形成された2つのN-FETと、これらのN-FETの間に位置する(110)結晶面に形成された1つのP-FETとを含む高性能半導体デバイスを形成する際に本発明で用いる上記基本的な処理方法の1ステップを示す断面図である。

【図19】(100)結晶面に形成された2つのN-FETと、これらのN-FETの間に位置する(110)結晶面に形成された1つのP-FETとを含む高性能半導体デバイスを形成する際に本発明で用いる上記基本的な処理方法の1ステップを示す断面図である。

【図20】(100)結晶面に形成された2つのN-FETと、これらのN-FETの間に位 50

置する(110)結晶面に形成された1つのP F E Tとを含む高性能半導体デバイスを形成する際に本発明で用いる上記基本的な処理方法の1ステップを示す断面図である。

【図21】(100)結晶面に形成された2つのN F E Tと、これらのN F E Tの間に位置する(110)結晶面に形成された1つのP F E Tとを含む高性能半導体デバイスを形成する際に本発明で用いる上記基本的な処理方法の1ステップを示す断面図である。

【図22】(100)結晶面に形成された2つのN F E Tと、これらのN F E Tの間に位置する(110)結晶面に形成された1つのP F E Tとを含む高性能半導体デバイスを形成する際に使用する代替の処理方法の1ステップを示す断面図である。

【図23】(100)結晶面に形成された2つのN F E Tと、これらのN F E Tの間に位置する(110)結晶面に形成された1つのP F E Tとを含む高性能半導体デバイスを形成する際に使用する上記代替の処理方法の1ステップを示す断面図である。 10

【図24】(100)結晶面に形成された2つのN F E Tと、これらのN F E Tの間に位置する(110)結晶面に形成された1つのP F E Tとを含む高性能半導体デバイスを形成する際に使用する上記代替の処理方法の1ステップを示す断面図である。

【図25】(100)結晶面に形成された2つのN F E Tと、これらのN F E Tの間に位置する(110)結晶面に形成された1つのP F E Tとを含む高性能半導体デバイスを形成する際に使用する上記代替の処理方法の1ステップを示す断面図である。

【図26】(100)結晶面に形成された2つのN F E Tと、これらのN F E Tの間に位置する(110)結晶面に形成された1つのP F E Tとを含む高性能半導体デバイスを形成する際に使用する上記代替の処理方法の1ステップを示す断面図である。 20

【図27】(100)結晶面に形成された2つのN F E Tと、これらのN F E Tの間に位置する(110)結晶面に形成された1つのP F E Tとを含む高性能半導体デバイスを形成する際に使用する上記代替の処理方法の1ステップを示す断面図である。

【図28】(100)結晶面に形成された2つのN F E Tと、これらのN F E Tの間に位置する(110)結晶面に形成された1つのP F E Tとを含む高性能半導体デバイスを形成する際に使用する上記代替の処理方法の1ステップを示す断面図である。

【図29】選択的な浮遊基板および非浮遊基板を備えた集積回路構造を形成する方法を実現する代替の実施形態を説明する断面図である。

【図30】選択的な浮遊基板および非浮遊基板を備えた集積回路構造を形成する方法を実現する上記代替の実施形態を説明する断面図である。 30

【図31】選択的な浮遊基板および非浮遊基板を備えた集積回路構造を形成する方法を実現する上記代替の実施形態を説明する断面図である。

【図32】選択的な浮遊基板および非浮遊基板を備えた集積回路構造を形成する方法を実現する上記代替の実施形態を説明する断面図である。

【図33】選択的な浮遊基板および非浮遊基板を備えた集積回路構造を形成する方法を実現する上記代替の実施形態を説明する断面図である。

【図34】互いに回転させた複数の基板を使用する代替の実施形態を示す断面図である。

【図35】F i n F E Tを形成する方法を実現する代替の実施形態を示す断面図である。

【図36】F i n F E Tを形成する方法を実現する上記代替の実施形態を示す断面図である。 40

【図37】F i n F E Tを形成する方法を実現する上記代替の実施形態を示す断面図である。

【図38】F i n F E Tを形成する方法を実現する上記代替の実施形態を示す断面図である。

【図39】F i n F E Tを形成する方法を実現する上記代替の実施形態を示す断面図である。

【図40】F i n F E Tを形成する方法を実現する上記代替の実施形態を示す断面図である。

【図41】F i n F E Tを形成する方法を実現する上記代替の実施形態を示す断面図である。 50

【図42】FinFETを形成する方法を実現する上記代替の実施形態を示す断面図である。

【符号の説明】

【0074】

- 10 接合基板

- 12 第2の半導体層

- 14 絶縁層

- 16 第1の半導体層

- 18 表面誘電体層

- 20 マスク

- 22 第1のデバイス領域

- 24 第2のデバイス領域

- 25 スペーサ(ライナ)

- 26 半導体材料

- 27 分離領域

- 29 トレンチ開口

- 30 第1の半導体デバイス

- 31 歪Si層

- 32 第2の半導体デバイス

- 34 ソース/ドレイン拡散領域

10

20

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図13】

【図14】

【図15】

【図10】

【図11】

【図12】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図28】

【図26】

【図29】

【図27】

【図30】

【図3 1】

【図3 2】

【図3 3】

【図3 7】

【図3 8】

【図3 9】

【図3 4】

【図3 5】

【図3 6】

【図4 0】

【図4 1】

【図4 2】

---

フロントページの続き(51) Int.Cl.<sup>7</sup>

F I

テーマコード(参考)

H 01 L 29/78 618C

(72)発明者 ブレント・エイ・アンダーソン

アメリカ合衆国05465 バーモント州ジェリコ シリー・ヒル・ロード 221

(72)発明者 メイケイ・イオン

アメリカ合衆国12590 ニューヨーク州ワッピンガーズ・フォールズ サマリン・コート 3

1

(72)発明者 エドワード・ジェイ・ノワク

アメリカ合衆国05452 バーモント州エセックス・ジャンクション ウィンドリッジ・ロード

8F ターム(参考) 5F048 AC01 AC04 BA02 BA10 BA15 BA16 BA20 BC19 BD06 BD09

BG06 BG13

5F110 AA01 BB04 CC02 CC10 DD01 DD05 EE22 FF02 FF23 GG01

GG02 GG03 GG04 GG17 GG19 GG22 GG24 HM02 NN62 NN74

QQ17 QQ19