(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년11월11일

(11) 등록번호 10-1326335

(24) 등록일자 2013년10월31일

- (51) 국제특허분류(Int. Cl.)

**H03M 13/11** (2006.01)

- (21) 출원번호 10-2010-0065917

(22) 출원일자 2010년07월08일

심사청구일자 2013년07월12일

(65) 공개번호 10-2011-0116954

(43) 공개일자 2011년10월26일

(30) 우선권주장

12/763,050 2010년04월19일 미국(US)

(56) 선행기술조사문헌

W.E.Ryan, Shu Lin, Channel Codes, Classical and modern, Cambridge University Press, 2009. pp.213-222.

Anand Selvarathinam, "Low-Density Parity-Check Decoder Architecture for High Throughput Optical Fiber Channels", IEEE International Conference on Computer Design, 2003.

전체 청구항 수 : 총 20 항

심사관 : 성경아

- (54) 발명의 명칭 데이터 프로세싱 회로, 데이터 프로세싱 시스템 및 방법

**(57) 요 약**

본 발명의 다양한 실시예는 데이터 프로세싱을 위한 시스템 및 방법을 제공한다. 일례로서, 디코더 회로 및 스칼라 회로를 포함하는 데이터 프로세싱 회로가 개시된다. 디코더 회로는 적어도 하나의 디코더 메시지를 프로세싱함으로써 데이터 디코딩 알고리즘을 수행할 수 있고, 스칼라 회로는 디코더 메시지에 가변 스칼라 값을 승산할 수 있다.

**대 표 도** - 도2a

## 특허청구의 범위

### 청구항 1

디코더 회로의 내부에 데이터 디코딩 알고리즘의 일부로서 적어도 하나의 디코더 메시지를 생성함으로써 상기 데이터 디코딩 알고리즘을 수행하도록 동작가능한 상기 디코더 회로와,

스칼라 회로(a scalar circuit)를 포함하되,

상기 디코더 메시지는 상기 디코더 회로의 내부로 전해지는 값이고,

상기 스칼라 회로는 상기 디코더 메시지에 가변 스칼라 값을 승산하도록 동작가능한 데이터 프로세싱 회로.

### 청구항 2

제 1 항에 있어서,

상기 가변 스칼라 값은 제 1 스칼라 값 및 제 2 스칼라 값을 포함하고,

상기 디코더 회로는 제 1 디코딩 프로세스 및 제 2 디코딩 프로세스를 수행하도록 동작가능하며,

상기 스칼라 회로는 상기 디코더 메시지에 상기 제 1 디코딩 프로세스 동안에는 제 1 스칼라 값을 승산하고 상기 제 2 디코딩 프로세스 동안에는 제 2 스칼라 값을 승산하는

데이터 프로세싱 회로.

### 청구항 3

제 2 항에 있어서,

상기 제 1 디코딩 프로세스는 상기 데이터 프로세싱 회로의 제 1 전체 반복(a first global iteration)의 일부로서 수행되며,

상기 제 2 디코딩 프로세스는 상기 데이터 프로세싱 회로의 제 2 전체 반복의 일부로서 수행되고,

상기 제 1 및 제 2 전체 반복의 각각은 데이터 검출 알고리즘과 상기 데이터 디코딩 알고리즘이 모두 적용되는 프로세스인

데이터 프로세싱 회로.

### 청구항 4

제 2 항에 있어서,

상기 제 1 디코딩 프로세스는 상기 데이터 프로세싱 회로의 제 1 로컬 반복(a first local iteration)의 일부로서 수행되며,

상기 제 2 디코딩 프로세스는 상기 데이터 프로세싱 회로의 제 2 로컬 반복의 일부로서 수행되고,

상기 제 1 및 제 2 로컬 반복의 각각은 데이터 검출 알고리즘과 상기 데이터 디코딩 알고리즘 중 하나가 적용되는 프로세스인

데이터 프로세싱 회로.

### 청구항 5

제 2 항에 있어서,

상기 제 1 스칼라 값은 상기 제 2 스칼라 값보다 크며,

상기 제 1 스칼라 값은 상기 데이터 디코딩 알고리즘의 고속 수렴(rapid convergence)을 가능하게 하도록 선택되며,

상기 제 2 스칼라 값은 상기 데이터 디코딩 알고리즘에 고급 정보(enhanced information)를 제공하도록 선택되는

데이터 프로세싱 회로.

### 청구항 6

제 1 항에 있어서,

상기 디코더 회로는 저밀도 패리티 체크 디코더(a low density parity check decoder)인

데이터 프로세싱 회로.

### 청구항 7

제 6 항에 있어서,

상기 저밀도 패리티 체크 디코더는 적어도 하나의 가변 노드 및 적어도 하나의 체크 노드를 포함하고,

상기 디코더 메시지는 상기 가변 노드로부터 상기 체크 노드로 전달되는

데이터 프로세싱 회로.

### 청구항 8

제 6 항에 있어서,

상기 저밀도 패리티 체크 디코더는 적어도 하나의 가변 노드 및 적어도 하나의 체크 노드를 포함하고,

상기 디코더 메시지는 상기 체크 노드로부터 상기 가변 노드로 전달되는

데이터 프로세싱 회로.

### 청구항 9

제 1 항에 있어서,

상기 데이터 프로세싱 회로는 저장 장치의 일부로서 구현되는

데이터 프로세싱 회로.

### 청구항 10

제 1 항에 있어서,

상기 데이터 프로세싱 회로는 데이터 전송 장치의 일부로서 구현되는

데이터 프로세싱 회로.

### 청구항 11

제 1 항에 있어서,

상기 데이터 프로세싱 회로는 집적 회로의 일부로서 구현되는

데이터 프로세싱 회로.

### 청구항 12

데이터 프로세싱 방법에 있어서,

데이터 디코딩 알고리즘의 일부로서 데이터 세트에 대응하는 적어도 하나의 디코더 메시지를 생성하는 것을 포함하는, 데이터 디코더 회로에 의해 상기 데이터 세트에 상기 데이터 디코딩 알고리즘을 적용하는 단계와,

상기 디코더 메시지에 가변 스칼라 값을 승산하는 단계를 포함하되,

상기 디코더 메시지는 상기 디코더 회로의 내부로 전해지는 값인

데이터 프로세싱 방법.

### 청구항 13

제 12 항에 있어서,

상기 가변 스칼라 값은 제 1 스칼라 값 및 제 2 스칼라 값을 포함하고,

상기 디코더 메시지는 제 1 디코더 메시지를 포함하며,

상기 제 1 디코더 메시지에 상기 가변 스칼라 값을 승산하는 것은 상기 제 1 디코더 메시지에 상기 제 1 스칼라 값을 승산하는 것이며,

상기 방법은,

상기 데이터 세트의 유도체(a derivative)에 대응하는 제 2 디코더 메시지를 프로세싱하는 단계를 포함하는, 상기 데이터 세트의 상기 유도체에 상기 데이터 디코딩 알고리즘을 적용하는 단계와,

상기 제 2 디코더 메시지에 상기 제 2 스칼라 값을 승산하는 단계를 더 포함하는

데이터 프로세싱 방법.

### 청구항 14

제 13 항에 있어서,

상기 제 1 디코더 메시지를 프로세싱하는 단계를 포함하는, 상기 데이터 세트에 상기 데이터 디코딩 알고리즘을 적용하는 단계는 데이터 디코더 회로의 제 1 로컬 반복의 일부로서 수행되고,

상기 제 2 디코더 메시지를 프로세싱하는 단계를 포함하는, 상기 데이터 세트의 상기 유도체에 상기 데이터 디코딩 알고리즘을 적용하는 단계는 상기 데이터 디코더 회로의 제 2 로컬 반복의 일부로서 수행되며,

상기 제 1 및 제 2 로컬 반복의 각각은 데이터 검출 알고리즘과 상기 데이터 디코딩 알고리즘 중 하나가 적용되는 프로세스인

데이터 프로세싱 방법.

### 청구항 15

제 13 항에 있어서,

상기 제 1 디코더 메시지를 프로세싱하는 단계를 포함하는, 상기 데이터 세트에 상기 데이터 디코딩 알고리즘을 적용하는 단계는 데이터 디코더 회로 및 데이터 검출기 회로를 포함하는 데이터 프로세싱 회로의 제 1 전체 반복의 일부로서 수행되고,

상기 제 2 디코더 메시지를 프로세싱하는 단계를 포함하는, 상기 데이터 세트의 상기 유도체에 상기 데이터 디코딩 알고리즘을 적용하는 단계는 상기 데이터 프로세싱 회로의 제 2 전체 반복의 일부로서 수행되며,

상기 제 1 및 제 2 전체 반복의 각각은 데이터 검출 알고리즘과 상기 데이터 디코딩 알고리즘이 모두 적용되는 프로세스인

데이터 프로세싱 방법.

### 청구항 16

제 12 항에 있어서,

상기 데이터 디코딩 알고리즘은 저밀도 패리티 체크 디코딩 알고리즘인

데이터 프로세싱 방법.

### 청구항 17

데이터 디코딩 알고리즘의 일부로서 적어도 하나의 디코더 메시지를 생성함으로써 상기 데이터 디코딩 알고리즘을 수행하도록 동작가능한 데이터 디코더와,

상기 디코더 메시지에 가변 스칼라 값을 승산하도록 동작가능한 스칼라 회로를 포함하되,

상기 디코더 메시지는 상기 디코더 회로의 내부로 전해지는 값인

데이터 프로세싱 시스템.

### 청구항 18

제 17 항에 있어서,

상기 데이터 프로세싱 시스템은 집적 회로의 일부로서 구현되는

데이터 프로세싱 시스템.

### 청구항 19

제 17 항에 있어서,

상기 데이터 프로세싱 시스템은 저장 장치 및 수신 장치로 구성된 그룹으로부터 선택된 장치의 일부로서 구현되는

데이터 프로세싱 시스템.

### 청구항 20

제 17 항에 있어서,

상기 가변 스칼라 값은 제 1 스칼라 값 및 제 2 스칼라 값을 포함하고,

상기 데이터 디코더는 제 1 디코딩 프로세스 및 제 2 디코딩 프로세스를 수행하도록 동작가능하며,

상기 스칼라 회로는 상기 디코더 메시지에 상기 제 1 디코딩 프로세스 동안에는 제 1 스칼라 값을 승산하고 상기 제 2 디코딩 프로세스 동안에는 제 2 스칼라 값을 승산하는

데이터 프로세싱 시스템.

## 명세서

### 기술 분야

[0001]

본 발명은 정보를 검출 및/또는 디코딩하는 시스템 및 방법에 관한 것으로, 특히 가변적으로 스케일링되는 데이터 프로세싱을 수행하는 시스템 및 방법에 관한 것이다.

### 배경 기술

[0002]

저장 시스템, 셀룰러 전화 시스템 및 무선 전송 시스템을 포함하는 다양한 데이터 전송 시스템이 개발되어 왔다. 시스템 각각에서 데이터는 어떤 매체를 통해 송신기로부터 수신기로 전송된다. 예를 들어, 저장 시스템에서, 데이터는 저장 매체를 통해 송신기(즉, 기록 기능)로부터 수신기(즉, 판독 기능)로 송신된다. 임의의 전송의 효율성은 다양한 요인에 의해 야기되는 임의의 데이터 손실에 의해 영향 받는다. 일부 경우에, 인코딩/디코딩 프로세스가 사용되어 데이터 에러를 검출하고 이러한 데이터 에러를 수정하는 기능을 개선한다. 예로서, 간단한 데이터 검출 및 디코딩이 수행될 수 있으나, 이러한 간단한 프로세스는 수정된 데이터 스트림에 수렴하는(converge) 기능이 없는 경우가 흔하다.

[0003]

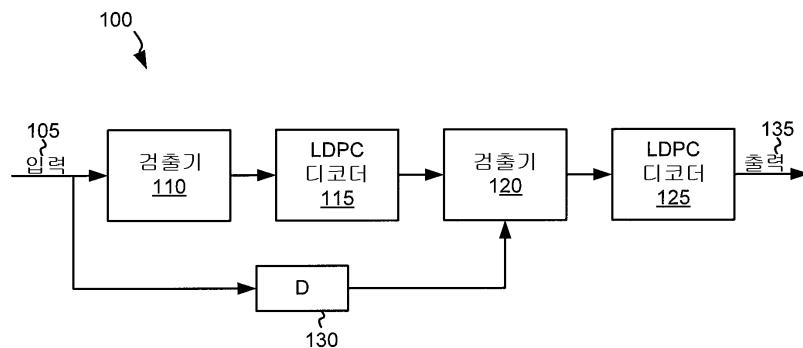

수렴의 확률을 높이기 위해, 다양한 기존 프로세스는 2개 이상의 검출 및 디코드 반복을 사용한다. 도 1을 참조하면, 예시적 종래 기술의 스테이지 2 스테이지 데이터 검출 및 디코드 회로(100)가 도시되어 있다. 2 스테이지 데이터 검출 및 디코드 회로(100)는 검출기(110)에 인가되는 데이터 입력(105)을 수신한다. 검출기(110)로부터의 하드 및 소프트 출력이 저밀도 패리티 체크(Low Density Parity Check) 디코더("an LDPC decoder") (115)에 제공된다. 입력(105)은 버퍼(130)를 통해 다른 검출기(120)로 전송된다. 검출기(120)는 LDPC 검출기(115)의 소프트 출력 및 입력(105)을 사용하여 추가 데이터 검출 프로세스를 수행한다. 검출기(120)로부터의 하드 및 소프트 출력은 제 2 디코딩 프로세스를 수행하고 출력(135)을 제공하는 LDPC 디코더(125)에 제공된다. 검출기(110) 및 LDPC 디코더(125)에 의해 제공되는 초기 검출 및 디코드가 수렴하지 않으면, 디코더(120) 및 LDPC 디코더(125)에 의해 제공되는 후속 검출 및 디코드가 추가 수렴 기회를 제공한다. 이를 시스템에서, 다양한 스칼라가 프로세스의 다양한 스테이지들 사이의 메시지 데이터에 대한 시스템으로 설계된다. 이를 스칼라는 설계 시에 고정되거나 일단 시스템이 저장 매체에 배치되면 조절될 수 있는 프로그래밍 가능한 정적 값일 수 있다. 그러나, 일부 실시예에서, 한 스테이지에서 다른 스테이지로의 데이터는 시스템 용량을 제공하며 포화된다.

[0004]

따라서, 적어도 전술한 이유로, 데이터 프로세싱을 위한 향상된 시스템 및 방법에 대한 필요성이 존재한다.

### 발명의 내용

#### 해결하려는 과제

[0005]

본 발명은 검출 및/또는 디코딩 정보를 위한 시스템 및 방법에 관한 것이며, 특히 가변적으로 스케일링되는 데이터 프로세싱을 수행하는 시스템 및 방법에 관한 것이다.

#### 과제의 해결 수단

[0006]

본 발명의 다양한 실시예는 디코더 회로 및 스칼라 회로를 포함하는 데이터 프로세싱 회로를 제공한다. 디코더 회로는 적어도 하나의 디코더 메시지를 프로세싱하여 데이터 디코딩 알고리즘을 수행할 수 있으며, 스칼라 회로

는 디코더 메시지에 가변 스칼라 값을 승산할 수 있다. 전술한 실시예의 일부에서, 스칼라 회로는 제 1 디코딩 프로세스 동안에 가변 디코더 값의 제 1 인스턴스에 의해 그리고 제 2 디코딩 프로세스 동안에 디코더 메시지에 가변 스칼라 값의 제 2 인스턴스를 승산한다. 일부 예에서, 제 1 디코딩 프로세스는 데이터 프로세싱 회로의 제 1 전체 반복의 일부로서 수행되고 제 2 디코딩 프로세스는 데이터 프로세싱 회로의 제 2 전체 반복의 일부로서 수행된다. 다른 경우에, 제 1 디코딩 프로세스는 데이터 프로세싱 회로의 제 1 로컬 반복의 일부로서 수행되고, 제 2 디코딩 프로세스는 데이터 프로세싱 회로의 제 2 로컬 반복의 일부로서 수행된다. 특정 경우에, 제 1 값은 제 2 값보다 크다. 제 1 값은 데이터 디코딩 알고리즘의 고속 수렴을 가능하게 하도록 선택되고, 제 2 스칼라는 데이터 디코딩 알고리즘에 고급 정보를 제공하도록 선택된다. 전술한 실시예의 특정 예에서, 디코더 회로는 저밀도 패리티 체크 디코더이다. 이러한 일부 예에서, 저밀도 패리티 체크 디코더는 적어도 하나의 가변 노드 및 적어도 하나의 체크 노드를 포함하고, 디코더 메시지는 가변 노드로부터 체크 노드로 전달된다. 이러한 다른 예에서, 저밀도 패리티 체크 디코더는 적어도 하나의 가변 노드 및 적어도 하나의 체크 노드를 포함하며, 디코더 메시지는 체크 노드로부터 가변 노드로 전달된다.

[0007] 본 발명의 다른 실시예는 데이터 검출기 회로 및 데이터 디코더 회로를 포함하는 데이터 프로세싱 시스템을 제공한다. 데이터 검출기 회로는 데이터 입력을 수신할 수 있고 검출된 출력을 제공할 수 있다. 데이터 디코더 회로는 검출된 출력에 대해 하나 이상의 로컬 반복을 수행하고 디코딩된 출력을 제공할 수 있다. 디코더 회로는 적어도 하나의 디코더 메시지를 프로세싱하여 데이터 디코딩 알고리즘을 수행할 수 있고, 디코더 회로는 디코더 메시지에 가변 스칼라 값을 승산할 수 있는 스칼라 회로를 포함한다.

[0008] 본 발명의 또 다른 실시예는 데이터 프로세싱 방법을 제공하는데, 이 방법은 데이터 세트에 대응하는 적어도 하나의 디코더 메시지를 프로세싱하는 것을 포함하는, 데이터 세트에 데이터 디코딩 알고리즘을 적용하는 단계와, 디코더 메시지에 가변 스칼라 값을 승산하는 단계를 포함한다. 일부 경우에, 가변 스칼라 값은 제 1 스칼라 값 및 제 2 스칼라 값을 포함하고, 디코더 메시지는 제 1 디코더 메시지이며, 제 2 디코더 메시지에 가변 스칼라 값을 승산하는 단계는 제 1 디코더 메시지에 제 1 스칼라 값을 승산하는 단계를 포함한다. 이러한 방법은 또한, 데이터 세트의 유도체(a derivative)에 대응하는 적어도 하나의 제 2 디코더 메시지를 프로세싱하는 것을 포함하는, 데이터 세트의 유도체에 데이터 디코딩 알고리즘을 적용하는 단계와, 제 2 디코더 메시지에 제 2 스칼라 값을 승산하는 단계를 더 포함한다.

[0009] 이 요약은 단지 본 발명의 일부 실시예의 전반적인 개요를 제공한다. 본 발명의 많은 다른 목적, 특징, 장점 및 다른 실시예는 다음의 상세한 설명과, 첨부된 청구범위 및 첨부된 도면으로부터 보다 완전히 명백해질 것이다.

## 발명의 효과

[0010] 본 발명에 의하면, 상대적으로 높은 로컬 스칼라 값의 초기 사용을 통해 상대적으로 작은 노이즈 양을 사용하는 코드워드의 수렴을 가속화하면서, 상대적으로 낮은 로컬 스칼라 값의 추후 사용을 통해 수렴하지 않았을지도 모르는 코드워드에 대한 보다 우수한 성능을 달성하게 한다.

## 도면의 간단한 설명

[0011] 본 명세서의 다른 부분에서 설명되는 도면을 참조하여 본 발명의 다양한 실시예의 추가적인 이해가 실현될 수 있다. 도면에서, 유사한 번호는 여러 도면에서 유사한 구성요소를 지칭하기 위해 사용된다. 일부 실시예에서, 소문자로 구성되는 세부 명칭은 다수의 유사한 구성요소 중 하나를 지칭하는 참조 번호와 관련된다. 기준 세부 명칭을 지정하지 않고 참조 번호를 지칭할 때, 이는 그러한 모든 다수의 유사한 구성요소를 지칭하도록 의도된다.

도 1은 종래 2 스테이지 데이터 검출 및 디코딩 시스템을 도시하고 있다.

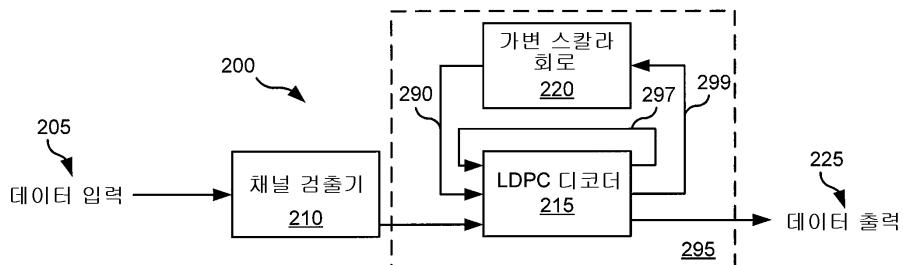

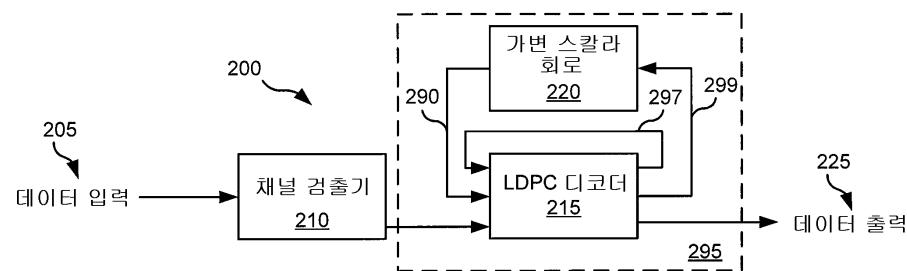

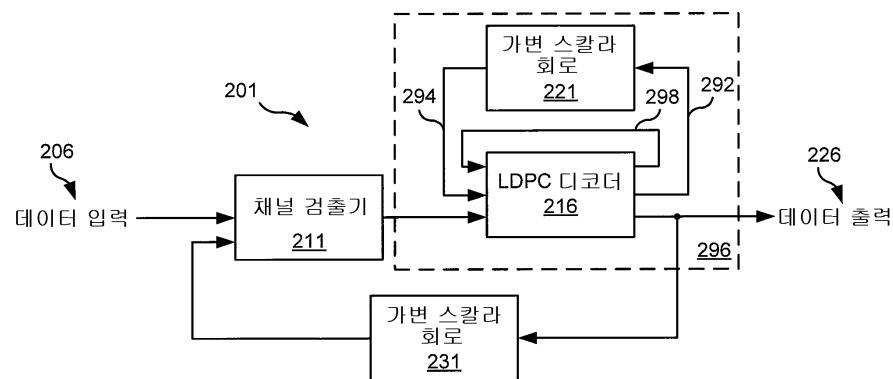

도 2a는 본 발명의 하나 이상의 실시예에 따른 내부 동적 스케일링을 사용하는 디코딩 회로를 포함하는 데이터 프로세싱 유닛 회로를 도시하고 있다.

도 2b는 본 발명의 일부 실시예에 따른 내부 동적 스케일링 및 전체적 동적 스케일링을 갖는 디코더 회로를 포함하는 다른 데이터 프로세싱 회로를 도시하고 있다.

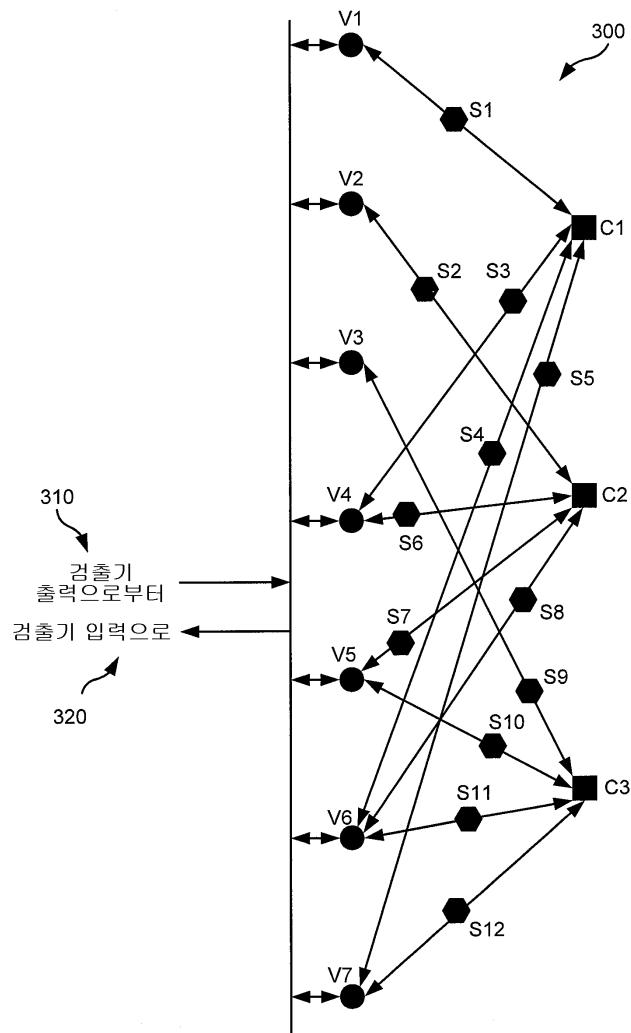

도 3은 본 발명의 일부 실시예에 따른 동적 스케일링을 도시하는 LDPC 디코더 회로의 시각적 도면이다.

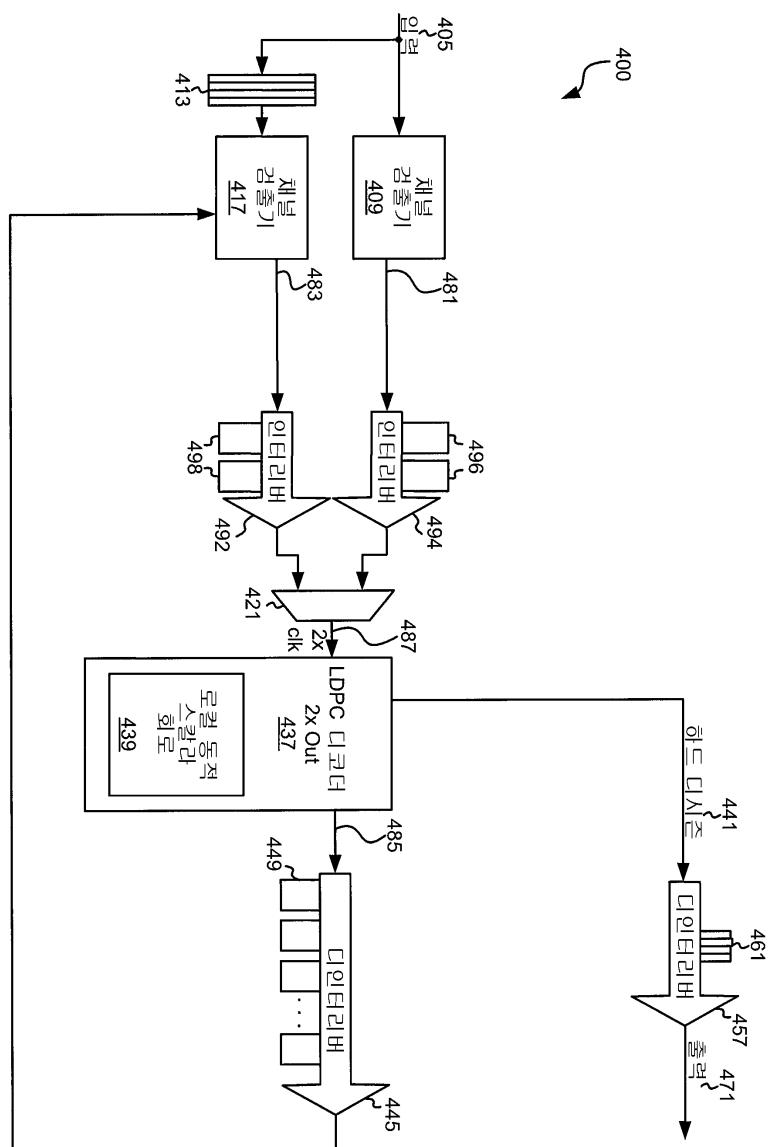

도 4a는 본 발명의 다양한 실시예에 따른 디코더 메시지의 동적 스케일링을 포함하는 큐잉 검출 및 디코딩 회로를 도시하고 있다.

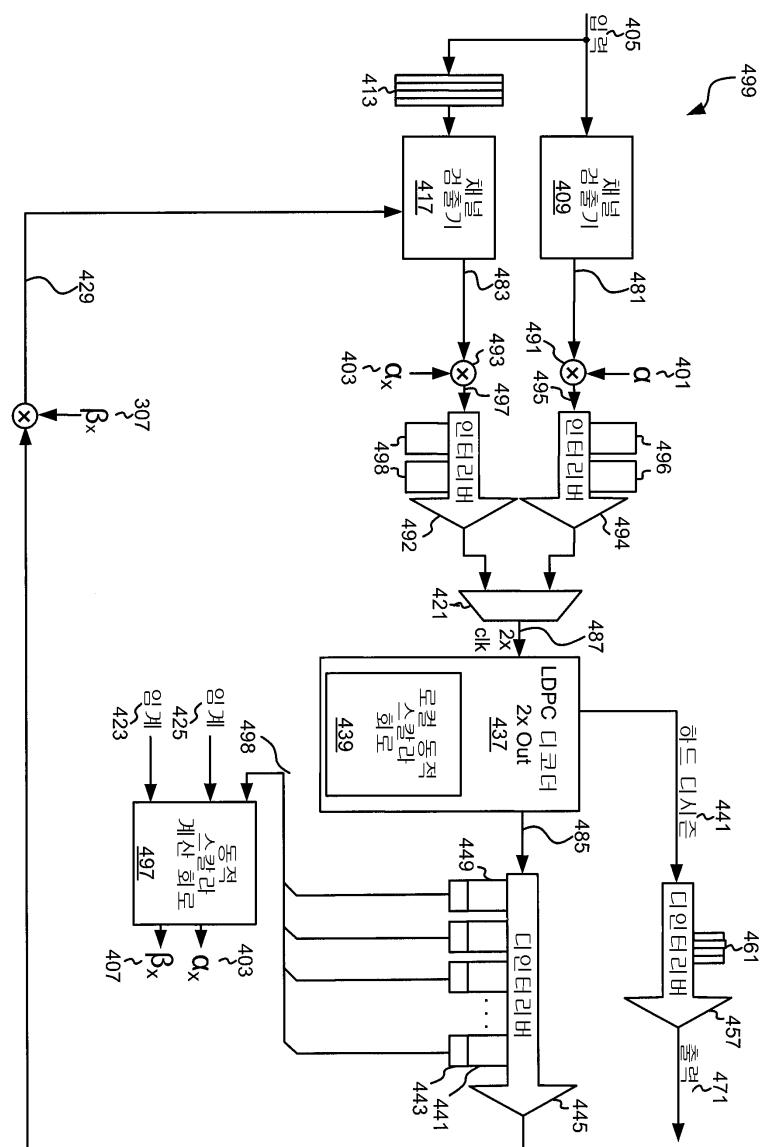

도 4b는 본 발명의 다양한 실시예에 따른 디코더 메시지의 동적 스케일링 및 전체적 루프의 동적 스케일링을 포함하는 큐잉 검출 및 디코딩 회로를 도시하고 있다.

도 5a는 디코더 메시지의 동적 스케일링을 사용하는 데이터 프로세싱을 위한 본 발명의 일부 실시예에 다른 방법을 도시하는 흐름도이다.

도 5b는 디코더 메시지의 동적 스케일링 및 전체적 프로세싱 루프의 동적 스케일링을 사용하는 동적 프로세싱을 위한 본 발명의 일부 실시예에 따른 방법을 도시하는 흐름도이다.

도 6a-6d는 본 발명의 여러 실시예에 따른 스케일링 비율을 동적으로 계산하는 여러 방안을 도시하는 4개의 흐름도이다.

도 7은 본 발명의 다양한 실시예에 따른 동적 디코더 스케일링을 사용하는 저장 시스템을 도시하고 있다.

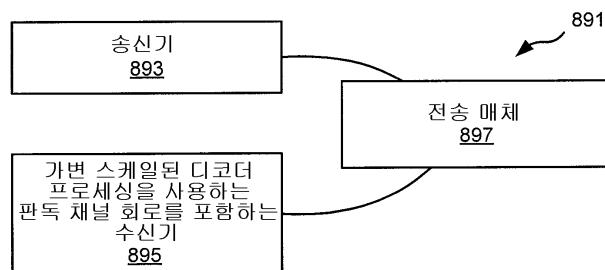

도 8은 본 발명의 여러 실시예에 따른 가변적으로 스케일링되는 디코더 프로세싱을 사용하는 판독 채널 회로를 갖는 수신기를 포함하는 통신 시스템을 도시하고 있다.

### 발명을 실시하기 위한 구체적인 내용

[0012]

본 발명은 정보를 검출 및/또는 디코딩하는 시스템 및 방법에 관한 것으로, 특히 가변적으로 스케일링되는 데이터 프로세싱을 수행하는 시스템 및 방법에 관한 것이다.

[0013]

본 발명의 다양한 실시예는 판독 채널, 무선 전송 및 다른 애플리케이션에 적합한 디코딩 해결책을 제공한다. 이러한 디코딩/검출 회로는 데이터를 데이터 검출기에 제공하는 소프트 디시즌(soft decision) 디코더를 포함한다. 소프트 디시즌 디코더 내의 메시지는 로컬 스케일링 값을 사용하여 스케일링된다. 이러한 방안은 상대적으로 높은 로컬 스칼라 값의 초기 사용을 통해 상대적으로 작은 노이즈 양을 사용하는 코드워드의 수렴을 가속화하면서, 상대적으로 낮은 로컬 스칼라 값의 추후 사용을 통해 수렴하지 않았을지도 모르는 코드워드에 대한 보다 우수한 성능을 달성하게 한다.

[0014]

본 발명의 일부 실시예는 디코더 회로 및 스칼라 회로를 포함하는 데이터 프로세싱 회로를 제공한다. 본 명세서에서 사용되는 바와 같이, "디코더 회로"라는 문구는 이전에 인코딩된 데이터 세트를 디코딩할 수 있는 임의의 회로를 의미하는 넓은 관점으로 사용된다. 따라서, 예로서, 디코더 회로는 LDPC 디코더 회로일 수 있다. 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 본 발명의 여러 실시예에 관련하여 사용될 수 있는 다양한 디코더 회로를 인식할 것이다. 본 명세서에서 사용되는 바와 같이, "스칼라 회로"라는 문구는 수신된 입력을 스케일링할 수 있는 임의의 회로를 의미하는 넓은 관점에서 사용된다. 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 본 발명의 여러 실시예에 관해 사용될 수 있는 다양한 스칼라 회로를 인식할 것이다. 디코더 회로는 적어도 하나의 디코더 메시지를 프로세싱함으로써 데이터 디코딩 알고리즘을 수행할 수 있으며, 스칼라 회로는 디코더 메시지에 가변 스칼라 값을 승산할 수 있다. 본 명세서에서 사용되는 바와 같이, "디코더 메시지"라는 문구는 디코더 회로 내부에 전해지는 임의의 값을 의미하는 넓은 관점에서 사용된다. 따라서, 예로서, 디코더 메시지는 LDPC 디코더 내의 가변 노드로부터 체크 노드로 전해지는 데이터 세트 또는 LDPC 디코더 내의 체크 노드로부터 가변 노드로 전해지는 데이터 세트일 수 있다. 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 본 발명의 여러 실시예에 관련해서 사용될 수 있는 다양한 디코더 메시지를 인식할 것이다.

[0015]

전술한 실시예의 일부 예에서, 스칼라 회로는 제 1 디코딩 프로세스 동안에 가변 디코더 값의 제 1 인스턴스(즉, 제 1 값)를 승산하고 제 2 디코딩 프로세스 동안에 디코더 메시지에 가변 스칼라 값의 제 2 인스턴스(즉, 제 2 값)를 승산한다. 일부 예에서, 제 1 디코딩 프로세스는 데이터 프로세싱 회로의 제 1 전체 반복의 부분으로서 수행되고, 제 2 디코딩 프로세스는 데이터 프로세싱 회로의 제 2 전체 반복의 부분으로서 수행된다. 본 명세서에서 사용되는 바와 같이, "전체 반복"이라는 문구는, 넓은 의미로, 데이터 검출 알고리즘 및 데이터 디코딩 알고리즘이 적용되는 프로세스를 의미하는 것으로 사용된다. 따라서, 예를 들어, 전체 반복은 데이터 세트에 데이터 검출 알고리즘을 적용한 후 데이터 검출의 결과에 데이터 디코딩 알고리즘을 하나 이상 적용하는 것을 포함한다. 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 본 발명의 여러 실시예에 관해 사용될 수 있는 다양한 전체 반복을 인식할 것이다. 다른 경우에, 제 1 디코딩 프로세스가 데이터 프로세싱

유닛의 제 1 로컬 반복의 부분으로서 수행되고, 제 2 디코딩 프로세스가 데이터 프로세싱 회로의 제 2 로컬 반복의 부분으로서 수행된다. 본 명세서에서 사용되는 바와 같이, "로컬 반복"이라는 문구는, 넓은 의미로, 데이터 검출 알고리즘 또는 데이터 디코딩 알고리즘 중 하나가 적용되는 프로세스를 의미하는 것으로 사용된다. 따라서, 일례로서, 로컬 반복은 데이터 검출기 회로에 의한 디코딩 알고리즘의 적용을 포함할 수 있다. 데이터 디코딩 알고리즘의 단 하나의 적용이 전체 반복 동안에 적용되는 경우, 이는 하나의 로컬 반복이 발생했다고 한다. 한편, 데이터 디코딩 알고리즘의 2개 이상의 애플리케이션이 적용되는 경우, 2개 이상의 로컬 반복이 적용된다고 한다. 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 본 발명의 여러 실시예와 관련하여 사용될 수 있는 다양한 로컬 반복을 인식할 것이다.

[0016] 도 2a를 참조하면, 본 발명의 하나 이상의 실시예에 따른 내부 동적 스케일링을 포함하는 디코더 회로(295)를 포함하는 데이터 프로세싱 회로(200)가 도시되어 있다. 또한, 데이터 프로세싱 회로(200)는 채널 검출기 회로(210)를 포함한다. 데이터 프로세싱 회로(200)는 채널 검출기(210)에서 데이터 입력(206)을 수신한다. 데이터 입력(205)은, 예를 들어, 저장 매체 또는 전송 채널로부터 유도될 수 있다. 특정한 경우, 데이터 입력(205)은 흔히 코드워드라 불리는 데이터 그룹 또는 데이터 세트로서 제공된다. 하드 디스크 드라이브의 경우, 수신된 데이터 세트는 하드 디스크 드라이브의 저장 매체로부터의 데이터 섹터일 수 있다. 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 데이터 입력을 위한 기타 소스와, 본 발명의 여러 실시예에 따라 처리될 수 있는 다른 데이터 세트를 인식할 것이다.

[0017] 채널 검출기(210)는 소프트 출력 비터비 알고리즘(SOVA) 검출기 또는 MAP(a maximum a posteriori) 검출기 등을 포함하는 이 기술 분야에 알려진 임의의 채널 검출기일 수 있다. 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 본 발명의 여러 실시예에 따라 사용될 수 있는 다양한 채널 검출기를 인식할 것이다. 채널 검출기(210)의 출력은 검출기 회로(295)에 제공된다.

[0018] 검출기 회로(295)는 LDPC 검출기(215) 및 가변 스칼라 회로(220)를 포함한다. LDPC 디코더(215)는 채널 검출기(210)로부터 수신되는 출력의 LDPC 디코딩을 최초로 수행한다. 이 최초 디코딩 패스(즉, 최초 로컬 반복)에서, LDPC 디코더(215)는 가변 스칼라 회로(220)로부터의 출력(290)으로서 제공되는 최초 스칼라 값으로 채널 검출기(210)의 출력을 승산한다. 일단 디코딩 프로세스가 완료되면, LDPC 디코더(215)를 통해 다른 패스(즉, 다른 로컬 반복)이 요구되는지를 판단한다. 이 판단은 LDPC 디코더(215)가 수렴하는지와, 수렴에 대한 장애가 LDPC 디코더(215)를 통해 추가 패스에 의해 이점을 갖는지에 기초하여 내려질 수 있다. 이 기술 분야에 알려진 추가로컬 디코더 루프에 대한 필요성을 판단하는 임의의 방안이 사용될 수 있다. 추가로컬 반복이 수행될 때, LDPC 디코더(215)는 신호(299)를 어서트하고, 가변 스칼라 회로(220)는 출력(290)으로서 제공되는 스칼라 값을 동적으로 수정한다. 또한, LDPC 디코더(215)의 출력(297)은 재처리를 위해 다시 공급된다. LDPC 디코더(215)를 통한 후속 패스에서, 디코딩 프로세스는 출력(290)으로서 수신되는 수정된 스칼라 값을 의해 조작되는 출력(297)에 적용된다. 이 프로세스는 LDPC 디코더(215)를 통해 각 로컬 반복에 대해 반복된다.

[0019] 본 발명의 하나의 특정 실시예에서, 출력(290)으로서 제공되는 초기 스칼라 값은 0.75이고, LDPC 디코더(215)를 통한 각 후속 로컬 반복에서, 가변 스칼라 회로(220)는 1/32의 하드웨어에 사용하기 편한 값(a hardware friendly value)에 의해 출력(290)으로서 제공되는 스칼라 값을 감소시킨다. 따라서, 제 2 로컬 반복에서 스칼라 값은 0.7188이고, 제 3 로컬 반복에서 스칼라 값은 0.6875이며, 제 4 로컬 반복에서 스칼라 값은 0.6563이고, 제 5 로컬 반복에서 스칼라 값은 0.625이며, 제 6 로컬 반복에서 스칼라 값은 0.5938이고, 제 7 로컬 반복에서 스칼라 값은 0.5625이며, 제 8 로컬 반복에서 스칼라 값은 0.5313이고, 제 9 로컬 반복에서 스칼라 값은 0.5이다. 어떤 지점에서, 가변 스칼라 회로(220)는 출력(290)으로서 제공되는 스칼라 값의 수정을 중단시키고, 스칼라 값 상수를 유지한다. 따라서, 이전의 예를 사용하면, 제 10 및 그 이후의 로컬 반복에서, 가변 스칼라 회로(220)는 스칼라 값을 0.5로 유지한다. 일단 모든 로컬 반복이 완료되면, LDPC 디코더(215)는 데이터 출력(225)을 제공한다.

[0020] 도 2b를 참조하면, 본 발명의 일부 실시예에 따른 내부 동적 스케일링 및 전체 동적 스케일링을 갖는 디코더 회로(296)를 포함하는 데이터 프로세싱 회로(201)가 도시되어 있다. 또한, 데이터 프로세싱 회로(201)는 데이터 입력(206)이 수신되는 채널 검출기 회로(211)를 포함한다. 데이터 입력(206)은 저장 매체 또는 전송 채널로부터 유도될 수 있다. 특별한 경우, 데이터 입력(206)은 흔히 코드워드라고 불리는 데이터 그룹 또는 데이터 세트로서 제공된다. 하드 디스크 드라이브의 경우에, 수신된 데이터 세트는 하드 디스크 드라이브의 저장 매체로부터의 데이터 섹터일 수 있다. 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 본 발명의 여러 실시예에 따라 처리될 수 있는 데이터 입력에 대한 다른 소스 및 다른 데이터 세트를 인식할 것이다.

- [0021] 채널 검출기(211)는 소프트 출력 비터비 알고리즘(SOVA) 검출기 또는 MAP(a maximum a posteriori) 검출기 등을 포함하는 이 기술 분야에 알려진 임의의 채널 검출기일 수 있다. 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 본 발명의 여러 실시예에 따라 사용될 수 있는 다양한 채널 검출기를 인식할 것이다. 채널 검출기(211)의 출력은 디코딩 회로(296)에 제공된다.

- [0022] 디코더 회로(296)는 LDPC 디코더(216) 및 가변 스칼라 회로(221)를 포함한다. LDPC 디코더(216)는 채널 검출기(211)로부터 수신되는 출력의 LDPC 디코딩을 최초로 수행한다. 이 최초 디코딩 패스(즉, 초기 로컬 반복)에서, LDPC 디코더(216)는 가변 스칼라 회로(221)로부터의 출력(294)으로서 제공되는 초기 스칼라 값으로 채널 검출기(211)의 출력을 승산한다. 일단 디코딩 프로세스가 완료되면, LDPC 디코더(216)를 통한 다른 패스가 요구되는지를 판단한다. 이 판단은 LDPC 디코더(216)가 수렴하는지와, 수렴에 대한 장애가 LDPC 디코더(216)를 통해 추가 패스에 의해 이점을 갖는지에 기초하여 내려질 수 있다. 이 기술 분야에 알려진 추가 로컬 디코더 루프에 대한 필요성을 판단하는 임의의 방안이 사용될 수 있다. 추가 로컬 반복이 수행될 때, LDPC 디코더(216)는 신호(296)를 어서트하고, 가변 스칼라 회로(221)는 출력(294)으로서 제공되는 스칼라 값은 동적으로 수정한다. 또한, LDPC 디코더(216)의 출력(298)은 재처리를 위해 다시 공급된다. LDPC 디코더(216)를 통한 후속 패스에서, 디코딩 프로세스는 출력(294)으로서 수신되는 수정된 스칼라 값에 의해 조작되는 출력(298)에 적용된다. 이 프로세스는 LDPC 디코더(216)를 통해 각 로컬 반복에 대해 반복된다.

- [0023] 본 발명의 하나의 특정 실시예에서, 출력(294)으로서 제공되는 초기 스칼라 값은 0.75이고, LDPC 디코더(216)를 통한 각 후속 로컬 반복에서, 가변 스칼라 회로(221)는 1/32의 하드웨어에 사용하기 편한 값에 의해 출력(294)으로서 제공되는 스칼라 값을 감소시킨다. 따라서, 제 2 로컬 반복에서 스칼라 값은 0.7188이고, 제 3 로컬 반복에서 스칼라 값은 0.6875이며, 제 4 로컬 반복에서 스칼라 값은 0.6563이고, 제 5 로컬 반복에서 스칼라 값은 0.625이며, 제 6 로컬 반복에서 스칼라 값은 0.5938이고, 제 7 로컬 반복에서 스칼라 값은 0.5625이며, 제 8 로컬 반복에서 스칼라 값은 0.5313이고, 제 9 로컬 반복에서 스칼라 값은 0.5이다. 어떤 지점에서, 가변 스칼라 회로(221)는 출력(294)으로서 제공되는 스칼라 값의 수정을 중단시키고, 스칼라 값 상수를 유지한다. 따라서, 이전의 예를 사용하면, 제 10 및 그 이후의 로컬 반복에서, 가변 스칼라 회로(221)는 스칼라 값을 0.5로 유지한다. 일단 모든 로컬 반복이 완료되면, LDPC 디코더(216)는 데이터 출력(226)을 제공한다.

- [0024] 또한, 다수의 전체 반복(즉, 채널 검출기(211) 및 디코더 회로(296) 모두를 통한 프로세싱)이 가능하다. 추가 전체 반복이 요구되는 경우, 데이터 출력(226)은 채널 검출기(211)로 다시 공급되는데, 여기서 채널 검출기(211) 및 디코더 회로(296) 모두를 통해 다시 처리된다. 이 기술 분야에 알려진 임의의 기준을 사용하여 다른 전체 동작을 수행할지에 관한 결정이 내려질 수 있다.

- [0025] 도 3을 참조하면, 본 발명의 일부 실시예에 따른 동적 스케일링을 도시하는 LDPC 디코더 회로의 시각적 도면이다. 시각적 도면(300)은 LDPC 디코더의 예시적 동작을 나타낸다. 시각적 도면(300)은 업스트림 검출기(도시 생략)의 출력으로부터 수신된 입력(310)과, 회로 출력으로서 제공되거나 업스트림 또는 다운스트림 검출기(도시 생략)에 대한 출력(320)을 도시하고 있다. 입력 데이터는 V1, V2, V3, V4, V5, V6, V7로서 표시되는 다수의 가변 노드에 제공된다. 가변 노드로부터의 메시지는 화살표로 표시되는 C1, C2, C3으로서 식별되는 노드를 체크하도록 전달된다. 이를 메시지는 S1, S2, S3, S4, S5, S6, S7, S8, S9, S10, S11, S12로서 식별되는 승수(multipliers)를 사용하여 로컬 스칼라 값만큼 증가된다. 각 승수(S1, S2, S3, S4, S5, S6, S7, S8, S9, S10, S11, S12)에 의해 증가되는 로컬 스칼라 값은 로컬 반복 횟수 및 전체 반복 횟수 중 하나 또는 모두에 따라 동적으로 변경될 수 있다. 체크 노드(C1, C2, C3)에 의해 구현되는 체크의 결과는 화살표로 도시되는 바와 같은 증가 없이 가변 노드(V1, V2, V3, V4, V5, V6, V7)에 다시 제공된다. 이를 결과는 출력(320)으로서 제공될 수 있으며, 다른 로컬 디코더 반복이 요구되는 경우, 가변 노드(V1, V2, V3, V4, V5, V6, V7)에서의 값은 화살표로 표시되는 바와 같이 체크 노드(C1, C2, C3)로 다시 전송되며, 가변 로컬 스칼라 값에 의한 증가가 수행된다. 이 프로세스에서, 가변 노드(V1, V2, V3, V4, V5, V6, V7)와 체크 노드(C1, C2, C3) 사이에서 전달되는 메시지는 다음 식에 따라 로컬 스칼라 값만큼 증가된다.

- [0026]  $(V\text{로부터 } C\text{로의 메시지}) = (\text{로컬 스칼라 값})(V\text{로부터 } C\text{로의 메시지})$

- [0027] 이러한 스케일링은 임의의 업데이팅 스케줄링에 무관한 LDPC 디코더에 적용될 수 있으며, 계층화 디코더 및 폴루딩 스케줄(flooding schedules)을 사용하는 디코더에 대해 사용될 수 있다는 것을 유의하자. 또한, 이러한 내부 스케일링이 가변 노드로부터 체크 노드로 전달되는 메시지에 적용되는 것으로 설명하지만, 본 발명의 다른 실시예에서 스케일링은 체크 노드로부터 가변 노드로 전달되는 메시지에 적용될 수 있다는 것을 유의해야 한다.

- [0028] 도 4a를 참조하면, 본 발명의 다양한 실시예에 따른 디코더 메시지의 동적 스케일링을 포함하는 큐잉 검출 및

디코딩 회로(400)가 도시되어 있다. 큐잉 검출 및 디코딩 회로(400)는 채널 검출기(409)에 공급되는 데이터 입력(405)을 포함한다. 일부 실시예에서, 데이터 입력(405)은 저장 매체 또는 전송 채널로부터 유도될 수 있다. 특정 경우에, 데이터 입력(405)은 흔히 코드워드라고 불리는 데이터 그룹 또는 데이터 세트로서 제공된다. 하드 디스크 드라이브의 경우에, 수신된 데이터 세트는 하드 디스크 드라이브의 저장 매체로부터의 데이터 셕터일 수 있다. 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 본 발명의 여러 실시예에 따라 처리될 수 있는 다른 데이터 입력 및 다른 데이터 세트를 인식할 것이다.

[0029] 채널 검출기(409)는 소프트 출력 비터비 알고리즘(SOVA) 검출기 또는 MAP(a maximum a posteriori) 검출기 등을 포함하는 이 기술 분야에 알려진 임의의 채널 검출기일 수 있다. 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 본 발명의 여러 실시예에 따라 사용될 수 있는 다양한 채널 검출기를 인식할 것이다. 또한, 데이터 입력(405)은 데이터 입력(405)으로부터 수신되는 다수의 데이터 세트를 유지하도록 설계되는 메모리 버퍼(413)에 제공된다. 메모리 버퍼(413)의 크기는 데이터 입력(405)을 통해 제공되는 데이터 세트가 적어도 그 동일한 데이터 세트의 제 1 반복 프로세싱이 완료되고 프로세싱된 데이터가 큐 버퍼(449)에서 이용 가능할 때까지 이용 가능하게 유지되도록 충분한 버퍼링을 제공하도록 선택될 수 있는데, 이는 보다 완전히 후술할 것이다. 메모리 버퍼(413)는 채널 검출기(417)에 데이터 세트를 제공한다. 채널 검출기(409)와 유사하게, 채널 검출기(417)는 SOVA 검출기 또는 MAP 검출기 등을 포함하는 이 기술 분야에 알려진 임의의 유형의 채널 검출기일 수 있다. 다시, 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 본 발명의 여러 실시예에 따라 사용될 수 있는 다양한 채널 검출기를 인식할 것이다.

[0030] 채널 검출기(409)의 출력(481)은 인터리버 회로(an interleaver circuit; 494)에 제공되며, 채널 검출기(417)의 출력(483)은 다른 인터리버 회로(492)에 제공된다. 인터리버 회로(494)는 평 풍 버퍼(496)를 사용하여 채널 검출기(409)의 출력을 인터리빙하고, 인터리버 회로(492)는 평 풍 버퍼(498)를 사용하여 채널 검출기(417)의 출력을 인터리빙한다. 평 풍 버퍼(496)의 버퍼 중 하나는 채널 검출기(409)로부터의 출력의 이전 인터리빙 프로세스의 결과를 유지하고 멀티플렉서(421)를 통해 LDPC 디코더(437)에 언로딩되며, 평 풍 버퍼(496)의 다른 버퍼는 현재 인터리빙되고 있는 채널 검출기(409)로부터의 데이터 세트를 유지한다. 유사하게, 평 풍 버퍼(498)의 버퍼들 중 하나는 채널 검출기(417)로부터의 출력의 이전 인터리빙 프로세스의 결과를 유지하며 멀티플렉서(421)를 통해 LDPC 디코더(437)로 언로딩되며, 평 풍 버퍼(498)의 다른 버퍼는 현재 인터리빙되고 있는 채널 검출기(417)로부터의 데이터 세트를 유지한다. 다른 소프트 디시즌 데이터 디코더는 본 발명의 여러 실시예의 LDPC 디코더(437) 대신에 사용될 수 있다는 것을 유의해야 한다.

[0031] LDPC 디코더(437)는 하나 이상의 데이터 세트를 동시에 디코딩할 수 있다. 일례로서, LDPC 디코더(437)는 평 풍 버퍼(496)로부터 인터리빙된 데이터 세트를 디코딩하고, 평 풍 버퍼(498)로부터 인터리빙된 데이터 세트를 디코딩하며, 평 풍 버퍼(496) 및 평 풍 버퍼(498)로부터의 인터리빙된 데이터 세트를 동시에 디코딩하도록 설계될 수 있다. LDPC 디코더(437)를 통한 하나 이상의 패스가 요구될 수 있다. 다시, 이러한 패스는 본 명세서에서 로컬 반복이라고 불리며 다시 LDPC 디코더에 의한 LDPC 디코더(437)의 출력을 재처리하는 것을 포함한다. 이러한 경우에, LDPC 디코더(437)의 내부 메시지는 로컬 동적 스칼라 회로(439)에 의해 생성되는 로컬 동적 스칼라 값에 의해 증가될 수 있다. 이 증가 프로세스는 도 3을 참조하여 설명한 것과 유사하게 구현될 수 있다.

[0032] 본 발명의 일부 실시예에서, 로컬 동적 스칼라 회로(439)는 제 1 전체 반복(즉, 채널 검출기(409) 및 LDPC 디코더(437)를 통한 프로세싱)에서 사용되는 초기 로컬 스칼라 값을 제공하며, 동일한 로컬 스칼라 값이 특정 전체 반복에 이어지는 각 후속 로컬 반복에 대해 사용된다. 각 추가 전체 반복(즉, 채널 검출기(417) 및 LDPC 디코더(437)를 통한 프로세싱)이 발생하면, 스칼라 값이 정의된 양만큼 감소되고, 감소된 스칼라 값은 후속 로컬 반복을 위해 사용된다. 본 발명의 특정 실시예에서, 초기 스칼라 값은 0.75이고, 각 후속 전체 반복에서 로컬 동적 스칼라 회로(439)는 1/32의 하드웨어에 사용하기 편한 값(a hardware friendly value)에 의해 스칼라 값을 감소시킨다. 따라서, 제 2 전체 반복에서 스칼라 값은 0.7188이고, 제 3 전체 반복에서 스칼라 값은 0.6875이며, 제 4 전체 반복에서 스칼라 값은 0.6563이고, 제 5 전체 반복에서 스칼라 값은 0.625이며, 제 6 전체 반복에서 스칼라 값은 0.5938이고, 제 7 전체 반복에서 스칼라 값은 0.5625이며, 제 8 전체 반복에서 스칼라 값은 0.5313이고, 제 9 전체 반복에서 스칼라 값은 0.5이다. 어떤 지점에서, 가변 스칼라 회로(439)는 출력(290)으로서 제공되는 스칼라 값의 수정을 중단시키고, 스칼라 값 상수를 유지한다. 따라서, 이전의 예를 사용하면, 제 10 및 그 이후의 전체 반복에서, 가변 스칼라 회로(439)는 스칼라 값을 0.5로 유지한다. 디코딩 프로세스를 수행하기 전에, LDPC 디코더(437)는 로컬 동적 스칼라 회로(439)로부터의 로컬 스칼라 값으로 멀티플렉서(421)로부터의 데이터 출력(487)을 승산한다. 본 발명의 다른 실시예에서, 로컬 스칼라 값의 값은 각 전체 반복 이후 발생하는 수정에 추가하여 또는 그 대신에 각 로컬 반복 후에 수정될 수 있다는 것을 유의해야 한다.

[0033]

일반적인 규칙으로서, 높은 로컬 스칼라 값을 사용하는 단계는 낮은 노이즈가 존재하는 디코더에 의한 수렴의 비율을 증가시킨다. 이와 반대로, 낮은 로컬 스칼라 값을 사용하는 단계는 수렴 레이트를 감소시키며 높은 노이즈가 데이터 스트림의 비트 중 하나 이상에 제시되는 수렴의 확률을 증가시킨다. 작은 스칼라에 의해 증가되는 비트는 디코더 회로를 포화시킬 가능성이 작으므로 더 많은 데이터가 디코딩 프로세스를 위해 사용되기 위해 유지되기 때문에 높은 수렴 확률이 발생한다. 가변 로컬 스칼라 값을 사용함으로써, 본 발명의 일부 실시예는 낮은 노이즈 레벨을 제시하는 코드워드의 다양한 영역에 상대적으로 빠른 수렴을 제공한다. 추후에, 노이즈의 높은 레벨을 제시하는 코드워드의 영역은 수렴의 비율을 감소시키는 점진적으로 낮은 스칼라를 사용하여 처리되지만 수렴을 달성하기 위해 사용될 수 있는 데이터의 범위를 증가시킨다.

[0034]

일단 원하는 로컬 반복이 LDPC 디코더(437)에 의해 완료되면, 최종 디코딩된 데이터는 하드 디시즌 출력(441)로서 제공되거나 채널 검출기(417)가 추가 프로세싱을 위해 이용 가능하게 될 때까지 디코딩된 데이터를 디-인터리빙하고 디-인터리빙된 데이터를 저장하기 위해 큐 버퍼(449)를 사용하는 디-인터리버 회로(445)에 대한 출력(485)으로서 제공된다.

[0035]

이전 디-인터리빙 프로세스의 결과를 보유하는 큐 버퍼(449)의 버퍼 중 하나는 채널 검출기(417)로 언로딩되며, 큐 버퍼(449)의 다른 버퍼는 현재 디-인터리빙되고 있는 디코딩된 데이터 세트를 유지하며, 큐 버퍼(449)의 큐의 하나 이상의 다른 버퍼는 채널 검출기(417)에 의한 프로세싱을 기다리는 다른 수렴되지 않는 데이터를 유지한다. 큐 버퍼(449)로부터의 수렴되지 않은 데이터는 디-인터리버(445)에 의해 디-인터리빙되고 메모리 버퍼(413)의 대응 데이터 세트로의 액세스를 갖는 채널 검출기(417)로 전달된다. 채널검출기(417)에 의해 수행되는 데이터 검출은 채널 검출기(409)에 의해 수행되는 것과 유사하다. 이와 달리, 데이터 세트가 LDPC 디코더(437)에서 수렴하는 경우, 이는 수신된 하드 디시즌 출력(441)을 디-인터리빙하는 디-인터리버 회로(457)에 대한 하드 디시즌 출력(441)으로서 제공되며, 디-인터리빙된 결과를 다수의 메모리 버퍼(461) 중 하나에 저장한다. 최종적으로, 디-인터리버 회로(457)는 출력(471)로서 메모리 버퍼(461)에 저장된 디-인터리빙된 데이터를 제공한다.

[0036]

큐잉 검출/디코딩 회로(400)는 도입된 데이터에 의존하여 변하는 수의 검출 및 디코딩 반복의 동작을 허용한다. 또한, 일부 경우에, 큐잉 검출/디코딩 회로(400)의 사용을 통해 상당한 전력 절감이 달성될 수 있다. 또한, 일부 경우에, 더 빠른 LDPC 디코더가 구현되어 스루풋을 증가시킬 수 있는데, 여기서 다수의 반복이 반드시 요구되지는 않으므로 실질적인 제 1 반복 데이터 수렴이 존재한다. 또한, LDPC 디코더(437)의 결과가 순서를 벗어나게 허용함으로써, 업스트림 프로세싱이 다운스트림 프로세싱의 완료를 기다리지 않아도 된다. 순서를 벗어난 결과의 재정렬은 검출/디코딩 회로(400)의 큐잉에 의해 또는 출력(471)이 다운스트림 수신에 의해 수행될 수 있다. 또한, 디코더(437) 내의 동적 스칼라를 사용하는 단계는 상대적으로 높은 로컬 스칼라 값을 사용하여 신속하게 코드워드의 실질적으로 노이즈가 없는 영역을 해결하게 하여, 상대적으로 작은 로컬 스칼라 값을 사용하여 코드워드의 노이즈가 더 많은 영역을 해결한다. 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 본 발명의 하나 이상의 구현을 통해 달성될 수 있는 다양한 다른 장점들을 인식할 것이다.

[0037]

도 4b를 참조하면, 본 발명에 따른 디코더 메시지의 동적 스케일링 및 전체 루프의 동적 스케일링을 포함하는 큐잉 검출 및 디코딩 회로(499)가 도시되어 있다. 큐잉 검출 및 디코딩 회로(499)는 채널 검출기(409)에 공급되는 데이터 입력(405)을 포함한다. 또한, 데이터 입력(405)은 데이터 입력(405)으로부터 수신된 다수의 데이터 세트를 유지하도록 설계되는 메모리 버퍼(413)에 제공된다. 메모리 버퍼(413)의 크기는 데이터 입력(405)을 통해 제공되는 데이터 세트가 적어도 그 동일한 데이터 세트의 제 1 반복 프로세싱이 완료되고 프로세싱된 데이터가 큐 버퍼(449)에서 이용 가능할 때까지 이용 가능하게 유지되도록 충분한 버퍼링을 제공하도록 선택될 수 있는데, 이는 보다 완전히 후술할 것이다. 메모리 버퍼(413)는 채널 검출기(417)에 데이터 세트를 제공한다.

[0038]

채널 검출기(409)의 출력(481)은 인터리버 회로(494)에 제공되고, 채널 검출기(417)의 출력(483)은 인터리버 회로(492)에 제공된다. 인터리버 회로(494)는 평 풍 버퍼(496)를 사용하여 채널 검출기(409)의 출력을 인터리빙하고, 인터리버 회로(492)는 평 풍 버퍼(498)를 사용하여 채널 검출기(417)의 출력을 인터리빙한다. 평 풍 버퍼(496)의 버퍼 중 하나는 채널 검출기(409)로부터의 출력의 이전 인터리빙 프로세스의 결과를 유지하고 멀티플렉서(421)를 통해 LDPC 디코더(437)로 언로딩하며, 평 풍 버퍼(496)의 다른 버퍼는 현재 인터리빙되고 있는 채널 검출기(409)로부터의 데이터 세트를 유지한다. 이와 유사하게, 평 풍 버퍼(498)의 버퍼 중 하나는 채널 검출기(417)로부터의 출력의 이전 인터리빙 프로세스의 결과를 유지하고 멀티플렉서(421)를 통해 LDPC 디코더(437)로 언로딩되며, 평 풍 버퍼(498)의 다른 버퍼는 현재 인터리빙되고 있는 채널 검출기(417)로부터의 데이터 세트를 유지한다.

- [0039] LDPC 디코더(437)를 통한 하나 이상의 패스(즉, 로컬 반복)이 요구될 수 있다. 이러한 경우, LDPC 디코더(437)의 내부 메시지는 로컬 동적 스칼라 회로(439)에 의해 생성되는 로컬 동적 스칼라 값에 의해 증가될 수 있다. 이 증가 프로세스는 도 3을 참조하여 설명한 것과 유사하게 구현될 수 있다.

- [0040] 본 발명의 일부 실시예에서, 로컬 동적 스칼라 회로(439)는 제 1 전체 반복(즉, 채널 검출기(409) 및 LDPC 디코더(437)를 통한 프로세싱)에서 사용되는 초기 로컬 스칼라 값을 제공하고, 동일한 로컬 스칼라 값은 특정 전체 반복에 이어지는 각 연속적인 로컬 반복을 위해 사용된다. 각 추가적인 전체 반복(즉, 채널 검출기(417) 및 LDPC 디코더(437)를 통한 프로세싱)이 발생하면, 스칼라 값은 정의된 양만큼 감소되고, 감소된 스칼라 값은 후속 로컬 반복을 위해 사용된다.

- [0041] 일단 원하는 로컬 반복이 LDPC 디코더(437)에 의해 완료되면, 최종 디코딩된 데이터는 하드 디시즌 출력(441)로서 제공되거나 채널 검출기(417)가 추가 프로세싱을 위해 이용 가능하게 될 때까지 디코딩된 데이터를 디-인터리빙하고 디-인터리빙된 데이터를 저장하기 위해 큐 버퍼(449)를 사용하는 디-인터리버 회로(445)에 대한 출력(485)으로서 제공된다.

- [0042] 이전 디-인터리빙 프로세스의 결과를 보유하는 큐 버퍼(449)의 버퍼 중 하나는 채널 검출기(417)로 언로딩되며, 큐 버퍼(449)의 다른 버퍼는 현재 디-인터리빙되고 있는 디코딩된 데이터 세트를 유지하며, 큐 버퍼(449)의 큐의 하나 이상의 다른 버퍼는 채널 검출기(417)에 의한 프로세싱을 기다리는 다른 수령되지 않는 데이터를 유지한다. 큐 버퍼(449)로부터의 수령되지 않은 데이터는 디-인터리버(445)에 의해 디-인터리빙되고 메모리 버퍼(413)의 대응 데이터 세트로의 액세스를 갖는 채널 검출기(417)로 전달된다. 특히, 디-인터리버(445)로부터의 디-인터리빙된 데이터는 승수 회로(427)를 사용하여 동적 스케일링 비율(407)( $\beta_x$ )에 의해 증가되고, 승수(429)의 곱셈 출력은 채널 검출기(417)에 제공된다. 채널 검출기(417)에 의해 수행되는 데이터 검출은 채널 검출기(409)에 의해 수행되는 것과 유사하다. 이와 달리, 데이터 세트가 LDPC 디코더(437)에서 수령하면, 이는 수신된 하드 디시즌 출력(441)을 디-인터리빙하는 디-인터리버 회로(457)에 대한 하드 디시즌 출력(441)으로서 제공되며, 디-인터리빙된 결과를 다수의 메모리 버퍼(461) 중 하나에 저장한다. 최종적으로, 디-인터리버 회로(457)는 출력(471)로서 메모리 버퍼(461)에 저장된 디-인터리빙된 데이터를 제공한다.

- [0043] 각 코드워드에 대응하는 디코딩된 출력(485)에 기초하여 각 코드워드에 대해 동적 스케일링 비율(403) 및 동적 스케일링 비율(407)이 계산된다. 큐 버퍼(449)의 각 버퍼는 각 코드워드에 대한 디코딩된 출력(485)을 위한 영역(441)과, 동적 스케일링 비율(403) 및 각 코드워드에 대응하는 동적 스케일링 비율(407)을 저장하는 다른 영역(443)을 포함한다. 채널 검출기(417)에 의한 디-인터리빙 및 프로세싱을 위해 각 큐 버퍼로부터 디코딩된 출력이 풀링되면, 스케일링 비율(403) 및 스케일링 비율(407)에 대한 값이 대응 큐 버퍼의 영역(441)으로부터 풀링되고 승수(493)에 의한 증가를 위해 사용된다.

- [0044] 동적 스칼라 계산 회로(497)는 각 코드워드에 대응하는 디코딩된 출력(485)에 기초하여 스케일링 비율(403)에 대한 값 및 각 코드워드에 대한 스케일링 비율(407)을 계산한다. 계산된 스케일링 비율은 스케일링 비율이 계산된 디코딩된 출력(485)에 대응하는 큐 버퍼(449)의 버퍼에 저장된다.

- [0045] 디코딩된 출력(485)을 사용하여, 동적 스칼라 계산 회로(497)는 먼저 스케일링 비율(403) 및 스케일링 비율(407)에 대한 값이 업데이트될지를 결정한다. 특히, 동적 스칼라 계산 회로(497)는 위반된 것으로 남은 LDPC 디코더 회로(437)에 의해 현재 프로세싱되고 있는 데이터 세트에 대한 패리티 체크의 수의 표시를 수신한다. 본 명세서에서 이 수는 위반 횟수라고 지칭한다. 또한, 동적 스칼라 계산 회로(497)는 포화된(즉, 최대 달성 가능한 값과 동일한 값을 갖는) 디코딩된 출력(485)의 비트 주기의 수를 카운트한다. 이 값을 포화 횟수라고 한다. 동적 스칼라 계산 회로(497)는 위반 횟수와 임계 값(423)을 비교하고 포화 횟수와 다른 임계 값을 비교한다. 일부 실시예에서, 임계 값(423)과 임계 값(425)은 모두 프로그래밍 가능하다. 위반 횟수가 임계 값(423)보다 작거나 포화 횟수가 임계(425)보다 크면 스케일링 비율(403) 및 스케일링 비율(407)의 값이 업데이트된다. 다음 유사코드가 업데이트 조건을 설명한다.

- ```

If (violation count < threshold 423 || saturation count > threshold 425) {

Update Scaling Factors

}

Else {

Maintain Scaling Factors

}

```

- [0046] 예시적인 경우에서, 스케일링 비율(403) 및 스케일링 비율(407)의 동적 수정은 현저한 개수의 포화된 소프트 디

시즌이 존재할 때마다 수행되기만 한다.

[0048] 업데이트가 호출될 때마다, 업데이팅 스케일링 비율(403) 및 스케일링 비율(407)은 특정 구현에 따라 다양한 방식으로 수행될 수 있다. 예를 들어, 업데이팅은 디폴트 값과 동일한 스케일링 비율(403) 및 스케일링 비율(407)을 초기에 설정함으로써 수행될 수 있다. 다음 유사코드가 초기 조건을 설명한다.

스케일링 비율 407 =  $\beta_{\text{default}}$ ; 및

스케일링 비율 403 =  $\alpha_{\text{default}}$

[0049] [0050] 디폴트 값,  $\beta_{\text{default}}$  및  $\alpha_{\text{default}}$ 는 설계시에 하드 코딩될 수 있고, 큐잉 검출 및 디코딩 회로(499)의 특정 전개에 의존하여 업데이트를 허용하도록 프로그래밍 가능할 수 있다. 디폴트 값  $\beta_{\text{default}}$  및  $\alpha_{\text{default}}$ 는 최소 포화만으로 우수한 성능을 제공하도록 선택될 수 있다. 일 실시예에서, 스케일링 비율(403) 및 스케일링 비율(407)의 값을 업데이트 하라는 디시즌에 따라, 스케일링 비율(403) 및 스케일링 비율(407)은 다음 유사코드에 따라 최대 값 스케일링 비율로 수정된다.

```

If (violation count < threshold 423 || saturation count > threshold 425) {

Scaling Factor 407 =  $\beta_{\text{maximum}}$ ; and

Scaling Factor 403 =  $\alpha_{\text{minimum}}$

}

Else {

Scaling Factor 407 =  $\beta_{\text{default}}$ ; and

Scaling Factor 403 =  $\alpha_{\text{default}}$

}

```

[0051]

[0052]  $\beta_{\text{maximum}}$  및  $\alpha_{\text{minimum}}$ 의 값을 설계시에 하드 코딩될 수 있거나 특정 전개에 의존하여 업데이트를 허용하도록 프로그래밍될 수 있다. 디폴트 값,  $\beta_{\text{maximum}}$  및  $\alpha_{\text{minimum}}$ 은 디폴트 스케일링 비율에 의해 허용되는 어떤 포화를 피하기 위해 설정되는 값으로 우수한 성능을 제공하도록 선택될 수 있다.

[0053] 큐잉 검출/디코딩 회로(499)는 도입된 데이터에 의존하여 다양한 개수의 검출 및 디코딩 반복의 수행을 허용한다. 또한, 일부 경우에, 큐잉 검출/디코딩 회로(499)의 사용을 통해 상당한 전력 절감이 달성될 수 있다. 또한, 일부 경우에, 더 빠른 LDPC 디코더가 구현되어 스투프을 증가시킬 수 있는데, 여기서 다수의 반복이 반드시 요구되지는 않으므로 실질적인 제 1 반복 데이터 수렴이 존재한다. 또한, LDPC 디코더(437)의 결과가 순서를 벗어나게 허용함으로써, 업스트림 프로세싱이 다운스트림 프로세싱의 완료를 기다리지 않아도 된다. 순서를 벗어난 결과의 재정렬은 검출/디코딩 회로(499)의 큐잉에 의해 또는 출력(471)이 다운스트림 수신에 의해 수행될 수 있다. 또한, 디코더(437) 내의 동적 스칼라를 사용하는 단계는 상대적으로 높은 로컬 스칼라 값을 사용하여 신속하게 코드워드의 실질적으로 노이즈가 없는 여역을 해결하게 하여, 상대적으로 작은 로컬 스칼라 값을 사용하여 코드워드의 노이즈가 더 많은 영역을 해결한다. 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 본 발명의 하나 이상의 구현을 통해 달성될 수 있는 다양한 다른 장점들을 인식할 것이다.

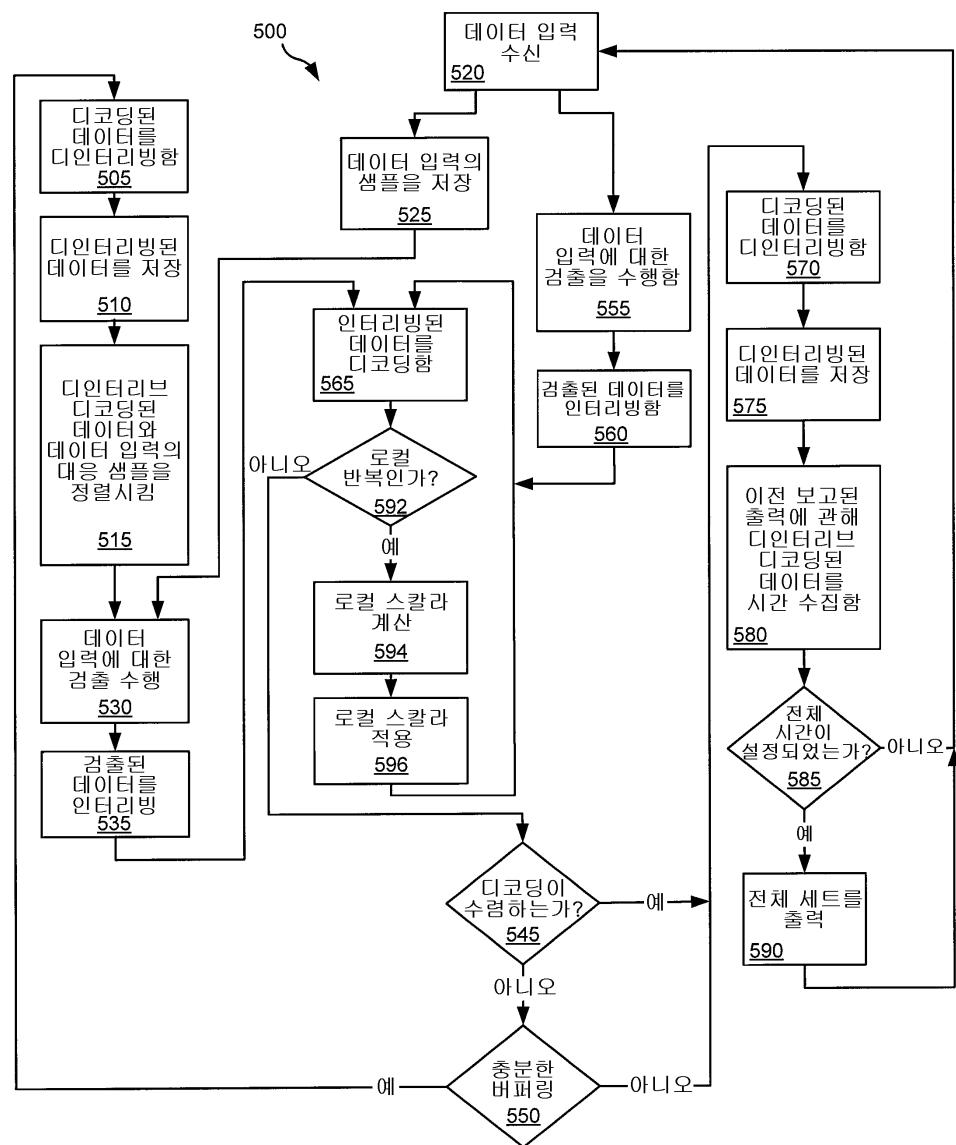

[0054] 도 5a를 참조하면, 흐름도(500)는 디코더 메시지의 동적 스케일링을 사용하는 데이터 프로세싱을 위한 본 발명의 일부 실시예에 따른 방법을 도시하고 있다. 흐름도(500)에 이어서, 데이터 입력이 수신된다(블록 520). 이 데이터 입력은 자기 기록 매체로부터 수신된 일련의 데이터 비트 또는 전송 채널로부터 수신된 일련의 비트 등 일 수 있다. 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 수신된 데이터 입력에 대한 다양한 소스 및 포맷을 인식할 것이다. 수신된 데이터의 샘플은 버퍼에 저장되어 추후 프로세싱을 위해 보관된다(블록 525). 데이터 검출 프로세스는 수신된 데이터상에서 수행된다(블록 555). 최종 검출된 데이터는 인터리빙된다(블록 560).

[0055] 인터리빙된 데이터가 디코딩된다(블록 565). 그 후, 다른 로컬 반복(즉, 디코더를 통한 다른 패스가 요구되는지)이 판단된다(블록 592). 이 판단은 디코더가 수렴되는지와, 수렴 실패가 디코더를 통한 추가 패스에 의해 이점을 가질 것인지에 기초하여 내려질 수 있다. 이 기술 분야에 알려진 추가 로컬 디코더 루프에 대한 필요성을 판단하는 방안이 사용될 수 있다. 추가 로컬 반복(즉, 디코딩 프로세스를 통한 다른 패스)이 요구되는 경우(블록 592), 로컬 스칼라가 계산된다(블록 594). 일부 경우, 이 로컬 스칼라 계산은 다수의 사전 결정된 스칼라 값 중 하나로부터 선택하는 것을 포함한다. 본 발명의 일부 실시예에서, 초기 로컬 스칼라 값이 제 1 전체 반복(즉, 데이터 검출 및 데이터 디코딩 모두의 수행)에서 사용되고, 동일한 로컬 스칼라 값이 전체 반복에 이어지는 각 후속 로컬 반복에 대해 사용된다. 각 추가적인 전체 반복이 발생하면, 스칼라 값은 정의된 양만큼 감소되고, 감소된 스칼라 값은 후속 로컬 반복을 위해 사용된다. 본 발명의 특정 실시예에서, 초기 스칼라 값은 0.75이고, 각 후속 전체 반복에서 스칼라 값은 1/32의 하드웨어에 사용하기 편한 값에 의해 감소된다. 따라

서, 제 2 전체 반복에서 스칼라 값은 0.7188이고, 제 3 전체 반복에서 스칼라 값은 0.6875이며, 제 4 전체 반복에서 스칼라 값은 0.6563이고, 제 5 전체 반복에서 스칼라 값은 0.625이며, 제 6 전체 반복에서 스칼라 값은 0.5938이고, 제 7 전체 반복에서 스칼라 값은 0.5625이며, 제 8 전체 반복에서 스칼라 값은 0.5313이고, 제 9 전체 반복에서 스칼라 값은 0.5이다. 어떤 지점에서, 스칼라 값은 감소되지 않고 상수를 유지한다. 따라서, 이전의 예를 사용하면, 제 10 및 그 이후의 전체 반복에서, 가변 스칼라 회로(439)는 스칼라 값을 0.5로 유지한다. 본 발명의 다른 실시예에서, 스칼라 값은 각 전체 반복 이후 발생하는 수정에 추가하여 또는 그 대신에 각 로컬 반복 후에 수정될 수 있다는 것을 유의해야 한다. 디코더 회로의 내부 값은 로컬 스칼라 값에 의해 증가되며(블록 596) 디코더 프로세스가 반복된다(블록 565). 다른 로컬 반복이 요구되는지가 판단된다(블록 592).

[0056] 일반적인 규칙으로서, 높은 로컬 스칼라 값을 사용하는 단계는 낮은 노이즈가 존재하는 디코더에 의한 수렴의 비율을 증가시킨다. 이와 반대로, 낮은 로컬 스칼라 값을 사용하는 단계는 수렴 레이트를 감소시키며 높은 노이즈가 데이터 스트림의 비트 중 하나 이상에 제시되는 수렴의 확률을 증가시킨다. 작은 스칼라에 의해 증가되는 비트는 디코더 회로를 포화시킬 가능성이 작으므로 더 많은 데이터가 디코딩 프로세스를 위해 사용되기 위해 유지되기 때문에 높은 수렴 확률이 발생한다. 가변 로컬 스칼라 값을 사용함으로써, 본 발명의 일부 실시예는 낮은 노이즈 레벨을 제시하는 코드워드의 다양한 영역에 상대적으로 빠른 수렴을 제공한다. 추후에, 노이즈의 높은 레벨을 제시하는 코드워드의 영역은 수렴의 비율을 감소시키는 점진적으로 낮은 스칼라를 사용하여 처리되지만 수렴을 달성하기 위해 사용될 수 있는 데이터의 범위를 증가시킨다.

[0057] 추가 로컬 반복이 요구되지 않는다고 판단하면(블록 592), 디코딩 프로세스가 수렴하는지(블록 545), 데이터를 재처리하기에 충분한 버퍼링이 이용 가능한지(블록 550)가 판단된다. 디코딩 프로세스가 수렴되거나(블록 545), 이용 가능한 버퍼링이 불충분한 경우(블록 550), 디코딩된 데이터는 인터리빙되고(블록 570) 버퍼에 저장된다(블록 575). 버퍼는 순서를 벗어난 이용 가능하게 되었을 수 있는 다양한 결과를 포함하는데, 다양한 결과는 대응 데이터 입력이 본래 수신된 순서를 나타내도록 버퍼에서 재정렬된다(블록 580). 그 후, 전체 시간 세트가 버퍼에서 사용 가능한지가 판단된다(블록 585). 전체 시간 세트는 주어진 시간 동안에 수신된 입력에 대응하는 모든 결과를 포함한다. 따라서, 예를 들어, 제 1 결과가 2개의 추후 결과가 보고되는 동안에 지연되는 경우, 일단 제 1 결과가 버퍼에서 최종적으로 이용 가능하면, 전체 시간 세트는 3개의 결과에 대해 존재한다. 본 발명의 일부 실시예에서, 결과는 수신자에게 순서를 벗어나서 보고된다는 것을 유의해야 한다. 이러한 경우, 결과를 보고하거나 전체 시간 세트가 이용 가능한지를 판단할 필요가 없다. 전체 시간 세트가 이용 가능한 경우(블록 585) 또는 순서에 상관 없이 수신된 대로 결과가 보고되어야 하는 경우, 결과는 수신자에게 출력된다(블록 590).

[0058] 이와 달리, 디코딩 프로세스가 수렴하지 않고(블록 545) 충분한 버퍼링이 이용 가능한 경우(블록 550), 다른 전체 반복이 수행된다. 전체 반복은 디코딩된 데이터를 디-인터리빙하는 것(블록 505)과, 버퍼에 디-인터리빙된 디코딩된 데이터를 버퍼에 저장하는 것(블록 510)을 포함한다. 디-인터리빙된 데이터는 데이터 검출기가 일단 이용 가능하게 되면 데이터 입력의 대응 샘플과 정렬된다(블록 515). 디-인터리빙된 데이터 및 대응 샘플 데이터 입력이 데이터 검출기에 제공되는데, 여기서 동일한 데이터 입력의 앞선 프로세싱(블록 555, 560, 565, 592, 594, 545, 550, 505, 510, 515)에서 개발된 소프트 입력을 사용하여 본래 저장된 데이터 입력의 샘플(블록 525)에 대해 후속 데이터 검출이 수행된다(블록 530). 데이터 검출 프로세스의 결과가 인터리빙되며(블록 535) 인터리빙된 데이터가 디코딩된다(블록 565). 이 지점에서, 블록(592, 594, 596, 545, 550)의 프로세스가 반복된다.

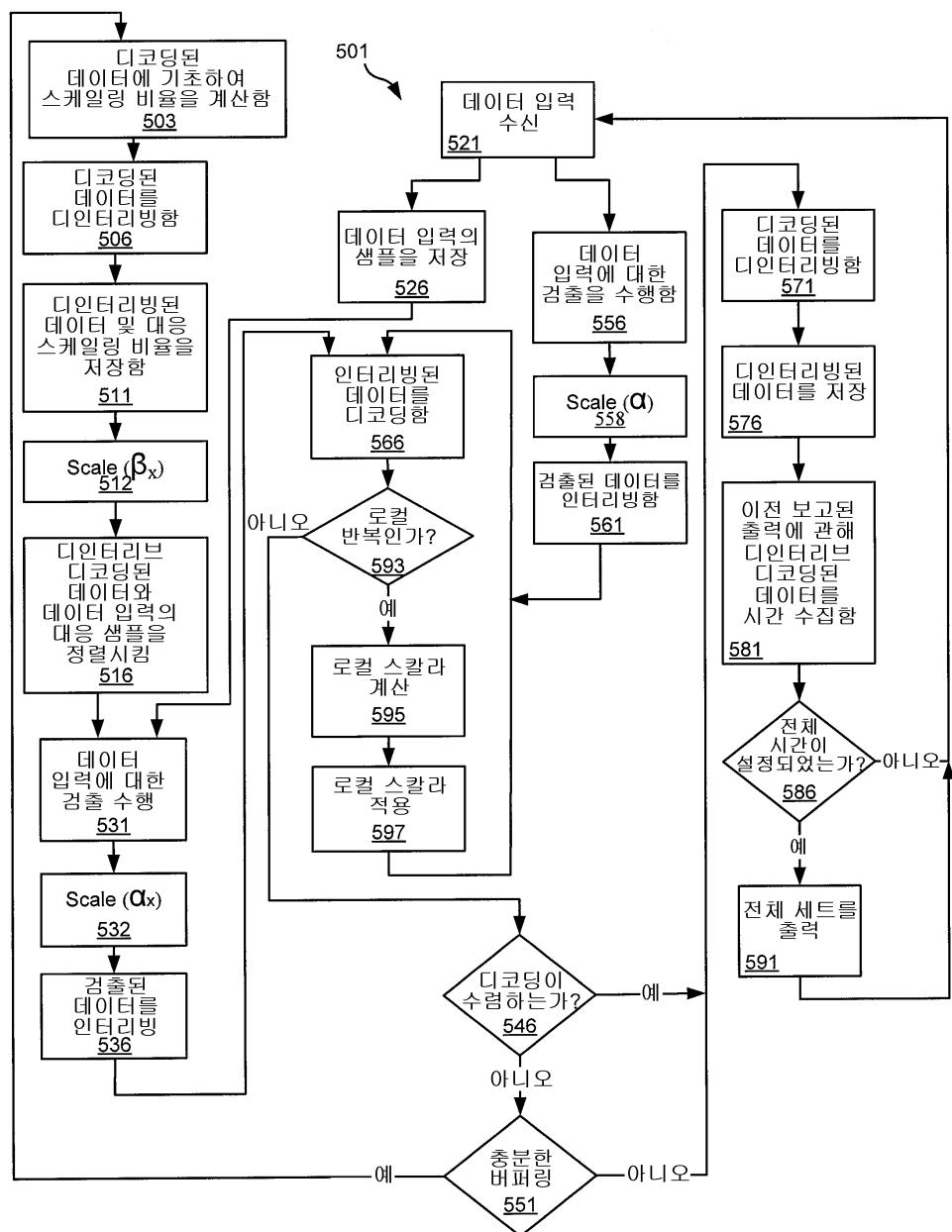

[0059] 도 5b를 참조하면, 흐름도(501)는 디코더 메시지의 동적 스케일링 및 전체 프로세스 루프의 동적 스케일링을 사용하여 데이터를 프로세싱하는 본 발명의 일부 실시예에 따른 방법을 도시하고 있다. 흐름도(501)에 이어서, 데이터 입력이 수신되나(블록 521). 이 데이터 입력은 자기 기록 매체로부터 수신된 일련의 데이터 비트 또는 전송 채널로부터 수신된 일련의 비트 등일 수 있다. 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 수신된 데이터 입력에 대한 다양한 소스 및 포맷을 인식할 것이다. 수신된 데이터의 샘플은 버퍼에 저장되어 추후 프로세싱을 위해 보관되고(블록 526), 데이터 검출 프로세스는 수신된 데이터상에서 수행된다(블록 556). 최종 검출된 데이터는 스케일링 비율( $\alpha$ )에 의해 증가되고(블록 558), 증가의 곱셈은 인터리빙된다(블록 561).

[0060] 인터리빙된 데이터가 디코딩된다(블록 566). 그 후, 다른 로컬 반복(즉, 디코더를 통한 다른 패스가 요구되는지)이 판단된다(블록 593). 이 판단은 디코더가 수렴하는지, 디코더를 통한 추가 패스에 의해 수렴 실패가 이점에 지니는지에 기초하여 내려질 수 있다. 이 기술 분야에 알려진 추가 로컬 디코더 루프에 대한 필요성을 판단하는 방안이 사용될 수 있다. 추가 로컬 반복(즉, 디코딩 프로세스를 통한 다른 패스)이 요구되는 경우(블록 592), 로컬 스칼라가 계산된다(블록 595). 일부 경우, 이 로컬 스칼라 계산은 다수의 사전 결정된 스칼라 값

중 하나로부터 선택하는 것을 포함한다. 본 발명의 일부 실시예에서, 초기 로컬 스칼라 값이 제 1 전체 반복(즉, 데이터 검출 및 데이터 디코딩 모두의 수행)에서 사용되고, 동일한 로컬 스칼라 값이 전체 반복에 이어지는 각 후속 로컬 반복에 대해 사용된다. 각 추가적인 전체 반복이 발생하면, 스칼라 값은 정의된 양만큼 감소되고, 감소된 스칼라 값은 후속 로컬 반복을 위해 사용된다. 본 발명의 특정 실시예에서, 초기 스칼라 값은 0.75이고, 각 후속 전체 반복에서 스칼라 값은 1/32의 하드웨어에 사용하기 편한 값에 의해 감소된다. 따라서, 제 2 전체 반복에서 스칼라 값은 0.7188이고, 제 3 전체 반복에서 스칼라 값은 0.6875이며, 제 4 전체 반복에서 스칼라 값은 0.6563이고, 제 5 전체 반복에서 스칼라 값은 0.625이며, 제 6 전체 반복에서 스칼라 값은 0.5938이고, 제 7 전체 반복에서 스칼라 값은 0.5625이며, 제 8 전체 반복에서 스칼라 값은 0.5313이고, 제 9 전체 반복에서 스칼라 값은 0.5이다. 어떤 지점에서, 스칼라 값은 감소되지 않고 상수를 유지한다. 따라서, 이전의 예를 사용하면, 제 10 및 그 이후의 전체 반복에서, 가변 스칼라 회로(439)는 스칼라 값을 0.5로 유지한다. 본 발명의 다른 실시예에서, 스칼라 값은 각 전체 반복 이후 발생하는 수정에 추가하여 또는 그 대신에 각 로컬 반복 후에 수정될 수 있다는 것을 유의해야 한다. 디코더 회로의 내부 값은 로컬 스칼라 값에 의해 증가되며(블록 597) 디코더 프로세스가 반복된다(블록 566). 다른 로컬 반복이 요구되는지가 판단된다(블록 593).

[0061]

일반적인 규칙으로서, 높은 로컬 스칼라 값을 사용하는 단계는 낮은 노이즈가 존재하는 디코더에 의한 수렴의 비율을 증가시킨다. 이와 반대로, 낮은 로컬 스칼라 값을 사용하는 단계는 수렴 레이트를 감소시키며 높은 노이즈가 데이터 스트림의 비트 중 하나 이상에 제시되는 수렴의 확률을 증가시킨다. 작은 스칼라에 의해 증가되는 비트는 디코더 회로를 포화시킬 가능성이 작으므로 더 많은 데이터가 디코딩 프로세스를 위해 사용되기 위해 유지되기 때문에 높은 수렴 확률이 발생한다. 가변 로컬 스칼라 값을 사용함으로써, 본 발명의 일부 실시예는 낮은 노이즈 레벨을 제시하는 코드워드의 다양한 영역에 상대적으로 빠른 수렴을 제공한다. 추후에, 노이즈의 높은 레벨을 제시하는 코드워드의 영역은 수렴의 비율을 감소시키는 점진적으로 낮은 스칼라를 사용하여 처리되지만 수렴을 달성하기 위해 사용될 수 있는 데이터의 범위를 증가시킨다.

[0062]

추가 로컬 반복이 요구되지 않는다고 판단하면(블록 593), 디코딩 프로세스가 수렴하는지(블록 546), 데이터를 재처리하기에 충분한 버퍼링이 이용 가능한지(블록 551)가 판단된다. 디코딩 프로세스가 수렴되거나(블록 546), 이용 가능한 버퍼링이 불충분한 경우(블록 551), 디코딩된 데이터는 인터리빙되고(블록 571) 버퍼에 저장된다(블록 576). 버퍼는 순서를 벗어난 이용 가능하게 되었을 수 있는 다양한 결과를 포함하는데, 다양한 결과는 대응 데이터 입력이 본래 수신된 순서를 나타내도록 버퍼에서 재정렬된다(블록 581). 그 후, 전체 시간 세트가 버퍼에서 사용 가능한지가 판단된다(블록 586). 전체 시간 세트는 주어진 시간 동안에 수신된 입력에 대응하는 모든 결과를 포함한다. 따라서, 예를 들어, 제 1 결과가 2개의 추후 결과가 보고되는 동안에 지연되는 경우, 일단 제 1 결과가 버퍼에서 최종적으로 이용 가능하면, 전체 시간 세트는 3개의 결과에 대해 존재한다. 본 발명의 일부 실시예에서, 결과는 수신자에게 순서를 벗어나서 보고된다는 것을 유의해야 한다. 이러한 경우, 결과를 보고하거나 전체 시간 세트가 이용 가능한지를 판단할 필요가 없다. 전체 시간 세트가 이용 가능한 경우(블록 586) 또는 순서에 상관 없이 수신된 대로 결과가 보고되어야 하는 경우, 결과는 수신자에게 출력된다(블록 591).

[0063]

이와 달리, 디코딩 프로세스가 수렴하지 않고(블록 546) 충분한 버퍼링이 이용 가능한 경우(블록 551), 다른 전체 반복이 수행된다. 전체 반복은 디코딩된 데이터에 기초하여, 전체 스케일링 비율( $\beta_x$  및  $\alpha_x$ )을 계산하는 것을 포함한다(블록 503). 스케일링 비율은 도 6a-6c를 참조하여 후술하는 방안 중 하나를 사용하여 계산될 수 있다. 또한, 디코딩된 데이터는 디-인터리빙되고(블록 506) 디-인터리빙된 디코딩된 데이터는 버퍼에 저장된다(블록 510). 디-인터리빙된 데이터는 일단 데이터 검출기가 이용 가능하면 데이터 입력의 대응 샘플과 정렬되고(블록 516) 스케일링 비율  $\beta_x$ 에 의해 증가된다(블록 512). 디-인터리빙된 데이터 및 대응 샘플 데이터 입력은 데이터 검출기로 제공되는데, 여기서 동일한 데이터 입력의 이전 프로세싱(블록 556, 558, 561, 566, 593, 595, 597, 546, 551, 503, 506, 511, 512, 516)에서 개발된 소프트 입력을 사용하여 데이터 입력의 본래 저장된 샘플(블록 526)에 대해 후속 데이터 검출기 수행된다(블록 531). 검출된 데이터는 스케일링 비율  $\alpha_x$ 에 의해 증가된다(블록 532). 데이터 검출 프로세스의 결과가 인터리빙되고(블록 536) 인터리빙된 데이터가 디코딩된다(블록 566). 여기서, 블록(593, 595, 597, 546, 551)의 프로세스가 반복된다.

[0064]

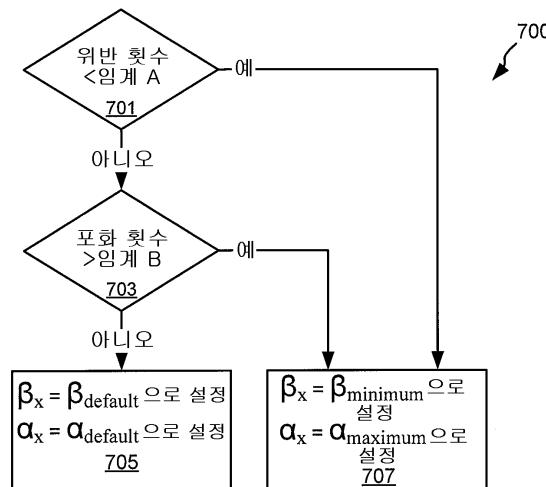

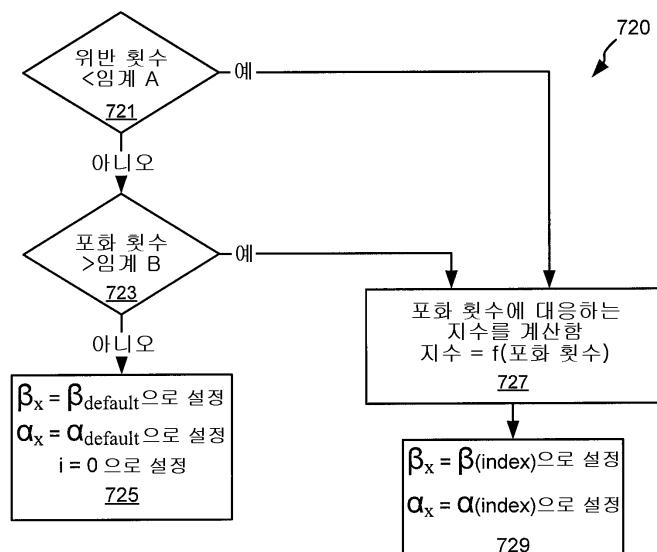

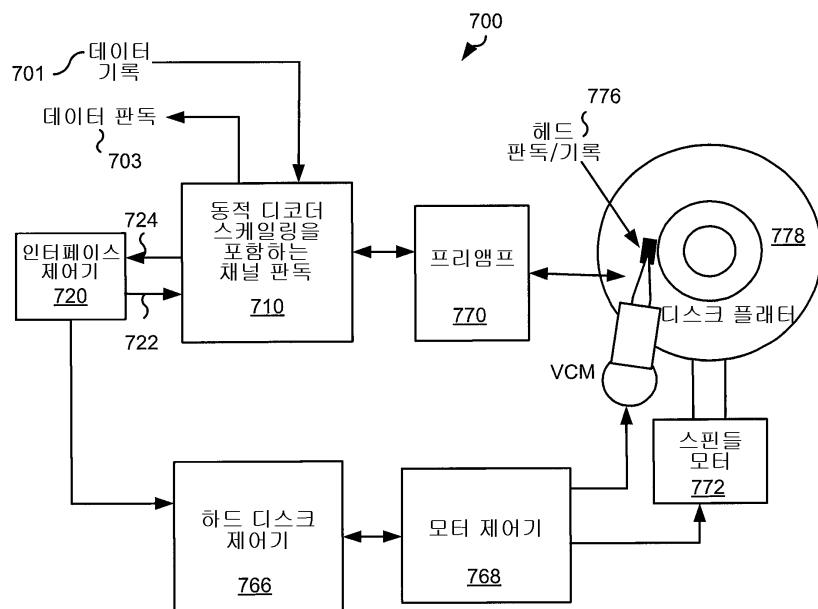

도 6a-6c를 참조하면, 본 발명의 여러 실시예에 따른 전체 루프에 대한 스케일링 비율을 동적으로 계산하는 3개의 상이한 방안이 도시되어 있다. 도 6a의 흐름도(700)에 이어서, 디코드 프로세스가 완료될 때마다, 위반 횟수가 제 1 임계(즉, 임계 A)보다 작은지(블록 701) 또는 포화 횟수가 제 2 임계(즉, 임계 B)보다 큰지(블록 703) 판단된다. 어느 쪽이든 참인 경우(블록 701, 703), 스케일링 비율은 업데이트된다(블록 707). 특히, 스

케일링 비율은 다음 식에 따라 업데이트된다.

[0065]  $\beta$  스케일링 비율 =  $\beta_{\text{maximum}}$ ; 및

$\alpha$  스케일링 비율 =  $\alpha_{\text{minimum}}$

[0066] 혹은, 업데이트가 호출되지 않으면(블록 701, 703), 스케일링 비율은 다음 식에 따라 디폴트 레벨로 설정된다(블록 705).

[0067]  $\beta$  스케일링 비율 =  $\beta_{\text{default}}$ ; 및

$\alpha$  스케일링 비율 =  $\alpha_{\text{default}}$

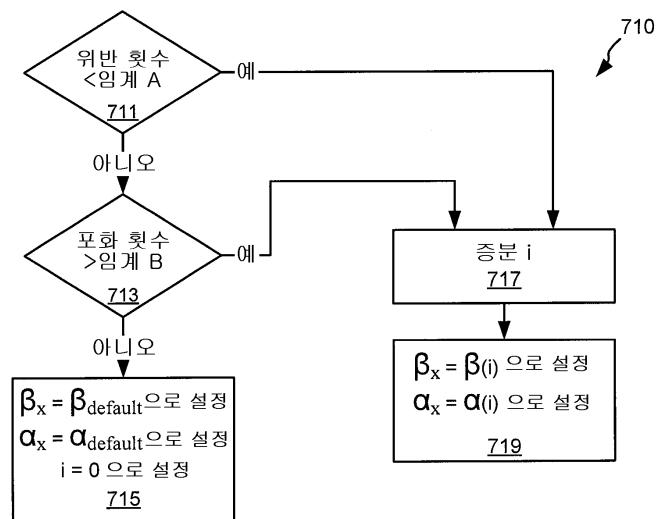

[0068] 도 6b의 흐름도(710)에 이어서, 디코드 프로세스가 완료될 때마다, 위반 횟수가 제 1 임계(즉, 임계 A)보다 작은지(블록 711) 또는 포화 횟수가 제 2 임계(즉, 임계 B)보다 큰지(블록 713) 판단된다. 어느 쪽이든 참인 경우(블록 711, 713), 루프 테이블로부터 스케일링 데이터에 액세스하도록 사용되는 index(i)가 증가된다(블록 717). 그 후, 스케일링 비율은 index를 사용하여 루프 테이블로부터 풀링된다(블록 729). 특히, 스케일링 비율은 다음 식에 따라 업데이트된다.

[0069]  $\beta$  스케일링 비율 =  $\beta(i)$ ; 및

$\alpha$  스케일링 비율 =  $\alpha(i)$

[0070]  $\beta(i+1)$ 은  $\beta(i)$ 보다 크고  $\alpha(i+1)$ 은  $\alpha(i)$ 보다 작다. 혹은, 업데이트가 호출되지 않으면(블록 711, 713), 스케일링 비율은 다음 식에 따라 디폴트 레벨(블록 715)으로 설정된다.

[0071]  $\beta$  스케일링 비율 =  $\beta_{\text{default}}$ ; 및

$\alpha$  스케일링 비율 =  $\alpha_{\text{default}}$

[0072] 도 6c의 흐름도(720)에 이어서, 디코드 프로세스가 완료될 때마다, 위반 횟수가 제 1 임계(즉, 임계 A)보다 작은지(블록 721) 또는 포화 횟수가 제 2 임계(즉, 임계 B)보다 큰지(블록 723) 판단된다. 어느 쪽이든 참인 경우(블록 721, 723), 포화 횟수에 대응하는 index가 계산된다(블록 727). 일부 경우에, index는 스칼라 값에 의해 증가되고 다음 전체 횟수로 증가되는 포화 횟수이다. 그 후, 스케일링 비율은 index를 사용하여 루프 테이블로부터 풀링된다(블록 729). 특히, 스케일링 비율은 다음 식에 따라 업데이트된다.

[0073]  $\beta$  스케일링 비율 =  $\beta(\text{index})$ ; 및

$\alpha$  스케일링 비율 =  $\alpha(\text{index})$

[0074]  $\beta(i+1)$ 은  $\beta(i)$ 보다 크고  $\alpha(i+1)$ 은  $\alpha(i)$ 보다 작다. 혹은, 업데이트가 호출되지 않으면(블록 721, 723), 스케일링 비율은 다음 식에 따라 디폴트 레벨(블록 725)으로 설정된다.

[0075]  $\beta$  스케일링 비율 =  $\beta_{\text{default}}$ ; 및

$\alpha$  스케일링 비율 =  $\alpha_{\text{default}}$

[0076] 도 6d의 흐름도(820)에 이어서, 디코드 프로세스가 완료될 때마다, 위반 횟수가 임계보다 작은지(블록 821) 판단된다. 이것이 참인 경우(블록 821), 스케일링 비율( $\beta_x$ ,  $\alpha_x$ )이 계산된다(블록 829). 혹은, 업데이트가 호출되지 않으면(블록 821), 스케일링 비율은 다음 식에 따라 디폴트 레벨로 설정된다(블록 825).

[0077]  $\beta$  스케일링 비율 =  $\beta_{\text{default}}$ ; 및

$\alpha$  스케일링 비율 =  $\alpha_{\text{default}}$

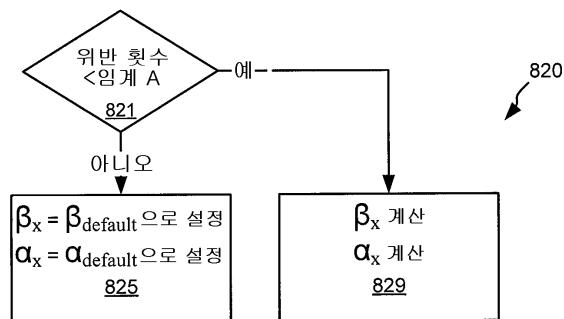

[0078] 도 7을 참조하면, 본 발명의 다양한 실시예에 따른 동적 디코더 스케일링을 포함하는 판독 채널(710)을 포함하는 저장 시스템(700)이 도시되어 있다. 저장 시스템(700)은, 예를 들어, 하드 디스크 드라이브일 수 있다. 판독 채널(710)은 동적 스케일링을 포함하는 디코더 회로를 포함하는 도 2 또는 도 4와 관련하여 설명한 것과 유사한 데이터 프로세싱 코덱 등을 포함할 수 있다. 일부 경우에, 데이터 프로세싱 코덱은 도 5 중 하나와 관련하여 설명한 것과 유사하게 동작할 수 있다.

[0079] 또한, 저장 시스템(700)은 사전 증폭기(770), 인터페이스 제어기(720), 하드 디스크 제어기(766), 모터 제어기(768), 스픈들 모터(spindle motor, 772), 디스크 플래터(disk platter, 778) 및 판독/기록 헤드 어셈블리(776)를 포함한다. 인터페이스 제어기(720)는 디스크 플래터로의/로부터의 데이터의 어드레싱 및 타이밍을 제어한다. 디스크 플래터(778)상의 데이터는 판독/기록 헤드 어셈블리(776)가 디스크 플래터(778) 위에 올바르게 위치될 때 이 어셈블리에 의해 검출될 수 있는 자기 신호 그룹으로 구성된다. 일 실시예에서, 디스크 플래터(778)는 수직 레코딩 방안에 따라 레코딩되는 자기 신호를 포함한다. 예를 들어, 자기 신호는 횡방향 또는 수

직 레코딩된 신호로서 레코딩될 수 있다.

[0080]

통상적인 판독 동작에서, 판독/기록 헤드 어셈블리(776)는 모터 제어기(768)에 의해 디스크 플래터(778)상의 원하는 데이터 트랙 위에 정확하게 위치된다. 인터페이스 제어기(720)를 통해 수신되는 어드레스에 의해 적합한 데이터 트랙이 정의된다. 모터 제어기(768)는 디스크 플래터(778)와 관련하여 판독/기록 헤드 어셈블리(776) 모두를 위치시키고 하드 디스크 제어기(766)의 방향 아래에서 디스크 플래터(778)상의 올바른 데이터 트랙으로 판독/기록 헤드 어셈블리를 이동시킴으로써 스픈들 모터(772)를 구동한다. 스픈들 모터(772)는 결정된 스픈 레이트(RPM)으로 디스크 플래터(778)를 회전시킨다. 일단 판독/기록 헤드 어셈블리(778)가 올바른 데이터 트랙 부근에 위치되면, 디스크 플래터(778)상의 데이터를 나타내는 자기 신호는 디스크 플래터(778)가 스픈들 모터(772)에 의해 회전됨에 따라 판독/기록 헤드 어셈블리(776)에 의해 감지된다. 감지된 자기 신호는 디스크 플래터(778)상의 자기 데이터를 나타내는 연속적인 미세한 아날로그 신호로서 제공된다. 이 미세한 아날로그 신호는 사전 증폭기(770)를 통해 판독/기록 헤드 어셈블리로부터 판독 채널(710)로 전달된다. 사전 증폭기(770)는 디스크 플래터(778)로부터 액세스되는 미세한 아날로그 신호를 증폭할 수 있다. 한편, 판독 채널 모듈(710)은 수신된 아날로그 신호를 디코딩하고 디지털화하여 디스크 플래터(778)에 본래 기록된 정보를 재생성한다. 디코딩 프로세스는 로컬 반복 루프를 사용할 수 있는데, 여기서 디코더 회로의 출력은 동적으로 스케일링되고 디코더 회로로의 입력으로서 제공된다. 이 입력은 다시 디코딩된다. 판독 데이터는 판독 데이터(703)로서 제공된다. 기록 동작은 판독 패널 모듈(710)에 제공되는 기록 데이터(701)를 갖는 이전 판독 동작의 실질적으로 반대이다. 그 후, 이 데이터는 디스크 플래터(778)로 인코딩되고 기록된다.

[0081]

도 8을 참조하면, 본 발명의 여러 실시예에 따른 가변 스케일링된 디코더 프로세싱을 갖는 판독 채널 회로를 갖는 수신기(895)를 포함하는 통신 시스템(891)이 도시되어 있다. 통신 시스템(891)은 이 기술 분야에 알려진 바와 같이 전송 매체(897)를 통해 인코딩된 정보를 전송할 수 있는 송신기(893)를 포함한다. 인코딩된 데이터는 수신기(895)에 의해 전송 매체(897)로부터 수신된다. 수신기(895)는 가변 스케일링된 디코더 프로세싱과 판독 채널 회로를 포함한다. 포함된 판독 채널 회로는 입력 스트림의 프로세싱에 기초하여 디코더 스케일링 비율을 적응적으로 계산할 수 있다. 따라서, 적응적 계산 회로는 도 2-5와 관련하여 설명한 바에 따라 구현될 수 있다. 본 명세서에서 제공되는 개시 내용에 기초하여, 당업자는 본 발명의 실시예에 따른 이퀄리제이션 및 타게팅이 수행될 수 있는 다양한 매체를 인식할 것이다.

[0082]

결론적으로, 본 발명은 데이터 디코딩 및/또는 검출을 수행하기 위한 신규한 시스템, 장치, 방법 및 배열을 제공한다. 본 발명의 하나 이상의 실시예의 상세한 설명은 설명하였지만, 본 발명의 사상을 벗어나지 않고 다양한 대체물, 수정물 및 균등물은 당업자에게 자명할 것이다. 예를 들어, 본 발명의 하나 이상의 실시예는 다양한 데이터 저장 시스템 및 디지털 통신 시스템에 적용될 수 있는데, 예를 들어, 테이프 레코딩 시스템, 광 디스크 드라이브, 무선 시스템 및 디지털 가입 라인 시스템 등에 적용될 수 있다. 그러므로, 전술한 내용은 본 발명의 범위를 제한하는 것으로 간주되어서는 안되며 본 발명의 범위는 첨부된 청구범위에 의해 정의된다.

## 도면

### 도면1

#### (종래기술)

## 도면2a

## 도면2b

## 도면3

도면4a

도면4b

### 도면5a

## 도면5b

## 도면6a

## 도면6b

## 도면6c

## 도면6d

## 도면7

## 도면8