(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5084887号

(P5084887)

(45) 発行日 平成24年11月28日(2012.11.28)

(24) 登録日 平成24年9月14日(2012.9.14)

(51) Int.Cl.

F 1

|              |           |              |         |

|--------------|-----------|--------------|---------|

| G 11 C 19/28 | (2006.01) | G 11 C 19/28 | D       |

| G 11 C 19/00 | (2006.01) | G 11 C 19/00 | J       |

| G 09 G 3/20  | (2006.01) | G 09 G 3/20  | 6 2 3 H |

| G 09 G 3/36  | (2006.01) | G 09 G 3/20  | 6 2 2 E |

|              |           | G 09 G 3/20  | 6 1 1 H |

請求項の数 9 (全 24 頁) 最終頁に続く

(21) 出願番号

特願2010-202554 (P2010-202554)

(22) 出願日

平成22年9月10日(2010.9.10)

(65) 公開番号

特開2011-86363 (P2011-86363A)

(43) 公開日

平成23年4月28日(2011.4.28)

審査請求日

平成24年7月27日(2012.7.27)

(31) 優先権主張番号

特願2009-214297 (P2009-214297)

(32) 優先日

平成21年9月16日(2009.9.16)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 小山 潤

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 堀田 和義

早期審査対象出願

最終頁に続く

(54) 【発明の名称】 駆動回路、当該駆動回路を具備する表示装置、当該表示装置を具備する電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

複数段のパルス出力回路を有し、

前記パルス出力回路は、

第1のノード及び第2のノードの電位に応じて出力信号を出力することができる機能を有する第1の回路と、

前記第1のノードに、前段のパルス出力回路の出力信号に応じた信号を供給することができる機能を有する第2の回路と、

前記第2のノードに間欠的に高電源電位の信号を供給することができる機能を有する第3の回路と、

前記第2のノードがゲートに電気的に接続され、前記第2のノードの電位に応じて、前記第1のノードの電位を制御することができる機能を有する第1のトランジスタと、

前記前段のパルス出力回路の出力信号に応じた信号がゲートに供給され、前記第2のノードの電位を制御することができる機能を有する第2のトランジスタと、

前記第1のトランジスタのソース端子と、低電源電位を供給することができる機能を有する配線との間に、前記第1のトランジスタのソース端子の電位を低電源電位より昇圧することができる機能を有する第4の回路と、

前記第2のトランジスタのソース端子と、低電源電位を供給することができる機能を有する前記配線との間に、前記第2のトランジスタのソース端子の電位を低電源電位より昇圧することができる機能を有する第5の回路と、

10

20

前記第1のトランジスタのソース端子の電位を低電源電位にすることができる機能を有する第1のスイッチと、

前記第2のトランジスタのソース端子の電位を低電源電位にすることができる機能を有する第2のスイッチと、を有し、

前記第1のトランジスタ及び前記第2のトランジスタは、チャネル領域に酸化物半導体を有し、

前記第1のスイッチ及び前記第2のスイッチは、前記第1のトランジスタ及び前記第2のトランジスタがエンハンスマント型、またはディプレッション型であるかを判定することができる機能を有する判定回路によって制御されることを特徴とする駆動回路。

【請求項2】

10

複数段のパルス出力回路を有し、

前記パルス出力回路は、

第1のノード及び第2のノードの電位に応じて出力信号を出力することができる機能を有する第1の回路と、

前記第1のノードに、前段のパルス出力回路の出力信号に応じた信号を供給することができる機能を有する第2の回路と、

前記第2のノードに間欠的に高電源電位の信号を供給することができる機能を有する第3の回路と、

前記第2のノードがゲートに電気的に接続され、前記第2のノードの電位に応じて、前記第1のノードの電位を制御することができる機能を有する第1のトランジスタと、

20

前記前段のパルス出力回路の出力信号に応じた信号がゲートに供給され、前記第2のノードの電位を制御することができる機能を有する第2のトランジスタと、

前記第1のトランジスタのソース端子と、低電源電位を供給することができる機能を有する配線との間に、前記第1のトランジスタのソース端子の電位を低電源電位より昇圧することができる機能を有する第4の回路と、

前記第2のトランジスタのソース端子と、低電源電位を供給することができる機能を有する前記配線との間に、前記第2のトランジスタのソース端子の電位を低電源電位より昇圧することができる機能を有する第5の回路と、

前記第1のトランジスタのソース端子の電位を低電源電位にすることができる機能を有する第1のスイッチと、

30

前記第2のトランジスタのソース端子の電位を低電源電位にすることができる機能を有する第2のスイッチと、を有し、

前記第1のスイッチ及び前記第2のスイッチは、前記第1のトランジスタ及び前記第2のトランジスタがエンハンスマント型、またはディプレッション型であるかを判定することができる機能を有する判定回路によって制御されることを特徴とする駆動回路。

【請求項3】

請求項1又は請求項2において、

前記第4の回路は、ゲートとドレイン端子が電気的に接続され、ソース端子が前記配線に電気的に接続された第3のトランジスタを有し、

前記第5の回路は、ゲートとドレイン端子が電気的に接続され、ソース端子が前記配線に電気的に接続された第4のトランジスタを有することを特徴とする駆動回路。

40

【請求項4】

請求項3において、

前記第3のトランジスタのL/Wは、前記第1のトランジスタのL/Wより大きく、かつ前記第2のトランジスタのL/Wより大きく、

前記第4のトランジスタのL/Wは、前記第1のトランジスタのL/Wより大きく、かつ前記第2のトランジスタのL/Wより大きいことを特徴とする駆動回路。

【請求項5】

請求項3又は請求項4において、

前記第3のトランジスタ及び前記第4のトランジスタは、チャネル領域に酸化物半導体

50

を有することを特徴とする駆動回路。

**【請求項 6】**

請求項 1 乃至請求項 5 のいずれか一において、

前記判定回路は、定電流源、トランジスタ、コンパレータ、及びバッファ回路を有することを特徴とする駆動回路。

**【請求項 7】**

請求項 1 乃至請求項 6 のいずれか一において、

前記第 1 のスイッチ及び前記第 2 のスイッチはそれぞれトランジスタで構成され、該トランジスタのチャネル領域は酸化物半導体を有することを特徴とする駆動回路。

**【請求項 8】**

請求項 1 乃至請求項 7 のいずれか一に記載の駆動回路を具備する表示装置。 10

**【請求項 9】**

請求項 8 に記載の表示装置を具備する電子機器。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、駆動回路（シフトレジスタ回路ともいう）に関する。または、画素部と同じ基板に形成される駆動回路を有する表示装置に関する。または、当該表示装置を具備する電子機器に関する。 20

**【背景技術】**

**【0002】**

表示装置は、液晶テレビなどの大型表示装置の普及に伴い、より付加価値の高い製品が求められており、開発が進められている。特に、チャネル領域が非晶質半導体、特に酸化物半導体によって構成される薄膜トランジスタ（TFT）を用いて、画素部と同じ基板に走査線駆動回路などの駆動回路を構成する技術は、活発に開発が進められている。

**【0003】**

チャネル領域が非晶質半導体によって構成される薄膜トランジスタは、単極性の回路構成によって駆動回路を構成することが多く、一例としては、特許文献 1 に記載の構成が挙げられる。 30

**【先行技術文献】**

**【特許文献】**

**【0004】**

**【特許文献 1】特開 2005-251348 号公報**

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

チャネル領域が非晶質半導体によって構成される薄膜トランジスタを単極性の駆動回路に用いる場合、しきい値電圧のばらつき等により、動作に不具合が生じる場合がある。具体的にしきい値電圧のばらつきにより生じる問題点について、図 11 を示し詳述する。 40

**【0006】**

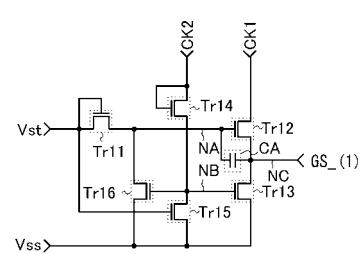

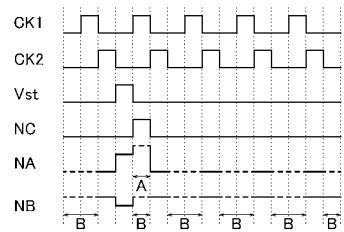

図 11 (A) に示す単極性回路は一例として特許文献 1 の図 1 に記載のシフトレジスタを構成するパルス出力回路の 1 段目について示した回路であり、トランジスタ Tr 11、トランジスタ Tr 12、トランジスタ Tr 13、トランジスタ Tr 14、トランジスタ Tr 15、トランジスタ Tr 16、容量素子 CA を有するものである。また図 11 (A) 中、NA はトランジスタ Tr 12 のゲート端子のノード、NB はトランジスタ Tr 13 のゲート端子のノード、NC は出力端子のノードについて、示すものである。また図 11 (A) では、トランジスタ Tr 12 に第 1 のクロック信号 CK 1 が入力され、トランジスタ Tr 14 に第 2 のクロック信号 CK 2 が入力され、トランジスタ Tr 11 及びトランジスタ Tr 15 にスタートパルス Vst が入力され、トランジスタ Tr 13、トランジスタ Tr 1 50

5、トランジスタTr16に低電源電位(Vss)が供給される構成が開示されている。また図11(A)で信号GS\_(1)は、1段目のパルス出力回路の信号について示すものである。また図11(B)に示すタイミングチャートは、特許文献1の図2に記載の図11(A)に示す回路のタイミングチャートである。図11(A)中の各素子は、図11(B)の信号に応じて動作することとなる。

【0007】

図11(A)中のノードNAでは、出力信号を高電源電位の信号(H信号ともいう)にするために、定期的に、電気的にフローティング状態(浮遊状態)及び所定の電位が入力される状態がある(図11(B)中、NAで点線の期間がフローティング状態の期間、実線の期間が所定の電位が入力される期間)。同様に、図11(A)中のノードNBでは、出力信号を低電源電位の信号(L信号ともいう)に保持するために、定期的に、電気的にフローティング状態及び所定の電位が入力される状態がある(図11(B)中、NBで点線の期間がフローティング状態の期間、実線の期間が所定の電位が入力される期間)。

10

【0008】

上述したように、チャネル領域が非晶質半導体によって構成される薄膜トランジスタを単極性の駆動回路に用いる場合、しきい値電圧のばらつきを生じることで、トランジスタがエンハンスマント型(ノーマリーオフともいう)、ディプレッション型(ノーマリーオンともいう)になることがある。ノーマリーオンの場合には、ノードNAの電位が、特に図11(B)中、Aの期間で、トランジスタTr16からのリーク電流により低下し、出力信号をH信号に保持できないといった問題がある。同様に、ノーマリーオンの場合には特に図11(B)中、Bの期間で、ノードNBの電位がトランジスタTr15からのリーク電流により低下し、ゲート電位がLレベルであっても、出力信号をL信号に保持できないといった問題がある。また、トランジスタがノーマリーオンとなることを抑制するために、各端子に入力する電位を調整することで対策をとった場合、トランジスタがノーマリーオフとなった場合には所望の動作が得られないといった問題が生じる。

20

【0009】

なお、図11(A)、(B)に示す例に限らずに、ダイナミック駆動により、順次パルスを出力する駆動回路の場合には、リーク電流の増加が誤動作の原因になる。また、パルス出力回路を具備する駆動回路を生産する上で、エンハンスマント型、またはディプレッション型となるかが基板毎に異なるといったバラツキが生じることもあり、その際予めエンハンスマント型、またはディプレッション型の一方となる際の対策を講じた回路設計では、エンハンスマント型、またはディプレッション型の他方となつた際の対応が難しくなるといった問題もあり得る。そのため、薄膜トランジスタの特性がエンハンスマント型、またはディプレッション型であるに関わらず、誤動作のない駆動回路となる回路設計であることが求められる。

30

【0010】

そこで本発明の一態様は、チャネルが非晶質半導体によって構成される薄膜トランジスタを単極性の駆動回路に用いる際、薄膜トランジスタの作製条件等に起因するしきい値電圧のばらつきによって、エンハンスマント型、またはディプレッション型のいずれかに変動する駆動回路であっても、回路内の誤動作を低減できる駆動回路を提供することを課題の一とする。

40

【課題を解決するための手段】

【0011】

本発明の一態様は、複数段のパルス出力回路を有する駆動回路において、パルス出力回路は、第1のノード、第2のノードの電位に応じて出力信号を出力するための第1の回路と、第1のノードに、前段のパルス出力回路の出力信号に応じた信号を供給する第2の回路と、第2のノードに間欠的に高電源電位の信号を供給するための第3の回路と、第2のノードがゲートに電気的に接続され、第2のノードの電位に応じて、第1のノードの電位を制御するための第1のトランジスタと、前段のパルス出力回路の出力信号に応じた信号がゲートに供給され、第2のノードの電位を制御するための第2のトランジスタと、を有

50

し、第1のトランジスタ及び第2のトランジスタのソース端子と、低電源電位を供給する配線との間には、ソース端子の電位を低電源電位より昇圧するための第4の回路が設けられており、ソース端子の電位を低電源電位にするためのスイッチを有し、スイッチは、第1のトランジスタ及び第2のトランジスタがエンハンスマント型、またはディプレッション型であるかを判定する判定回路によって、制御されることを特徴とする駆動回路である。

【0012】

本発明の一態様において、第4の回路は、ゲートとドレイン端子が電気的に接続され、ソース端子が低電源電位が供給される配線に電気的に接続されたトランジスタを有する回路である駆動回路でもよい。

10

【0013】

本発明の一態様において、第4の回路を構成するトランジスタのL/Wは、第1のトランジスタ及び第2のトランジスタのL/Wより大きい駆動回路でもよい。

【0014】

本発明の一態様において、判定回路は、定電流源、トランジスタ、コンパレータ、及びバッファ回路を有する駆動回路でもよい。

【0015】

本発明の一態様において、スイッチはトランジスタである駆動回路でもよい。

【0016】

本発明の一態様において、駆動回路を構成するトランジスタは、酸化物半導体層でなる半導体層を有する駆動回路でもよい。

20

【発明の効果】

【0017】

本発明の一態様により、チャネルが非晶質半導体によって構成される薄膜トランジスタを単極性の駆動回路に用いる際、薄膜トランジスタの作製条件等に起因するしきい値電圧のばらつきによって、エンハンスマント型、またはディプレッション型のいずれかに変動する駆動回路であっても、回路内の誤動作を低減できる駆動回路を提供することができる。

【図面の簡単な説明】

【0018】

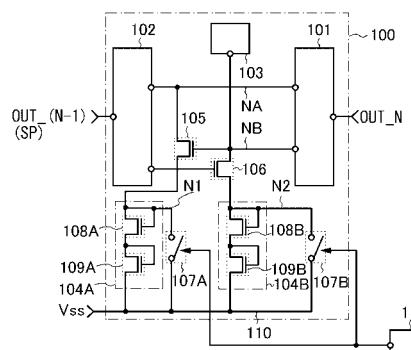

【図1】パルス出力回路の一例を示す図。

30

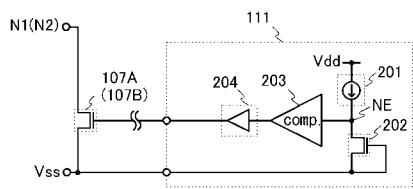

【図2】判定回路の一例を示す図。

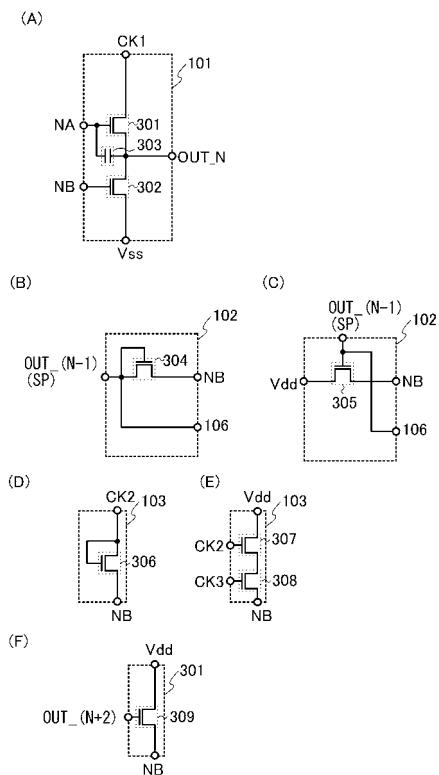

【図3】パルス出力回路を構成する各回路の一例を示す図。

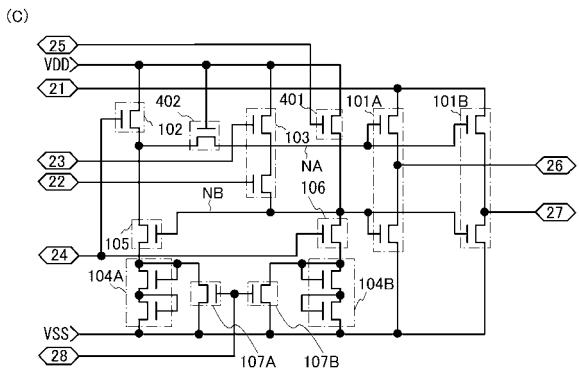

【図4】パルス出力回路及びシフトレジスタの一例を示す図。

【図5】シフトレジスタのタイミングチャートを示す図。

【図6】パルス出力回路の動作を説明するフローチャート図。

【図7】表示装置の断面図の一例を示す図。

【図8】表示装置のブロック図の一例を示す図。

【図9】シフトレジスタのブロック図及びタイミングチャートの一例を示す図。

【図10】表示装置の一例を示す図。

【図11】従来の回路の課題について説明するための図。

40

【発明を実施するための形態】

【0019】

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従つて実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じ物を指し示す符号は異なる図面間において共通とする。

【0020】

なお、各実施の形態の図面等において示す各構成の、大きさ、層の厚さ、又は領域は、明瞭化のために誇張されて表記している場合がある。よって、必ずしもそのスケールに限定

50

されない。

【0021】

なお本明細書にて用いる第1、第2、第3、乃至第N（Nは自然数）という用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

【0022】

（実施の形態1）

本実施の形態では、まず、複数段のパルス出力回路を有する駆動回路でのパルス出力回路の一段の構成について図面を参照して説明する。

【0023】

本実施の形態で示すパルス出力回路100は、第1の回路101、第2の回路102、第3の回路103、第4の回路104A及び104B、第1のトランジスタ105、第2のトランジスタ106、スイッチ107A及び107Bを有する。なおパルス出力回路100を構成する各トランジスタはnチャネル型の薄膜トランジスタである。

【0024】

なおパルス出力回路100を構成する各トランジスタの半導体層として、酸化物半導体を用いてもよい。酸化物半導体を用いたトランジスタはアモルファスシリコン等のシリコン系半導体材料を用いたトランジスタと比較して電界効果移動度が高い。なお酸化物半導体としては、例えば、酸化亜鉛（ZnO）、酸化スズ（SnO<sub>2</sub>）なども用いることができる。また、ZnOにInやGaなどを添加することもできる。

【0025】

酸化物半導体としてInMO<sub>3</sub>（ZnO）<sub>x</sub>（x>0）で表記される薄膜を用いることができる。なお、Mは、ガリウム（Ga）、鉄（Fe）、ニッケル（Ni）、マンガン（Mn）及びコバルト（Co）から選ばれた一の金属元素又は複数の金属元素を示す。例えばMとして、Gaの場合があることの他、GaとNi又はGaとFeなど、Ga以外の上記金属元素が含まれる場合がある。また、上記酸化物半導体において、Mとして含まれる金属元素の他に、不純物元素としてFe、Niその他の遷移金属元素、又は該遷移金属の酸化物が含まれているものがある。例えば、酸化物半導体層としてIn-Ga-Zn-O系膜を用いることができる。

【0026】

酸化物半導体（InMO<sub>3</sub>（ZnO）<sub>x</sub>（x>0）膜）としてIn-Ga-Zn-O系膜のかわりに、Mを他の金属元素とするInMO<sub>3</sub>（ZnO）<sub>x</sub>（x>0）膜を用いてもよい。また、酸化物半導体として上記の他にも、In-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系、In-Zn-O系、Sn-Zn-O系、Al-Zn-O系、In-O系、Sn-O系、Zn-O系の酸化物半導体を適用することができる。

【0027】

なお、第1の回路101は、第1のノードNA、第2のノードNBの電位に応じて高電源電位の信号または低電源電位の信号を出力信号として出力するための回路であり、第1のノードNA、第2のノードNBの電位に応じて当該段（図1ではN段目）の出力信号OUT<sub>N</sub>とする回路である。

【0028】

なお高電源電位とは、基準電位より高い電位のことであり、低電源電位とは基準電位以下の電位のことをいう。なお高電源電位及び低電源電位ともに、トランジスタが動作できる程度の電位、すなわち高電源電位がゲートに印加されることで理想的なトランジスタ（しきい値電圧が0V）がオン状態となり、低電源電位が印加されることで理想的なトランジスタオフ状態となる電位であることが望ましい。

【0029】

なお、電圧とは、ある電位と、基準の電位（例えばグラウンド電位）との電位差のことと示す場合が多い。よって、電圧、電位、電位差を、各々、電位、電圧、電圧差と言い換える。

10

20

30

40

50

ることが可能である。

【0030】

なお、薄膜トランジスタの構成は、様々な形態をとることができ、特定の構成に限定されない。例えば、ゲート電極が2個以上のマルチゲート構造を適用することができる。

【0031】

また、チャネル領域の上下にゲート電極が配置されている構造を適用することができる。

なお、チャネル領域の上下にゲート電極が配置される構成にすることにより、複数の薄膜トランジスタが並列に接続されたような構成とすることも可能である。

【0032】

なお、AとBとが接続されている、と明示的に記載する場合は、AとBとが電気的に接続されている場合と、AとBとが機能的に接続されている場合と、AとBとが直接接続されている場合とを含むものとする。ここで、A、Bは、対象物（例えば、装置、素子、回路、配線、電極、端子、導電膜、層、など）であるとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも含むものとする。

10

【0033】

なお第1のノードNAとは、第1の回路101、第2の回路102、及び第1のトランジスタ105に接続されるノードであり、第2のノードNBとは、第1の回路101、第3の回路103、第1のトランジスタ105、第2のトランジスタ106に接続されるノードである。

20

【0034】

第2の回路102は、第1のノードNAに、前段のパルス出力回路の出力信号OUT\_ (N-1) (1段目であれば、スタートパルスSP)に応じた信号を供給するための回路である。また第2の回路102は、前段のパルス出力回路の出力信号OUT\_ (N-1)を、第2のトランジスタ106のゲートに出力するための回路である。

【0035】

第3の回路103は、第2のノードNBに対し、クロック信号の入力等によって得られる所定のタイミングに応じて、間欠的に高電源電位の信号を供給するための回路である。

【0036】

第1のトランジスタ105は、第2のノードNBがゲートに接続され、ドレイン端子が第1のノードNAに接続され、第2のノードNBの電位に応じて、第1のノードNAの電位を制御するためのトランジスタである。

30

【0037】

第2のトランジスタ106は、前段のパルス出力回路の出力信号OUT\_ (N-1)に応じた信号がゲートに供給され、ドレイン端子が第2のノードNBに接続され、第2のノードNBの電位を制御するためのトランジスタである。

【0038】

なお、薄膜トランジスタは、ゲート端子と、ドレイン端子と、ソース端子とを含む少なくとも三つの端子を有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイン領域とチャネル領域とソース領域とを介して電流を流すことが出来る。本明細書においては、高電源電位を供給するための配線側に接続される端子をドレイン端子、低電源電位が供給される配線側に接続される端子をソース端子として説明することとする。なお、ソース端子とドレイン端子を、第1端子、第2端子と表記する場合がある。

40

【0039】

第4の回路104Aは、第1のトランジスタ105のソース端子と、低電源電位を供給する配線110との間に設け、第1のトランジスタ105のソース端子の電位を配線110の電位より昇圧させる回路である。また第4の回路104Bは、第4の回路104Aと同様に、第2のトランジスタ106のソース端子と、低電源電位を供給する配線110との間に設け、第2のトランジスタ106のソース端子の電位を配線110の電位より昇圧さ

50

せる回路である。

#### 【0040】

なお本実施の形態で示す構成において、第4の回路104Aとして第3のトランジスタ108A、第4のトランジスタ109Aを設け、それぞれのトランジスタのゲートとドレイン端子を短絡するように接続している。その結果、第1のトランジスタ105のソース端子、すなわち第3のノードN1の電位を配線110の電位より第3のトランジスタ108Aと第4のトランジスタ109Aとのしきい値電圧の和の分だけ高くすることができる。同様に、第4の回路104Bとして第3のトランジスタ108B、第4のトランジスタ109Bを設け、それぞれのトランジスタのゲートとドレイン端子を短絡するように接続している。その結果、第2のトランジスタ106のソース端子、すなわち第3のノードN2の電位を配線110の電位より第3のトランジスタ108Bと第4のトランジスタ109Bとのしきい値電圧の和の分だけ高くすることができる。なお第4の回路104A及び第4の回路104Bは、いずれか一方を省略してもよいし、さらに複数のトランジスタで冗長化してもよい。10

#### 【0041】

なお、第4の回路104A及び第1のトランジスタ105、並びに第4の回路104B及び第2のトランジスタ106は、第1の回路101を制御するためにフローティング状態とするノードの数に応じて設けられるものである。本実施の形態では一例として、第1のノードNA及び第2のノードNBの2つの構成を示すものである。また本実施の形態では、第4の回路104Aとして第3のトランジスタ108A及び第4のトランジスタ109Aの2つ、並びに第4の回路104Bとして第3のトランジスタ108B及び第4のトランジスタ109Bの2つを配置する構成としたが、更にトランジスタ数を増やして、第3のノードN1、N2の電位を高くするようにする構成としてもよい。また、第4の回路104A、104Bを構成するトランジスタである第3のトランジスタ108A、第4のトランジスタ109A、及び第3のトランジスタ108B、第4のトランジスタ109Bのトランジスタの抵抗値を、さらなるオフ電流の低減のために、第1のトランジスタ105、第2のトランジスタ106よりも高くなるように予めすることが好ましい。20

#### 【0042】

すなわち第4の回路を構成するトランジスタである第3のトランジスタ108A、第4のトランジスタ109A、及び第3のトランジスタ108B、第4のトランジスタ109BのトランジスタのL/W比を、第1のトランジスタ105、第2のトランジスタ106のL/W比より大きくすることが好ましい。また、第4の回路を構成するトランジスタである第3のトランジスタ108A、第4のトランジスタ109A、及び第3のトランジスタ108B、第4のトランジスタ109Bの半導体層の膜厚を、第1のトランジスタ105、第2のトランジスタ106の半導体層の膜厚より小さくすることが好ましい。なおゲート長Lはトランジスタのゲートと半導体層が重なる領域でのソース、ドレイン間の長さに相当し、ゲート幅Wはトランジスタのゲートと半導体層が重なる領域でのソース、ドレイン間の幅に相当する。従って、L/W比は、ゲート長とゲート幅の比に相当する。30

#### 【0043】

スイッチ107Aは、第1のトランジスタ105のソース端子、すなわち第3のノードN1を低電源電位が供給される配線110と短絡するための回路である。スイッチ107Bは、第1のトランジスタ105のソース端子及び第2のトランジスタ106のソース端子、すなわち第3のノードN2を低電源電位が供給される配線110と短絡するための回路である。なおスイッチ107A、107Bとしては、第1乃至第4のトランジスタと同様に作製されるトランジスタで形成すればよい。また、スイッチ107A、107Bのオンまたはオフは、外部に設けられた判定回路111により供給される判定信号により制御される。なおスイッチ107A、107Bをトランジスタで作製する場合には、判定回路111からの信号は当該トランジスタを確実にオン又はオフできる電位の信号であることが好ましい。なお、スイッチ107A、Bと同様の機能を有するスイッチをさらに複数設ける構成としてもよい。40

## 【0044】

すなわち第1のトランジスタ105及び第2のトランジスタ106がノーマリーオンの場合には、第4の回路104A、104Bにより第3のノードN1、N2を低電源電位Vssより高くして、第1のトランジスタ105及び第2のトランジスタ106を電流が流れにくくし、ノーマリーオフのときにはスイッチ107A、107Bを短絡させて第3のノードN1、N2の電位を低電源電位に下げることで第1のトランジスタ105及び第2のトランジスタ106を電流が流れやすくし、ノーマリーオンでもノーマリーオフでも問題なく動作させることができるものとなる。なお、スイッチ107A、107Bをトランジスタで構成する場合には、ノーマリーオンであると動作が不安定になるので、外部回路である判定回路111よりスイッチ107A、107Bとなるトランジスタのゲートに十分な電圧レベルの信号を印加する構成とすることが好ましい。

10

## 【0045】

次いで判定回路111の構成例について図2を用いて説明する。

## 【0046】

判定回路111は、定電流源201、トランジスタ202、コンパレータ203（比較回路ともいう）、バッファ回路204を有する。なお、定電流源201と、トランジスタ202、及びコンパレータ203が接続されるノードを、説明のため、ノードNEと呼ぶことにする。

## 【0047】

図2において、定電流源201は一方の端子が高電源電位Vddを供給する配線に接続され、他方の端子がノードNEに接続される。トランジスタ202はドレイン端子がノードNEに接続され、ゲート及びソース端子が低電源電位Vssを供給する配線に接続される。コンパレータ203は、入力端子がノードNEに接続され、出力端子がバッファ回路204の入力端子に接続される。バッファ回路204の出力端子は、スイッチ107A、107Bとなるトランジスタのゲートに接続される。

20

## 【0048】

なお、バッファ回路204は、トランジスタでなるスイッチ107A、107Bまでの距離が長い場合に、各段のパルス出力回路に入力するための信号の電荷供給能力を高めるために設けるものであり、省略してもよい。

## 【0049】

判定回路111ではトランジスタ202が、駆動回路を構成するトランジスタのノーマリーオンまたはノーマリーオフを判定するためのトランジスタであり、同一基板上に同じ条件で作製され、同じトランジスタ特性を有するものである。そして定電流源201より流れる電流がトランジスタ202を流れる際、トランジスタ202がノーマリーオンまたはノーマリーオフによって、ノードNEの電位の高低を判定することで、スイッチ107A、107Bのオン又はオフを制御するものである。なお、トランジスタ202がノーマリーオンとなるときには、トランジスタ202がノーマリーオフとなるときより、ノードNEの電位が低くなる。なおコンパレータ203では予め設定された参照電位（一例としては、高電源電位Vddと低電源電位Vssとの中間電位）とノードNEの電位を比較し、ノーマリーオフのときには、高電源電位の信号を出力し、ノーマリーオンのときには低電源電位の信号を出力する。そしてバッファ回路204で、トランジスタでなるスイッチ107A、107Bのオン又はオフを十分制御できる電圧の信号（判定信号）となる。

30

## 【0050】

なお、駆動回路を構成するトランジスタがノーマリーオンであるかノーマリーオフであるかは、作製工程が同じであっても基板毎にばらつきが生じることもあり得る。そのため、本実施の形態の構成によって、ノーマリーオンであるかノーマリーオフであるかを表示装置となる基板毎に判定し、補正することのできる構成により、駆動回路での歩留まりの向上を図ることができる。

## 【0051】

なおコンパレータ203で比較する参照電位は、ノーマリーオンとなる際のノードNEの

40

50

電位の上昇、及びノーマリーオフとなる際のノードN Eの電位の低下を予めモニターしておき、適宜設定される電位であってもよい。

【0052】

次いで、第1の回路101、第2の回路102、及び第3の回路103の一例について、図3を用いて説明する。

【0053】

図3(A)に示す第1の回路101の一例としては、図11(A)と同様に、トランジスタ301、トランジスタ302を設ける。そしてトランジスタ301のゲートを第1のノードN Aに接続し、トランジスタ302のゲートを第2のノードN Bに接続し、トランジスタ301のドレイン端子をクロック信号CK1(第1のクロック信号ともいう)が供給される配線に接続し、トランジスタ301のソース端子とトランジスタ302のドレイン端子とを接続して出力信号OUT\_Nを出力する端子とし、トランジスタ302のソース端子を低電源電位Vssを供給する配線に接続する構成とすればよい。また、トランジスタ301のゲートとソースの間に必要に応じて、容量素子303を設ける構成としてもよい。容量素子を設けることで、第1のノードがフローティング状態となった際に、ゲートとソースの間でのブートストラップが起こりやすくなり好適である。

10

【0054】

次いで図3(B)に示す第2の回路102の一例としては、図11(A)と同様に、トランジスタ304を設ける。そして、トランジスタ304のゲートとドレイン端子、及び第2のトランジスタ106のゲートが接続される端子を前段のパルス出力回路の出力信号OUT\_(N-1)が入力される端子に接続し、トランジスタ304のソース端子を第2のノードN Bに接続する構成とすればよい。また図3(B)とは異なる第2の回路102の別の構成としては、図3(C)に示すトランジスタ305を設ける構成がある。そして、トランジスタ305のドレイン端子を高電源電位Vddが供給される配線に接続し、トランジスタ305のゲート及び第2のトランジスタ106のゲートが接続される端子を前段のパルス出力回路の出力信号OUT\_(N-1)が入力される端子に接続し、トランジスタ305のソース端子を第2のノードN Bに接続する構成とすればよい。

20

【0055】

次いで図3(D)に示す第3の回路103の一例としては、図11(A)と同様に、トランジスタ306を設ける。トランジスタ306のゲート及びドレイン端子をクロック信号CK2(第2のクロック信号ともいう)が供給される配線に接続し、トランジスタ306のソース端子を第2のノードN Bに接続する構成とする。なお図3(D)でのクロック信号CK2は、図3(A)でのクロック信号CK1の反転信号であることが好ましい。また図3(D)とは異なる第3の回路103の別の構成としては、図3(E)に示すトランジスタ307及びトランジスタ308がある。トランジスタ307のゲートをクロック信号CK2(第2のクロック信号ともいう)が供給される配線に接続し、トランジスタ307のドレイン端子を高電源電位Vddが供給される配線に接続し、トランジスタ307のソース端子とトランジスタ308のドレイン端子とを接続し、トランジスタ308のゲートをクロック信号CK3(第3のクロック信号ともいう)が供給される配線に接続され、トランジスタ308のソース端子が第2のノードN Bに接続される構成とする。なお、図3(D)でのクロック信号CK2は、図3(A)でのクロック信号CK1が1/4周期分遅延した信号であり、図3(E)でのクロック信号CK3は、図3(E)でのクロック信号CK2が1/4周期分遅延した信号であることが好ましい。

30

【0056】

また図1に示す構成は、第1の回路101、第2の回路102、及び第3の回路103の他にも、別途回路を設ける構成としてもよい。例えば、図3(F)に示すトランジスタ309を有する回路を図1に示す第2のノードN Bに接続して設ける。図3(F)に示すトランジスタ309は、ドレイン端子を高電源電位Vddが供給される端子に接続し、ゲートをパルス出力回路で2段後段の出力信号OUT\_(N+2)が入力される端子に接続し、ソース端子を第2のノードN Bに接続する構成とすればよい。図3(F)に示す回路を

40

50

追加して設ける構成とすることで第2のノードNBの電位をより確実に制御することができるため好適である。

【0057】

なお第1の回路101、第2の回路102、及び第3の回路103をそれぞれ複数個設ける構成とすることも可能である。

【0058】

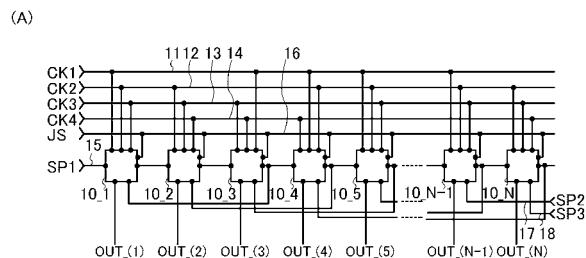

次いで、複数段のパルス出力回路を具備する駆動回路であるシフトレジスタの構成について図4に示し、本実施形態で示す構成の効果等について詳述していく。なお、図4は、図1における第1の回路101として図3(A)の回路とし、図1における第2の回路102として図3(C)の回路とし、図1における第3の回路103として図3(E)の回路とし、第2のノードNBに図3(F)の回路を設ける構成について具体的に示した回路である。なお図4では第1の回路101を複数設ける例について説明するものである。

10

【0059】

図4(A)に示すシフトレジスタは、第1のパルス出力回路10\_1乃至第Nのパルス出力回路10\_N(N=3の自然数)を有している。図4(A)に示すシフトレジスタの第1のパルス出力回路10\_1乃至第Nのパルス出力回路10\_Nには、第1の配線11より第1のクロック信号CK1、第2の配線12より第2のクロック信号CK2、第3の配線13より第3のクロック信号CK3、第4の配線14より第4のクロック信号CK4が供給される。また第1のパルス出力回路10\_1では、第5の配線15からのスタートパルスSP1(第1のスタートパルス)が入力される。また2段目以降の第nのパルス出力回路10\_n(nは、2~Nの自然数)では、一段前段のパルス出力回路からの信号(前段信号OUT(n-1))が入力される。また第1のパルス出力回路10\_1では、2段後段の第3のパルス出力回路10\_3からの信号が入力される。同様に、2段目以降の第nのパルス出力回路10\_nでは、2段後段の第(n+2)のパルス出力回路10\_(n+2)からの信号(後段信号OUT(n+2))が入力される。従って、各段のパルス出力回路からは、後段及び/または二つ前段のパルス出力回路に入力するための第1の出力信号OUT(1)(SR)~OUT(N)(SR)、別の回路等に入力される第2の出力信号OUT(1)~OUT(N)が出力される。また各段のパルス出力回路には、第6の配線16より、判定回路111からの判定信号JSが供給される。ただし、図4(A)に示すように、シフトレジスタの最終段の2つの段には、後段信号OUT(n+2)が入力されないため、一例としては、別途第7の配線17より第2のスタートパルスSP2、第8の配線18より第3のスタートパルスSP3をそれぞれ入力する構成でもよい。または別途、内部で生成された信号であってもよい。例えば、表示部へのパルス出力に寄与しない第(n+1)のパルス出力回路10\_(n+1)、第(n+2)のパルス出力回路10\_(n+2)を設け(ダミー段ともいう)、当該ダミー段より第2のスタートパルス(SP2)及び第3のスタートパルス(SP3)に相当する信号を生成する構成としてもよい。

20

【0060】

なお、第1のクロック信号(CK1)~第4のクロック信号(CK4)は、一定の間隔でH信号とL信号を繰り返す信号である。また、第1のクロック信号(CK1)~第4のクロック信号(CK4)は、順に1/4周期分遅延している(すなわち、互いに90°位相がずれている)。本実施の形態では、第1のクロック信号(CK1)~第4のクロック信号(CK4)を利用して、パルス出力回路の駆動の制御等を行う。なお、クロック信号は、入力される駆動回路に応じて、GCK、SCKということもあるが、ここではCKとして説明を行う。

30

【0061】

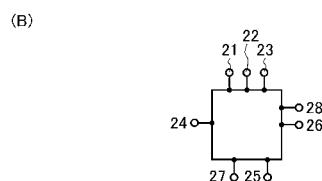

第1のパルス出力回路10\_1~第Nのパルス出力回路10\_Nの各々は、第1の入力端子2\_1、第2の入力端子2\_2、第3の入力端子2\_3、第4の入力端子2\_4、第5の入力端子2\_5、第1の出力端子2\_6、第2の出力端子2\_7、第6の入力端子2\_8を有している(図4(B)参照)。

40

50

## 【0062】

図4(B)に図4(A)で示したパルス出力回路10\_nの一つを示す。第1の入力端子21、第2の入力端子22及び第3の入力端子23は、第1の配線11～第4の配線14のいずれかと電気的に接続されている。例えば、図4(A)、(B)において、第1のパルス出力回路10\_1は、第1の入力端子21が第1の配線11と電気的に接続され、第2の入力端子22が第2の配線12と電気的に接続され、第3の入力端子23が第3の配線13と電気的に接続されている。また、第2のパルス出力回路10\_2は、第1の入力端子21が第2の配線12と電気的に接続され、第2の入力端子22が第3の配線13と電気的に接続され、第3の入力端子23が第4の配線14と電気的に接続されている。

## 【0063】

また図4(A)、(B)において、第1のパルス出力回路10\_1は、第4の入力端子24にスタートパルスが入力され、第5の入力端子25に後段信号OUT(3)が入力され、第1の出力端子26より第1の出力信号OUT(1)(SR)が出力され、第2の出力端子27より第2の出力信号OUT(1)が出力され、第6の入力端子28より判定信号JSが入力されていることとなる。

## 【0064】

次に、パルス出力回路の具体的な回路構成の一例について、図4(C)で説明する。

## 【0065】

第1のパルス出力回路10\_1は、図1と同様に、第1の回路101A及び101B、第2の回路102、第3の回路103、第4の回路104A及び104B、第1のトランジスタ105、第2のトランジスタ106、トランジスタであるスイッチ107A及び107Bを有している。また、図1の構成に加えて第2のノードNBに接続されるトランジスタ401を有する。トランジスタ401は後段信号OUT(n+2)がH信号となるタイミングに応じて、第2のノードNBの電位を上昇させるためのトランジスタである。また、図1の構成に加えて第1のノードNAにおいて、トランジスタ402を挿入し、ゲートを高電源電位Vddが供給される配線に接続する構成としてもよい。トランジスタ402を第1のノードNAに挿入することによって、第1の回路101Aでのトランジスタのゲートが、フローティング状態となりやすくなるため好適である。ここで第1のクロック信号(CK1)～第4のクロック信号(CK4)は、一定の間隔でHレベルとLレベルを繰り返す信号であるが、HレベルのときVdd、LレベルのときVssであるとする。

## 【0066】

図4(C)におけるパルス出力回路が第1のパルス出力回路10\_1の場合、第1の入力端子21には第1のクロック信号CK1が入力され、第2の入力端子22には第2のクロック信号CK2が入力され、第3の入力端子23には第3のクロック信号CK3が入力され、第4の入力端子24にはスタートパルスSPが入力され、第5の入力端子25には後段信号OUT(3)が入力され、第1の出力端子26からは第1の出力信号OUT(1)(SR)が出力され、第2の出力端子27からは第2の出力信号OUT(1)が出力され、第6の入力端子28からは判定信号JSが入力される。

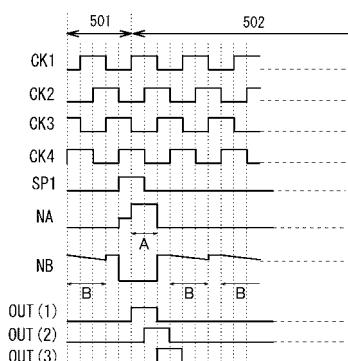

## 【0067】

ここで、図4(C)に示したパルス出力回路を複数具備するシフトレジスタのタイミングチャートについて図5に示す。なおシフトレジスタが走査線駆動回路である場合、図5中の期間501は垂直帰線期間であり、期間502はゲート選択期間に相当する。

## 【0068】

図4(C)中のノードNAでは、出力信号OUT\_(N)をH信号にするために、定期的に、電気的にフローティング状態(浮遊状態)及び所定の電位が入力される状態がある。図5中のNAで矢印A区間の期間がフローティング状態の期間であり、フローティング状態となる際にリーク電流による電位の低下が問題となる期間である。同様に、図5中のノードNBで矢印B区間の期間がフローティング状態の期間であり、フローティング状態となる際にリーク電流による電位の低下が問題となる期間である。具体的にいえば、フロー

10

20

30

40

50

ティング状態となる矢印 A 区間、及び矢印 B 区間での電位低下の度合いが、トランジスタがノーマリーオンまたはノーマリーオフかによって変化することが問題である。一方で、単にノーマリーオンまたはノーマリーオフの状態を補正する回路を付加するだけでは、ノーマリーオンまたはノーマリーオフの各状態が基板間でばらつく場合に、対策として不十分である。

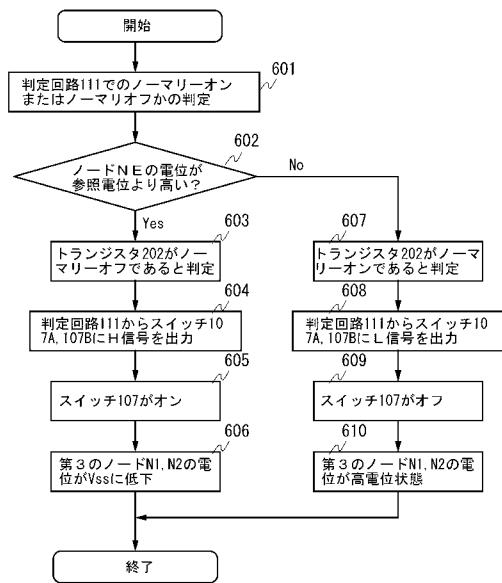

#### 【 0 0 6 9 】

次に、図 6 に図 1 で示したパルス出力回路の動作について説明する。そしてノーマリーオンまたはノーマリーオフの各状態が基板間でばらつく場合に、いずれの状態であっても正確な動作を補償できる図 1 のパルス出力回路を具備する駆動回路での動作による効果について説明する。

10

#### 【 0 0 7 0 】

まず、判定回路 111 で各回路を構成するトランジスタがノーマリーオンかノーマリーオフかの指標として、トランジスタ 202 がノーマリーオンかノーマリーオフの判定を行い、第 4 の回路 104A、104B による第 3 のノード N1、N2 の電位の上昇を行うか否かを判定する（図 6、ステップ 601）。

#### 【 0 0 7 1 】

次いで、図 2 に示す判定回路 111 は、ノード N E の電位が参照電位よりも高いかどうかの判定を行う（図 6、ステップ 602）。トランジスタ 202 に流れる電流が大きく、ノード N E の電位が参照電位よりも高くなる場合、トランジスタ 202 がノーマリーオフであると判定される（図 6、ステップ 603）。

20

#### 【 0 0 7 2 】

次いで、コンパレータ 203 及びバッファ回路 204 を介して判定回路 111 より、スイッチ 107A 及び 107B に H 信号が出力される（図 6、ステップ 604）。スイッチ 107A 及び 107B が n チャネル型のトランジスタの場合には、スイッチ 107A 及び 107B がオン状態となる（図 6、ステップ 605）。その結果、第 3 のノード N1、N2 の電位が配線 110 の電位にあたる低電源電位 Vss に低下する（図 6、ステップ 606）。

#### 【 0 0 7 3 】

また逆に、トランジスタ 202 に流れる電流が小さく、ノード N E の電位が参照電位よりも低くなる場合、トランジスタ 202 がノーマリーオンであると判定される（図 6、ステップ 607）。

30

#### 【 0 0 7 4 】

次いで、コンパレータ 203 及びバッファ回路 204 を介して判定回路 111 より、スイッチ 107A 及び 107B に L 信号が出力される（図 6、ステップ 608）。スイッチ 107A 及び 107B が n チャネル型のトランジスタの場合には、スイッチ 107A 及び 107B がオフ状態となる（図 6、ステップ 609）。その結果、第 3 のノード N1 及び N2 の電位が低電源電位 Vss より高い電位を保持することとなる（図 6、ステップ 610）。

#### 【 0 0 7 5 】

上述の動作によって第 1 のトランジスタ 105 及び第 2 のトランジスタ 106 がノーマリーオンであってもノーマリーオフであってもトランジスタがオン状態またはオフ状態をとるのに十分なゲートとソースの間の電圧 Vgs を得ることのできるパルス出力回路とすることができる。すなわちノーマリーオンのトランジスタの場合にはトランジスタのゲートとソース端子との間にかかる電圧 Vgs を上昇させることで、スイッチング特性の向上を行い、ノーマリーオフのトランジスタの場合にはソース端子の電位を低下させて十分に高い電圧 Vgs を確保することができる。そのため、トランジスタがノーマリーオンであるかノーマリーオフであるかが基板毎にばらついても、より確度が高く誤動作を低減することのできる駆動回路とすることができます。すなわち、薄膜トランジスタの作製条件等に起因するしきい値電圧のばらつきによって、エンハンスメント型、またはディプレッション型のいずれかに変動する駆動回路であっても、回路内の誤動作を低減できる駆動回路を提

40

50

供することができる。

【0076】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0077】

(実施の形態2)

本実施の形態では、上記実施の形態で説明した駆動回路、及び当該駆動回路によって制御される表示部を具備する表示装置の断面図について、図7を用いて説明する。また本実施の形態では、表示装置として液晶表示装置の一例について説明をおこなうが、有機EL素子等の発光素子を具備するEL表示装置、または電気泳動素子を具備する電気泳動表示装置にも適用することが可能である。なお、上記実施の形態で説明した構成は、表示装置の駆動回路に限らず、光センサ用駆動回路等の他の装置にも適用可能である。

10

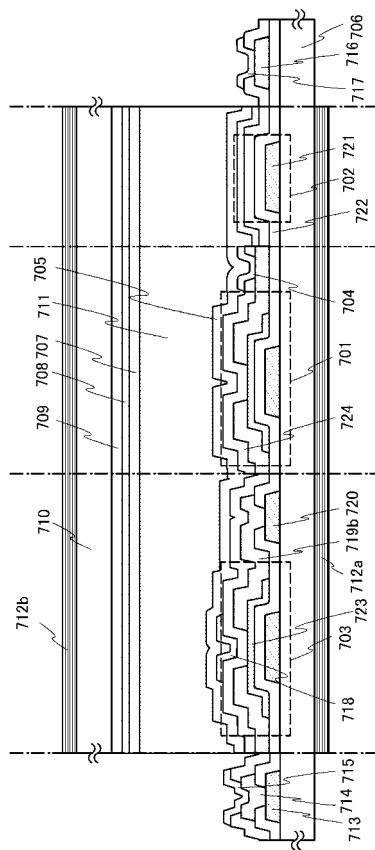

【0078】

本発明の一形態である液晶表示装置を図7に示す。図7の液晶表示装置は、薄膜トランジスタ701及び容量702を含む画素部、及び薄膜トランジスタ703を含む駆動回路部、画素電極層704、配向膜として機能する絶縁層705が設けられた基板706と、配向膜として機能する絶縁層707、対向電極層708、カラーフィルタとして機能する着色層709が設けられた対向基板710とが液晶層711を挟持して対向している。また、基板706及び対向基板710の液晶層711と反対側には、それぞれ偏光板(偏光子を有する層、単に偏光子ともいう)712a、712bが設けられ、ゲート配線の端子部には第1の端子713、接続電極714、及び接続用の端子電極715、ソース配線の端子部には第2の端子716及び接続用の端子電極717が設けられている。

20

【0079】

駆動回路部において、薄膜トランジスタ703はゲート電極層721及びゲート絶縁層722上の半導体層723の上方の酸化物絶縁層724上に導電層718が設けられ、ドレイン電極層719bはゲート電極層と同工程で形成される導電層720と電気的に接続している。また、画素部において、薄膜トランジスタ701のドレイン電極層は画素電極層704と電気的に接続している。

【0080】

酸化物半導体を用いた薄膜トランジスタで形成することにより、製造コストを低減することができる。また酸化物半導体を用いた薄膜トランジスタは電界効果移動度が高く表示装置の画素部及び駆動回路を構成するものとして好適である。一方で、酸化物半導体は外因性の不純物が添加されなくても、酸素が抜けた空孔欠陥によりn型化しやすいという性質がある。酸化物半導体層に接して酸化物絶縁膜を形成することによって、安定した電気特性を有する薄膜トランジスタを得ることができるが、仮に酸化物半導体がn型化してノーマリーオンの薄膜トランジスタが形成された場合でも、本実施の形態の駆動回路を用いることによって、駆動回路を安定に動作させることができる。

30

【0081】

なお、本実施の形態では、酸化物半導体をチャネルに用いる薄膜トランジスタの例について説明したが、実施の形態1で開示する構成は、駆動回路を構成する薄膜トランジスタがノーマリーオンまたはノーマリーオフでも動作することができるものである。従って、例えば、非晶質シリコンを用いた薄膜トランジスタの半導体層において、意図的または非意図的にn型の導電性を付与する不純物が含まれることによってノーマリーオンとして動作するトランジスタにも、用いることができる。また、チャネル領域を形成する半導体層のゲート絶縁膜とは反対側(バックチャネル側)に電荷が蓄積されることによって寄生チャネルが形成され、ノーマリーオンとして動作するトランジスタにおいても適用可能である。

40

【0082】

半導体層のチャネル形成領域は高抵抗化領域であるので、薄膜トランジスタの電気特性は安定化し、オフ電流の増加などを防止することができる。よって、電気特性が良好で信頼

50

性のよい薄膜トランジスタを有する半導体装置とすることが可能となる。

【0083】

また、薄膜トランジスタは静電気などにより破壊されやすいため、画素部または駆動回路と同一基板上に保護回路を設けることが好ましい。保護回路は、酸化物半導体層を用いた非線形素子を用いて構成することが好ましい。例えば、保護回路は画素部と、走査線入力端子及び信号線入力端子との間に配設されている。本実施の形態では複数の保護回路を配設して、走査線、信号線及び容量バス線に静電気等によりサージ電圧が印加され、画素トランジスタなどが破壊されないように構成されている。そのため、保護回路にはサージ電圧が印加されたときに、共通配線に電荷を逃がすように構成する。また、保護回路は、走査線に対して並列に配置された非線形素子によって構成されている。非線形素子は、ダイオードのような二端子素子又はトランジスタのような三端子素子で構成される。例えば、画素部の薄膜トランジスタ701と同じ工程で形成することも可能であり、例えばゲート端子とドレイン端子を接続することによりダイオードと同様の特性を持たせることができる。10

【0084】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【0085】

(実施の形態3)

本実施の形態では、同一基板上に少なくとも駆動回路の一部と、画素部に配置する薄膜トランジスタを作製する例について以下に説明する。なお基板上に配置する薄膜トランジスタは、実施の形態2の断面図に示すよう形成すればよい。20

【0086】

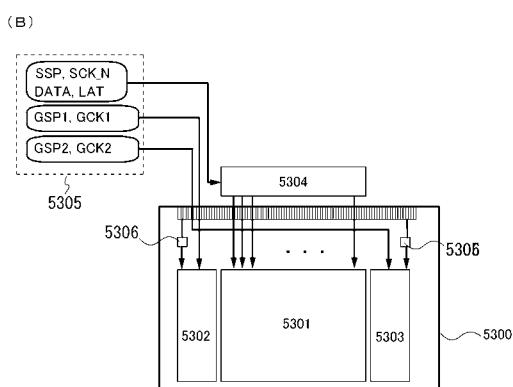

アクティブマトリクス型表示装置のブロック図の一例を図8(A)に示す。表示装置の基板5300上には、画素部5301、第1の走査線駆動回路5302、第2の走査線駆動回路5303、信号線駆動回路5304、判定回路5306を有する。画素部5301には、複数の信号線が信号線駆動回路5304から延伸して配置され、複数の走査線が第1の走査線駆動回路5302、及び第2の走査線駆動回路5303から延伸して配置されている。なお走査線と信号線との交差領域には、各々、表示素子を有する画素がマトリクス状に配置されている。また、表示装置の基板5300はFPC(Flexible Printed Circuit)等の接続部を介して、タイミング制御回路5305(コントローラ、制御ICともいう)に接続されている。30

【0087】

図8(A)では、第1の走査線駆動回路5302、第2の走査線駆動回路5303、信号線駆動回路5304、判定回路5306は、画素部5301と同じ基板5300上に形成される。そのため、外部に設ける駆動回路等の部品の数が減るので、コストの低減を図ることができる。また、基板5300外部に駆動回路を設けた場合の配線を延伸させることによる接続部での接続数を減らすことができ、信頼性の向上、又は歩留まりの向上を図ることができる。なお判定回路5306は、基板上に複数設けられていてもよく、一例としては駆動回路毎に設けられる構成とすればよい。40

【0088】

なお、タイミング制御回路5305は、第1の走査線駆動回路5302に対し、一例として、第1の走査線駆動回路用スタート信号(GSP1)(スタートパルスともいう)、走査線駆動回路用クロック信号(GCK1)を供給する。また、タイミング制御回路5305は、第2の走査線駆動回路5303に対し、一例として、第2の走査線駆動回路用スタート信号(GSP2)、走査線駆動回路用クロック信号(GCK2)を供給する。信号線駆動回路5304に、信号線駆動回路用スタート信号(SSP)、信号線駆動回路用クロック信号(SCK)、ビデオ信号用データ(DATA)(単にビデオ信号ともいう)、ラッピング信号(LAT)を供給するものとする。なお各クロック信号は、周期のずれた複数のクロック信号でもよいし、クロック信号を反転させた信号(CKB)とともに供給される50

ものであってもよい。なお、第1の走査線駆動回路5302と第2の走査線駆動回路5303との一方を省略することが可能である。

【0089】

図8(B)では、判定回路5306及び第1の走査線駆動回路5302と第2の走査線駆動回路5303を画素部5301と同じ基板5300に形成し、信号線駆動回路5304を画素部5301とは別の基板に形成する構成について示している。

【0090】

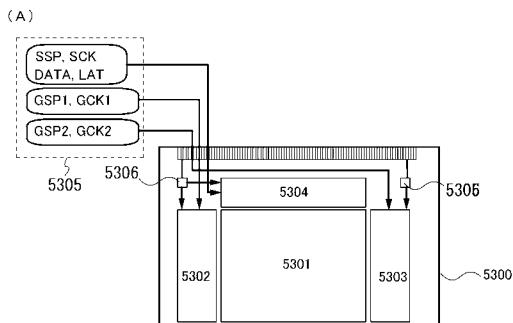

また、実施の形態1及び実施の形態2に示す薄膜トランジスタは、nチャネル型TFTである。図9(A)、図9(B)ではnチャネル型TFTで構成する信号線駆動回路の構成、動作について一例を示し説明する。

10

【0091】

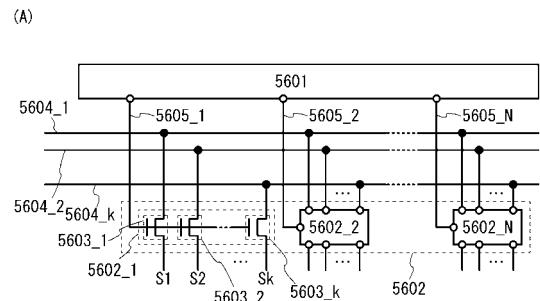

信号線駆動回路は、シフトレジスタ5601、及びスイッチング回路5602を有する。スイッチング回路5602は、スイッチング回路5602\_1～5602\_N(Nは自然数)という複数の回路を有する。スイッチング回路5602\_1～5602\_Nは、各々、薄膜トランジスタ5603\_1～5603\_k(kは自然数)という複数のトランジスタを有する。薄膜トランジスタ5603\_1～5603\_kは、Nチャネル型TFTである例を説明する。

【0092】

信号線駆動回路の接続関係について、スイッチング回路5602\_1を例にして説明する。薄膜トランジスタ5603\_1～5603\_kの第1端子は、各々、配線5604\_1～5604\_kと接続される。薄膜トランジスタ5603\_1～5603\_kの第2端子は、各々、信号線S1～Skと接続される。薄膜トランジスタ5603\_1～5603\_kのゲートは、配線5605\_1と接続される。

20

【0093】

シフトレジスタ5601は、配線5605\_1～5605\_Nに順番にHレベル(H信号、高電源電位レベル、ともいう)の信号を出力し、スイッチング回路5602\_1～5602\_Nを順番に選択する機能を有する。

【0094】

スイッチング回路5602\_1は、配線5604\_1と信号線S1との導通状態(第1端子と第2端子との間の導通)を制御する機能、即ち配線5604\_1の電位を信号線S1に供給するか否かを制御する機能を有する。このように、スイッチング回路5602\_1は、セレクタとしての機能を有する。同様に、薄膜トランジスタ5603\_2～5603\_kは、各々、配線5604\_2～5604\_kと信号線S2～Skとの導通状態を制御する機能、即ち配線5602\_1～5604\_kの電位を信号線S2～Skに供給する機能を有する。このように、薄膜トランジスタ5603\_1～5603\_kは、各々、スイッチとしての機能を有する。

30

【0095】

なお、配線5604\_1～5604\_kには、各々、ビデオ信号用データ(DATA)が入力される。ビデオ信号用データ(DATA)は、画像情報又は画像信号に応じたアナログ信号である場合が多い。

40

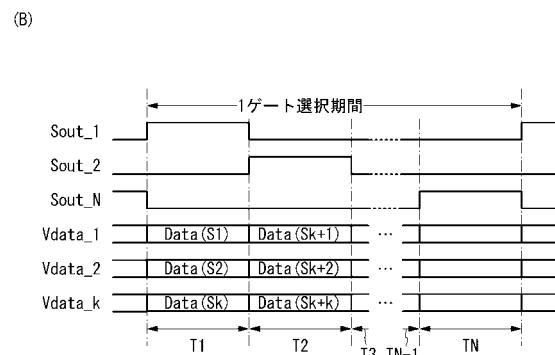

【0096】

次に、図9(A)の信号線駆動回路の動作について、図9(B)のタイミングチャートを参照して説明する。図9(B)には、信号Sout\_1～Sout\_N、及び信号Vdata\_1～Vdata\_kの一例を示す。信号Sout\_1～Sout\_Nは、各々、シフトレジスタ5601の出力信号の一例であり、信号Vdata\_1～Vdata\_kは、各々、配線5604\_1～5604\_kに入力される信号の一例である。なお、信号線駆動回路の1動作期間は、表示装置における1ゲート選択期間に対応する。1ゲート選択期間は、一例として、期間T1～期間TNに分割される。期間T1～TNは、各々、選択された行に属する画素にビデオ信号用データ(DATA)を書き込むための期間である。

【0097】

50

期間 T 1 ~ 期間 T N において、シフトレジスタ 5601 は、H レベルの信号を配線 5605\_1 ~ 5605\_N に順番に出力する。例えば、期間 T 1 において、シフトレジスタ 5601 は、ハイレベルの信号を配線 5605\_1 に出力する。すると、薄膜トランジスタ 5603\_1 ~ 5603\_k はオンになるので、配線 5604\_1 ~ 5604\_k と、信号線 S 1 ~ S k とが導通状態になる。このとき、配線 5604\_1 ~ 5604\_k には、Data(S1) ~ Data(Sk) が入力される。Data(S1) ~ Data(Sk) は、各々、薄膜トランジスタ 5603\_1 ~ 5603\_k を介して、選択される行に属する画素のうち、1 列目 ~ k 列目の画素に書き込まれる。こうして、期間 T 1 ~ T N において、選択された行に属する画素に、k 列ずつ順番にビデオ信号用データ (DATA) が書き込まれる。

10

#### 【0098】

以上のように、ビデオ信号用データ (DATA) が複数の列ずつ画素に書き込まれることによって、ビデオ信号用データ (DATA) の数、又は配線の数を減らすことができる。よって、外部回路との接続数を減らすことができる。また、ビデオ信号が複数の列ずつ画素に書き込まれることによって、書き込み時間を長くすることができ、ビデオ信号の書き込み不足を防止することができる。

#### 【0099】

なお、走査線駆動回路の構成について説明する。走査線駆動回路は、シフトレジスタを有している。また場合によってはレベルシフタやバッファ等を有していても良い。走査線駆動回路において、シフトレジスタにクロック信号 (CK) 及びスタートパルス信号 (SP) が入力されることによって、選択信号が生成される。生成された選択信号はバッファにおいて緩衝増幅され、対応する走査線に供給される。走査線には、1 ライン分の画素のトランジスタのゲート電極が接続されている。そして、1 ライン分の画素のトランジスタを一斉に ON にしなくてはならないので、バッファは大きな電流を流すことが可能なものが用いられる。

20

#### 【0100】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することができる。

#### 【0101】

##### (実施の形態 4)

30

本実施形態においては、上記実施の形態で説明した表示装置を表示部に具備する電子機器の例について説明する。

#### 【0102】

上記実施の形態の各々の図で述べた内容（一部でもよい）を様々な電子機器に適用することができる。具体的には、電子機器の表示部に適用することができる。そのような電子機器として、ビデオカメラ、デジタルカメラなどのカメラ、ゴーグル型ディスプレイ、ナビゲーションシステム、音響再生装置（カーオーディオ、オーディオコンポ等）、コンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話、携帯型ゲーム機又は電子書籍等）、記録媒体を備えた画像再生装置（具体的には Digital Versatile Disc (DVD) 等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。

40

#### 【0103】

図 10 (A) はディスプレイであり、筐体 1011、支持台 1012、表示部 1013 を含む。図 10 (A) に示すディスプレイは、様々な情報（静止画、動画、テキスト画像など）を表示部に表示する機能を有する。なお、図 10 (A) に示すディスプレイが有する機能はこれに限定されず、様々な機能を有することができる。

#### 【0104】

図 10 (B) はカメラであり、本体 1031、表示部 1032、受像部 1033、操作キー 1034、外部接続ポート 1035、シャッターボタン 1036 を含む。図 10 (B) に示すカメラは、静止画を撮影する機能を有する。動画を撮影する機能を有する。なお、

50

図10( B )に示すカメラが有する機能はこれに限定されず、様々な機能を有することができる。

【0105】

図10( C )はコンピュータであり、本体1051、筐体1052、表示部1053、キー ボード1054、外部接続ポート1055、ポインティングデバイス1056を含む。

図10( C )に示すコンピュータは、様々な情報(静止画、動画、テキスト画像など)を表示部に表示する機能を有する。なお、図10( C )に示すコンピュータが有する機能はこれに限定されず、様々な機能を有することができる。

【0106】

本実施形態の表示部に上記実施の形態で説明した表示装置を用いる構成とすることで、上述の図10( A )乃至図10( C )の表示部を構成する画素に接続される信号線及び電源線の数を削減することができる。そして信号線に接続された信号線駆動回路において、駆動回路の素子数を削減することができ、低コスト化を図ることができ、表示部での高精細な表示を行うことができる。

【0107】

本実施の形態は、他の実施の形態に記載した構成と適宜組み合わせて実施することが可能である。

【符号の説明】

【0108】

|      |           |    |

|------|-----------|----|

| 10   | パルス出力回路   | 20 |

| 11   | 配線        |    |

| 12   | 配線        |    |

| 13   | 配線        |    |

| 14   | 配線        |    |

| 15   | 配線        |    |

| 16   | 配線        |    |

| 17   | 配線        |    |

| 18   | 配線        |    |

| 21   | 入力端子      |    |

| 22   | 入力端子      | 30 |

| 23   | 入力端子      |    |

| 24   | 入力端子      |    |

| 25   | 入力端子      |    |

| 26   | 出力端子      |    |

| 27   | 出力端子      |    |

| 28   | 入力端子      |    |

| 100  | パルス出力回路   |    |

| 101  | 第1の回路     |    |

| 102  | 第2の回路     |    |

| 103  | 第3の回路     | 40 |

| 105  | 第1のトランジスタ |    |

| 104A | 第4の回路     |    |

| 104B | 第4の回路     |    |

| 106  | 第2のトランジスタ |    |

| 107A | スイッチ      |    |

| 107B | スイッチ      |    |

| 110  | 配線        |    |

| 111  | 判定回路      |    |

| 201  | 定電流源      |    |

| 202  | トランジスタ    | 50 |

|         |          |    |

|---------|----------|----|

| 2 0 3   | コンパレータ   |    |

| 2 0 4   | バッファ回路   |    |

| 3 0 1   | トランジスタ   |    |

| 3 0 2   | トランジスタ   |    |

| 3 0 3   | 容量素子     |    |

| 3 0 4   | トランジスタ   | 10 |

| 3 0 5   | トランジスタ   |    |

| 3 0 6   | トランジスタ   |    |

| 3 0 7   | トランジスタ   |    |

| 3 0 8   | トランジスタ   |    |

| 3 0 9   | トランジスタ   |    |

| 4 0 1   | トランジスタ   |    |

| 4 0 2   | トランジスタ   |    |

| 5 0 1   | 期間       |    |

| 5 0 2   | 期間       |    |

| 6 0 1   | ステップ     |    |

| 6 0 2   | ステップ     |    |

| 6 0 3   | ステップ     |    |

| 6 0 4   | ステップ     |    |

| 6 0 5   | ステップ     | 20 |

| 6 0 6   | ステップ     |    |

| 6 0 7   | ステップ     |    |

| 6 0 8   | ステップ     |    |

| 6 0 9   | ステップ     |    |

| 6 1 0   | ステップ     |    |

| 7 0 1   | 薄膜トランジスタ |    |

| 7 0 2   | 容量       |    |

| 7 0 3   | 薄膜トランジスタ |    |

| 7 0 4   | 画素電極層    |    |

| 7 0 5   | 絶縁層      | 30 |

| 7 0 6   | 基板       |    |

| 7 0 7   | 絶縁層      |    |

| 7 0 8   | 対向電極層    |    |

| 7 0 9   | 着色層      |    |

| 7 1 0   | 対向基板     |    |

| 7 1 1   | 液晶層      |    |

| 7 1 2 a | 偏光板      |    |

| 7 1 2 b | 偏光板      |    |

| 7 1 3   | 端子       |    |

| 7 1 4   | 接続電極     | 40 |

| 7 1 5   | 端子電極     |    |

| 7 1 6   | 端子       |    |

| 7 1 7   | 端子電極     |    |

| 7 1 8   | 導電層      |    |

| 7 1 9 b | ドレイン電極層  |    |

| 7 2 0   | 導電層      |    |

| 7 2 1   | ゲート電極層   |    |

| 7 2 2   | ゲート絶縁層   |    |

| 7 2 3   | 半導体層     |    |

| 7 2 4   | 酸化物絶縁層   | 50 |

|         |             |    |

|---------|-------------|----|

| 1 0 1 1 | 筐体          |    |

| 1 0 1 2 | 支持台         |    |

| 1 0 1 3 | 表示部         |    |

| 1 0 1 A | 第1の回路       |    |

| 1 0 1 B | 第1の回路       |    |

| 1 0 3 1 | 本体          |    |

| 1 0 3 2 | 表示部         |    |

| 1 0 3 3 | 受像部         |    |

| 1 0 3 4 | 操作キー        |    |

| 1 0 3 5 | 外部接続ポート     | 10 |

| 1 0 3 6 | シャッター ボタン   |    |

| 1 0 5 1 | 本体          |    |

| 1 0 5 2 | 筐体          |    |

| 1 0 5 3 | 表示部         |    |

| 1 0 5 4 | キー ボード      |    |

| 1 0 5 5 | 外部接続ポート     |    |

| 1 0 5 6 | ポインティングデバイス |    |

| 1 0 8 A | 第3のトランジスタ   |    |

| 1 0 8 B | 第3のトランジスタ   |    |

| 1 0 9 A | 第4のトランジスタ   | 20 |

| 1 0 9 B | 第4のトランジスタ   |    |

| 4 0 4 B | 回路          |    |

| 5 3 0 0 | 基板          |    |

| 5 3 0 1 | 画素部         |    |

| 5 3 0 2 | 走査線駆動回路     |    |

| 5 3 0 3 | 走査線駆動回路     |    |

| 5 3 0 4 | 信号線駆動回路     |    |

| 5 3 0 5 | タイミング制御回路   |    |

| 5 3 0 6 | 判定回路        |    |

| 5 6 0 1 | シフトレジスタ     | 30 |

| 5 6 0 2 | スイッチング回路    |    |

| 5 6 0 3 | 薄膜トランジスタ    |    |

| 5 6 0 4 | 配線          |    |

| 5 6 0 5 | 配線          |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

(B)

(C)

【図11】

(B)

---

フロントページの続き

(51)Int.Cl.

F I

G 09 G 3/20 670 E

G 09 G 3/36

(56)参考文献 特開2005-251348 (JP, A)

特開平9-116408 (JP, A)

特開平8-6653 (JP, A)

特開2011-120221 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 11 C 19 / 28