## (12)发明专利

(10)授权公告号 CN 105551932 B

(45)授权公告日 2019.04.09

(21)申请号 201510896742.1

(74)专利代理机构 北京集佳知识产权代理有限

(22)申请日 2010.09.28

公司 11227

(65)同一申请的已公布的文献号

代理人 丁永凡 张春水

申请公布号 CN 105551932 A

(51)Int.Cl.

(43)申请公布日 2016.05.04

H01L 21/02(2006.01)

(30)优先权数据

H01L 33/00(2010.01)

102009047881.7 2009.09.30 DE

(56)对比文件

(62)分案原申请数据

DE 10151092 A1, 2003.05.08,

201080044047.8 2010.09.28

CN 1203285 A, 1998.12.30,

(73)专利权人 欧司朗光电半导体有限公司

CN 101427391 A, 2009.05.06,

地址 德国雷根斯堡

DE 10151092 A1, 2003.05.08,

审查员 赵凤瑗

(72)发明人 彼得·施陶斯

菲利普·德雷克塞尔

权利要求书2页 说明书6页 附图4页

## (54)发明名称

用于制造层结构的方法

## (57)摘要

本发明涉及用于制造层结构的方法，具有下述步骤：提供具有硅表面(1a)的支承衬底(1)；沿生长方向(R)在所述硅表面(1a)上沉积层序列(100)，其中所述层序列(100)包含至少两个GaN层(5)，所述GaN层利用氮化镓形成，所述层序列包含掩膜层(12)，所述掩膜层利用氮化硅形成，所述掩膜层(12)沿生长方向(R)跟随在所述GaN层(5)的至少一部分之后，以及最早在第一GaN层(5a)的沉积之后施加掩膜层(12)。

1. 用于制造层结构的方法,具有下述步骤:

- 提供具有硅表面(1a)的支承衬底(1);

- 沿生长方向(R)在所述硅表面(1a)上沉积层序列(100),其中

- 所述层序列(100)包含至少两个GaN层(5),所述GaN层利用氮化镓形成,

- 所述层序列包含掩膜层(12),所述掩膜层利用氮化硅形成,

- 所述掩膜层(12)沿生长方向(R)跟随在所述GaN层(5)的至少一部分之后,

- 最早在第一GaN层(5a)的沉积之后施加掩膜层(12),以及

- 所述第一GaN层(5a)是假晶的GaN层(5a)。

2. 用于制造层结构的方法,具有下述步骤:

- 提供具有硅表面(1a)的支承衬底(1);

- 沿生长方向(R)在所述硅表面(1a)上沉积层序列(100),其中,具有下述步骤:

- 将由氮化铝构成的成核层(2)直接沉积到所述硅表面(1a)上,

- 将由氮化铝构成的缓冲层(3)直接沉积到所述成核层(2)上,

- 将假晶的GaN层(5)直接沉积到所述缓冲层(3)上;其中

- 假晶的GaN层(5)利用氮化镓形成,

- 所述层序列包含掩膜层(12),所述掩膜层利用氮化硅形成,

- 所述掩膜层(12)沿生长方向(R)跟随在所述假晶的GaN层(5)的至少一部分之后,以及

- 与所述成核层(2)相比在更高的生长温度下沉积所述缓冲层(3)。

3. 根据权利要求1或2所述的方法,

其中所述掩膜层(12)设置在GaN层内。

4. 根据权利要求1或2所述的方法,

其中所述掩膜层(12)直接邻接两个GaN层。

5. 根据权利要求1或2所述的方法,

其中沿生长方向(R)在所述掩膜层(12)之前设置有至少两个GaN层(5、8、11)。

6. 根据权利要求1或2所述的方法,

其中所述层序列(100)包含至少两个GaN层(5、8、11),并且沿生长方向(R)在每个GaN层(5、8、11)之后均跟随有AlN层(7、10、15)。

7. 根据权利要求1或2所述的方法,

其中所述层序列(100)包含至少两个GaN层(5、8、11),并且沿生长方向(R)在每个GaN层(5、8、11)之后均跟随有AlGaN层(7、10、15)。

8. 根据权利要求1或2所述的方法,

其中所述层序列(100)包含至少两个GaN层(5、8、11),沿生长方向(R)在每个GaN层(5、8、11)之后均跟随有AlGaN层(7、10、15)或AlN层(7、10、15)。

9. 根据权利要求7所述的方法,

其中在所述AlGaN层(7、10、15)中的至少一个中的Ga浓度在最少5%和最多10%之间。

10. 根据权利要求1或2所述的方法,

其中所述层序列(100)包含至少两个GaN层(5、8、11),并且在每个GaN层(5、8、11)内均设置有掩膜层(12)。

11. 根据权利要求1或2所述的方法,

其中所述层序列(100)在所述硅表面(1a)和沿生长方向(R)的首个掩膜层(12)之间没有AlGaN层。

12.根据权利要求1或2所述的方法，

其中所述层序列(100)没有AlGaN层。

13.根据权利要求1所述的方法，

其中所述层序列(100)包括缓冲层(3)，

其中沿生长方向(R)在缓冲层(3)之后直接跟随有GaN层(5a)。

14.根据权利要求13所述的方法，

其中沿生长方向(R)的首个所述掩膜层(12)设置在所述假晶的GaN层(5a)和GaN层(8)之间，其中所述掩膜层(12)的厚度在0.5nm和2.5nm之间。

15.根据权利要求2所述的方法，

其中沿生长方向(R)的首个所述掩膜层(12)设置在所述假晶的GaN层(5a)和GaN层(8)之间，其中所述掩膜层(12)的厚度在0.5nm和2.5nm之间。

## 用于制造层结构的方法

[0001] 本发明申请是于申请日为2010年9月28日提交的、申请号为201080044047.8(国际申请号为PCT/EP2010/064353)以及发明名称为“用于制造发光二极管的方法”的发明专利申请的分案申请。

### 技术领域

[0002] 提出了一种用于制造发光二极管的方法。

### 背景技术

[0003] 参考文献WO 2007/096405和US 6,611,002描述了将基于氮化镓的层外延地沉积在硅衬底上。

### 发明内容

[0004] 待实现的目的存在于,提出一种方法,借助所述方法能够将高层厚度和高材料质量的基于氮化镓的层的沉积在硅表面上。

[0005] 根据用于制造发光二极管的方法的至少一个实施形式,在一个方法步骤中提供具有硅表面的支承衬底。为此,支承衬底例如能够由硅组成。此外,可能的是,支承衬底为SOI衬底(绝缘衬底上的硅)。支承衬底的硅表面例如为(111)硅表面。

[0006] 支承衬底例如以其至少130W/(mK)的良好导热性为特征。

[0007] 根据方法的至少一个实施形式,在一个方法步骤中将层序列沉积在硅表面上。例如,层序列外延地施加到硅表面上。层序列具有生长方向,所述层序列沿该生长方向生长到硅表面上。例如,生长方向垂直于硅表面或者与硅表面上的焊料成例如<7°的小角。

[0008] 根据方法的至少一个实施形式,在一个方法步骤中,将发光二极管结构沉积到层序列上,也就是说,例如得到沿生长方向的下述序列:硅表面、层序列、发光二极管结构。发光二极管结构例如基于氮化镓。层序列例如用于实现在硅表面上生长具有至少3μm、例如至少5μm的相对高的层厚度和高材料质量的发光二极管结构。

[0009] 根据方法的至少一个实施形式,层序列包括以氮化镓形成的GaN层。例如,GaN层由n掺杂的氮化镓组成。

[0010] 在该实施形式中,层序列此外包括以氮化硅形成并且例如由氮化硅制成的掩膜层。掩膜层的生长例如能够通过将例如为硅烷或者乙硅烷的硅前体或者例如为氨草胶或二甲肼的具有氮前体的有机硅化合物同时导入到生长腔室中来进行,在所述生长腔室中例如进行外延生长。然后,两种前体在生长表面上在形成氮化硅的情况下进行反应。

[0011] 在此,掩膜层能够如参考文献WO 2007/096405所描述的那样构成和制造。参考文献WO 2007/096405关于在此描述的掩膜层的构成和制造明确地通过引用结合于此。

[0012] 在此,掩膜层沿生长方向跟随GaN层的至少一部分。即,根据方法的该实施形式,在GaN层的第一生长之后沿生长方向沉积掩膜层。在此,掩膜层能够直接邻接到GaN层上。在此,“GaN层的至少一部分”是说掩膜层还能够设置在GaN层中。也就是说,沉积GaN层的一部

分,然后跟随有掩膜层并且然后跟随有GaN层的剩余部分。

[0013] 在此示出,最早在第一GaN层的沉积之后施加掩膜层对于改进后续的发光二极管结构的材料质量为尤其有利的。相反地,在沉积第一GaN层之前引入掩膜层表现为抑制在层序列中的压缩张力的建立,这引起发光二极管结构的材料质量变差。

[0014] 总而言之能够实现在此描述的方法,即在层序列中稍后地引入掩膜层,随后将在较高层厚度下具有特别高的材料质量的发光二极管结构施加到层序列上。因此,在发光二极管结构中的材料质量的改进例如可以解释为:通过在层序列中稍后地引入掩膜层正面地影响在层序列中压缩张力的建立。

[0015] 根据方法的至少一个实施形式,掩膜层设置在GaN层内。换而言之,掩膜层在该实施形式中既沿生长方向又逆着生长方向直接邻接到GaN上。因此,GaN层优选为沿生长方向的最后的GaN层,所述最后的GaN层在发光二极管结构生长之前沉积。

[0016] 根据方法的至少一个实施形式,沿生长方向,在掩膜层之前设置至少两个GaN层。即,掩膜层例如沉积在层堆的第三GaN层中。这证实为优点,因为掩膜层以这种方式较晚地在层堆中沉积并且因此能够不负面地影响压缩张力的建立。

[0017] 根据方法的至少一个实施形式,掩膜层为没有完全封闭的层。因此,在掩膜层中构成窗,在所述窗中双侧地邻接有掩膜层的GaN层没有由于掩膜层而中断。

[0018] 根据方法的至少一个实施形式,层序列包括至少两个GaN层。沿生长方向每个GaN层之后都跟随有AlN层和/或AlGaN层。这尤其还对于在层堆中的沿生长方向最后的GaN层是这种情况,使得发光二极管结构例如能够直接地跟随在层堆中的最后的AlN层或最后的AlGaN层之后。

[0019] 如果使用AlGaN层,则该层优选具有在例如最少5%和最多10%之间的少量的Ga部分。

[0020] 根据方法的至少一个实施形式,层序列包括至少两个GaN层并且在至少两个GaN层的每个GaN层之一内设有掩膜层。因此,例如能够在每个层序列的GaN层内设有掩膜层。

[0021] 掩膜层为如更上面所描述的掩膜层。在GaN层内的掩膜层因此沿生长方向和逆着生长方向分别邻接GaN(部分)层。将掩膜层引入到层序列的至少两个GaN层或者每个GaN层中尤其正面地影响在层序列中的压缩张力的建立。

[0022] 根据方法的至少一个实施形式,在硅表面和从硅表面来看沿层序列的生长方向跟随的第一掩膜层之间的层序列没有AlGaN层。换而言之,层序列至少在第一掩膜层出现之前的区域中没有AlGaN过渡层。

[0023] 相反地,例如在参考文献US 6,617,060B1中发表的观点示出,能够至少局部地省去在层序列中的AlGaN过渡层。AlGaN层尤其设置用于,降低由于在尤其为硅表面的支承衬底和生长的GaN层之间的不同热膨胀系数所形成的张力,所述张力在冷却层序列时建立。然而,期望的是,通过相对于硅表面收缩GaN层在层序列的冷却时形成多个其他的匹配错位。因此,省去AlGaN层能够证实为是有利的。

[0024] 根据至少一个实施形式,层序列整体上没有AlGaN层。即,在该实施形式中,在整个层序列中未设置AlGaN过渡层。

[0025] 根据方法的至少一个实施形式,在硅表面上设置的缓冲层之后沿生长方向直接跟随有GaN层,其中该GaN层尤其为假晶的GaN层。此外,假晶的GaN层以其实现到置于其下的层

的反向的张力为特征。因此,在冷却层序列时,假晶的GaN层能够反作用于相对于硅表面收缩置于其下的其他的GaN层。

[0026] 在此,假晶的GaN层尤其理解为在保持硅表面的晶体结构的情况下生长的GaN层。在此,尤其还可能的是,硅表面的晶格常数传输到假晶的GaN层上。

[0027] 根据方法的至少一个实施形式,以生长方向在假晶的GaN层和另一GaN层之间设置第一掩膜层。掩膜层例如能够直接邻接到两个GaN层上,因此所述掩膜层设置在GaN层内,其中GaN层的沿生长方向置于掩膜层之下部分是假晶的,并且GaN层的沿生长方向置于掩膜层之上部分不是假晶的。

[0028] 在此示出,引入假晶的GaN层结合有利地构成的、优选是SiN掩膜层的掩膜层引起:随后的GaN层重新地在通过掩膜层部分覆盖的假晶的GaN层上生长,并且在此能够完全有效地阻止能够产生自置于之下的层中的或者能够在那里形成的错位。

[0029] 在此,优选的是,掩膜层具有最小0.5nm和最多2.5nm之间、尤其至少1nm和最多2nm之间的范围中的厚度。在此,掩膜层如上面描述优选构成为不封闭的层。例如,掩膜层具有窗,并且以网形式覆盖置于其下的假晶的GaN层。

[0030] 根据方法的至少一个实施形式,发光二极管结构在其施加之后从层序列剥离。因此,发光二极管结构能够以无衬底的二极管的形式使用。此外,可能的是,发光二极管结构在剥离之前以其背离层序列的侧施加到支承体上。支承体例如能够包括硅或者锗或者由这些材料之一组成。

## 附图说明

[0031] 下面,借助实施例和相关附图详细阐明在此所描述的方法。

[0032] 图1和6示出图形显示,根据所述图形显示详细阐明在此所描述的方法。

[0033] 图2、3、4和5示出外延地制造的层结构的示意剖面图,根据所述示意剖面图详细阐明在此所描述的方法。

## 具体实施方式

[0034] 相同的、同类的或者起相同作用的元件在附图中设有相同的附图标记。附图和在附图中示出的元件的大小比例彼此之间不视为按照尺寸的。相反地,各个元件能够为了更好的可示出性和/或为了更好的理解夸张大地示出。

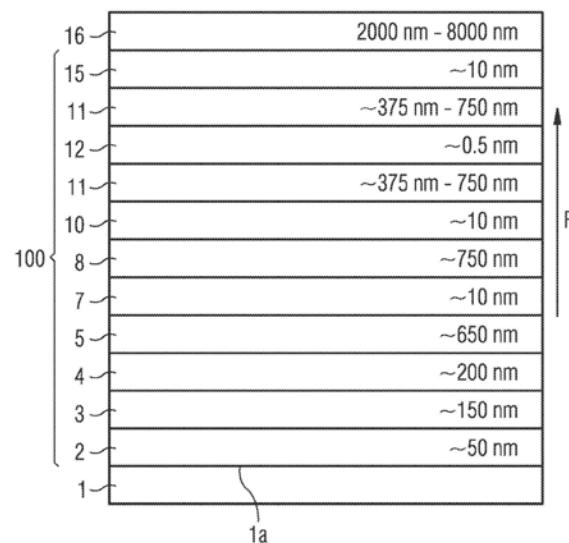

[0035] 图1是示出层序列的沉积到硅表面的层以及发光二极管结构的曲率K与以秒计的生长时间T的关系的图形显示。在此,生长方向R对应于时间变化曲线。在图1中示出两条曲线:曲线A涉及其中以氮化硅形成的掩膜层在层序列100的第一GaN层之前生长的实施例。

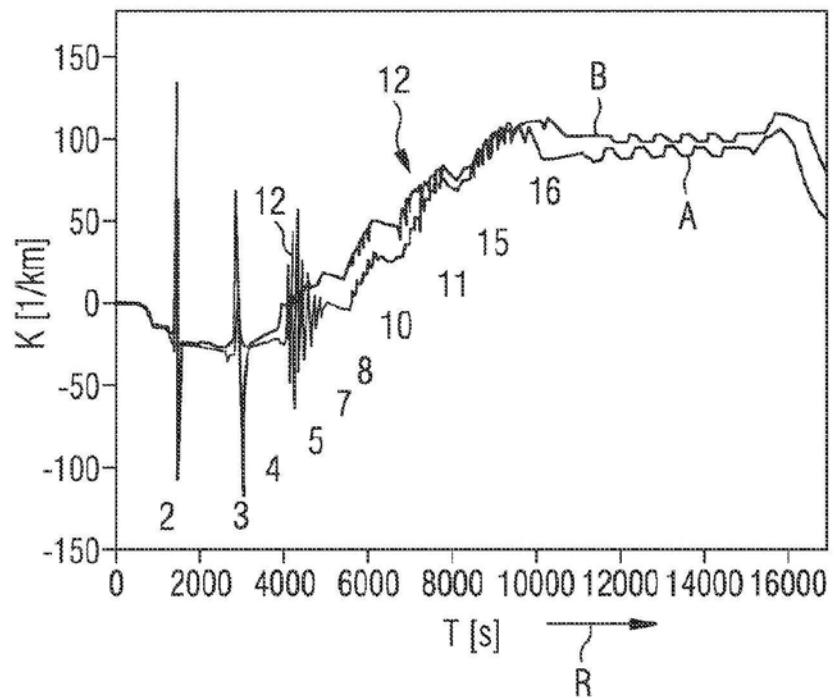

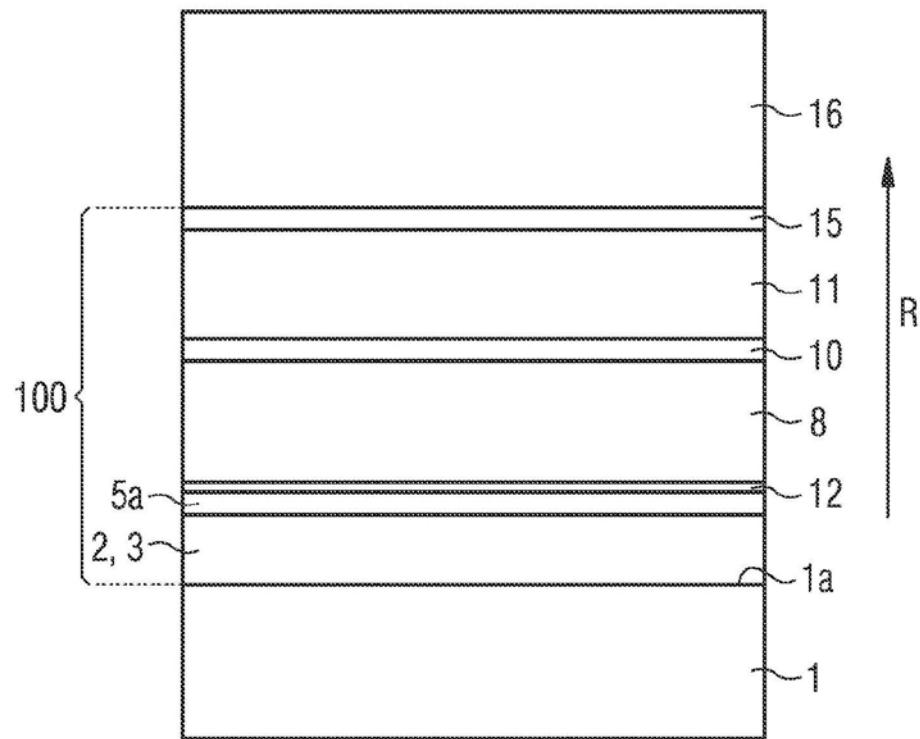

[0036] 在图2的示意剖面图中示出这种层变化:具有其硅表面1a的支承衬底1之后跟随有掩膜层12,所述掩膜层12之后在生长方向R中跟随有层堆100的第一GaN层5。层堆100包括总共三个GaN层,即GaN层5、8和11。

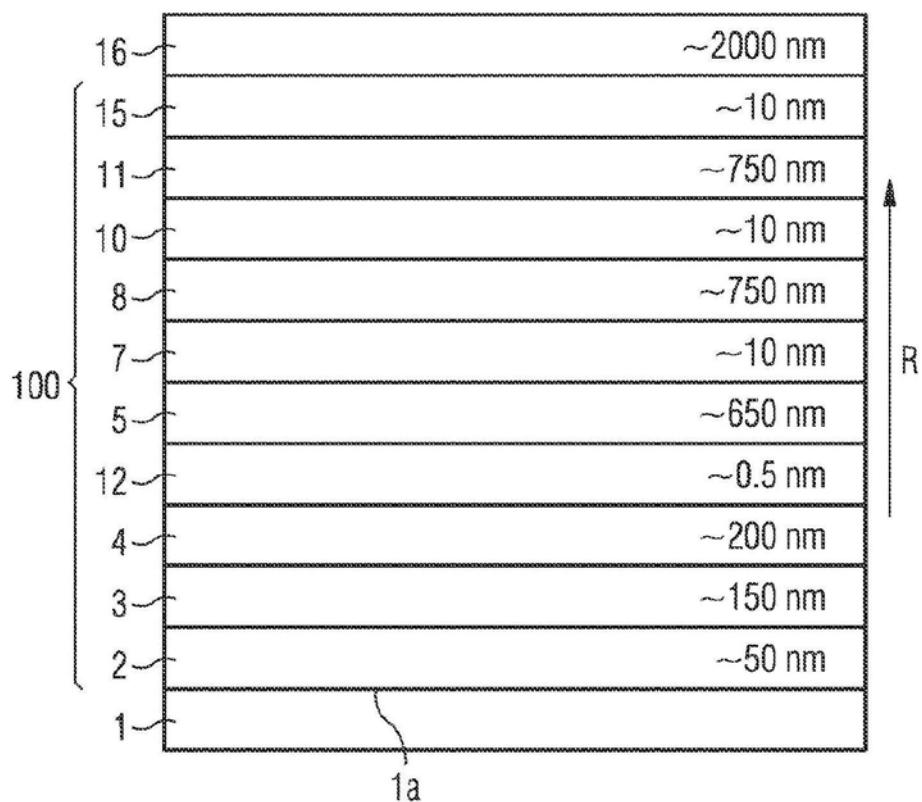

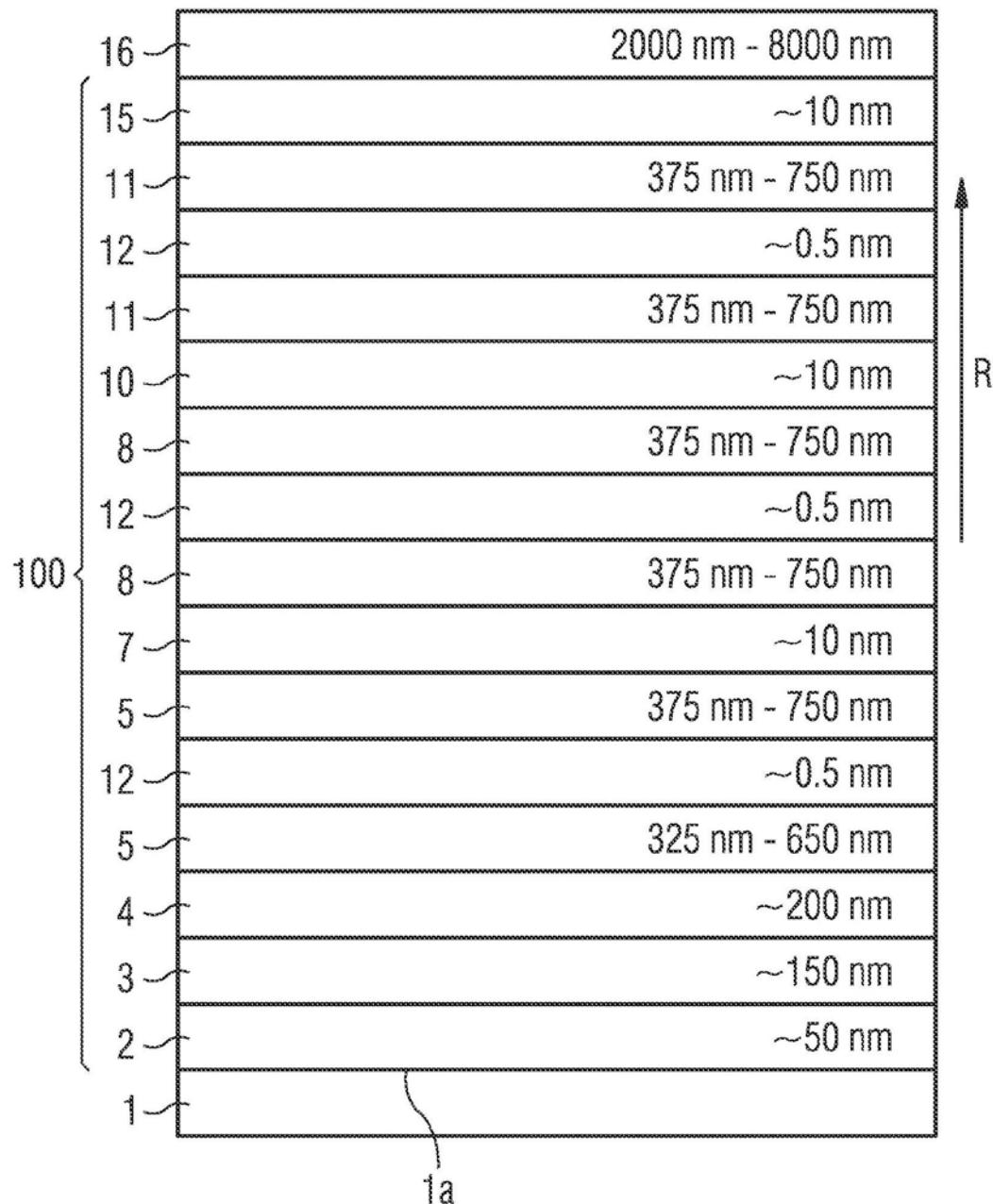

[0037] 曲线B涉及其中掩膜层设置在层堆100的第三GaN层11中的实施例。这例如在图3中根据示意的剖面图来图形地阐明。

[0038] 如从图1中可见,曲率在情况B中尤其在发光二极管16的区域中大于在情况A中。因此,将掩膜层12时间上稍后引入到层序列100中引起生长的层的更大的压缩张力。

- [0039] 在此,对于情况B,层的顺序如下(参见图3的示意剖面图) :

- [0040] 层结构100包括支承衬底1,其例如由硅组成并且具有例如为111表面1a的硅表面。

- [0041] 层序列100的随后的层在生长方向R中例如以直接彼此相继的方式沉积到硅表面上:

- [0042] -由氮化铝组成的成核层2,

- [0043] -由氮化铝组成的缓冲层3,所述缓冲层在比成核层2高的生长温度下、例如在至少1000°C下沉积。

- [0044] -AlGaN层4,在其中铝浓度沿生长方向R逐级地从最高95%下降至最低15%,

- [0045] -第一GaN层5

- [0046] -AlN层或者AlGaN层7,其能够在大约850°C的生长温度中生长,

- [0047] -第二GaN层8,

- [0048] -跟随的AlN层或者AlGaN层10,其也能够在大约850°C中生长,

- [0049] -第三GaN层11,在所述第三GaN层内设置有掩膜层12,和

- [0050] -AlN层或者AlGaN层15。

- [0051] 在AlN层或者AlGaN层15的背离支承衬底1的侧上设置发光二极管结构16,所述发光二极管结构例如包括多量子阱结构并且基于GaN。

- [0052] 在图2中示出符合曲线A的层结构。

- [0053] 结合图4详细阐明在此所描述的方法的另一实施例。借助该方法,产生层的在图4中以剖面图示意性示出的序列。

- [0054] 不同于结合图3所描述层顺序,层序列100在该实施例中在每个GaN层5、8、11之间包括掩膜层12,所述掩膜层以氮化硅形成并且例如由氮化硅组成。在此,掩膜层12能够具有在生长方向R中相应地测量的最少0.35nm和最多0.65nm的厚度。

- [0055] 将掩膜层12引入到层序列100的每个GaN层中引起在层序列100的背离支承衬底1的表面上尤其高的压缩张力的建立,所述压缩张力实现具有在生长方向R中测量的直至8μm的厚度的发光二极管结构16的生长,而没有在发光二极管结构16中出现裂纹。

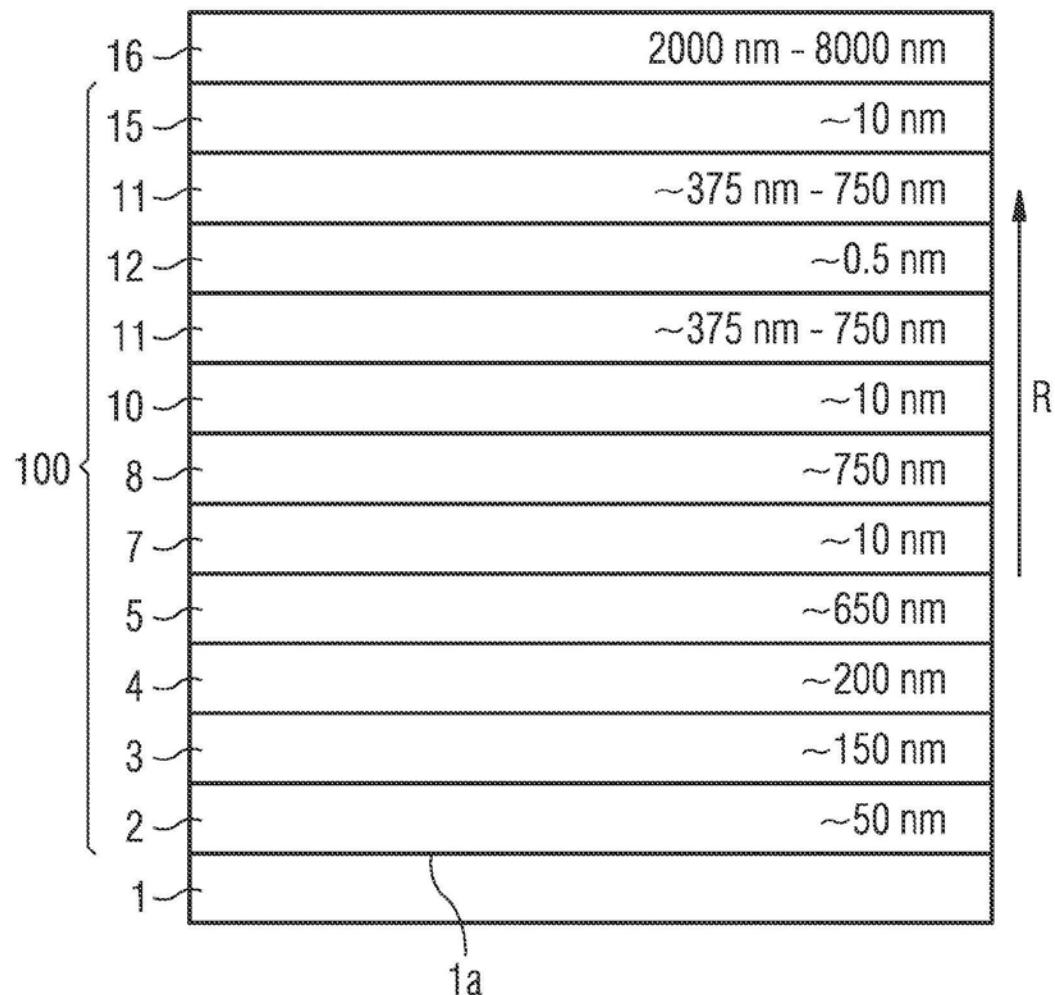

- [0056] 结合图5,详细阐明在此所描述的方法的另一实施例。例如不同于图2的实施例,层序列100当前没有AlGaN过渡层。层序列100的层结构沿生长方向例如能够如下所述:

- [0057] -具有硅表面1a的衬底1,

- [0058] -成核层2以及缓冲层3,其能够分别例如由氮化铝组成并且能够具有总共大约200nm的厚度,

- [0059] -GaN层,其假晶地生长并且具有大约100nm的厚度,

- [0060] -第一掩膜层12,其例如以氮化硅形成并且具有在1nm和2nm之间的厚度,

- [0061] -另一GaN层8,其具有大约700nm的厚度,

- [0062] -第一AlN层10,其例如能够在大约850°C的温度中生长,

- [0063] -第三GaN层11,其例如具有大约700nm的厚度,和

- [0064] -另一AlN层,其能够在大约850°C的低生长温度中生长。

- [0065] 该层序列100之后跟随有例如具有在4μm和8μm之间的厚度的发光二极管结构16。

- [0066] 图5的实施例尤其以省去在缓冲层3和第一掩膜层12之间的AlGaN过渡层为特征。

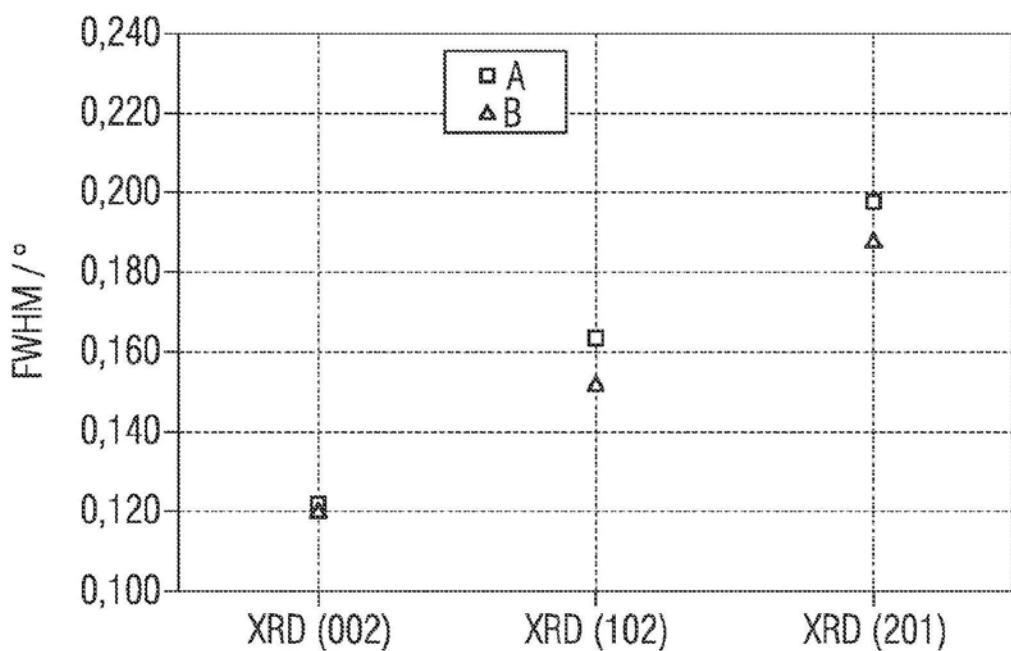

- [0067] 结合图6图形地示出省去该AlGaN过渡层4的效果。为此,图6示出用于不同反射的X

**射线摇摆曲线的半值宽度( Halbwärtsbreiten )。**

[0068] 在图6中的值A涉及基准结构,如其例如在图2中示出,所述基准结构包括AlGaN层4。值B涉及层序列100,如其在图5中示出,在所述层序列中省去过渡层AlGaN。

[0069] 特别地,图6示出反射102和201的X射线摇摆曲线的半值宽度的较低的数值。这是级错位的降低的缺陷密度的明显提示。这使得可以期待在发光二极管结构16的构建用于辐射产生的有源层中提高的内部量子效率。额外地,这种层序列100能够显著更简单并且因此更低成本地制造。

[0070] 在图2、3和4中以及在对图5的描述中,对于每个层说明示例性厚度或者厚度范围。在此,厚度或者厚度范围的所说明的边界能够在所说明的值+/-30%、优选+/-20%、尤其优选+/-10%的范围中波动。

[0071] 该专利申请要求德国专利申请102009047881.7的优先权,其公开内容通过引用结合于此。

[0072] 本发明不通过根据实施例的描述而限制于此。相反地,本发明包括任何新的特征以及特征的任何组合,这尤其是包含在权利要求中的特征的任意组合,即使这些特征或者这些组合本身在权利要求或者实施例中未明确说明。

[0073] 根据上述描述可知,本发明的实施例涵盖但不限于以下技术方案:

[0074] 方案1. 用于制造发光二极管的方法,具有下述步骤:

[0075] - 提供具有硅表面1a的支承衬底1;

[0076] - 沿生长方向R在所述硅表面1a上沉积层序列100,并且

[0077] - 将发光二极管结构16沉积到所述层序列100上,其中

[0078] - 所述层序列100包含以氮化镓形成的GaN层5,

[0079] - 所述层序列包含以氮化硅形成的掩膜层12,并且

[0080] - 所述掩膜层12沿生长方向R跟随在所述GaN层5的至少一部分之后。

[0081] 方案2. 根据上一项方案所述的方法,其中

[0082] - 所述掩膜层12设置在GaN层内。

[0083] 方案3. 根据上述方案之一所述的方法,其中

[0084] - 所述掩膜层12直接邻接两个GaN层。

[0085] 方案4. 根据上述方案之一所述的方法,其中

[0086] - 沿生长方向R在所述掩膜层12之前设置有至少两个GaN层5、8、11。

[0087] 方案5. 根据上述方案之一所述的方法,其中

[0088] - 所述层序列100包含至少两个GaN层5、8、11,

[0089] - 沿生长方向R在每个GaN层5、8、11之后均跟随有AlN层7、10、15。

[0090] 方案6. 根据上述方案之一所述的方法,其中

[0091] - 所述层序列100包含至少两个GaN层5、8、11,

[0092] - 沿生长方向R在每个GaN层5、8、11之后均跟随有AlGaN层7、10、15。

[0093] 方案7. 根据上述方案之一所述的方法,其中

[0094] - 所述层序列100包含至少两个GaN层5、8、11,

[0095] - 沿生长方向R在每个GaN层5、8、11之后均跟随有AlGaN层7、10、15和/或AlN层7、10、15。

- [0096] 方案8.根据方案6或7之一所述的方法,其中在所述AlGaN层7、10、15中的至少一个中的Ga浓度在最少5%和最多10%之间。

- [0097] 方案9.根据上述方案之一所述的方法,其中

- [0098] -所述层序列100包含至少两个GaN层5、8、11,并且

- [0099] -在每个GaN层5、8、11内均设置有掩膜层12。

- [0100] 方案10.根据上述方案之一所述的方法,其中

- [0101] -所述层序列100在所述硅表面1a和沿生长方向R的首个掩膜层12之间没有AlGaN层。

- [0102] 方案11.根据上述方案之一所述的方法,其中

- [0103] -所述层序列100没有AlGaN层。

- [0104] 方案12.根据上述方案之一所述的方法,其中

- [0105] -沿生长方向R在缓冲层3之后直接跟随有GaN层5a。

- [0106] 方案13.根据上一项方案所述的方法,其中

- [0107] -所述GaN层5a是假晶的GaN层5a。

- [0108] 方案14.根据上一项方案所述的方法,其中

- [0109] -沿生长方向R的首个所述掩膜层12设置在所述假晶的GaN层5a和GaN层8之间,其中所述掩膜层12的厚度在0.5nm和2.5nm之间。

- [0110] 方案15.根据上述方案之一所述的方法,其中

- [0111] -将发光二极管结构16从所述层序列100剥离。

图1

图2

图3

图4

图5

图6