(19) 日本国特許庁 (JP)

(12) 公開特許公報(A)

(11) 特許出願公開番号

特開2009-229502

(P2009-229502A)

(43) 公開日 平成21年10月8日(2009.10.8)

(51) Int.Cl.

|               |        |           |

|---------------|--------|-----------|

| <i>GO 2 F</i> | 1/136  | (2006.01) |

| <i>HO 1 L</i> | 31/10  | (2006.01) |

| <i>HO 1 L</i> | 27/146 | (2006.01) |

| <i>GO 6 F</i> | 3/041  | (2006.01) |

| <i>HO 1 L</i> | 21/205 | (2006.01) |

F

GO 2 F 1/136

HO 1 L 31/10

HO 1 L 27/14

GO 6 F 3/041

HO 1 L 21/205

### テーマコード（参考）

2H092

2H191

4KO30

4M118

5BO87

審査請求 未請求 請求項の数 10 O L (全 27 頁) 最終頁に続く

(21) 出願番号

(22) 出願日

特願2008-71255 (P2008-71255)

(22) 出願日

平成20年3月19日(2008.3.19)

(71) 出願人 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74) 代理人 100094053

弁理士 佐藤 隆久

(72) 発明者 浅野 明彦

東京都港区港南1丁目7番1号 ソニー株

式会社内

|          |       |       |      |      |      |      |

|----------|-------|-------|------|------|------|------|

| Fターム(参考) | 2H092 | GA29  | JA26 | JA46 | KA04 | MA05 |

|          |       | MA08  | MA12 | MA35 | MA37 | PA06 |

|          |       | PA07  |      |      |      |      |

|          | 2H191 | FA91Y | FB15 | FB23 | FC10 | FC36 |

|          |       | FC41  | FD04 | GA17 | GA19 | LA40 |

|          | 4K030 | BA30  | BA44 | DA09 | FA01 |      |

最終頁に統ぐ

(54) 【発明の名称】 表示装置、および、その製造方法

(57) 【要約】

【課題】フォトセンサ素子の感度を向上可能とする。

【解決手段】n層47nとi層47iとp層47pとのそれぞれを液晶パネル200の面の法線方向zにおいて、順次、積層することで、フォトセンサ素子32を形成する。ここでは、ポリシリコンよりも光吸収係数が高い微結晶シリコンによって、i層47iを形成する。

### 【選択図】図 3

**【特許請求の範囲】****【請求項 1】**

画素領域に画素が配置された表示パネルを含み、当該表示パネルに入射する光を受光するフォトセンサ素子が当該表示パネルに設けられている表示装置であって、

前記フォトセンサ素子は、

第1導電型半導体層と、

前記第1導電型半導体層と異なる導電型の第2導電型半導体層と、

真性半導体層と

を含み、前記第1導電型半導体層と前記第2導電型半導体層とが前記真性半導体層を挟むように設けられているフォトダイオードであり、

前記第1導電型半導体層と前記真性半導体層と前記第2導電型半導体層とのそれぞれは、前記表示パネルの法線方向において、前記光が入射する側から、順次、積層されており、

前記真性半導体層は、非晶質半導体または微結晶半導体の少なくとも一方を含む半導体薄膜によって形成されている、

表示装置。

**【請求項 2】**

前記表示パネルは、

前記画素領域において前記画素をスイッチングする画素スイッチング素子を有し、

20

前記画素スイッチング素子は、

チャネル領域が形成された半導体層

を有する薄膜トランジスタであり、

前記フォトセンサ素子は、

当該フォトセンサ素子の前記第1導電型半導体層と前記真性半導体層と前記第2導電型半導体層とのいずれかと、前記画素スイッチング素子の半導体層とのそれぞれは、同じ半導体層がパターン加工されることで形成されている、

請求項1に記載の表示装置。

**【請求項 3】**

前記第1導電型半導体層は、非晶質半導体であり、

30

前記第2導電型半導体層は、微結晶半導体または多結晶半導体である、

請求項1に記載の表示装置。

**【請求項 4】**

前記第1導電型半導体層は、微結晶半導体であり、

前記第2導電型半導体層は、微結晶半導体または多結晶半導体である、

請求項1に記載の表示装置。

**【請求項 5】**

前記第2導電型半導体層は、

高抵抗層と、

前記高抵抗層よりも抵抗率が低い低抵抗層とを有し、

40

前記高抵抗層は、前記真性半導体層と前記低抵抗層との間に介在するように設けられている、

請求項1に記載の表示装置。

**【請求項 6】**

前記第1導電型半導体層は、透明材料で形成されている、

請求項1に記載の表示装置。

**【請求項 7】**

前記第1導電型半導体層と前記第2導電型半導体層と前記真性半導体層とのそれぞれは、シリコン半導体である、

請求項1に記載の表示装置。

50

**【請求項 8】**

前記表示パネルの一方の面に照明光を出射する照明部

を含み、

前記照明部は、可視光線と不可視光線とを前記照明光として出射するように構成されて

おり、

前記フォトセンサ素子は、前記表示パネルの他方の面の側において前記画素領域に移動

した被検知体によって前記照明光が反射された反射光を受光するように構成されている、

請求項 1 に記載の表示装置。

**【請求項 9】**

前記表示パネルは、

第 1 基板と、

前記第 1 基板から間隔を隔てて対面している第 2 基板と、

前記第 1 基板と前記第 2 基板との間に挟持されており、液晶分子が配向されている液

晶層と

を含む液晶パネルであって、前記第 1 基板が前記一方の面の側に位置し、前記第 2 基板

が前記他方の面の側に位置しており、

前記フォトセンサ素子は、前記第 2 基板に設けられている、

請求項 8 に記載の表示装置。

**【請求項 10】**

画素領域に画素が配置される表示パネルを含み、当該表示パネルに入射する光を受光す

るフォトセンサ素子が当該表示パネルに設けられる表示装置であって、前記フォトセンサ

素子は、第 1 導電型半導体層と、前記第 1 導電型半導体層と異なる導電型の第 2 導電型半

導体層と、真性半導体層とを含み、前記第 1 導電型半導体層と前記第 2 導電型半導体層と

が前記真性半導体層を挟むように設けられているフォトダイオードである表示装置の製造

方法であって、

前記表示パネルの法線方向において前記光が入射する側から、前記第 1 導電型半導体層

と前記真性半導体層と前記第 2 導電型半導体層とのそれぞれが、順次、設けられるよう

に、前記第 1 導電型半導体層と前記真性半導体層と前記第 2 導電型半導体層とのそれぞれを

形成する工程

を有し、当該工程においては、前記真性半導体層を非晶質半導体または微結晶半導体の

少なくとも一方を含む半導体によって形成する、

表示装置の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、表示装置、および、その製造方法に関する。特に、本発明は、画素領域に画

素が配置された表示パネルを含み、その表示パネルに入射する光を受光するフォトセンサ

素子が、その表示パネルに設けられている表示装置、および、その製造方法に関する。

**【背景技術】****【0002】**

液晶表示装置、有機EL表示装置などの表示装置は、薄型、軽量、低消費電力といった

利点を有する。

**【0003】**

このような表示装置において、液晶表示装置は、一対の基板の間に液晶層が封入された

液晶パネルを、表示パネルとして有している。液晶パネルは、たとえば、透過型であって

、液晶パネルの背面に設けられたバックライトなどの照明装置が射出した照明光を、その

液晶パネルが変調して透過させる。そして、その変調した照明光によって画像の表示が、

液晶パネルの正面にて実施される。

**【0004】**

この液晶パネルは、たとえば、アクティブマトリクス方式であり、画素スイッチング素

10

子として機能する薄膜トランジスタ (TFT : Thin Film Transistor) が複数形成されている TFT アレイ基板と、その TFT アレイ基板に対面するように対向する対向基板と、TFT アレイ基板および対向基板の間に設けられた液晶層とを有する。このアクティブマトリクス方式の液晶パネルにおいては、画素スイッチング素子が画素電極に電位を入力することによって、液晶層に印加する電圧を印加し、その画素を透過する光の透過率を制御して、その光を変調させる。

#### 【0005】

上記のような液晶パネルにおいては、上記の画素スイッチング素子として機能する TFT の他に、光を受光して受光データを得るフォトセンサ素子が位置センサ素子として内蔵されたものが提案されている。

10

#### 【0006】

上記のようにフォトセンサ素子が位置センサ素子として内蔵された液晶パネルは、ユーザーインターフェイスとしての機能が実現できるため、I/O タッチパネル (Integrated-Optical touch panel) と呼ばれている。このタイプの液晶パネルにおいては、液晶パネルの前面に、別途、抵抗膜方式や静電容量方式のタッチパネルを設置する必要がなくなる。このため、装置の小型化を、容易に実現できる。また、さらに、抵抗膜方式や静電容量方式のタッチパネルを設置した場合には、そのタッチパネルによって画素領域において透過する光が減少する場合や、その光が干渉される場合があるため、表示画像の品質が低下する場合があるが、上記のように位置センサ素子として液晶パネルにフォトセンサ素子を内蔵することによって、この不具合の発生を防止できる。

20

#### 【0007】

このような液晶パネルにおいては、たとえば、液晶パネルの前面に触れられたユーザーの指やタッチペンなどの被検知体からの可視光線を、そのフォトセンサ素子が受光する。その後、そのフォトセンサ素子によって得られた受光データに基づいて、その被検知体が接触した位置を特定し、その特定された位置に対応する操作が、液晶表示装置自身や、その液晶表示装置に接続された他の電子機器において実施される。

#### 【0008】

上記のように、位置センサ素子として内蔵されたフォトセンサ素子を用いて、被検知体の位置を検出する場合には、そのフォトセンサ素子によって得られる受光データは、外光に含まれる可視光線の影響によって、多くのノイズを含む場合がある。また、画素領域において黒表示を実施する場合には、TFT アレイ基板に設けられたフォトセンサ素子は、被検知体から出射される可視光線を受光することが困難である。このため、正確に、被検知体の位置を検出することが、困難な場合がある。

30

#### 【0009】

このような不具合を改善するために、赤外線など、可視光線以外の不可視光線を用いる技術が提案されている。ここでは、被検知体から反射される赤外線を、位置センサ素子として内蔵されたフォトセンサ素子が受光することによって、受光データを取得し、その取得したデータに基づいて、被検知体の位置を特定している（たとえば、特許文献 1、特許文献 2、特許文献 3 参照）。

40

#### 【0010】

【特許文献 1】特開 2005-275644 号公報

【特許文献 2】特開 2004-318819 号公報

【特許文献 3】特開 2006-301864 号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0011】

しかしながら、上記においては、位置センサ素子として内蔵されたフォトセンサ素子が、高感度に受光データを生成することが困難な場合がある。

#### 【0012】

50

特に、画素スイッチング素子と同様に、多結晶半導体を半導体薄膜として用いてフォトセンサ素子を形成する場合には、その半導体シリコン薄膜は、波長が700nm以上の光を吸収する吸収率が低いので、この不具合の発生が顕在化する場合がある。つまり、多結晶半導体の半導体薄膜においては、赤外線を吸収する吸収率が可視光線の吸収率と比較して低いために、上記の不具合の発生が顕在化し、位置検出感度の低下が生ずる場合がある。

#### 【0013】

また、画素スイッチング素子と異なり、非晶質シリコンを半導体薄膜として用いてフォトセンサ素子を形成した場合には、製造プロセスが増加するために、製造効率が低下する場合がある。そして、それに伴って、コストが増加する場合がある。

10

#### 【0014】

したがって、本発明は、フォトセンサ素子の感度を向上可能な表示装置、および、その製造方法を提供する。

#### 【課題を解決するための手段】

#### 【0015】

本発明は、画素領域に画素が配置された表示パネルを含み、当該表示パネルに入射する光を受光するフォトセンサ素子が当該表示パネルに設けられている表示装置であって、前記フォトセンサ素子は、第1導電型半導体層と、前記第1導電型半導体層と異なる導電型の第2導電型半導体層と、真性半導体層とを含み、前記第1導電型半導体層と前記第2導電型半導体層とが前記真性半導体層を挟むように設けられているフォトダイオードであり、前記第1導電型半導体層と前記真性半導体層と前記第2導電型半導体層とのそれぞれは、前記表示パネルの法線方向において、前記光が入射する側から、順次、積層されており、前記真性半導体層は、非晶質半導体または微結晶半導体の少なくとも一方を含む半導体によって形成されている。

20

#### 【0016】

好適には、前記表示パネルは、前記画素領域において前記画素をスイッチングする画素スイッチング素子を有し、前記画素スイッチング素子は、チャネル領域が形成された半導体層を有する薄膜トランジスタであり、前記フォトセンサ素子は、当該フォトセンサ素子の前記第1導電型半導体層と前記真性半導体層と前記第2導電型半導体層とのいずれかと、前記画素スイッチング素子の半導体層とのそれは、同じ半導体層がパターン加工されることで形成されている。

30

#### 【0017】

好適には、前記第1導電型半導体層は、非晶質半導体であり、前記第2導電型半導体層は、微結晶半導体または多結晶半導体である。

#### 【0018】

好適には、前記第1導電型半導体層は、微結晶半導体であり、前記第2導電型半導体層は、微結晶半導体または多結晶半導体である。

40

#### 【0019】

好適には、前記第2導電型半導体層は、高抵抗層と、前記高抵抗層よりも抵抗率が低い低抵抗層とを有し、前記高抵抗層は、前記真性半導体層と前記低抵抗層との間に介在するように設けられている。

#### 【0020】

好適には、前記第1導電型半導体層は、透明材料で形成されている。

#### 【0021】

好適には、前記第1導電型半導体層と前記第2導電型半導体層と前記真性半導体層とのそれは、シリコン半導体である。

#### 【0022】

好適には、前記表示パネルの一方の面上に照明光を出射する照明部を含み、前記照明部は、可視光線と不可視光線とを前記照明光として出射するように構成されており、前記フォトセンサ素子は、前記表示パネルの他方の面の側において前記画素領域に移動した被検知

50

体によって前記照明光が反射された反射光を受光するように構成されている。

【0023】

好適には、前記表示パネルは、第1基板と、前記第1基板から間隔を隔てて対面している第2基板と、前記第1基板と前記第2基板との間に挟持されており、液晶分子が配向されている液晶層とを含む液晶パネルであって、前記第1基板が前記一方の面の側に位置し、前記第2基板が前記他方の面の側に位置しており、前記フォトセンサ素子は、前記第2基板に設けられている。

【0024】

本発明は、画素領域に画素が配置される表示パネルを含み、当該表示パネルに入射する光を受光するフォトセンサ素子が当該表示パネルに設けられる表示装置であって、前記フォトセンサ素子は、第1導電型半導体層と、前記第1導電型半導体層と異なる導電型の第2導電型半導体層と、真性半導体層とを含み、前記第1導電型半導体層と前記第2導電型半導体層とが前記真性半導体層を挟むように設けられているフォトダイオードである表示装置の製造方法であって、前記表示パネルの法線方向において前記光が入射する側から、前記第1導電型半導体層と前記真性半導体層と前記第2導電型半導体層とのそれぞれが、順次、設けられるように、前記第1導電型半導体層と前記真性半導体層と前記第2導電型半導体層とのそれぞれを形成する工程を有し、当該工程においては、前記真性半導体層を非晶質半導体または微結晶半導体の少なくとも一方を含む半導体によって形成する。

10

【0025】

本発明においては、表示パネルの法線方向において光が入射する側から、第1導電型半導体層と真性半導体層と第2導電型半導体層とのそれぞれが、順次、設けられるように、第1導電型半導体層と真性半導体層と第2導電型半導体層とのそれぞれを形成する。ここでは、真性半導体層を非晶質半導体または微結晶半導体の少なくとも一方を含む半導体によって形成する。

20

【発明の効果】

【0026】

本発明によれば、フォトセンサ素子の感度を向上可能な表示装置、および、その製造方法を提供することができる。

【発明を実施するための最良の形態】

【0027】

30

本発明にかかる実施形態の一例について説明する。

<実施形態1>

(液晶表示装置の構成)

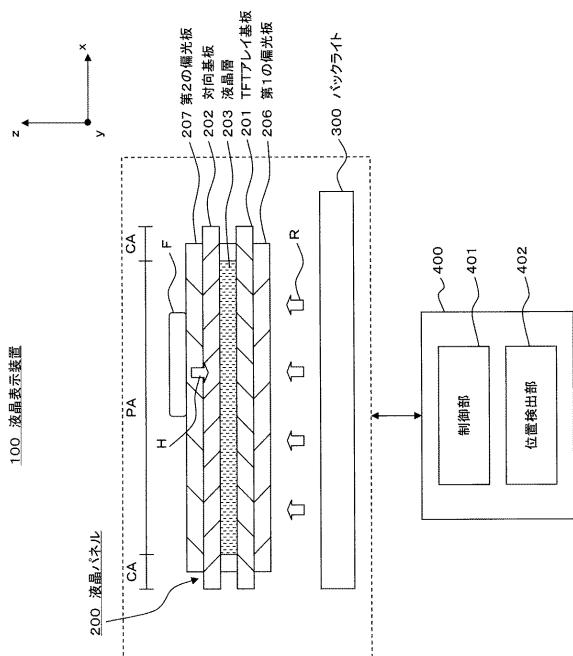

図1は、本発明の実施形態1において、液晶表示装置100の構成を示す断面図である。

【0028】

本実施形態の液晶表示装置100は、図1に示すように、液晶パネル200と、バックライト300と、データ処理部400とを有する。各部について順次説明する。

【0029】

液晶パネル200は、アクティブマトリクス方式であり、図1に示すように、TFTアレイ基板201と対向基板202と液晶層203とを有する。

40

【0030】

この液晶パネル200においては、TFTアレイ基板201と対向基板202とが、互いに間隔を隔てるよう対面している。そして、そのTFTアレイ基板201と対向基板202との間に挟まれるように、液晶層203が設けられている。この液晶層203は、TFTアレイ基板201および対向基板202に形成された液晶配向膜(図示なし)によって配向されている。

【0031】

そして、液晶パネル200は、図1に示すように、TFTアレイ基板201の側に位置するようにバックライト300が配置されており、TFTアレイ基板201において対向

50

基板 202 に対面している面とは反対側の面に、バックライト 300 から出射された照明光 R が照射される。

【0032】

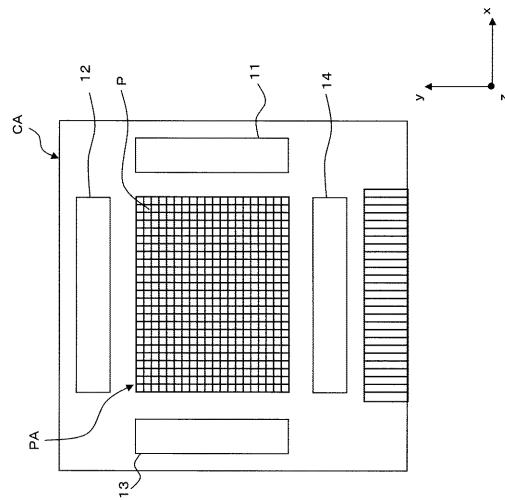

図 2 は、本発明の実施形態 1 において、液晶パネル 200 を示す平面図である。

【0033】

液晶パネル 200 は、図 2 に示すように、画素領域 PA と、周辺領域 CA とを有する。

【0034】

液晶パネル 200 において画素領域 PA には、図 2 に示すように、複数の画素 P が面に沿って配置されている。具体的には、画素領域 PA においては、複数の画素 P が、x 方向と、x 方向に垂直な y 方向とのそれぞれに、マトリクス状に並ぶように配置されている。

10

【0035】

この画素領域 PA においては、液晶パネル 200 の背面側に設置されたバックライト 300 が射出した照明光 R を、第 1 の偏光板 206 を介して背面から受け、その背面から受けた照明光 R が透過する。そして、液晶パネル 200 を透過した照明光 R が第 2 の偏光板 207 を透過し、画像表示が実行される。つまり、液晶パネル 200 は、透過型である。

【0036】

たとえば、本実施形態の液晶表示装置 100 は、ノーマリ・ブラック方式であり、液晶パネル 200 において液晶層 203 に電圧を加えない時に光透過率が低下して黒表示が実施され、一方で、液晶層 203 に電圧を加えた時に光透過率が上がり白表示が実施されるように、第 1 の偏光板 206 と第 2 の偏光板 207 とが配置されている。たとえば、第 1 の偏光板 206 と第 2 の偏光板 207 とは、互いの透過軸がクロスニコルになるように、配置されている。

20

【0037】

具体的には、画素領域 PA においては、複数の画素 P に対応するように、複数の画像スイッチング素子（図示無し）と、複数の画素電極（図示無し）とが TFT アレイ基板 201 に設けられている。そして、対向基板 202 には、複数の画素電極に対面するように共通電極が設けられると共に、複数の画素 P に対応するように、カラーフィルタ層（図示無し）が設けられている。この画素領域 PA においては、画素スイッチング素子が画素 P をスイッチング制御することによって、第 1 の偏光板 206 を介して背面において入射する照明光 R を変調する。たとえば、ポリシリコンを半導体薄膜とする TFT が、画素スイッチング素子として形成され、液晶層 203 に印加する電圧をスイッチング制御することで、液晶層 203 の液晶分子の長尺方向の向きを変えて、照明光 R が透過する透過率を変化させる。そして、その液晶層 203 によって変調された照明光 R が、カラーフィルタ層によって着色され、第 2 の偏光板 207 を介して、正面側から出射し、画素領域 PA においてカラー画像が表示される。

30

【0038】

また、詳細については後述するが、画素領域 PA においては、複数の画素 P に対応するように、受光素子（図示無し）が形成されている。たとえば、フォトダイオード（図示無し）を含むように、受光素子が形成されている。そして、図 1 に示すように、液晶パネル 200 においてバックライト 300 が設置された背面に対して反対側となる正面に、ユーザーの指やタッチペンなどの被検知体 F が接触または近接した際に、その被検知体 F によって反射される反射光 H を受光素子が受光し、受光データを生成するように構成されている。すなわち、対向基板 202 の側から TFT アレイ基板 201 の側へ向かう反射光 H を受光素子が受光し、光電変換することによって、受光データを生成する。

40

【0039】

液晶パネル 200 において周辺領域 CA は、図 2 に示すように、画素領域 PA の周辺を囲うように位置している。この周辺領域 CA においては、図 2 に示すように、表示用垂直駆動回路 11 と、表示用水平駆動回路 12 と、センサ用垂直駆動回路 13 と、センサ用水平駆動回路 14 とが、周辺回路として形成されている。たとえば、画素スイッチング素子 31 と同様に、ポリシリコンを半導体薄膜とする TFT が、この周辺回路を構成する周辺

50

回路素子として形成されている。

【0040】

そして、画素領域PAにおいて画素Pに対応するように設けられた複数の画素スイッチング素子を、表示用垂直駆動回路11および表示用水平駆動回路12が線順次に駆動し、画像表示を実行する。そして、これと共に、画素領域PAにおいて画素Pに対応するように設けられた複数の受光素子(図示無し)を、センサ用垂直駆動回路13とセンサ用水平駆動回路14とが線順次に駆動し、受光データを収集する。

【0041】

具体的には、表示用垂直駆動回路11は、y方向において複数の画素Pに対応するように形成された画素スイッチング素子に接続されている。そして、表示用垂直駆動回路11は、供給される制御信号に基づいて、そのy方向に並ぶ複数の画素スイッチング素子に、走査信号を、順次、供給する。ここでは、x方向に並ぶ複数の画素Pに対応して形成された複数の画素スイッチング素子のそれぞれにゲート線(図示無し)が接続され、そのゲート線が垂直方向yに並ぶ複数の画素Pに対応するように複数形成されており、表示用垂直駆動回路11は、その複数のゲート線を順次選択するように、走査信号を供給する。

10

【0042】

表示用水平駆動回路12は、x方向において複数の画素Pに対応するように形成された各画素スイッチング素子(図示無し)に接続されている。そして、表示用水平駆動回路12は、供給される制御信号に基づいて、そのy方向に並ぶ複数の画素スイッチング素子のそれぞれに、映像データ信号を順次供給する。ここでは、垂直方向yに並ぶ複数の画素Pに対応して形成された複数の画素スイッチング素子のそれぞれに信号線(図示無し)が接続され、その信号線が水平方向xに並ぶ複数の画素Pに対応するように複数形成されており、表示用水平駆動回路12は、その複数の信号線に、順次、映像データ信号を供給する。そして、表示用垂直駆動回路11によって走査信号が供給された画素スイッチング素子を介して、その映像データ信号が液晶層203に印加され、画像表示が実行される。

20

【0043】

センサ用垂直駆動回路13は、y方向において複数の画素Pに対応するように形成された複数の受光素子(図示無し)に接続されている。そして、センサ用垂直駆動回路13は、供給される制御信号に基づいて、そのy方向に並ぶ複数の受光素子において、受光データを読み出す受光素子を選択するように走査信号を供給する。ここでは、x方向に並ぶ複数の受光素子のそれぞれに対応するように、ゲート線(図示無し)が設けられ、そのゲート線がy方向に並ぶ複数の受光素子に対応するように複数形成されており、センサ用垂直駆動回路13は、その複数のゲート線を順次選択するように走査信号を供給する。

30

【0044】

センサ用水平駆動回路14は、x方向において複数の画素Pに対応するように形成された複数の受光素子(図示無し)に接続されている。そして、センサ用水平駆動回路14は、供給される制御信号に基づいて、そのy方向に並ぶ複数の受光素子から受光データを、順次、読み出す。ここでは、y方向に並ぶ複数の画素Pに対応して形成された複数の受光素子のそれぞれに、信号線(図示無し)が接続され、その信号線がx方向に並ぶ複数の画素Pに対応するように複数形成されており、センサ用水平駆動回路14は、その複数の信号線を介して受光素子から、順次、受光データを読み出す。具体的には、センサ用垂直駆動回路13によって走査信号が供給され、選択された受光素子から受光データを、順次、読み出す。

40

【0045】

バックライト300は、図1に示すように、液晶パネル200の背面に対面しており、その液晶パネル200の背面に照明光Rを出射する。

【0046】

具体的には、バックライト300は、液晶パネル200を構成するTFTアレイ基板201の側に配置されており、そのTFTアレイ基板201において対向基板202に対面している面に対して反対側の面に、照明光Rを照射する。つまり、バックライト300は

50

、 TFT アレイ基板 201 の側から対向基板 202 の側へ向かうように照明光 R を照明する。

【 0047 】

データ処理部 400 は、図 1 に示すように、制御部 401 と、位置検出部 402 を有する。データ処理部 400 は、コンピュータを含み、プログラムによってコンピュータが各部として動作するように構成されている。

【 0048 】

データ処理部 400 の制御部 401 は、液晶パネル 200 とバックライト 300 との動作を制御するように構成されている。制御部 401 は、液晶パネル 200 に制御信号を供給することによって、液晶パネル 200 に複数設けられた画素スイッチング素子（図示無し）の動作を制御する。たとえば、線順次駆動を実行させる。また、制御部 401 は、外部から供給される駆動信号に基づいて、バックライト 300 に制御信号を供給することによって、バックライト 300 の動作を制御し、バックライト 300 から照明光 R を照射する。このように、制御部 401 は、液晶パネル 200 とバックライト 300 との動作を制御することによって、液晶パネル 200 の画素領域 PA に画像を表示する。

10

【 0049 】

このほかに、制御部 401 は、液晶パネル 200 に制御信号を供給することによって、液晶パネル 200 に位置センサ素子として複数設けられた受光素子（図示無し）の動作を制御し、その受光素子から受光データを収集する。たとえば、線順次駆動を実行させて、複数の受光素子から受光データを順次収集する。

20

【 0050 】

データ処理部 400 の位置検出部 402 は、液晶パネル 200 に複数設けられた受光素子（図示無し）から収集した受光データに基づいて、液晶パネル 200 の正面側において、画素領域 PA にユーザーの指やタッチペンなどの被検知体が接触または近接した位置を検出する。たとえば、受光データの信号強度が基準値よりも大きい座標位置を、被検知体 F が画素領域 PA において接触した座標位置として検出する。

20

【 0051 】

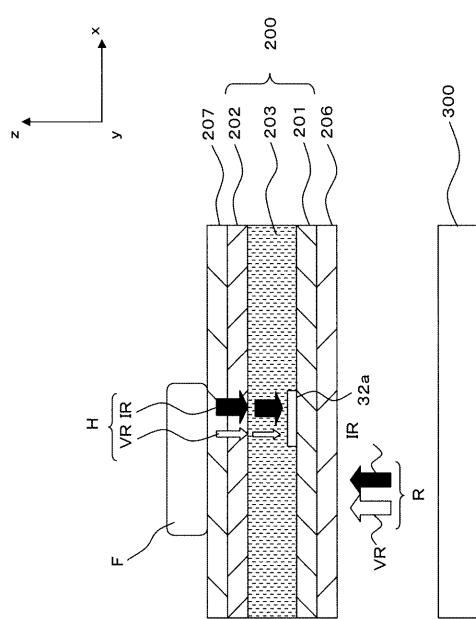

（液晶パネルの画素領域）

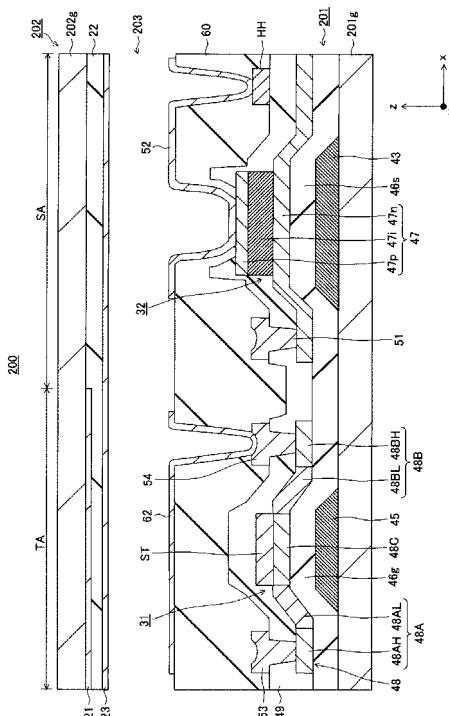

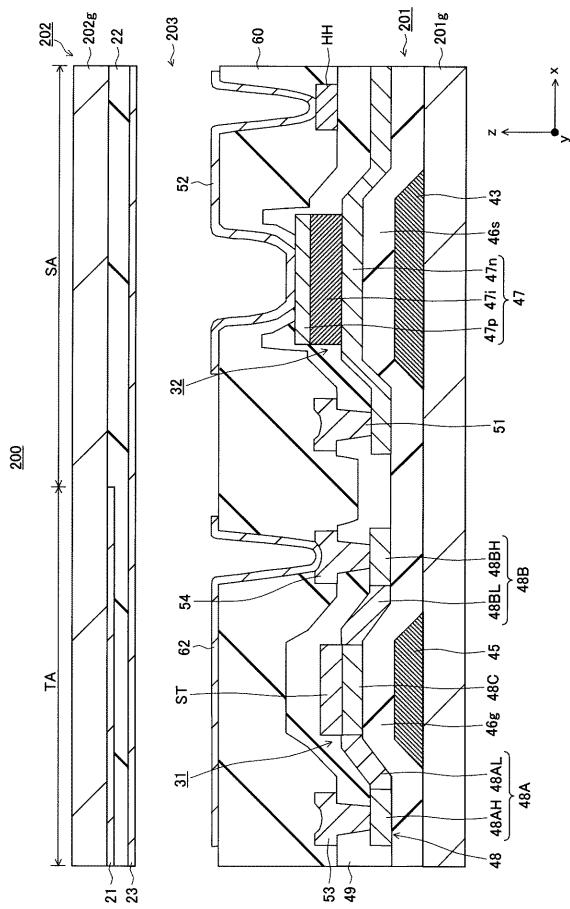

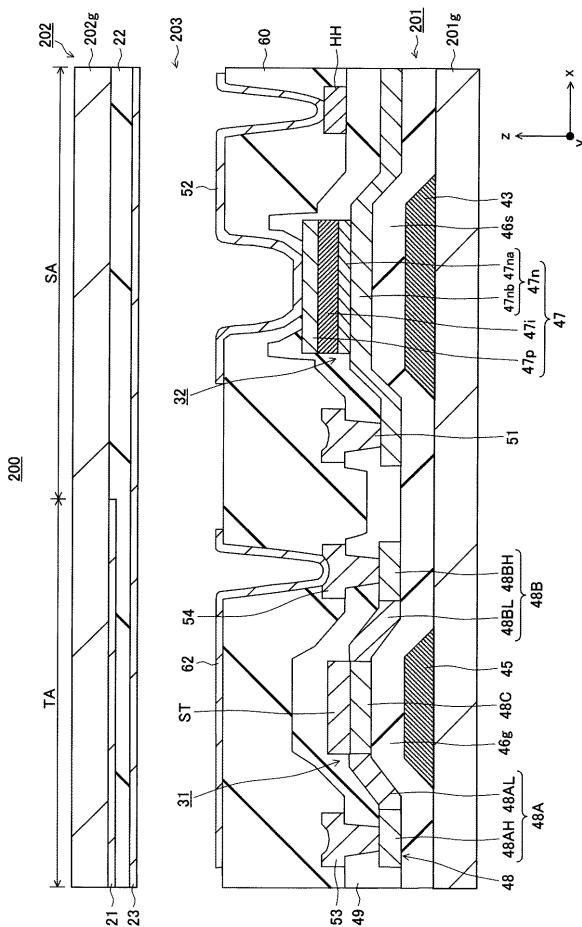

図 3 は、本発明の実施形態 1 において、液晶パネル 200 の画素領域 PA の要部を模式的に示す断面図である。

30

【 0052 】

図 3 に示すように、液晶パネル 200 は、TFT アレイ基板 201 と、対向基板 202 と、液晶層 203 とを有する。この液晶パネル 200 においては、図 3 に示すように、TFT アレイ基板 201 と対向基板 202 とが間隔を隔てられて貼り合わされており、その TFT アレイ基板 201 と対向基板 202 との間の間に、液晶層 203 が設けられている。液晶パネル 200 の各部について順次説明する。

【 0053 】

TFT アレイ基板 201 について説明する。

【 0054 】

TFT アレイ基板 201 は、図 3 に示すように、ガラス基板 201g を含む。ガラス基板 201g は、光を透過する絶縁体の基板であり、ガラスにより形成されている。そして、このガラス基板 201g にて対向基板 202 に對面する側の面には、図 3 に示すように、画素スイッチング素子 31 と、フォトセンサ素子 32 と、画素電極 62 とが形成されている。TFT アレイ基板 201 に設けられた各部について順次説明する。

40

【 0055 】

TFT アレイ基板 201 において画素スイッチング素子 31 は、図 3 に示すように、画素領域 PA の表示領域 TA に形成されている。

【 0056 】

画素スイッチング素子 31 は、図 3 に示すように、ゲート電極 45 と、ゲート絶縁膜 46g と、半導体層 48 とを含み、LDD (Lightly Doped Drain) 構

50

造のボトムゲート型 TFT として形成されている。たとえば、N チャネル型の TFT として形成されている。

【0057】

具体的には、画素スイッチング素子 31 において、ゲート電極 45 は、モリブデン (Mo) などの金属材料を用いて形成されている。ここでは、図 3 に示すように、ゲート電極 45 は、ガラス基板 201g の面において、ゲート絶縁膜 46g を介して、半導体層 48 のチャネル領域 48C に対面するように設けられている。

【0058】

また、画素スイッチング素子 31 において、ゲート絶縁膜 46g は、図 3 に示すように、たとえば、ゲート電極 45 を被覆するように形成されている。ここでは、たとえば、シリコン窒化膜とシリコン酸化膜とを積層することによって形成される。

10

【0059】

また、画素スイッチング素子 31 において、半導体層 48 は、たとえば、ポリシリコンで形成されている。この半導体層 48 においては、図 3 に示すように、ゲート電極 45 に対応するようにチャネル領域 48C が形成されると共に、そのチャネル領域 48C を挟むように一対のソース・ドレイン領域 48A, 48B が形成されている。この一対のソース・ドレイン領域 48A, 48B は、チャネル領域 48C を挟むように一対の低濃度不純物領域 48AL, 48BL が形成され、さらに、その低濃度不純物領域 48AL, 48BL よりも不純物の濃度が高い一対の高濃度不純物領域 48AH, 48BH が、その一対の低濃度不純物領域 48AL, 48BL を挟むように形成されている。

20

【0060】

そして、画素スイッチング素子 31 において、ソース電極 53 とドレイン電極 54 とのそれぞれは、アルミニウムなどの導電材料を用いて形成されている。ここでは、図 3 に示すように、層間絶縁膜 49 が半導体層 48 を被覆するように設けられており、ソース電極 53 は、その層間絶縁膜 49 を貫通するコンタクトホールに導電材料が埋め込まれ、パターン加工されることで、一方のソース・ドレイン領域 48A に電気的に接続するように設けられている。そして、同様に、ドレイン電極 54 は、層間絶縁膜 49 を貫通するコンタクトホールに導電材料が埋め込まれ、パターン加工されることで、他方のソース・ドレイン領域 48B に電気的に接続するように設けられている。

30

【0061】

TFT アレイ基板 201 においてフォトセンサ素子 32 は、図 3 に示すように、画素領域 PA のセンサ領域 TA に形成されている。

【0062】

フォトセンサ素子 32 は、たとえば、フォトダイオードであって、図 3 に示すように、遮光膜 43 と、半導体層 47 とを含む。そして、フォトセンサ素子 32 は、入射する光を受光し、光電変換することによって、受光データを生成し、読み出される。たとえば、逆方向バイアスが印加されることによって、光電流が受光データとして読み出されるように構成されている。

【0063】

具体的には、フォトセンサ素子 32 において、遮光膜 43 は、たとえば、モリブデンなどの金属材料を用いて形成されている。遮光膜 43 は、図 3 に示すように、ガラス基板 201g の面において、絶縁膜 46s を介して、半導体層 47 に対面するように設けられており、ガラス基板 201g において遮光膜 43 が設けられた面の反対側の面の側から半導体層 47 に入射する照明光を遮光する。

40

【0064】

また、フォトセンサ素子 32 において、半導体層 47 は、図 3 に示すように、ガラス基板 201g の面において絶縁膜 46s を介して遮光膜 43 に対面するように設けられている。半導体層 47 は、p 層 47p と n 層 47n と i 層 47i とを含み、PIN 構造になるように構成されており、光電変換を行う。ここでは、p 層 47p は、p 型不純物が高濃度にドープされることによって形成され、n 層 47n は、n 型不純物が高濃度にドープされ

50

ることによって形成され、i層47iは、高抵抗であって、p層47pとn層47nとの間に介在している。

【0065】

本実施形態においては、フォトセンサ素子32の半導体層47は、n層47nとi層47iとp層47pとのそれぞれが、順次、TFTアレイ基板201の面の法線方向zに沿って、積み重なるように設けられている。つまり、光電変換が行われる半導体層47が、液晶パネル200の面の法線方向zにおいて電流が流れる縦型構造になるように、フォトセンサ素子32が構成されている。

【0066】

この半導体層47において、n層47nは、多結晶シリコンで形成されている。ここでは、n層47nは、図3に示すように、i層47iの側面に対応する部分から外側へ延在するように形成されており、その延在した部分の表面には、第1電極51が電気的に接続されている。

10

【0067】

また、半導体層47において、i層47iは、微結晶シリコンで形成されている。つまり、i層47iは、非晶質シリコンと、粒径が100nm以下のシリコン微結晶粒子との混合物によって形成されている。そして、i層47iは、n層47nを介して、遮光膜43に対面するように設けられている。

【0068】

そして、半導体層47において、p層47pは、i層47iと同様に、微結晶シリコンで形成されており、i層47iと同一形状であって、i層47iを介して、n層47nに対面するように設けられている。

20

【0069】

そして、フォトセンサ素子32においては、第1電極51がn層47nに接続するように設けられている。ここでは、第1電極51は、図3に示すように、n層47nがi層47iに対応する部分からガラス基板201gの面方向に延在しており、その延在した部分の表面に形成されている。具体的には、n層47nにおいてi層47iに対応する部分からガラス基板201gの面方向に延在する部分を被覆する層間絶縁膜49に開口を設けた後、その開口を埋めるように、この第1電極51が形成されている。たとえば、この第1電極51は、アルミニウムなどの金属材料を用いて形成されている。

30

【0070】

そして、フォトセンサ素子32においては、第2電極52がp層47pに電気的に接続するように設けられている。ここでは、第2電極52は、図3に示すように、p層47pの上方において、たとえば、ITOなどの透明な導電材料を用いて設けられている。そして、層間絶縁膜49上に設けられた配線HHに接続されている。具体的には、フォトセンサ素子32を被覆するように層間絶縁膜49が設けられると共に、その層間絶縁膜49を被覆するように、絶縁材料によって平坦化膜60が設けられており、その平坦化膜60を貫通するように設けられたコンタクトホールに、上記の透明な導電材料を成膜し、パターン加工することで、この第2電極52が形成されている。

40

【0071】

TFTアレイ基板201において画素電極62は、図3に示すように、平坦化膜60において、表示領域TAに対応するように形成されており、画素スイッチング素子31のドレイン電極54に接続されている。画素電極62は、いわゆる透明電極であって、たとえば、ITOを用いて形成されている。そして、画素電極62は、バックライト300によって照明された光を変調するように、図3に示した対向基板に設けられた対向電極23との間において、液晶層203に電圧を印加する。

【0072】

対向基板202について説明する。

【0073】

対向基板202は、TFTアレイ基板201の場合と同様に、光を透過する絶縁体のガ

50

ラス基板 202g を有しており、図 3 に示すように、TFT アレイ基板 201 に対して間隔を隔てるよう対面している。そして、対向基板 202 においては、図 3 に示すように、カラーフィルタ層 21 と、対向電極 23 とが形成されている。

【0074】

この対向基板 202 においてカラーフィルタ層 21 は、図 3 に示すように、対向基板 202 にて TFT アレイ基板 201 に対面する側の面に形成されている。カラーフィルタ層 21 は、バックライト 300 から出射された照明光が着色されて、TFT アレイ基板 201 の側から対向基板 202 の側へ透過するように構成されている。なお、図 3 においては、図示を省略しているが、カラーフィルタ層 21 は、赤フィルタ層と緑フィルタ層と青フィルタ層とを 1 組として画素 P ごとに設けられており、この赤フィルタ層と緑フィルタ層と青フィルタ層とのそれぞれに対応するように、上述した画素スイッチング素子 31 が設けられている。

10

【0075】

そして、対向基板 202 において対向電極 23 は、図 3 に示すように、対向基板 202 にて TFT アレイ基板 201 に対面する側の面に形成されている。対向電極 23 は、いわゆる透明電極であって、たとえば、ITO を用いて形成されている。ここでは、図 3 に示すように、カラーフィルタ層 21 を被覆するように、平坦化膜 22 が設けられており、その平坦化膜 22 の上に、対向電極 23 がベタ状に全面に設けられている。

20

【0076】

液晶層 203 について示す。

【0077】

液晶層 203 は、図 3 に示すように、TFT アレイ基板 201 と対向基板 202 との間に挟持され、配向処理される。たとえば、液晶層 203 は、TFT アレイ基板 201 と対向基板 202 との間ににおいて、スペーサ (図示なし) により所定の距離が保持された間に、封入されている。そして、液晶層 203 は、TFT アレイ基板 201 および対向基板 202 に形成された液晶配向膜 (図示なし) によって配向されている。たとえば、液晶層 203 は、液晶分子が垂直配向するように形成される。

【0078】

(バックライトの構成)

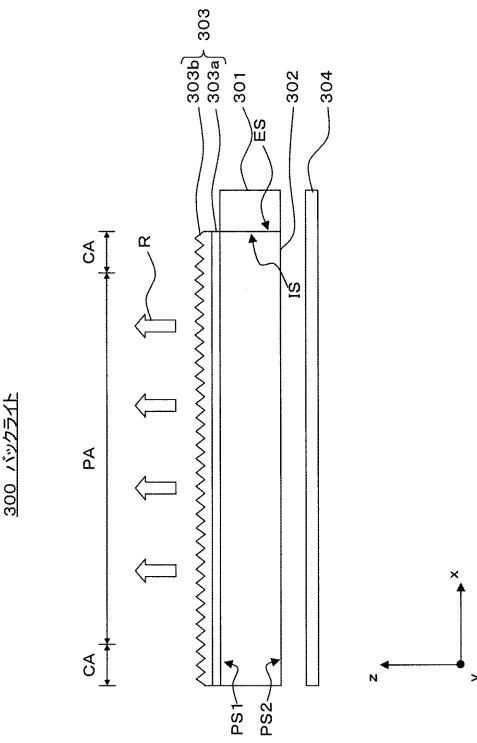

図 4 は、本発明の実施形態 1 において、バックライト 300 を模式的に示す断面図である。図 5 は、本発明の実施形態 1 において、バックライト 300 の要部を模式的に示す斜視図である。

30

【0079】

図 4 に示すように、バックライト 300 は、光源 301 と、導光板 302 とを有しており、液晶パネル 200 の画素領域 PA の全面を照明するように、照明光 R を出射する。

【0080】

光源 301 は、図 4 に示すように、光を照射する照射面 ES を含み、この照射面 ES が、導光板 302 において光が入射される入射面 IS に対面するように配置されている。ここでは、導光板 302 の側面に設けられている入射面 IS に、光源 301 の照射面 ES が対面している。そして、光源 301 は、制御信号が制御部 401 から供給され、その制御信号に基づいて、発光動作を実施するように構成されている。

40

【0081】

本実施形態においては、光源 301 は、図 5 に示すように、可視光源 301a と、赤外光源 301b とを有する。

【0082】

可視光源 301a は、たとえば、白色 LED であり、白色の可視光線を照射するように構成されている。この可視光源 301a は、図 5 に示すように、導光板 302 の入射面 IS に照射面 ES が対面するように配置されており、その導光板 302 の入射面 IS に照射面 ES から可視光線を照射する。ここでは、可視光源 301a は、複数であり、その複数が、導光板 302 の入射面 IS に沿うように並べられて配置されている。

50

## 【0083】

赤外光源301bは、たとえば、赤外線LEDであり、赤外光線を照射するように構成されている。この赤外光源301bは、図5に示すように、導光板302の入射面ISに照射面ESが対面するように配置されており、その導光板302の入射面ISに照射面ESから赤外光線を照射する。たとえば、中心波長が850nmである赤外光線を照射する。ここでは、赤外光源301bは、たとえば、単数であり、可視光源301aが設けられた導光板302の入射面ISにおいて、その可視光源301aと並ぶように配置されている。本実施形態においては、図5に示すように、赤外光源301bは、可視光源301aが設けられた導光板302の入射面ISにおいて、略中央部分になるように配置されている。

10

## 【0084】

導光板302は、図4に示すように、入射面ISに光源301の照射面ESが対面するように設けられており、その照射面ESから照射された光が入射される。そして、導光板302は、その入射面ISに入射された光を導光する。そして、その導光した光を、入射面ISに対して直交するように設けられた出射面PS1から照明光Rとして出射する。導光板302は、液晶パネル200の背面に対面するように配置され、その液晶パネル200の背面に向かって、出射面PS1から照明光Rを出射する。この導光板302は、たとえば、アクリル樹脂など、光透過性が高い透明な材料を用いて、射出成型により形成される。

20

## 【0085】

本実施形態においては、導光板302は、可視光源301aから出射された可視光線と、赤外光源301bから出射された赤外光線との両者が、入射面ISに入射され、その入射面ISから入射された可視光線と赤外光線とを導光する。そして、その導光した可視光線と赤外光線とが、出射面PS1から照明光Rとして出射される。そして、上記のように、透過型の液晶パネル200の画素領域PAにおいて画像が表示される。

## 【0086】

導光板302は、図4に示すように、光学フィルム303と反射フィルム304とが設けられている。

## 【0087】

光学フィルム303は、図4に示すように、導光板302において出射面PS1に対面するように設けられている。光学フィルム303は、導光板302の出射面PS1から出射される照明光Rを受け、その光学特性を変調するように構成されている。

30

## 【0088】

本実施形態においては、光学フィルム303は、拡散シート303aとプリズムシート303bとを有しており、拡散シート303aとプリズムシート303bとが導光板302の側から順次配置されている。そして、拡散シート303aは、導光板302の出射面PSから出射される光を拡散し、プリズムシート303bは、その拡散された光を導光板302の出射面PSの法線方向zに沿うように集光する。このようにすることで、光学フィルム303は、導光板302から出射された光を、平面光の照明光Rとして液晶パネル200の裏面へ出射する。

40

## 【0089】

反射フィルム304は、図4に示すように、導光板302において出射面PSにに対して反対側に位置する面に対面するように設けられている。反射フィルム304は、導光板302において出射面PS1にに対して反対側に位置する面PS2から出射される光を受けて、導光板302の出射面PS1の側へ、その光を反射する。

## 【0090】

## (動作)

以下より、上記の液晶表示装置100において、ユーザーの指などの被検知体が液晶パネル200の画素領域PAに接触もしくは移動された位置を検出する際の動作について説明する。

50

## 【0091】

図6は、本発明の実施形態1において、被検知体が液晶パネル200の画素領域PAに接触もしくは移動された位置を検出する際の様子を模式的に示す断面図である。図6においては、要部を記載し、その他の部分については、記載を省略している。

## 【0092】

液晶表示装置100が白表示をしている際において、ユーザーの指などの被検知体Fが画素領域PAに接触もしくは移動されたときには、図6に示すように、バックライト300から照明された照明光Rが、液晶パネル200を介して第2の偏光板207を透過し、その被検知体Fによって、反射される。そして、その反射された反射光Hが、液晶パネル200に形成されたフォトセンサ素子32によって受光される。

10

## 【0093】

ここでは、上述したように、バックライト300が可視光線VRと赤外光線IRとを含む照明光Rを、平面光として、液晶パネル200の背面に照射する。そして、その照明光Rは、液晶パネル200を介して、被検知体Fに照射され、被検知体Fによって反射される。そして、その被検知体Fによって反射された反射光Hを、フォトセンサ素子32が受光する。

## 【0094】

このとき、照明光Rにおいて可視光線VRは、液晶パネル200などの各部において吸収され、その強度が低下した状態で、フォトセンサ素子32によって受光される。これに20 対して、照明光Rにおいて赤外光線IRは、液晶パネル200の各部において吸収される割合が可視光線VRよりも小さいため、可視光線VRよりも大きな強度で、フォトセンサ素子32によって受光される。

20

## 【0095】

そして、その受光した光の強度に応じた信号強度の受光データをフォトセンサ素子32が生成する。その後、周辺回路によって受光データが読み出され、その受光データが読み出されたフォトセンサ素子32の位置と、そのフォトセンサ素子32から読み出された受光データの信号強度とのそれぞれに基づいて、被検知体Fが画素領域PAにおいて接触した位置が、位置検出部402によって検出される。

## 【0096】

一方で、液晶表示装置100が黒表示をしている際には、バックライト300から照明された照明光Rに含まれる可視光線VRは、液晶パネル200を介して第2の偏光板207を透過しないが、その照明光Rに含まれる赤外光線IRは、第2の偏光板207を透過する。このため、白表示の場合と同様に、赤外光線IRをフォトセンサ素子32が受光可能であるため、被検知体Fが画素領域PAにおいて接触した位置が、位置検出部402によって検出される。

30

## 【0097】

## (製造方法)

上記の液晶パネル200を製造する製造方法について、以下より、説明する。

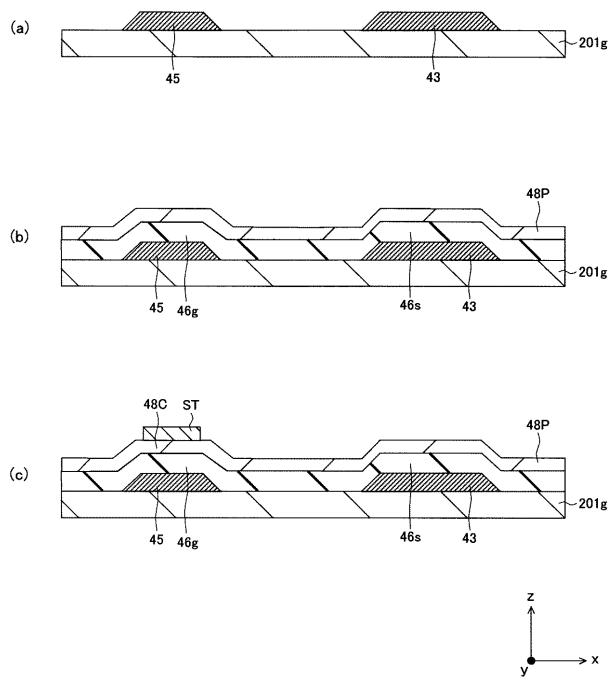

## 【0098】

図7と図8と図9とのそれぞれは、本発明にかかる実施形態1において、液晶パネル200について製造する際の製造工程の要部を示す断面図である。図7と図8と図9においては、本実施形態の液晶パネル200を製造する際に、TFTアレイ基板201を製造する製造工程について、(a), (b), (c), (d), (e), (f), (g), (h), (i)の順で示している。

40

## 【0099】

まず、図7(a)に示すように、画素スイッチング素子31のゲート電極45と、フォトセンサ素子32の遮光膜43とを形成する。

## 【0100】

ここでは、ガラス基板201g上に、たとえば、厚さが50~100nmのモリブデン膜(図示なし)を、マグнетロン・スパッタ法で成膜した後に、フォトリソグラフィーお

50

および反応性イオンエッティングで、そのモリブデン膜をパターン加工することによって、図7(a)に示すように、画素スイッチング素子31のゲート電極45と、フォトセンサ素子32の遮光膜43とを形成する。

#### 【0101】

なお、必要に応じて、ガラス基板201gの表面に、予めSiNxやSiO<sub>2</sub>などの絶縁膜を、熱緩衝層として形成し、その上に、上記のように、ゲート電極45と遮光膜43とを形成してもよい。たとえば、厚さ100nmのSiNxと、厚さ200nmのSiO<sub>2</sub>とを、プラズマCVD法によって形成し、この熱緩衝層を形成することができる。

#### 【0102】

つぎに、図7(b)に示すように、画素スイッチング素子31のゲート絶縁膜46gと、フォトセンサ素子32の絶縁膜46sとを形成後、その画素スイッチング素子31のゲート絶縁膜46gと、フォトセンサ素子32の絶縁膜46sとを被覆するように、ポリシリコン膜48pを形成する。

#### 【0103】

ここでは、たとえば、SiNx膜(図示無し)と、SiO<sub>2</sub>膜(図示無し)とを、画素スイッチング素子31のゲート電極45およびフォトセンサ素子32の遮光膜43を被覆するように、順次、ガラス基板201gの表面に設けて、画素スイッチング素子31のゲート絶縁膜46gと、フォトセンサ素子32の絶縁膜46sとを形成する。たとえば、プラズマCVD法によって、厚さが25~50nmのSiNx膜と、厚さ30~50nmのSiO<sub>2</sub>膜とを、順次、ガラス基板201gの表面に堆積させる。

#### 【0104】

そして、これに続いて、原料ガスの切り替えを行い、上記の画素スイッチング素子31のゲート絶縁膜46gと、フォトセンサ素子32の絶縁膜46sとを被覆するように、非晶質シリコン膜(図示なし)を成膜する。たとえば、プラズマCVD法によって、膜厚が約30~60nmになるように、この非晶質シリコン膜を成膜する。

#### 【0105】

この後、非晶質シリコン膜について、脱水素アニール処理を行う。具体的には、窒素雰囲気の下、温度が400の炉において、1~3時間程度、熱処理を実施することによって、上記の非晶質シリコン膜AMの膜中の水素量を、0.1~2原子数%程度まで低減させる。

#### 【0106】

そして、つぎに、エキシマ・レーザ・アニール(ELA)を行い、その非晶質シリコン膜をポリシリコン膜48pに転換する。具体的には、波長が308nmであるエキシマレーザを、非晶質シリコン膜に照射することによって、その非晶質シリコン膜をポリシリコン膜48pに転換する。

#### 【0107】

そして、さらに、TFTである画素スイッチング素子31の閾電圧Vthを制御するために、上記のポリシリコン膜48pに対して、イオンインプランテーションを必要に応じて行う。たとえば、B<sup>+</sup>イオンをドーパントとし、10keVの加速エネルギーでドーズ量 $1 \times 10^{11} \sim 1 \times 10^{12} / \text{cm}^2$ 程度になるように、ポリシリコン膜48pにイオン注入する。

#### 【0108】

つぎに、図7(c)に示すように、ストップ層STを形成する。

#### 【0109】

ここでは、ポリシリコン膜48pを被覆するように、SiO<sub>2</sub>層(図示なし)を成膜した後、そのSiO<sub>2</sub>層についてパターン加工することで、ゲート電極45に整合するよう、ストップ層STを形成する。

#### 【0110】

具体的には、まず、プラズマCVD法によって、約10~200nmの厚みになるように、SiO<sub>2</sub>膜を成膜する。たとえば、シランガスSiH<sub>4</sub>と亜酸化窒素ガスN<sub>2</sub>Oとを

10

20

30

40

50

プラズマ分解させることで、このSiO<sub>2</sub>膜を堆積させる。そして、このSiO<sub>2</sub>膜を、フォトリソグラフィーおよび反応性イオンエッティングによって、所定の形状にパターンングし、ストップ膜STに加工する。たとえば、裏面露光技術によって、ゲート電極45と自己整合するように、このストップ膜STを形成する。

【0111】

なお、ポリシリコン膜48pにおいて、ストップ膜STの直下に位置する部分は、チャネル領域48Cとして、ストップ層STによって保護されており、このチャネル領域48Cには、前述したように、予め閾値を制御するために実施されたイオンインプランテーションにより、B<sup>+</sup>イオンが、比較的、低ドーザ量で注入されている。

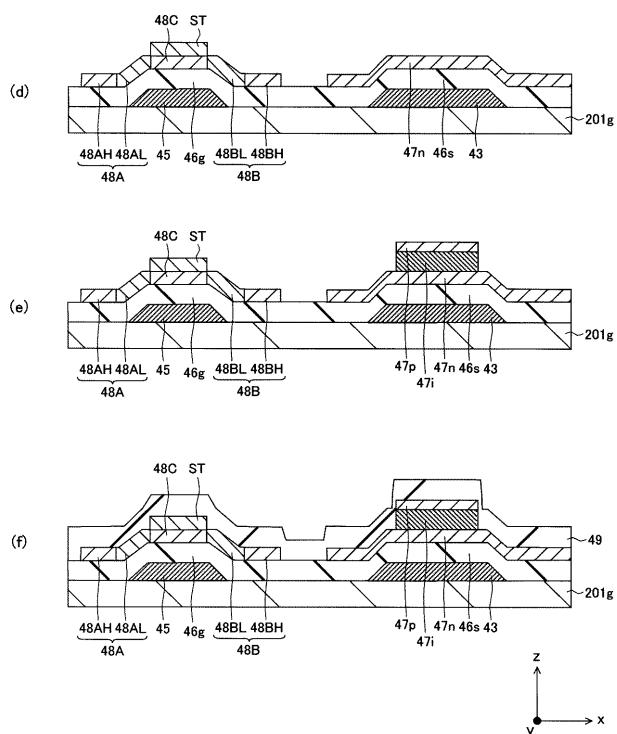

【0112】

つぎに、図8(d)に示すように、画素スイッチング素子31のソース・ドレイン領域48A, 48Bと、フォトセンサ素子32のn層47nを形成する。

【0113】

ここでは、上記のストップ膜STをマスクとして、ポリシリコン膜48pにおいて、ソース・ドレイン領域48A, 48Bの低濃度不純物領域48AL, 48BLを形成する部分に、たとえば、P<sup>+</sup>イオンを注入する。たとえば、 $5 \times 10^{12} \sim 1 \times 10^{13} / \text{cm}^2$ のドーザ量であって、たとえば、10keVの加速エネルギーの条件において、このイオン注入を実施する。

【0114】

この後、ストップ膜STと、低濃度不純物領域48AL, 48BLとを被覆するようにフォトレジストマスク(図示なし)をパターン加工して形成する。そして、そのフォトレジストマスクをマスクとして、たとえば、P<sup>+</sup>イオンなどのn型不純物を、ポリシリコン膜48pに注入する。ここでは、ポリシリコン膜48pにおいて、高濃度不純物領域48AH, 48BHと、n層47nとを形成する部分に、P<sup>+</sup>イオンなどのn型不純物を注入する。このイオン注入においては、たとえば、イオンシャワーにて実施することができる。具体的には、質量分離をかける事なく、電界加速によって、不純物イオンを注入する。たとえば、 $1 \times 10^{15} / \text{cm}^2$ 程度のドーザ量であって、加速エネルギーが、10keVの条件にて、このイオン注入を実施する。

【0115】

そして、紫外線ランプを用いて、RTA(急速熱アニール)処理を実施することで、上記にてポリシリコン膜48pに注入された不純物イオンを活性化する。

【0116】

その後、フォトリソグラフィーと反応性イオンエッティングによって、ポリシリコン膜48pをパターン加工することで、画素スイッチング素子31のソース・ドレイン領域48A, 48Bと、フォトセンサ素子32のn層47nを形成する

【0117】

つぎに、図8(e)に示すように、フォトセンサ素子32のi層47iと、p層47pとを形成する。

【0118】

ここでは、たとえば、微結晶シリコン膜(図示なし)と、ボロンがドープされた微結晶シリコン膜(図示なし)とを順次成膜する。

【0119】

具体的には、プラズマCVD法によって、厚さが約40~2000nmになるように、この微結晶シリコン膜(図示なし)を成膜する。ここでは、シランガスSiH<sub>4</sub>と水素との混合ガスを用いることで、この微結晶シリコン膜(図示なし)を形成する。

【0120】

そして、プラズマCVD法によって、厚さが約5~30nmになるように、ボロンがドープされた微結晶シリコン膜(図示なし)を成膜する。ここでは、ジボランB<sub>2</sub>H<sub>6</sub>ガスを濃度が0.1~3%程度になるように水素希釈した混合ガスを用いた。つまり、ジボランB<sub>2</sub>H<sub>6</sub>ガスのシランガスSiH<sub>4</sub>に対する流量比を、0.1~3%として、ボロンが

10

20

30

40

50

ドープされた微結晶シリコン膜（図示なし）を成膜する。

【0121】

その後、フォトリソグラフィーおよび反応性イオンエッティングによって、上記の微結晶シリコン膜（図示なし）と、ボロンイオンがドープされた微結晶シリコン膜（図示なし）とをパターン加工し、フォトセンサ素子32のi層47iと、p層47pとを形成する。

【0122】

つぎに、図8（f）に示すように、層間絶縁膜49を形成する。

【0123】

ここでは、上記にて形成した各層を被覆するように、層間絶縁膜49を形成する。具体的には、プラズマCVD法によって、SiO<sub>2</sub>膜とSiN<sub>x</sub>膜とを、順次、連続して成膜し、層間絶縁膜49とする。たとえば、SiO<sub>2</sub>膜を厚さが約100nm～200nmになるように成膜後、SiN<sub>x</sub>膜を厚さが約200nm～400nmになるように成膜する。

10

【0124】

その後、層間絶縁膜49に含まれる水素原子を、上記の半導体膜中に拡散させる水素化アニール処理を実施する。たとえば、窒素ガス、または、フォーミングガス中、または、真空中雰囲気下において、250～400程度の温度で、加熱処理を、1～3時間、実施することで、この水素化アニールを実施する。

【0125】

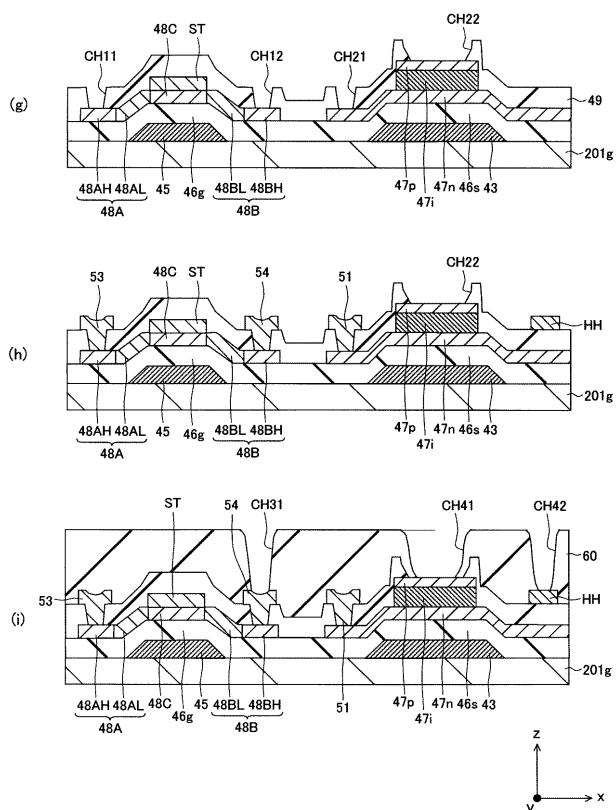

つぎに、図9（g）に示すように、コンタクトホールCH11, CH12, CH21, CH22を形成する。

20

【0126】

ここでは、フォトリソグラフィーと反応性イオンエッティングにより、層間絶縁膜49にコンタクトホールCH11, CH12, CH21, CH22を形成する。具体的には、高濃度不純物領域48AH, 48BHの各表面が露出するように、コンタクトホールCH11, CH12を形成する。また、n層47nおよびp層47bの表面が露出するように、コンタクトホールCH21, CH22を形成する。

【0127】

つぎに、図9（h）に示すように、ソース電極53とドレイン電極54と第1電極51と配線HHとを形成する。

30

【0128】

ここでは、コンタクトホールCH11, CH12, CH21を埋めるように、たとえば、A1などの導電材料を、スパッタリング法によって、堆積し、導電膜（図示なし）を成膜する。たとえば、100nm～1μmの厚みになるように、この導電膜を成膜する。

【0129】

その後、フォトリソグラフィーと反応性イオンエッティングによって、その導電膜をパターン加工することによって、ソース電極53とドレイン電極54と第1電極51と配線HHとを形成する。

【0130】

つぎに、図9（i）に示すように、平坦化膜60を形成後に、その平坦化膜60にコンタクトホールCH31, CH41, CH42を形成する。

40

【0131】

ここでは、上記にて形成した各層を被覆するように、平坦化膜60を形成する。具体的には、感光性のアクリル樹脂などの感光性樹脂を、厚みが1～3μm程度になるように成膜することで、この平坦化膜60を形成する。

【0132】

その後、フォトリソグラフィーによって、ドレイン電極54とp層47pと配線HHとのそれぞれの表面を露出するように、この平坦化膜60にコンタクトホールCH31, CH41, CH42を形成する。そして、120～200程度の温度で焼成する。

【0133】

50

つぎに、図3に示すように、画素電極62と、第2電極52とを形成する。

【0134】

ここでは、たとえば、酸化インジウム錫 ( $In_2O_3 + SnO_2$ 、以下、ITO) などからなる透明導電膜(図示なし)を、平坦化層60上に形成後、その透明導電膜をパターン加工することで、画素電極62と、第2電極52とを形成する。なお、駆動回路部のトランジスタについては、画素電極を形成しない。また、反射型にする際には、AgまたはAlなどからなる反射電極を、画素電極として形成する。

【0135】

そして、上記のように画素電極62などの各部が形成されたTFTアレイ基板201と、対向電極23などの各部が形成された対向基板202とを、画素電極62と対向電極23とが対向するように貼り合わせる。ここでは、貼り合わせるに当たり、TFTアレイ基板201と対向基板202とのそれぞれに、たとえば、ポリイミドで配向膜を形成した後に、その配向膜をラビング処理する。そして、TFTアレイ基板201と対向基板202とを、間隔を隔てて対面するように貼り合わせる。その後、そのTFTアレイ基板201と対向基板202との間の間隔に液晶を注入し、液晶層203を配向させて液晶パネル200を形成する。

【0136】

その後、偏光板、バックライトなどの周辺機器を実装して液晶表示装置100を完成する。

【0137】

以上のように、本実施形態の液晶表示装置100は、画素領域PAに画素Pが配置された液晶パネル200を含み、その液晶パネル200に入射する光を受光するフォトセンサ素子32が液晶パネル200に設けられている。ここでは、そのフォトセンサ素子32は、n層47nとp層47pとi層47iとを含み、n層47nとp層47pとがi層47iを挟むように設けられているフォトダイオードであって、n層47nとi層47iとp層47pとのそれぞれが、液晶パネル200の面の法線方向zにおいて、順次、積層されている。つまり、フォトセンサ素子32は、液晶パネル200の面の法線方向zにおいて電流が流れる縦型構造になるように形成されている。そして、さらに、本実施形態においては、i層47iは、ポリシリコンよりも光吸収係数が高い微結晶シリコンによって形成されている。このため、本実施形態においては、赤外線のように、長波長の光に対するフォトセンサ素子32の感度を、高感度化することができる。

【0138】

したがって、本実施形態は、フォトセンサ素子32が、高感度に受光データを生成することができるので、位置検出感度を向上させることができる。特に、本実施形態のように、フォトセンサ素子32が赤外線を受光して受光データを生成する場合には、効果的である。

【0139】

また、本実施形態においては、画素領域PAにおいて画素Pをスイッチングする画素スイッチング素子31は、チャネル領域48Cが形成された半導体層48を有する薄膜トランジスタであり、フォトセンサ素子32は、n層47nが画素スイッチング素子31の半導体層47と同じ半導体層をパターン加工することで形成されている。このため、本実施形態は、高い製造効率にて、液晶パネル200を製造することができる。

【0140】

<実施形態2>

以下より、本発明の実施形態2について説明する。

【0141】

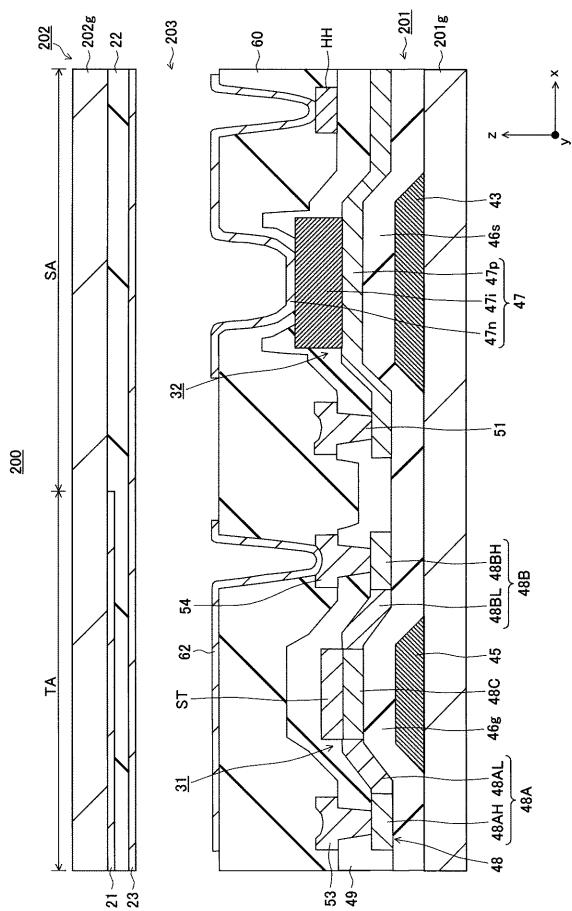

図10は、本発明の実施形態2において、液晶パネル200の画素領域PAの要部を模式的に示す断面図である。

【0142】

本実施形態においては、図10に示すように、フォトセンサ素子32の構成が実施形態

10

20

30

40

50

1と異なる。この点を除き、本実施形態は、実施形態1と同様である。このため、重複する個所については、説明を省略する。

【0143】

本実施形態のフォトセンサ素子32においては、n層47nは、高抵抗層47naと、低抵抗層47nbとを含む。

【0144】

n層47nにおいて高抵抗層47naは、図10に示すように、低抵抗層47nbを介して、遮光膜43に対面するように設けられている。つまり、高抵抗層47naは、i層47iと低抵抗層47nbとの間に介在するように設けられている、ここでは、高抵抗層47naは、i層47iと同様に形成されている。たとえば、高抵抗層47naは、プラズマCVD法によって、リンがドープされた微結晶シリコン膜(図示なし)を、パターン加工することで形成される。

10

【0145】

n層47nにおいて低抵抗層47nbは、高抵抗層47naよりも抵抗率が低くなる材料で形成されている。具体的には、低抵抗層47nbは、高抵抗層47naよりもドーピング効率が高い、レーザ結晶化による多結晶シリコン薄膜を用いている。ここでは、低抵抗層47nbは、実施形態1のn層47nと同様にして形成されている。つまり、低抵抗層47nbは、多結晶シリコンで形成されており、図10に示すように、i層47iの側面に対応する部分から外側へ延在するように形成されており、その延在した部分の表面には、第1電極51が電気的に接続されている。

20

【0146】

以上のように、本実施形態は、実施形態1と同様に、縦型構造になるようにフォトセンサ素子32を形成すると共に、i層47iを微結晶シリコン半導体によって形成している。このため、本実施形態においては、実施形態1と同様に、フォトセンサ素子32の感度を、高感度化することができる。

【0147】

<実施形態3>

以下より、本発明にかかる実施形態3について説明する。

【0148】

図11は、本発明の実施形態3において、液晶パネル200の画素領域PAの要部を模式的に示す断面図である。

30

【0149】

本実施形態においては、図11に示すように、フォトセンサ素子32の構成が実施形態1と異なる。この点を除き、本実施形態は、実施形態1と同様である。このため、重複する個所については、説明を省略する。

【0150】

本実施形態においては、フォトセンサ素子32の半導体層47は、実施形態1と同様に、n層47nとi層47iとp層47pとが積層されており、光電変換が行われる半導体層47が、液晶パネル200の面の法線方向zにおいて電流が流れる縦型構造になるように、構成されている。しかし、半導体層47は、実施形態1と異なり、p層47p、i層47iとn層47nとが、順次、TFTアレイ基板201のガラス基板201gの側から設けられている。

40

【0151】

また、半導体層47において、n層47nは、実施形態1の第2電極52と同様に、ITO、ZnOなどの透明な材料を用いて設けられている。つまり、i層47iおよび配線HHの表面が露出するように平坦化膜60を貫通させて設けられてコンタクトホールに、上記の透明な導電材料を成膜し、パターン加工することで、このn層47nが形成されている。

【0152】

以上のように、本実施形態は、実施形態1と同様に、縦型構造になるようにフォトセン

50

サ素子 3 2 を形成すると共に、 i 層 4 7 i を微結晶シリコン半導体によって形成している。このため、本実施形態においては、実施形態 1 と同様に、フォトセンサ素子 3 2 の感度を、高感度化することができる。

【 0 1 5 3 】

なお、本発明の実施に際しては、上記した実施の形態に限定されるものではなく、種々の変形形態を採用することができる。

【 0 1 5 4 】

たとえば、上記の実施形態においては、画素スイッチング素子 3 1 を、ボトムゲート型の薄膜トランジスタとして構成する場合について説明したが、これに限定されない。たとえば、トップゲート型の TFT を、画素スイッチング素子 3 1 として形成してもよい。

10

【 0 1 5 5 】

また、上記の実施形態においては、複数の画素 P に対応するように複数のフォトセンサ素子 3 2 を設ける場合について示したが、これに限定されない。たとえば、複数の画素 P に対して 1 つのフォトセンサ素子 3 2 を設けてもよく、逆に、1 つの画素 P に対して複数のフォトセンサ素子 3 2 を設けてもよい。

【 0 1 5 6 】

また、IPS ( I n - P l a n e - S w i t c h i n g ) 、 FFS ( F i e l d F r i n g e S w i t c h i n g ) 方式など、さまざまな方式の液晶パネルに適用可能である。さらに、有機 EL 表示素子、電子ペーパーなどの他の表示装置においても、適用可能である。

20

【 0 1 5 7 】

また、上記の実施形態においては、多結晶半導体または微結晶半導体によって、 n 層 4 7 n または p 層 4 7 p を形成する場合について説明したが、これに限定されない。たとえば、非晶質シリコンのような非晶質半導体によって、 n 層 4 7 n または p 層 4 7 p を形成してもよい。

【 0 1 5 8 】

また、上記の実施形態においては、シリコン半導体を用いてフォトセンサ素子 3 2 を形成する場合について説明したが、これに限定されない。たとえば、プラズマ C V D の際に原料ガスにメタン C H<sub>4</sub> やアセチレンガス C<sub>2</sub> H<sub>2</sub> 、エタンガス C<sub>2</sub> H<sub>6</sub> を添加することで、非晶質シリコンカーバイド a - S i<sub>1-x</sub> C<sub>x</sub> : H ( ここで x は炭素組成比 ) を形成し、その非晶質シリコンカーバイド a - S i<sub>1-x</sub> C<sub>x</sub> : H を用いてフォトセンサ素子 3 2 を構成しても良い。具体的には、縦型構造のフォトセンサ素子 3 2 を構成する p 層 4 7 p と n 層 4 7 n において、ガラス基板 2 0 1 g から離れた方の層について、非晶質シリコンカーバイド a - S i<sub>1-x</sub> C<sub>x</sub> : H を用いて形成することが好適である。ここでは、光学的バンドギャップを、1.9 ~ 2.3 eV 程度まで広げることで、 p 層 4 7 p と n 層 4 7 n においてガラス基板 2 0 1 g から離れた方の層によって光が吸収される量を減少させることができるため、フォトセンサ素子 3 2 の感度を、より高感度にすることができます。

30

【 0 1 5 9 】

また、上記の実施形態においては、赤外光線を含むように照明光を照射する場合について説明したが、これに限定されない。たとえば、赤外光線を含まずに、可視光線のみを含む照明光を照射する場合においても、適用可能である。なお、この場合において、赤外光線でなく、可視光線をフォトセンサ素子が受光する際には、たとえば、非晶質シリコンを用いて、 i 層を形成することが好適である。

40

【 0 1 6 0 】

また、本実施形態の液晶表示装置 1 0 0 は、さまざまな電子機器の部品として適用することができる。

【 0 1 6 1 】

図 1 2 から図 1 6 は、本発明の実施形態において、液晶表示装置 1 0 0 を適用した電子機器を示す図である。

50

## 【0162】

図12に示すように、テレビジョン放送を受信し表示するテレビにおいて、その受信した画像を表示画面に表示すると共に、オペレータの操作指令が入力される表示装置として液晶表示装置100を適用することができる。

## 【0163】

また、図13に示すように、デジタルスチルカメラにおいて、その撮像画像などの画像を表示画面に表示すると共に、オペレータの操作指令が入力される表示装置として液晶表示装置100を適用することができる。

## 【0164】

また、図14に示すように、ノート型パーソナルコンピュータにおいて、操作画像などを表示画面に表示すると共に、オペレータの操作指令が入力される表示装置として液晶表示装置100を適用することができる。

10

## 【0165】

また、図15に示すように、携帯電話端末において、操作画像などを表示画面に表示すると共に、オペレータの操作指令が入力される表示装置として液晶表示装置100を適用することができる。

## 【0166】

また、図16に示すように、ビデオカメラにおいて、操作画像などを表示画面に表示すると共に、オペレータの操作指令が入力される表示装置として液晶表示装置100を適用することができる。

20

## 【0167】

なお、上記の実施形態において、液晶表示装置100は、本発明の表示装置に相当する。

また、上記の実施形態において、画素スイッチング素子31は、本発明の画素スイッチング素子に相当する。また、上記の実施形態において、フォトセンサ素子32は、本発明のフォトセンサ素子に相当する。また、上記の実施形態において、n層47nは、本発明の第1導電型半導体層、第2導電型半導体層に相当する。また、上記の実施形態において、高抵抗層47naは、本発明の高抵抗層に相当する。また、上記の実施形態において、低抵抗層47nbは、本発明の低抵抗層に相当する。また、上記の実施形態において、p層47pは、本発明の第1導電型半導体層、第2導電型半導体層に相当する。また、上記の実施形態において、i層47iは、本発明の真性半導体層に相当する。また、上記の実施形態において、半導体層48は、本発明の半導体層に相当する。また、上記の実施形態において、液晶パネル200は、本発明の表示パネルに相当する。また、上記の実施形態において、TFTアレイ基板201は、本発明の第1基板に相当する。また、上記の実施形態において、対向基板202は、本発明の第2基板に相当する。また、上記の実施形態において、液晶層203は、本発明の液晶層に相当する。また、上記の実施形態において、バックライト300は、本発明の照明部に相当する。また、上記の実施形態において、画素Pは、本発明の画素に相当する。また、上記の実施形態において、画素領域PAは、本発明の画素領域に相当する。

30

## 【図面の簡単な説明】

40

## 【0168】

【図1】図1は、本発明の実施形態1において、液晶表示装置100の構成を示す断面図である。

【図2】図2は、本発明の実施形態1において、液晶パネル200を示す平面図である。

【図3】図3は、本発明の実施形態1において、液晶パネル200の画素領域PAの要部を模式的に示す断面図である。

【図4】図4は、本発明の実施形態1において、バックライト300を模式的に示す断面図である。

【図5】図5は、本発明の実施形態1において、バックライト300の要部を模式的に示す斜視図である。

50

【図 6】図 6 は、本発明の実施形態 1 において、被検知体が液晶パネル 200 の画素領域 PA に接触もしくは移動された位置を検出する際の様子を模式的に示す断面図である。

【図 7】図 7 は、本発明にかかる実施形態 1 において、液晶パネル 200 について製造する際の製造工程の要部を示す断面図である。

【図 8】図 8 は、本発明にかかる実施形態 1 において、液晶パネル 200 について製造する際の製造工程の要部を示す断面図である。

【図 9】図 9 は、本発明にかかる実施形態 1 において、液晶パネル 200 について製造する際の製造工程の要部を示す断面図である。

【図 10】図 10 は、本発明の実施形態 2 において、液晶パネル 200 の画素領域 PA の要部を模式的に示す断面図である。

【図 11】図 11 は、本発明の実施形態 3 において、液晶パネル 200 の画素領域 PA の要部を模式的に示す断面図である。

【図 12】図 12 は、本発明の実施形態において、液晶表示装置 100 を適用した電子機器を示す図である。

【図 13】図 13 は、本発明の実施形態において、液晶表示装置 100 を適用した電子機器を示す図である。

【図 14】図 14 は、本発明の実施形態において、液晶表示装置 100 を適用した電子機器を示す図である。

【図 15】図 15 は、本発明の実施形態において、液晶表示装置 100 を適用した電子機器を示す図である。

【図 16】図 16 は、本発明の実施形態において、液晶表示装置 100 を適用した電子機器を示す図である。

【符号の説明】

【0169】

32：フォトセンサ素子（フォトセンサ素子）、47n：n層（第1導電型半導体層、第2導電型半導体層）、47p：p層（第1導電型半導体層、第2導電型半導体層）、47i：i層（真性半導体層）、31：画素スイッチング素子、48：半導体層、47na：高抵抗層、47nb：低抵抗層、200：液晶パネル（表示パネル）、201：TFTアレイ基板（第1基板）、202：対向基板（第2基板）、203：液晶層、300：バックライト（照明部）、PA：画素領域、P：画素

10

20

30

【 図 1 】

【 図 2 】

【図3】

〔 四 4 〕

【図5】

【図6】

【図7】

【図8】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図14】

【図15】

【図16】

## フロントページの続き

| (51) Int.CI.                     | F I             | テーマコード(参考) |

|----------------------------------|-----------------|------------|

| <b>C 2 3 C 16/24 (2006.01)</b>   | C 2 3 C 16/24   | 5 F 0 4 5  |

| <b>C 2 3 C 16/42 (2006.01)</b>   | C 2 3 C 16/42   | 5 F 0 4 9  |

| <b>G 0 2 F 1/135 (2006.01)</b>   | G 0 2 F 1/135   | 5 G 4 3 5  |

| <b>G 0 9 F 9/00 (2006.01)</b>    | G 0 9 F 9/00    | 3 6 6 Z    |

| <b>G 0 2 F 1/13357 (2006.01)</b> | G 0 2 F 1/13357 |            |

F ターム(参考) 4M118 AA01 AB01 BA05 CA05 CA11 CA15 CB05 CB06 FB03 FB09

FB13 FB16 FB24 GA10 GB05 GB11

5B087 AA02 AC09 AC12 CC02 CC11 CC13 CC14 CC33

5F045 AA08 AB03 AB04 AC01 AC07 AC19 CA13 CA15 DA52

5F049 MA04 MB04 NA01 NB10 PA05 PA12 PA14 RA08 UA14 UA17

WA01 WA03

5G435 AA16 BB12 DD10 EE49 HH13 KK05 LL08 LL14