(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7339481号**

**(P7339481)**

(45)発行日 令和5年9月6日(2023.9.6)

(24)登録日 令和5年8月29日(2023.8.29)

(51)国際特許分類

|        |                   |     |        |       |   |

|--------|-------------------|-----|--------|-------|---|

| H 01 L | 21/768 (2006.01)  | F I | H 01 L | 21/90 | A |

| H 01 L | 21/3205 (2006.01) |     | H 01 L | 21/88 | B |

| H 01 L | 21/321 (2006.01)  |     | H 01 L | 21/88 | K |

| H 01 L | 23/532 (2006.01)  |     | H 01 L | 21/88 | M |

H 01 L 21/90

P

請求項の数 11 (全17頁)

|                   |                             |

|-------------------|-----------------------------|

| (21)出願番号          | 特願2020-571839(P2020-571839) |

| (86)(22)出願日       | 令和1年6月26日(2019.6.26)        |

| (65)公表番号          | 特表2021-530101(P2021-530101) |

|                   | A)                          |

| (43)公表日           | 令和3年11月4日(2021.11.4)        |

| (86)国際出願番号        | PCT/US2019/039260           |

| (87)国際公開番号        | WO2020/006087               |

| (87)国際公開日         | 令和2年1月2日(2020.1.2)          |

| 審査請求日             | 令和4年2月25日(2022.2.25)        |

| (31)優先権主張番号       | 62/690,838                  |

| (32)優先日           | 平成30年6月27日(2018.6.27)       |

| (33)優先権主張国・地域又は機関 | 米国(US)                      |

|          |                                                                                               |

|----------|-----------------------------------------------------------------------------------------------|

| (73)特許権者 | 000219967<br>東京エレクトロン株式会社<br>東京都港区赤坂五丁目3番1号                                                   |

| (74)代理人  | 100107766<br>弁理士 伊東 忠重                                                                        |

| (74)代理人  | 100070150<br>弁理士 伊東 忠彦                                                                        |

| (74)代理人  | 100135079<br>弁理士 宮崎 修                                                                         |

| (72)発明者  | タピリー, カンダバラ<br>アメリカ合衆国 ニューヨーク州 122<br>03, オールバニー, フラーロード 2<br>55, スイート 214, ナノファブ 3<br>00 サウス |

| (72)発明者  | スミス, ジェフリー                                                                                    |

最終頁に続く

(54)【発明の名称】 選択的二重層誘電体再成長を用いた完全な自己整合ピア

**(57)【特許請求の範囲】****【請求項1】**

基板を処理するための方法であって、

基板を提供するステップであって、前記基板は第1の誘電体層を含み、前記第1の誘電体層内には複数の導電性構造が形成され、前記第1の誘電体層の上面は前記導電性構造の上面と同じ高さである、ステップと、

前記導電性構造の上に導電性キャップ層を形成するステップであって、前記導電性キャップ層は、上面及び側壁を有して、前記導電性構造の上に選択的に配置される、ステップと、

前記第1の誘電体層の上に第2の誘電体層を形成するステップであって、前記第2の誘電体層は、前記導電性キャップ層の前記上面が覆われていない状態になり、前記導電性キャップ層の前記側壁が前記第2の誘電体層によって取り囲まれるように、前記第1の誘電体層の上に選択的に配置される、ステップと、

前記第2の誘電体層の上に第3の誘電体層を形成するステップであって、前記第3の誘電体層は、前記導電性キャップ層の前記上面が覆われていない状態になり、前記第3の誘電体層の上面よりも低くなるように、前記第2の誘電体層の上に選択的に配置される、ステップと、

前記第3の誘電体層および前記導電性キャップ層を被覆するように、第4の誘電体層を形成するステップと、

前記第4の誘電体層の内部に相互接続構造を形成するステップであって、前記相互接続

構造は、トレンチ構造及びビア構造を含み、前記ビア構造は、前記トレンチ構造の下側に配置され、前記トレンチ構造に接続され、前記ビア構造は、第1の部分及び第2の部分を有し、前記第1の部分は、前記導電性キャップ層の上に配置され、前記第1の部分の側壁は、前記第3の誘電体層によって取り囲まれ、前記第2の部分は、前記第1の部分及び前記第3の誘電体層の上に配置される、ステップと、

を含む、方法。

#### 【請求項2】

前記導電性キャップ層は、前記第2の誘電体層が形成された後で、前記複数の導電性構造の上に選択的に堆積される、請求項1に記載の方法。

#### 【請求項3】

前記ビア構造の前記第2の部分は、前記トレンチ構造と前記ビア構造の前記第1の部分との間に配置され、前記ビア構造のビア抵抗を低減するように、前記ビア構造の前記第1の部分よりも大きな限界寸法を有する、請求項1に記載の方法。

#### 【請求項4】

前記導電性キャップ層は、ルテニウム、タングステン、ニッケル、又はコバルトのうちの少なくとも1つを含む、請求項1に記載の方法。

#### 【請求項5】

前記第2の誘電体層の高さは、前記第3の誘電体層の高さの少なくとも2倍である、請求項1に記載の方法。

#### 【請求項6】

前記第3の誘電体層は金属含有誘電体材料で構成される、請求項1に記載の方法。

#### 【請求項7】

前記第2の誘電体層及び前記第3の誘電体層の両方は、同じ堆積チャンバ内で形成される、請求項1に記載の方法。

#### 【請求項8】

前記導電性キャップ層、前記第2及び前記第3の誘電体層は、共通の処理ツールを使用することにより形成され、前記共通の処理ツールは、前記導電性キャップ層、前記第2の誘電体層、及び前記第3の誘電体層をそれぞれ形成するように構成されている1つ又は複数のチャンバを含む、請求項1に記載の方法。

#### 【請求項9】

前記第4の誘電体層の内部に前記相互接続構造を形成するステップは、更に、

エッチングプロセスを通じて前記第4の誘電体層内に相互接続開口部を形成するステップであって、前記相互接続開口部は、トレンチ開口部、及び前記トレンチ開口部の下に配置され、前記複数の導電性構造のうちの1つの上に配置された前記導電性キャップ層を露出させるビア開口部を含む、ステップと、

バリア層を形成して、前記相互接続開口部、及び前記複数の導電性構造の上に配置された被覆されていない前記導電性キャップ層を覆うステップと、

導電層を前記バリア層の上に形成して前記相互接続開口部を充填するステップであって、前記導電層は、前記第4の誘電体層の上面を更に覆う、ステップと、

表面平坦化処理を実施して、前記第4の誘電体層の前記上面上の過剰な導電層を除去するステップと、を含む、請求項1に記載の方法。

#### 【請求項10】

前記第3の誘電体層は、前記相互接続開口部が前記第4の誘電体層内に形成される際に、前記エッチングプロセスから前記第2の誘電体層を保護するように構成されている、請求項9に記載の方法。

#### 【請求項11】

前記第2の誘電体層が、前記導電性構造と前記相互接続構造との間の電気的短絡を防止するように、前記第2の誘電体層の高さは3nm～15nmの範囲内である、請求項5に記載の方法。

#### 【発明の詳細な説明】

10

20

30

40

50

**【技術分野】****【0001】****関連出願の相互参照**

本出願は、2018年6月27日に出願された米国仮特許出願第62/690,838号明細書の利益を主張するものであり、この仮特許出願の内容全体が参考により本明細書に組み込まれる。

**【0002】**

本発明は、所与の基板又はウェハ上での材料のパターン形成、堆積及び除去のためのシステム及びプロセスを含む半導体微細加工に関する。

**【背景技術】****【0003】**

リソグラフィプロセスにおいて線幅を縮小する方法は、歴史的に、より大きいNAの光学系（開口数）、より短い露光波長、又は空気以外の界面媒体（水浸など）の使用を伴う。従来のリソグラフィプロセスの解像度が理論上の限界に近づくにつれ、製造者は、光学的限界を克服するために、ダブルパターニング（DP）法などのマルチプルパターニング（MP）法に目を向け始めている。

**【0004】**

材料処理方法論（例えば、フォトリソグラフィ）では、パターン形成された層を生成することには、フォトレジストなどの放射線感受性の材料の薄い層を基板の上側表面に塗布することが含まれる。この放射線感受性材料の薄い層は、レリーフパターンに変換され、これをエッキングマスクとして使用して、パターンを基板上の下にある層に転写することができる。放射線感受性材料の薄い層のパターン形成は、一般的に、例えば、フォトリソグラフィシステムを使用することによる、この放射線感受性材料の薄い層の上へのレチクル（及び関連する光学系）を介した活性エネルギー線への露光プロセスを伴う。次いで、露光プロセスに続いて、現像溶剤を使用することにより、（ポジ型のフォトレジストの場合と同様に）放射線感受性材料の薄い層の照射領域の除去か、又は（ネガ型レジストの場合と同様に）非照射領域の除去が行われることがある。幾つかの実施形態では、エッキングマスクは、複数のサブレイヤを更に含むことがある。

**【0005】**

基板上に放射線又は光のパターンを露光するための従来のリソグラフィ技術には、露光されたフィーチャのサイズを制限し、且つ露光されたフィーチャ間のピッチ又は間隔を制限する、様々な課題がある。従来のリソグラフィ技術を改善するために、様々な研究が行われてきた。例えば、露光限界を緩和するための関連技術では、ダブルパターニング方式を適用して、従来のリソグラフィ技術で現在可能であるよりも小さなピッチでのより小さなフィーチャのパターン形成を可能にしている。

**【発明の概要】****【課題を解決するための手段】****【0006】**

製造されるデバイスが小型化するにつれて、パターン形成されるフィーチャの限界寸法（CD）又は解像度の生成がますます困難になっている。その問題に加えて、更なる課題が、フォトリソグラフィ位置合わせ不良などの、2つのフォトリソグラフィプロセス間のオーバーレイに関連して存在する。マスク及びパターンが正しく位置合わせされていないと、デバイス不良及び故障が発生することがある。例えば、ラインが部分的に切断されるか又は所望の位置で切断されないことがあり、開口部が誤った場所に配置されることがあり、或いはそうでなければ短絡が発生することがある。そのような位置合わせ不良は、金属ライン及びビアの複数の層を下にあるトランジスタと相互接続する場合に、基板のメタライゼーション中にも課題をもたらす。メタライゼーションに関連した別の課題は、トレンチ及びビアを、周囲の誘電材料に損傷を与えることなく生成することである。

**【0007】**

本明細書の技術（又は方法）は、配線工程（B E O L）におけるメタライゼーション中

10

20

30

40

50

のパターン形成などの、基板にパターン形成するための方法を含む。本明細書の技術は、完全に自己整合されたビア及びラインを可能にする。本明細書の技術は、二重層誘電体の選択的成長を使用して、望ましくない構成のエッティング停止層又は膜を使用することなく、トレンチ及びビアパターン形成の自己整合を可能にする。二重層誘電体構造では、第1の誘電体層は、隣接する金属ラインからの電気的絶縁を提供することができ、第2の誘電体層は、トレンチ及びビアのパターン形成中の第1の誘電体のエッティングを防止することができる。両方の誘電体層とも、同じチャンバ内で堆積させることができ、殆どのエッティング停止層のように除去される代わりに、配線層内の基板上に残ることができる。

#### 【 0 0 0 8 】

当然ながら、本明細書に開示する製造ステップの順序は、明確にするために提示されている。一般に、これらの製造ステップは、任意の好適な順序で実施され得る。加えて、本明細書における様々な特徴、技術、構成などのそれぞれは、本開示の異なる箇所で考察されることがあるが、それらの概念のそれぞれは、互いに独立して又は互いに組み合わせて実行され得ることに留意されたい。従って、本開示は、多くの異なる態様で具現化及び検討することができる。

10

#### 【 0 0 0 9 】

この要約のセクションは、本開示又は特許請求される本発明の全ての実施形態及び／又は付加的に新規な態様を指定するものではないことに留意されたい。代わりに、この概要是、異なる実施形態と、従来技術に対する新規性に関する対応点とについての、予備的な考察のみを提供する。本発明及び実施形態の更なる詳細及び／又は予想される観点については、読者は、以下で更に議論されるような、本開示の発明を実施するための形態セクション及び対応する図面を参照されたい。

20

#### 【 0 0 1 0 】

本開示の態様によれば、基板を処理するための方法が提供される。開示する方法では、基板が提供される。基板は、第1の誘電体層と、第1の誘電体層内に形成された複数の導電性構造とを含む。第1の誘電体層の上面は、導電性構造の上面と同じ高さになっている。次いで、導電性構造の上に導電性キャップ層が形成され、この導電性キャップ層は、上面及び側壁を有して、導電性構造の上に選択的に配置される。続いて、第1の誘電体層の上に第2の誘電体層が形成される。第2の誘電体層は、導電性キャップ層の上面が露出するか又は覆われていない状態になり、導電性キャップ層の側壁が第2の誘電体層と直接的に接触するように、第1の誘電体層の上に選択的に配置される。

30

#### 【 0 0 1 1 】

第2の誘電体層が第1の誘電体層の上に選択的に形成された後、第3の誘電体層が第2の誘電体層の上に形成され、ここで、第3の誘電体層は、導電性キャップ層の上面が露出するか覆われていない状態になり且つ第3の誘電体層の上面よりも低くなるように、第2の誘電体層の上に選択的に配置される。次いで、複数の導電性構造及び第3の誘電体層の上に第4の誘電体層が形成される。続いて、第4の誘電体層の内部に相互接続構造が形成される。相互接続構造はビア構造を含み、このビア構造は第1の部分及び第2の部分を有し、第1の部分は、第1の部分の側壁が第3の誘電体層と直接的に接触するように導電性キャップ層の上に配置され、第2の部分は、第1の部分及び第3の誘電体層の上に配置される。

40

#### 【 0 0 1 2 】

幾つかの実施形態では、第3の誘電体層は、エッティングプラズマが第3の誘電体層を除去するよりも速く第4の誘電体層を除去することができるよう、第4の誘電体層に対するエッティング選択比を有することができる。第3の誘電体層は、金属含有誘電体材料、又は第4の誘電体層に対してある程度のエッティング選択比を有する任意の誘電体材料から作製することができる。

#### 【 0 0 1 3 】

幾つかの実施形態では、導電性キャップ層は、第2の誘電体層が形成された後で、複数の導電性構造の上に選択的に堆積される。幾つかの実施形態では、導電性構造の各々は、

50

ピア構造及びライン構造のうちの少なくとも1つを含む。更に、導電性キャップ層は、ルテニウム、タングステン、ニッケル、又はコバルトのうちの少なくとも1つを含むことがある。第3の誘電体層は、金属含有誘電体材料から作製することができる。

#### 【0014】

幾つかの実施形態では、第2の誘電体層の高さは、第3の誘電体層の高さの少なくとも2倍である。幾つかの実施形態では、第2の誘電体層及び第3の誘電体層は、同じ堆積チャンバ内で形成される。幾つかの実施形態では、導電性キャップ層、第2及び第3の誘電体層は、共通の処理ツールを使用することにより形成される。処理ツールは、導電性キャップ層、第2の誘電体層、及び第3の誘電体層をそれぞれ形成するように構成されている1つ又は複数のチャンバを含む。

10

#### 【0015】

開示される方法では、第4の誘電体層内に相互接続開口部を形成することがあり、この相互接続開口部は、トレーナー開口部と、トレーナー開口部の下に配置され、複数の導電性構造のうちの1つを露出させるピア開口部と、を含む。バリア層（又はライナー）が、相互接続開口部と、複数の導電性構造のうちの露出した（又は覆われていない）1つとを覆うように形成される。続いて、導電層をバリア層の上に形成して相互接続開口部を充填し、この導電層は、第4の誘電体層の上面を更に覆う。表面平坦化処理を実施して、第4の誘電体層の上面上の過剰な導電層を除去する。

#### 【0016】

幾つかの実施形態では、導電層は、以下を含む複数の方式を通して形成することができる。（a）導電層の上部が第4の誘電体膜の上面と同じ高さである底部充填堆積、（b）第4の誘電体膜に対して結果的に得られる導電層の過剰分は最小限であり非常に均一であり、第4の誘電体層の上面上の過剰な導電層を除去するために、エッチリセス（etch - recess）又は表面平坦化処理を行うことができるよう、導電層の堆積、（c）導電層は第4の誘電体層の上面を覆い、表面平坦化処理を実施して第4の誘電体層の上面上の過剰な導電層を除去することができる、従来の導電層の堆積。

20

#### 【0017】

幾つかの実施形態では、第3の誘電体層は、相互接続開口部が第4の誘電体層内に形成されるときに、エッチング処理から第2の誘電体層を保護するように構成されている。第2の誘電体層の高さは3nm～15nmの範囲内であり、その結果、第2の誘電体層は、導電性構造と相互接続構造との間の電気的短絡を防止する。

30

#### 【0018】

本開示の別の態様によれば、半導体デバイスが提供される。開示されるデバイスでは、複数の導電性構造が第1の誘電体層内に配置され、この複数の導電性構造の上面及び第1の誘電体層の上面は、同一平面上にある。更に、導電性キャップ層は、上面及び側壁を有して、導電性構造の上に選択的に配置される。第2の誘電体層は、第1の誘電体層の上に選択的に配置され、その結果、導電性キャップ層の側壁が第2の誘電体層と直接的に接触するようになる。第3の誘電体層は、第2の誘電体層の上に選択的に配置され、その結果、導電性キャップ層の上面が、第3の誘電体層の上面よりも低くなる。幾つかの実施形態では、導電性キャップ層と第3の誘電体層との間の上述した高さの差は、続いて形成されるピア構造のための自己整合をもたらす。

40

#### 【0019】

開示されるデバイスでは、第4の誘電体層は、複数の導電性構造及び第3の誘電体層の上に配置される。第4の誘電体層内に相互接続構造が更に置かれる。相互接続構造は、トレーナー構造と、トレーナー構造の下に配置されトレーナー構造に接続されるピア構造と、を含む。ピア構造は第1の部分及び第2の部分を有し、第1の部分は、第1の部分の側壁が第3の誘電体層と直接的に接触するように導電性キャップ層の上に配置され、第2の部分は、第1の部分及び第3の誘電体層の上に配置される。開示されるデバイスでは、導電性キャップ層と第3の誘電体層との間の高さの差、及び第3の誘電体層と第4の誘電体層との間のエッチング選択比は、ピア構造と導電性キャップ層との間の自己整合をもたらす。

50

**【 0 0 2 0 】**

本開示の更に別の態様によれば、第1の導電性構造が第1の誘電体層内に形成され、第1の導電性構造は、第1の誘電体層の上面から第1の誘電体層の中へと延びる。導電性キャップ層は、上面及び側壁を有して、導電性構造の上に選択的に配置される。更に、誘電体スタックが、第1の誘電体層の上に選択的に配置される。誘電体スタックは導電性キャップ層の側壁と直接的に接触し、誘電体スタックの上面は、導電性キャップ層の上面よりも高い。開示されるデバイスは、第1の導電性構造の上に形成される第2の導電性構造も含む。第2の導電性構造は第1の部分及び第2の部分を有し、第1の部分は、第1の部分の側壁が誘電体スタックと直接的に接触するように導電性キャップ層の上に配置され、第2の部分は、第1の部分及び誘電体スタックの上に配置される。

10

**【 0 0 2 1 】**

本開示の態様は、添付の図面と共に読まれると、以下の詳細な説明から最もよく理解される。業界の標準的な慣行に従い、様々な特徴が縮尺通りに描かれていないことに留意されたい。実際に、様々な特徴の寸法は、説明を明確にするために任意に拡大又は縮小される場合がある。

**【図面の簡単な説明】****【 0 0 2 2 】**

**【図1 - 6】**幾つかの実施形態による、相互接続構造を製造する様々な中間ステップの断面図である。

**【図7】**幾つかの実施形態による、相互接続構造を形成するように構成されている第1の半導体装置の概略図である。

20

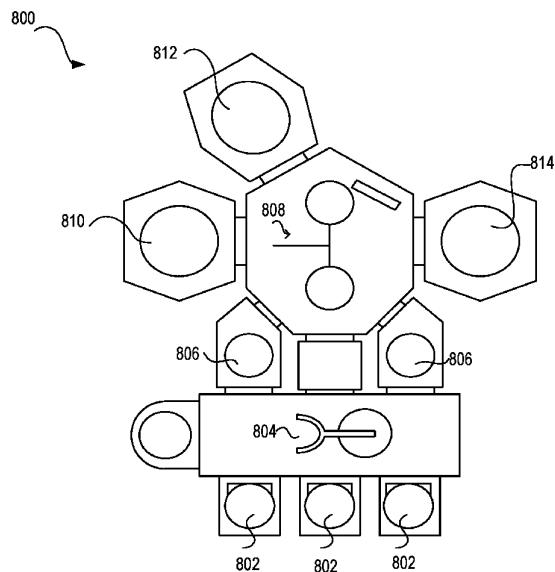

**【図8】**幾つかの実施形態による、相互接続構造を形成するように構成されている第2の半導体装置の概略図である。

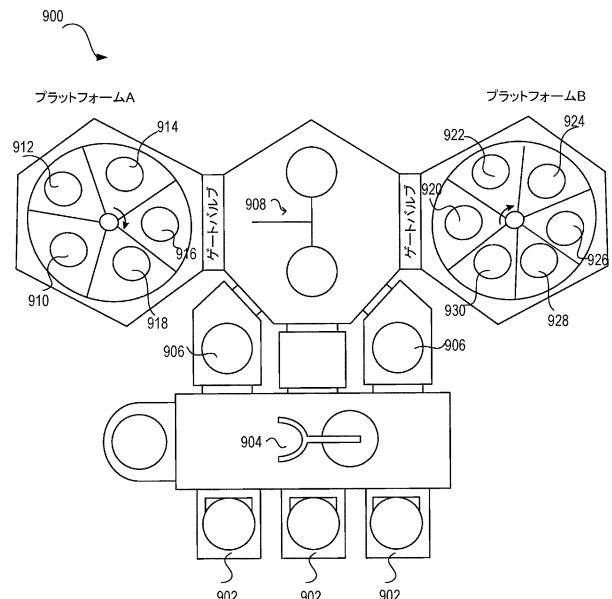

**【図9】**幾つかの実施形態による、相互接続構造を形成するように構成されている第3の半導体装置の概略図である。

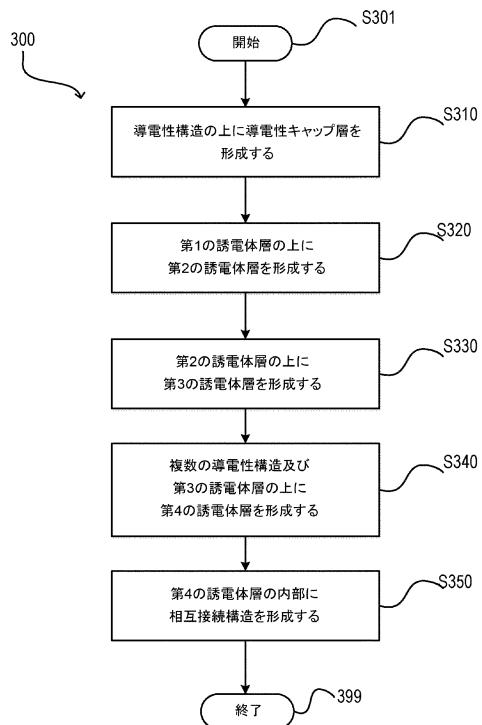

**【図10】**幾つかの実施形態による、相互接続構造を製造するためのプロセスの流れ図である。

**【発明を実施するための形態】****【 0 0 2 3 】**

以下の本開示は、提供される主題の異なる特徴を実装するための多くの異なる実施形態又は実施例を提供する。本開示を単純にするために、構成要素及び配置の特定の例について以下に説明する。当然のことながら、これらは、単なる例に過ぎず、限定することを意図するものではない。加えて、本開示は、様々な例において参照番号及び／又は文字を繰り返すことがある。この繰り返しは、単純化及び明確化を目的とするものであり、それ自体、考査された様々な実施形態及び／又は構成間の関係を決定付けるものではない。

30

**【 0 0 2 4 】**

更に、本明細書では、「下」、「下方」、「より下」、「上方」、「より上」などの空間的に相対的な用語を、説明を簡単にするために使用して、図に示すような1つの要素又は特徴の、別の要素又は特徴に対する関係を説明することがある。空間的に相対的な用語は、図示の向きに加えて、使用中又は動作中の装置の様々な向きを包含することが意図されている。装置は、他の態様で方向付けられる（90度回転されるか又は他の方向に向けられる）ことがあり、本明細書で使用される空間的に相対的な記述子もそれに応じて解釈することができる。

40

**【 0 0 2 5 】**

本明細書の全体を通して「一実施形態」又は「実施形態」に言及することは、その実施形態に関して記載する特定の特徴、構造、材料又は特性が少なくとも1つの実施形態に含まれることを意味するが、それらが全ての実施形態に存在することを示すものではない。従って、本明細書の様々な箇所で「一実施形態では」という語句が登場することは、必ずしも同じ実施形態に言及しているわけではない。更に、特定の特徴、構造、材料又は特性は、1つ又は複数の実施形態において任意の適切な様式で組み合わされ得る。

50

### 【 0 0 2 6 】

本明細書で開示する技術は、配線工程（B E O L）メタライゼーションプロセスなどの基板にパターン形成する方法を含む。本明細書に開示する技術は、完全に自己整合されたビア及びラインを可能にし、これは、二重層誘電体の選択的成長を使用して、望ましくない構成のエッティング停止層又は膜を使用することなく、トレンチ及びビアのパターン形成の自己整合を可能にすることを含む。開示する二重層誘電体構造では、第1の誘電体層は、金属ラインなどの隣接する導電性構成要素からの電気的絶縁を提供することができ、第2の誘電体層は、トレンチ及びビアのパターン形成中の第1の誘電体のエッティングを防止することができる。第1及び第2の誘電体層の両方とも、同じチャンバ内で堆積させることができ、殆どのエッティング停止層のように除去される代わりに、配線層（誘電体層とも呼ばれる）内の基板上に残ることができる。

10

### 【 0 0 2 7 】

導電性構造の自己整合を提供するための関連技術には、幾つかの課題がある。例えば、1つの関連技術は、周囲の誘電体材料の上面より下方に銅のライン及びビアを引っ込めて設けることにより、導電性構造の自己整合を提供する。そのような銅の窪みは、著しい集積上の問題（例えば、エッジ配置エラー）を持ち込み、潜在的な汚染の問題を引き起こすことがある。開示する技術では、金属ラインを引っ込めて設ける代わりに、垂直堆積／再成長プロセスを通じて下にある導電性構造を取り囲む1つ又は複数の誘電体層を導入して、下にある導電性構造と上になる導電性構造との間の自己整合をもたらすのを助けることができる。幾つかの実施形態では、その1つ又は複数の選択的に堆積された誘電体層は、2つの異なる誘電体材料から作製される2つの層を含むことがある。例えば、選択的に堆積される誘電体層は、比較的に薄い金属酸化物キャップを備えた二酸化ケイ素構造を含むことがある。二重層酸化物（例えば、SiO<sub>2</sub>及び金属酸化物）層は両方とも、同じ処理チャンバ内で又は同じツール／プラットフォーム内で、その場で堆積させることができる。開示する技術では、ビアCD許容誤差を、10ナノメートル低減することができる。

20

### 【 0 0 2 8 】

上述したように、金属酸化物層（即ち、第2の誘電体層）は、トレンチ及びビアパターンの形成中の、金属酸化物層の下に配置される第1の誘電体層のエッティングを防止するための保護層として機能することができ、第1及び第2の誘電体層は、下にある導電性構造（例えば、銅金属ライン、タンゲステン接点、銅ビアなど）とトレンチ及びビアパターンとの間の自己整合を提供する。関連技術では、通常、下にある導電性構造の上方にはエッティング停止層が堆積される。トレンチ及びビアパターンの形成中に、エッティング停止層を除去する必要がある。エッティング停止層の除去は、下にある導電性構造の損傷を引き起こすことがある。

30

### 【 0 0 2 9 】

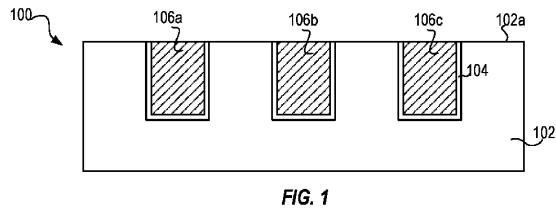

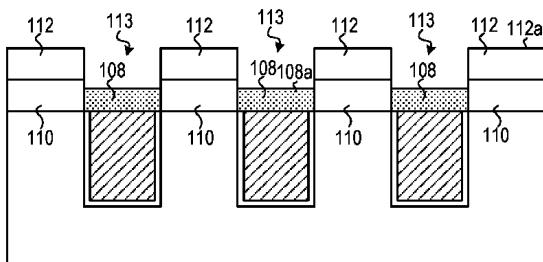

図1～図6は、相互接続構造を製造する様々な中間ステップの断面図である。図1に示すように、基板100が設けられる（受け取られる、取得される、又はさもなければ製造される）。基板100は、第1の導電性材料から作製される複数の導電性構造106を有する。導電性構造106は、第1の誘電体材料から作製される第1の配線層（第1の誘電体層とも呼ばれる）102の内部に形成されることがある。例えば、図1に示すように、3つの導電性構造106a～106bが、第1の配線層102内に形成される。第1の配線層102は、覆われていない（露出しているか又は他の様でアクセス可能である）平面102aを規定し、導電性構造106の上面はこの平面102aと同じ高さであり、その結果、導電性構造106の上面も覆われていない状態である。言い換えると、そのような基板は、導電性構造106を完成させるための銅充填及び化学機械研磨の後の所与の第1の配線層102を含むことができる。導電性構造106は、ライン及び／又はビアであり得る。従って、そのような基板100は、上面102aの上に追加の配線層又は追加の構造を製造する準備ができている状態であり得る。

40

### 【 0 0 3 0 】

幾つかの実施形態では、第1の配線層（又は第1の誘電体層）102は、LOW-K（

50

低誘電率)膜、SiO層、又は他の適切な誘電体層であり得る。導電性構造は、銅、ルテニウム、タンクス滕、ニッケル、コバルト、又は他の適切な導電性材料から作製されることがある。幾つかの実施形態では、導電性構造106と第1の配線層102との間にバリア層104が形成されることがある。バリア層104は、Ti、TiN、Ta、Ta<sub>N</sub>、又は他の適切な材料から作製されることがある。

#### 【0031】

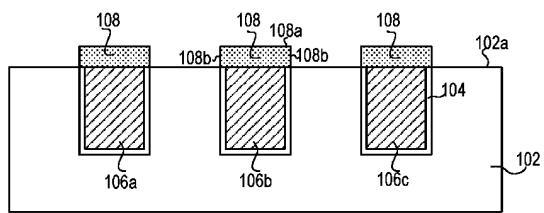

図2Aでは、導電性キャップ層(又は金属キャップ)108が、第1の配線層102の上面102a上には堆積されることなく、導電性構造106の覆われていない上面に選択的に堆積されることがある。導電性キャップ層108は、上面108a及び側壁108bを有することがある。幾つかの実施形態では、導電性キャップ層は、ルテニウム、コバルト、タンクス滕、及びニッケルを含むことがあるが、これらに限定はされない。

10

#### 【0032】

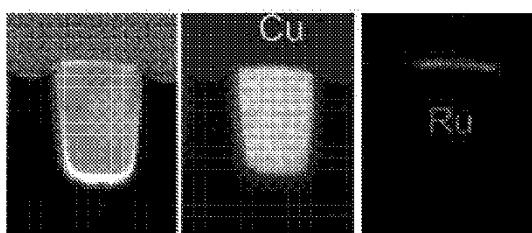

図2Bは、例示的な導電性キャップ層を例示するために、走査型透過電子顕微鏡(STEM)を通じて得られた3つの画像である。図2Bに示すように、左の画像は、STEMに基づいて、導電性構造と導電性構造の上に形成された導電性キャップ層とを示す。中央の画像は、導電性構造から得られた元素分析データを示す。中央の画像は、導電性構造が銅でできていることを示す。右の画像は、導電性キャップ層から得られた別の元素分析データを示す。右の画像は、導電性キャップ層がルテニウム層であることを示す。導電性キャップ層108は、CVDプロセス、PVDプロセス、スパッタプロセス、拡散プロセス、原子層堆積プロセス、又は他の適切な堆積プロセスを通じて作製することができる。導電性キャップ層108を形成することができる例示的な装置を図7～図9に示すことができる。

20

#### 【0033】

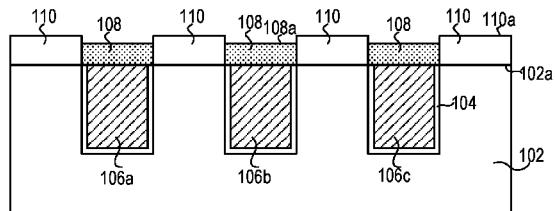

図3では、第2の誘電体層110が、第1の誘電体層102の覆われていない上面102a上に選択的に成長／堆積されている。従って、導電性キャップ層108の上面108aは露出しており(又は覆われていない状態であり)、導電性キャップ層108の側壁108bは、第2の誘電体層110と直接的に接触している。幾つかの実施形態では、導電性キャップ層108の側壁108bは、第2の誘電体層110によって取り囲まれる。幾つかの実施形態では、第1及び第2の誘電体層は、同じ材料でできていることがある。例えば、第1の誘電体層102はSiO<sub>2</sub>から作製され、第2の誘電体層110もSiO<sub>2</sub>から作製される。幾つかの実施形態では、第1及び第2の誘電体層は、異なる材料でできている。例えば、第1の誘電体層102はlow-k層であり、第2の誘電体層110はSiO層である。幾つかの実施形態では、第2の誘電体層110は、3nm～15nmの範囲の厚さを有することがある。第2の誘電体層110のk値は、4よりも小さいことがある。当然ながら、回路設計要件に従って、他の適切なk値を適用することができる。

30

#### 【0034】

幾つかの実施形態では、第2の誘電体層110の上面110aは、導電性キャップ層108の上面108aよりも高いことがある。幾つかの実施形態では、第2の誘電体層110の上面110aは、堆積プロセスに従って、導電性キャップ層108の上面108aよりも低いことがある。第2の誘電体層110は、CVDプロセス、PVDプロセス、スパッタプロセス、拡散プロセス、原子層堆積プロセス、又は他の適切な堆積プロセスを通じて作製することができる。第2の誘電体層110を形成することができる例示的な装置を図7～図9に示すことができる。

40

#### 【0035】

図4に示すように、第2の誘電体層110が選択的に堆積された後、第3の誘電体層112を、第2の誘電体層110上に選択的に成長させることができる。従って、導電性キャップ層108の上面108aは、依然として露出しているか又は覆われていない状態であり、第3の誘電体層112の上面112aよりも低くなっている。更に、複数の窪み領域113が、第3の誘電体層112内に形成されることがある。窪み領域113は、第3の誘電体層112を露出させる側壁を有することがある。幾つかの実施形態では、窪み領

50

域 113 の側壁は、更に第 2 の誘電体層 110 の一部を露出させることがある。窪み領域 113 は、導電性キャップ層 108 を露出させる底部部分を有することがある。

#### 【 0036 】

幾つかの実施形態では、第 3 の誘電体層 112 は、第 2 の誘電体層 110 のエッティング抵抗率とは異なるエッティング抵抗率を有することがある。第 3 の誘電体層 112 は、 $1 \text{ nm} \sim 5 \text{ nm}$  の間の厚さを有することがある。第 3 の誘電体層 112 は、 $\text{Al}_2\text{O}_3$ 、 $\text{HfO}_2$ 、 $\text{ZrO}_2$ 、 $\text{TiO}_2$ 、及びそれらの組み合わせなどの金属含有誘電体又は金属酸化物から作製することができる。幾つかの実施形態では、第 3 の誘電体層 112 は、 $\text{SiC}$  又は  $\text{SiCN}$  などの非金属含有誘電体であることがあり、これは、エッティングプラズマが第 3 の誘電体層を除去するよりも速く第 4 の誘電体層を除去することができるよう、第 4 の誘電体層に対するエッティング選択性を有する。第 3 の誘電体層 112 は、第 2 の誘電体層 110 と比べて比較的に薄いことがある。例えば、第 2 の誘電体層の高さは、第 3 の誘電体層の高さの少なくとも 2 倍であり得る。当然ながら、第 2 及び第 3 の誘電体層は、異なる製造条件に従って、他の厚さ比率を有することがある。

10

#### 【 0037 】

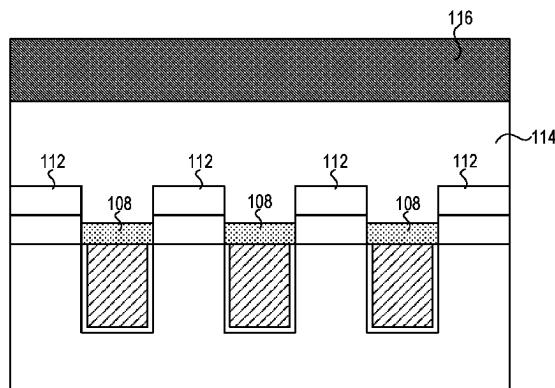

図 5 では、第 2 の配線層（第 4 の誘電体層とも呼ばれる）114 が、第 3 の誘電体層 112 及び導電性キャップ層 108 の上に形成され、その結果、窪み領域 113 は第 2 の配線層 114 によって充填される。第 2 の配線層 114 は、 $\text{low-K}$  材料、 $\text{SiO}_2$ 、又は他の適切な誘電体材料などの第 4 の誘電体材料でできている。図 5 に示すように、第 4 の誘電体層 114 は、第 2 及び第 3 の誘電体層並びに導電性キャップ層を覆い、平面状の上面を提供することができる。言い換えると、後続のステップで追加の金属層を形成するために、基板 100 を第 4 の誘電体層 114 でコーティングすることができる。通常、集積回路は、 $10 \sim 20$  の配線層など、多数の配線層を有することがある。1 つの配線層が完成した後（通常、所与の層のメタライゼーション及び平坦化の後）で、次の配線層が生成されることがある。

20

#### 【 0038 】

依然として図 5 を参照すると、ハードマスク層 116 が第 4 の誘電体層 114 の上に形成されることがある。ハードマスク層 116 は、 $\text{TiN}$  層などの単一の層であるか、又は複数の層を含むことがある。ハードマスク層の上には、フォトレジスト層（図示せず）が、リソグラフィプロセス（例えば、フォトリソグラフィ又は電子ビームリソグラフィ）を通して堆積及びパターン形成されることがある、このリソグラフィプロセスは、フォトレジストコーティング（例えば、スピノンオンコーティング）、ソフトベーリング、マスク位置合わせ、露光、露光後ベーリング、フォトレジスト現像、すすぎ、乾燥（例えば、スピノン乾燥及び / 又はハードベーリング）、などを更に含むことがある。フォトレジストに形成されたパターンを、その後、エッティングプロセスによってハードマスク層に、更には第 2 の配線層 114 の部分へと転写して、1 つ又は複数の相互接続開口部（図示せず）を形成することができる。相互接続開口部の各々は、後に続くメタライゼーションのためのトレンチ開口部及び / 又はピア開口部を有して、1 つ又は複数のデュアルダマシン構造などの 1 つ又は複数の相互接続構造を形成することができる。

30

#### 【 0039 】

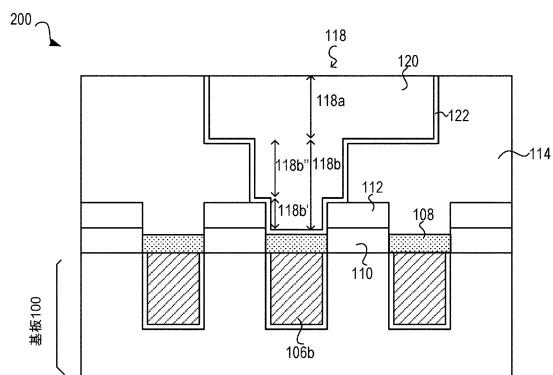

図 6 では、相互接続開口部（図示せず）が第 2 の配線層（又は第 4 の誘電体層）114 内部に形成された後、そこに形成された相互接続開口部は、金属化される、即ち導電性材料 120 で満たされることがある。導電性材料 120 は、銅、タンゲステン、ルテニウム、コバルト、又は他の適切な材料であり得る。そのようなメタライゼーションには、ライナー（又はバリア層）122 を堆積させ、それに続いてバルク導電性材料 120 を堆積せざることが含まれることがある。バルク導電性材料 120 は、第 4 の誘電体層 114 の上面を更に覆うことがある。CMP プロセスなどの表面平坦化プロセスを適用して、第 4 の誘電体層の上面から過剰な導電性材料 120 を除去することができる。相互接続開口部内に残った導電性材料 120 が、相互接続構造になる。ライナー 122 は、 $\text{Ti}$ 、 $\text{TiN}$ 、 $\text{Ta}$ 、 $\text{Ta}$ 、又は他の適切な材料から作製されることがある。

40

50

### 【0040】

依然として図6を参照すると、相互接続構造118が第4の誘電体層114内に形成される。相互接続構造118は、トレンチ構造118aと、トレンチ構造の下に配置されトレンチ構造に接続されるビア構造118bと、を有することがある。ビア構造118bは、第1の部分118b'及び第2の部分118b''を有することがある。ビア構造の第1の部分118b'は、導電性キャップ層108の上に配置され、第1の部分118b'の側壁は、第3の誘電体層112と直接的に接触している。幾つかの実施形態では、第1の部分118b'の側壁は、第3の誘電体層112によって取り囲まれる。幾つかの実施形態では、第1の部分118b'の側壁は、プロセス条件に基づいて、第2の誘電体層110の一部に接触している方向もある。第2の部分118b''は、第1の部分118'の上に配置される。第2の部分118b''は、更に第3の誘電体層112の上に配置され、第3の誘電体層112と直接的に接触していることがある。相互接続構造118は、ビア構造118bを介して導電性構造106bに電気的に結合される。

10

### 【0041】

一旦相互接続構造118が形成されると、半導体デバイス200が完成する。半導体デバイス200は、基板100を有する。基板100は、第1の誘電体層102内に形成された導電性構造106を有する。導電性構造106の上には、導電性キャップ層108が選択的に配置される。第2の誘電体層110は、導電性キャップ層108の側壁が第2の誘電体層110によって取り囲まれるように、第1の誘電体層102の上に選択的に配置される。第3の誘電体層112は、第3の誘電体層112の上面が導電性キャップ層108の上面より上方にあるように、第2の誘電体層110の上に選択的に形成される。更に、相互接続構造118が形成される。相互接続構造118は、相互接続構造のビア構造を介して導電性構造のうちの1つ106bに電気的に結合される。

20

### 【0042】

開示する半導体デバイス200では、選択的に成長させた二重層誘電体（例えば、第1及び第2の誘電体層）は、ビア構造（例えば、118b）と下にある導電性構造（例えば、106b）との間の自己整合と、位置合わせ不良によって引き起こされる静電容量の問題からの保護とをもたらす。例えば、対応するリソグラフィパターン（例えば、ビア開口部）が、意図される金属ライン（例えば、導電性構造106b）と整列するように完全に位置合わせされていない場合であっても、二重層誘電体は、意図される下にある金属ライン（例えば、導電性構造106b）又は他の導電性構造にビア開口部を導くことができる、その理由は、第3の誘電体層は、第4の誘電体層と比べてエッチング速度が遅いからである。開示する半導体デバイス200では、二重層誘電体の高さは導電性キャップ層の高さよりも高くなっている、これにより、ビア構造118bが隣接する導電性構造と重なるのを防ぐことができ、また、ビア構造118bと隣接する下にある導電性構造との間に十分な距離をもたらして、電気的短絡などの欠陥を防ぐことができる。

30

### 【0043】

開示する方法では、第1、第2、及び第4の誘電体層は同じ誘電体材料でできていることがある。他の実施形態では、第1の誘電体層は超10w-K材料から作製されがあり、第2の誘電体層は酸化ケイ素から作製されることがあり、第3の誘電体層は金属酸化物から作製されることがあり、第4の誘電体層は超10w-K膜であり得る。従って、活性金属（例えば、導電性構造106）の上にSiCNエッチング停止層は必要なく、超10w-K材料（例えば、第4の誘電体層114）を、下にある金属層（例えば、導電性構造106）/配線層（例えば、第1の誘電体層）の上に形成することができる。開示する方法では、導入された二重層誘電体及び導入された導電性キャップ層は、自己容量（寄生容量）の約1~2%増加をもたらすに過ぎない。しかしながら、ビア構造の第1の部分を下にある導電性構造と自己整合させることができ、ビアの第2の部分のビアサイズが第1の部分よりも増加しておりビア抵抗が低減される場合には、ビアサイズを増加させることにより、ビア抵抗を5%より多く減らすことができる。従って、本明細書の技術は、性能への影響を最小限に抑えながら、欠陥（例えば、位置合わせ不良）を低減するという利

40

50

点をもたらす。

**【 0 0 4 4 】**

開示する方法は、スループットという利点ももたらす。開示する方法は、共通のプラットフォーム又は共通のツール内で実施することができ、そこでは、金属キャップの堆積及び誘電体層の堆積のためにそれぞれ異なるチャンバが使用され、全ての対応するモジュールが、単一のプラットフォーム又はウェハ供給システムに接続されることがある。他の実施形態では、両方の誘電体材料を堆積させるために同じチャンバが使用されることがある。

**【 0 0 4 5 】**

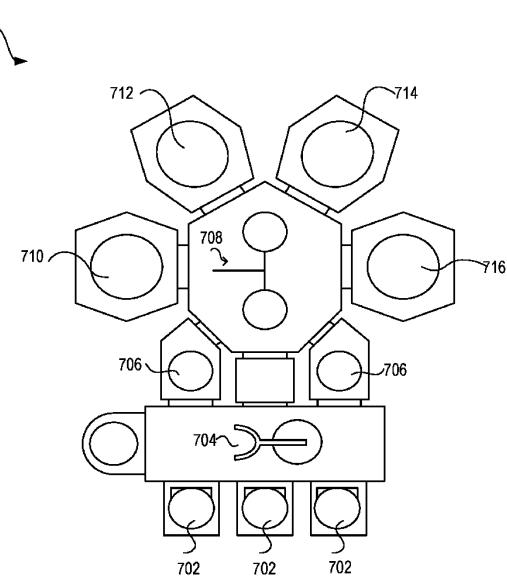

図7は、本開示の幾つかの実施形態による、相互接続構造を形成するように構成されている第1の半導体装置700の概略図である。図7に示すように、装置700は、化学気相堆積(CVD)プロセスを提供することができる。装置700は、ウェハを受け取るように構成されている複数のウェハロードポート702、及びウェハロードポートからロードロック706へウェハを運ぶように構成されているウェハハンドラ704を含むことがある。ロードロック706は、ウェハを収容し且つ更にウェハを処理チャンバに移送するための二次真空チャンバとして機能する。装置700は、複数の処理チャンバ710～716と、処理チャンバ間でウェハを移送するように構成されているウェハ移送機構708と、も含む。

10

**【 0 0 4 6 】**

装置700は、ルテニウムなどの導電性キャップ層を堆積させるように構成されている第1の処理チャンバ710と、プラズマプロセス又はH<sub>2</sub>O蒸気プロセスを通じて導電性構造の上の表面酸化物を除去するように構成されている処置チャンバ712と、を含むことがある。処置チャンバ712は、アニーリングプロセスも提供し、また、導電性キャップ層、第2の誘電体層、及び第3の誘電体層の選択的な成長を支援する自己整合単層(SAM)の堆積も提供することができる。装置700は、SiOから作製することができる第2の誘電体層を形成するように構成されている第2の堆積チャンバ714と、金属酸化物から作製することができる第3の誘電体層を形成するように構成されている第3の堆積チャンバ716と、を更に含む。

20

**【 0 0 4 7 】**

SiOを形成するための装置700に基づく例示的な堆積プロセスには、処理ガスSiH<sub>4</sub>及びN<sub>2</sub>O、300～400の間の処理温度、及び2～3 Torrの間の処理圧力を適用することができる。ルテニウムを形成するための例示的な堆積プロセスには、第1の処理チャンバ710及び400～600の間の処理温度の中にRuCVD前駆体を導入することが含まれることがある。Ru CVD前駆体は、Ru(acac)<sub>3</sub>(acacはアセチルアセチナートとも呼ばれる)、Ru(EtCp)<sub>2</sub>(EtCpは、エチルシクロペンタジエニルとも呼ばれる)、Ru<sub>3</sub>(CO)<sub>12</sub>などを含む。

30

**【 0 0 4 8 】**

図8は、本開示の幾つかの実施形態による、相互接続構造を形成するように構成されている第2の半導体装置800の概略図である。図8に示すように、半導体装置800は、複数のウェハロードポート802、ウェハハンドラ804、1つ又は複数のロードロック806、複数の処理チャンバ810～814、及びウェハ移送機構808を含むことがある。処理チャンバは、導電性キャップ層などの金属層を形成するように構成されている第1の処理チャンバ810と、上述した処置チャンバ712と同様の機能を有する処置チャンバ812と、第2の処理チャンバ814と、を含む。装置700と比べると、第2の処理チャンバ814は、SiO誘電体層及び金属酸化物層をその場で生成することができる。言い換えると、第2の処理チャンバ814は、まずSiO層を形成し、続いて金属酸化物層を形成することができる。

40

**【 0 0 4 9 】**

図9は、本開示の幾つかの実施形態による、相互接続構造を形成するように構成されている第3の半導体装置900の概略図である。装置700又は800と比べると、装置900はより簡潔なレイアウト及び高いスループットを提供することができる。図9に

50

示すように、装置 900 は、複数のウェハロードポート 902、ウェハハンドラ 904、1つ又は複数のロードロック 906、並びに2つのプラットフォーム A 及び B を含むことがある。プラットフォーム A は、金属の堆積及び処置を行うように構成されている。プラットフォーム A は、金属堆積を実施するように構成されている第 1 のチャンバ 910 と、前のステップからの前駆物質をバージするための第 1 のバージチャンバ 912 と、導電性構造から表面酸化物を除去するために Ar 又は H<sub>2</sub> プラズマ処置などのプラズマ処置を実施するように構成されているプラズマ処置チャンバ 914 と、第 2 のバージチャンバ 916 と、処置チャンバ 918 と、を含む。処置チャンバは、アニーリングを行うか、又は自己整合単層を形成することができる。

#### 【0050】

装置 900 のプラットフォーム B は、誘電体層を生成するように構成されている。例えば、プラットフォーム B は、第 1 の誘電体材料を形成するように構成されている第 1 の準備チャンバ 920 と、前のステップからの前駆物質をバージするように構成されている第 1 のバージチャンバ 922 と、第 2 の誘電体材料を生成するように構成されている第 2 の準備チャンバ 924 と、第 2 のバージチャンバ 926 と、第 3 の誘電体材料を生成するように構成されている第 3 の準備チャンバ 928 と、第 3 のバージチャンバ 930 と、を有する。

#### 【0051】

例示的な製造プロセスでは、ウェハをプラットフォーム A に送ることができる。ウェハは、プラズマ処置チャンバ 914 内でプラズマ処置を受けて、下にある導電性構造（例えば、導電性構造 106）の上面上の表面酸化物を取り除くことができる。次いで、ウェハを第 2 のバージチャンバ 916 に送って、プラズマ処置チャンバ 914 からの処理ガスの残留物を取り除く。次いで、ウェハは第 1 のチャンバ 910 内で Ru 堆積などの金属層堆積を受け、次いで、第 1 のバージチャンバ 922 に送られて Ru CVD 前駆体を除去することができる。次いで、ウェハは、ウェハ移送機構 908 を介してプラットフォーム B に送られる。プラットフォーム B では、ウェハは第 1 の準備チャンバ 920 内で第 1 の誘電体材料（例えば、第 2 の誘電体層）を受け取り、次いで、第 1 のバージチャンバ 922 に送られて、第 1 の誘電体材料の形成からの CVD 前駆体を除去することができる。次いで、ウェハを第 2 の準備チャンバ 924 に送って、第 2 の誘電体材料（例えば、第 3 の誘電体層）を受け取る。次いで、ウェハを第 2 のバージチャンバ 926 に移送して、第 2 の誘電体材料の形成からの前駆物質を除去する。ウェハを更に第 3 の準備チャンバ 928 に送って、第 3 の誘電体材料（例えば、第 4 の誘電体層）を受け取り、その後、第 3 のバージチャンバ 930 に送って、第 3 の誘電体材料の形成からの前駆物質を除去する。

#### 【0052】

図 10 は、相互接続構造を製造するためのプロセス 300 の流れ図である。プロセス 300 はステップ 310 で開始し、このステップでは、導電性キャップ層が複数の導電性構造の上に選択的に形成される。導電性構造は第 1 の誘電体層内に形成されており、第 1 の誘電体層の上面は、導電性構造の上面と同じ高さである。幾つかの実施形態では、ステップ 310 は、図 1、図 2A、及び図 2B を参照して説明したように実施することができる。

#### 【0053】

次いでプロセス 300 はステップ 320 に進み、このステップでは、第 2 の誘電体層が第 1 の誘電体層の上に形成される。第 2 の誘電体層は、第 1 の誘電体層の上に選択的に配置され、その結果、導電性キャップ層の上面が露出するか又は覆われていない状態になり、導電性キャップ層の側壁が第 2 の誘電体層によって取り囲まれるようになる。幾つかの実施形態では、ステップ 320 は、図 3 を参照して説明したように実施することができる。

#### 【0054】

プロセス 300 はステップ 330 に進み、このステップでは、第 3 の誘電体層が第 2 の誘電体層の上に形成される。第 3 の誘電体層は、第 2 の誘電体層の上に選択的に配置され、その結果、導電性キャップ層の上面は、露出するか又は覆われていない状態になり、且つ第 3 の誘電体層の上面よりも低くなる。幾つかの実施形態では、ステップ 330 は、図

10

20

30

40

50

4を参照して説明したように実施することができる。

**【0055】**

プロセス300のステップ340では、第4の誘電体層が、複数の導電性構造及び第3の誘電体層の上に形成される。幾つかの実施形態では、ステップ340は、図5を参照して説明したように実施することができる。

**【0056】**

次いでプロセス300はステップ350に進み、このステップでは、相互接続構造が第4の誘電体層の内部に形成される。相互接続構造はビア構造を含み、このビア構造は第1の部分及び第2の部分を有し、第1の部分は、第1の部分の側壁が第3の誘電体層によって取り囲まれるように導電性キャップ層の上に配置され、第2の部分は、第1の部分及び第3の誘電体層の上に配置される。幾つかの実施形態では、ステップ350は、図6を参考して説明したように実施することができる。

10

**【0057】**

プロセス300の前、その間中、及びその後に追加のステップを設けることができ、プロセス300の更なる実施形態のために、説明したステップの一部を置き換えるか、削除するか、又は異なる順序で実施することができることに留意されたい。後続のプロセスステップでは、半導体デバイス200の上に様々な追加の相互接続構造（例えば、導電性ライン及び／又はビアを有するメタライゼーション層）が形成されることがある。そのような相互接続構造は、半導体デバイス200を他のコンタクト構造及び／又は能動デバイスと電気的に接続して、機能回路を形成する。パッシベーション層、入力／出力構造等などの更なるデバイス特徴部が形成されることもある。

20

**【0058】**

前述の説明では、処理システムの特定の形状並びにそこで使用される様々な構成要素及びプロセスの説明など、特定の詳細を説明してきた。しかしながら、本明細書における技術は、これらの特定の詳細から逸脱する他の実施形態で実施することができ、そのような詳細は、説明のためのものであり、限定のためのものではないことを理解されたい。本明細書で開示される実施形態が添付の図面を参照して説明してきた。同様に、説明の目的のため、詳細な理解を提供するために特定の番号、材料、及び構成が示してきた。それにもかかわらず、そのような特定の詳細なしで実施形態を実施することができる。実質的に同じ機能的構成を有する構成要素は、同様の参照記号によって示され、したがって、冗長な説明は省略される場合がある。

30

**【0059】**

様々な実施形態の理解を支援するために、様々な技術が複数の個別の動作として説明されてきた。説明の順序は、これらの動作が必ず順序に依存することを意味すると解釈されるべきではない。実際に、これらの動作は、提示した順序で実行される必要はない。説明された動作は、説明された実施形態と異なる順序で実行されてもよい。追加の実施形態では、様々な追加の動作を実行することができ、且つ／又は説明した動作を省略することができる。

**【0060】**

本明細書で使用される「基板」又は「ターゲット基板」は、本発明に従って処理される物体を総称して指す。基板は、デバイス、特に半導体又は他の電子デバイスの任意の材料部分又は構造を含むことがあり、例えば半導体ウェハ、レチクルなどのベース基板構造、又は薄膜などのベース基板構造上の若しくはそれに重なる層であり得る。従って、基板は、いかなる特定のベース構造、下層又は上層、パターン付き又はパターンなしにも限定されず、むしろ任意のそのような層若しくはベース構造並びに層及び／又はベース構造の任意の組み合わせを含むことが企図されている。説明では、特定の種類の基板を参照している場合があるが、これは、説明のみを目的とするものである。

40

**【0061】**

また、当業者であれば、本発明の同じ目的を達成しながらも、上記で説明した技術の動作に対してなされる多くの変形形態が存在し得ることを理解するであろう。そのような変

50

形態は、本開示の範囲に包含されることが意図されている。従って、本発明の実施形態の前述の説明は、限定することを意図したものではない。むしろ、本発明の実施形態に対する任意の限定は、以下の特許請求の範囲に提示される。

## 【図面】

【図 1】

FIG. 1

【図 2 A】

FIG. 2A

10

【図 2 B】

FIG. 2B

【図 3】

FIG. 3

20

【図 4】

FIG. 4

【図 5】

FIG. 5

30

40

50

【図6】

【図7】

FIG. 7

10

20

【図8】

FIG. 8

【図9】

30

40

50

【図10】

10

20

30

40

50

---

フロントページの続き

アメリカ合衆国 ニューヨーク州 12203, オールバニー, フラーロード 255, スイート

214, ナノファブ 300 サウス

審査官 船越 亮

- (56)参考文献

- 米国特許出願公開第2006/0118962 (US, A1)

- 米国特許出願公開第2016/0218034 (US, A1)

- 米国特許出願公開第2017/0110397 (US, A1)

- 米国特許出願公開第2003/0148618 (US, A1)

- 米国特許出願公開第2018/0076027 (US, A1)

- 米国特許第09530691 (US, B1)

(58)調査した分野 (Int.Cl., DB名)

- H01L 21/768

- H01L 21/3205

- H01L 21/321