MINISTERO DELLO SVILUPPO ECONOMICO

DIREZIONE GENERALE PER LA LOTTA ALLA CONTRAFFAZIONE

UFFICIO ITALIANO BREVETTI E MARCHI

|                    |                 |

|--------------------|-----------------|

| DOMANDA NUMERO     | 102001900934373 |

| Data Deposito      | 01/06/2001      |

| Data Pubblicazione | 01/12/2002      |

| Sezione | Classe | Sottoclasse | Gruppo | Sottogruppo |

|---------|--------|-------------|--------|-------------|

| G       | 06     | F           |        |             |

Titolo

METODO DI CONTROLLO DELL'ERRORE IN CELLE DI MEMORIA MULTILIVELLO CON NUMERO DI BIT MEMORIZZATI CONFIGURABILE.

D E S C R I Z I O N E

del brevetto per invenzione industriale

di STMICROELECTRONICS S.R.L.

di nazionalità italiana,

5 con sede a 20041 AGRATE BRIANZA (MILANO) - VIA C. OLIVETTI, 2

Inventori: MICHELONI Rino, PICCA Massimiliano,

RAVASIO Roberto, ZANARDI Stefano

\*\*\* \* \*\*\* \* \* 16 2004A 000529

La presente invenzione è relativa ad un metodo di

10 controllo dell'errore per celle di memoria multilivello

con numero di bit memorizzati configurabile.

Come è noto, grazie all'evoluzione dei processi

tecnologici che rende realizzabili dispositivi

elementari di dimensioni sempre più ridotte, negli

15 ultimi anni sono state realizzate memorie a

semiconduttore aventi capacità di memorizzazione molto

elevate.

Un ulteriore aumento della capacità di

memorizzazione è stato ottenuto ricorrendo alla

20 memorizzazione multilivello, la quale permette di

aumentare la densità di memorizzazione a parità di

generazione tecnologica. Infatti, con questa tecnica si

memorizzano più bit d'informazione all'interno della

singola cella di memoria normalmente utilizzata per

25 contenere un solo bit.

BERGADANNO MARKO

iscritto all'Albo n. 8/36

È altresì noto che per leggere una cella di memoria bilivello ( contenente 1 bit) si confronta un'opportuna grandezza elettrica, legata allo stato della cella, con un valore di riferimento e in base all'esito del 5 confronto si determina se la cella di memoria contiene uno "0" oppure un "1" logico.

Nel caso di celle in grado di contenere  $r$  bit, la lettura avviene confrontando la grandezza elettrica correlata allo stato della cella di memoria con  $2^r - 1$  10 livelli di riferimento. L'esito dei confronti permette di determinare in quale dei  $2^r$  intervalli ammessi si trova la cella di memoria, e quindi di ricostruirne il contenuto in termini di informazione binaria.

L'approccio multilivello può essere applicato sia 15 alle memorie volatili (come le memorie DRAM) sia alle memorie nonvolatili (come le memorie EEPROM e Flash). In ogni caso l'aumento del numero di bit per cella rende più critica la tolleranza ai disturbi, la ritenzione dell'informazione e l'accuratezza delle operazioni di 20 lettura e di scrittura. Inoltre, l'incremento della capacità di memorizzazione richiesto dal mercato tende a ridurre l'affidabilità complessiva. Per questi motivi si prevede che l'utilizzo di codici a controllo dell'errore sarà fondamentale soprattutto per memorie multilivello a 25 elevata capacità.

BERGADANO Marco

*(scritto all'Alto n. 8430)*

Al momento, i dispositivi commerciali a maggior capacità contengono alcune centinaia di milioni di bit, e nei prossimi anni è prevista la realizzazione di dispositivi con capacità via via più elevata.

5 L'aumento del numero di celle tende a ridurre la vita media al guasto (o MTTF) dell'intero dispositivo di memoria. Ma data l'esigenza di realizzare apparecchiature o sistemi sempre più affidabili, il livello di affidabilità richiesto per il singolo

10 componente di memoria diventa sempre più stringente. Per questo motivo si adottano tecniche di progettazione dedicate e un attento controllo di qualità sui processi produttivi per prevenire e ridurre i guasti.

Tuttavia i malfunzionamenti dei chip di memoria non

15 possono essere eliminati completamente e possono essere ridotti solo a spese di una riduzione delle prestazioni o di un aumento dei costi.

Un modo molto efficace per aumentare l'affidabilità è costituito dalla progettazione di memorie immuni

20 dall'errore utilizzando codici a controllo dell'errore, ossia codici in grado di rivelare e correggere errori dei dati memorizzati nelle memorie.

In particolare codici a correzione del singolo errore o a rivelazione del doppio errore e a correzione

25 del singolo errore sono utilizzati in dispositivi di

BERGADANCO MIRKO

*(iscritto all'Albo n. 843pt)*

memoria a semiconduttore di vario tipo.

In particolare, gli errori nelle memorie sono normalmente classificati come errori "soft" ed errori "hard". Con errore "soft" si intende un cambiamento 5 dello stato di una cella casuale, non ripetitivo e non permanente. Gli errori "soft" sono causati da rumore elettrico occasionale o indotti da radiazione (particelle  $\alpha$ , raggi cosmici, ...), riguardano un numero molto limitato di celle per volta e sono recuperabili 10 col successivo ciclo di scrittura.

Con errore "hard" si intende invece un guasto fisico permanente associato a difetti presenti nel dispositivo o creatisi durante il suo funzionamento per incapacità dei materiali di sopportare gli stress 15 applicati. Generalmente gli errori "hard" sono molto più rari degli errori "soft".

I codici a controllo dell'errore permettono di ridurre drasticamente gli effetti degli errori "soft", che rappresentano il problema più grave, specialmente 20 per le memorie multilivello. Essi possono peraltro risultare utili anche al fine di recuperare alcuni errori "hard".

Per proteggere l'informazione da immagazzinare nella memoria è necessario aggiungere ai bit che 25 costituiscono ogni parola di informazione un certo

numero di bit di controllo o di parità, opportunamente calcolati. L'operazione che associa a ogni parola di informazione un preciso valore dei bit di controllo viene chiamata *codifica*. I bit di controllo calcolati 5 dal circuito che effettua la codifica devono essere memorizzati unitamente alla parola di informazione.

Ogni parola memorizzata sarà successivamente letta insieme con i bit di controllo che le competono. Il circuito di *decodifica* è in grado di rivelare e 10 correggere un certo numero di bit errati per parola confrontando opportunamente il valore dei bit di controllo con il valore dei bit di informazione.

Il numero di bit di controllo che è necessario aggiungere a ogni parola di informazione viene 15 determinato in base alla lunghezza della parola di informazione stessa ed al numero di errori per parola che si vogliono correggere.

Più in generale, la codifica a controllo dell'errore può essere estesa dall'alfabeto binario 20 (contenente solo i due simboli "0" e "1") a un alfabeto più esteso contenente  $q$  simboli. In questo caso la codifica consiste nell'aggiunta di un certo numero di simboli (non più di bit) a ogni parola da memorizzare, e la correzione degli errori consiste nella correzione dei 25 simboli errati.

Questa estensione al caso  $q$ -ario si addice in modo particolare alle memorie multilivello, in cui ogni cella di memoria è in grado di immagazzinare più di un bit (ad esempio  $r$  bit). In questo caso, infatti, il

5 malfunzionamento di una cella di memoria può degradare il valore di tutti i bit in essa memorizzati. Risulta quindi più agevole associare a ogni blocco di  $r$  bit, memorizzati in unica cella, un simbolo  $q$ -ario, cioè appartenente a un alfabeto costituito da  $q=2^r$  simboli

10 distinti. Ogni simbolo viene quindi memorizzato in una cella di memoria multilivello distinta. In questo modo, ogni parola di informazione di  $k$  bit viene vista come una parola costituita da  $k/r$  simboli  $q$ -ari (pari al numero di celle di memoria che formano ogni parola), e

15 la correzione di un simbolo equivale alla correzione di tutti gli  $r$  bit a esso associati.

I metodi di controllo dell'errore integrati in una memoria a semiconduttore devono soddisfare tre requisiti fondamentali:

- 20 - il tempo richiesto per l'operazione di codifica e per l'operazione di decodifica (comprendente la rivelazione e la correzione dell'errore) deve influire solo in minima parte sul tempo d'accesso alla memoria;

- 25 - l'area aggiuntiva dovuta ai circuiti di codifica e decodifica e alle celle di controllo deve essere

minimizzata;

- la tecnica usata deve almeno garantire la correzione di qualsiasi tipo di errore sulla singola cella, che nel caso di celle multilivello può consistere

5 nell'errore su più bit.

Affinché i tempi di codifica e decodifica non degradino il tempo di accesso, si ricorre tipicamente all'utilizzo di strutture di codifica parallela o a matrice, che offrono le maggiori velocità di calcolo.

10 Per quanto riguarda invece il secondo punto, l'area viene minimizzata scegliendo codici con caratteristiche adatte all'applicazione ed opportunamente ottimizzati.

L'ultimo punto è infine garantito dall'utilizzo di codici  $q$ -ari, che consentono la rivelazione e la

15 correzione degli errori sulle celle di memoria,

indipendentemente dal numero di bit errati associati a

ciascuna di esse.

Le memorie multilivello progettate per contenere  $r$  bit per cella possono però anche funzionare

20 immagazzinando un numero minore di bit per cella. In questo caso per la scrittura e per la lettura si può usare un sottoinsieme dei  $2^r - 1$  livelli di riferimento disponibili. L'esempio estremo e più semplice di questa condizione di funzionamento si ha quando si utilizza una

25 memoria multilivello come normale memoria bilivello.

BERGADANO MIRKO

*(scritto all'Albo n. 843B)*

La scelta di diminuire il numero di bit memorizzati in ogni cella riduce la capacità di memorizzazione della memoria, ma ne aumenta l'affidabilità. Ad esempio, nel caso delle memorie nonvolatili, la riduzione del numero 5 di bit memorizzati in ogni cella consente di garantire la ritenzione dell'informazione per un tempo più lungo e in condizioni ambientali più sfavorevoli.

Normalmente la scelta della modalità di funzionamento viene effettuata in modo permanente dal 10 produttore. In particolare, la scelta di questa modalità di funzionamento può essere interessante per ottenere una memoria con un numero minore di bit per cella come sottoselezione di una progettata per contenere un numero maggiore di bit, al fine di una complessiva riduzione 15 dei costi, oppure questa modalità di funzionamento può essere adottata o perché esiste l'esigenza di ricavare da un medesimo dispositivo di memoria tagli di memoria differenti, oppure più semplicemente per motivi di "debug" del dispositivo di memoria; infatti, quando si 20 realizza il primo prototipo su silicio di un nuovo dispositivo di memoria può essere utile poter passare a modalità di funzionamento più semplici di quelle normali per permettere di verificare il funzionamento delle circuiterie in circostanze meno critiche di quelle 25 nominali.

Attualmente, poi, per soddisfare le crescenti richieste del mercato, si stanno progettando dispositivi di memoria in cui anche l'utilizzatore finale possa decidere la modalità di funzionamento in base al tipo di 5 impiego del dispositivo, e di conseguenza è sempre più sentita l'esigenza di adottare un codice di controllo dell'errore polivalente che sia in grado, utilizzando gli stessi circuiti, di proteggere i dati immagazzinati in celle che funzionano a un numero diverso di livelli.

10        Tale esigenza è ulteriormente rafforzata dal fatto che i dispositivi di memoria delle prossime generazioni, con grande capacità di memorizzazione, potranno essere configurabili settore per settore ed avere quindi settori interni impostati con un numero diverso di bit 15 per cella (si veda ad esempio il brevetto statunitense US 5,574,879). Dispositivi di memoria di questo tipo potranno ad esempio essere utilizzati all'interno di carte multimediali, consentendo di memorizzare in settori a basso numero di bit per cella il microcodice 20 per il microprocessore che gestisce la carta e in settori ad alto numero di bit per cella i dati dell'utente.

Tuttavia, i codici a controllo dell'errore abitualmente utilizzati nelle memorie Flash sono codici 25 a blocchi realizzati con reti logiche CMOS e la loro

BERGADANO MIRKO

*(firma)* Città di Asti n. 243B

funzionalità è fissata una volta per tutte quando il dispositivo di memoria viene progettato. Infatti, durante la definizione di questo tipo di codici il progettista fissa una volta per tutte alcune

5 caratteristiche strutturali del codice che ne vincolano i limiti di utilizzo allo specifico ambito per il quale il codice è stato progettato. In particolare, durante la fase di progetto del codice vengono scelti il numero di bit su cui il codice deve operare, la capacità

10 correttiva e l'alfabeto ed il numero di simboli dell'alfabeto con cui operare.

Da queste scelte dipende il numero di bit di parità necessari e pertanto risulta evidente che codici a controllo dell'errore che operano efficacemente in

15 dispositivi di memoria memorizzanti un determinato numero di bit per cella sono differenti da codici a controllo dell'errore progettati per operare in dispositivi di memoria memorizzanti un numero di bit per cella inferiore.

20 Scopo della presente invenzione è quindi quello di fornire un metodo che consenta di utilizzare lo stesso codice a controllo dell'errore progettato per operare su celle di memoria memorizzanti un determinato numero di bit per cella anche quando queste ultime memorizzano un

25 numero di bit per cella inferiore.

BERGADANO MIRKO

(iscritto nell'Albo n. 343B)

Secondo la presente invenzione viene realizzato un metodo di controllo dell'errore in celle di memoria multilivello memorizzanti un numero di bit configurabile, come definito nella rivendicazione 1.

5 Per una migliore comprensione della presente invenzione viene ora descritta una forma di realizzazione preferita, a puro titolo di esempio non limitativo e con riferimento ai disegni allegati, nei quali:

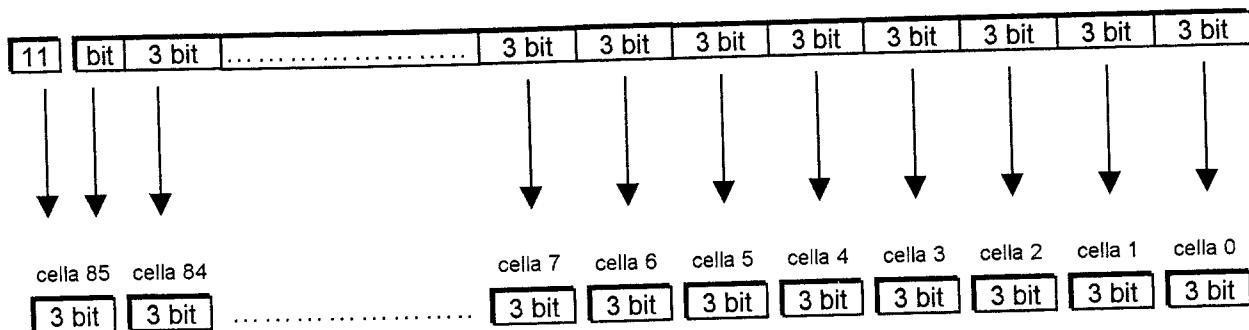

10 - la figura 1 mostra l'organizzazione dei bit di una stringa sulla quale agisce un codice a controllo dell'errore operante su simboli formati da tre bit e l'associazione di tali bit a celle di memoria a tre bit;

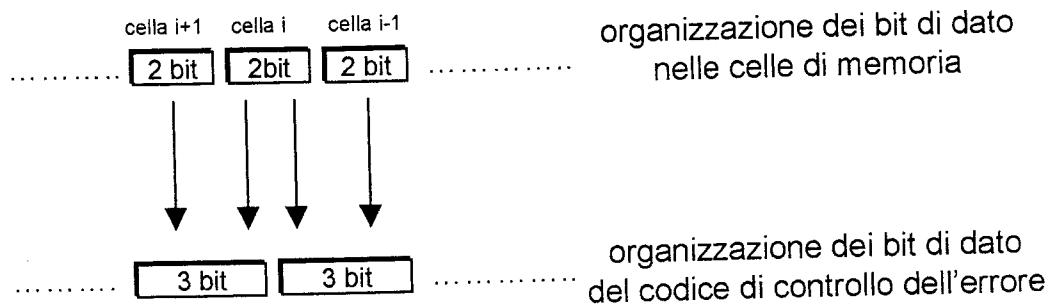

15 - la figura 2 mostra l'organizzazione dei bit di una parola di informazione memorizzati in celle di memoria a due bit, l'organizzazione dei bit di una stringa sulla quale agisce un codice a controllo dell'errore operante su simboli formati da tre bit ciascuno, ed una incorretta associazione fra i bit della 20 parola di informazione ed i bit dei simboli su quali agisce il suddetto codice a controllo dell'errore;

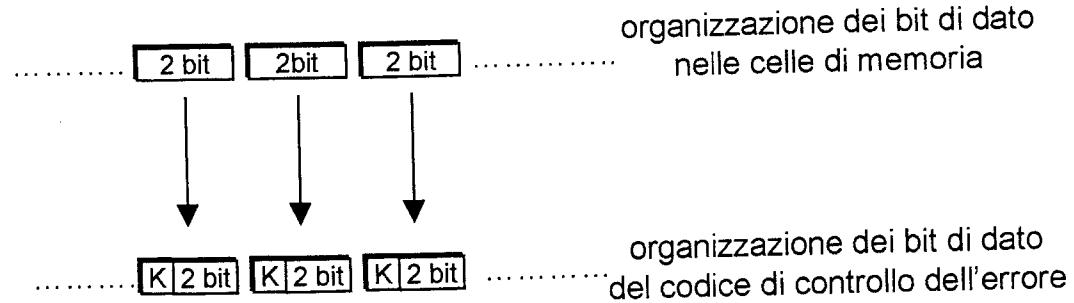

25 - la figura 3 mostra l'organizzazione dei bit di una parola di informazione memorizzati in celle di memoria a due bit, l'organizzazione dei bit di una stringa sulla quale agisce un codice a controllo

BERGADÀNO MIRKO

*(Iscritto all'Albo n. 843B)*

dell'errore operante su simboli formati da tre bit ciascuno, ed una corretta associazione fra i bit della parola di informazione ed i bit dei simboli su quali agisce il suddetto codice a controllo dell'errore;

5 - la figura 4 mostra una stringa binaria secondo la presente invenzione ottenuta a partire dai bit di una parola di informazione memorizzati in celle di memoria a due bit e sulla quale agisce un codice a controllo dell'errore operante su simboli formati da tre bit;

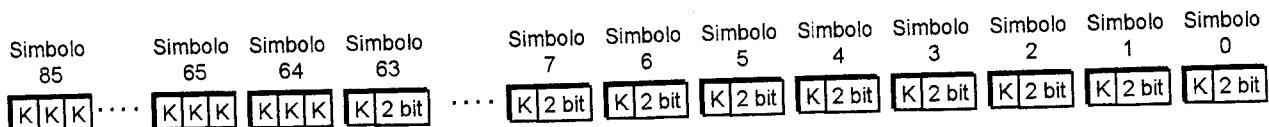

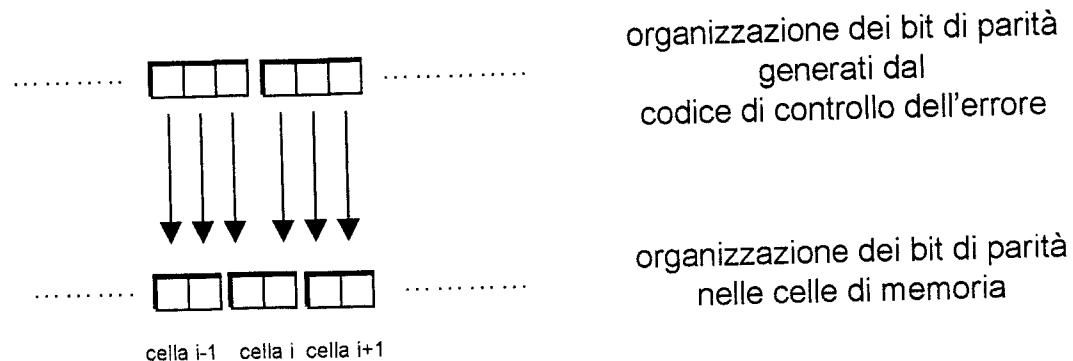

10 - la figura 5 mostra l'organizzazione dei bit di parità generati dal codice a controllo dell'errore, l'organizzazione dei bit di parità in celle di memoria a due bit, ed una errata memorizzazione dei bit di parità nelle celle di memoria a due bit; e

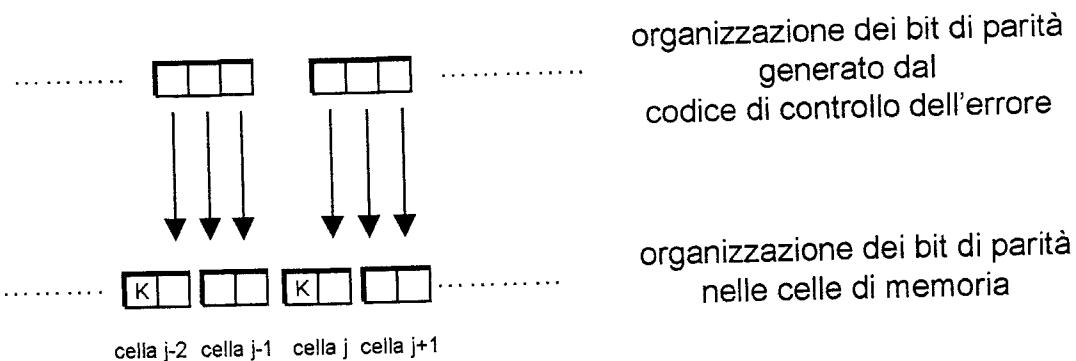

15 - la figura 6 mostra l'organizzazione dei bit di parità generati dal codice a controllo dell'errore, l'organizzazione dei bit di parità in celle di memoria a due bit, ed una corretta memorizzazione dei bit di parità nelle celle di memoria a due bit.

20 Per facilitare la comprensione della presente invenzione verranno qui di seguito introdotte alcune notazioni relative alla codifica lineare a blocco utilizzata per rivelare e correggere errori in memorie multilivello. Per una trattazione più dettagliata di

25 tale argomento si vedano ad esempio W. W. Peterson, E.

J. Weldon, *Error-Correcting Codes*, 2<sup>nd</sup> ed., M.I.T. Press, Cambridge (Massachusetts), 1972, ed R. E. Blahut, *Theory and Practice of Error Control Codes*, Addison-Wesley, Reading (Massachusetts), 1983.

5 In particolare, chiamiamo simboli  $q$ -ari gli elementi di un alfabeto contenente  $q$  simboli distinti, chiamiamo *parola di informazione* il vettore di  $k$  simboli  $q$ -ari da scrivere nella memoria e lo indichiamo con:

10

$$\underline{i} = (i_1, i_2, \dots, i_k)$$

Nella codifica lineare a blocco, la parola di informazione viene mappata biunivocamente in un vettore di  $n$  simboli  $q$ -ari (con  $n > k$ ), che chiamiamo *parola di codice* e indichiamo con:

15

$$\underline{c} = (c_1, c_2, \dots, c_n)$$

L'operazione di codifica può essere descritta in forma algebrica introducendo la matrice  $\mathbf{G}$ , chiamata *matrice generatrice* del codice (si veda a tale proposito

20 W. W. Peterson, E.J. Weldon, *Error-Correcting Codes*, 2<sup>nd</sup> ed., M.I.T. Press, Cambridge (Massachusetts), 1983).

Ogni parola di codice  $\underline{c}$  può essere generata semplicemente effettuando il prodotto della parola di informazione per la matrice generatrice, come espresso

25 nella seguente equazione:

BERGADANO MIRKO

(scritto all'Albo n. 843B)

$$\underline{c} = \underline{i} \cdot G$$

dove  $\underline{i}$  e  $\underline{c}$  sono vettori riga.

La matrice  $G$  è una matrice rettangolare con  $k$  righe,  $n$  colonne e rango  $k$  (affinché l'applicazione  $\underline{i} \rightarrow \underline{c}$  sia iniettiva).

Per ogni codice lineare  $(n, k)$  esiste una matrice  $H$ , chiamata *matrice del controllo di parità* (si veda il succitato testo *Error-Correcting Codes*), avente  $n-k$  righe e  $n$  colonne, tale che:

$$G \cdot {}^t H = 0$$

dove  $0$  indica la matrice  $k \times (n-k)$  con elementi tutti nulli, e  ${}^t H$  indica la trasposta della matrice  $H$ .

Gli  $n-k$  simboli, aggiunti durante la codifica, prendono il nome di *simboli di parità* o *simboli di controllo*.

Chiamiamo *codice  $q$ -ario*  $(n, k)$  l'insieme delle  $q^k$  parole di codice ottenute dalla codifica di tutte le possibili parole di informazione e definiamo *capacità di correzione* del codice  $q$ -ario  $(n, k)$  il numero  $t$  di errori (cioè di simboli  $q$ -ari errati) per parola che il codice è in grado di correggere.

La seguente disequazione, nota col nome di limite di Hamming (si veda il succitato testo *Error-Correcting*

Codes), fornisce il minimo numero di simboli di parità richiesti affinché un codice lineare  $q$ -ario ( $n, k$ ) abbia capacità di correzione  $t$ :

$$q^{n-k} \geq \sum_{i=0}^t \binom{n}{i} (q-1)^i \quad (1)$$

5 Alla luce delle notazioni sopra introdotte ed al solo scopo di facilitare la comprensione della presente invenzione, verrà qui di seguito descritta l'applicazione del metodo secondo la presente invenzione a un esempio specifico, e successivamente ne verrà 10 quindi illustrata l'applicabilità al caso generale.

In particolare, qui di seguito verrà descritto il metodo che consente l'utilizzazione di un codice a controllo dell'errore progettato per operare efficacemente su celle di memoria memorizzanti 3 bit per 15 cella anche quando queste celle di memoria vengono utilizzate per memorizzare 2 soli bit per cella.

Si prenda inoltre in considerazione il caso di un codice a controllo dell'errore agente su parole di informazione di 256 bit formate da simboli di tre bit ciascuno, ed in grado di rilevare e correggere al più 20 gli errori causati dal malfunzionamento di una stessa cella di memoria, ovvero l'errore di un singolo bit, l'errore di 2 bit e l'errore di 3 bit imputabili a tale

BERGADANO MARKO

fischiato dall'Albo n. 8438

cella di memoria ( $t = 1$ ).

Nel caso preso in considerazione, una soluzione ottimale è quella di realizzare un codice a controllo dell'errore su di uno spazio vettoriale  $GF(2^3)$ , ossia uno spazio vettoriale di Galois in cui i possibili simboli dell'alfabeto sono otto, come otto sono le distribuzioni salvate in una singola cella di memoria.

Per una trattazione dettaglia dell'argomento si veda ad esempio il succitato *Theory and Practice of Error Control Codes*.

Nella figura 1 è mostrata l'organizzazione dei bit della stringa sulla quale agisce il suddetto codice a controllo dell'errore e l'associazione di tali bit a celle di memoria a tre bit.

In particolare, come illustrato in tale figura, i 256 bit della parola di informazione vengono memorizzati in 86 celle di memoria a 3 bit; una delle 86 celle di memoria è parzialmente utilizzata e contiene 2 bit fissati al valore logico "11" e un bit della parola di informazione.

Supponendo che per l'applicazione a cui è destinato il codice sia sufficiente correggere un solo errore per parola di informazione ( $t = 1$ ), alle 86 celle di memoria che contengono la parola di informazione, il codice aggiunge cinque simboli di parità di 3 bit ciascuno, per

BERGADANO MIRKO

Iscriz. all'Albo n. 840

un totale di 15 bit, che vengono memorizzati in cinque

celle di memoria. Tale numero è fissato dalla

disuguaglianza di Hamming precedentemente riportata, in

cui  $q = 8$  (numero di simboli dell'alfabeto),  $k = 86$

5 (numero di simboli della parola di informazione),  $n = 91$

(somma del numero di simboli della parola di

informazione e del numero di simboli di parità) e  $t = 1$

(numero di simboli errati che si vogliono correggere).

Si supponga ora che il dispositivo di memoria passi

10 da una modalità di memorizzazione a tre bit per cella ad

una modalità di memorizzazione a due bit per cella.

In questa differente modalità di memorizzazione, le

86 celle di memoria possono quindi contenere al più 172

bit. È però conveniente fare in modo che il numero di

15 bit contenuto nelle celle di memoria sia una potenza di

due per evitare complicate modifiche all'indirizzamento

delle celle di memoria stesse. Così facendo, infatti, si

mantiene quasi inalterato l'indirizzamento, in quanto è

sufficiente eliminare semplicemente il bit meno

20 significativo degli indirizzi, tornando così ad una

situazione in cui il numero di bit memorizzati nelle

celle di memoria è una potenza di due.

Per far ciò, quindi, nella modalità di

memorizzazione a due bit per cella, è opportuno che

25 nelle 86 celle di memoria vengano memorizzati soltanto

128 bit, anziché 172. La memorizzazione di 128 bit richiede però soltanto 64 celle di memoria, per cui 22 delle 86 disponibili rimangono inutilizzate.

La rete logica che implementa il codice a correzione di errore opera però sempre su una stringa binaria di 256 bit e genera 15 bit di controllo.

5

L'idea per consentire ugualmente l'utilizzo del codice a controllo dell'errore già presente è pertanto quella di fornire alla circuiteria di codifica una stringa binaria di 256 bit formata da una porzione di dato vero e proprio costituita dai 128 bit memorizzati nelle 64 celle di memoria e costituenti la parola di informazione vera e propria, e da una porzione costante costituita da bit aventi ciascuno un valore logico determinato o costante.

10

15

L'aggiunta dei bit aventi un valore logico costante alla parola di informazione deve essere fatta con attenzione tenendo in considerazione come agisce il codice a controllo dell'errore e come vengono memorizzati i bit nelle celle di memoria.

20

In particolare, per come è stato illustrato precedentemente, il codice a controllo dell'errore è pensato per operare su simboli di tre bit, per cui sarebbe scorretto generare la stringa binaria di 256 bit nel modo illustrato nella figura 2, nella quale sono

25

BERGADÀNO Milko

(Scribo ex Albo n. 843B)

mostrate l'organizzazione dei bit della parola di informazione memorizzati in celle di memoria a due bit, l'organizzazione dei bit della stringa sulla quale agisce il codice a controllo dell'errore.

5        In particolare, secondo quanto mostrato in tale figura, sarebbe scorretto associare semplicemente la porzione di dato vero e proprio memorizzata (parola di informazione vera e propria) alla parte meno significativa o più significativa della stringa di 256

10      bit sulla quale il codice a controllo dell'errore opera, perché potrebbero verificarsi situazioni non corrette in cui errori causati dal malfunzionamento di una stessa cella di memoria facciano parte di due simboli differenti.

15      Infatti, se si effettuasse l'associazione schematizzata nella figura 2, un errore imputabile alla cella  $i$ -esima che coinvolge entrambe i due bit in essa contenuti non verrebbe corretto dal codice di controllo dell'errore perché tale codice è progettato per

20      correggere uno più errori facenti parte del medesimo gruppo di tre bit corrispondenti a una singola cella di memoria.

L'associazione fra i bit della parola di informazione ed i bit dei simboli su quali agisce il

25      codice a controllo dell'errore che consente di evitare

BERGADANCO MIRKO

fiscttto all'Albo n. 34381

il problema appena descritto è schematizzata invece nella figura 3 e consiste nell'aggiungere un bit avente un valore logico costante ad ogni coppia di bit della parola di informazione memorizzati in una cella di memoria a due bit.

In altri termini, la parte più significativa o meno significativa di un simbolo di tre bit viene costituita dalla coppia di bit memorizzati nella cella di memoria a due bit, mentre la restante parte del simbolo è costituita da un bit avente un valore logico costante.

Si evita così facendo l'inconveniente sopra menzionato perché la capacità correttiva del codice, che agisce su tre errori adiacenti, risulta associata ad una singola cella di memoria.

Risulta evidente che nella matrice di memoria vengono salvati solo i bit di informazione e non quelli aggiunti per consentire il calcolo dei bit di parità.

L'associazione sopra mostrata non porta però ancora alla formazione di una stringa binaria di 256 bit, per cui alla sottostringa ottenuta inserendo un bit avente un valore logico costante dopo ogni coppia di bit della parola di informazione è opportuno inserire nella parte più significativa o meno significativa della stringa binaria di 256 bit una ulteriore sottostringa di bit

MIRKO

BORGATICO

Iscritto all'Albo n. 843B/

a venti valore logico costante.

In particolare, nell'esempio preso in considerazione, per fornire al codice a controllo dell'errore una stringa di 256 bit, si devono aggiungere

5  $22 \cdot 3 = 66$  bit aventi valore logico costante, ottenendo così la stringa binaria mostrata nella figura 4, in cui i 66 bit sono indicati con K e sono stati inseriti nella parte più significativa della stringa.

Il valore logico K da associare ai bit costanti è

10 legato alla convenzione che impone che le celle di memoria dopo una cancellazione siano considerate tutte ad un livello logico "1", comprese le celle di memoria nelle quali vengono memorizzati i bit di parità.

Infatti, dato che l'operazione di cancellazione

15 coinvolge indistintamente sia le celle di memoria in cui sono memorizzati i bit della parola di informazione che le celle di memoria in cui solo memorizzati i bit di parità, il codice a controllo dell'errore deve associare alla parola di informazione formata da bit aventi tutti

20 valore logico "1", bit di parità aventi tutti valore logico "1", per evitare situazioni di inconsistenza dopo una cancellazione.

Per consentire l'utilizzo del codice a controllo dell'errore già presente anche quando la modalità di

25 memorizzazione del dispositivo di memoria viene cambiata

BERGAMANO MILANO

*(Iscritto all'Albo n. 243B)*

da tre bit per cella a due bit per cella, anche la memorizzazione dei bit di parità generati dal codice a controllo dell'errore (che sono sempre 15) richiede una gestione opportuna.

5        In particolare, le cinque celle di memoria che durante la modalità di memorizzazione a tre bit per cella servivano a memorizzare i 15 bit di parità diventano evidentemente insufficienti durante la modalità di memorizzazione a due bit per cella; infatti,

10      si devono memorizzare 15 bit e le cinque celle di memoria possono in questa seconda modalità di memorizzazione memorizzare solo 10 bit.

Per superare questo problema, si possono utilizzare parte delle 22 celle di memoria che nel passaggio dalla

15      modalità di memorizzazione a tre bit per cella alla modalità di memorizzazione a due bit per cella sono divenute sovrabbondanti.

Anche in questo caso bisogna prestare attenzione a come si associano i bit di parità alle celle di memoria.

20      Infatti, ogni gruppo di tre bit di parità deve essere indipendente dai restanti, per cui non è possibile effettuare un'associazione del tipo mostrato nella figura 5, nella quale sono mostrate l'organizzazione dei bit di parità generati dal codice a controllo dell'errore e l'organizzazione dei bit di parità in

BERGADANO MIRKO

(iscritto all'Albo n. 843B)

celle di memoria a due bit.

In particolare, secondo quanto mostrato in tale figura, sarebbe scorretto memorizzare due bit di un simbolo in una determinata cella di memoria ed il terzo bit dello stesso simbolo in una cella di memoria differente, in quanto questa associazione potrebbe far sì che un errore nella cella di parità *i* che coinvolge entrambe i bit in essa memorizzati possa provocare che il codice a controllo dell'errore esegua una correzione 10 in questa o in altra posizione in maniera incontrollata perché l'errore va oltre la capacità di correzione del medesimo (si ricorda infatti che una delle ipotesi alla base della presente invenzione è quella che il codice a controllo dell'errore sia in grado di rilevare e 15 correggere errori imputabili al malfunzionamento di una singola cella di memoria).

Per evitare questo problema i tre bit di un simbolo non devono essere memorizzati in celle di memorie condivise con i bit di altri simboli.

20 Un'associazione efficace è ad esempio quella mostrata nella figura 6, in cui due bit di un simbolo vengono memorizzati in una determinata cella di memoria mentre il terzo bit dello stesso simbolo viene memorizzato in una cella di memoria differente, nella 25 quale non viene poi memorizzato un bit di un altro

BERGADANO MIRKO

Iscritto all'Albo n. 84387

simbolo bensì un bit avente un valore logico costante.

Questa associazione evita i problemi precedentemente indicati e consente che un errore che si verifica sulla cella  $j$  possa essere recuperato dal 5 codice a controllo dell'errore. Con questa associazione ogni errore che si verifica su di una cella può essere corretto dal codice a controllo dell'errore senza modificare la rete logica che lo implementa.

Il principio inventivo sopra descritto 10 relativamente al passaggio da una modalità di memorizzazione a tre bit per cella ad una modalità di memorizzazione a due bit per cella, può poi essere generalizzato anche al passaggio da una modalità di memorizzazione a  $r$  bit per cella ad una modalità di memorizzazione a  $s$  bit per cella. 15

In questo caso generale, il codice a controllo dell'errore opera su di uno spazio vettoriale  $GF(2^r)$ , ossia su di uno spazio vettoriale di Galois in cui i possibili simboli  $q$ -ari sono  $2^r$ , e su una stringa di  $b$  20 bit, mentre i  $p$  bit di parità generati dall'operazione di codifica possono essere calcolati utilizzando la disuguaglianza di Hamming sopra riportata.

In particolare, quando si opera nella modalità di memorizzazione a  $s$  bit per cella, dato che il codice a controllo dell'errore è progettato per operare su 25

BERGADANO MARKO

(scritto nell'Albo n. 843B)

simboli di  $r$  bit, ciascuno di questi deve essere formato dagli  $s$  bit memorizzati in una cella di memoria, ai quali si aggiungono  $r - s$  bit aventi valore logico predeterminato. Gli  $s$  bit memorizzati in una cella di memoria vengono disposti nella parte meno significativa, mentre gli  $r - s$  bit aventi valore logico predeterminato vengono disposti nella parte più significativa.

Inoltre, dato che il codice a controllo dell'errore è progettato per operare su una stringa di  $b$  bit, nella parte significativa o meno significativa della stringa si devono inserire un ulteriore insieme di bit aventi valore logico predeterminato in numero sufficiente a portare la lunghezza della stringa ad essere pari a  $b$  bit.

Delle  $k$  celle di memoria che nella modalità di memorizzazione a  $r$  bit per cella contenevano  $i$  bit della parola di informazione, nella modalità di memorizzazione a  $s$  bit un numero  $m$  di queste celle di memoria saranno utilizzate per memorizzare i bit di informazione, mentre le restanti potranno essere utilizzate per memorizzare alcuni dei  $p = n - k$  bit di parità che non possono essere memorizzati nelle celle di memoria che nella modalità di memorizzazione a  $r$  bit riuscivano a contenere tutti i  $p$  bit di parità.

Inoltre, nella modalità di memorizzazione a  $s$  bit,

la memorizzazione dei  $p$  bit di parità viene effettuata in modo analogo a quanto sopra descritto, ossia facendo in modo che due simboli di parità non condividano alcuna cella di memoria, ossia che ogni simbolo di  $r$  bit sia 5 memorizzato in un insieme di celle di memorie distinto dagli insiemi di celle di memoria utilizzati per la memorizzazione degli altri simboli di  $r$  bit. In particolare, la memorizzazione di un gruppo di  $r$  bit riempirà completamente  $r/s$  celle di memoria, mentre i 10 rimanenti  $R\{r/s\}$  bit, dove  $R\{r/s\}$  indica il resto della divisione  $r/s$ , vengono memorizzati in un'altra cella di memoria insieme a  $s - R\{r/s\}$  bit costanti.

Da un esame delle caratteristiche della presente invenzione sono evidenti i vantaggi che essa consente di 15 ottenere.

Risulta infine chiaro che a quanto qui descritto ed illustrato possono essere apportate modifiche e varianti senza per questo uscire dall'ambito protettivo della presente invenzione, come definito nelle rivendicazioni 20 allegate.

In particolare, si sottolinea il fatto che così come nella costruzione della stringa binaria su cui agisce il codice a controllo dell'errore l'insieme di bit aventi valore logico costante possono essere 25 indifferentemente inseriti sia nella parte più

BERGADANCO Marco

(Iscritto all'Anagrafe n. 843B)

significativa che nella parte meno significativa della stringa binaria, in modo analogo nella costruzione di un simbolo di informazione nella modalità di memorizzazione a  $s$  bit per cella i bit aventi valore logico costante aggiunti agli  $s$  bit memorizzati in ciascuna cella di memoria possono essere indifferentemente inseriti sia nella parte più significativa che nella parte meno significativa del simbolo di informazione.

BERGAMO

Iscr. all'Albo n. 8436

1970

## R I V E N D I C A Z I O N I

1. Metodo di controllo dell'errore in celle di memoria multilivello memorizzanti un numero di bit configurabile, detto controllo dell'errore essendo

5 effettuato utilizzando un codice a controllo dell'errore operante, in codifica, su stringhe binarie di  $b$  bit formate da  $k$  simboli di informazione di  $r$  bit ciascuno; caratterizzato dal fatto che, quando dette celle di memoria memorizzano un numero  $s$  di bit minore di  $r$ , un

10 detto simbolo di informazione viene formato con i bit di informazione memorizzati in una detta cella di memoria, e con  $r - s$  bit aventi ciascuno un determinato valore logico.

2. Metodo di controllo dell'errore secondo la

15 rivendicazione 1, caratterizzato dal fatto che detti  $r - s$  bit aventi un determinato valore logico sono disposti nella parte più significativa del simbolo di informazione.

3. Metodo di controllo dell'errore secondo la

20 rivendicazione 1, caratterizzato dal fatto che detti  $r - s$  bit aventi un determinato valore logico sono disposti nella parte meno significativa del simbolo di informazione.

4. Metodo di controllo dell'errore secondo una

25 qualsiasi delle rivendicazioni precedenti,

BERGADANO MIRKO

(Iscritto all'Albo n. 843B)

caratterizzato dal fatto che, quando dette celle di memoria memorizzano un numero  $r$  di bit, un detto simbolo di informazione viene formato solo con i bit di informazione memorizzati in una detta cella di memoria.

5        5. Metodo di controllo dell'errore secondo una qualsiasi delle rivendicazioni precedenti, caratterizzato dal fatto che quando dette celle di memoria memorizzano un numero  $r$  di bit, ciascuna di dette stringhe binarie viene memorizzata utilizzando  $k$

10      celle di memoria multilivello; e dal fatto che, quando dette celle di memoria memorizzano un numero  $s$  di bit minore di  $r$ , in dette  $k$  celle di memoria multilivello viene memorizzato soltanto un numero  $m$  di bit di informazione pari ad una potenza di due; dette  $k$  celle

15      di memoria multilivello risultando così suddivise in un primo sottoinsieme di celle di memoria nelle quali vengono memorizzati detti  $m$  bit di informazione, ed in un secondo sottoinsieme di celle di memoria non utilizzate per memorizzare bit di informazione.

20        6. Metodo di controllo dell'errore secondo la rivendicazione 5, caratterizzato dal fatto che quando dette celle di memoria memorizzano un numero  $s$  di bit minore di  $r$  e in dette  $k$  celle di memoria multilivello viene memorizzato soltanto un numero  $m$  di bit di

25      informazione pari ad una potenza di due, una detta

BERGADANO MIRKO

Iscritto all'Albo n. 8433

stringa binaria di  $b$  bit viene formata utilizzando un ulteriore insieme di bit aventi ciascuno un determinato valore logico.

7. Metodo di controllo dell'errore secondo la

5 rivendicazione 6, caratterizzato dal fatto che detto un ulteriore insieme di bit aventi un determinato valore logico è disposto nella parte più significativa della stringa binaria.

8. Metodo di controllo dell'errore secondo la

10 rivendicazione 6, caratterizzato dal fatto che detto un ulteriore insieme di bit aventi un determinato valore logico è disposto nella parte meno significativa della stringa binaria.

9. Metodo di controllo dell'errore secondo una

15 qualsiasi delle rivendicazioni da 5 a 8, caratterizzato dal fatto che detto codice a controllo dell'errore fornisce un insieme di  $p$  simboli di parità di  $r$  bit; e dal fatto che, quando dette celle di memoria memorizzano un numero  $s$  di bit minore di  $r$ , i bit di ciascun simbolo

20 di parità vengono memorizzati in un insieme di celle di memoria distinto dagli insiemi di celle di memoria utilizzati per memorizzare i bit dagli altri simboli di parità.

10. Metodo di controllo dell'errore secondo la

25 rivendicazione 9, caratterizzato dal fatto che almeno

BERGADANO MiRKO

Iscritto all'Albo n. 8433

alcuni dei bit di detti simboli di parità vengono memorizzati nelle celle di memoria appartenenti al detto secondo sottoinsieme di dette  $k$  celle di memoria.

11. Metodo di controllo dell'errore secondo una

5 qualsiasi delle rivendicazioni precedenti,

caratterizzato dal fatto che il determinato valore

logico di ciascuno dei bit aggiunti ai bit di

informazione per la formazione di detto simbolo e di

detta stringa binaria è determinato sulla base della

10 convenzione che impone che le celle di memoria dopo una

cancellazione siano considerate tutte memorizzanti un

valore logico "1", comprese le celle di memoria

memorizzanti i bit di parità associati dal codice a

controllo dell'errore alla parola di informazione da

15 codificare, e dalla convenzione che impone che ad una

parola di informazione da codificare formata da bit

aventi tutti valore logico "1" il codice a controllo

dell'errore associ bit di parità aventi tutti valore

logico "1".

20 12. Metodo di controllo dell'errore in celle di

memoria multilivello memorizzanti un numero di bit

configurabile, sostanzialmente come descritto con

riferimento ai disegni allegati.

p.i.: STMICROELECTRONICS S.R.L.

BERGADANO MIRKO

(scritto all'Albo n. 843B)

TO 2001A 9 00 52 9

Fig.1

Fig.2

Fig.3

T0 2001A000329

Fig.4

Fig.5

Fig.6

p.i.: STMICROELECTRONICS S.R.L.

BERGAMASCO MIRKO

(Iscritto all'Albo n. 8438)