(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-147500

(P2010-147500A)

(43) 公開日 平成22年7月1日(2010.7.1)

(51) Int.Cl.

H01L 23/29 (2006.01)

H01L 23/31 (2006.01)

H01L 21/3205 (2006.01)

H01L 23/52 (2006.01)

F 1

H01L 23/30

H01L 21/88D

T

テーマコード(参考)

4M109

5FO33

審査請求 有 請求項の数 7 O L (全 8 頁)

(21) 出願番号 特願2010-37667 (P2010-37667)

(22) 出願日 平成22年2月23日 (2010.2.23)

(62) 分割の表示 特願2003-546400 (P2003-546400)

の分割

原出願日 平成14年11月20日 (2002.11.20)

(31) 優先権主張番号 01204504.3

(32) 優先日 平成13年11月23日 (2001.11.23)

(33) 優先権主張国 欧州特許庁 (EP)

(71) 出願人 500262038

台湾積體電路製造股▲ふん▼有限公司

Taiwan Semiconductor Manufacturing Company, Ltd.

台湾新竹科學工業園區新竹市力行六路八號

8, Li-Hsin Rd. 6, Hsinchu Science Park, Hsinchu, Taiwan 300-777, R. O. C.

(74) 代理人 100117787

弁理士 勝沼 宏仁

(74) 代理人 100082991

弁理士 佐藤 泰和

最終頁に続く

(54) 【発明の名称】半導体デバイス

## (57) 【要約】

【課題】機械的なストレスを減少させた半導体デバイスを提供する。

【解決手段】キャリア及び集積回路(10)を有する半導体デバイスにおいて、前記集積回路は、1つ以上の半導体素子と、前記半導体素子が接している1つ以上の接続領域と、前記接続領域を覆うパッシベーションレイヤ(20)とを有し、エンベロープにより周囲から絶縁され、前記エンベロープは相互境界面を持つ内部レイヤ(21)及び外部レイヤ(16)を有し、前記キャリアは、前記接続領域に接続手段により接続される導電部分を有し、前記相互境界面が、前記内部レイヤと前記外部レイヤとが分離した領域である層間剥離エリア(22)を完全に囲み、その結果、前記層間剥離エリアが前記接続領域から絶縁される。

【選択図】図3

**【特許請求の範囲】****【請求項 1】**

キャリア及び集積回路を有する半導体デバイスであり、

前記集積回路は、1つ以上の半導体素子と、前記半導体素子が接している1つ以上の接続領域と、前記接続領域を覆うパッシベーションレイヤとを有し、エンベロープにより周囲から絶縁され、前記エンベロープは相互境界面を持つ内部レイヤ及び外部レイヤを有し、

前記キャリアは、前記接続領域に接続手段により接続される導電部分を有し、

前記相互境界面が、前記内部レイヤと前記外部レイヤとが分離した領域である層間剥離エリアを完全に囲み、その結果、前記層間剥離エリアが前記接続領域から絶縁されることを特徴とする半導体デバイス。

**【請求項 2】**

前記層間剥離エリア及び前記相互境界面は、前記内部レイヤの表面上に置かれ、前記層間剥離エリアは前記内部レイヤの表面エリアの30%から70%の間の大きさであることを特徴とする請求項1に記載の半導体デバイス。

**【請求項 3】**

前記パッシベーションレイヤと前記内部レイヤは前記接続領域にあるボンディングパッドが露出したままであることを特徴とする請求項1に記載の半導体デバイス。

**【請求項 4】**

一定量の硬化される合成樹脂が前記層間剥離エリアに置かれることを特徴とする請求項1に記載の半導体デバイス。

**【請求項 5】**

前記エンベロープは前記キャリアに、又はキャリア上に取り付けられることを特徴とする請求項1に記載の半導体デバイス。

**【請求項 6】**

前記キャリアはリードフレームであることを特徴とする請求項1に記載の半導体デバイス。

**【請求項 7】**

前記一定量の硬化される合成樹脂はエポキシ樹脂であることを特徴とする請求項4に記載の半導体デバイス。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、キャリアと、1つ以上の半導体素子及びこれら半導体素子が接している1つ以上の接続領域を有する集積回路とを有する半導体デバイスについて、この回路はエンベロープ(envelope)により周囲から絶縁され、このエンベロープは相互境界面を持つ内部レイヤ及び外部レイヤを持ち、前記キャリアは接続手段により前記接続領域に接続される導電部分を有する。

**【背景技術】****【0002】**

このような半導体デバイスは、特開昭62-185343号から既知である。この既知のデバイスの内部レイヤはシリコン材料を有する。外部レイヤは水晶又はガラス粉末を充填したエポキシ樹脂を有する。さらに、相互接続構造が設けられる。接続手段はボンドワイヤ(bond wire)である。前記集積回路は、他の処理及び後の使用寿命中に破損及び汚れから守られるように、パッシベーションレイヤで覆われる。このレイヤは例えば燐珪酸ガラス(phosphorus silicate glass)又は窒化珪素からなる1つ以上のレイヤからなる。

**【0003】**

内部レイヤの材料と外部レイヤの材料との間に有する熱膨張係数の差異は、温度が変化する場合、特に集積回路の寸法がかなり大きい場合、半導体デバイスに大きな機械的ストレスを生じさせてしまう。これは、チップスケールパッケージ(CSP)型のエンベロープ

10

20

30

40

50

が用いられる場合である。これらのストレス及びこれらストレスのせいではパッシベーション層に現れる微細な亀裂(micro-crack)が回路を破損させてしまうので、半導体デバイスの機能的欠陥及び故障さえも起こってしまう。周囲の水分が前記亀裂を通り前記回路に到達し、そこに腐食が起こる。前記欠陥を減少させるために、合成樹脂材料、例えばポリアミド及びシリコン樹脂からなる内部レイヤが慣例的に用いられる。

#### 【0004】

既知のデバイスの内部レイヤは、外部レイヤからの圧力に対する耐性を持たせるために、マイクロカプセル(microcapsule)を含んでいる。処理が加圧下で行われる外部レイヤの密閉は温度を上昇させ、マイクロカプセル内に存在するガスが漏れてくる。このガスがエンベロープの内部レイヤと外部レイヤとの間の空隙を形成する。

10

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0005】

この既知のデバイスの欠点は、空隙の存在が外部レイヤに非常に厳しい必要条件を課すことである。この外部レイヤが何処か一点において完全に封止されていない場合、水分が前記空隙を通り接続領域に到達することができ、これによりこの水分が集積回路内に浸透してしまう。加えて、漏れているガスは、特にこの漏れが完全に制御された方法では起こらない又はガスの一部が後の段階で漏れる場合に、外部レイヤにおいてストレスとなり、この外部レイヤの破損につながる。

#### 【課題を解決するための手段】

20

#### 【0006】

従って、本発明の第1の目的は、機械的ストレスが減少する冒頭の段落に述べられた型式の半導体デバイスを提供することである。

#### 【0007】

この第1の目的は、前記相互境界面が層間剥離エリア(delamination area)の完全な境界を形成し、この結果として、層間剥離エリアの完全な境界の形成がボンディングパッドから絶縁されることを達成することである。機械的ストレスは層間剥離エリアを作ることにより制御されたやり方で取り除かれることができる。この層間剥離エリアは密封されているので、このエリアを通り集積回路に水分が浸透する又はさもなくばこの回路に損害を与える機会は無い。

30

#### 【0008】

前記層間剥離エリアは、相互境界面として内部レイヤの表面に又は表面上に置かれる。この層間剥離エリアは、内部レイヤの表面の30%から70%の大きさとなることが好ましい。この層間剥離エリアの大きさと接着エリアの大きさとの間の比率がよく作用するような経験が示される。最適な比率は内部レイヤと外部レイヤとの間の膨張係数の差に依存していることが分かっている。これにより、接着剤がちょうど集積回路の接続領域の周囲にだけある。しかしこれでも十分である。機械的ストレスを免れ得る場合、内部レイヤの残りの部分を外部レイヤに接着させる必要は無くなる。

#### 【0009】

有利な実施例において、一定量の硬化した合成樹脂が層間剥離エリアに存在する。このような合成樹脂の存在は、本発明による方法の実施例の結果である。例えばエポキシ樹脂、アクリル樹脂又はシリコンラバーのような合成樹脂は、ディスペンサーデバイス、インクジェットプリンタを用いて内部レイヤ上に簡単なやり方で置かれ又は何か他の方法で置かれる。この後、合成樹脂及び内部レイヤの表面が活性化される。次いで、外部レイヤが置かれる。合成樹脂で覆われた表面部分は活性化しないので、この合成樹脂と内部レイヤとの間の接着力は活性化された部分よりも良くない。代わりに、合成樹脂が活性化した後にだけ置かれることが可能である。半導体デバイスが後続するはんだ付けプロセスを高い温度で行う場合、機械的ストレスは合成樹脂の不活性である表面に集中するであろう。このプロセス中に層間剥離エリアが形成される。

40

#### 【0010】

50

硬化した合成樹脂の代わりとして、内部レイヤ上に局部的に置かれ、内部レイヤ又は外部レイヤに対し少なくとも相対的に弱い接着力を持つ何か他の材料が用いられてもよい。前記材料が流体として置かれることが利点であるが、この材料が内部レイヤの表面にわたり延在してはいけないことが必要とされる。その上、前記材料は、はんだ付け動作の温度では殆ど膨張してはいけないことが必要とされる。

【0011】

内部レイヤは接続領域を被覆されないまま残すことが好ましい。半導体デバイスの上記実施例は、一般的に知られていて、様々なやり方で応用可能である。既知のボンディング手段は、とりわけはんだのような導電材料からなるボンドワイヤ及び小球体である。代わりには、内部レイヤ自身がボンディング手段である。これは容量性又は誘導性結合が集積回路とキャリアとの間の接合に用いられる場合である。この場合は、識別目的には非常に有利であり、ここではデータ及びエネルギーの転送は制限される。キャリアは読み取り装置との非接触結合を供給するアンテナを有する。

10

【0012】

他の実施例において、エンベロープはキャリアに又はキャリア上に固定される。本発明による半導体デバイスのキャリアは、リードフレームでもよいし、また代わりにプリント基板、セラミック基板又はその他の基板でもよい。本実施例において、これはチップスケールパッケージ型としても知られ、前記被覆の外部レイヤは、集積回路が基板に固定されるまで設けられない。この集積回路はBGA (ball-grid array) 型のボンディングによりキャリア上の導電部分に接続される。それは、前記基板が内部レイヤ及び外部レイヤからなるエンベロープを持つことである。大部分がシリコンである基板と外部レイヤとの間の熱膨張の差が大きいために、層間剥離エリアが存在する場合にも有利である。

20

【0013】

本発明の第2の目的は、機械的ストレスが制御されたやり方で除去される導入部において述べた型式の方法を提供することである。

【0014】

この第2の目的は、内部レイヤの表面の活性化がパターンに従って起こり、その間、内部レイヤの表面に又は表面上における層間剥離エリアが不活性のまま残ることを達成する。パターン化された活性化は層間剥離エリアを発生させる。機械的ストレスが起こる場合、これらストレスは層間剥離エリアにおける肩間剥離により放電される。接続領域の近くの微細な亀裂及び他の亀裂の形成がこれにより避けられるか又は少なくとも大幅に減少する。

30

【0015】

パターンでの活性化は様々なやり方でもたらされる。第1の実施例において、活性化は光源からの光を用いて起こる。この間に、マスクがこの光源と内部レイヤの表面との間に置かれる。このマスクは光源の前に設置される。このマスクは内部レイヤの上のレイヤとしても設置される。このようなレイヤの実施例はフォトレジストである。この層は、活性化が止まった後に除去され得る。しかしながら、内部レイヤ上に一定量の流動材料を供給することが利点であり、この一定量は活性化が止まった後も除去されない。結果生じる層間剥離エリアが円形、橢円形又はそうでなければ角の無い形状であることが一定量の流動材料の利点である。層間剥離エリアの境界エリアにおける角が、亀裂が始まる弱点を形成する。一定量の流動材料が丸い表面を持つので、外部レイヤに対しさらに適切なボンディングが存在する。

40

【0016】

第2の実施例において、内部レイヤの全表面が活性化され、その後、内部レイヤの被覆が局部的に設けられる。この被覆は、例えば一定量の流動材料である。外部レイヤが続いて与えられる場合、被覆部と外部レイヤとの間の接着力は、内部レイヤの間の活性化した表面と外部レイヤとの間の接着力よりは強くない。これが層間剥離を定める。

【0017】

前記量を適切に位置決めすることにより、層間剥離エリアは、適切な接着力を持つエリ

50

アに囲まれる。後者のエリアは、前記ストレスを層間剥離エリアに移動させることができ、このストレスは外部レイヤが置かれた場合に現れ、この移動は接着力にとって有利であり、好ましくないストレスの危険性を減少させる。この位置決めは好ましくは一度設計され、その後にテンプレートを用いて決められる。他方では、このテンプレートがスタンプ面上のパターンに実装されるプリンティング技術を利用することができる。このようなプリンティング技術の好適な実施例は、マイクロコンタクトプリンティングである。

【0018】

流動材料は好ましくはドロップ形状で設けられる。例えばディスペンサーデバイスを用いて配置される上記ドロップが供給される。これは、前記流動材料の量がディスペンサの時間、ニードルの直径、又はアプリケーションの圧力を適応させることにより同様に設定され得ることで好ましい。流動材料は好ましくは、硬化され得るポリマ、例えばエポキシ樹脂又はアクリル樹脂である。このドロップの好ましい大きさ及び位置は、設計の幾何学形状に依存する。このドロップは集積回路の下側又は上側のどちらか、若しくは両側に設けられる。

10

【0019】

内部レイヤは好ましくはシリコン材料を有し、この材料は通常、反復性ユニットとしてジアルキルシロキサン(dialkylsiloxane)を有する。代わりにポリアミドが与えられてもよい。

【0020】

硬化可能な材料はとりわけプラズマ又はコロナ処理を用いて活性化される。好ましい実施例は酸素プラズマ処理である。この処理は低い気圧下だけでなく大気圧下でも行われる。それが数秒間だけ継続することがこの処理の利点である。

20

【発明を実施するための最良の形態】

【0021】

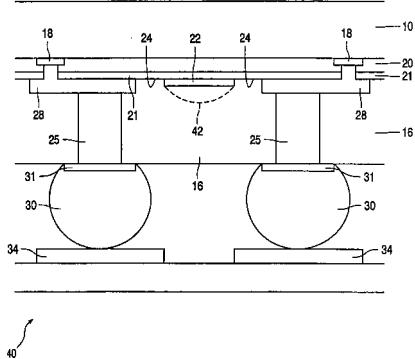

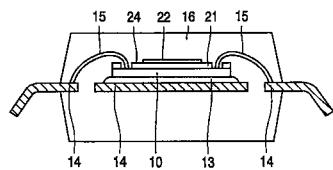

図1は半導体デバイスの概略的な断面図である。シリコン基板内又は基板上に形成される集積回路10は、接着レイヤ(例えば銀ペースト)13によりリードフレーム14に接続される。このリードフレーム14は通常、鉄ニッケル(FeNi)又は銅鉄(CuFe)から構成される。前記集積回路はボンドワイヤ15を介してリードフレーム14に接続され、エンベロープの内部レイヤ21で覆われている。本実施例におけるこの内部レイヤ21はシリコンゴムを有する。通常は室化シリコンであるバッシベーション層(図示せず)は集積回路10と内部レイヤ21との間に置かれる。この全体は、通常は水晶粉末又はガラス粉末が充填されるエポキシ樹脂であるエンベロープの外部レイヤ16内に封入される。

30

【0022】

図2は図1に示される半導体デバイスの細部を示す。酸化シリコンレイヤ17は集積回路10を覆っている。アルミニウムのボンディングパッド18が酸化シリコン17上に置かれる。集積回路全体は、前記ボンディングパッドに設けられる開口を備えた室化シリコンのバッシベーション層20で覆われる。この室化シリコン層の厚さは約1マイクロメートルである。室化シリコンレイヤ20はPECVDプロセスにより与えられる。

【0023】

続いて、室化シリコンレイヤ20を備える複数の集積回路10を有するシリコンウェハは、リードフレーム14に搭載されるチップ(ダイシング)に分割される。ワイヤ15が一度リードフレーム14及びボンディングパッド18に接続されると、この全体は、ポリ(ジメチルシロキサン)の内部レイヤ21で覆われる。次いで、Techcon System社によるバリメータ/制御器TS9300型のディスペンサーデバイスからエポキシ樹脂のドロップは、各チップ10の内部レイヤに与えられる。次いで、このドロップ及び残っている表面は、5秒から10秒の間、1又は2ミリバール(mbar)の圧力下且つ300から500ワットの電力でTepla300マイクロ波プラズマシステムにおいて酸素プラズマにより活性化される。次いで、チップ10はエポキシ樹脂16内に封入される。この目的のために、慣例的な充填するエポキシ樹脂は、例えばEMF-6210(製造元:住友)を用いることができる。前記ドロップは外部レイヤ16の熱処理の後、層間剥離エリア22となり、この層間剥離エリア

40

50

22は相互境界面24に隣接している。すなわち、相互境界面24は層間剥離エリア22を囲んでいる。

【0024】

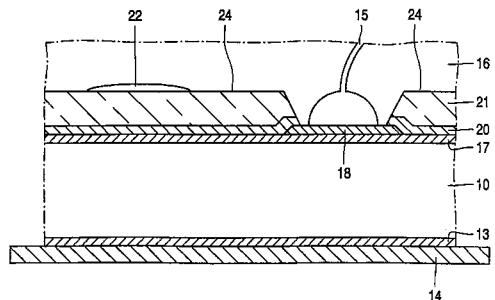

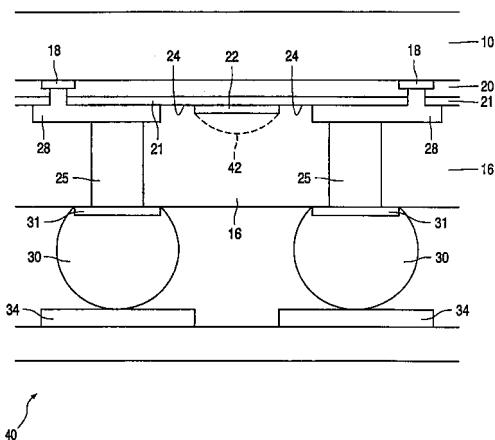

図3は本発明による半導体デバイスの第2の実施例を示す。この半導体デバイスは、本場合はシリコン(Si)である半導体材料の基板を有し、この基板内及び基板上に集積回路10が設けられる。集積回路10は、アルミニウム(Al)のボンディングパッド18を露出したままにした室化シリコンのパッシベーションレイヤ20で覆われる。このパッシベーションレイヤ20の上に、ポリアミドからなる内部レイヤ21を置く。ボンディングパッド18は、導電材料、例えば銅(Cu)からなる相互接続部28及びブリッジ25を介してはんだ粒30に接続される。バリアレイヤ31はブリッジ25とはんだ粒30との間に置かれる。これらはんだ粒30はキャリア40の導電部分34と接触する。

10

【0025】

外部レイヤ16は内部レイヤ21の上に設けられ、これら内部レイヤ21及び外部レイヤ16は相互境界面24を持つ。硬化され得る一定量の材料も内部レイヤ21上に存在する。はんだ付けステップの後、この材料は層間剥離エリアを形成する。このとき起こっている温度及び圧力の結果として、内部レイヤ21及び外部レイヤ16は層間剥離エリア22において互いに層状に剥離されている。この図において、この層間剥離は破線42で示される。同時に、内部レイヤ21と外部レイヤ16との間にある相互境界面24は、ブリッジ25及び相互接続部28の近くはそのままである。

20

【0026】

要約すると、集積回路を有する半導体デバイスのパッケージは、通常内部レイアと外部レイアとを有し、これらレイアは相互境界面を持っている。前記パッケージの改善された安定性は、前記境界面が層間剥離エリアを囲むことを実現し、このエリアは集積回路の如何なるボンディングパッドからも絶縁されている。この層間剥離エリアは内部レイアの表面のパターンに関する活性化により作成され得る。これにより、一定量の硬化可能なポリマがこの表面上に置かれる。

【図面の簡単な説明】

【0027】

【図1】半導体デバイスの概略的断面図。

30

【図2】半導体デバイスのより詳細な概略的断面図。

【図3】半導体デバイスの第2の実施例の概略的断面図。

【図1】

【図2】

【図3】

---

フロントページの続き

(74)代理人 100103263

弁理士 川崎 康

(74)代理人 100107582

弁理士 關根 毅

(74)代理人 100118843

弁理士 赤岡 明

(74)代理人 100088889

弁理士 橋谷 英俊

(72)発明者 ウェイデネス ヤコブ

オランダ国 5 6 5 6 アーアー アインドーフェン プロフ ホルストラーン 6

F ターム(参考) 4M109 AA01 BA01 BA07 CA21 DB17 EA02 ED04 ED06 EE02

5F033 HH11 JJ11 KK08 RR06 RR21 VV07