(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2017년05월22일

(11) 등록번호 10-1738552

(24) 등록일자 2017년05월16일

- (51) 국제특허분류(Int. Cl.)

*G11B 5/31* (2006.01) *G11B 5/60* (2006.01)

(21) 출원번호 10-2014-7032943

(22) 출원일자(국제) 2013년04월25일

심사청구일자 2014년11월24일

(85) 번역문제출일자 2014년11월24일

(65) 공개번호 10-2015-0013592

(43) 공개일자 2015년02월05일

(86) 국제출원번호 PCT/US2013/038280

(87) 국제공개번호 WO 2013/163470

국제공개일자 2013년10월31일

(30) 우선권주장

61/637,985 2012년04월25일 미국(US)

(56) 선행기술조사문헌

US20110096431 A1\*

US20100329085 A1\*

US20110205863 A1\*

\*는 심사관에 의하여 인용된 문헌

- (73) 특허권자

시게이트 테크놀로지 엘엘씨

미국 캘리포니아 95014 쿠퍼티노 사우쓰 디 엔자

블러바드 10200

(72) 발명자

차오, 통

미국 55344 미네소타 애덴 프레리 스트래턴 애비

뉴 11343 유니트 218

추, 맹

미국 55431 미네소타 블루밍턴 데본샤이어 써클

10300 아파트먼트 312

(뒷면에 계속)

(74) 대리인

특허법인 남엔드남

전체 청구항 수 : 총 17 항

심사관 : 황승희

(54) 발명의 명칭 니어 필드 트랜스듀서 및 접착 층을 포함하는 디바이스들

**(57) 요 약**

디바이스는, NFT(near field transducer); 기입 폴; NFT와 기입 폴 사이에 포지셔닝되는 적어도 하나의 유전 재료; 및 NFT와 적어도 하나의 유전 재료 사이에 포지셔닝되는 접착 층을 포함한다.

**대 표 도** - 도2

(72) 발명자

후양, 시아오유에

미국 55347 미네소타 에덴 프레리 브랙스턴 드라이

브 8628

카우츠키, 마이클, 씨.

미국 55122 미네소타 래건 카렐 글렌 4143

## 명세서

### 청구범위

#### 청구항 1

디바이스로서,

NFT(near field transducer);

기입 폴;

상기 NFT와 상기 기입 폴 사이에 포지셔닝되는 적어도 하나의 유전 재료; 및

상기 NFT의 상단과 적어도 하나의 유전 재료 사이에 포지셔닝되는 접착 층을 포함하며,

상기 접착 층은,

지르코늄(Zr), 이트륨(Y), 스칸듐(Sc), 알루미늄(Al), 루테늄(Ru), 바나듐(V), 실리콘(Si), 게르마늄(Ge) 및 이들의 조합들;

코발트(Co), 니켈(Ni), 크롬(Cr), 텉스텐(W), 티타늄 텉스텐(TiW), 몰리브덴(Mo), 마그네슘(Mg), 니오븀(Nb), 하프늄(Hf), 아연(Zn), 및 이들의 조합들;

티타늄 질화물(TiN), 지르코늄 질화물(ZrN), 탄탈 질화물(TaN), 하프늄 질화물(HfN) 및 이들의 조합들;

인듐 산화물( $In_2O_3$ ),  $In_2O_3-SnO_2$ (ITO)의 고용체, 아연 산화물(ZnO), 알루미늄(Al) 도핑된 ZnO, 갈륨(Ga) 도핑된 ZnO, 및 이들의 조합들;

Zr, Zn, Ti, Co, 은(Ag), 구리(Cu), 인듐(In), 카드뮴(Cd), Sn, 비스무트(Bi), 납(Pb), 셀레늄(Se), 철(Fe), Mo의 황화물들; 또는 이들의 이원 황화물들; 그리고

실리콘 탄화물(SiC) 또는 수소화 실리콘 탄화물(SiC:H)로부터 선택되는 하나 또는 그 초과의 재료들을 포함하는, 디바이스.

#### 청구항 2

삭제

#### 청구항 3

제 1 항에 있어서,

상기 접착 층은 Zr, Y, Sc, Al, Ru, V, Si, Ge, 또는 이들의 조합들을 포함하며,

상기 접착 층은 2.5 Å 내지 50 Å의 평균 두께를 갖는, 디바이스.

#### 청구항 4

제 1 항에 있어서,

상기 접착 층은 Co, Ni, Cr, W, TiW, Mo, Mg, Nb, Hf, Zn, 또는 이들의 조합들을 포함하며,

상기 접착 층은 25 Å를 초과하지 않는 평균 두께를 갖는, 디바이스.

#### 청구항 5

제 1 항에 있어서,

상기 접착 층은, TiN, ZrN, TaN, HfN, 또는 이들의 조합들을 포함하며,

상기 접착 층은 50 Å를 초과하지 않는 평균 두께를 갖는, 디바이스.

**청구항 6**

제 1 항에 있어서,

상기 접착 층은  $\text{In}_2\text{O}_3$ , ITO, ZnO, Al 도핑된 ZnO, Ga 도핑된 ZnO, 또는 이들의 조합들을 포함하며,

상기 접착 층은 50 Å를 초과하지 않는 평균 두께를 갖는, 디바이스.

**청구항 7**

제 1 항에 있어서,

상기 접착 층은, Zr, Zn, Ti, Co, Ag, Cu, In, Cd, Sn, Bi, Pb, Se, Fe, Mo의 황화물들; 또는 이들의 이원 황화물들을 포함하는, 디바이스.

**청구항 8**

제 1 항에 있어서,

상기 접착 층은 SiC, SiC:H, 또는 이들의 조합들을 포함하는, 디바이스.

**청구항 9**

제 1 항에 있어서,

상기 NFT의 바닥에 인접한 제 2 접착 층을 더 포함하는, 디바이스.

**청구항 10**

제 9 항에 있어서,

상기 제 2 접착 층은,

Co, Ni, Cr, W, TiW, Mo, Mg, Nb, Hf, Zn, 및 이들의 조합들;

TiN, ZrN, TaN, HfN, 및 이들의 조합들;

$\text{In}_2\text{O}_3$ , ITO, ZnO, Al 도핑된 ZnO, Ga 도핑된 ZnO 및 이들의 조합들;

Zr, Zn, Ti, Co, Ag, Cu, In, Cd, Sn, Bi, Pb, Se, Fe, Mo의 황화물들; 또는 이들의 이원 황화물들;

그리고

SiC, SiC:H, 및 이들의 조합들

로부터 선택되는 하나 또는 그 초파의 재료들을 포함하는, 디바이스.

**청구항 11**

제 1 항에 있어서,

NFT의 하나 또는 그 초파의 측면들에 인접한 추가의 접착 층들을 더 포함하는, 디바이스.

**청구항 12**

제 11 항에 있어서,

상기 추가의 접착 층은,

Co, Ni, Cr, W, TiW, Mo, Mg, Nb, Hf, Zn, 및 이들의 조합들;

TiN, ZrN, TaN, HfN, 및 이들의 조합들;

$\text{In}_2\text{O}_3$ , ITO, ZnO, Al 도핑된 ZnO, Ga 도핑된 ZnO 및 이들의 조합들;

Zr, Zn, Ti, Co, Ag, Cu, In, Cd, Sn, Bi, Pb, Se, Fe, Mo의 황화물들; 또는 이들의 이원 황화물들;

그리고

SiC, SiC:H, 및 이들의 조합들

로부터 선택되는 하나 또는 그 초과의 재료들을 포함하는, 디바이스.

### 청구항 13

제 9 항에 있어서,

상기 NFT의 하나 또는 그 초과의 측면들에 인접한 추가의 접착 층들을 더 포함하는, 디바이스.

### 청구항 14

제 1 항 및 제 3 항 내지 제 13 항 중 어느 한 항에 있어서,

상기 NFT는, Au, 다른 재료로 도핑된 Au, Ag, 다른 재료로 도핑된 Ag, Cu, 또는 Al를 포함하는, 디바이스.

### 청구항 15

제 1 항 및 제 3 항 내지 제 12 항 중 어느 한 항에 있어서,

상기 NFT는 페그(peg) 및 디스크(disc) 타입 NFT인, 디바이스.

### 청구항 16

제 1 항 및 제 3 항 내지 제 12 항 중 어느 한 항에 있어서,

에너지 소스를 더 포함하며, 상기 NFT는 상기 에너지 소스로부터의 에너지를 수용하도록 구성되는, 디바이스.

### 청구항 17

제 16 항에 있어서,

상기 에너지 소스는 레이저를 포함하는, 디바이스.

### 청구항 18

제 16 항에 있어서,

도파관(waveguide)을 더 포함하며,

상기 도파관은, 상기 에너지 소스로부터의 에너지를 수용하고 이를 상기 NFT에 커플링하도록 구성되는, 디바이스.

## 발명의 설명

### 배경기술

[0001] 가열 자기 기록(본원에서 "HAMR"로 칭함) 기술은, 1 Tbit/inch<sup>2</sup> 이상으로(beyond) 저장 밀도를 증가시키기 위한 유망한 방안이다. HAMR 헤드들은, 자기 기록 층들을 가열하는데 NFT(near field transducer)들을 이용할 수 있다. HAMR 헤드에서의 주변 구조들과 NFT의 재료들 간의 불량한(poor) 접착은 프로세싱 또는 사용 동안의 고장(failure)을 유도할 수 있다. 따라서, 이러한 고장을 줄이는 것이 계속해서 요구되고 있다.

### 발명의 내용

[0002] NFT(near field transducer); 기입 폴(write pole); NFT와 기입 폴 사이에 포지셔닝되는 적어도 하나의 유전 재료; 및 NFT와 적어도 하나의 유전 재료 사이에 포지셔닝되는 접착 층을 포함하는 디바이스들이 개시된다.

[0003] 또한, 에너지 소스; 에너지 소스로부터의 에너지를 수용하도록 구성된 NFT; 기입 폴; NFT와 기입 폴 사이에 포지셔닝되는 적어도 하나의 유전 재료; 및 NFT와 적어도 하나의 유전 재료 사이에 포지셔닝되는 접착 층을 포함하는 디바이스들이 개시된다.

[0004] 또한, 에너지 소스; 에너지 소스로부터의 에너지를 수용하고 이를 NFT에 커플링하도록 구성된 도파관; 도파관으로부터의 에너지를 수용하도록 구성된 NFT; 기입 폴; NFT와 기입 폴 사이에 포지셔닝되는 적어도 하나의 유전

재료; 및 NFT와 적어도 하나의 유전 재료 사이에 포지셔닝되는 접착 층을 포함하는 디바이스들이 개시된다.

### 도면의 간단한 설명

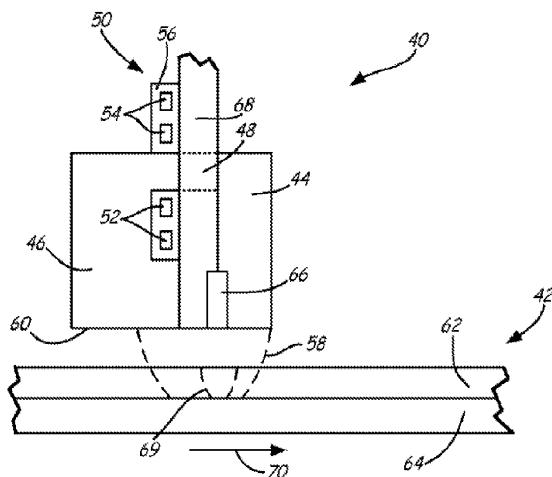

[0005] 도 1은, HAMR 디바이스들을 포함할 수 있는 자기 디스크 드라이브의 투시도이다.

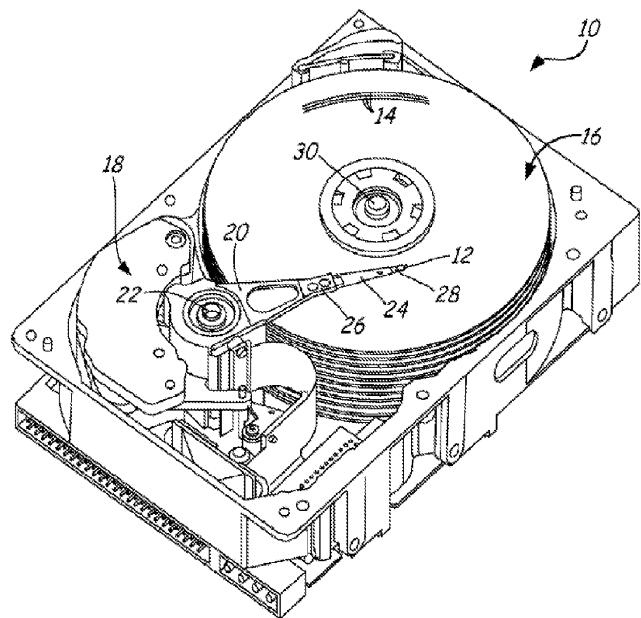

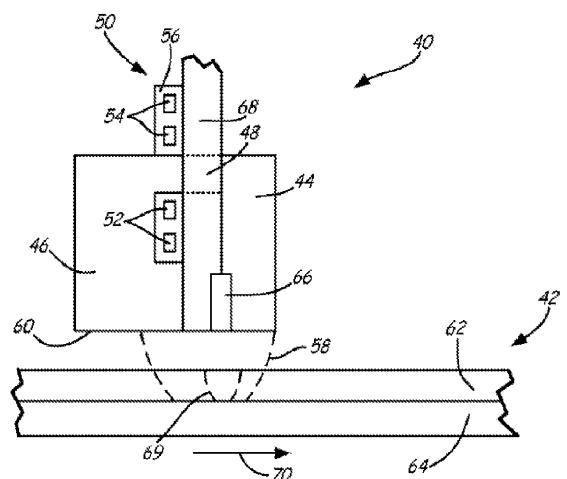

도 2는 수직형 HAMR 자기 기록 헤드 및 연관된 기록 매체의 단면도이다.

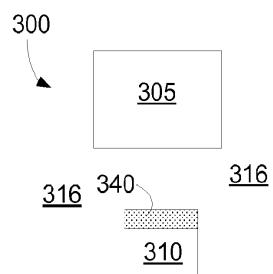

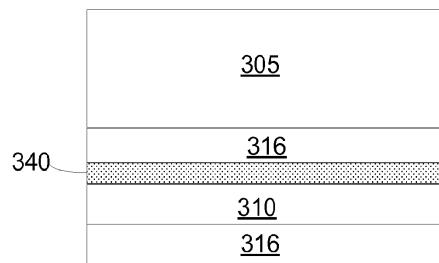

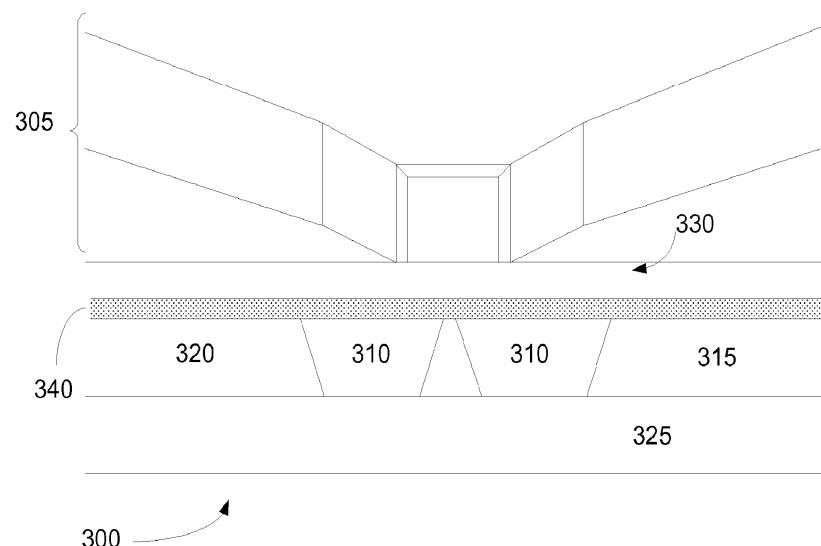

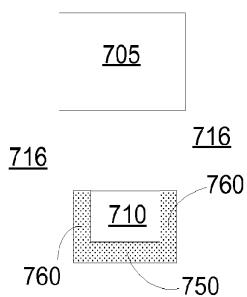

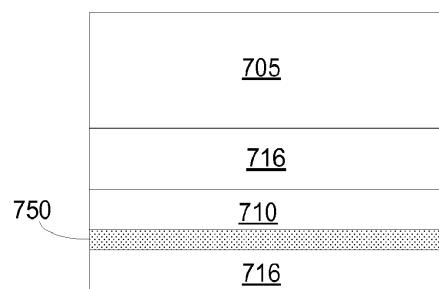

도 3a, 3b, 및 3c는, 개시되는 상단 접착 층을 포함하는 자기 디바이스의 적어도 일부에 대한 도면들이며, 도 3a는 ABS로부터의 도면이며; 도 3b는 측면도이며; 그리고 도 3c는 투시도이다.

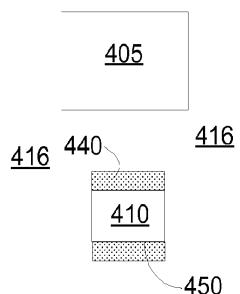

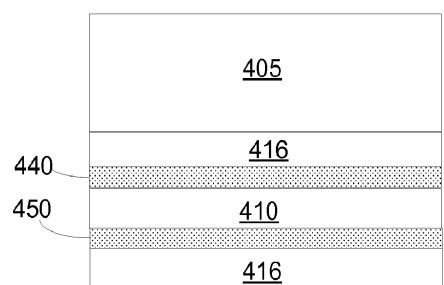

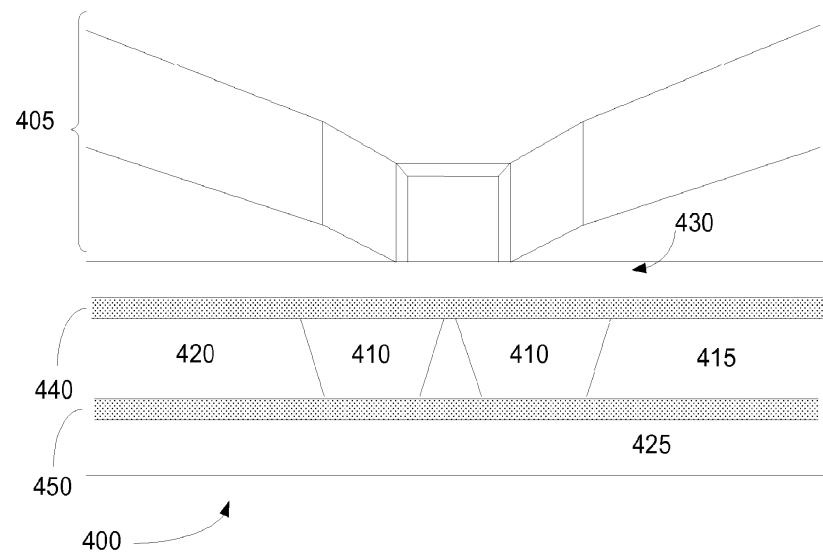

도 4a, 4b, 및 4c는, 개시되는 상단 및 바닥 접착 층의 적어도 일부를 포함하는 자기 디바이스의 적어도 일부에 대한 도면들이며, 도 4a는 ABS로부터의 도면이며; 도 4b는 측면도이며; 그리고 도 4c는 투시도이다.

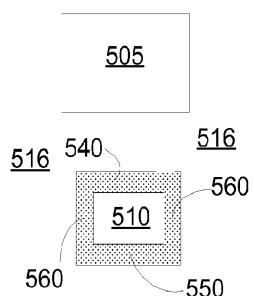

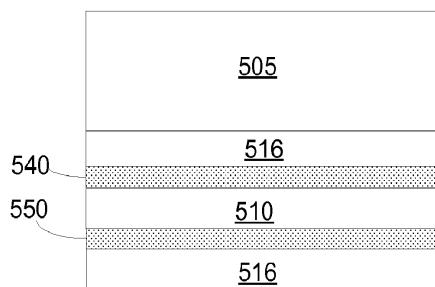

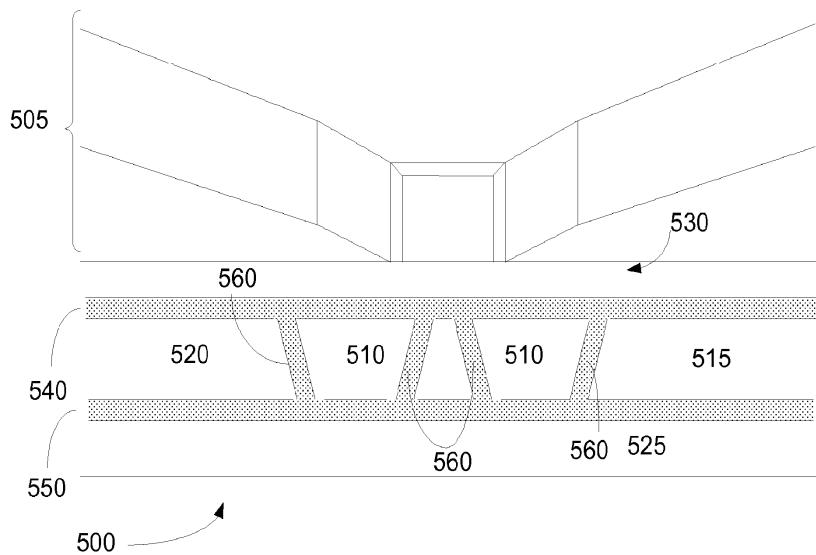

도 5a, 5b, 및 5c는, 개시되는 상단, 바닥 및 측면 접착 층을 포함하는 자기 디바이스의 적어도 일부에 대한 도면들이며, 도 5a는 ABS로부터의 도면이며; 도 5b는 측면도이며; 그리고 도 5c는 투시도이다.

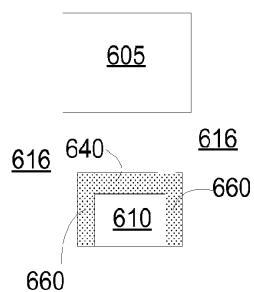

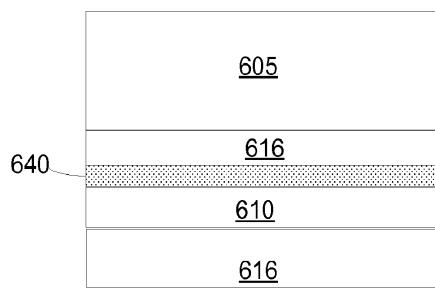

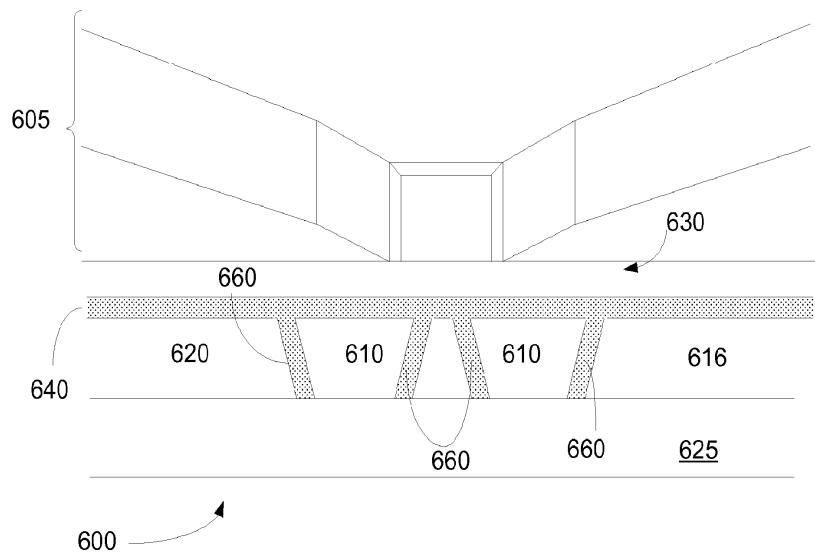

도 6a, 6b, 및 6c는, 개시되는 상단 및 측면 접착 층을 포함하는 자기 디바이스의 적어도 일부에 대한 도면들이며, 도 6a는 ABS로부터의 도면이며; 도 6b는 측면도이며; 그리고 도 6c는 투시도이다.

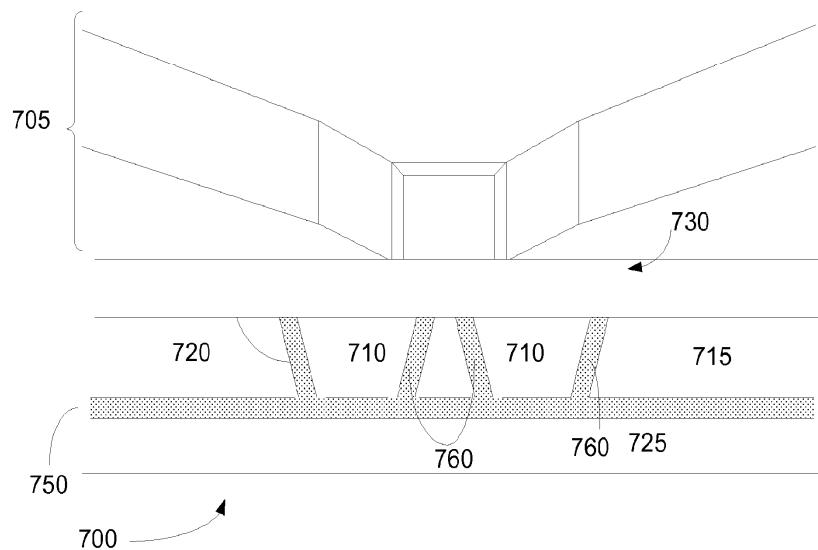

도 7a, 7b, 및 7c는, 개시되는 바닥 및 측면 접착 층을 포함하는 자기 디바이스의 적어도 일부에 대한 도면들이며, 도 7a는 ABS로부터의 도면이며; 도 7b는 측면도이며; 그리고 도 7c는 투시도이다.

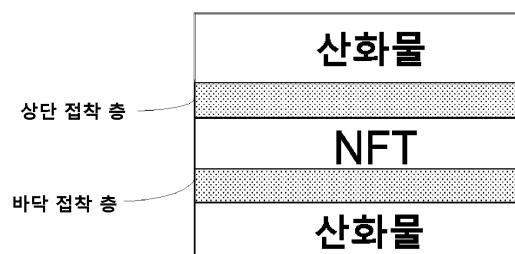

도 8은 개시되는 예들을 실행하는데 이용되는 예시적인 스택(stack)에 대한 측면도를 도시한다.

도면들은 반드시 실체대로는 아니다. 도면들에서 사용되는 유사한 번호들은 유사한 컴포넌트들을 지칭한다. 그러나 제시되는 도면에서 컴포넌트를 지칭하는 번호의 사용은 동일한 번호로 라벨링된 다른 도면에서의 컴포넌트를 제한하도록 의도되지 않는다는 것이 이해될 것이다.

### 발명을 실시하기 위한 구체적인 내용

[0006] 하기의 설명에서는, 몇 개의 특정 실시예들의 예로써 도시되며 본원의 일부를 형성하는 첨부 도면들의 세트에 대한 참조가 이루어진다. 본 개시의 범위 또는 사상을 이탈하지 않고 다른 실시예들이 고려되거나 구성될 수 있다는 것이 이해될 것이다. 따라서, 하기 상세한 설명은 제한적 의미로 취해지지 않는다.

[0007] 달리 표시되지 않는다면, 명세서 및 청구항들에서 사용되는 괴처 크기들, 양들 및 물리적 특성들을 표현하는 모든 수들은, "약"이란 용어에 의해 모든 경우들에서 변형되는 것으로 이해될 것이다. 따라서, 다르게 표시되지 않는다면, 앞서 말한 명세서 및 첨부되는 청구항들에서 개시되는 수치적 파라미터들은, 본원에 개시되는 교시들을 이용하여 당업자들이 얻고자 하는 특성들에 따라 변할 수 있는 근사치들이다.

[0008] 최종점들에 의한 수치적 범위들의 인용은, 해당 범위 내에 포함되는 모든 수들(예를 들어, 1 내지 5는, 1, 1.5, 2, 2.75, 3, 3.80, 4, 및 5를 포함함) 및 해당 범위 내의 임의의 범위를 포함한다.

[0009] 본 명세서 및 첨부된 청구항들에서 사용되는 것처럼, 문맥에 달리 명확히 표시되지 않는다면, 단수 형태들은 복수의 지시대상들을 갖는 실시예들을 포함한다. 본 명세서 및 첨부된 청구항들에서 사용되는 것처럼, "또는"이란 용어는 일반적으로, 그 의미에 있어, 문맥에 달리 명확히 표시되지 않는다면, "및/또는"을 포함하는 것으로 이용된다.

[0010] "포함한다(include)", "포함하는(including)" 등의 용어들은, 이로 제한되는 것은 아니지만, 포괄하는 것(encompassing), 즉 배타적이지 않고 포함하는 것(including)을 의미한다. "상단(top)" 및 "바닥(bottom)"(또는 "위" 및 "아래"와 같은 다른 용어들)은 순전히(strictly) 상대적 설명들을 위해 이용되며 설명된 엘리먼트가 위치된 물품의 어떤 전체 배향을 의미하지 않는다는 것을 주목해야 한다.

[0011] 도 1은 자기 매체(16)의 트랙(14) 위에 슬라이더(12)를 포지셔닝하기 위한 액추에이션 시스템을 포함하는 디스크 드라이브(10)의 투시도이다. 디스크 드라이브(10)의 특정 구성은 설명의 용이함을 위해 도시된 것이며 본 개시의 범위를 어떤 식으로 한정하고자 의도된 것은 아니다. 디스크 드라이브(10)는, 축(22) 둘레의 스판들 상의 액추에이터 암(20)을 회전시키도록 배열된 보이스 코일 모터(18)를 포함한다. 로드 빔(load beam)(24)은, 헤드 장착 블록(26)에서 액추에이터 암(20)에 연결된다. 서스펜션(28)은 로드 빔(24)의 단부에 연결되며 슬라이더(12)는 서스펜션(28)에 부착된다. 자기 매체(16)가 축(30) 주위를 회전하여, 펀류(windage)가 슬라이더(12)와 만나 자기 매체(16)의 표면 상에서 작은 거리를 두고 떠있게(aloft) 슬라이더가 유지된다. 자기 매체

(16)의 각각의 트랙(14)은, 데이터를 저장하기 위한 데이터 저장 셀들의 어레이로 포맷된다. 슬라이더(12)는 자기 매체(16)의 트랙들(14) 상에서 데이터를 판독하기 위해 그리고/또는 기입하기 위해 자기 디바이스 또는 트랜스듀서(도 1에는 도시되지 않음)를 보유한다. 자기 트랜스듀서는, 가열 자기 기록(HAMR)이라 불리는 프로세스에 의한 기록을 용이하게 하기 위해, 매체(16)의 표면을 가열하기 위해 추가의 전자기 에너지를 이용한다.

[0012] HAMR 트랜스듀서는, 자기 매체(예를 들어, 자기 매체(16))에 대한 기입을 위해 자기장을 발생시키기 위한 자기 기입기(magnetic writer) 및 기입 필드 근처의 자기 매체의 일부를 가열하기 위한 광학 디바이스(optical device)를 포함한다. 도 2는, 자기 디바이스, 예를 들어 HAMR 자기 디바이스(40)의 일부 및 연관된 자기 저장 매체(42)의 일부에 대한 단면도이다. HAMR 자기 디바이스(40)는 페데스탈(48)에 의해 커플링되는 기입 폴(44) 및 리턴(return) 폴(46)을 포함한다. 도전체들(52, 54)을 포함하는 코일(50)은 페데스탈을 둘러싸며 절연체(56)에 의해 지지된다. 도시된 것처럼, 자기 저장 매체(42)는 자기적 하드(hard) 저장 층(62) 및 하부 연자성 층(soft magnetic underlayer)(64)을 포함하는 수직형 자기 매체이나, 다른 형태들의 매체, 예컨대 패터닝된 매체일 수 있다. 코일에서의 전류는 페데스탈 및 폴들에서의 자기장을 유도한다. 자속(58)은, 에어 베어링 표면(ABS)(60)에서 기록 헤드를 벗어나, 영역(58) 내에 에워싸인 저장 매체(42)의 자기적 하드 층(62)의 부분들에 대한 자화(magnetization)를 변화시키는데 이용된다. 니어 필드 트랜스듀서(66)는, 에어 베어링 표면(60) 근처의 기입 폴(44)에 인접하게 포지셔닝된다. 니어 필드 트랜스듀서(66)는, 레이저와 같은 에너지 소스로부터의 전자기 파를 수용하는 도파관(68)에 커플링된다. 니어 필드 트랜스듀서(66)의 단부에서의 전기장은, 기입 폴로부터의 자기장이 저장 매체의 자화에 영향을 미칠 수 있도록, 자기적 하드 층(62)의 일부(69)를 가열하여 보자력(coercivity)을 더 낮추는데 이용된다.

[0013] 본원에 개시되는 자기 디바이스들은 또한 다른 구조들을 포함할 수 있다. 본원에 개시되는 자기 디바이스들은 또한 더 큰 디바이스들에 통합될 수 있다. 예를 들어, 본원에 개시된 것처럼 슬라이더들은 자기 디바이스들을 포함할 수 있다. 예시적인 슬라이더들은 리딩 에지(leading edge), 트레일링 에지(trailing edge), 및 에어 베어링 표면을 갖는 슬라이더 바디를 포함할 수 있다. 이후, 기입 폴, 판독 폴, 광학적 니어 필드 트랜스듀서 및 콘택 패드(및 선택적인 히트 싱크(heat sink))가 슬라이더 바디 상에 (또는 내부에) 위치될 수 있다. 이러한 예시적인 슬라이더들은, 예를 들어 디스크 드라이브에 통합될 수 있는 서스펜션에 부착될 수 있다.

[0014] 도 3a는, 자기 디바이스의 일부에 대한 간략화된 에어 베어링 표면(ABS) 도면을 도시한다. 자기 디바이스(300)는 기입 폴(305)(위에서 논의된 것과 같은 특징들을 가질 수 있음) 및 NFT(near field transducer)(310)를 포함할 수 있다. 기입 폴(305) 및 NFT(310)는 일반적으로 유전 재료(316)에 의해 둘러싸인다. 일부 실시예들에서, 기입 폴(305)과 NFT(310) 사이의 층은 NPS(NFT to pole spacing) 층으로서 지칭될 수 있고, NFT와 코어(도 3a에는 미도시) 사이의 층은 CNS(core to NFT spacing) 층으로 지칭될 수 있다. 유전 재료(316)는 또한 클래딩 재료들 또는 클래딩 층들로 설명될 수 있다. NPS 층 및 CNS 층의 재료들은 동일할 필요는 없으며, 예를 들어 산화물들일 수 있다.

[0015] 도 3에 도시된 NFT(310)가 2개 부분의 구조를 갖는 것으로 설명될 수 있지만, 설명된 실시예들은 임의의 타입 또는 구조의 NFT(예를 들어, 플라즈모닉(plasmonic) 캡 타입 NFT들, 또는 "롤리팝(lollipop)" 타입 NFT들로서 또한 지칭될 수 있는 페그(peg) 및 디스크(disc) 타입 NFT들)에 이용될 수 있다는 것을 인식해야 한다. 통상적으로, NFT(310)는, 예를 들어, 금(Au), 다른 재료로 도핑된 금(Au)(예를 들어, AuGe), 은(Ag), 다른 재료로 도핑된 은(Ag)(예를 들어, AgGe), 구리(Cu), 및 알루미늄(Al)과 같은 재료들로 만들어질 수 있다. 일부 실시예들에서, NFT(310)는 또한, 2011년 2월 23일자로 "HAMR NFT Materials with Improved Thermal Stability"란 명칭으로 출원된 미국 특허 공보 2011/0205863(이 개시물은 인용에 의해 본원에 통합됨)에 나열된 재료들로 만들어질 수 있다. 도 3a 및 3b; 4a 및 4b; 5a 및 5b; 6a 및 6b; 그리고 7a 및 7b에 도시된 NFT는 단순화되어 도시된 것이며 롤리팝 타입(또한 페그 및 디스크 타입으로도 불림) NFT 구조들; 및 캡 타입 NFT 구조들 둘 다를 표현하는 것을 의미한다는 것을 주목해야 한다.

[0016] 일부 실시예들에서, 자기 디바이스(300)는 또한 상단 접착 층(340)을 포함할 수 있다. 상단 접착 층(340)은 또한, 시드 층으로서 설명될 수 있다. 이로써, 상단 접착 층(340)은, 하나의 재료에 대한 다른 재료의 접착력(adherence)을 증가시킴으로써 NFT(310) 대 유전체(316) 인터페이스의 구조적 보전성(structural integrity)을 유리하게 강화시킬 수 있다. 상단 접착 층(340)의 재료는 또한, NFT(310)의 플라즈모닉 특성 및 요건들을 인식하고 있어야 한다. 도 3b는, 본질적으로 NFT(310)와 유전 재료(316) 사이의 상단 접착 층(340)을 도시하며 동일한 컴포넌트들을 포함하고 디스플레이하는 측면도를 도시한다.

[0017] 도 3c는, 예시적인 자기 디바이스(300)의 많은(more) 컴포넌트들을 보다 특정하게 도시하는 자기 디바이스의 일

부에 대한 부분적 투시도를 도시한다. 이 도면은, 도 3a 및 도 3b에 도시되었던 유전 재료(316)를 기술한다. 이로써, 이 예시적인 자기 디바이스(300)는, 전방 클래딩(315, 320), 바닥 클래딩(325), 및 상단 클래딩(330)을 포함한다. 일반적으로, 설명된 실시예에서, NFT(310)는 클래딩 재료들로 완전히 둘러싸이며, 이는 이전 도면들에서 유전 재료(316)로 도시되었다. 적어도 하나의 클래딩 층(및 본 실시예에서, 전방 클래딩(315, 320), 바닥 클래딩(325), 및 상단 클래딩(330))은 일반적으로, (NFT의 재료에 비해) 낮은 굴절률을 갖는 유전 재료들로 형성될 수 있다. 예시적인 재료들은,  $Ta_2O_5$ ,  $Al_2O_3$ ,  $SiO_2$ ,  $MgO$ ,  $MgF_2$ ,  $Si_3N_4$ ,  $SiON$ , 및  $TaSiO$ 를 포함할 수 있다. "Optical Waveguide Clad Material"란 명칭으로 2011년 2월 23일자로 출원된 미국 특허 공보 제2011/0205864호(이 개시물은 모순되지 않는 범위로 인용에 의해 본원에 통합됨)에 개시된 재료들이 또한, 전방 클래딩(315, 320), 바닥 클래딩(325), 및 상단 클래딩(330) 또는 이들의 일부 결합을 위해 이용될 수 있다. 실시예들에서, 클래딩 층들은 예를 들어,  $Al_2O_3$  또는  $SiO_2$ 로 만들어진다.

[0018]

NFT(310)를 주위 클래딩 층들에 잘 부착하는 것은 종종 어려울 수 있다. NFT(310)가 그를 둘러싸는 재료에 대해 양호한 접착성을 갖지 않을 경우, 자기 디바이스는 자기 디바이스의 프로세싱 동안 또는 동작 동안 고장날 수 있다. 이에 따라, 개시된 자기 디바이스들은 상단 접착 층(340)을 포함한다. 상단 접착 층(340)은, 그럴 필요는 없지만, 단일 층일 수 있다는 것이 주목되어야 한다. "상단 접착 층"이란 문구는, 본 예시적인 실시예에서 NFT와 상단 클래딩 층 사이에 포지셔닝되는 하나 보다는 많은 구조 또는 층을 지칭하는데 이용될 수 있다. 개시된 상단 접착 층은 일반적으로, 인접한 주위 클래딩 층과 NFT의 표면 사이에 위치될 수 있다.

[0019]

도 4a, 4b, 및 4c는, 개시된 자기 디바이스의 또 다른 예시적인 실시예를 도시한다. 이 자기 디바이스는 NFT의 마주하는 표면들, 즉 상단 그리고 바닥의 적어도 일부 상에 접착 층들을 포함한다. 이 예시적인 자기 디바이스는, 기입 폴(405), NFT(410), 유전 재료(416)(도 4c에 전방 클래딩(415, 420), 바닥 클래딩(425) 및 상단 클래딩(430)으로 보다 구체적으로 도시됨), 상단 접착 층(440) 및 바닥 접착 층(450)을 포함한다. 바닥 접착층(450)은, 상단 접착 층과 동일한 또는 유사한 재료들로 만들어질 수 있고, 그리고 동일한 또는 유사한 특징들(예를 들어, 두께, 불연속성 등)을 가질 수 있다. 그러나, 바닥 접착 층(450)이 상단 접착 층(440)과 동일한 재료이거나 그리고/또는 동일한 특징들을 가질 필요는 없다.

[0020]

도 5a, 5b, 및 5c는 개시된 자기 디바이스의 또 다른 예시적인 실시예를 도시한다. 이 자기 디바이스는, NFT의 모든 표면들, 즉 상단, 및 바닥 및 측면들 상에 또는 그 주변에 접착 층들을 포함한다. 여기서, NFT의 바닥 표면들은, 일부 실시예들에서, 측면 접착 층들(560)에 의해 표시된 측면들을 포함할 수 있다는 것을 주목해야 한다. NFT 재료가 트렌치(이들 실시예들에서 접착 층 재료로 먼저 라이닝됨) 내에 중착될 수 있기 때문에, 측면들은 바닥의 일부로서 간주될 수 있다. 이 예시적인 자기 디바이스는, 기입 폴(505), NFT(510), 유전 재료(516)(도 5c에 전방 클래딩(515, 520), 바닥 클래딩(525) 및 상단 클래딩(530)으로서 보다 구체적으로 도시됨), 상단 접착 층(540), 바닥 접착 층(550) 및 측면 접착 층(560)을 포함한다. 바닥 접착 층(550)은, 상단 접착 층(540), 및/또는 측면 접착 층(560)과 동일한 또는 유사한 재료들로 만들어질 수 있고 그리고 동일한 또는 유사한 특징들(예를 들어, 두께, 불연속성 등)을 가질 수 있다. 그러나, 바닥 접착 층(550)이, 상단 접착 층(540) 및/또는 측면 접착 층(560)과 동일한 재료이고 그리고/또는 동일한 특징들을 가질 필요는 없다. 상단 접착 층(540), 바닥 접착 층(550) 및 측면 접착 층(560)이 모두 단일 재료로서 도시되지만, 이는 그럴 필요는 없으며 사실 다양한 엘리먼트들이 서로 전혀 접촉할 필요가 없다는 것을 주목해야 한다.

[0021]

도 6a, 6b, 및 6c는 개시된 자기 디바이스의 또 다른 예시적인 실시예를 도시한다. 자기 디바이스는 NFT의 상단, 및 측면들에 또는 그 부근에 접착 층들을 포함한다. NFT 재료가 트렌치(이들 실시예들에서는 접착 층 재료로 먼저 라이닝됨) 내에 중착될 수 있기 때문에, 측면들은 바닥의 일부로서 간주될 수 있다는 것을 여기서 주목해야 한다. 이러한 실시예에서, (예를 들어 캡 타입 NFT의 경우에) 캡들의 측면들만이, 그 위에 중착되는 접착 층 재료를 가질 것이다. 이 예시적인 자기 디바이스는 기입 폴(605), NFT(610), 유전 재료(616)(도 6c에, 전방 클래딩(615 및 620), 바닥 클래딩(625) 및 상단 클래딩(630)으로 보다 구체적으로 도시됨), 상단 접착 층(640) 및 측면 접착 층(660)을 포함한다. 상단 접착 층(640)은, 측면 접착 층(660)과 동일한 또는 유사한 재료들로 만들어질 수 있고 그리고 동일한 또는 유사한 특징들(예를 들어, 두께, 불연속성 등)을 가질 수 있다. 그러나, 상단 접착 층(640)이 측면 접착 층(660)과 동일한 재료이고 그리고/또는 동일한 특징들을 가질 필요는 없다. 상단 접착 층(640) 및 측면 접착 층(660) 모두 단일 재료로 도시되지만, 이는 그럴 필요는 없으며 사실 다양한 엘리먼트들이 서로 전혀 접촉할 필요가 없다는 것을 주목해야 한다.

[0022]

도 7a, 7b, 및 7c는 개시된 자기 디바이스의 또 다른 예시적인 실시예를 도시한다. 이 자기 디바이스는 NFT의

바닥, 및 측면들에 또는 그 부근에 접착 층들을 포함한다. NFT 재료가 트렌치(이들 실시예들에서, 접착 층 재료로 먼저 라이닝됨) 내에 중착될 수 있기 때문에, 측면들은 바닥의 일부로서 간주될 수 있다는 것을 여기서 주목해야 한다. 이러한 실시예에서, (예를 들어, 캡 타입 NFT의 경우에) 캡들의 측면들 그리고 캡들의 바닥 둘다, 그 위에 중착되는 접착 층 재료를 가질 것이다. 이러한 예시적인 자기 디바이스는, 기입 폴(705), NFT(710), 유전 재료(716)(도 7c에, 전방 클래딩(715 및 720), 바닥 클래딩(725) 및 상단 클래딩(730)으로 보다 구체적으로 도시됨), 바닥 접착 층(750) 및 측면 접착 층(760)을 포함한다. 바닥 접착 층(750)은 측면 접착 층(760)과 동일한 또는 유사한 재료들로 만들어질 수 있고 그리고 동일한 또는 유사한 특징들(예를 들어, 두께, 불연속성 등)을 가질 수 있다. 그러나, 바닥 접착 층(750)이 측면 접착 층(760)과 동일한 재료이고, 그리고/또는 동일한 특징들을 가질 필요는 없다. 바닥 접착 층(750) 및 측면 접착 층(760) 모두 단일 재료로 도시되나, 이는 그럴 필요는 없으며 사실 다양한 엘리먼트들이 서로 전혀 접촉할 필요가 없다는 것을 주목해야 한다.

[0023] 접착 층들(상단, 바닥, 측면 또는 이들의 조합들) 중 임의의 것은 독립적으로, 2.5 Å 내지 50 Å; 5Å 내지 30 Å; 또는 5Å 내지 20Å의 두께를 가질 수 있다. 접착 층들(상단, 바닥, 측면 또는 이들의 조합들) 중 임의의 것은 또한 독립적으로, 불연속 또는 연속인 것으로 설명될 수 있다. 개시된 불연속 접착 층들은, 금속 재료의 다수의 "아일랜드들(islands)"로 구성되는 것으로 설명될 수 있다. 그러나 아일랜드들은, 그럴 필요는 없지만, 상이한(disparate) 크기들 및 형상들을 가질 수 있다. 그럴 필요는 없지만, 아일랜드들은 사실상 전부(entirely) 불규칙할 수 있다. 개시된 불연속 접착 층들은, 단층(monolayer) 두께 미만인 것으로 설명될 수 있거나, 혹은 단층 두께 미만인 평균 두께를 가질 수 있다. 개시된 불연속 접착 층들의 재료는 구조의 전체 표면에 걸쳐 존재하지 않을 수 있고, 구조의 상단에 있을 수 있다는 것이 이해될 것이다. 개시된 연속 접착 층들은, 층의 전체 영역에 걸쳐 확산되는 재료를 포함할 수 있다. 개시된 연속 접착 층들은, 적어도 단층 두께 또는 그 이상인 것으로 설명될 수 있거나, 혹은 적어도 단층 두께인 평균 두께를 가질 수 있다. 개시된 불연속 접착 층들 및 연속 접착 층들 둘 다 평균 두께로 설명될 수 있다.

[0024] 접착 층의 평균 두께는, 예를 들어 TEM(transmission electron microscopy) 또는 XRR(X-ray reflectivity), 또는 XPS(x-ray photoelectron spectroscopy)에 의해 측정될 수 있다. 두께는 공지된 두께들을 갖는 표준 샘플들로부터의 교정을 이용하여 결정될 수 있다.

[0025] 개시된 접착 층들은 일반적으로, 강화된 화학적 결합(chemical bonding)을 그 옆의 층들(예를 들어, 클래딩 층 및 NTF 재료)에 제공할 수 있고; 제한된 인터페이스 상호작용들을 갖거나 또는 아무런 인터페이스 상호작용들도 갖지 않는; 허용가능한 레벨들의 NFT 커플링 효율 손실을 갖는; 또는 이들의 일부 조합을 갖는 재료들로 형성될 수 있다.

[0026] 일부 실시예들에서, 강화된 화학적 결합을 클래딩 층에 제공할 수 있는 재료들은, 적어도 부분적으로 충진된(filled) 전도대(conduction band) 또는 일부 실시예들에서, 빈(empty) 전도대를 갖는 재료들로서 설명될 수 있다. 빈 전도대는, 재료가 추가의 전자들을 수용하고 (클래딩 재료로부터) 산소와 화학적 결합들을 형성하는 것을 더 쉽게 만들 수 있다. 재료들은 또한, 페르미 레벨(Fermi level)에서 비충진 상태들(unfilled states)의 큰 파풀레이션(population)들을 갖는 3d 전전이 금속들(early 3d transition metal)이며, 그리고 (클래딩 재료로부터의 전자들(예를 들어, 옥사이드 음이온(oxide anion)(산소) 원자들)이 불연속 금속 층의 비충진 3d 상태들로 전이(transfer)할 수 있는) 도너-엑셉터 타입 결합에 참여할 수 있는 것들로서 설명될 수 있다. 강화된 화학적 결합을 클래딩 층에 제공할 수 있는 재료들은 또한, 그들의 산화물들의 포메이션(formation)에 대해 더 큰 네거티브 열(negative heat)을 갖는 재료들로서 설명될 수 있다. 이러한 재료들은, 이러한 결합이 열역학으로 선호될 수 있기 때문에, 산화물 기판들과 잘 결합되는 더 나은 가능성을 가질 것이다. 이러한 재료들은, 예를 들어, 지르코늄(Zr), 티타늄(Ti), 이트륨(Y), 스칸듐(Sc), 알루미늄(Al), 루테늄(Ru), 바나듐(V), 실리콘(Si), 게르마늄(Ge), 탄탈(Ta), 및 주석(Sn)을 포함할 수 있다. 일부 실시예들에서, 상단 접착 층들, 측면 접착 층들, 또는 이 둘다는 독립적으로, Zr, Ti, Y, Sc, Al, Ru, V, Si, Ge, Ta, Sn, 또는 이들의 조합들로 만들어질 수 있다. 일부 실시예들에서, 상단 접착 층들, 측면 접착 층들, 바닥 접착 층들, 또는 이들의 임의의 조합은 독립적으로, Zr, Ti, Y, Sc, Al, Ru, V, Si, Ge, Ta, Sn, 또는 이들의 조합으로 만들어질 수 있다.

[0027] 일부 실시예들에서, 개시된 접착 층들은, 코발트(Co), 니켈(Ni), 크롬(Cr), 텉스텐(W), 티타늄 텉스텐(TiW), 몰리브덴(Mo), 마그네슘(Mg), 니오븀(Nb), 하프늄(Hf), 아연(Zn), 또는 이들의 일부 조합으로 만들어질 수 있다. 일부 실시예들에서, 상단 접착 층들, 측면 접착 층들, 바닥 접착 층들, 또는 이들의 임의의 조합은 독립적으로, Co, Ni, Cr, W, TiW, Mo, Mg, Nb, Hf, Zn 또는 이들의 조합으로 만들어질 수 있다. 일부 실시예들에서, Co, Ni, Cr, W, TiW, Mo, Mg, Nb, Hf, Zn, 또는 이들의 조합들의 비교적 열악한(bad) 광학적 특성들은, 이러한 접착 층들의 두께가 비교적 작게(low), 예를 들어, 25 Å을 초과하지 않게, 또는 10 Å를 초과하지 않게 바람직하

게 유지될 것임을 의미할 수 있다.

[0028] 일부 실시예들에서, 개시된 접착 층들은, 예를 들어, 티타늄 질화물(TiN), 지르코늄 질화물(ZrN), 탄탈 질화물(TaN), 하프늄 질화물(HfN) 또는 이들의 일부 조합과 같은 질화물로 만들어질 수 있다. 일부 실시예들에서, 상단 접착 층들, 측면 접착 층들, 바닥 접착 층들, 또는 이들의 임의의 조합은 독립적으로 TiN, ZrN, TaN, HfN 또는 이들의 조합으로 만들어질 수 있다. 일부 실시예들에서, TiN, ZrN, TaN, HfN 또는 이들의 조합들은, 약한 플라즈모닉(weakly plasmonic)일 수 있으며 이에 따라 비교적 더 낮은 광학적 패널티를 부여할 수 있으며, 이는 이러한 접착 층들의 두께가, 약간 더 두꺼울 수 있다(예를 들어, 50Å를 초과하지 않거나 또는 20Å를 초과하지 않음)는 것을 의미한다.

[0029] 일부 실시예들에서, 개시된 접착 층들은, 산화물들, 예를 들어 투명 산화물들, 예컨대 예를 들어, 인듐 산화물( $In_2O_3$ ), 주석 산화물( $SnO_2$ ),  $In_2O_3-SnO_2$  (ITO)의 고용체, 아연 산화물( $ZnO$ ), 알루미늄(Al) 도핑된  $ZnO$ , 갈륨(Ga) 도핑된  $ZnO$ , 또는 이들의 일부 조합으로 만들어질 수 있다. 일부 실시예들에서, 상단 접착 층들, 측면 접착 층들, 바닥 접착 층들, 또는 이들의 임의의 조합은 독립적으로,  $In_2O_3$ ,  $SnO_2$ , ITO,  $ZnO$ , Al 도핑된  $ZnO$ , Ga 도핑된  $ZnO$ , 또는 이들의 조합들로 만들어질 수 있다. 일부 실시예들에서,  $In_2O_3$ ,  $SnO_2$ , ITO,  $ZnO$ , Al 도핑된  $ZnO$ , Ga 도핑된  $ZnO$ , 또는 이들의 조합들은, 약한 플라즈모닉일 수 있으며 이에 따라 비교적 더 낮은 광학적 패널티를 부여할 수 있으며, 이는 이러한 접착 층들의 두께가, 약간 더 두꺼울 수 있다(예를 들어, 50Å를 초과하지 않거나 또는 20Å를 초과하지 않음)는 것을 의미한다.

[0030] 일부 실시예들에서, 개시된 접착 층들은, 황화물들, 예컨대, 예를 들어 Zr, Zn, Ti, Co, 은(Ag), 구리(Cu), 인듐(In), 카드뮴(Cd), Sn, 비스무트(Bi), 납(Pb), 셀레늄(Se), 철(Fe), Mo의 황화물들; 또는 이들의 이원 황화물들로 만들어질 수 있다. 일부 실시예들에서, 상단 접착 층들, 측면 접착 층들, 바닥 접착 층들, 또는 이들의 임의의 조합은 독립적으로, Zr, Zn, Ti, Co, Ag, Cu, In, Cd, Sn, Bi, Pb, Se, Fe, 또는 Mo의 황화물들; 또는 이들의 이원 황화물들로 만들어질 수 있다.

[0031] 일부 실시예들에서, 개시된 접착 층들은 또한, 예를 들어, 실리콘 탄화물(SiC), 수소화(hydrogenated) 실리콘 탄화물(SiC:H), 또는 이들의 조합들로 만들어질 수 있다.

[0032] 제한된 인터페이스 상호작용들을 갖거나 또는 어떠한 인터페이스 상호작용들도 갖지 않는 재료들은, 일반적으로 NFT 및/또는 클래딩 재료들로의 최소 확산을 갖는 또는 이를 갖지 않는 재료들을 포함한다. 이러한 재료들은 또한 일반적으로 금속간 포메이션(intermetallic formation)을 갖지 않는다. 바람직하게 재료는, 약 400°C의 온도들까지 이러한 특성들을 유지할 것이다. 이는, 양호한 열 안정성 및 NFT 재료의 광학적 특성들에 대한 최소 경감을 허용(또는 확보)할 수 있다.

[0033] 허용 가능한 레벨들의 NFT 커플링 효율 손실을 제공하는 재료들이 또한 요구된다. 이러한 재료들은 일반적으로, 비교적 높은 굴절률들을 가질 수 있다. NFT 재료 및 클래딩 재료 층의 인터페이스에, 비-플라즈모닉 재료 층, 예를 들어, 일부 실시예들에서 개시된 접착 층의 존재는, 해당 인터페이스가 표면 플라즈몬들을 지지하는 능력을 "약화(dampen)"시킬 수 있으며, 이는 NFT로부터의 더 약한 전기장 방출을 야기할 수 있다.

[0034] 또한, 본원에는, 니어 필드 트랜스듀서 및 기입 폴(예컨대, 도 3a의 310 및 305)을 포함하는 디바이스들이 개시된다. 이러한 예시적인 디바이스는 또한, NPS(NFT to pole spacer or spacing) 층, CNS(core to NFT spacer or spacing) 층 또는 이를 둘다(도편트로 도핑된 산화물, 예를 들어  $SiO_2$ 로 만들어짐)를 포함할 수 있다. 예시적인 도편트들은, 예를 들어 Ta, Ti, Nb, Hf, 또는 이들의 조합들을 포함할 수 있다. 이러한 NPS, CNS, 또는 이를 둘 다의 층들은, NFT 재료에 양호한 접착력을 제공할 것이지만, 여전히 허용 가능한 또는 심지어 양호한 광학적 특성들을 제공할 것이다. 재료에서의 도핑 레벨을 제어하기 위해 원하는 굴절률(예를 들어,  $n < 1.6$ )이 이용될 수 있다.

[0035] 개시된 접착 층들을 포함하는 디바이스들을 제조하는 방법들은, 접착 층의 위치(즉, 바닥, 측면, 상단)에 따라 변한다. 바닥 접착 층 및/또는 측면 접착 층이 이용되는 실시예들에서, 바닥 및/또는 측면 접착 층이 증착되고, 이후 NFT 재료가 증착되고, 이후 클래딩 또는 유전 재료가 증착된다. 이후 바닥 및/또는 측면 접착 층들은, NFT 재료와 하부에 놓인 유전 재료(예를 들어, 바닥 클래딩 층 및 전방 클래딩 층, 도 3을 참조로, 바닥 클래딩 층(325) 및 전방 클래딩 층(315 및 320)) 간의 접착력에 영향을 미친다. 상단 접착 층이 이용되는 실시예들에서, 상단 접착 층 재료는, 예를 들어 트렌치(개시된 접착 층 재료로 라이닝되거나 또는 라이닝되지 않음)에 증착된 이후, NFT 재료상에 증착된다. 이후 상단 접착 층은, NFT 재료와 상부에 놓인 유전 재료(예를

들어, 상단 클래딩 층, 도 3을 참조로 예를 들어 상단 클래딩 층(330) 간의 접착력에 영향을 미친다.

[0036] 개시된 접착 층들을 형성하는 예시적인 방법은, 매우느린(ultraslow) 증착 레이트를 이용하는 마그네트론 스팍터링을 포함할 수 있다. 일부 실시예들에서, 프로세스는, 금속 단층의 두께 미만인 두께를 목표로 설정되며 불연속 층이 형성된다.

[0037] 개시된 접착 층들을 형성하는 하나의 예시적인 방법은, 인-시츄(in-situ) 증착이며, 여기서 접착 층 및 NFT 층, 또는 접착 층 및 상단 산화물 층은, 진공 파손 없이 증착된다. 이러한 방법은, 접착 층의 접착 특성들을 손상 시킬 수 있는 접착 층의 산화를 방지한다.

[0038] 개시된 접착 층들을 형성하는 다른 예시적인 방법은, 화학적 기상 증착(CVD) 또는 원자 층 증착(ALD)과 같은 저-에너지 프로세스들을 포함할 수 있다. 이러한 기술들을 사용할 때, 클래딩 층의 재료에 비해 높은 금속 표면 자유 에너지 및 흡착원자 이동성(adatom mobility) 부재는, 다소 (또는 실시예들에서, 매우) 규칙적인 분포의 작은 직경의 아일랜드들이 성장되며 야기시킬 수 있다. 이는 NFT/클래딩 층 인터페이스에서의 지형적 (topographical) 인터록킹을 조장한다. 아일랜드형(island like) 막 구조는 또한, 재료의 "활성화된 디웨팅 (activated dewetting)" (여기서는, 대기 금속 증착(ambient metal deposition) 다음에, 아일랜드들로의 막의 분리(segregation)를 조장하는 금속 열 어닐링이 행해짐)을 이용하여 형성될 수 있다.

[0039] 개시된 접착 층들을 형성하는 또 다른 예시적인 방법은, 접착 층(들)이 형성된 이후 NPS로서, 원하는 산화물과 상이한 산화물 층의 보호 층의 증착을 포함할 수 있다. 이는, 유전 재료 층의 증착 이전에 진공이 파손되게 할 수 있다.

[0040] 접착 층들은, NFT와 적어도 하나의 클래딩 층 간의 접착력을 개선하기 위해, 강화된 화학적 결합, 나노스케일 토포그래피, 제한된 인터페이스 상호작용들(화산, 금속간 포메이션) 또는 이들의 일부 조합을 제공하는 것으로 생각된다. 접착 층의 일부 실시예들에 대한 불연속 특성, 그리고/또는 접착 층의 다른 실시예들에서의 연속 층의 작은 두께 때문에, 접착 층의 재료는 NFT의 활성 플라즈모닉 인터페이스의 작은 부분(small fraction)만을 점유한다. 이는 NFT의 광학적 특성들에 불리하게 영향을 미치지 않고 접착력이 강화되게 허용한다.

[0041] 접착 층을 형성하는 프로세스들은, 자기 디바이스의 전체 제조 프로세스에 쉽게 통합될 수 있다. 전체적으로, 개시된 접착 층들의 사용은, NFT의 박리(delamination)로 인한 수율 손실을 줄이거나 없앨 수 있으며 자기 디바이스에 대한 현재 포메이션 프로세스들에 매우 작은 영향력으로, 자기 디바이스의 동작 동안 증가된 NFT 수명에 기여할 수 있다.

[0042] 예들

[0043] 본 개시가 그렇게 제한되는 것은 아니지만, 본 개시의 다양한 양상들에 대한 인식은 하기 제공되는 예들의 논의를 통해 얻어질 것이다.

#### 익스-시튜 프로세스에서의 접착력(Adhesion in Ex-Situ Processes)

[0045] 도 8에 도시된 층 구조가 제조되었다. 바닥 산화물 층은 개시된 디바이스들에서의 CNS 층(즉, core to NFT space 층)을 나타내며 50nm TaSiO<sub>x</sub>였다. 바닥 접착 층은 제 1 Zr 층으로 표현된다. 25nm 금 층은, 개시된 디바이스들에서의 NFT 층을 나타낸다. 실시예들 중 일부에서, 상단 접착 층은 제 2 Zr 층이다. Zr 층은 익스-시튜로 형성되었다. 상단 산화물 층은, 개시된 디바이스들의 NPS(NFT to pole space) 층을 나타내며, 그 자체에는 물리적 기상 증착(PVD)된 SiO<sub>2</sub> 층; PVD 플래시(flash)의 5nm SiO<sub>2</sub> 및 25 nm TEOS(tetra- ethyl-orthosilicate) SiO<sub>2</sub>; 그리고 30 nm TaSiO<sub>x</sub>로 이루어진 3개 층 구조가 포함된다.

[0046] 구조물이 박리되었는지 여부를 결정하기 위해 구조들 상에서 시트 막 테입 테스트(sheet film tape test)가 수행되었다. 시트 막 테스트는, 웨이퍼 상에 막을 증착하고, 이후 막 상에 (아래 쪽이 끈끈하게) 테잎을 적용하고 이를 풀 오프(pulling off)함으로써 수행된다. 강하게 접착되는 막들은 기판에 결합된 채 유지될 것이며 박리 없이 테잎이 풀 오프될 것이다. 열악하게 접착되는 막들은 테잎과 함께 막을 풀 오프할 것이다.

[0047] 표 1은 테스트되었던 다양한 스택들 및 획득된 결과들을 도시한다. 표 1에서의 테스트된 모든 스택들에는 5Å Zr의 바닥 접착 층이 포함된다. 모든 스택들은 15분 동안 350°C에서 금속 열 어닐링(RTA) 처리되었다. 모든 스택들은, 테잎 테스트가 수행되기 이전에 시작적으로 양호한 것으로 보인다.

표 1

| No. | Zr 상단 접착 층 두께(Å) | NPS 타입                | 테입 테스트                                                |

|-----|------------------|-----------------------|-------------------------------------------------------|

| 1   | 0                | TEOS-SiO <sub>2</sub> | SiO <sub>2</sub> 막이 테입과 함께 쉽게 풀 오프되었음                 |

| 2   | 5                | TEOS-SiO <sub>2</sub> | SiO <sub>2</sub> 가 일부 위치들상에서 테입과 함께 풀 오프될 수 있음- 최소 박리 |

| 3   | 10               | TEOS-SiO <sub>2</sub> | 박리 없음-테입 테스트 통과됨                                      |

| 4   | 20               | TEOS-SiO <sub>2</sub> | 박리 없음-테입 테스트 통과됨                                      |

| 5   | 30               | TEOS-SiO <sub>2</sub> | 박리 없음-테입 테스트 통과됨                                      |

| 6   | 40               | TEOS-SiO <sub>2</sub> | 박리 없음-테입 테스트 통과됨                                      |

| 7   | 50               | TEOS-SiO <sub>2</sub> | 박리 없음-테입 테스트 통과됨                                      |

| 8   | 0                | PVD-SiO <sub>2</sub>  | SiO <sub>2</sub> 가 일부 위치들상에서 테입과 함께 풀 오프될 수 있음- 최소 박리 |

| 9   | 5                | PVD-SiO <sub>2</sub>  | 박리 없음-테입 테스트 통과됨                                      |

| 10  | 0                | TaSiOx                | 박리 없음-테입 테스트 통과됨                                      |

| 11  | 5                | TaSiOx                | 박리 없음-테입 테스트 통과됨                                      |

## 인-시튜 프로세스에서의 접착력(Adhesion in In-Situ Processes)

표 2에서의 스택들은, 상단 접착 층을 증착하기 위한 인-시튜 프로세스들을 이용하여 Si/SiO<sub>2</sub>/TaSiOx 50nm/Zr 5 Å/Au 25nm 스택 상에 마련되었다. 이는, 25 nm 금 층과 (상단 접착 층을 나타내는) 상단 Zr 층의 증착 사이에서 진공이 파손되지 않았다는 것을 의미한다. 각각의 스택은 제 2 중복 랜(second duplicate ran)을 가지며, 이는 제 1 것 바로 아래에 제공된다. 스택들은 표 2에서 제시되는 상이한 조건들에서 어닐링되었다. 명확성을 위해, 표 2에서 첫 번째 4개(중복을 고려하면 8개)의 엔트리들은, 상단 접착 층을 포함하지 않으며 마지막 4개(중복을 고려하면 8개)의 엔트리들은, 상단 접착 층을 포함한다.

표 2

| No. | 추가 층들                                    | 증착직후<br>(As deposited)           | 테입 테스트 결과들                            |                             |                                  |

|-----|------------------------------------------|----------------------------------|---------------------------------------|-----------------------------|----------------------------------|

|     |                                          |                                  | 15분 동안<br>225°C에서 RAT                 | 3시간 동안<br>225°C에서<br>진공 어닐링 | 15분 동안<br>300°C 에어 어<br>닐링       |

| 12  | 30 nm PVD<br>SiO <sub>2</sub>            | 90-100% 박리                       | X                                     | X                           | X                                |

| 13  | 중복                                       | 90-100% 박리                       | X                                     | X                           | X                                |

| 14  | 5 nm FC/ 25<br>nm LTC                    | 100% 박리                          | X                                     | X                           | X                                |

| 15  | 중복                                       | 100% 박리                          | X                                     | X                           | X                                |

| 16  | 10 nm FC/<br>25 nm LTC                   | 100% 박리                          | X                                     | X                           | X                                |

| 17  | 중복                                       | 100% 박리                          | X                                     | X                           | X                                |

| 18  | 30 nm<br>TaSiOx                          | 0% 박리                            | 0% 박리                                 | 0% 박리                       | 0% 박리                            |

| 19  | 중복                                       | 하나의 위치는 박리를 나<br>타내나, 다른 위치들은 0% |                                       |                             |                                  |

| 20  | Zr 5 Å/ 30<br>nm PVD<br>SiO <sub>2</sub> | 하나의 위치는 박리를 나<br>타내나, 다른 위치들은 0% | 하나의 위치는<br>박리를<br>나타내나, 다른<br>위치들은 0% | 다른<br>위치들은 0%               | 보다 많은<br>박리(10~20%)를<br>나타내기 시작함 |

|    |                                 |                                       |                                       |                            |            |

|----|---------------------------------|---------------------------------------|---------------------------------------|----------------------------|------------|

| 21 | 중복                              | 하나의 위치는 박리를 나타내나, 다른 위치들은 0%          |                                       |                            |            |

| 22 | 5 Å Zr/5 nm<br>FC/25 nm<br>LTC  | 웨이퍼 에지 근처에서는 5-10% 박리, 그러나 다른 위치들은 0% | 웨이퍼 에지 근처에서는 5-10% 박리, 그러나 다른 위치들은 0% | 보다 많은 박리(50-60%)를 나타내기 시작함 | 90-100% 박리 |

| 23 | 중복                              | 0% 박리                                 |                                       |                            |            |

| 24 | 5 Å Zr/10 nm<br>FC/20 nm<br>LTC | 웨이퍼 에지 근처에서는 5-10% 박리, 그러나 다른 위치들은 0% | 웨이퍼 에지 근처에서는 5-10% 박리, 그러나 다른 위치들은 0% | 보다 많은 박리(50-60%)를 나타내기 시작함 | 90-100% 박리 |

| 25 | 중복                              | 0% 박리                                 |                                       |                            |            |

| 26 | 5 Å Zr/30 nm<br>TaSiOx          | 0% 박리                                 | 하나의 위치는 박리를 나타내나, 다른 위치들은 0%          | X<br>(웨이퍼 파손)              | X          |

| 27 | 중복                              | 0% 박리                                 | 0% 박리                                 | 0% 박리                      | 0% 박리      |

[0052] FC = 플래시 PVD SiO<sub>2</sub>

[0053] LTC=LDR 테트라-에틸-오로쏘-실리케이트(tetra-ethyl-ortho-silicate) SiO<sub>2</sub>

#### [0054] 광학적 특성들

표 2로부터의 예들 12, 14, 18, 20, 22, 및 26에 대한 광학적 특성들은, 증착직후(as deposited) 및 다양한 조건들에서의 어널링 이후 엘립소미트리(ellipsometry)에 의해 굴절률(n) 및 흡광 계수(K)를 측정함으로써 평가되었다. 테이터는 아래 표 3에 도시된다.

표 3

|    | 증착직후 |      | 15분 동안 225°C에서 RTA |      | 15분 동안 300°C에서 RTA |      |

|----|------|------|--------------------|------|--------------------|------|

|    | n    | k    | n                  | k    | n                  | k    |

| 12 | 0.23 | 5.51 | 0.178              | 5.5  | 0.173              | 5.5  |

| 14 | 0.23 | 5.5  | 0.175              | 5.5  | 0.171              | 5.5  |

| 18 | 0.27 | 5.54 | 0.231              | 5.54 | 0.22               | 5.52 |

| 20 | 0.33 | 5.56 | 0.31               | 5.57 | 0.294              | 5.51 |

| 22 | 0.35 | 5.58 | 0.28               | 5.53 | 0.267              | 5.52 |

| 26 | 0.26 | 5.52 | 0.23               | 5.54 | 0.213              | 5.5  |

[0057] 따라서, "INTERLAYER FOR DEVICE INCLUDING NFT AND CLADDING LAYERS"의 실시예들이 개시된다. 앞서 개시된 구현들 및 다른 구현들은 하기 청구항들의 범위 내에 속한다. 당업자들은, 본 개시가 이들 개시된 것들 이외의 실시예들과 함께 실시될 수 있다는 것을 인식할 것이다. 개시된 실시예들은 제한이 아닌 예시를 목적으로 제공된다.

도면

도면1

도면2

도면3a

도면3b

도면3c

도면4a

도면4b

도면4c

도면5a

도면5b

도면5c

도면6a

도면6b

도면6c

도면7a

도면7b

도면7c

도면8