(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4402178号

(P4402178)

(45) 発行日 平成22年1月20日(2010.1.20)

(24) 登録日 平成21年11月6日(2009.11.6)

(51) Int.Cl.

F 1

G 11 C 15/04 (2006.01)

G 11 C 15/04

6 3 1 F

G 06 F 17/30 (2006.01)

G 06 F 17/30

H 04 L 12/56 (2006.01)

H 04 L 12/56

請求項の数 5 (全 18 頁)

(21) 出願番号 特願平9-276556

(22) 出願日 平成9年9月24日(1997.9.24)

(65) 公開番号 特開平10-126422

(43) 公開日 平成10年5月15日(1998.5.15)

審査請求日 平成16年9月21日(2004.9.21)

審判番号 不服2007-2642(P2007-2642/J1)

審判請求日 平成19年1月22日(2007.1.22)

(31) 優先権主張番号 08/722,587

(32) 優先日 平成8年9月27日(1996.9.27)

(33) 優先権主張国 米国(US)

(73) 特許権者 504199127

フリースケール セミコンダクター イン

コーポレイテッド

アメリカ合衆国 78735 テキサス州

オースティン ウィリアム キャノン

ドライブ ウエスト 6501

(74) 代理人 100142907

弁理士 本田 淳

(74) 代理人 100149641

弁理士 池上 美穂

(72) 発明者 ジョン・アショア・ロシェク

アメリカ合衆国テキサス州78759、オ

ースチン、モラード・コウブ 10306

#261

最終頁に続く

(54) 【発明の名称】同時サーチ内容アドレス可能メモリ回路のための装置および方法

## (57) 【特許請求の範囲】

## 【請求項 1】

内容アドレス可能メモリ(CAM)を使用する方法であって、

前記CAMの第1のメモリアレイおよび前記CAMの第2のメモリアレイを提供する段階であり、前記第1のメモリアレイは整合ワードを備えかつ前記第2のメモリアレイはリンクワードを備える、段階、

基準ワードを前記CAMに提供する段階、

前記第1のメモリアレイを2進サーチして前記基準ワードに等しい整合ワードを検出する段階であって、前記2進サーチする段階は、選択されたロケーションの内容が前記基準ワードと同じでない間は、さらに以下のループすなわち、

前記第1のメモリアレイにおけるあるロケーション、すなわち前記選択されたロケーション、にアクセスする段階であって、前記ロケーションは前記第1のメモリアレイを第1の部分と第2の部分とに分割する、段階、

前記選択されたロケーションの内容を前記基準ワードと比較する段階、

前記第1のメモリアレイの部分集合として前記第1の部分または前記第2の部分を選択して引き続くるループ反復動作においてサーチを行なう段階、

からなるループを実行する段階を備える、段階、そして

前記第2のメモリアレイから前記整合ワードに対応するリンクワードを出力する段階、

を具備することを特徴とする内容アドレス可能メモリ(CAM)を実施する方法。

## 【請求項 2】

10

20

ヘッダ情報の同時サーチのための方法であって、

ヘッダから第1および第2のフィールドを読み取る段階、そして

並列的に、

1) 前記第1のフィールドおよび第1の値、

2) 前記第2のフィールドおよび第2の値、そして

3) 前記第2のフィールドおよび所定の値であって、前記所定の値は長さが前記第2のフィールドに等しいもの、

を比較する段階、

を具備することを特徴とするヘッダ情報の同時サーチのための方法。

**【請求項3】**

10

前記読み取る段階は、さらに、メモリアレイの2進インデクシングを行う段階を具備し、前記2進インデクシングを行う段階は、整合条件が満たされない間は以下のループすなわち、

メモリアレイのあるロケーションから前記第1の値および前記第2の値を含むヘッダ比較値にアクセスする段階であって、前記ロケーションは前記メモリアレイを第1の部分および第2の部分に分割する、段階、

前記項目1)~3)の比較を実行して整合条件を発生する段階、そして

前記メモリアレイの部分集合として前記第1の部分または前記第2の部分を選択しその後のループ反復動作においてサーチを行う段階、

からなるループを実行する段階、

20

を具備することを特徴とする請求項2に記載の方法。

**【請求項4】**

前記第1のフィールドおよび前記第2のフィールドはATMヘッダを構成することを特徴とする請求項2に記載の方法。

**【請求項5】**

さらに、前記比較する段階に応じて前記第1のフィールドおよび前記第2のフィールドを変換する段階を具備することを特徴とする請求項2に記載の方法。

**【発明の詳細な説明】**

**【0001】**

**【発明の属する技術分野】**

30

本発明は一般的にはデジタル電子装置に関し、かつより特定的には交換ネットワークにおいてヘッダ情報を管理するために使用される装置に関する。

**【0002】**

**【従来の技術】**

通信およびコンピュータネットワークは種々のハードウェア機器およびソフトウェアから構成されかつ用途および複雑さが増大してきている。コンピュータの典型としてのコンピュータネットワークの人気およびネットワークユーザの間で転送されるデータの量の増大はネットワークの容量およびプロトコルを時間と共に増大させている。種々のネットワーク通信プロトコルはデータをネットワークによって結合された装置の間で転送する。イーサネットおよび非同期転送モードはそのような通信プロトコルの例である。

40

**【0003】**

非同期転送モード(以後“ATM”と称する)はツイストケーブルを使用して25メガビット/秒程度の低いかつ光ケーブルを使用して10ギガビット/秒程度の高い帯域幅を提供する。ATMスイッチまたは交換機(ATM switch)はセルをネットワーク内の種々のポイントの間で転送する。セルは制御情報、ヘッダおよびデータパケットを含む。セル内のヘッダはATM交換機がデータを導くことができるようとする交換識別子(swapping identifiers)を含む。ATMスイッチはプログラムされたりストに対してそれが受信する各々の交換識別子を問合せてどの出力チャネルにセルが出力されるべきかを決定する。データパケットが中間ノードによって受信されたとき、データパケットに付随するヘッダにデスティネイション情報が含まれている。ノードはその

50

メモリを調べてデスティネイション情報が前に記憶されているか否かを決定することによりその伝送に対するデータパケットを導くことにそれが前に同意したか否かを判定する。もし同意しておれば、フォワードアドレス (forwarding address) もまた記憶されておりかつノードはそのデータパケットをデスティネイションアドレスに向かうルートにおける次のノードへと送る。それが各々のデータ転送を受信したとき、ノードはそのメモリの内容を問合せてそれが送信を送ることに同意したか否かを決定する。もしデスティネイション情報があらかじめ送られれば、メモリはそのデータパケットを次のノードに導くために該デスティネイション情報に関連するフォワードアドレスを作成する。

#### 【0004】

内容アドレス可能メモリまたは連想記憶装置（以後“CAM”と称する）はATMスイッチのための交換識別子を記憶する。連想または内容アドレス可能メモリにおいては、整合ワードおよび交換識別子がメモリ内に関連する対として記憶される。CAMが基準ワードを受信したとき、それは該基準ワードに等しい整合ワードがメモリに格納されているか否かを判定する。もし格納されておれば、それは整合した基準ワードに関連するリンクワードを作成する。CAMの重要な面は整合ワードおよびその関連するリンクワードの間の関連または連想であり、各々のワードがその定義と関連して記憶されている辞書とよく似ている。辞書においては、ある提供されたワードがルックアップされかつ該ワードに関連する定義が生成される。CAMにおいては、提供された基準ワードがルックアップされ、すなわち、整合ワードと比較され、かつもしそれらが等しければ、整合ワードに関連するリンクワードが生成される。

#### 【0005】

一般に、ATMのCAMのメモリアレイは整合ワードテーブルおよびリンクワードテーブルへと編成される。もし基準ワードが整合ワードテーブルからのエントリと整合すれば、関連するリンクワードが出力に生成される。もし整合が検出されなければ、出力ワードは、例えば、エラーフラグビットをセットすることにより不首尾または障害を指示する。ATMの用途においては、基準ワードは交換識別子からなる。交換識別子は仮想パス識別子 (virtual path identifier)（以後“VPI”と称する）および仮想チャネル識別子 (virtual channel identifier)（以後“VCI”と称する）から構成される。CAMはヘッダにおけるVPIおよびVCIをCAMにおけるVPIおよびVCIエントリと比較する。交換識別子は仮想パス接続（以後“VPC”と称する）または仮想回路接続（以後“VCC”と称する）が存在するか否かを決定する。

#### 【0006】

小さなサイズのCAMはしばしばこの機能をハードウェアで提供し、従って基準ワードが同時に整合ワードテーブルにおけるそれぞれのワードと比較されるようにし、それによって出力ワードが1クロックサイクルで生成される全並列モード (full parallel mode) で動作する。しかしながら、より大きなCAMの必要性が増大するに応じて、並列モードは長いサーチ時間のため可能ではなくなる。

#### 【0007】

##### 【発明が解決しようとする課題】

大きなCAMを実施するための従来より知られた技術はメモリを区別可能なまたは別個のクラスに予めソートする (pre sort) ことである。例えば、4,096ワードの深さのCAMは特定の整合およびリンクワード対がCAMの1つにのみ記憶される4つの別個のより浅い1,024ワードのCAMへと予め分類される。しかしながら、この手法は他のものが実質的に空きを有する一方で1つのクラスに対応するCAMが満たされることになり、それによってCAMの深さを実効的に低減する。必要に応じて各々のCAMのサイズを動的に調整するためCAMに論理を加えることはCAMの複雑さおよびコストを実質的に増大させる。

#### 【0008】

10

20

30

40

50

さらに、VCCまたはVPCを確立するため、並列サーチ戦略が使用されてもあるいは直列サーチ戦略が使用されても、各々のCAMエントリに対して2つのサーチが必要とされる。第1のサーチはVCCをチェックし、入力ヘッダおよび交換識別子を比較する。第2のサーチはVPCに対するもので、入力ヘッダおよび交換識別子を比較する。

#### 【0009】

並列サーチを行うために2つの知られた手法が使用される。1つの方法は1つのCAMアレイを使用し、各アレイを2回問合せる。他の方法は2つの別個のCAMを使用し、各々のCAMがVCIまたはVPIのみを記憶する。1つのCAMの手法はデュアルCAM手法よりも多くの時間を必要とする。しかしながら、デュアルCAM手法は交換ネットワークにより多くのハードウェアおよびコストを加えることになる。

10

#### 【0010】

##### 【課題を解決するための手段】

本発明の一態様によれば、内容アドレス可能メモリ(CAM)を実施する方法が提供され、該方法は第1のメモリアレイおよび第2のメモリアレイを提供する段階であり、前記第1のメモリアレイは整合ワードを備えかつ前記第2のメモリアレイはリンクワードを備えるもの、基準ワードを前記CAMに提供する段階、前記第1のメモリアレイを2進サーチして前記基準ワードに等しい整合ワードを検出する段階、そして前記第2のメモリアレイから前記整合ワードに対応するリンクワードを出力する段階、を具備することを特徴とする。

#### 【0011】

20

本発明の別の態様では、制御情報の同時サーチのための方法が提供され、該方法はヘッダから第1および第2のフィールドを読み取る段階、そして並列的に、(1)前記第1のフィールドおよび第1のタグ(2)前記第2のフィールドおよび第2のタグ、そして(3)所定のベクトルを備えた第2のフィールド、を比較する段階、を具備することを特徴とする。

#### 【0012】

この場合、前記読み取る段階は、メモリアレイの2進インデクシングを行う段階を具備すると好都合である。

#### 【0013】

また、前記第1のフィールドおよび前記第2のフィールドはATMヘッダを含むものとすることができる。

30

#### 【0014】

さらに、前記比較する段階に応じて前記第1のフィールドおよび前記第2のフィールドを変換する段階を具備すると好都合である。

#### 【0015】

##### 【発明の実施の形態】

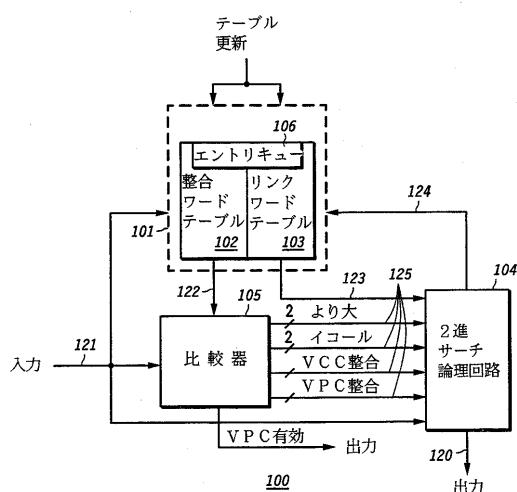

図1は、本発明に係わるネットワークデーターティング回路において使用される内容アドレス可能メモリ(CAM)回路100のブロック図である。CAM100はデータを記憶しつつ新規な方法に従って比較のためにデータをアクセスする。この機構はCAM100の部分からヘッダ情報を人為的に排除することなくアクセス時間を低減する。CAM100はこれによってそのメモリの使用において高速でありかつ効率的である。さらに、VCCまたはVPC整合のための各々の個々の比較は開示された発明の第2の面によって加速される。

40

#### 【0016】

図1を参照して説明を続けると、CAM100はメモリワードのアレイ101、比較回路105、2進サーチ論理回路104、およびエントリキューリー106を具備する。CAM100は基準ワードの内容に基づき出力ワードを提供するために端子120に出力を有する。ここで使用されているように、用語「端子(terminal)」は单一の導電ラインに言及しつつ複数の導電ラインを含むバスラインを含む。CAM100はデスティネイションヘッダ信号または他の伝送されたデータをネットワークから受けるための入力を

50

端子 121 に有する。基準ワードは前記デスティネイションヘッダ信号の一部として伝送される。

【 0017 】

メモリワードのアレイ 101 はスタティック RAM セルのコアを備えかつ整合ワードテーブル 102 およびリンクワードテーブル 103 として構成され、それによって各々のロケーションアドレスにおいて記憶されたメモリワードが整合ワードおよび関連するリンクワードから構成されるようにされる。1 つの実施形態では、各々のスタティック RAM セルは 4 つのトランジスタからなりかつ 5 ナノセカンドのアクセス時間有する。用途に応じて、メモリワードのアレイ 101 はこれに代えてダイナミック RAM またはフラッシュメモリから構成できる。端子 124 における入力は前記アレイからメモリワードを選択するロケーションアドレス信号を受信し、かつ端子 122 および 123 における第 1 および第 2 の出力はそれぞれ選択された整合ワードおよびリンクワードを提供する。

10

【 0018 】

比較回路 105 はそれぞれ基準ワードおよび選択された整合ワードを受けるたに端子 121 および 122 において第 1 および第 2 の入力を有し、かつ 5 つの出力信号、「より大きい (G R E A T E R ) 」信号、「等しい (E Q U A L ) 」信号、「V C C 整合 (V C C M A T C H ) 」信号、「V P C 整合 (V P C M A T C H ) 」信号」、および「V P C 有効 (V P C V A L I D ) 」信号を提供するための出力を端子 125 に有する。比較回路 105 は基準ワードおよび前記選択された整合ワードの内容を比較しつつその比較の論理的結果に對応する出力信号を肯定する。例えば、もし入力基準ワードが選択された整合ワードより大きければ、比較器 105 は「より大きい」信号を肯定する。V C C および V P C 整合に對してはそれぞれ前記「V C C 整合」および「V P C 整合」が肯定される。もし V P C 整合が存在すれば、比較器 105 は「V P C 有効」信号を肯定する。比較器 105 および「より大きい」信号、「等しい」信号、「V C C 整合」信号、「V P C 整合」信号、および「V P C 有効」信号については図 8 および図 10 を参照して後に説明する。

20

【 0019 】

前記エントリキューリー 106 はテーブル更新のために基準ワードを受信する。C A M 100 に加えられるべき基準ワードまたは C A M 100 から削除されるべき基準ワードはバッファリングされる。いくつかの実施形態では、エントリキューリー 106 におけるバッファリングされたエントリ (b u f f e r e d \_ e n t r i e s ) は整合ワードテーブルをサーチする前に直線的にまたはリニアに (l i n e a r l y ) サーチされる。整合ワードテーブルをサーチする方法はすぐ後に説明する。さらに別の実施形態では、エントリキューリー 106 は除去されかつ基準ワードが C A M が利用可能になるや否やソートされる。

30

【 0020 】

前記 2 進サーチ論理回路 104 は整合ワードテーブル 102 の 2 進サーチを行い整合ワードテーブル 102 におけるエントリが基準ワードと同じ内容を有するか否かを判定する。2 進サーチはサーチされるべきテーブルが所定の順序にソートされる必要がある。従って、システムのスタートアップ時に、かつ基準ワードを受け入れる前に、メモリワードのアレイ 101 は整合ワードテーブル 102 のエントリに基づき所定の順序にソートされる。示された実施形態では、最も小さな基準ワードを有する基準ワード - リンクワード対がメモリワードのアレイ 101 の最初のエントリに記憶され、第 2 に小さな基準ワードを有する基準ワードがメモリワードのアレイの第 2 のエントリに格納されるなどとなる。

40

【 0021 】

理論上は、整合ワードテーブルは任意の所定の順序にソートすることができる。しかしながら、この順序は比較回路 105 によって認識することができ、従ってそれがある与えられた基準ワードを選択された整合ワードと比較するときにそれが整合する整合ワードが、もしそれが整合ワードテーブル 102 に見出されるべきであれば、前記選択された整合ワードよりも高いまたはより低いアドレスを有するか否かを決定できなければならない。

【 0022 】

50

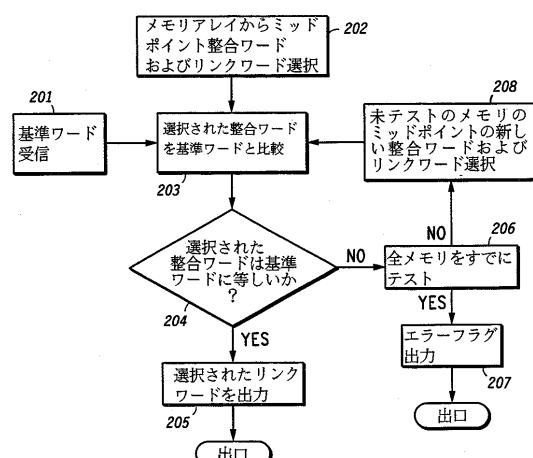

図2は、2進サーチ論理回路104によって使用されて基準ワードに整合する整合ワードが格納されているかを判定するためにメモリワードのアレイ101を2進サーチするための2進サーチアルゴリズムのCAM構成の流れ図である。整合テーブルは予め、例えば、ローからハイへと増大するロケーションアドレスでソートされているものと仮定する。ステップ201において、基準ワードが、例えば、ネットワークバスから受信される。ステップ202において、メモリアレイの中間点(mid point)に対応するロケーションアドレスがアレイから整合ワードおよび関連するリンクワードを選択するために提供される。ステップ203は選択された整合ワードを基準ワードと比較する。もしそれらが等しければ、(ステップ204)、選択されたリンクワードがステップ205においてCAMの出力に提供されかつ2進サーチは終了する。

10

#### 【0023】

もし選択された整合ワードが基準ワードに等しくなければ(ステップ204)、2進サーチ論理回路はステップ206においてアレイ全体が既に基準ワードと比較されたか否かを判定する。もしメモリワードのアレイ101全体がまだテストされていなければ、基準ワードと整合する整合ワードが検出される可能性のあるメモリアレイのハーフ(half)の中間点に対応する新しいロケーションアドレスが提供される。ステップ203および204による各々の比較の後にメモリの半分が整合する整合ワードを含む可能性からはずされ、それはメモリアレイの所定の順序への前もってのソートのためである。従って、2進サーチの各々のサイクルはメモリアレイのテストされていない部分の半分を累進的に低減する。

20

#### 【0024】

もしステップ206が整合する整合ワードが検出されることなくメモリアレイ全体がテストされたことを判定すれば、ステップ207においてエラーフラグが出力にセットされかつ2進サーチが終了する。しかしながら、もしメモリアレイの一部がテストするために残っておれば、ステップ208においてメモリアレイのテストされていない部分の中間点に対応する新しいロケーションアドレスが提供される。新しいロケーションアドレスはステップ202において新しい整合およびリンクワードを選択しかつこのサイクルは2進サーチが終了するまで反復する。

#### 【0025】

図1に戻ると、2進サーチ論理回路104はメモリワードのアレイにロケーションアドレス信号を提供するための第1の出力を端子124に有する。2進サーチのいずれかのサイクルにおいて、ロケーションアドレスはメモリワードのアレイ101のテストされていない部分の本質的に中間点となるよう選択される。もし、一般的にあるように、整合ワードテーブルにおいて偶数のエントリがあれば、正確な中間点のロケーションアドレスはなく、従って次のより高いまたはより低いロケーションアドレスが選択され、すなわち、アレイの上部ハーフの最も低いアドレスが選択される。

30

#### 【0026】

このロケーションアドレス信号がメモリワードのアレイ101によって受信されたとき、選択された整合ワードおよび選択されたリンクワードがそれぞれ端子122および123における第1および第2の出力に生成される。選択された整合ワードは比較回路105において基準ワードと比較され、該比較回路105は比較の結果に対応する出力信号を生成する。該出力信号は比較の6つの結果の内の1つを指示し、すなわち第1に基準ワードおよび整合ワードが等しいこと、第2により高いロケーションアドレスにおいてサーチを継続すること、および第3により低いロケーションアドレスにおいてサーチを継続すること、および第4にもしVPCが生じればサーチを終了すること、および第5にもしVCCが発生すればサーチを終了すること、および第6に比較器105が前記「VPC有効」信号を肯定しこれは出力論理ピンに伝搬することがある。

40

#### 【0027】

2進サーチ論理回路104は比較回路105から出力信号を受ける端子125に第1の入力を有する。端子123における第2の入力はリンクワードテーブル103から選択され

50

た整合ワードに関連する選択されたリンクワードを受信する。もし前記基準および選択された整合ワードの内容が等しければ、2進サーチ論理回路104はその端子120におけるその出力に選択されたリンクワードを生成し、これはCAM100の出力に結合される。CAM100の出力は従って選択されたリンクワードを含み、多分フラグビットを加えて整合が首尾よく行われたことを指示する。限定的なものではないが、サーチの数、サーチの時間量、およびCAM内の首尾よいヒットの割合を含む他の情報をCAM100の出力に提供することもできる。

#### 【0028】

もし基準および選択整合ワードが整合しなければ、比較回路105からの出力信号は整合する整合ワードが、もしそれが整合ワードテーブル102に格納されておれば、前記中間点のロケーションアドレスより上に位置するかあるいは下に位置するかを示す。もし、例えば、比較回路105がサーチが前の中間点のロケーションアドレスより上の整合ワードテーブル102のハーフにおいて継続すべきことを示しておれば、2進サーチ論理回路104は今テストした領域のすぐ上の整合ワードテーブルの領域の中間点において新しいロケーションアドレスを提供する。該新しい中間点のロケーションアドレスに対応する新しい整合ワードは前記基準ワードと比較されかつサイクルそれ自体が反復する。

#### 【0029】

2進サーチにおいて、新しい整合ワードに対する基準ワードの各々の比較は整合を生じるかあるいは整合が検出できる可能なロケーションアドレスとしての整合ワードテーブル102の半分を除去する。引き続くサイクルが効果的に整合ワードテーブル102の残りの部分をそれが新しいテーブルであるかのように処理し、メモリワードのアレイ101の残りの部分の中間点に対応する新しいロケーションアドレスを送る。

#### 【0030】

2進サーチの各々のサイクルを完了するために必要な時間は一般にメモリワードのアレイ101を含むスタティックRAMコアの速度によって決定される。メモリワードのアレイ101が4,096のメモリエントリの深さである実施形態では、各サイクルを完了するのに必要な時間は10ナノセカンドである。4,096メモリワードを1つのメモリワードに低減するために12の引き続くバイセクション(bisections)が必要であり、メモリワードのアレイ101は多くても12のサイクルで2進サーチすることができる。従って完全なサーチは120ナノセカンドで完了する。16,384メモリワードの容量を有するメモリワードのアレイ101に対しては、2つの付加的な2進サーチサイクルを提供しなければならず、従ってサーチは140ナノセカンドで完了する。

#### 【0031】

2進サーチは基準ワードと整合する整合ワードが検出されることなく完了することもあり得る。その場合、CAM100の出力に何らのリンクワードも提供されず、かつ整合が検出されなかつたかあるいはサーチが完了したことを示すエラーフラグビットが一般に提供される。

#### 【0032】

いくつかの用途においては、新しいエントリを含めるためあるいはもはや有用でないエントリを削除するため整合ワードテーブル102およびリンクワードテーブル103を更新することが必要である。このため、2進サーチ論理回路104は新しいエントリを受けるために端子121に接続された第3の入力を有する。もしメモリワードのアレイ101が満杯でかつ存在するエントリが削除できなければ、新しいエントリはこれ以上処理されることはなく、かつ新しいエントリが受け入れられないことを示すためにエラービットが出力ワードにおいてセットされる。

#### 【0033】

もしメモリワードのアレイ101が空きのロケーションを有しておれば、新しいエントリが受け入れられかつ挿入される。新しいエントリはメモリワードのアレイ101の所定の順序を保つように挿入されなければならないことに注意を要する。1つの実施形態では、2進サーチ論理回路104は前記空きのロケーションで開始し、すなわちメモリワードの

10

20

30

40

50

アレイ 101 の最上部で開始し、かつ該新しいエントリおよびメモリワードのアレイ 101 の所定の順序を維持する必要性に照らして記憶されたメモリワードを調べる。前記新しいエントリはそうすることが前記所定の順序を維持する場合には前記空きのロケーションに挿入される。2進サーチ論理回路 104 は新しいエントリの適切なロケーションを決定する。

【0034】

これに対し、もし CAM100 が前記挿入プロセスの間にアイドルであれば、4,096 ワードの深さであるメモリワードのアレイ 101 は新しいエントリを正しいロケーションに挿入するために平均で約 20 マイクロセカンド、最悪の場合約 40 マイクロセカンドを必要とする。

10

【0035】

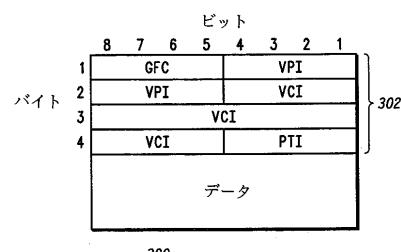

図 3 は、本発明に係わる非同期転送モデル (ATM) セル 300 を示す。ATM セルはヘッダ 302 を含み、該ヘッダ 302 はそれ自体で交換ネットワークのためのルーティング情報を含む。ヘッダ 302 の情報は端子 121 を介して図 1 の比較器 105 に入力される。前記交換識別子はデータパケットをヘッダ 302 に含まれる VCI および VPI に基づき導く。バイト 1 は包括的なフロー制御 (generic flow control) (以後 "GFC" と称する) のための 4 ビットおよびユーザネットワークインターフェース (以後 "UNI" と称する) プロトコルにおける VPI のための 4 ビットを含む。しかしながら、ネットワーク・ネットワークインターフェース (以後 "NNI" と称する) プロトコルにおいては、バイト 1 は VPI のために 8 ビットを含む。バイト 2 は VPI のために 4 ビットを含み VCI のために 4 ビットを含む。バイト 3 は VCI のために 8 ビットを含む。バイト 4 は、UNI および NNI プロトコルの双方に対して、VCI のために 4 ビットを含みかつペイロードタイプ識別子 (payload type identifier) (以後 "PTI" と称する) のために 4 ビットを含む。残りのバイトはデータパケットを含む。データパケット (以後「データ」と称する) はコンピュータコード、電話通信、または任意の導かれるべき情報から構成できる。

20

【0036】

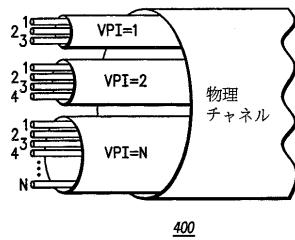

図 4 は、本発明に係わる VCI および VPI を含む物理チャネル 400 を示す。物理チャネル 400 は光ケーブル、ツイストケーブル、および電話ケーブルのような、物理的なデータ伝送構造を表す。物理チャネル 400 は VPC および VCC を含み、この場合 VPC および VCC は個々の VPI および VCI を含む。VPC は、すべて同じ VPI を備えかつすべて同じ方式でスイッチングされる、複数の回路のトランクとして概念化しあるいは概念的に説明することができる。1つのVCC は異なる VPI 内の異なる VCI に導く VPI 内の 1 つの特定の VCI である。VCC および VPC のためのルーティングは図 5 において後に説明する。この実施形態では、4,096 までの VPI が可能でありかつ VPI ごとに 65,536 までの VCI が可能である。

30

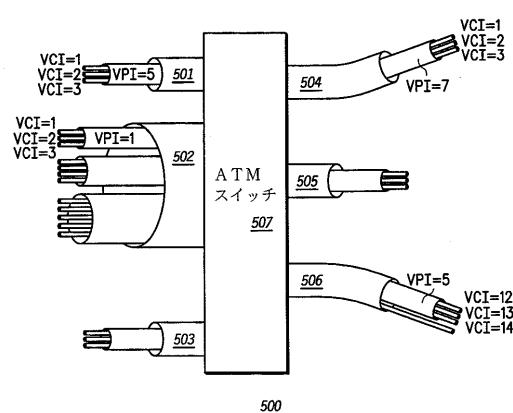

【0037】

図 5 は、本発明に係わる VCC および VPC を含む ATM スイッチ 507 を示す。ATM スイッチ 507 は複数の入力バスを受け入れかつ種々のデータを備えた複数の出力バスを発生する。ATM スイッチ 507 は入力および出力バス内のデータを処理しあつバスのルーティングは瞬時に (急速に: on the fly) 行われる。ATM スイッチ 507 は複数の物理チャネル 400 を備えた交換ネットワークを示している。1つの例では、ATM スイッチ 507 は物理チャネル 501、物理チャネル 502、および物理チャネル 503 を受け入れる。ATM スイッチ 507 は個々のヘッダ 302 に基づき入力セル、VCI および VPI、を物理チャネル 504、物理チャネル 505、および物理チャネル 506 に導く。

40

【0038】

CAM100 はヘッダ 302 における VPI および VCI を CAM100 における VPI および VCI エントリと比較する。もし VPI および VPC を識別する CAM100 内の特別の VCI 値に対する整合が生じれば VPC が存在する。整合データは ATM スイッチ

50

507にデータをどこに導くかおよびヘッダ302におけるデータのすべてまたは一部をどのように変換するかを通知する。

【0039】

1つの例では、物理チャネル501は5のVPI値を含み、1のVCI値、2のVCI値、および3のVCI値を備えている。CAM100は整合ワードテーブル102をサーチしつつVPCを識別する特別のVCI値と上のVPIおよびVCIに対する整合が生じる。整合ワードに関連するリンクワードは7のVPIに対する変換値を含む。ATMスイッチ507は物理チャネル501を物理チャネル504に導きかつVPI値を5から7に変換するが、VCIは1, 2および3の値を保持する。従って、VPCに対しては、VPI値は変換されるがVCI値は同じ値に留まっている。

10

【0040】

他の例では、物理チャネル502は1のVPI値を含み、1のVCI値、2のVCI値、および3のVCI値を、ヘッダ302に備えている。CAM100は整合ワードテーブル102をサーチしつつVPIおよびVCI値の双方に対して整合が生じ、VCCを生じる。整合ワードに関連するリンクワードは5のVPIに対する変換値を含みかつ1, 2および3のVCI値に対してそれぞれ12, 13および14のVCIに対する変換値を含む。ATMスイッチ507は物理チャネル502を物理チャネル506に導きかつVPI値を1から5に変換し、かつVCI値を1, 2および3から12, 13および14にそれぞれ変換する。従って、VCCに対しては、VPI値およびVCI値の双方が変換される。

20

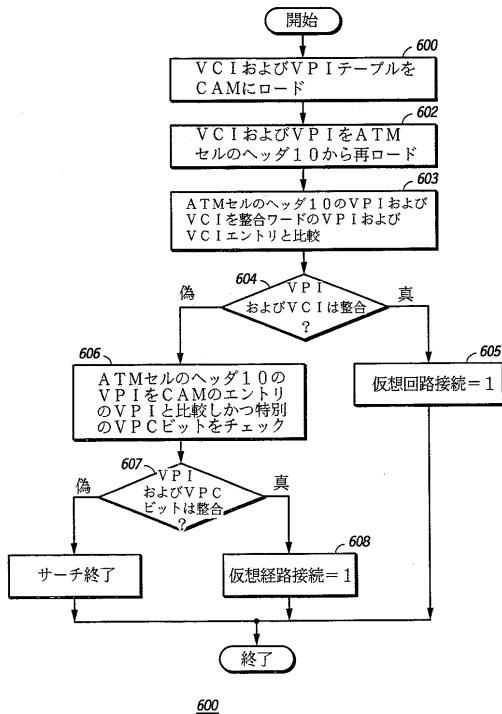

【0041】

図6は、フローチャート形式で、ヘッダ302のサーチの知られた方法を示す。ステップ601において、所定の組のVPIおよびVCI値がヘッダ302におけるデータを導くためにCAM100にロードされる。最初のサーチはVCIおよびVPI値をヘッダ302から読み出すことによって始まる、ステップ602。該最初のサーチはヘッダ302におけるVPIおよびVCI値を整合ワードテーブル102におけるVPIおよびVCI値と比較することによりVCCに対して行われる、ステップ603。ステップ604において、VPIおよびVCI値が整合するか否かの判定が行われる。もし該判定が真（整合）であれば、ステップ605においてVCCは有効とされる。該VPIおよびVCI値は関連するリンクワードにおいて規定される値に変換される。しかしながら、前記判定が偽（整合なし）であれば、ステップ606において、ヘッダ302におけるVPI値を整合ワードテーブル102におけるVPI値と比較しつつ整合ワードテーブル102における特別のVPCビットをチェックする。ステップ607において、VPI値が整合するか否かおよび整合ワードテーブル102に特別のVPCビットが存在するかの判定が行われる。もし該判定が真であれば、VPCは有効である、ステップ608。VPI値は関連するリンクワードにおいて規定された値に変換される。しかしながら、もし前記判定が偽（整合なし）であれば、サーチは整合なしに終了する。当業者は容易にこの知られたアルゴリズムは2つの別個のCAMルックアップを必要とし、1つのCAMが2回使用されるあるいは2つのCAMが各々1度使用されるかを理解するであろう。いずれの場合も、時間またはシリコンが過剰に使用される。

30

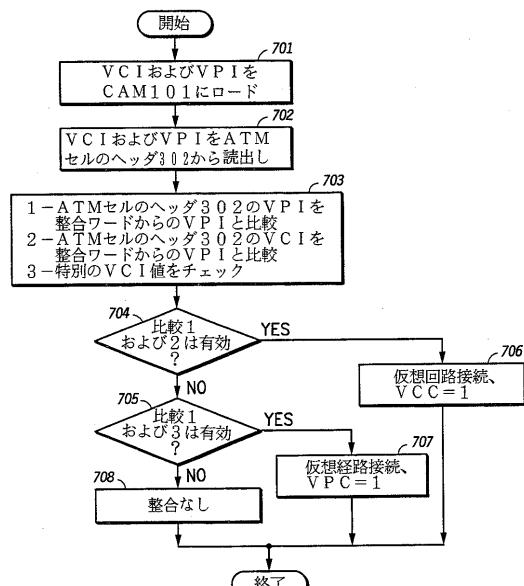

【0042】

図7は、フローチャート形式で、本発明に係わるヘッダ302のサーチを示す。ステップ701において、ヘッダ302におけるデータを導くために所定の組のVPIおよびVCI値がCAM100にロードされる。示された実施形態では、VCIおよびVPI値は、図1において前に述べたように、増大する数でソートされかつ記憶される。しかしながら、開示された発明の両方の面（aspects）はお互いに独立に実施することができあるいは組合せることができる。両方のサーチは、ステップ702において、ヘッダ302からVCIおよびVPI値を読み出すこと始まる。ステップ703は3つの比較からなり、第1の比較はヘッダ302からのVPIを整合ワードテーブル102からのVPIと比較することからなり、第2の比較はヘッダ302からのVCIを整合ワードテーブル102からのVCIと比較することからなり、第3の比較は整合ワードテーブル102から

40

50

のVCIを論理“1”の特別のVCI値に対して比較することからなる。

【0043】

引き続くステップ、704および705、は直列的に発生するように説明するが、同時に行われる。ステップ704においては、前記第1の比較（ヘッダ302からのVPIが整合ワードからのVPIと等しい）および前記第2の比較（ヘッダ302からのVCIが整合ワードからのVCIと等しい）が真（整合）であるか否かが判断される。もし該判断が真（整合）であれば、ステップ706においてVCCは有効でありかつVPIおよびVCI値は関連するリンクワードにおける値に変換される。しかしながら、もし前記判断が偽であれば、VCCサーチは整合なしに終了する。VPCサーチはヘッダ302のVPI値をCAM100における整合ワードテーブル102のエントリのVPI値と比較しつつ整合ワードテーブル102のエントリにおける特別のVCI値に対してチェックを行う。ステップ705において、VPI値が整合しつつ特別のVCI値が整合ワードテーブル102のエントリに存在するかが判定される。もしこの判定が真（整合）であれば、ステップ707においてVPCは有効でありかつVPI値は関連するリンクワードにおける値に変換される。しかしながら、もし前記判断が偽であれば、VPCサーチは整合なしに終了する。もし前記VPCが有効であれば、前記「VPC有効」信号は論理ピンを肯定する。

【0044】

VPCを識別する前記特別のVCI値は整合ワードテーブル102の初期ロードにおいてセットされかつ任意的なものである。この実施形態では、前記特別のVCI値は16の論理“1”を含む。

【0045】

有効なVPCに対して論理ピンを「VPC有効」信号により肯定することは試験を簡単にしつつエンドユーザによる動作または運用を簡単にする。前記論理ピンは装置の状態を識別することによりCAM100の試験を簡単にする。装置を適切にテストするためにVPCまたはVCCが有効であるか否かを判定する必要性が存在する。他の利点はエンドユーザがVPCが有効であるか否かを前記ピンにおける論理ハイによって認識することである。システム設計者のような、エンドユーザは前記論理ピンを使用して有効なVPCに基づき他のシステム機能をイネーブルまたはディスエーブルする。例えば、もしシステム設計者が有効なVPCに基づき他のATMスイッチに導く必要があれば、前記論理ピンが制御回路のためのゲート信号として使用される。前記論理ピンはシステム設計を簡単にしつつ柔軟性を増大する。

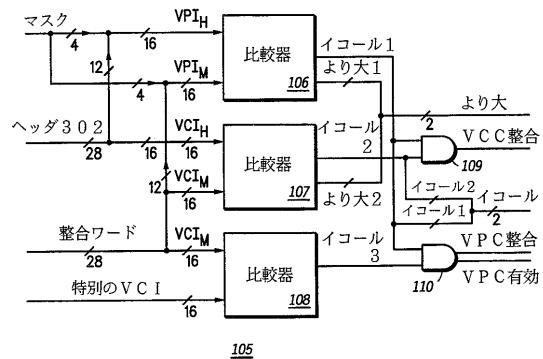

【0046】

図8は、比較器105のブロック図を示す。比較器105は3つの比較要素、すなわち比較器106、比較器107、および比較器108、そしてANDゲート109およびANDゲート110から構成されている。比較器105は端子121に基準ワードをそして端子122に整合ワードを受信する。この実施形態では、基準ワードはヘッダ302である。比較器106は1つの入力に16ビットのVPI、すなわちヘッダ302からの12ビット（バイト1およびバイト2のビット5:8）および4ビット、を受ける。4ビットはマスクにより最上位ビットとして加えられ、かつユーザ定義される。前記4ビットを加えることは図10において後に説明する。4ビットは各々の比較要素が同じ16ビットの比較器の設計で実施できるようにする。比較器106は他の入力に16ビットのVPI、すなわち整合ワードからの12ビットおよび4ビット、を受ける。4ビットはマスクにより最上位ビットとして加えられ、かつユーザ定義される。比較器107は1つの入力にヘッダ302からの16ビットのVCIを受ける。比較器107は他の入力に整合ワードからの16ビットのVCIを受ける。比較器108は一方の入力に16ビットのVCIを整合ワードから受ける。比較器108は他の入力に特別の16ビットのVCI値を受ける。

【0047】

VPI<sub>H</sub>はヘッダ302からのVPIを示し、VPI<sub>M</sub>は整合ワードからのVPIを示し、VCI<sub>H</sub>はヘッダ302からのVCIを示し、VCI<sub>M</sub>は整合ワードからのVCIを示す。各々の比較要素は2つの16ビット入力が等しいか否かをビットごとの比較で判定す

10

20

30

40

50

る。比較器 106 の出力はもし 2 つの VPI 入力が等しければ「イコール 1 ( EQUAL 1 )」を発生する。比較器 107 はもし 2 つの VCI 入力が等しければ「イコール 2 ( EQUAL 2 )」信号を発生する。比較器 108 の出力はもし 2 つの VCI 入力が等しければ「イコール 3 ( EQUAL 3 )」信号を発生する。

#### 【 0048 】

AND ゲート 109 は 1 つの入力に前記「イコール 1 」信号を受けかつ他の入力に前記「イコール 2 」信号を受信する。AND ゲート 110 は 1 つの入力に前記「イコール 1 」信号を受けかつ他の入力に前記「イコール 3 」信号を受ける。AND ゲート 109 の出力は「VCC 整合」信号を発生する。AND ゲート 110 の出力は前記「VPC 整合」信号および前記「VPC 有効」信号を発生する。

10

#### 【 0049 】

比較要素、比較器 106 、比較器 107 および比較器 108 、は VPC または VCC が存在するか否かを判定する。ヘッダ 302 からの VPI および VCI 情報および整合ワードテーブル 102 からの整合ワードを比較することにより、各々の比較要素は入力が等しいか否かを判定する。もしヘッダ 302 からの VPI および整合ワードがビットごとのベースで同じであれば「イコール 1 」信号は論理“ 1 ”である。もしヘッダ 302 からの VCI および整合ワードがビットごとのベースで同じであれば「イコール 2 」は論理“ 1 ”である。もし整合ワードからの VCI および前記特別の VCI がビットごとのベースで同じであれば「イコール 3 」は論理“ 1 ”である。AND ゲート 109 の出力、「VCC 整合」信号、はもし VCC が存在すれば論理“ 1 ”である。AND ゲート 110 の出力、「VPC 整合」信号および「VPC 有効」信号、は VPC が存在すれば論理“ 1 ”である。比較器 108 は比較器 106 および比較器 107 がそれぞれ「イコール 1 」および「イコール 2 」を発生するよりも早く「イコール 3 」を発生する。「イコール ( EQUAL )」信号は 2 ビットを含み、1 ビットは「イコール 1 」を表しかつ 1 ビットは「イコール 2 」を表す。「イコール 1 」および「イコール 2 」信号の発生については図 10 においてより詳細に説明する。前記特別の VCI 値は 16 の論理“ 1 ”を含み、従って比較器 108 は整合ワードからの VCI を論理“ 1 ”につきチェックする。比較器 106 および比較器 107 は論理“ 1 ”および論理“ 0 ”に対する両方の入力を比較する必要があり、比較器 108 は整合ワードからの VCI を論理“ 1 ”についてチェックするのみであり、従って、比較器 106 および比較器 107 よりも高速で比較を行う。

20

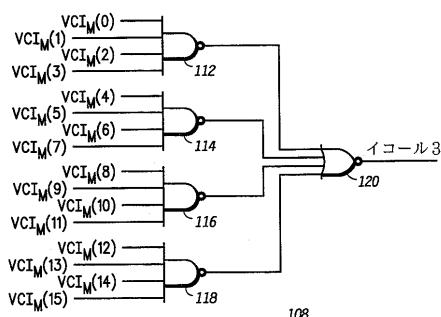

#### 【 0050 】

図 9 は、比較器 108 の回路図を示す。比較器 108 は整合ワードから 16 ビットの VCI を受けかつ前記特別の VCI 値とビットごとの比較を行う。この実施形態では、前記特別の VCI 値はオール論理“ 1 ”を含む。従って、比較器 108 は整合ワードからの 16 ビットの VCI を論理“ 1 ”につきチェックする。NAND ゲート 112 は整合ワードの VCI から 4 ビット、ビット 0, 1, 2 および 3 、を受信する。NAND ゲート 114 は整合ワードの VCI から 4 ビット、ビット 4, 5, 6 および 7 、を受信する。NAND ゲート 116 は整合ワードの VCI から 4 ビット、ビット 8, 9, 10 および 11 、を受信する。NAND ゲート 118 は整合ワードの VCI から 4 ビット、ビット 12, 13, 14 および 15 、を受信する。NOR ゲート 120 は NAND ゲート 112 の出力、NAND ゲート 114 の出力、NAND ゲート 116 の出力、および NAND ゲート 118 の出力を受ける。NOR ゲート 120 の出力は前記「イコール 3 」信号を発生する。

30

#### 【 0051 】

比較器 108 の動作は特別の VCI 値に対して論理“ 1 ”を使用することにより論理を最小にすることに基づいている。比較を単純化することにより、比較器 108 は整合ワードからの VCI を論理“ 1 ”についてチェックする。「イコール 3 」信号はもし整合ワードからの VCI が論理“ 1 ”から構成されれば論理“ 1 ”である。他の実施形態では、比較器 108 は異なるビットパターンにつきテストを行うことができ、あるいはプログラム可能とすることができます。そのような場合、比較器 108 は、図 10 において以下に説明するように、比較器 106 および比較器 107 と同様に構成できる。

40

50

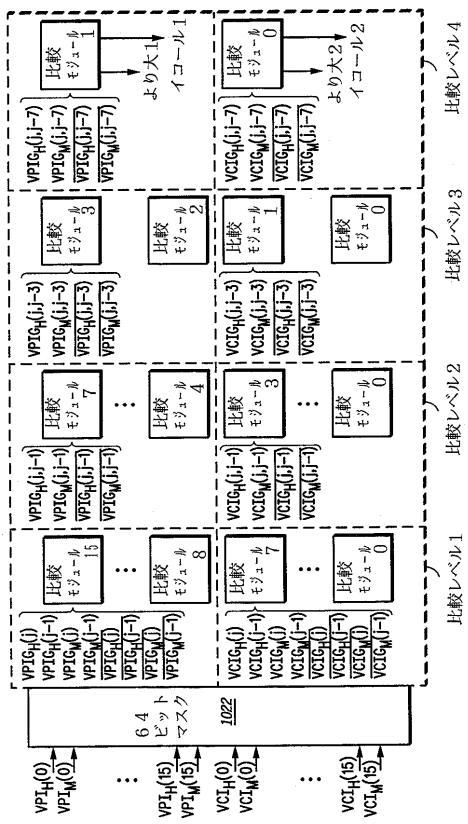

## 【0052】

図10は、比較器106および比較器107の詳細なブロック図を示す。このブロック図はマスク可能なXORブロック1022および各々1つまたはそれ以上の比較モジュール<sub>a</sub>,<sub>b</sub>を備えた一連の比較レベルブロックから構成され、この場合<sub>a</sub>および<sub>b</sub>は整数の指數またはインデクスであり、<sub>a</sub>は1から4におよび、<sub>b</sub>は0から15におよぶ。比較レベル<sub>1</sub>は16の比較モジュール<sub>1</sub>,<sub>j</sub>からなり、この場合<sub>j</sub>は0から15におよぶ整数指數である。比較レベル<sub>2</sub>は8つの比較モジュール<sub>2</sub>,<sub>k</sub>からなり、この場合<sub>k</sub>は0から7におよぶ整数指數である。比較レベル<sub>3</sub>は4つの比較モジュール<sub>3</sub>,<sub>m</sub>からなり、この場合<sub>m</sub>は0から3におよぶ整数指數である。比較レベル<sub>4</sub>は2つの比較モジュール<sub>4</sub>,<sub>n</sub>からなり、この場合<sub>n</sub>は0から1におよぶ整数指數である。前記マスク可能XORブロック1022はヘッダ302から16ビットのVPIを、整合ワードから16ビットのBPIを、ヘッダ302から16ビットのVCIを、そして整合ワードから16ビットのVCIを、そしてマスクバスを受ける。

## 【0053】

マスク可能XORブロック1022はVPI<sub>H</sub>のすべてのビットをVPI<sub>M</sub>のすべてのビットと、一度に2ビットずつ、比較する。また、マスク可能XORブロック1022は、一度に2ビットずつ、VCI<sub>H</sub>のすべてのビットをVCI<sub>M</sub>のすべてのビットと比較する。マスク可能XORブロックはVPI<sub>H</sub>およびVPI<sub>M</sub>の2つの最上位ビットを比較しあつその結果を比較モジュール<sub>1</sub>,<sub>15</sub>に出力する。マスク可能XORブロックはVPI<sub>H</sub>およびVPI<sub>M</sub>の次の2つの最上位ビットを比較しあつその結果を比較モジュール<sub>1</sub>,<sub>1</sub>4に出力する。比較モジュール<sub>1</sub>,<sub>8</sub>はVPI<sub>H</sub>およびVPI<sub>M</sub>の2つの最下位ビットの比較結果を受ける。同様の方法で、マスク可能XORブロックはVCI<sub>H</sub>およびVCI<sub>M</sub>の2つの最上位ビットを比較しあつその結果を比較モジュール<sub>1</sub>,<sub>7</sub>へ出力する。比較モジュール<sub>1</sub>,<sub>0</sub>はVCI<sub>H</sub>およびVCI<sub>M</sub>の2つの最下位ビットの比較結果を受信する。マスク可能XORブロック1022によって8つの信号が発生されビットごとのベースで比較された4つのビットの結果およびその結果の補数を表しあつ比較レベル<sub>1</sub>における比較モジュールに提供される。

## 【0054】

比較レベル<sub>1</sub>における比較モジュール<sub>1</sub>,<sub>j</sub>(8,j,15に対して)は8つの入力、VPI<sub>G</sub><sub>H</sub>(j),VPI<sub>G</sub><sub>H</sub>(j-1),VPI<sub>G</sub><sub>M</sub>(j),VPI<sub>G</sub><sub>M</sub>(j-1)および4つの前の信号の補数をマスク可能XORブロック1022から受ける。比較レベル<sub>1</sub>における比較モジュール<sub>1</sub>,<sub>j</sub>(0,j,7に対して)は8つの入力、VCI<sub>G</sub><sub>H</sub>(j),VCI<sub>G</sub><sub>H</sub>(j-1),VCI<sub>G</sub><sub>M</sub>(j),VCI<sub>G</sub><sub>M</sub>(j-1)および前記4つの信号の補数をマスク可能XORブロック1022から受ける。各々の信号はVPI<sub>H</sub>およびVPI<sub>M</sub>、およびVCI<sub>H</sub>およびVCI<sub>M</sub>の間の<sub>j</sub>または<sub>j</sub>-1に対応する比較を表す。VPI<sub>G</sub><sub>H</sub>(j)はVPI<sub>H</sub>の<sub>j</sub>番目のビットがVPI<sub>M</sub>の<sub>j</sub>番目のビットより大きいか否かを表す。

## 【0055】

比較レベル<sub>1</sub>における各比較モジュールは4つの出力を表す。比較モジュール<sub>1</sub>,<sub>j</sub>(8,j,15に対し)はVPI<sub>G</sub><sub>H</sub>(j,j-1),VPI<sub>G</sub><sub>M</sub>(j,j-1)、および前の2つの信号の各々の補数を発生しあつそれらを入力として比較レベル<sub>2</sub>の比較モジュールに供給する。比較モジュール<sub>1</sub>,<sub>j</sub>(0,j,7)はVCI<sub>G</sub><sub>H</sub>(j,j-1),VCI<sub>M</sub>(j,j-1)、および前の2つの信号の各々の補数を発生しあつそれらを入力として比較レベル<sub>2</sub>の比較モジュールに供給する。

## 【0056】

比較レベル<sub>2</sub>の各比較モジュールは比較レベル<sub>1</sub>における比較モジュール<sub>1</sub>,<sub>j</sub>の内の2つから8つの出力を受ける。比較レベル<sub>2</sub>の各比較モジュールは4つの出力を発生する。比較モジュール<sub>2</sub>,<sub>k</sub>(4,k,7に対して)はVPI<sub>G</sub><sub>H</sub>(j,j-3),VPI<sub>G</sub><sub>M</sub>(j,j-3)、および前の2つの信号の各々の補数を発生しあつそれらを入力として比較レベル<sub>3</sub>の比較モジュールに供給する。比較モジュール<sub>2</sub>,<sub>k</sub>(0,k,3に対して)は

$VCI_{GH}(j, j-3)$ ,  $VCI_M(j, j-3)$ 、および前の2つの信号の各々の補数を発生しつつそれらを入力として比較レベル<sub>3</sub>の比較モジュールに供給する。

#### 【0057】

比較モジュール<sub>3, m</sub>(2 m 3に対して)は $VPI_{GH}(j, j-7)$ ,  $VPI_{GM}(j, j-7)$ 、および前の2つの信号の各々の補数を発生しつつそれらを入力として比較レベル<sub>4</sub>の比較モジュールに供給する。比較モジュール<sub>3, m</sub>(0 m 1に対して)は $VCI_{GH}(j, j-7)$ ,  $VCI_M(j, j-7)$ 、および前の2つの信号の各々の補数を発生しつつそれらを入力として比較レベル<sub>4</sub>の比較モジュールに供給する。比較モジュール<sub>4, 1</sub>は $VPI_{GH}(j, j-7)$ ,  $VPI_{GM}(j, j-7)$ 、および前の2つの信号の各々の補数を受ける。比較モジュール<sub>4, 1</sub>は「より大1(Greater 1)」および「イコール1(Equal 1)」信号を発生する。比較モジュール<sub>4, 0</sub>は $VCI_{GH}(j, j-7)$ ,  $VCI_M(j, j-7)$ 、および前の2つの信号の各々の補数を受信する。比較モジュール<sub>4, 0</sub>は「より大2(Greater 2)」および「イコール2(Equal 2)」信号を発生する。10

#### 【0058】

図10の比較器は比較器106および比較器107の機能を達成する。図10の比較器は入力、 $VPI_H$ ,  $VPI_M$ ,  $VCI_H$ および $VCI_M$ の並列比較によるモジュール手法を使用する。このモジュール手法(modular approach)の利点は整合する負荷との並列比較を含む。整合する負荷は並列比較を行う安定した、一貫した設計を提供する。他の利点は64ビットのマスク可能XORはユーザに64ビットの内の任意のものを無視しあるいは「マスキング(masking)」除去する柔軟性を与える。この実施形態では、それぞれのビットが比較され、いずれのビットもマスク除去されない。20

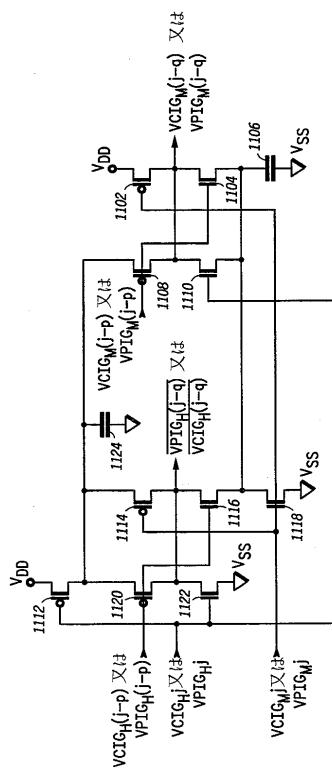

#### 【0059】

図11は、図10に示された比較モジュールの回路図を示す。該回路図は図10における任意の比較モジュールを表す。比較モジュールは $VPI$ または $VCI$ を比較するために使用され、従って回路図は $VPI$ または $VCI$ の双方に対する信号を示す。この回路図への入力は( $j-p$ )ビットを備えて示されており、この場合 $p$ は0, 1, 3または7を表す整数である。図10から思い起こすと、比較レベル<sub>1</sub>および比較レベル<sub>2</sub>における比較モジュールへの入力は( $j-1$ )であり、比較レベル<sub>3</sub>の比較モジュールへの入力は( $j-3$ )であり、かつ比較レベル<sub>4</sub>における比較モジュールへの入力は( $j-7$ )である。従つて、( $j-p$ )は任意の比較レベルにおける比較モジュールへの任意の入力を表している。同様の方法で、前記回路図の出力は( $j-q$ )であり、この場合 $q$ は整数1, 3, 7でありかつ $q$ は常に $p$ より大きい。比較レベル<sub>4</sub>における比較モジュールにおいては、出力は「より大1」、「より大2」、「イコール1」および「イコール2」である。30

#### 【0060】

出力、 $VCI_{GM}(j-q)$ および $VPI_{GM}(j-q)$ は $p$ 型トランジスタ1102のドレインにかつ $n$ 型トランジスタ1104のソースに結合され、かつ $p$ 型トランジスタ1108のドレインにおよび $n$ 型トランジスタ1110のソースに結合されている。トランジスタ1102のソースは電源 $Vdd$ に結合されている。トランジスタ1108のソースは容量1124の1つの端子に、 $p$ 型トランジスタ1114のソースおよび $p$ 型トランジスタ1120のソースに、そしてトランジスタ1112のドレインに接続されている。トランジスタ1112のソースは電源 $Vdd$ に接続されている。容量1124の他の端子はグランド $Vss$ に結合されている。トランジスタ1104のドレインは容量1106の1つの端子、トランジスタ1110のドレインおよび $n$ 型トランジスタ1116のドレインに、そして $n$ 型トランジスタ1118のソースに結合されている。容量1106の他の端子はグランド $Vss$ に結合されている。トランジスタ1118のドレインはグランド $Vss$ に結合されている。トランジスタ1104のゲートおよびトランジスタ1108のゲートは $VCI_{GM}(j)$ または $VPI_{GM}(j)$ の入力に結合されている。トランジスタ1102のゲートはトランジスタ1114のゲートにかつ $VCI_{GM}(j-p)$ または $VPI_{GM}(j-p)$ の補数の入力に結合されている。トランジスタ1110のゲートは $n$ 型40

トランジスタ 1122 のゲート、トランジスタ 1112 のゲート、および V C I G<sub>M</sub> ( j ) または V P I G<sub>M</sub> ( j ) の入力に結合されている。p 型トランジスタ 1120 のゲートは n 型トランジスタ 1116 のゲートにかつ入力、V C I G<sub>M</sub> ( j - p ) または V P I G<sub>M</sub> ( j - p ) に結合されている。出力、V C I G<sub>M</sub> ( j - q ) または V P I G<sub>M</sub> ( j - q ) 、はトランジスタ 1120 のドレインにかつトランジスタ 1116 のソースに結合され、そしてトランジスタ 1114 のドレインにおよびトランジスタ 1122 のソースに結合されている。トランジスタ 1122 のドレインはグランド V<sub>SS</sub> に結合されている。

#### 【 0061 】

##### 【発明の効果】

以上から、内容アドレス可能メモリ回路および交換識別子の同時的サーチを実施するための回路および方法が提供されたことが理解されるべきである。前記内容アドレス可能メモリ回路は現存する半導体プロセス技術によって実施することができかつ半導体ダイ上に容易に集積される。交換識別子の同時的サーチは 1 つの C A M のみを使用しかつ同時サーチを使用して V P C または V C C を決定する。

10

#### 【 0062 】

本発明が特定の実施形態に関して説明されたが、当業者にはさらに他の修正および改善をなすことができる。例えば、A T M セルヘッダ 302 の識別情報の量が増大するに応じてより多くの並列サーチが必要になる。例えば、将来のより複雑なネットワークに対するより大きな帯域幅により、より多くの交換識別子が並列サーチを必要とする。従って、本発明はより多くの並列サーチを含むよう拡張できる。従って、本発明は添付の特許請求の範囲に規定された発明の精神および範囲から離れることのないすべてのそのような変更を含むことが理解されるべきである。

20

##### 【図面の簡単な説明】

【図 1】本発明に従って構成された内容アドレス可能メモリ回路を示すブロック図である。

【図 2】本発明に係わる内容アドレス可能メモリ回路を実施するための方法を示す流れ図である。

【図 3】本発明に係わる非同期転送モード ( A T M ) セルのヘッダを示す説明図である。

【図 4】本発明に係わる仮想回路識別子および仮想経路識別子を含む物理チャネルを示す説明図である。

30

【図 5】本発明に係わる仮想回路接続および仮想経路接続を含む A T M スイッチを示す説明図である。

【図 6】A T M セルのヘッダサーチの知られた方法を示す流れ図である。

【図 7】本発明に係わる A T M セルのヘッダのサーチを示す流れ図である。

【図 8】本発明に係わる比較器を示すブロック図である。

【図 9】図 8 に示される比較器の詳細を示す回路図である。

【図 10】図 8 に示される比較器の詳細なブロック図である。

【図 11】図 10 に示される 2 ビット比較器を示す回路図である。

##### 【符号の説明】

100 内容アドレス可能メモリ ( C A M ) 回路

40

101 メモリワードのアレイ

102 整合ワードテーブル

103 リンクワードテーブル

104 2 進サーチ論理回路

105 比較器

106 a エントリキュー

106, 107, 108 比較器

109, 110 A N D ゲート

112, 114, 116, 118 N A N D ゲート

120 N O R ゲート

50

## 1 0 2 2 マスク可能 X O R ブロック

【 四 1 】

【図2】

〔 3 〕

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

---

フロントページの続き

- (72)発明者 チャーリー・マイケル・パークス

アメリカ合衆国テキサス州78727、オースチン、オーク・クリーク・ドライブ 4105

- (72)発明者 マーク・フランクリン

アメリカ合衆国テキサス州78759、オースチン、オーク・ノール・ドライブ 11305

- (72)発明者 ケニス・ウェイド・ジョーンズ

アメリカ合衆国テキサス州78749、オースチン、ジョン・チサム・レーン 6308

合議体

審判長 石井 研一

審判官 萩原 義則

審判官 松元 伸次

(56)参考文献 国際公開第95/23380 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

H04L12/56