(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-317685

(P2004-317685A)

(43) 公開日 平成16年11月11日(2004.11.11)

(51) Int.CI.<sup>7</sup>**G02F 1/1368****G02F 1/1335****G02F 1/1343****H01L 29/786**

F 1

G02F 1/1368

G02F 1/1335 505

G02F 1/1343

H01L 29/78 619A

H01L 29/78 616V

テーマコード(参考)

2H091

2H092

5F110

審査請求 未請求 請求項の数 19 O L (全 44 頁)

(21) 出願番号

特願2003-109730(P2003-109730)

(22) 出願日

平成15年4月15日(2003.4.15)

(71) 出願人 303016443

クオンタ・ディスプレイ・ジャパン株式会社

大阪府大阪市中央区内平野町3丁目2番1

2号 HPCビル内

(71) 出願人 501046327

廣輝電子股▲ふん▼有限公司

台灣桃園縣龜山鄉華亞2路189号

(74) 上記1名の代理人 303016443

クオンタ・ディスプレイ・ジャパン株式会社

(72) 発明者 川崎 清弘

大阪府枚方市楠葉並木1丁目8番3号

Fターム(参考) 2H091 FA02Y GA02 GA03 GA13 LA12

LA30

最終頁に続く

(54) 【発明の名称】 液晶表示装置とその製造方法

## (57) 【要約】

【課題】従来の製造工程数を削減した製造方法では製造裕度(マージン)が小さく歩留が低下する。

【解決手段】半導体層の島化工程とエッチストップ層の形成工程をハーフトーン露光技術の導入により合理化する新規技術と、公知技術であるソース・ドレイン配線の陽極酸化工程にハーフトーン露光技術を導入することで電極端子の保護層形成工程を合理化する新規技術と、公知技術である絵素電極と走査線とを同時に形成する合理化技術との技術の組合せによるTN型液晶表示装置とIPS型液晶表示装置の4枚マスク・プロセス、3枚マスク・プロセス案を構築する。

【選択図】 図2

**【特許請求の範囲】****【請求項 1】**

チャネル上に保護絶縁層を有し、ソース・ドレイン配線材とは異なった導電性材質よりなるソース配線の電気的接続領域の一部を含んで形成されたソース・ドレイン配線上に感光性有機絶縁層が形成されていることを特徴とするボトムゲート型の絶縁ゲート型トランジスタ。

**【請求項 2】**

チャネル上に保護絶縁層を有し、ソース配線の電気的接続領域を除いてソース配線上にのみ感光性有機絶縁層が形成されていることを特徴とするボトムゲート型の絶縁ゲート型トランジスタ。10

**【請求項 3】**

チャネル上に保護絶縁層を有し、ソース・ドレイン配線が陽極酸化可能な金属層で構成されるとともにソース配線の電気的接続領域を除いてソース・ドレイン配線上に陽極酸化層が形成されていることを特徴とするボトムゲート型の絶縁ゲート型トランジスタ。

**【請求項 4】**

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、ドレイン配線に接続された絵素電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、少なくとも20

第1の透明性絶縁基板の一主面上に1層以上の金属層よりなる走査線が形成され、

ゲート電極上に1層以上のゲート絶縁層を介して不純物を含まない第1の半導体層が島状に形成され、20

ゲート電極上の第1の半導体層上に前記ゲート電極よりも幅細く保護絶縁層が形成され、

前記保護絶縁層の一部上と第1の半導体層上とに不純物を含む第2の半導体層と陽極酸化可能な金属層との積層よりなるソース(信号線)・ドレイン配線が形成され、30

前記ドレイン配線の一部上とゲート絶縁層上に透明導電性の絵素電極と画像表示部外の領域で信号線上に透明導電性の電極端子とが形成され、30

前記ドレイン配線の絵素電極と重なった領域と信号線の電極端子領域を除いてソース・ドレイン配線の表面に陽極酸化層が形成されていることを特徴とする液晶表示装置。30

**【請求項 5】**

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、ドレイン配線に接続された絵素電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、少なくとも40

第1の透明性絶縁基板の一主面上に透明導電層と第1の金属層との積層よりなる走査線と透明導電性の絵素電極と同じく信号線の電極端子とが形成され、40

ゲート電極上にプラズマ保護層とゲート絶縁層を介して不純物を含まない第1の半導体層が島状に形成され、40

ゲート電極上の第1の半導体層上に前記ゲート電極よりも幅細く保護絶縁層が形成され、

前記絵素電極上のプラズマ保護層とゲート絶縁層に開口部が形成され、40

前記保護絶縁層の一部上と第1の半導体層上と信号線の電極端子の一部上に不純物を含む

第2の半導体層と1層以上の第2の金属層との積層よりなるソース(信号線)配線と、前記保護絶縁層の一部上と第1の半導体層上と前記開口部内の絵素電極の一部上と同じく

ドレイン配線とが形成され、40

前記ソース・ドレイン配線上に感光性有機絶縁層が形成されていることを特徴とする液晶

表示装置。

**【請求項 6】**

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲ

50

ート電極も兼ねる走査線とソース配線も兼ねる信号線と、ドレイン配線に接続された絵素電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、少なくとも

第1の透明性絶縁基板の一主面上に透明導電層と第1の金属層との積層よりなる走査線と透明導電性の絵素電極とが形成され、

ゲート電極上にプラズマ保護層とゲート絶縁層を介して不純物を含まない第1の半導体層が島状に形成され、

ゲート電極上の第1の半導体層上に前記ゲート電極よりも幅細く保護絶縁層が形成され、前記絵素電極上のプラズマ保護層とゲート絶縁層に開口部が形成され、

前記保護絶縁層の一部上と第1の半導体層上とに不純物を含む第2の半導体層と1層以上の第2の金属層との積層よりなるソース(信号線)配線と、前記保護絶縁層の一部上と第1の半導体層上と前記開口部内の絵素電極の一部上とに同じくドレイン配線とが形成され、

信号線の電極端子を除いて信号線上に感光性有機絶縁層が形成されていることを特徴とする液晶表示装置。

#### 【請求項7】

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、ドレイン配線に接続された絵素電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、少なくとも

第1の透明性絶縁基板の一主面上に透明導電層と金属層との積層よりなる走査線と透明導電性の絵素電極とが形成され、

ゲート電極上にプラズマ保護層とゲート絶縁層を介して不純物を含まない第1の半導体層が島状に形成され、

ゲート電極上の第1の半導体層上に前記ゲート電極よりも幅細く保護絶縁層が形成され、前記絵素電極上のプラズマ保護層とゲート絶縁層に開口部が形成され、

前記保護絶縁層の一部上と第1の半導体層上とに不純物を含む第2の半導体層と陽極酸化可能な金属層との積層よりなるソース(信号線)配線と、前記保護絶縁層の一部上と第1の半導体層上と第1の透明性絶縁基板上と前記開口部内の絵素電極の一部上とに同じくドレイン配線とが形成され、

信号線の電極端子を除いてソース・ドレイン配線の表面に陽極酸化層が形成されていることを特徴とする液晶表示装置。

#### 【請求項8】

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、前記絶縁ゲート型トランジスタのドレインに接続された絵素電極と、前記絵素電極とは所定の距離を隔てて形成された対向電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、少なくとも

第1の透明性絶縁基板の一主面上に1層以上の第1の金属層よりなる走査線と対向電極とが形成され、

ゲート電極上に1層以上のゲート絶縁層を介して不純物を含まない第1の半導体層が島状に形成され、

ゲート電極上の第1の半導体層上に前記ゲート電極よりも幅細く保護絶縁層が形成され、前記保護絶縁層の一部上と第1の半導体層上とに不純物を含む第2の半導体層と1層以上の第2の金属層との積層よりなるソース配線(信号線)とドレイン配線(絵素電極)とが形成され、

信号線の電極端子を除いて信号線上に感光性有機絶縁層が形成され、

10

20

30

40

50

走査線の電極端子は画像表示部外の領域で走査線上のゲート絶縁層に形成された開口部を含んで形成された第2の金属層よりなることを特徴とする液晶表示装置。

【請求項9】

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、前記絶縁ゲート型トランジスタのドレインに接続された絵素電極と、前記絵素電極とは所定の距離を隔てて形成された対向電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、少なくとも

第1の透明性絶縁基板の一主面上に1層以上の金属層よりなる走査線と対向電極とが形成され、10

ゲート電極上に1層以上のゲート絶縁層を介して不純物を含まない第1の半導体層が島状に形成され、

ゲート電極上の第1の半導体層上に前記ゲート電極よりも幅細く保護絶縁層が形成され、前記保護絶縁層の一部上と第1の半導体層上とに不純物を含む第2の半導体層と陽極酸化可能な金属層との積層よりなるソース配線（信号線）とドレイン配線（絵素電極）とが形成され、

信号線の電極端子を除いてソース・ドレイン配線の表面に陽極酸化層が形成され、走査線の電極端子は画像表示部外の領域で走査線上のゲート絶縁層に形成された開口部を含んで形成された陽極酸化可能な金属層よりなることを特徴とする液晶表示装置。20

【請求項10】

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、前記絶縁ゲート型トランジスタのドレインに接続された絵素電極と、前記絵素電極とは所定の距離を隔てて形成された対向電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、少なくとも

第1の透明性絶縁基板の一主面上に1層以上の第1の金属層よりなる走査線と対向電極とが形成され、20

ゲート電極上に1層以上のゲート絶縁層を介して不純物を含まない第1の半導体層が島状に形成され、30

ゲート電極上の第1の半導体層上に前記ゲート電極よりも幅細く保護絶縁層が形成され、前記保護絶縁層の一部上と第1の半導体層上とに不純物を含む第2の半導体層と1層以上の第2の金属層との積層よりなるソース配線（信号線）とドレイン配線（絵素電極）とが形成され、

信号線の電極端子を除いて信号線上に感光性有機絶縁層が形成され、走査線の電極端子は画像表示部外の領域で走査線上のゲート絶縁層に形成された開口部を含んで形成された第2の半導体層と第2の金属層との積層よりなることを特徴とする液晶表示装置。30

【請求項11】

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、前記絶縁ゲート型トランジスタのドレインに接続された絵素電極と、前記絵素電極とは所定の距離を隔てて形成された対向電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、少なくとも

第1の透明性絶縁基板の一主面上に1層以上の金属層よりなる走査線と対向電極とが形成され、40

ゲート電極上に1層以上のゲート絶縁層を介して不純物を含まない第1の半導体層が島状に形成され、50

ゲート電極上の第1の半導体層上に前記ゲート電極よりも幅細く保護絶縁層が形成され、前記保護絶縁層の一部上と第1の半導体層上とに不純物を含む第2の半導体層と陽極酸化可能な金属層との積層よりなるソース(信号線)とドレイン配線(絵素電極)とが形成され、

信号線の電極端子を除いてソース・ドレイン配線の表面に陽極酸化層が形成され、走査線の電極端子は画像表示部外の領域で走査線上のゲート絶縁層に形成された開口部を含んで形成された第2の半導体層と陽極酸化可能な金属層との積層よりなることを特徴とする液晶表示装置。

#### 【請求項12】

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、ドレイン配線に接続された絵素電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、10

少なくとも第1の透明性絶縁基板の一主面上に1層以上の金属層よりなる走査線を形成する工程と、

1層以上のゲート絶縁層と不純物を含まない第1の非晶質シリコン層と保護絶縁層とを順次被着する工程と、10

走査線の電極端子形成領域上に開口部を有しゲート電極上の保護絶縁層形成領域の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、20

前記開口部内の保護絶縁層と第1の非晶質シリコン層とゲート絶縁層とを除去して走査線の電極端子形成領域を露出する工程と、

前記感光性樹脂パターンの膜厚を減少して保護絶縁層を露出する工程と、

ゲート電極上にゲート電極よりも幅細く保護絶縁層を残して第1の非晶質シリコン層を露出する工程と、

前記感光性樹脂パターンの除去後、全面に不純物を含む第2の非晶質シリコン層を被着する工程と、20

前記保護絶縁層と一部重なるように第2の非晶質シリコン層と1層以上の陽極酸化可能な金属層との積層よりなるソース(信号線)・ドレイン配線を形成する工程と、

ゲート絶縁層上と前記ドレイン配線の一部上に透明導電性の絵素電極と画像表示部外の領域で信号線上に透明導電性の電極端子とを形成する工程と、30

前記絵素電極と電極端子の選択的パターン形成に用いられた感光性樹脂パターンをマスクとして絵素電極と電極端子とを保護しながらソース・ドレイン配線を陽極酸化する工程とを有する液晶表示装置の製造方法。40

#### 【請求項13】

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、ドレイン配線に接続された絵素電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、40

少なくとも第1の透明性絶縁基板の一主面上に透明導電層と第1の金属層との積層よりなる走査線と信号線の擬似電極端子と擬似絵素電極とを形成する工程と、

プラズマ保護層とゲート絶縁層と不純物を含まない第1の非晶質シリコン層と保護絶縁層とを順次被着する工程と、

走査線と信号線の電極端子形成領域上と擬似絵素電極上とに開口部を有しゲート電極上の保護絶縁層形成領域の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、前記開口部内の保護絶縁層と第1の非晶質シリコン層とゲート絶縁層とプラズマ保護層と第1の金属層とを除去して透明導電性の走査線と信号線の電極端子形成領域と同じく絵素電極とを露出する工程と、50

前記感光性樹脂パターンの膜厚を減少して保護絶縁層を露出する工程と、

ゲート電極上にゲート電極よりも幅細く保護絶縁層を残して第1の非晶質シリコン層を露出する工程と、

前記感光性樹脂パターンの除去後、全面に不純物を含む第2の非晶質シリコン層を被着する工程と、

1層以上の第2の金属層を被着後、第2の非晶質シリコン層と1層以上の第2の金属層との積層よりなり前記保護絶縁層と一部重なるように信号線の電極端子形成領域を含んでその表面に感光性有機絶縁層を有するソース配線（信号線）と同じく絵素電極を含んでドレイン配線とを形成する工程とを有する液晶表示装置の製造方法。

【請求項14】

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、ドレイン配線に接続された絵素電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、10

少なくとも第1の透明性絶縁基板の一主面上に透明導電層と第1の金属層との積層よりなる走査線と擬似絵素電極とを形成する工程と、

プラズマ保護層とゲート絶縁層と不純物を含まない第1の非晶質シリコン層と保護絶縁層とを順次被着する工程と、20

走査線の電極端子形成領域上と擬似絵素電極上とに開口部を有しゲート電極上の保護絶縁層形成領域の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、20

前記開口部内の保護絶縁層と第1の非晶質シリコン層とゲート絶縁層とプラズマ保護層と第1の金属層とを除去して透明導電性の走査線の電極端子形成領域と同じく絵素電極とを露出する工程と、20

前記感光性樹脂パターンの膜厚を減少して保護絶縁層を露出する工程と、

ゲート電極上にゲート電極よりも幅細く保護絶縁層を残して第1の非晶質シリコン層を露出する工程と、20

前記感光性樹脂パターンの除去後、全面に不純物を含む第2の非晶質シリコン層を被着する工程と、20

1層以上の第2の金属層を被着後、前記保護絶縁層と一部重なりソース配線（信号線）と同じく絵素電極を含んでドレイン配線と透明導電性の走査線の電極端子形成領域を含んで走査線の電極端子と信号線の一部よりなる信号線の電極端子とに対応し信号線上の膜厚が他の領域よりも厚い感光性有機絶縁層パターンを形成する工程と、30

前記感光性有機絶縁層パターンをマスクとして第2の金属層と第2の非晶質シリコン層と第1の非晶質シリコン層とを選択的に除去して走査線と信号線の電極端子とソース・ドレイン配線とを形成する工程と、30

前記感光性有機絶縁層パターンの膜厚を減少して走査線と信号線の電極端子とドレイン配線とを露出する工程とを有する液晶表示装置の製造方法。30

【請求項15】

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、ドレイン配線に接続された絵素電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、40

少なくとも第1の透明性絶縁基板の一主面上に透明導電層と金属層との積層よりなる走査線と擬似絵素電極とを形成する工程と、40

プラズマ保護層とゲート絶縁層と不純物を含まない第1の非晶質シリコン層と保護絶縁層とを順次被着する工程と、40

走査線の電極端子形成領域上と擬似絵素電極上とに開口部を有しゲート電極上の保護絶縁層形成領域の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、40

前記開口部内の保護絶縁層と第1の非晶質シリコン層とゲート絶縁層とプラズマ保護層と50

金属層とを除去して透明導電性の走査線の電極端子形成領域と同じく絵素電極とを露出する工程と、

前記感光性樹脂パターンの膜厚を減少して保護絶縁層を露出する工程と、

ゲート電極上にゲート電極よりも幅細く保護絶縁層を残して第1の非晶質シリコン層を露出する工程と、

前記感光性樹脂パターンの除去後、全面に不純物を含む第2の非晶質シリコン層を被着する工程と、

1層以上の陽極酸化可能な金属層を被着後、前記保護絶縁層と一部重なりソース配線（信号線）と同じく絵素電極を含んでドレイン配線と透明導電性の走査線の電極端子形成領域を含んで走査線の電極端子と信号線の一部よりなる信号線の電極端子とに対応し走査線と信号線の電極端子上の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、前記感光性樹脂パターンをマスクとして陽極酸化可能な金属層と第2の非晶質シリコン層と第1の非晶質シリコン層とを選択的に除去して走査線と信号線の電極端子とソース・ドレイン配線とを形成する工程と、

前記感光性樹脂パターンの膜厚を減少してソース・ドレイン配線を露出する工程と、

前記電極端子上を保護しながらソース・ドレイン配線を陽極酸化する工程とを有する液晶表示装置の製造方法。

#### 【請求項 1 6】

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、前記絶縁ゲート型トランジスタのドレインに接続された絵素電極と、前記絵素電極とは所定の距離を隔てて形成された対向電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、

少なくとも第1の透明性絶縁基板の一主面上に1層以上の第1の金属層よりなる走査線と対向電極とを形成する工程と、

1層以上のゲート絶縁層と不純物を含まない第1の非晶質シリコン層と保護絶縁層とを順次被着する工程と、

ゲート電極上にゲート電極よりも幅細く保護絶縁層を残して第1の非晶質シリコン層を露出する工程と、

全面に不純物を含む第2の非晶質シリコン層を被着後、走査線の電極端子形成領域上に開口部を形成して前記開口部内の第2の非晶質シリコン層と第1の非晶質シリコン層とゲート絶縁層とを除去して走査線の一部を露出する工程と、

1層以上の第2の金属層を被着後、前記保護絶縁層と一部重なりソース配線（信号線）・ドレイン配線（絵素電極）と前記開口部を含んで走査線の電極端子と信号線の一部よりなる信号線の電極端子とに対応し信号線上の膜厚が他の領域よりも厚い感光性有機絶縁層パターンを形成する工程と、

前記感光性有機絶縁層パターンをマスクとして第2の金属層と第2の非晶質シリコン層と第1の非晶質シリコン層とを選択的に除去して走査線と信号線の電極端子とソース・ドレイン配線とを形成する工程と、

前記感光性有機絶縁層パターンの膜厚を減少して走査線と信号線の電極端子とドレイン配線とを露出する工程とを有する液晶表示装置の製造方法。

#### 【請求項 1 7】

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、前記絶縁ゲート型トランジスタのドレインに接続された絵素電極と、前記絵素電極とは所定の距離を隔てて形成された対向電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、

少なくとも第1の透明性絶縁基板の一主面上に1層以上の金属層よりなる走査線と対向電

10

20

30

40

50

極とを形成する工程と、

1層以上のゲート絶縁層と不純物を含まない第1の非晶質シリコン層と保護絶縁層とを順次被着する工程と、

ゲート電極上にゲート電極よりも幅細く保護絶縁層を残して第1の非晶質シリコン層を露出する工程と、

全面に不純物を含む第2の非晶質シリコン層を被着後、走査線の電極端子形成領域上に開口部を形成して前記開口部内の第2の非晶質シリコン層と第1の非晶質シリコン層とゲート絶縁層とを除去して走査線の一部を露出する工程と、

1層以上の陽極酸化可能な金属層を被着後、前記保護絶縁層と一部重なりソース配線（信号線）・ドレイン配線（絵素電極）と前記開口部を含んで走査線の電極端子と信号線の一部よりなる信号線の電極端子とに対応し走査線と信号線の電極端子上の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、

前記感光性樹脂パターンをマスクとして陽極酸化可能な金属層と第2の非晶質シリコン層と第1の非晶質シリコン層とを選択的に除去して走査線と信号線の電極端子とソース・ドレイン配線とを形成する工程と、

前記感光性樹脂パターンの膜厚を減少してソース・ドレイン配線を露出する工程と、

前記電極端子上を保護しながらソース・ドレイン配線を陽極酸化する工程とを有する液晶表示装置の製造方法。

#### 【請求項18】

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、前記絶縁ゲート型トランジスタのドレインに接続された絵素電極と、前記絵素電極とは所定の距離を隔てて形成された対向電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、

少なくとも第1の透明性絶縁基板の一主面上に1層以上の第1の金属層よりなる走査線と対向電極とを形成する工程と、

1層以上のゲート絶縁層と不純物を含まない第1の非晶質シリコン層と保護絶縁層とを順次被着する工程と、

走査線の電極端子形成領域上に開口部を有しゲート電極上の保護絶縁層形成領域の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、

前記開口部内の保護絶縁層と第1の非晶質シリコン層とゲート絶縁層とを除去して走査線の一部を露出する工程と、

前記感光性樹脂パターンの膜厚を減少して保護絶縁層を露出する工程と、

ゲート電極上にゲート電極よりも幅細く保護絶縁層を残して第1の非晶質シリコン層を露出する工程と、

前記感光性樹脂パターンの除去後、全面に不純物を含む第2の非晶質シリコン層を被着する工程と、

1層以上の第2の金属層を被着後、前記保護絶縁層と一部重なりソース配線（信号線）・ドレイン配線（絵素電極）と開口部内の第2の非晶質シリコン層を含んで走査線の電極端子と信号線の一部よりなる信号線の電極端子とに対応し信号線上の膜厚が他の領域よりも厚い感光性有機絶縁層パターンを形成する工程と、

前記感光性有機絶縁層パターンをマスクとして第2の金属層と第2の非晶質シリコン層と第1の非晶質シリコン層とを選択的に除去して走査線と信号線の電極端子とソース・ドレイン配線とを形成する工程と、

前記感光性有機絶縁層パターンの膜厚を減少して走査線と信号線の電極端子とドレイン配線とを露出する工程とを有する液晶表示装置の製造方法。

#### 【請求項19】

一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、前記絶縁ゲート型トランジスタ

10

20

30

40

50

のドレインに接続された絵素電極と、前記絵素電極とは所定の距離を隔てて形成された対向電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、

少なくとも第1の透明性絶縁基板の一主面上に1層以上の金属層よりなる走査線と対向電極とを形成する工程と、

1層以上のゲート絶縁層と不純物を含まない第1の非晶質シリコン層と保護絶縁層とを順次被着する工程と、

走査線の電極端子形成領域上に開口部を有しゲート電極上の保護絶縁層形成領域の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、

前記開口部内の保護絶縁層と第1の非晶質シリコン層とゲート絶縁層とを除去して走査線の一部を露出する工程と、

前記感光性樹脂パターンの膜厚を減少して保護絶縁層を露出する工程と、

ゲート電極上にゲート電極よりも幅細く保護絶縁層を残して第1の非晶質シリコン層を露出する工程と、

前記感光性樹脂パターンの除去後、全面に不純物を含む第2の非晶質シリコン層を被着する工程と、

1層以上の陽極酸化可能な金属層を被着後、前記保護絶縁層と一部重なりソース（信号線）配線・ドレイン配線（絵素電極）と開口部内の第2の非晶質シリコン層を含んで走査線の電極端子と信号線の一部よりなる信号線の電極端子とに対応し走査線と信号線の電極端子上の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、

前記感光性樹脂パターンをマスクとして陽極酸化可能な金属層と第2の非晶質シリコン層と第1の非晶質シリコン層とを選択的に除去して走査線と信号線の電極端子とソース・ドレイン配線とを形成する工程と、

前記感光性樹脂パターンの膜厚を減少してソース・ドレイン配線を露出する工程と、

前記電極端子上を保護しながらソース・ドレイン配線を陽極酸化する工程とを有する液晶表示装置の製造方法。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明はカラー画像表示機能を有する液晶表示装置、とりわけアクティブ型の液晶表示装置に関するものである。

##### 【0002】

##### 【従来の技術】

近年の微細加工技術、液晶材料技術および高密度実装技術等の進歩により、5～50cm対角の液晶表示装置でテレビジョン画像や各種の画像表示機器が商用ベースで大量に提供されている。また、液晶パネルを構成する2枚のガラス基板の一方にRGBの着色層を形成しておくことによりカラー表示も容易に実現している。特にスイッチング素子を絵素毎に内蔵させた、いわゆるアクティブ型の液晶パネルではクロストークも少なく、応答速度も早く高いコントラスト比を有する画像が保証されている。

##### 【0003】

これらの液晶表示装置（液晶パネル）は走査線としては200～1200本、信号線としては300～1600本程度のマトリクス編成が一般的であるが、最近は表示容量の増大に対応すべく大画面化と高精細化とが同時に進行している。

##### 【0004】

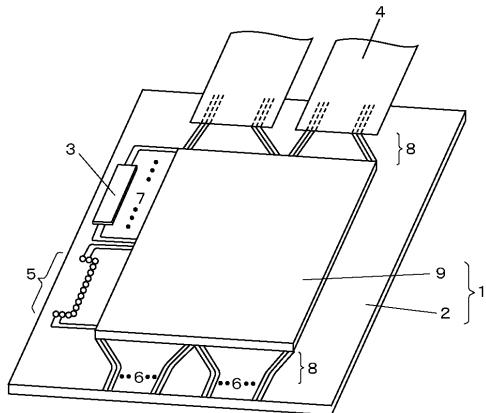

図17は液晶パネルへの実装状態を示し、液晶パネル1を構成する一方の透明性絶縁基板、例えばガラス基板2上に形成された走査線の電極端子群5に駆動信号を供給する半導体集積回路チップ3を導電性の接着剤を用いて接続するCOG（Chip-On-Glass）方式や、例えばポリイミド系樹脂薄膜をベースとし、金または半田メッキされた銅箔の端子（図示せず）を有するTCPフィルム4を信号線の電極端子群6に導電性媒体を含

む適當な接着剤で圧接して固定するTCP(Tape-Carrier-Package)方式などの実装手段によって電気信号が画像表示部に供給される。ここでは便宜上二つの実装方式を同時に図示しているが實際には何れかの方式が適宜選択される。

#### 【0005】

7、8は液晶パネル1のほぼ中央部に位置する画像表示部内の画素と走査線及び信号線の電極端子5,6との間を接続する配線路で、必ずしも電極端子群5,6と同一の導電材で構成される必要はない。9は全ての液晶セルに共通する透明導電性の対向電極を対向面上に有するもう1枚の透明性絶縁基板である対向ガラス基板またはカラーフィルタである。

#### 【0006】

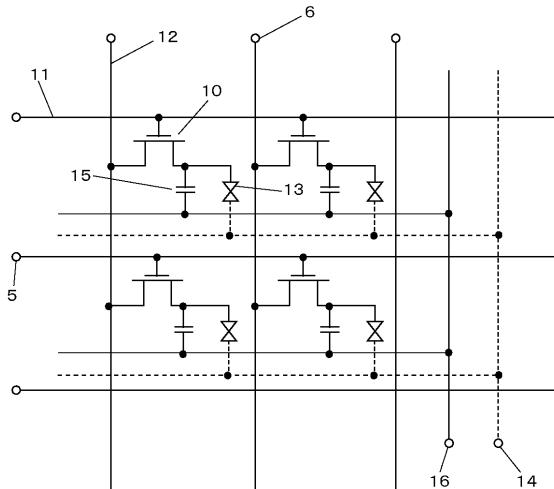

図18はスイッチング素子として絶縁ゲート型トランジスタ10を絵素毎に配置したアクティブ型液晶表示装置の等価回路図を示し、11(図17では7)は走査線、12(図17では8)は信号線、13は液晶セルであって、液晶セル13は電気的には容量素子として扱われる。実線で描かれた素子類は液晶パネルを構成する一方のガラス基板2上に形成され、点線で描かれた全ての液晶セル13に共通な対向電極14はもう一方のガラス基板9の対向する主面上に形成されている。絶縁ゲート型トランジスタ10のOFF抵抗あるいは液晶セル13の抵抗が低い場合や表示画像の階調性を重視する場合には、負荷としての液晶セル13の時定数を大きくするための補助の蓄積容量15を液晶セル13に並列に加える等の回路的工夫が加味される。なお16は蓄積容量15の共通母線である。

#### 【0007】

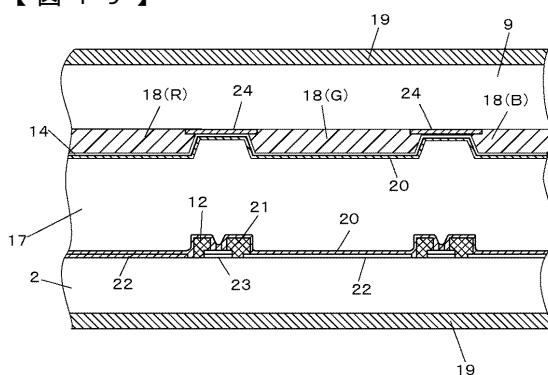

図19は液晶表示装置の画像表示部の要部断面図を示し、液晶パネル1を構成する2枚のガラス基板2,9は樹脂性のファイバ、ビーズあるいはカラーフィルタ9上に形成された柱状スペーサ等のスペーサ材(図示せず)によって数μm程度の所定の距離を隔てて形成され、その間隙(ギャップ)はガラス基板9の周縁部において有機性樹脂よりなるシール材と封口材(何れも図示せず)とで封止された閉空間になっており、この閉空間に液晶17が充填されている。

#### 【0008】

カラー表示を実現する場合には、ガラス基板9の閉空間側に着色層18と称する染料または顔料のいずれか一方もしくは両方を含む厚さ1~2μm程度の有機薄膜が被着されて色表示機能が与えられるので、その場合にはガラス基板9は別名カラーフィルタ(Color Filter 略語はCF)と呼称される。そして液晶材料17の性質によってはガラス基板9の上面またはガラス基板2の下面の何れかもしくは両面上に偏光板19が貼付され、液晶パネル1は電気光学素子として機能する。現在、市販されている大部分の液晶パネルでは液晶材料にTN(ツイスト・ネマチック)系の物を用いており、偏光板19は通常2枚必要である。図示はしないが、透過型液晶パネルでは光源として裏面光源が配置され、下方より白色光が照射される。

#### 【0009】

液晶17に接して2枚のガラス基板2,9上に形成された例えは厚さ0.1μm程度のポリイミド系樹脂薄膜20は液晶分子を決められた方向に配向させるための配向膜である。21は絶縁ゲート型トランジスタ10のドレインと透明導電性の絵素電極22とを接続するドレイン電極(配線)であり、信号線(ソース線)12と同時に形成されることが多い。信号線12とドレイン電極21との間に位置するのは半導体層23であり詳細は後述する。カラーフィルタ9上で隣り合った着色層18の境界に形成された厚さ0.1μm程度のCr薄膜層24は半導体層23と走査線11及び信号線12に外部光が入射するのを防止するための光遮蔽部材で、いわゆるブラックマトリクス(Black Matrix 略語はBM)として定着化した技術である。

#### 【0010】

ここでスイッチング素子として絶縁ゲート型トランジスタの構造と製造方法に関して説明する。絶縁ゲート型トランジスタには2種類のものが現在多用されており、そのうちの一つを従来例(エッチ・ストップ型と呼称される)として紹介する。図20は従来の液晶パ

10

20

30

40

50

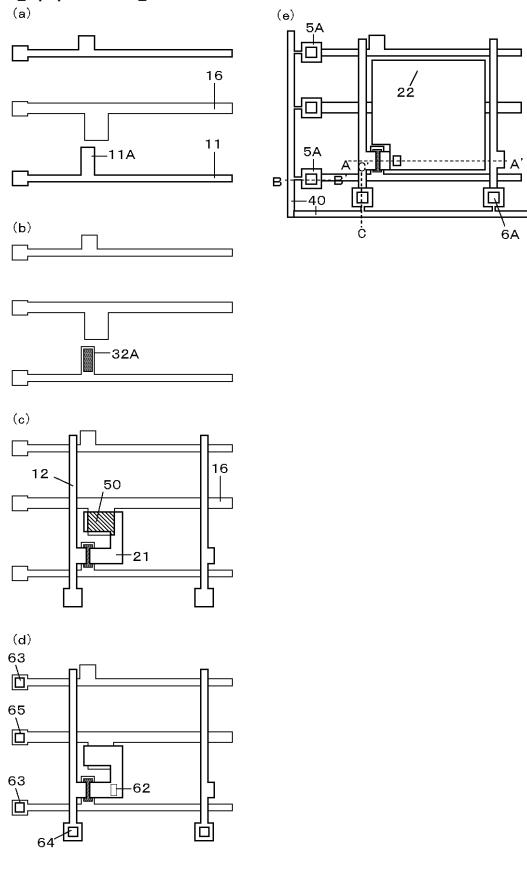

ネルを構成するアクティブ基板（表示装置用半導体装置）の単位絵素の平面図であり、図 20 (e) の A - A' 、 B - B' および C - C' 線上の断面図を図 21 に示し、その製造工程を以下に簡単に説明する。

#### 【 0 0 1 1 】

先ず、図 20 (a) と図 21 (a) に示したように耐熱性と耐薬品性と透明性が高い絶縁性基板として厚さ 0.5 ~ 1.1 mm 程度のガラス基板 2 、例えばコーニング社製の商品名 1737 の一主面上に SPT (スパッタ) 等の真空製膜装置を用いて膜厚 0.1 ~ 0.3 μm 程度の第 1 の金属層として例えば Cr, Ta, Mo 等あるいはそれらの合金やシリサイドを被着して微細加工技術によりゲート電極 11A も兼ねる走査線 11 と蓄積容量線 16 とを選択的に形成する。走査線の材質は耐熱性と耐薬品性と耐弗酸性と導電性とを総合的に勘案して選択すると良い。

#### 【 0 0 1 2 】

液晶パネルの大画面化や高精細化に対応して走査線の抵抗値を下げるためには走査線の材料として AL (アルミニウム) を用いるのが合理的であるが、AL は単体では耐熱性が低いので上記した耐熱金属である Cr, Ta, Mo またはそれらのシリサイドと積層化する、あるいは AL の表面に陽極酸化で酸化層 (Al2O3) を附加することも現在では一般的な技術である。すなわち走査線 11 は 1 層以上の金属層で構成される。

#### 【 0 0 1 3 】

次に、ガラス基板 2 の全面に P C V D (プラズマ・シープイディ) 装置を用いてゲート絶縁層となる第 1 の SiNx (シリコン窒化) 層 30 、不純物をほとんど含まず絶縁ゲート型トランジスタのチャネルとなる第 1 の非晶質シリコン (a-Si) 層 31 、及びチャネルを保護する絶縁層となる第 2 の SiNx 層 32 と 3 種類の薄膜層を例えば、0.3 - 0.05 - 0.1 μm 程度の膜厚で順次被着し、図 20 (b) と図 21 (b) に示したように微細加工技術によりゲート電極 11A 上の第 2 の SiNx 層をゲート電極 11A よりも幅細く選択的に残して 32A として第 1 の非晶質シリコン層 31 を露出する。

#### 【 0 0 1 4 】

続いて同じく P C V D 装置を用いて全面に不純物として例えば磷を含む第 2 の非晶質シリコン層 33 を例えば 0.05 μm 程度の膜厚で被着した後、図 20 (c) と図 21 (c) に示したように SPT 等の真空製膜装置を用いて膜厚 0.1 μm 程度の耐熱金属層として例えば Ti, Cr, Mo 等の耐熱金属薄膜層 34 を、低抵抗配線層として膜厚 0.3 μm 程度の AL 薄膜層 35 を、さらに膜厚 0.1 μm 程度の中間導電層として例えば Ti 薄膜層 36 を順次被着し、微細加工技術によりソース・ドレイン配線材であるこれら 3 種の薄膜の積層 34A, 35A, 36A よりなる絶縁ゲート型トランジスタのドレイン電極 21 とソース電極も兼ねる信号線 12 とを選択的に形成する。この選択的パターン形成は、ソース・ドレイン配線の形成に用いられる感光性樹脂パターンをマスクとして Ti 薄膜層 36 、 AL 薄膜層 35 、 Ti 薄膜層 34 を順次食刻した後、ソース・ドレイン電極 12, 21 間の第 2 の非晶質シリコン層 33 を除去して第 2 の SiNx 層 32A を露出するとともに、その他の領域では第 1 の非晶質シリコン層 31 をも除去してゲート絶縁層 30 を露出することによってなされる。このようにチャネルの保護層である第 2 の層 SiNx 層 32A が存在して第 2 の非晶質シリコン層 33 の食刻が自動的に終了することからこの製法はエッチストップと呼称される。

#### 【 0 0 1 5 】

絶縁ゲート型トランジスタがオフセット構造とならぬようソース・ドレイン電極 12, 21 はゲート電極 11A と一部 (数 μm) 平面的に重なって形成される。この重なりは寄生容量として電気的に作用する所以小さいほど良いが、露光機の合わせ精度とフォトマスクの精度とガラス基板の膨張係数及び露光時のガラス基板温度で決定され、実用的な数値は精々 2 μm 程度である。

#### 【 0 0 1 6 】

そしてガラス基板 2 の全面に透明性の絶縁層としてゲート絶縁層と同様に P C V D 装置を用いて 0.3 μm 程度の膜厚の SiNx 層を被着してパシベーション絶縁層 37 とし、図

20 (d) と図 21 (d) とに示したようにパシベーション絶縁層 37 を微細加工技術により選択的に除去してドレイン電極 21 上に開口部 62 と、画像表示部外の領域で走査線 11 の電極端子 5 が形成される位置上に開口部 63 と、信号線 12 の電極端子 6 が形成される位置上に開口部 64 とを形成してドレイン電極 21 と走査線 11 と信号線 12 の一部分を露出する。蓄積容量線 16 (を平行に束ねた電極パターン) 上には開口部 65 を形成して蓄積容量線 16 の一部を露出する。

#### 【0017】

最後に SPT 等の真空製膜装置を用いて膜厚  $0.1 \sim 0.2 \mu\text{m}$  程度の透明導電層として例えれば ITO (Indium-Tin-Oxide) あるいは IZO (Indium-Zinc-Oxide) を被着し、図 20 (e) と図 21 (e) とに示したように微細加工技術により開口部 62 を含んでパシベーション絶縁層 37 上に絵素電極 22 を選択的に形成してアクティブ基板 2 として完成する。開口部 63 内の露出している走査線 11 の一部を電極端子 5 とし、開口部 64 内の露出している信号線 12 の一部を電極端子 6 としても良く、図示したように開口部 63, 64 を含んでパシベーション絶縁層 37 上に ITO よりなる電極端子 5A, 6A を選択的に形成しても良いが、通常は電極端子 5A, 6A 間を接続する透明導電性の短絡線 40 も同時に形成される。その理由は、図示はしないが電極端子 5A, 6A と短絡線 40 との間を細長いストライプ状に形成することにより高抵抗化して静電気対策用の高抵抗とすることが出来るからである。同様に開口部 65 を含んで蓄積容量線 16 への電極端子が形成される。

#### 【0018】

信号線 12 の配線抵抗が問題とならない場合には AL よりなる低抵抗配線層 35 は必ずしも必要ではなく、その場合には Cr, Ta, Mo 等の耐熱金属材料を選択すればソース・ドレイン配線 12, 21 を単層化して簡素化することが可能である。なお、絶縁ゲート型トランジスタの耐熱性については先行例である特開平 7-74368 号公報に詳細が記載されている。なお、図 20 (c) において蓄積容量線 16 とドレイン電極 21 とがゲート絶縁層 30 を介して重なっている領域 50 (右下がり斜線部) が蓄積容量 15 を形成しているが、ここではその詳細な説明は省略する。

#### 【0019】

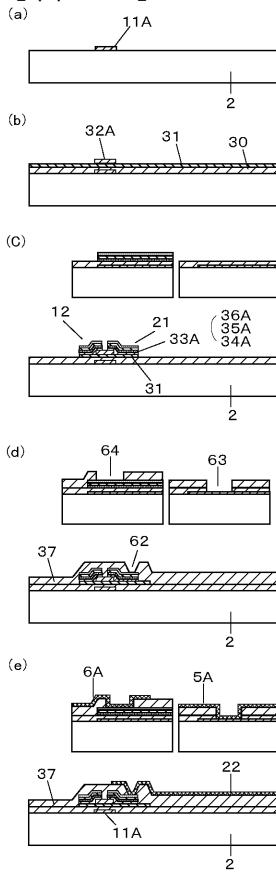

以上述べた 5 枚マスク・プロセスは詳細な経緯は省略するが、半導体層の島化工程の合理化とコンタクト形成工程が 1 回削減された結果得られたもので、当初は 7 ~ 8 枚程度必要であったフォトマスクもドライエッチ技術の導入により、現時点では 5 枚に減少してプロセスコストの削減に大きく寄与している。液晶表示装置の生産コストを下げるためにはアクティブ基板の作製工程ではプロセスコストを、またパネル組立工程とモジュール実装工程では部材コストを下げることが有効であることは周知の開発目標である。プロセスコストを下げるためにはプロセスを短くする工程削減と、安価なプロセス開発またはプロセスへの置き換えとがあるが、ここでは 4 枚のフォトマスクでアクティブ基板が得られる 4 枚マスク・プロセスを工程削減の一例として説明する。4 枚マスク・プロセスはハーフトーン露光技術の導入に写真食刻工程を削減するもので、図 22 は 4 枚マスク・プロセスに対応したアクティブ基板の単位絵素の平面図で、図 22 (e) の A-A'、B-B' および C-C' 線上の断面図を図 23 に示す。既に述べたように絶縁ゲート型トランジスタには 2 種類のものが現在多用されているが、ここではチャネルエッチ型の絶縁ゲート型トランジスタを採用している。

#### 【0020】

先ず、5 枚マスク・プロセスと同様にガラス基板 2 の一主面上に SPT 等の真空製膜装置を用いて膜厚  $0.1 \sim 0.3 \mu\text{m}$  程度の第 1 の金属層を被着し、図 22 (a) と図 23 (a) に示したように微細加工技術によりゲート電極 11A も兼ねる走査線 11 と蓄積容量線 16 とを選択的に形成する。

#### 【0021】

次に、ガラス基板 2 の全面に PCD 装置を用いてゲート絶縁層となる SiN<sub>x</sub> 層 30、不純物をほとんど含まず絶縁ゲート型トランジスタのチャネルとなる第 1 の非晶質シリコ

10

20

30

40

50

ン層 3 1、及び不純物を含み絶縁ゲート型トランジスタのソース・ドレインとなる第2の非晶質シリコン層 3 3と3種類の薄膜層を、例えば 0 . 3 - 0 . 2 - 0 . 0 5  $\mu\text{m}$  程度の膜厚で順次被着する。引き続き、S P T等の真空製膜装置を用いて膜厚 0 . 1  $\mu\text{m}$  程度の耐熱金属層として例えば Ti 薄膜層 3 4を、膜厚 0 . 3  $\mu\text{m}$  程度の低抵抗配線層として Al 薄膜層 3 5を、膜厚 0 . 1  $\mu\text{m}$  程度の中間導電層として例えば Ti 薄膜層 3 6、すなわちソース・ドレイン配線材を順次被着し、微細加工技術により絶縁ゲート型トランジスタのドレイン電極 2 1とソース電極も兼ねる信号線 1 2とを選択的に形成するのであるが、この選択的パターン形成に当たりハーフトーン露光技術により図 2 2 ( b )と図 2 3 ( b )に示したようにソース・ドレイン配線間のチャネル形成領域 8 0 C ( 右上がり斜線部 )の膜厚が例えば 1 . 5  $\mu\text{m}$  で、ソース・ドレイン配線形成領域 8 0 A , 8 0 B の膜厚 3  $\mu\text{m}$  よりも薄い感光性樹脂パターン 8 0 A ~ 8 0 C を形成する点が大きな特徴である。

## 【 0 0 2 2 】

このような感光性樹脂パターン 8 0 A ~ 8 0 C は、液晶表示装置用基板の作製には通常ポジ型の感光性樹脂を用いるので、ソース・ドレイン配線形成領域 8 0 A , 8 0 B が黒、すなわち Cr 薄膜が形成されており、チャネル領域 8 0 C は灰色、たとえば幅 0 . 5 ~ 1  $\mu\text{m}$  程度のラインアンドスペースの Cr パターンが形成されており、その他の領域は白、すなわち Cr 薄膜が除去されているようなフォトマスクを用いれば良い。灰色領域は露光機の解像力が不足しているためにラインアンドスペースが解像されることはなく、ランプ光源からのフォトマスク照射光を半分程度透過させることができるので、ポジ型感光性樹脂の残膜特性に応じて図 2 3 ( b )に示したような断面形状を有する感光性樹脂パターン 8 0 A ~ 8 0 C を得ることができる。

## 【 0 0 2 3 】

上記感光性樹脂パターン 8 0 A ~ 8 0 C をマスクとして図 2 3 ( b )と図 2 3 ( b )に示したように Ti 薄膜層 3 6、Al 薄膜層 3 5、Ti 薄膜層 3 4、第2の非晶質シリコン層 3 3 及び第1の非晶質シリコン層 3 1 を順次食刻してゲート絶縁層 3 0 を露出した後、図 2 2 ( c )と図 2 3 ( c )に示したように酸素プラズマ等の灰化手段により感光性樹脂パターン 8 0 A ~ 8 0 C の膜厚を例えば 3  $\mu\text{m}$  から 1 . 5  $\mu\text{m}$  以上減少せしめて 8 1 A , 8 1 B とすると 8 0 C が消失しチャネル領域が露出する。そこで膜減りした感光性樹脂パターン 8 1 A , 8 1 B をマスクとして、再びソース・ドレイン配線間(チャネル形成領域)の Ti 薄膜層 3 6 A , Al 薄膜層 3 5 A , Ti 薄膜層 3 4 A , 第2の非晶質シリコン層 3 3 A 及び第1の非晶質シリコン層 3 1 A を順次食刻し、第1の非晶質シリコン層 3 1 A は 0 . 0 5 ~ 0 . 1  $\mu\text{m}$  程度残して食刻する。チャネルエッチと呼称される理由はこのようにチャネルとなる半導体層がエッティングして形成される点にある。なお上記酸素プラズマ処理ではパターン寸法の変化を抑制するため異方性を強めることが望ましいがその理由は後述する。

## 【 0 0 2 4 】

さらに上記感光性樹脂パターン 8 1 A , 8 1 B を除去した後は、5枚マスク・プロセスと同じく図 2 2 ( d )と図 2 3 ( d )に示したようにガラス基板 2 の全面に透明性の絶縁層として 0 . 3  $\mu\text{m}$  程度の膜厚の Si N<sub>x</sub> 層を被着してパシベーション絶縁層 3 7 とし、ドレイン電極 2 1と走査線 1 1と信号線 1 2の電極端子 5 , 6 が形成される領域にそれぞれ開口部 6 2 , 6 3 , 6 4 を形成して開口部内のパシベーション絶縁層 3 7 とゲート絶縁層 3 0 とを除去する。

## 【 0 0 2 5 】

最後に S P T等の真空製膜装置を用いて膜厚 0 . 1 ~ 0 . 2  $\mu\text{m}$  程度の透明導電層として例えば ITOあるいはIZOを被着し、図 2 2 ( e )と図 2 3 ( e )に示したように微細加工技術によりパシベーション絶縁層 3 7 上に開口部 6 2 を含んで透明導電性の絵素電極 2 2 を選択的に形成してアクティブ基板 2 として完成する。電極端子に関してはここでは開口部 6 3 , 6 4 を含んでパシベーション絶縁層 3 7 上に ITO よりなる電極端子 5 A , 6 A を選択的に形成している。

## 【 0 0 2 6 】

10

20

30

40

50

**【発明が解決しようとする課題】**

このように5枚マスク・プロセスと4枚マスク・プロセスにおいてはドレイン電極21と走査線11へのコンタクト形成工程が同時になされるため、それらに対応した開口部62, 63内の絶縁層の厚さと種類が異なっている。パシベーション絶縁層37はゲート絶縁層30に比べると製膜温度が低く膜質が劣悪で、弗酸系のエッティング液による食刻では食刻速度が夫々数1000 /分、数100 /分と1桁も異なり、ドレイン電極21上の開口部62の断面形状は上部に余りにも過食刻が生じて穴径が制御できない理由から弗素系のガスを用いた乾式食刻(ドライエッチ)を採用している。

**【0027】**

ドライエッチを採用してもドレイン電極21上の開口部62はパシベーション絶縁層37のみであるので、走査線11上の開口部63と比較して過食刻になるのは避けられず、材質によっては中間導電層36Aが食刻ガスによって膜減りがある。また、食刻終了後の感光性樹脂パターンの除去に当たり、まずは弗素化された表面のポリマー除去のために酸素プラズマ灰化で感光性樹脂パターンの表面を0.1~0.3 μm程度削り、その後に有機剥離液、例えば東京応化製の剥離液106等を用いた薬液処理がなされるのが一般的であるが、中間導電層36Aが膜減りして下地のアルミニウム層35Aが露出した状態になっていると、酸素プラズマ灰化処理でアルミニウム層35Aの表面に絶縁体であるAL2O3が形成されて、絵素電極22との間でオーミック接触が得られなくなる。そこで中間導電層36Aが膜減りしてもいいように、その膜厚を例えば0.2 μmと厚く設定することでこの問題から逃れようとしている。あるいは開口部62~65の形成時、アルミニウム層35Aを除去して下地の耐熱金属層である薄膜層34Aを露出してから絵素電極22を形成する回避策も可能であり、この場合には当初から中間導電層36Aは不要となるメリットもある。

**【0028】**

しかしながら、前者の対策ではこれら薄膜の膜厚の面内均一性が良好でないとこの取組みも必ずしも有効に作用するわけではなく、また食刻速度の面内均一性が良好でない場合にも全く同様である。後者の対策では中間導電層36Aは不要となるが、アルミニウム層35Aの除去工程が増加し、また開口部62の断面制御が不十分であると絵素電極22が段切れを起こす恐れがあった。

**【0029】**

加えてチャネルエッチ型の絶縁ゲート型トランジスタではチャネル領域の不純物を含まない第1の非晶質シリコン層31はどうしても厚めに(チャネルエッチ型では通常0.2 μm以上)被着しておかないと、ガラス基板の面内均一性に大きく影響されてトランジスタ特性、とりわけOFF電流が不揃いになりがちである。このことはPCVDの稼働率とパーティクル発生状況とに大きく影響し、生産コストの観点からも非常に重要な事項である。

**【0030】**

また4枚マスク・プロセスにおいて適用されているチャネル形成工程はソース・ドレイン配線12, 21間のソース・ドレイン配線材と半導体層とを選択的に除去するので、絶縁ゲート型トランジスタのON特性を大きく左右するチャネルの長さ(現在の量産品で4~6 μm)を決定する工程である。このチャネル長の長さの変動は絶縁ゲート型トランジスタのON電流値を大きく変化させるので、通常は厳しい製造管理を要求されるが、チャネル長、すなわちハーフトーン露光領域のパターン寸法は露光量(光源強度とフォマスクのパターン精度、特にライン&スペース寸法)、感光性樹脂の塗布厚、感光性樹脂の現象処理、および当該のエッティング工程における感光性樹脂の膜減り量等多くのパラメータに左右され、加えてこれら諸量の面内均一性もあいまって必ずしも歩留高く安定して生産できるわけではなく、従来の製造管理よりも一段と厳しい製造管理が必要となり、決して高度に完成したレベルにあるとは言えないのが現状である。特にチャネル長が6 μm以下ではその傾向が顕著となる。

**【0031】**

10

20

30

40

50

本発明はかかる現状に鑑みなされたもので、従来の5枚マスク・プロセスや4枚マスク・プロセスに共通するコンタクト形成時の不具合を回避するだけでなく、製造マージンの大きいハーフトーン露光技術を採用して製造工程の削減を実現するものである。また液晶パネルの低価格化を実現し、需要の増大に対応していくためにも製造工程数の更なる削減を鋭意追求していく必要性があることは明白であり、他の主要な製造工程を簡略化あるいは低コスト化する技術を付与することによりさらに本発明の価値を高めんとするものである。

#### 【課題を解決するための手段】

本発明においては、まずハーフトーン露光技術をパターン精度管理が容易なエッチストップ層の形成工程とコンタクト形成工程とに適用することで製造工程の削減を実現している。次にソース・ドレイン配線のみを有効にパシベーションするために先行技術である特開平2-216129号公報に開示されているアルミニウムよりなるソース・ドレイン配線の表面に絶縁層を形成する陽極酸化技術と融合させてプロセスの合理化と低温化を実現せんとするものである。さらに先行技術である特願平5-268726号公報に開示されている絵素電極の形成工程を合理化したものを本発明に適合させて採用している。また更なる工程削減のためにソース・ドレイン配線の陽極酸化層形成にもハーフトーン露光技術を適用して電極端子の保護層形成工程を合理化している。

#### 【0032】

請求項1に記載の絶縁ゲート型トランジスタは、チャネル上に保護絶縁層を有し、ソース・ドレイン配線材とは異なった導電性材質よりなるソース配線の電気的接続領域の一部を含んで形成されたソース・ドレイン配線上に感光性有機絶縁層が形成されていることを特徴とするボトムゲート型の絶縁ゲート型トランジスタであり、感光性有機絶縁層がパシベーション機能を発揮するのでSiNx等の保護絶縁層を付与する必要は無く、液晶表示装置との関わりは請求項5と第2の実施形態で明確にする。

#### 【0033】

請求項2に記載の絶縁ゲート型トランジスタは、チャネル上に保護絶縁層を有し、ソース配線の電気的接続領域を除いてソース配線上にのみ感光性有機絶縁層が形成されていることを特徴とするボトムゲート型の絶縁ゲート型トランジスタであり、感光性有機絶縁層がパシベーション機能を発揮するのでSiNx等の保護絶縁層を付与する必要は無く、液晶表示装置との関わりは請求項6、請求項8、請求項10と第3、第5、第7の実施形態で明確にする。

#### 【0034】

請求項3に記載の絶縁ゲート型トランジスタは、チャネル上に保護絶縁層を有し、ソース・ドレイン配線が陽極酸化可能な金属層で構成されるとともにソース配線の電気的接続領域を除いてソース・ドレイン配線上に陽極酸化層が形成されていることを特徴とするボトムゲート型の絶縁ゲート型トランジスタであり、陽極酸化層がパシベーション機能を発揮するのでSiNx等の保護絶縁層を付与する必要は無く、液晶表示装置との関わりは請求項4、請求項7、請求項9、請求項11と第1、第4、第6、第8の実施形態で明確にする。

#### 【0035】

請求項4に記載の液晶表示装置は、一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、ドレイン配線に接続された絵素電極とを有する単位絵素が二次元のマトリクスに配列された第1の透明性絶縁基板と、前記第1の透明性絶縁基板と対向する第2の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、少なくとも第1の透明性絶縁基板の一主面上に1層以上の金属層よりなる走査線が形成され、

ゲート電極上に1層以上のゲート絶縁層を介して不純物を含まない第1の半導体層が島状に形成され、

ゲート電極上の第1の半導体層上に前記ゲート電極よりも幅細く保護絶縁層が形成され、

10

20

30

40

50

前記保護絶縁層の一部上と第1の半導体層上とに不純物を含む第2の半導体層と陽極酸化可能な金属層との積層よりなるソース(信号線)・ドレイン配線が形成され、

前記ドレイン配線の一部上とゲート絶縁層上に透明導電性の絵素電極と画像表示部外の領域で信号線上に透明導電性の電極端子とが形成され、

前記ドレイン配線の絵素電極と重なった領域と信号線の電極端子領域を除いてソース・ドレイン配線の表面に陽極酸化層が形成されていることを特徴とする。

この構成によりソース・ドレイン間のチャネル上には保護絶縁層が形成されてチャネルを保護するとともに信号線とドレイン配線の表面には絶縁性の陽極酸化層である5酸化タンタル(Ta<sub>2</sub>O<sub>5</sub>)または酸化アルミニウム(Al<sub>2</sub>O<sub>3</sub>)が形成されてパシベーション機能が付与されている。このためパシベーション絶縁層をガラス基板の全面に被着する必要はなくなり、絶縁ゲート型トランジスタの耐熱性が問題となることはなくなる。そして透明導電性の電極端子を有するTN型の液晶表示装置が得られる。

#### 【0036】

請求項5に記載の液晶表示装置は、同じく

少なくとも第1の透明性絶縁基板の一主面上に透明導電層と第1の金属層との積層よりなる走査線と透明導電性の絵素電極と同じく信号線の電極端子が形成され、

ゲート電極上にプラズマ保護層とゲート絶縁層を介して不純物を含まない第1の半導体層が島状に形成され、

ゲート電極上の第1の半導体層上に前記ゲート電極よりも幅細く保護絶縁層が形成され、前記絵素電極上のプラズマ保護層とゲート絶縁層に開口部が形成され、

前記保護絶縁層の一部上と第1の半導体層上と信号線の電極端子の一部上に不純物を含む第2の半導体層と1層以上の第2の金属層との積層よりなるソース(信号線)配線と、前記保護絶縁層の一部上と第1の半導体層上と第1の透明性絶縁基板上と前記開口部内の絵素電極の一部上と同じくドレイン配線とが形成され、

前記ソース・ドレイン配線上に感光性有機絶縁層が形成されていることを特徴とする。

この構成によりソース・ドレイン間のチャネル上には保護絶縁層が形成されてチャネルを保護するとともに信号線とドレイン配線の表面には感光性有機絶縁層が形成されてパシベーション機能が付与されている。このためパシベーション絶縁層をガラス基板の全面に被着する必要はなくなり、絶縁ゲート型トランジスタの耐熱性が問題となることはなくなる。そして透明導電性の電極端子を有するTN型の液晶表示装置が得られる。

#### 【0037】

請求項6に記載の液晶表示装置は、同じく

少なくとも第1の透明性絶縁基板の一主面上に透明導電層と第1の金属層との積層よりなる走査線と透明導電性の絵素電極とが形成され、

ゲート電極上にプラズマ保護層とゲート絶縁層を介して不純物を含まない第1の半導体層が島状に形成され、

ゲート電極上の第1の半導体層上に前記ゲート電極よりも幅細く保護絶縁層が形成され、前記絵素電極上のプラズマ保護層とゲート絶縁層に開口部が形成され、

前記保護絶縁層の一部上と第1の半導体層上とに不純物を含む第2の半導体層と1層以上の第2の金属層との積層よりなるソース(信号線)配線と、前記保護絶縁層の一部上と第1の半導体層上と前記開口部内の絵素電極の一部上と同じくドレイン配線とが形成され、

、

信号線の電極端子を除いて信号線上に感光性有機絶縁層が形成されていることを特徴とする。

この構成によりソース・ドレイン間のチャネル上には保護絶縁層が形成されてチャネルを保護するとともに信号線の表面には感光性有機絶縁層が形成されてパシベーション機能が付与されている。このためパシベーション絶縁層をガラス基板の全面に被着する必要はなくなり、絶縁ゲート型トランジスタの耐熱性が問題となることはなくなる。そして信号線と同一の金属性の電極端子を有するTN型の液晶表示装置が得られる。

#### 【0038】

10

20

30

40

50

請求項 7 に記載の液晶表示装置は、

同じく少なくとも第 1 の透明性絶縁基板の一主面上に透明導電層と金属層との積層よりなる走査線と透明導電性の絵素電極とが形成され、

ゲート電極上にプラズマ保護層とゲート絶縁層を介して不純物を含まない第 1 の半導体層が島状に形成され、

ゲート電極上の第 1 の半導体層上に前記ゲート電極よりも幅細く保護絶縁層が形成され、前記絵素電極上のプラズマ保護層とゲート絶縁層に開口部が形成され、

前記保護絶縁層の一部上と第 1 の半導体層上とに不純物を含む第 2 の半導体層と陽極酸化可能な金属層との積層よりなるソース（信号線）配線と、前記保護絶縁層の一部上と第 1 の半導体層上と第 1 の透明性絶縁基板上と前記開口部内の絵素電極の一部上と同じくドレイン配線とが形成され、

信号線の電極端子を除いてソース・ドレイン配線の表面に陽極酸化層が形成されていることを特徴とする。

この構成によりソース・ドレイン間のチャネル上には保護絶縁層が形成されてチャネルを保護するとともに信号線とドレイン配線の表面には絶縁性の陽極酸化層である Ta<sub>2</sub>O<sub>5</sub> または酸化アルミニウム (Al<sub>2</sub>O<sub>3</sub>) が形成されてパシベーション機能が付与されている。このためパシベーション絶縁層をガラス基板の全面に被着する必要はなくなり、絶縁ゲート型トランジスタの耐熱性が問題となることはなくなる。そして信号線と同一の金属性の電極端子を有する TN 型の液晶表示装置が得られる。

#### 【 0 0 3 9 】

請求項 8 に記載の液晶表示装置は、一主面上に少なくとも絶縁ゲート型トランジスタと、前記絶縁ゲート型トランジスタのゲート電極も兼ねる走査線とソース配線も兼ねる信号線と、前記絶縁ゲート型トランジスタのドレインに接続された絵素電極と、前記絵素電極とは所定の距離を隔てて形成された対向電極とを有する単位絵素が二次元のマトリクスに配列された第 1 の透明性絶縁基板と、前記第 1 の透明性絶縁基板と対向する第 2 の透明性絶縁基板またはカラーフィルタとの間に液晶を充填してなる液晶表示装置において、少なくとも第 1 の透明性絶縁基板の一主面上に 1 層以上の第 1 の金属層よりなる走査線と対向電極とが形成され、

ゲート電極上に 1 层以上のゲート絶縁層を介して不純物を含まない第 1 の半導体層が島状に形成され、

ゲート電極上の第 1 の半導体層上に前記ゲート電極よりも幅細く保護絶縁層が形成され、前記保護絶縁層の一部上と第 1 の半導体層上とに不純物を含む第 2 の半導体層と 1 層以上の第 2 の金属層との積層よりなるソース配線（信号線）とドレイン配線（絵素電極）とが形成され、

信号線の電極端子を除いて信号線上に感光性有機絶縁層が形成され、

走査線の電極端子は画像表示部外の領域で走査線上のゲート絶縁層に形成された開口部を含んで形成された第 2 の金属層よりなることを特徴とする。

この構成によりソース・ドレイン間のチャネル上には保護絶縁層が形成されてチャネルを保護するとともに信号線の表面には感光性有機絶縁層が形成されてパシベーション機能が付与されている。このためパシベーション絶縁層をガラス基板の全面に被着する必要はなくなり、絶縁ゲート型トランジスタの耐熱性が問題となることはなくなる。そして信号線と同一の金属性の電極端子を有する IPS 型の液晶表示装置が得られる。

#### 【 0 0 4 0 】

請求項 9 に記載の液晶表示装置は、

同じく少なくとも第 1 の透明性絶縁基板の一主面上に 1 層以上の金属層よりなる走査線と対向電極とが形成され、

ゲート電極上に 1 层以上のゲート絶縁層を介して不純物を含まない第 1 の半導体層が島状に形成され、

ゲート電極上の第 1 の半導体層上に前記ゲート電極よりも幅細く保護絶縁層が形成され、前記保護絶縁層の一部上と第 1 の半導体層上とに不純物を含む第 2 の半導体層と陽極酸化

10

20

30

40

50

可能な金属層との積層よりなるソース配線（信号線）とドレイン配線（絵素電極）とが形成され、

信号線の電極端子を除いてソース・ドレイン配線の表面に陽極酸化層が形成され、走査線の電極端子は画像表示部外の領域で走査線上のゲート絶縁層に形成された開口部を含んで形成された陽極酸化可能な金属層よりなることを特徴とする。

この構成によりソース・ドレイン間のチャネル上には保護絶縁層が形成されてチャネルを保護するとともに信号線とドレイン配線の表面には絶縁性の陽極酸化層である5酸化タンタル（Ta<sub>2</sub>O<sub>5</sub>）または酸化アルミニウム（Al<sub>2</sub>O<sub>3</sub>）が形成されてパシベーション機能が付与されている。このためパシベーション絶縁層をガラス基板の全面に被着する必要はなくなり、絶縁ゲート型トランジスタの耐熱性が問題となることはなくなる。そして信号線と同一の金属属性の電極端子を有するIPS型の液晶表示装置が得られる。10

#### 【0041】

請求項10に記載の液晶表示装置は、

同じく少なくとも第1の透明性絶縁基板の一主面上に1層以上の第1の金属層よりなる走査線と対向電極とが形成され、

ゲート電極上に1層以上のゲート絶縁層を介して不純物を含まない第1の半導体層が島状に形成され、

ゲート電極上の第1の半導体層上に前記ゲート電極よりも幅細く保護絶縁層が形成され、前記保護絶縁層の一部上と第1の半導体層上とに不純物を含む第2の半導体層と1層以上の第2の金属層との積層よりなるソース配線（信号線）とドレイン配線（絵素電極）とが形成され。20

信号線の電極端子を除いて信号線上に感光性有機絶縁層が形成され、

走査線の電極端子は画像表示部外の領域で走査線上のゲート絶縁層に形成された開口部を含んで形成された第2の半導体層と第2の金属層との積層よりなることを特徴とする。

この構成により請求項8に記載された液晶表示装置と略同一の構成でありながらも製造工程の短いIPS型の液晶表示装置が得られる。20

#### 【0042】

請求項11に記載の液晶表示装置は、同じく

少なくとも第1の透明性絶縁基板の一主面上に1層以上の金属層よりなる走査線と対向電極とが形成され、30

ゲート電極上に1層以上のゲート絶縁層を介して不純物を含まない第1の半導体層が島状に形成され、

ゲート電極上の第1の半導体層上に前記ゲート電極よりも幅細く保護絶縁層が形成され、前記保護絶縁層の一部上と第1の半導体層上とに不純物を含む第2の半導体層と陽極酸化可能な金属層との積層よりなるソース（信号線）とドレイン配線（絵素電極）とが形成され、

信号線の電極端子を除いてソース・ドレイン配線の表面に陽極酸化層が形成され、走査線の電極端子は画像表示部外の領域で走査線上のゲート絶縁層に形成された開口部を含んで形成された第2の半導体層と陽極酸化可能な金属層との積層よりなることを特徴とする。40

この構成により請求項9に記載された液晶表示装置と略同一の構成でありながらも製造工程の短いIPS型の液晶表示装置が得られる。

#### 【0043】

請求項12は請求項4に記載の液晶表示装置の製造方法であって、

少なくとも第1の透明性絶縁基板の一主面上に1層以上の金属層よりなる走査線を形成する工程と、

1層以上のゲート絶縁層と不純物を含まない第1の非晶質シリコン層と保護絶縁層とを順次被着する工程と、

走査線の電極端子形成領域上に開口部を有しゲート電極上の保護絶縁層形成領域の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、50

前記開口部内の保護絶縁層と第1の非晶質シリコン層とゲート絶縁層とを除去して走査線の電極端子形成領域を露出する工程と、

前記感光性樹脂パターンの膜厚を減少して保護絶縁層を露出する工程と、

ゲート電極上にゲート電極よりも幅細く保護絶縁層を残して第1の非晶質シリコン層を露出する工程と、

前記感光性樹脂パターンの除去後、全面に不純物を含む第2の非晶質シリコン層を被着する工程と、

前記保護絶縁層と一部重なるように第2の非晶質シリコン層と1層以上の陽極酸化可能な金属層との積層よりなるソース(信号線)・ドレイン配線を形成する工程と、

ゲート絶縁層上と前記ドレイン配線の一部上に透明導電性の絵素電極と画像表示部外の領域で信号線上に透明導電性の電極端子とを形成する工程と、

前記絵素電極と電極端子との選択的パターン形成に用いられた感光性樹脂パターンをマスクとして絵素電極と電極端子とを保護しながらソース・ドレイン配線を陽極酸化する工程とを有することを特徴とする。

この構成によりエッチング工程と半導体層の島化工程とを1枚のフォトマスクを用いて処理することができて写真食刻工程数の削減が実現する。また絵素電極の形成時にソース・ドレイン配線を陽極酸化することでパシベーション絶縁層の形成を不要とする製造工程の削減もなされる結果、4枚のフォトマスクを用いてTN型の液晶表示装置を作製する事ができる。

#### 【0044】

10

請求項13は請求項5に記載の液晶表示装置の製造方法であって、

少なくとも第1の透明性絶縁基板の一主面上に透明導電層と第1の金属層との積層よりなる走査線と信号線の擬似電極端子と擬似絵素電極とを形成する工程と、プラズマ保護層とゲート絶縁層と不純物を含まない第1の非晶質シリコン層と保護絶縁層とを順次被着する工程と、

走査線と信号線の電極端子形成領域上と擬似絵素電極上とに開口部を有しゲート電極上の保護絶縁層形成領域の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、前記開口部内の保護絶縁層と第1の非晶質シリコン層とゲート絶縁層とプラズマ保護層と第1の金属層とを除去して透明導電性の走査線と信号線の電極端子形成領域と同じく絵素電極とを露出する工程と、

20

前記感光性樹脂パターンの膜厚を減少して保護絶縁層を露出する工程と、

ゲート電極上にゲート電極よりも幅細く保護絶縁層を残して第1の非晶質シリコン層を露出する工程と、

前記感光性樹脂パターンの除去後、全面に不純物を含む第2の非晶質シリコン層を被着する工程と、

1層以上の第2の金属層を被着後、第2の非晶質シリコン層と1層以上の第2の金属層との積層よりなり前記保護絶縁層と一部重なるように信号線の電極端子形成領域を含んでその表面に感光性有機絶縁層を有するソース配線(信号線)と同じく絵素電極を含んでドレン配線とを形成する工程とを有することを特徴とする。

30

この構成により絵素電極と走査線とを1枚のフォトマスクを用いて処理する写真食刻工程数の削減と、エッチング工程と半導体層の島化工程とを1枚のフォトマスクを用いて処理することができて写真食刻工程数の削減が実現する。またソース・ドレン配線の形成時に用いた感光性有機絶縁層をそのまま残すことでパシベーション絶縁層の形成を不要とする製造工程の削減もなされる結果、3枚のフォトマスクを用いてTN型の液晶表示装置を作製する事ができる。

40

#### 【0045】

請求項14は請求項6に記載の液晶表示装置の製造方法であって、

少なくとも第1の透明性絶縁基板の一主面上に透明導電層と第1の金属層との積層よりなる走査線と擬似絵素電極とを形成する工程と、

プラズマ保護層とゲート絶縁層と不純物を含まない第1の非晶質シリコン層と保護絶縁層

50

とを順次被着する工程と、

走査線の電極端子形成領域上と擬似絵素電極上とに開口部を有しゲート電極上の保護絶縁層形成領域の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、

前記開口部内の保護絶縁層と第1の非晶質シリコン層とゲート絶縁層とプラズマ保護層と第1の金属層とを除去して透明導電性の走査線の電極端子形成領域と同じく絵素電極とを露出する工程と、

前記感光性樹脂パターンの膜厚を減少して保護絶縁層を露出する工程と、

ゲート電極上にゲート電極よりも幅細く保護絶縁層を残して第1の非晶質シリコン層を露出する工程と、

前記感光性樹脂パターンの除去後、全面に不純物を含む第2の非晶質シリコン層を被着する工程と、

1層以上の第2の金属層を被着後、前記保護絶縁層と一部重なりソース配線（信号線）と同じく絵素電極を含んでドレイン配線と透明導電性の走査線の電極端子形成領域を含んで走査線の電極端子と信号線の一部よりなる信号線の電極端子とに対応し信号線上の膜厚が他の領域よりも厚い感光性有機絶縁層パターンを形成する工程と、

前記感光性有機絶縁層パターンをマスクとして第2の金属層と第2の非晶質シリコン層と第1の非晶質シリコン層とを選択的に除去して走査線と信号線の電極端子とソース・ドレイン配線とを形成する工程と、

前記感光性有機絶縁層パターンの膜厚を減少して走査線と信号線の電極端子とドレイン配線とを露出する工程とを有することを特徴とする。

この構成により絵素電極と走査線とを1枚のフォトマスクを用いて処理する写真食刻工程数の削減と、エッチストップ層の形成工程と半導体層の島化工程とを1枚のフォトマスクを用いて処理することができて写真食刻工程数の削減が実現する。またソース・ドレイン配線の形成時にハーフトーン露光技術を用いて信号線上にのみ選択的に感光性有機絶縁層を残すことでパシベーション絶縁層の形成を不要とする製造工程の削減もなされる結果、3枚のフォトマスクを用いてTN型の液晶表示装置を作製する事ができる。

#### 【0046】

請求項15は請求項7に記載の液晶表示装置の製造方法であって、

少なくとも第1の透明性絶縁基板の一主面上に透明導電層と金属層との積層よりなる走査線と擬似絵素電極とを形成する工程と、

プラズマ保護層とゲート絶縁層と不純物を含まない第1の非晶質シリコン層と保護絶縁層とを順次被着する工程と、

走査線の電極端子形成領域上と擬似絵素電極上とに開口部を有しゲート電極上の保護絶縁層形成領域の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、

前記開口部内の保護絶縁層と第1の非晶質シリコン層とゲート絶縁層とプラズマ保護層と金属層とを除去して透明導電性の走査線の電極端子形成領域と同じく絵素電極とを露出する工程と、

前記感光性樹脂パターンの膜厚を減少して保護絶縁層を露出する工程と、

ゲート電極上にゲート電極よりも幅細く保護絶縁層を残して第1の非晶質シリコン層を露出する工程と、

前記感光性樹脂パターンの除去後、全面に不純物を含む第2の非晶質シリコン層を被着する工程と、

1層以上の陽極酸化可能な金属層を被着後、前記保護絶縁層と一部重なりソース配線（信号線）と同じく絵素電極を含んでドレイン配線と透明導電性の走査線の電極端子形成領域を含んで走査線の電極端子と信号線の一部よりなる信号線の電極端子とに対応し走査線と信号線の電極端子上の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、前記感光性樹脂パターンをマスクとして陽極酸化可能な金属層と第2の非晶質シリコン層と第1の非晶質シリコン層とを選択的に除去して走査線と信号線の電極端子とソース・ドレイン配線とを形成する工程と、

前記感光性樹脂パターンの膜厚を減少してソース・ドレイン配線を露出する工程と、

10

20

30

40

50

前記電極端子上を保護しながらソース・ドレイン配線を陽極酸化する工程とを有することを特徴とする。

この構成により絵素電極と走査線とを1枚のフォトマスクを用いて処理する写真食刻工程数の削減と、エッチストップ層の形成工程と半導体層の島化工程とを1枚のフォトマスクを用いて処理することができて写真食刻工程数の削減が実現する。またソース・ドレイン配線の形成時にハーフトーン露光技術を用いてソース・ドレイン配線上に選択的に陽極酸化層を形成することでパシベーション絶縁層の形成を不要とする製造工程の削減もなされる結果、3枚のフォトマスクを用いてTN型の液晶表示装置を作製する事ができる。

#### 【0047】

請求項16は請求項8に記載の液晶表示装置の製造方法であって、

少なくとも第1の透明性絶縁基板の一主面上に1層以上の第1の金属層よりなる走査線と対向電極とを形成する工程と、

1層以上のゲート絶縁層と不純物を含まない第1の非晶質シリコン層と保護絶縁層とを順次被着する工程と、

ゲート電極上にゲート電極よりも幅細く保護絶縁層を残して第1の非晶質シリコン層を露出する工程と、

全面に不純物を含む第2の非晶質シリコン層を被着後、走査線の電極端子形成領域上に開口部を形成して前記開口部内の第2の非晶質シリコン層と第1の非晶質シリコン層とゲート絶縁層とを除去して走査線の一部を露出する工程と、

1層以上の第2の金属層を被着後、前記保護絶縁層と一部重なりソース配線（信号線）・ドレイン配線（絵素電極）と前記開口部を含んで走査線の電極端子と信号線の一部よりなる信号線の電極端子とに対応し信号線上の膜厚が他の領域よりも厚い感光性有機絶縁層パターンを形成する工程と、

前記感光性有機絶縁層パターンをマスクとして第2の金属層と第2の非晶質シリコン層と第1の非晶質シリコン層とを選択的に除去して走査線と信号線の電極端子とソース・ドレイン配線とを形成する工程と、

前記感光性有機絶縁層パターンの膜厚を減少して走査線と信号線の電極端子とドレイン配線とを露出する工程とを有することを特徴とする。

この構成によりソース・ドレイン配線の形成時にハーフトーン露光技術を用いて信号線上にのみ選択的に感光性有機絶縁層を残すことでパシベーション絶縁層の形成を不要とする製造工程の削減がなされる結果、4枚のフォトマスクを用いてIPS型の液晶表示装置を作製する事ができる。

#### 【0048】

請求項17は請求項9に記載の液晶表示装置の製造方法であって、

少なくとも第1の透明性絶縁基板の一主面上に1層以上の金属層よりなる走査線と対向電極とを形成する工程と、

1層以上のゲート絶縁層と不純物を含まない第1の非晶質シリコン層と保護絶縁層とを順次被着する工程と、

ゲート電極上にゲート電極よりも幅細く保護絶縁層を残して第1の非晶質シリコン層を露出する工程と、

全面に不純物を含む第2の非晶質シリコン層を被着後、走査線の電極端子形成領域上に開口部を形成して前記開口部内の第2の非晶質シリコン層と第1の非晶質シリコン層とゲート絶縁層とを除去して走査線の一部を露出する工程と、

1層以上の陽極酸化可能な金属層を被着後、前記保護絶縁層と一部重なりソース配線（信号線）・ドレイン配線（絵素電極）と前記開口部を含んで走査線の電極端子と信号線の一部よりなる信号線の電極端子とに対応し走査線と信号線の電極端子上の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、

前記感光性樹脂パターンをマスクとして陽極酸化可能な金属層と第2の非晶質シリコン層と第1の非晶質シリコン層とを選択的に除去して走査線と信号線の電極端子とソース・ドレイン配線とを形成する工程と、

10

20

30

40

50

前記感光性樹脂パターンの膜厚を減少してソース・ドレイン配線を露出する工程と、前記電極端子上を保護しながらソース・ドレイン配線を陽極酸化する工程とを有することを特徴とする。

この構成によりソース・ドレイン配線の形成時にハーフトーン露光技術を用いてソース・ドレイン配線上に選択的に陽極酸化層を形成することでパシベーション絶縁層の形成を不要とする製造工程の削減がなされる結果、4枚のフォトマスクを用いてIPS型の液晶表示装置を作製する事ができる。

#### 【0049】

請求項18は請求項10に記載の液晶表示装置の製造方法であって、

少なくとも第1の透明性絶縁基板の一主面上に1層以上の第1の金属層よりなる走査線と対向電極とを形成する工程と、10

1層以上のゲート絶縁層と不純物を含まない第1の非晶質シリコン層と保護絶縁層とを順次被着する工程と、

走査線の電極端子形成領域上に開口部を有しゲート電極上の保護絶縁層形成領域の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、

前記開口部内の保護絶縁層と第1の非晶質シリコン層とゲート絶縁層とを除去して走査線の一部を露出する工程と、

前記感光性樹脂パターンの膜厚を減少して保護絶縁層を露出する工程と、

ゲート電極上にゲート電極よりも幅細く保護絶縁層を残して第1の非晶質シリコン層を露出する工程と、20

前記感光性樹脂パターンの除去後、全面に不純物を含む第2の非晶質シリコン層を被着する工程と、

1層以上の第2の金属層を被着後、前記保護絶縁層と一部重なりソース配線（信号線）・ドレイン配線（絵素電極）と開口部内の第2の非晶質シリコン層を含んで走査線の電極端子と信号線の一部よりなる信号線の電極端子とに対応し信号線上の膜厚が他の領域よりも厚い感光性有機絶縁層パターンを形成する工程と、

前記感光性有機絶縁層パターンをマスクとして第2の金属層と第2の非晶質シリコン層と第1の非晶質シリコン層とを選択的に除去して走査線と信号線の電極端子とソース・ドレイン配線とを形成する工程と、

前記感光性有機絶縁層パターンの膜厚を減少して走査線と信号線の電極端子とドレイン配線とを露出する工程とを有することを特徴とする。30

この構成によりエッチトップ層の形成工程とゲート絶縁層への開口部形成工程とを同一枚のフォトマスクを用いて処理することができて写真食刻工程数の削減が実現する。またソース・ドレイン配線の形成時にハーフトーン露光技術を用いて信号線上にのみ選択的に感光性有機絶縁層を残すことでパシベーション絶縁層の形成を不要とする製造工程の削減がなされる結果、3枚のフォトマスクを用いてIPS型の液晶表示装置を作製する事ができる。

#### 【0050】

請求項19は請求項11に記載の液晶表示装置の製造方法であって、

少なくとも第1の透明性絶縁基板の一主面上に1層以上の金属層よりなる走査線と対向電極とを形成する工程と、40

1層以上のゲート絶縁層と不純物を含まない第1の非晶質シリコン層と保護絶縁層とを順次被着する工程と、

走査線の電極端子形成領域上に開口部を有しゲート電極上の保護絶縁層形成領域の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、

前記開口部内の保護絶縁層と第1の非晶質シリコン層とゲート絶縁層とを除去して走査線の一部を露出する工程と、

前記感光性樹脂パターンの膜厚を減少して保護絶縁層を露出する工程と、

ゲート電極上にゲート電極よりも幅細く保護絶縁層を残して第1の非晶質シリコン層を露出する工程と、50

前記感光性樹脂パターンの除去後、全面に不純物を含む第2の非晶質シリコン層を被着する工程と、

1層以上の陽極酸化可能な金属層を被着後、前記保護絶縁層と一部重なりソース（信号線）配線・ドレイン配線（絵素電極）と開口部内の第2の非晶質シリコン層を含んで走査線の電極端子と信号線の一部よりなる信号線の電極端子とに対応し走査線と信号線の電極端子上の膜厚が他の領域よりも厚い感光性樹脂パターンを形成する工程と、

前記感光性樹脂パターンをマスクとして陽極酸化可能な金属層と第2の非晶質シリコン層と第1の非晶質シリコン層とを選択的に除去して走査線と信号線の電極端子とソース・ドレイン配線とを形成する工程と、

前記感光性樹脂パターンの膜厚を減少してソース・ドレイン配線を露出する工程と、 10

前記電極端子上を保護しながらソース・ドレイン配線を陽極酸化する工程とを有することを特徴とする。

この構成によりエッチストップ層の形成工程とゲート絶縁層への開口部形成工程とを同一のフォトマスクを用いて処理することができて写真食刻工程数の削減が実現する。またソース・ドレイン配線の形成時にハーフトーン露光技術を用いてソース・ドレイン配線上に選択的に陽極酸化層を形成することでパシベーション絶縁層の形成を不要とする製造工程の削減がなされる結果、3枚のフォトマスクを用いてIPS型の液晶表示装置を作製する事ができる。

### 【0051】

#### 【発明の実施の形態】

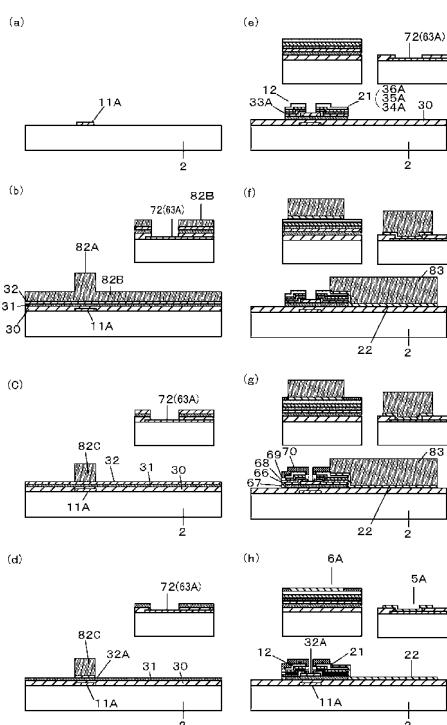

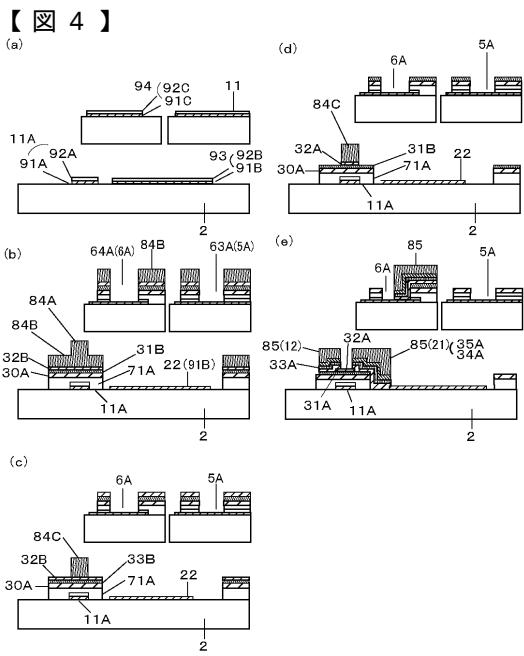

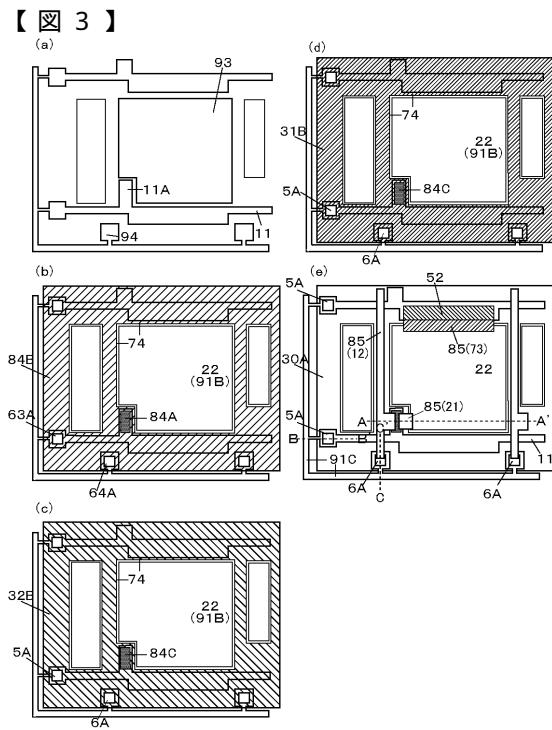

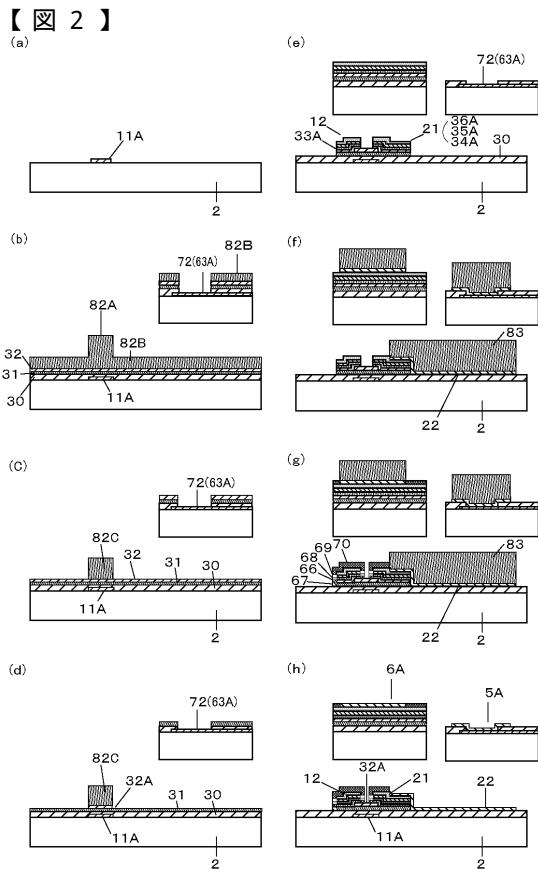

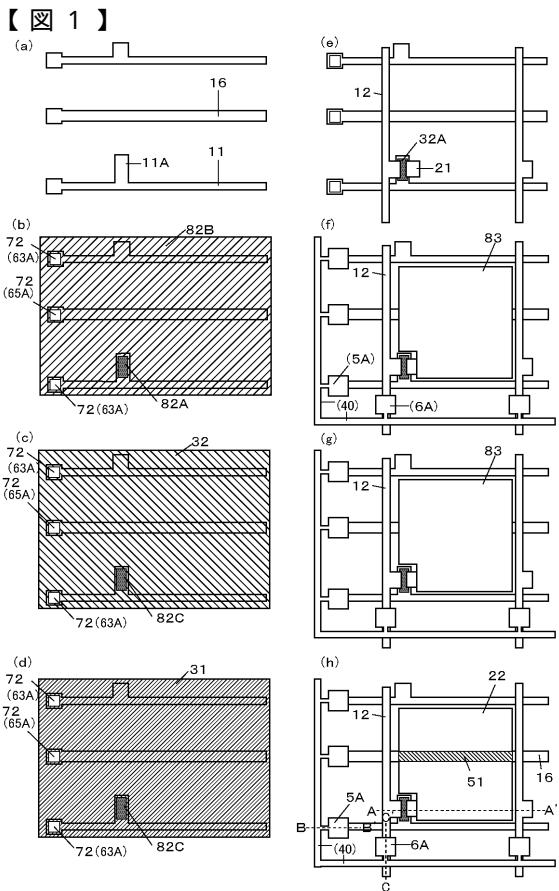

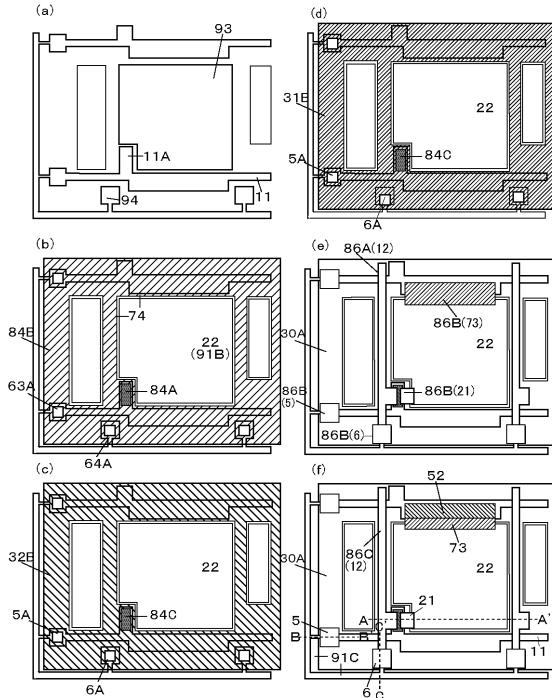

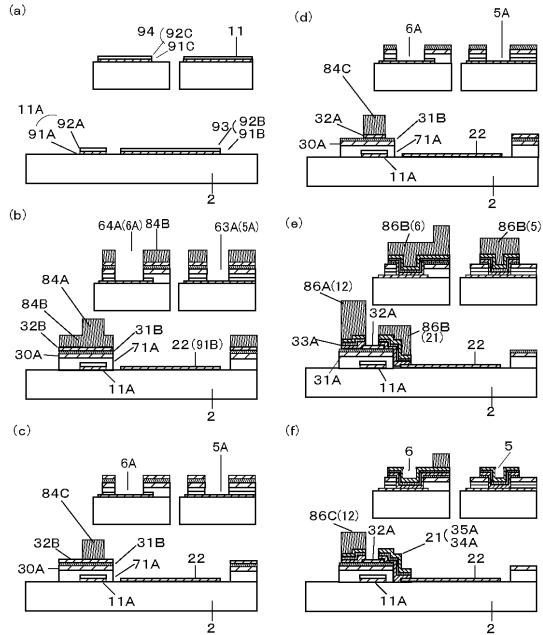

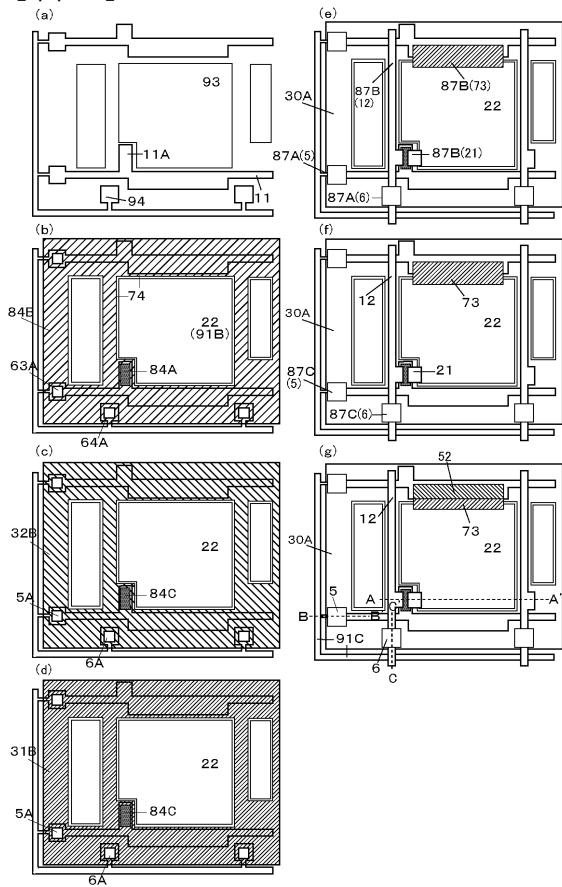

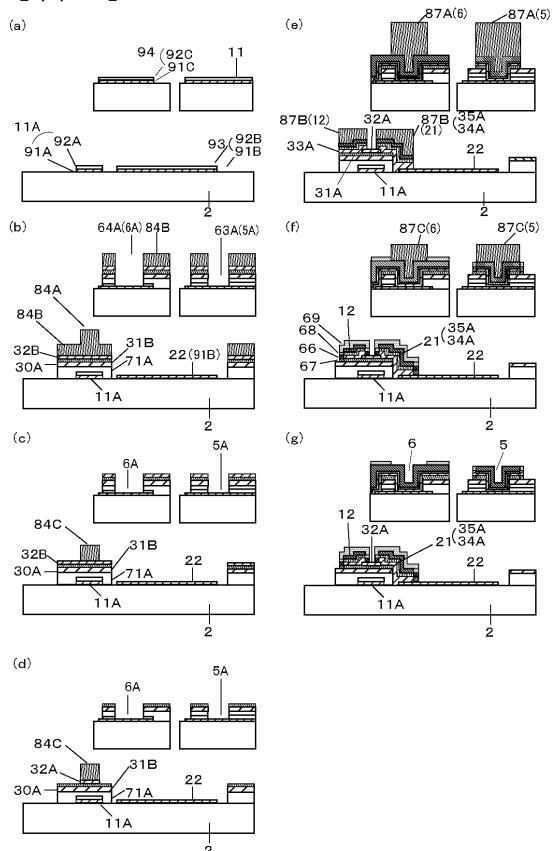

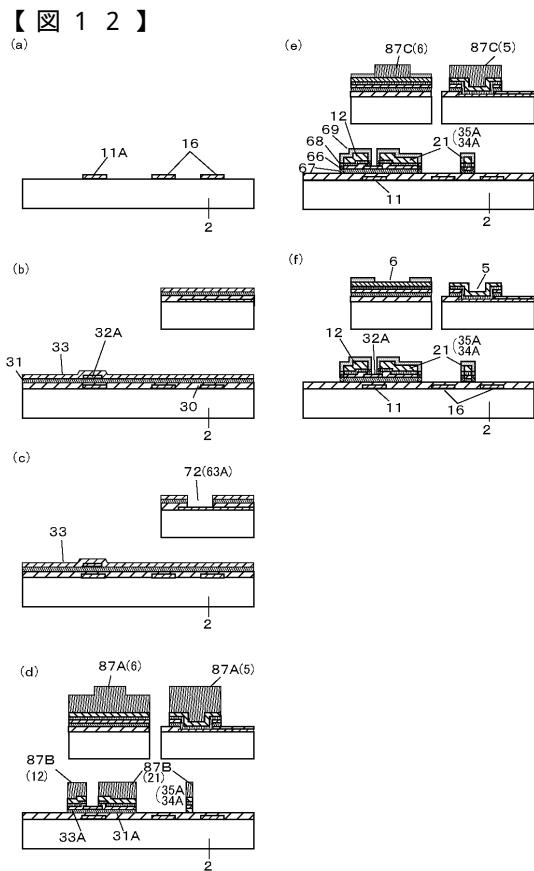

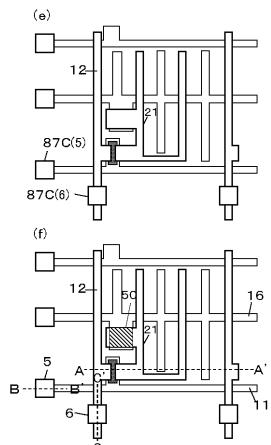

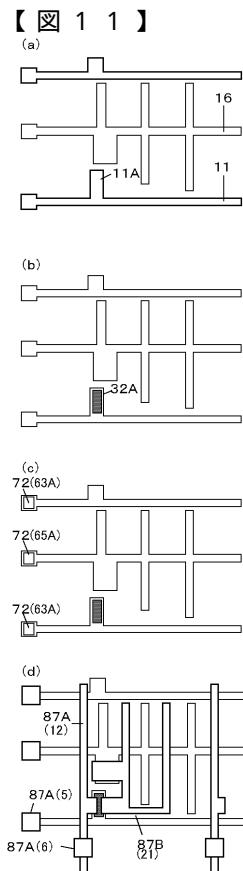

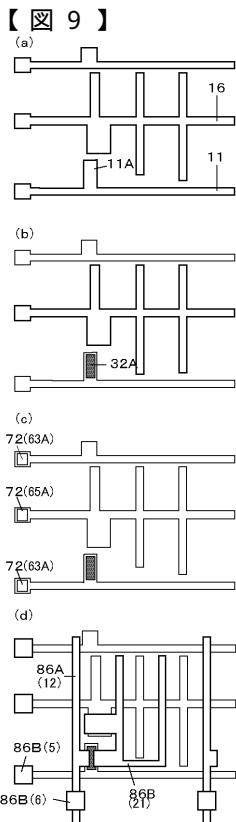

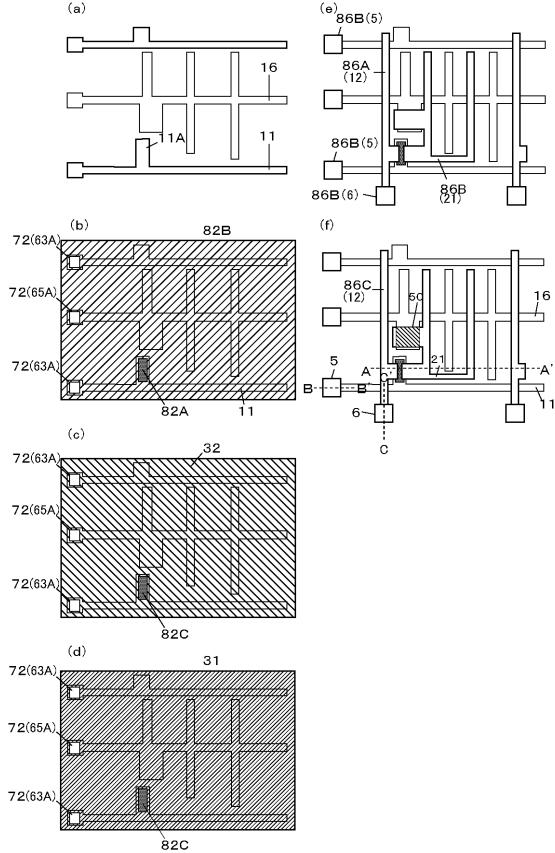

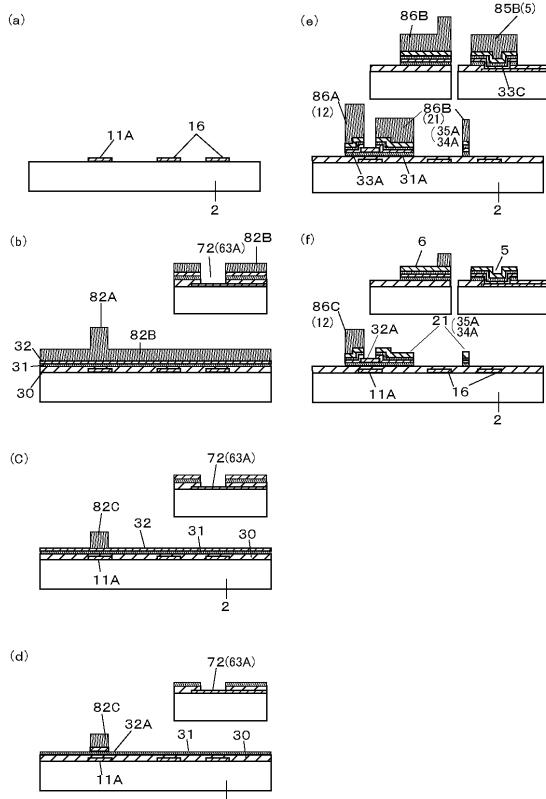

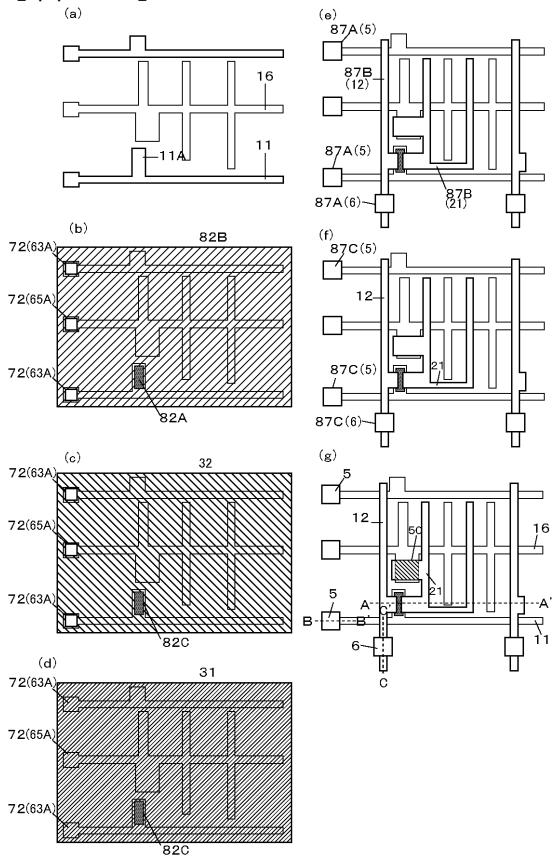

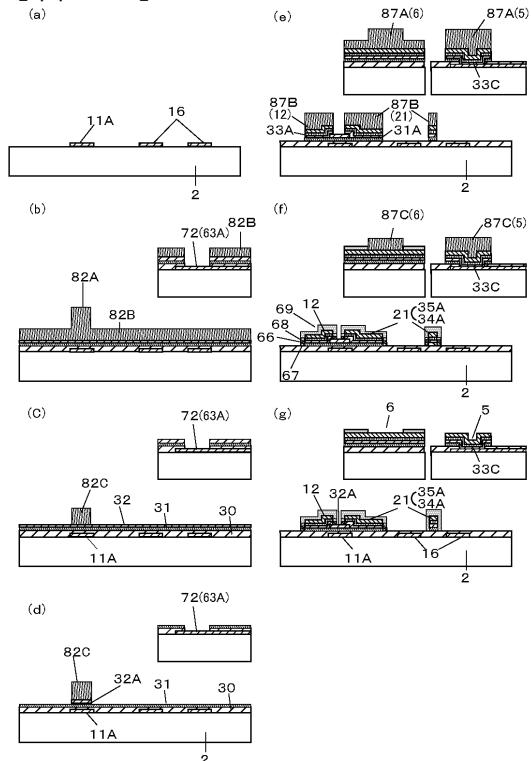

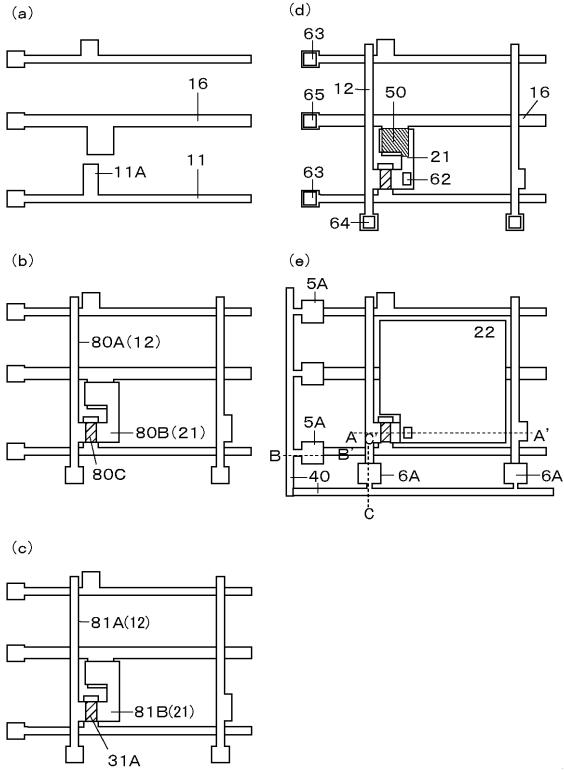

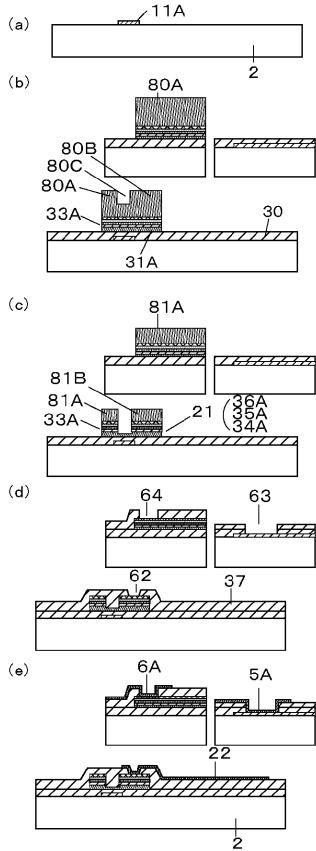

本発明の実施形態を図1～図16に基づいて説明する。図1に本発明の第1の実施形態に係る表示装置用半導体装置（アクティブ基板）の平面図を示し、図2に図1のA-A'線上とB-B'線上及びC-C'線上の製造工程の断面図を示す。同様に第2の実施形態は図3と図4、第3の実施形態は図5と図6、第4の実施形態は図7と図8、第5の実施形態は図9と図10、第6の実施形態は図11と図12、第7の実施形態は図13と図14、第8の実施形態は図15と図16とで夫々アクティブ基板の平面図と製造工程の断面図を示す。なお従来例と同一の部位については同一の符号を付して詳細な説明は省略する。

（第1の実施形態）

### 【0052】

本発明の第1の実施形態について説明する。第1の実施形態では従来例と同様に先ず、図1(a)と図2(a)に示したようにガラス基板2ー主面上にSPT(スパッタ)等の真空製膜装置を用いて膜厚0.1～0.3μm程度の第1の金属層として例えばCr, Ta, Mo等あるいはそれらの合金やシリサイドを被着して微細加工技術によりゲート電極11Aも兼ねる走査線11と共に容量線16とを選択的に形成する。以降の説明で明確になるが本発明においては走査線材料がもたらす制約はほとんど無い。

### 【0053】

次に、ガラス基板2の全面にPCVD装置を用いてゲート絶縁層となる第1のSiNx(シリコン窒化)層30、不純物をほとんど含まず絶縁ゲート型トランジスタのチャネルとなる第1の非晶質シリコン(a-Si)層31、及びチャネルを保護する絶縁層となる第2のSiNx層32と3種類の薄膜層を例えば、0.3-0.05-0.1μm程度の膜厚で順次被着し、そして図1(b)と図2(b)に示したように画像表示部外の領域で走査線11の電極端子形成領域上に開口部63A(共通容量線16の電極端子形成領域上には開口部65A)を有するとともに保護絶縁層形成領域、すなわちゲート電極11A上の領域82Aの膜厚が例えば2μmと他の領域82Bの膜厚1μmよりも厚い感光性樹脂パターン82A, 82Bをハーフトーン露光技術により形成し、感光性樹脂パターン82A, 82Bをマスクとして開口部63A(と開口部65A)内のチャネル保護層である第2のSiNx層32と第1の非晶質シリコン層31とゲート絶縁層である第1のSiNx層30とを選択的に除去して走査線11(と共に容量線16)の一部72を露出する。走査線11の電極端子は最大で駆動用LSIの電極ピッチの半分程度まで、通常20μm以上の大きさを有するので開口部63A(白領域)を形成するためのフォトマスクの作製もそ

10

20

30

40

50

の仕上がり寸法の精度管理も極めて容易である。

#### 【0054】

続いて、酸素プラズマ等の灰化手段により上記感光性樹脂パターン82A, 82Bを1μm以上膜減りさせると感光性樹脂パターン82Bが消失し、図1(c)と図2(c)に示したように第2のSiNx層32が露出すると共に保護絶縁層形成領域上にのみ感光性樹脂パターン82Cを選択的に形成することができる。なお上記酸素プラズマ処理ではパターン寸法の変化を抑制するため異方性を強めることが望ましいが、パターン精度が低い場合はその必要性は少ない。感光性樹脂パターン82C、すなわちエッチトップ層のパターン幅はソース・ドレイン配線間の寸法にマスク合わせ精度を加算したものであるから、ソース・ドレイン配線間を4~6μm、合わせ精度を±3μmとすると10~12μmとなり寸法精度としては厳しいものではない。しかしながらレジストパターン82Aから82Cへの変換時にレジストパターンが等方的に1μm膜減りすると、寸法が2μm小さくなるだけでなく、ソース・ドレイン配線形成時のマスク合わせ精度が1μm小さくなつて±2μmとなり、前者よりも後者の影響がプロセス的には厳しいものとなる。したがって上記酸素プラズマ処理ではパターン寸法の変化を抑制するため異方性を強めることが望ましい。具体的にはRIE(Reactive Ion Etching)方式、さらに高密度のプラズマ源を有するICP(Inductive Coupled Plasma)方式やTCP(Transfer Coupled Plasma)方式の酸素プラズマ処理がより望ましい。そして図1(d)と図2(d)に示したように感光性樹脂パターン82Cをマスクとして第2のSiNx層32をゲート電極11Aよりも幅細く選択的に食刻して第2のSiNx層32Aとともに第1の非晶質シリコン層31を露出する。保護絶縁層形成領域、すなわち感光性樹脂パターン82C(黒領域)の大きさは最小寸法でも10μmの大きさを有し、白領域と黒領域以外の領域をハーフトーン露光領域とするフォトマスクの作製が容易なだけでなく、チャネルエッチ型の絶縁ゲートトランジスタと比較すると絶縁ゲート型トランジスタのON電流を決定するのはチャネル保護絶縁層32Aの寸法であってソース・ドレイン配線12, 21間の寸法ではないことからもプロセス管理がさらに容易となることを理解されたい。具体的には例えばチャネルエッチ型においてソース・ドレイン配線間の寸法が5±1μmとなり、エッチトップ型における保護絶縁層の寸法が10±1μmとなるような同一の現像条件の下ではON電流の変動量は略半減する。この時に露出している走査線11の一部72は保護絶縁層32Aの食刻ガスあるいは薬液に晒されるので走査線11の材質によっては走査線11の一部72の膜減りが生じることには注意が必要であるが、AL合金が露出するようなことがあってもソース・ドレイン配線材として最下層にTiが選択してあれば酸化の影響を回避する事は容易である。その他にも従来例で説明したように走査線11を例えばAL/Ti/ALの積層としておき、上層のTiが消失してもALを除去して下層のTiを露出させる製法も可能である。

#### 【0055】

前記感光性樹脂パターン82Cを除去した後、PCVD装置を用いてガラス基板2の全面に不純物として例えば燐を含む第2の非晶質シリコン層33を例えば0.05μm程度の膜厚で被着した後、SPT等の真空製膜装置を用いて膜厚0.1μm程度の陽極酸化可能な耐熱金属層として例えばTi, Ta等の耐熱金属薄膜層34を、そして膜厚0.3μm程度の同じく陽極酸化可能な低抵抗配線層としてAL薄膜層35を、さらに膜厚0.1μm程度の同じく陽極酸化可能な中間導電層としてTa等の耐熱金属薄膜層36を順次被着する。そしてこれら3層の薄膜よりなるソース・ドレイン配線材と第2の非晶質シリコン層33と第1の非晶質シリコン層31とを微細加工技術により感光性樹脂パターンを用いて順次食刻してゲート絶縁層30を露出し、図1(e)と図2(e)に示したように34A, 35A, 36Aの積層よりなる絶縁ゲート型トランジスタのドレイン電極21とソース電極も兼ねる信号線12とを選択的に形成する。なお、通常はソース・ドレイン配線12, 21の形成と同時に走査線の一部72を含んで走査線の電極端子5を同時に形成するが、ソース・ドレイン配線の材質によっては図示したようにここで電極端子を形成しない

10

20

30

40

50

ことも可能である。ソース・ドレイン配線 12, 21 の構成としては抵抗値の制約が緩いのであれば簡素化して Ta 単層とすることも可能であり、また Nd を添加した Al 合金では化学的電位が下がりアルカリ溶液中でのITOとの化学腐食反応が抑制されるので、この場合には中間導電層 36 が不要となりソース・ドレイン配線 12, 21 の積層構造を 2 層構成とすることが可能で、ソース・ドレイン配線 12, 21 の構成が若干ではあるが簡素化される。

#### 【0056】

ソース・ドレイン配線 12, 21 の形成後、ガラス基板 2 の全面に SPT 等の真空製膜装置を用いて膜厚 0.1 ~ 0.2 μm 程度の透明導電層として例えば ITO を被着し、図 1 (f) と図 2 (f) に示したように微細加工技術によりドレイン電極 21 の中間導電層 36 A の一部を含んでゲート絶縁層 30 上に絵素電極 22 を選択的に形成する。この時、走査線の一部 72 (または電極端子 5) 上と画像表示部外の信号線 12 上にも透明導電層を形成して透明導電性の電極端子 5A, 6A とする。なおここでは従来例と同様に透明導電性の短絡線 40 を設け、電極端子 5A, 6A と短絡線 40 との間を細長いストライプ状に形成することにより高抵抗化して静電気対策用の高抵抗とすることが容易である。

#### 【0057】

引き続き、図 1 (g) と図 2 (g) に示したように絵素電極 22 の選択的パターン形成に用いられた感光性樹脂パターン 83 をマスクとして光を照射しながらソース・ドレイン配線 12, 21 を陽極酸化してその表面に酸化層を形成する。ソース・ドレイン配線 12, 21 の上面には Ta が、また側面には Ta, Al, Ti, 第 2 の非晶質シリコン層 33 A 及び第 1 の非晶質シリコン層 31 A の積層が露出しており、陽極酸化によって第 2 の非晶質シリコン層 33 A は不純物を含む酸化シリコン層 (SiO<sub>2</sub>) 66 に、第 1 の非晶質シリコン層 31 A は不純物を含まない酸化シリコン層 (SiO<sub>2</sub>) 67 に、Ti は半導体である酸化チタン (TiO<sub>2</sub>) 68 に、Al は絶縁層であるアルミナ (Al<sub>2</sub>O<sub>3</sub>) 69 に、そして Ta は絶縁層である 5 酸化タンタル (Ta<sub>2</sub>O<sub>5</sub>) 70 に夫々変質する。酸化チタン層 68 は絶縁層ではないが膜厚が極めて薄く露出面積も小さいのでパシベーション上はまず問題とならないが、耐熱金属薄膜層 34 A も Ta を選択しておくことが望ましい。しかしながら Ta は Ti と異なり下地の表面酸化層を吸収してオーミック接触を容易にする機能に欠ける特性に注意する必要がある。

#### 【0058】

ドレイン配線 21 上にも良好な膜質の陽極酸化層を形成するためには光を照射しながら陽極酸化を実施することが陽極酸化工程の重要なポイントとなることは先行例にも開示されている。具体的には 1 万ルックス程度の十分強力な光を照射して絶縁ゲート型トランジスタのリーク電流が μA を越えればドレイン電極 21 の面積から計算して 10 mA / cm<sup>2</sup> 程度の陽極酸化で良好な膜質を得るための電流密度が得られる。しかしながらドレイン配線 21 上の陽極酸化層の膜質が不十分なものであっても通常、十分な信頼性が得られる理由は液晶セルに印可される駆動信号は基本的に交流であり、対向電極 14 と絵素電極 22 (ドレイン電極 21) との間には直流電圧成分が少なくなるように対向電極 14 の電圧は画像検査時に調整されるので(フリッカ低減調整)、基本原理的には信号線 12 上にのみ直流成分が流れないように絶縁層を形成しておけば良いからである。

#### 【0059】

陽極酸化で形成される 5 酸化タンタル 70、アルミナ 69、酸化チタン 68、酸化シリコン層 66, 67 の各酸化層の膜厚は配線のパシベーションとしては 0.1 ~ 0.2 μm 程度で十分であり、エチレングリコール等の化成液を用いて印可電圧は同じく 100 V 超で実現する。ソース・ドレイン配線 12, 21 の陽極酸化に当たって留意すべき事項は、図示はしないが全ての信号線 12 は電気的に並列または直列に形成されている必要があり、後に続く製造工程の何処かでこの直並列を解除しないとアクティブ基板 2 の電気検査のみならず、液晶表示装置としての実動作に支障があることは言うまでもないだろう。解除手段としてはレーザ光の照射による蒸散、またはスクライプによる機械的切除が簡易的であるが詳細な説明は省略する。

10

20

30

40

50

## 【 0 0 6 0 】

絵素電極 22 を感光性樹脂パターン 83 で覆っておくのは絵素電極 22 を陽極酸化する必要が無いだけでなく、絶縁ゲート型トランジスタを経由してドレイン電極 21 に流れる化成電流を必要以上に大きく確保しなくて済むためである。

## 【 0 0 6 1 】

最後に、前記感光性樹脂パターン 83 を除去して図 1(h) と図 2(h) に示したようにアクティブ基板 2(表示装置用半導体装置)として完成する。このようにして得られたアクティブ基板 2 とカラーフィルタとを貼り合わせて液晶パネル化し、本発明の第 1 の実施形態が完了する。蓄積容量 15 の構成に関しては、図 1(h) に示したように蓄積容量線 16 と絵素電極 22 とがゲート絶縁層 30 を介して平面的に重なることで(右下がり斜線部 51)構成している例を例示しているが、蓄積容量 15 の構成はこれに限られるものではなく、絵素電極 22 と前段の走査線 11 との間にゲート絶縁層 30 を含む絶縁層を介して構成しても良い。またその他の構成も可能であるが詳細な説明は省略する。同様に走査線へのコンタクト形成工程を有するので、透明導電層以外の導電性材料あるいは半導体層を用いて静電気対策を行うことも容易である。

## 【 0 0 6 2 】

第 1 の実施形態では走査線へのコンタクト形成工程とチャネル保護層(エッチトップ層あるいは保護絶縁層)の形成工程というパターン精度の低いレイヤにハーフトーン露光技術を適用して写真食刻工程の削減を行い 4 枚のフォトマスクでアクティブ基板を作製しているが、絵素電極と走査線の形成を 1 枚のフォトマスクで処理することによりさらに工程削減を推進して 3 枚のフォトマスクでアクティブ基板を作製する事が可能であるので、それを第 2 ~ 第 4 の実施形態として説明する。

## (第 2 実施形態)

## 【 0 0 6 3 】

第 2 の実施形態では先ずガラス基板 2 の一主面上に S P T 等の真空製膜装置を用いて膜厚 0.1 ~ 0.2 μm 程度の透明導電層 91 として例えば I T O と、膜厚 0.1 ~ 0.3 μm 程度の第 1 の金属層 92 とを被着し、図 3(a) と図 4(a) に示したように微細加工技術により透明導電層 91A と第 1 の金属層 92A との積層よりなりゲート電極 11A も兼ねる走査線 11 と、透明導電層 91B と第 1 の金属層 92B との積層よりなる擬似絵素電極 93 と、透明導電層 91C と第 1 の金属層 92C との積層よりなる信号線の擬似電極端子 94 とを選択的に形成する。第 1 の金属層として例えば Cr, Ta, Mo 等の高融点金属あるいはそれらの合金やシリサイドが選ばれる。ゲート絶縁層を介して信号線との絶縁耐圧を向上させ、歩留を高めるためにはこれらの電極は乾式食刻(ドライエッチ)による断面形状のテーパ制御を行うことが望ましいが、ITO のドライエッチ技術は食刻ガスに沃化水素や臭化水素を用いたものが開発されたもののガス排気系での反応生成物による堆積量が大きく実用化に至らなかったので、当面は例えば Ar(ガス)を用いたスパッタ・エッチを採用すると良い。

## 【 0 0 6 4 】

次にガラス基板 2 の全面にプラズマ保護層となる透明絶縁層、例えば TaOx や SiO2 を 0.1 μm 程度の膜厚で被着して 71 とする。このプラズマ保護層 71 は後続の P C V D 装置によるゲート絶縁層である SiNx の形成時に走査線 11 と擬似絵素電極 93 のエッジ部に露出している透明導電層 91A, 91B が還元されて SiNx の膜質が変動するのを防止するために必要で、詳細は先行例特開昭 59-9962 号公報を参照されたい。

## 【 0 0 6 5 】

プラズマ保護層 71 の被着後は第 1 の実施形態と同様に、P C V D 装置を用いてゲート絶縁層となる第 1 の SiNx 層 30、不純物をほとんど含まず絶縁ゲート型トランジスタのチャネルとなる第 1 の非晶質シリコン層 31、及びチャネルを保護する絶縁層となる第 2 の SiNx 層 32 と 3 種類の薄膜層を、例えば 0.2 - 0.05 - 0.1 μm 程度の膜厚で順次被着し、擬似絵素電極 93 上に開口部 74 と画像表示部外の領域で走査線 11 の電極端子形成領域上に開口部 63A と擬似電極端子 94 上に開口部 64A を有するとともに

10

20

30

40

50

保護絶縁層形成領域、すなわちゲート電極 11 A 上の領域 84 A の膜厚が例えれば 2 μm と他の領域 84 B の膜厚 1 μm よりも厚い感光性樹脂パターン 84 A, 84 B をハーフトーン露光技術により形成する。ここではゲート絶縁層がプラズマ保護層と第 1 の SiNx 層との積層になるため第 1 の SiNx 層は従来よりも薄く形成して良い。そして感光性樹脂パターン 84 A, 84 B をマスクとして図 3 (b) と図 4 (b) と示したように上記開口部内の第 2 の SiNx 層 32、第 1 の非晶質シリコン層 31、ゲート絶縁層 30、プラズマ保護層 71 に加えて第 1 の金属層 92 をも順次食刻し、走査線 11 の一部の透明導電層を露出して走査線の電極端子 5A とし、同様に擬似電極端子 94 の透明導電層を露出して信号線の電極端子 6A とし、擬似絵素電極 93 の透明導電層 91B を露出して絵素電極 22 とする。

10

## 【0066】

続いて酸素プラズマ等の灰化手段により上記感光性樹脂パターン 84 A, 84 B を 1 μm 以上膜減りさせると感光性樹脂パターン 84 B が消失し、図 3 (c) と図 4 (c) に示したように第 2 の SiNx 層 32B が露出すると共に保護絶縁層形成領域上にのみ感光性樹脂パターン 84 C を選択的に形成することができる。上記酸素プラズマ処理では後続のソース・ドレイン配線形成工程におけるマスク合わせ精度が低下しないように異方性を強めてパターン寸法の変化を抑制することが望ましい。そして図 3 (d) と図 4 (d) に示したように感光性樹脂パターン 84 C をマスクとして第 2 の SiNx 層 32B を選択的に食刻してゲート電極 11 A よりもパターン幅の細い第 2 の SiNx 層 32A とともに第 1 の非晶質シリコン層 31B を露出する。この時に上記開口部 63A 内に露出している透明導電性の走査線の電極端子 5A、信号線の電極端子 6A 及び絵素電極 22 は第 2 の SiNx 層 32B の食刻ガスに晒されるが、弗素系の食刻ガスでこれらの透明導電層の膜厚が減少するとか、抵抗値が変化するとか、透明度が変化すると言った不具合は生じないのは極めて好都合である。

20

## 【0067】

引き続き前記感光性樹脂パターン 84 C を除去した後、PCVD 装置を用いてガラス基板 2 の全面に不純物として例えれば燐を含む第 2 の非晶質シリコン層 33 を例えれば 0.05 μm 程度の膜厚で被着した後、SPT 等の真空製膜装置を用いて膜厚 0.1 μm 程度の耐熱金属層として例えれば Ti, Ta 等の耐熱金属薄膜層 34 を、そして膜厚 0.3 μm 程度の低抵抗配線層として AL 薄膜層 35 を順次被着する。そしてこれら 2 層の薄膜よりなるソース・ドレイン配線材と第 2 の非晶質シリコン層 33 と第 1 の非晶質シリコン層 31B とを微細加工技術により感光性樹脂パターン 85 を用いて順次食刻してゲート絶縁層 30A を露出し、図 3 (e) と図 4 (e) に示したように絵素電極 22 の一部を含んで 34A と 35A との積層よりなる絶縁ゲート型トランジスタのドレイン電極 21 と信号線の電極端子 6A の一部を含んでソース電極も兼ねる信号線 12 とを選択的に形成する。走査線の電極端子 5A と信号線の電極端子 6A はソース・ドレイン配線 12, 21 の食刻が終るとガラス基板 2 上に露出して形成されることが理解されよう。なおソース・ドレイン配線 12, 21 の構成としては抵抗値の制約が緩いのであれば簡素化して Ta, Cr, Mo 等の単層とすることも可能である。

30

## 【0068】

このようにして得られたアクティブ基板 2 とカラーフィルタとを貼り合わせて液晶パネル化し、本発明の第 2 の実施形態が完了する。第 2 の実施形態では感光性樹脂パターン 85 は液晶に接しているので、感光性樹脂パターン 85 はノボラック系の樹脂を主成分とする通常の感光性樹脂ではなく、純度が高く主成分にアクリル樹脂やポリイミド樹脂を含む耐熱性の高い感光性有機絶縁層を用いることが大切であり、材質によっては加熱することで流動化してソース・ドレイン配線 12, 21 の側面を覆うように構成することも可能で、この場合には液晶パネルとして信頼性が一段と向上する。蓄積容量 15 の構成に関しては図 3 (e) に示したように、ソース・ドレイン配線 12, 21 と同時に絵素電極 22 の一部を含んで形成された蓄積電極 73 と前段の走査線 11 に設けられた突起部とがプラズマ保護層 71A とゲート絶縁層 30A を介して平面的に重なることで構成している例（右下

40

50

がり斜線部 52) を例示しているが、蓄積容量 15 の構成はこれに限られるものではなく、第 1 の実施形態と同じように走査線 11 と同時に形成される共通容量線 16 と絵素電極 22 との間にゲート絶縁層 30A を含む絶縁層を介して構成しても良い。またその他の構成も可能であるが詳細な説明は省略する。

#### 【 0069 】

第 2 の実施形態ではこのように走査線の電極端子と信号線の電極端子がともに透明導電層であるデバイス構成上の制約が生ずるが、その制約を解除するデバイス・プロセスも可能であり、それを第 3、第 4 の実施形態として説明する。

#### ( 第 3 の実施形態 )

#### 【 0070 】

第 3 の実施形態では、図 5 (d) と図 6 (d) に示したようにコンタクト形成工程とチャネル保護層(エッチストップ層)の形成工程とまでは第 2 の実施形態とほぼ同一のプロセスで進行する。ただし後述する理由で擬似電極端子 94 は必ずしも必要ではない。その後は感光性樹脂パターン 84C を除去し、PCVD 装置を用いてガラス基板 2 の全面に不純物として例えば燐を含む第 2 の非晶質シリコン層 33 を例えば 0.05 μm 程度の膜厚で被着した後、ソース・ドレイン配線の形成工程では SPT 等の真空製膜装置を用いて膜厚 0.1 μm 程度の耐熱金属層として例えば Ti, Ta 等の耐熱金属薄膜層 34 を、そして膜厚 0.3 μm 程度の低抵抗配線層として AL 薄膜層 35 を順次被着する。そしてこれら 2 層の薄膜よりなるソース・ドレイン配線材と第 2 の非晶質シリコン層 33 と第 1 の非晶質シリコン層 31B を微細加工技術により感光性樹脂パターン 86 を用いて順次食刻してゲート絶縁層 30A を露出し、図 5 (e) と図 6 (e) に示したように絵素電極 22 の一部を含んで 34A と 35A との積層よりなる絶縁ゲート型トランジスタのドレイン電極 21 とソース配線も兼ねる信号線 12 とを選択的に形成し、ソース・ドレイン配線 12, 21 の形成と同時に露出している走査線の電極端子形成領域 5A を含んで走査線の電極端子 5 と信号線の一部よりなる電極端子 6 も同時に形成する。すなわち第 2 の実施形態のように擬似電極端子 94 は必ずしも必要ではない。この時に信号線 12 上の 86A の膜厚が例えば 3 μm とドレイン電極 21 上と電極端子 5, 6 上と蓄積電極 73 上の 86B の膜厚 1.5 μm よりも厚い感光性樹脂パターン 86A, 86B をハーフトーン露光技術により形成しておくことが第 3 の実施形態の重要な特徴である。電極端子 5, 6 に対応した 86B の最小寸法は数 10 μm と大きく、フォトマスク製作もまたその仕上がり寸法管理も極めて容易であるが、信号線 12 に対応した領域 86A の最小寸法は 4 ~ 8 μm と比較的寸法精度が高いのでハーフトーン領域としては細いスリットパターンを必要とする。しかしながら従来例で説明したように 1 回の露光処理と 2 回の食刻処理で形成するソース・ドレイン配線 12, 21 と比較すると本発明のソース・ドレイン配線 12, 21 は 1 回の露光処理と 1 回の食刻処理で形成するためにパターン幅の変動する要因が少なく、ソース・ドレイン配線 12, 21 の寸法管理も、ソース・ドレイン配線 12, 21 間すなわちチャネル長の寸法管理も従来のハーフトーン露光技術よりはパターン精度の管理が容易である。またチャネルエッチ型の絶縁ゲートトランジスタと比較すると絶縁ゲート型トランジスタの ON 電流を決定するのはチャネル保護絶縁層 32A の寸法であってソース・ドレイン配線 12, 21 間の寸法ではないことからもプロセス管理がさらに容易となることを理解されたい。

#### 【 0071 】

ソース・ドレイン配線 12, 21 の形成後、酸素プラズマ等の灰化手段により上記感光性樹脂パターン 86A, 86B を 1.5 μm 以上膜減りさせると感光性樹脂パターン 86B が消失し、図 5 (f) と図 6 (f) に示したようにドレイン電極 21 と電極端子 5, 6 が露出すると共に信号線 12 上にのみ感光性樹脂パターン 86C を選択的に形成することができるが、上記酸素プラズマ処理で感光性樹脂パターン 86C のパターン幅が細くなると信号線 12 の上面が露出して信頼性が低下するので異方性を強めてパターン寸法の変化を抑制することが望ましい。なおソース・ドレイン配線 12, 21 の構成としては抵抗値の制約が緩いのであれば簡素化して Ta, Cr, Mo 等の単層とすることも可能である。

10

20

30

40

50

## 【0072】

このようにして得られたアクティブ基板2とカラーフィルタとを貼り合わせて液晶パネル化し、本発明の第3の実施形態が完了する。第3の実施形態でも感光性樹脂パターン86Cは液晶に接しているので感光性樹脂パターン86Cはノボラック系の樹脂を主成分とする通常の感光性樹脂ではなく、純度が高く主成分にアクリル樹脂やポリイミド樹脂を含む耐熱性の高い感光性有機絶縁層を用いることが大切であり、材質によっては加熱することで流動化して信号線12の側面を覆うように構成することも可能で、この場合には液晶パネルとして信頼性が一段と向上する。蓄積容量15の構成に関しては図5(f)に示したように、ソース・ドレイン配線12, 21と同時に絵素電極22の一部を含んで形成された蓄積電極73と前段の走査線11に設けられた突起部とがプラズマ保護層71Aとゲート絶縁層30Aを介して平面的に重なることで構成している例(右下がり斜線部52)を例示している。なお、電極端子形成領域5A及び信号線12下に形成された透明導電性のパターン6A(擬似電極端子91C)と短絡線40とを接続する透明導電層パターンはその形状を細長い線状とすることで静電気対策における高抵抗配線とすることが可能であるが、その他の導電性部材を用いた静電気対策も勿論可能である。

10

## 【0073】

本発明の第3の実施形態では信号線12上のみに有機絶縁層を形成してドレイン電極21は導電性を保ったまま露出しているが、これでも十分な信頼性が得られる理由は液晶セルに印可される駆動信号は基本的に交流であり、対向電極14と絵素電極22(ドレイン電極21)との間には直流電圧成分が少なくなるように対向電極14の電圧は画像検査時に調整されるので(フリッカ低減調整)、従って信号線12上にのみ直流成分が流れないように絶縁層を形成しておけば良いからである。

20

## 【0074】

本発明の第2と第3の実施形態では有機絶縁層を夫々ソース・ドレイン配線上と信号線上にのみ形成することで製造工程の削減を推進しているが、有機絶縁層の厚みが通常は1μm以上あるのでラビング布を用いた配向膜の配向処理でその段差が非配向状態をもたらす、あるいは液晶セルのギャップ精度の確保に支障が出る恐れもある。そこで第4の実施形態では最小限度の工程数の追加で有機絶縁層に変わるパシベーション技術を具備させるものである。

30

## (第4の実施形態)

## 【0075】

第4の実施形態では、図7(d)と図8(d)に示したようにコンタクト形成工程とチャネル保護層(エッチストップ層)の形成工程までは第2、第3の実施形態とほぼ同一のプロセスで進行する。感光性樹脂パターン84Cを除去した後、PCVD装置を用いてガラス基板2の全面に不純物として例えば燐を含む第2の非晶質シリコン層33を例えば0.05μm程度の膜厚で被着した後、ソース・ドレイン配線の形成工程ではSPT等の真空製膜装置を用いて膜厚0.1μm程度の陽極酸化可能な耐熱金属層として例えばTi, Ta等の耐熱金属薄膜層34を、そして膜厚0.3μm程度の同じく陽極酸化可能な低抵抗配線層としてAL薄膜層35を順次被着する。そしてこれら2層の薄膜よりなるソース・ドレイン配線材と第2の非晶質シリコン層33と第1の非晶質シリコン層31Bとを微細加工技術により感光性樹脂パターン87を用いて順次食刻してゲート絶縁層30Aを露出し、図7(e)と図8(e)に示したように絵素電極22の一部を含んで34Aと35Aの積層よりなる絶縁ゲート型トランジスタのドレイン電極21とソース配線も兼ねる信号線12とを選択的に形成し、ソース・ドレイン配線12, 21の形成と同時に露出している走査線の電極端子形成領域5Aを含んで走査線の電極端子5と信号線の一部よりなる電極端子6も形成する。この時に電極端子5, 6上の87Aの膜厚(黒領域)が例えば3μmとソース・ドレイン配線12, 21と蓄積電極73に対応した領域87B(中間調領域)の膜厚1.5μmよりも厚い感光性樹脂パターン87A, 87Bをハーフトーン露光技術により形成しておくことが第4の実施形態の重要な特徴である。

40

## 【0076】

50

ソース・ドレイン配線 12, 21 の形成後、酸素プラズマ等の灰化手段により上記感光性樹脂パターン 87A, 87B を 1.5 μm 以上膜減りさせると感光性樹脂パターン 87B が消失してソース・ドレイン配線 12, 21 と蓄積電極 73 が露出すると共に電極端子 5, 6 上にのみ感光性樹脂パターン 87C を選択的に形成することができる。上記酸素プラズマ処理で感光性樹脂パターン 87C のパターン幅が細くなても大きなパターン寸法を有する電極端子 5, 6 の周囲に陽極酸化層が形成されるだけで、電気特性と歩留及び品質に与える影響は殆ど無いのは特筆すべき特徴である。そして感光性樹脂パターン 87C をマスクとして光を照射しながら図 7(f) と図 8(f) に示したようにソース・ドレイン配線 12, 21 を陽極酸化して酸化層 68, 69 を形成するとともにソース・ドレイン配線 12, 21 の下側面に露出している第 2 の非晶質シリコン層 33A と第 1 の非晶質シリコン層 31A を陽極酸化して絶縁層である酸化シリコン層 (SiO<sub>2</sub>) 66, 67 を形成する。

10

20

30

40

## 【0077】

陽極酸化終了後、感光性樹脂パターン 87C を除去すると図 7(g) と図 8(g) に示したようにその側面に陽極酸化層を形成された低抵抗薄膜層よりなる電極端子 5, 6 が露出する。走査線の電極端子 6 の側面は静電気対策用の高抵抗短絡線 91C を経由して陽極酸化電流が流れるので信号線の電極端子 5 と比べると側面に形成された絶縁層の厚みは薄くなることを理解されたい。なおソース・ドレイン配線 12, 21 の構成としては抵抗値の制約が緩いのであれば簡素化して陽極酸化可能な Ta 単層とすることも可能である。このようにして得られたアクティブ基板 2 とカラーフィルタとを貼り合わせて液晶パネル化し、本発明の第 4 の実施形態が完了する。蓄積容量 15 の構成に関しては図 7(g) に示したように、ソース・ドレイン配線 12, 21 と同時に絵素電極 22 の一部を含んで形成された蓄積電極 73 と前段の走査線 11 に設けられた突起部とがプラズマ保護層 71A とゲート絶縁層 30A を介して平面的に重なることで構成している例(右下がり斜線部 52)を例示している。

20

## 【0078】

第 4 の実施形態ではこのように、ソース・ドレイン配線 12, 21 と第 2 の非晶質シリコン層 33A 及び第 1 の非晶質シリコン層 31A の陽極酸化時にドレイン電極 21 と電気的に繋がっている絵素電極 22 も露出しているために絵素電極 22 も同時に陽極酸化される点が第 1 の実施形態と大きく異なる。このため絵素電極 22 を構成する透明導電層の膜質によっては陽極酸化によって抵抗値の増大することもあり、その場合には透明導電層の製膜条件を適宜変更して酸素不足の膜質としておく必要があるが陽極酸化で透明導電層の透明度が低下することはない。また、ドレイン電極 21 と絵素電極 22 を陽極酸化するための電流も絶縁ゲート型トランジスタのチャネルを通って供給されるが、絵素電極 22 の面積が大きいために大きな化成電流または長時間の化成が必要となり、いくら強い外光を照射してもチャネル部の抵抗が障害となり、ドレイン電極 21 と蓄積電極 73 上に信号線 12 上と同等の膜質と膜厚の陽極酸化層を形成することは化成時間の延長だけでは対応困難である。しかしながらドレイン配線 21 上に形成される陽極酸化層が多少不完全であっても実用上は支障の無い信頼性が得られることが多い。なぜならば先述したように液晶セルに印可される駆動信号は基本的に交流であり、対向電極 14 と絵素電極 22 (ドレイン電極 21)との間には直流電圧成分が少なくなるように対向電極 14 の電圧は画像検査時に調整されるからで(フリッカ低減調整)、従って信号線 12 上にのみ直流成分が流れないように絶縁層を形成しておけば良いからである。

30

40

## 【0079】

以上説明した液晶表示装置は TN 型の液晶セルを用いたものであったが、絵素電極とは所定の距離を隔てて形成された一対の対向電極と絵素電極とで横方向の電界を制御する IPS (In-Plane-Switching) 方式の液晶表示装置においても本発明で提案する工程削減は有用であるので、それを以降の実施形態で説明する。

(第 5 の実施形態)

## 【0080】

50

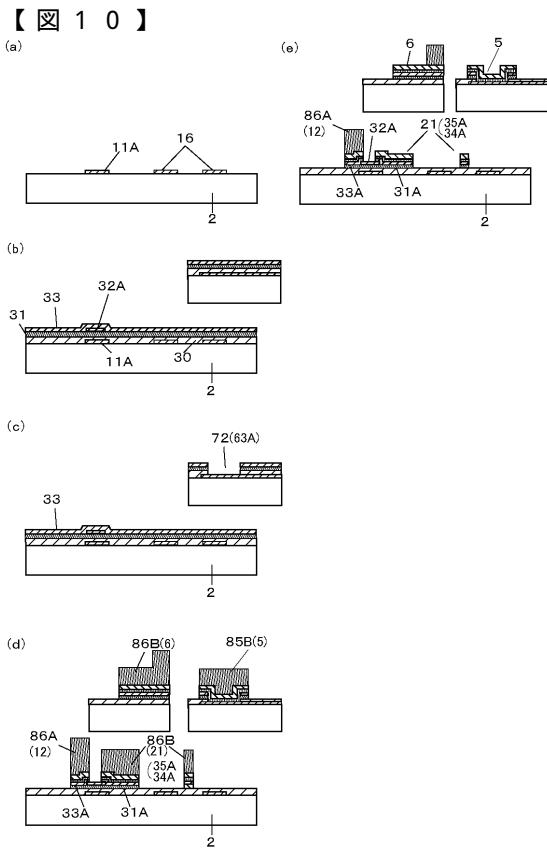

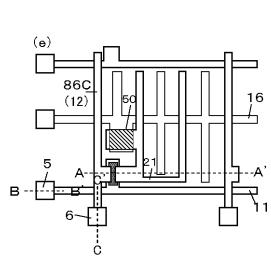

第5の実施形態では先ずガラス基板2の一主面上にSPT等の真空製膜装置を用いて膜厚0.1~0.3μm程度の第1の金属層を被着して図9(a)と図10(a)に示したように微細加工技術によりゲート電極11Aも兼ねる走査線11と対向電極16とを選択的に形成する。

#### 【0081】

次にガラス基板2の全面にPCVD装置を用いてゲート絶縁層となる第1のSiNx(シリコン窒化)層30、不純物をほとんど含まず絶縁ゲート型トランジスタのチャネルとなる第1の非晶質シリコン(a-Si)層31、及びチャネルを保護する絶縁層となる第2のSiNx層32と3種類の薄膜層を例えば、0.3-0.05-0.1μm程度の膜厚で順次被着し、図9(b)に示したように微細加工技術によりゲート電極11A上の第2のSiNx層をゲート電極11Aよりも幅細く選択的に残して32Aとして第1の非晶質シリコン層31を露出する。そして図10(b)に示したようにPCVD装置を用いてガラス基板2の全面に不純物として例えば燐を含む第2の非晶質シリコン層33を例えば0.05μm程度の膜厚で被着する。

#### 【0082】

続いて微細加工技術により図9(c)と図10(c)に示したように画像表示部外の領域で走査線11の電極端子形成領域に開口部63A(と蓄積容量線も兼ねる対向電極16の電極端子形成領域では65A)を形成し、開口部63A内の第2の非晶質シリコン層33と第1の非晶質シリコン層31とゲート絶縁層30とを選択的に除去して走査線11の一部72を露出する。

#### 【0083】

引き続きガラス基板2の全面にSPT等の真空製膜装置を用いて膜厚0.1μm程度の耐熱金属層として例えばTi,Ta等の耐熱金属薄膜層34を、そして膜厚0.3μm程度の低抵抗配線層としてAL薄膜層35を順次被着する。そしてこれら2層の薄膜よりなるソース・ドレイン配線材と第2の非晶質シリコン層33と第1の非晶質シリコン層31とを微細加工技術により感光性樹脂パターン86A,86Bを用いて順次食刻してゲート絶縁層30を露出し、図9(d)と図10(d)に示したようにゲート絶縁層30上に34Aと35Aとの積層よりなり絵素電極となる絶縁ゲート型トランジスタのドレイン電極21とソース配線も兼ねる信号線12とを選択的に形成し、ソース・ドレイン配線12,21の形成と同時に開口部63A内の露出している走査線11の一部72を含んで走査線の電極端子5と信号線12の一部よりなる電極端子6も同時に形成する。この時、第3の実施形態と同様に信号線12上の86Aの膜厚が例えば3μmとドレイン電極21上と電極端子5,6上との86Bの膜厚1.5μmよりも厚い感光性樹脂パターン86A,86Bをハーフトーン露光技術により形成している。

#### 【0084】

ソース・ドレイン配線12,21の形成後、酸素プラズマ等の灰化手段により上記感光性樹脂パターン86A,86Bを1.5μm以上膜減りさせると感光性樹脂パターン86Bが消失し、図9(e)と図10(e)に示したようにドレイン配線21と電極端子5,6が露出すると共に信号線12上にのみ感光性樹脂パターン86Cを選択的に形成することができる。上記酸素プラズマ処理で感光性樹脂パターン86Cのパターン幅が細くならないよう異方性を強めてパターン寸法の変化を抑制することが望ましいこと既に述べた通りである。なおここでもソース・ドレイン配線12,21の構成としては抵抗値の制約が緩いのであれば簡素化してTa,Cr,Mo等の単層とすることも可能である。

#### 【0085】

このようにして得られたアクティブ基板2とカラーフィルタとを貼り合わせて液晶パネル化し、本発明の第5の実施形態が完了する。感光性樹脂パターン86Cにはノボラック系の樹脂を主成分とする通常の感光性樹脂ではなく、純度が高く主成分にアクリル樹脂やポリイミド樹脂を含む耐熱性の高い感光性有機絶縁層を用いる必然性があることも既に説明した通りである。蓄積容量15の構成に関しては図9(e)に示したように対向電極(蓄積容量線)16と絵素電極(ドレイン電極)21とがゲート絶縁層30を介して重なって

10

20

30

40

50

いる領域 5 0 (右下がり斜線部) が蓄積容量 1 5 を構成する場合を例示しており、ドレイン電極 2 1 と前段の走査線 1 1 とがゲート絶縁層 3 0 を介して蓄積容量 1 5 を構成することも可能であるが、ここではその詳細な説明は省略する。なお、図 9 (e) において走査線の電極端子 5 と信号線の電極端子 6 との間を高抵抗性部材で、IPS 型液晶表示装置の場合透明導電層が不要なので走査線材料、信号線材料および半導体層の何れかを用いて OFF 状態の絶縁ゲート型トランジスタや細長い導電性線路で接続する静電気対策や設計技術は特に図示しなかったが、開口部 6 3 A が設けられ走査線 1 1 の一部 7 2 を露出する工程が付与されているので静電気対策は容易であることを補足しておく。

#### 【 0 0 8 6 】

本発明の第 5 の実施形態では有機絶縁層を信号線上にのみ選択的に形成することで製造工程の削減を推進しているが、有機絶縁層の厚みが 1  $\mu\text{m}$  以上あるので液晶セルのギャップ精度の確保に支障が出る恐れもある。そこで第 6 の実施形態では最小限度の工程数の追加で有機絶縁層に代わるパシベーション技術を提供するものである。

#### ( 第 6 の実施形態 )

#### 【 0 0 8 7 】

第 6 の実施形態では、図 1 1 (c) と図 1 2 (c) に示したように走査線 1 1 の電極端子形成領域に開口部 6 3 A を形成して走査線 1 1 の一部 7 2 を露出するまでは第 5 の実施形態とほぼ同一のプロセスで進行する。引き続きソース・ドレイン配線の形成工程では SPT 等の真空製膜装置を用いて膜厚 0.1  $\mu\text{m}$  程度の陽極酸化可能な耐熱金属層として例えば Ti, Ta 等の耐熱金属薄膜層 3 4 を、そして膜厚 0.3  $\mu\text{m}$  程度の同じく陽極酸化可能な低抵抗配線層として Al 薄膜層 3 5 を順次被着する。そしてこれら 2 層の薄膜よりなるソース・ドレイン配線材と第 2 の非晶質シリコン層 3 3 と第 1 の非晶質シリコン層 3 1 とを微細加工技術により感光性樹脂パターン 8 7 A, 8 7 B を用いて順次食刻してゲート絶縁層 3 0 を露出し、図 1 1 (d) と図 1 2 (d) に示したようにゲート絶縁層 3 0 上に 3 4 A と 3 5 A との積層よりなり絵素電極となる絶縁ゲート型トランジスタのドレイン電極 2 1 とソース配線も兼ねる信号線 1 2 とを選択的に形成し、ソース・ドレイン配線 1 2, 2 1 の形成と同時に開口部 6 3 A 内に露出している走査線 1 1 の一部 7 2 を含んで走査線の電極端子 5 と信号線の一部よりなる電極端子 6 も同時に形成する。この時、電極端子 5, 6 上の 8 7 A の膜厚 (黒領域) が例えば 3  $\mu\text{m}$  とソース・ドレイン配線 1 2, 2 1 に対応した領域 8 7 B (中間調領域) の膜厚 1.5  $\mu\text{m}$  よりも厚い感光性樹脂パターン 8 7 A, 8 7 B をハーフトーン露光技術により形成しておくことが第 6 の実施形態の重要な特徴である。

#### 【 0 0 8 8 】

ソース・ドレイン配線 1 2, 2 1 の形成後、酸素プラズマ等の灰化手段により上記感光性樹脂パターン 8 7 A, 8 7 B を 1.5  $\mu\text{m}$  以上膜減りさせると感光性樹脂パターン 8 7 B が消失してソース・ドレイン配線 1 2, 2 1 が露出すると共に電極端子 5, 6 上にのみ感光性樹脂パターン 8 7 C を選択的に形成することができる。そこで感光性樹脂パターン 8 7 C をマスクとして光を照射しながら図 1 1 (e) と図 1 2 (e) に示したようにソース・ドレイン配線 1 2, 2 1 を陽極酸化して酸化層 6 8, 6 9 を形成するとともにソース・ドレイン配線 1 2, 2 1 の下側面に露出している第 2 の非晶質シリコン層 3 3 A と第 1 の非晶質シリコン層 3 1 A を陽極酸化して絶縁層である酸化シリコン層 (SiO<sub>2</sub>) 6 6, 6 7 を形成する。

#### 【 0 0 8 9 】

陽極酸化終了後、感光性樹脂パターン 8 7 C を除去すると図 1 1 (f) と図 1 2 (f) に示したように低抵抗薄膜層よりなる電極端子 5, 6 が露出する。なおここでもソース・ドレイン配線 1 2, 2 1 の構成としては抵抗値の制約が緩いのであれば簡素化して陽極酸化可能な Ta 単層とすることも可能である。このようにして得られたアクティブ基板 2 とカラーフィルタとを貼り合わせて液晶パネル化し、本発明の第 6 の実施形態が完了する。蓄積容量 1 5 の構成に関しては図 1 1 (f) に示したように対向電極 (蓄積容量線) 1 6 と絵素電極 2 1 (ドレイン電極) 2 1 とがゲート絶縁層 3 0 を介して重なっている領域 5 0

10

20

30

40

50

(右下がり斜線部)が蓄積容量15を構成する場合を例示している。また図11(f)と図12(f)においては走査線の電極端子5と信号線の電極端子6との間を高抵抗性部材で接続する静電気対策は特に図示しなかったので信号線12の電極端子6はソース・ドレイン配線12, 21とは異なり側面にのみ絶縁層である陽極酸化層が形成され、走査線11の電極端子5の側面には陽極酸化層は形成されていないが、既に述べたように開口部63Aが設けられ走査線11の一部72を露出する工程が付与されているので静電気対策は容易であり、静電気対策を実施した場合には走査線11の電極端子5の側面にも薄い陽極酸化層が形成されることを説明を要しない。

#### 【0090】

第5と第6の実施形態ではソース・ドレイン配線の形成にあたり、ハーフトーン露光技術を適用することで新規なパシベーション形成を行うと共に工程削減を推進して4枚のフォトマスクで液晶表示装置の作製を実現しているが、第1～第4の実施形態と同様にエッチストップ層の形成工程とゲート絶縁層の開口部形成工程とにハーフトーン露光技術を適用することで3枚のフォトマスクで液晶表示装置を作製する事が可能となり、さらなる製造工程の削減が見込まれるのでそれを第7と第8の実施形態で説明する。10

#### (第7の実施形態)

#### 【0091】

第7の実施形態では先ずガラス基板2の一主面上にSPT等の真空製膜装置を用いて膜厚0.1～0.3μm程度の第1の金属層を被着して図13(a)と図14(a)に示したように微細加工技術によりゲート電極11Aも兼ねる走査線11と対向電極16とを選択的に形成する。20

#### 【0092】

次に、ガラス基板2の全面にPCVD(プラズマ・シープライディ)装置を用いてゲート絶縁層となる第1のSiNx(シリコン窒化)層30、不純物をほとんど含まず絶縁ゲート型トランジスタのチャネルとなる第1の非晶質シリコン(a-Si)層31、及びチャネルを保護する絶縁層となる第2のSiNx層32と3種類の薄膜層を例えば、0.3-0.05-0.1μm程度の膜厚で順次被着し、画像表示部外の領域で走査線11の電極端子形成領域上に開口部63Aを有するとともに保護絶縁層形成領域、すなわちゲート電極11A上の領域82Aの膜厚が例えば2μmと他の領域82Bの膜厚1μmよりも厚い感光性樹脂パターン82A, 82Bをハーフトーン露光技術により形成し、感光性樹脂パターン82A, 82Bをマスクとして図13(b)と図14(b)とに示したように開口部63A内の第2のSiNx層32と第1の非晶質シリコン層31とゲート絶縁層30とを選択的に除去して走査線11の一部72を露出する。30

#### 【0093】

続いて酸素プラズマ等の灰化手段により上記感光性樹脂パターン82A, 82Bを1μm以上膜減りさせると感光性樹脂パターン82Bが消失し、図13(c)と図14(c)に示したように第2のSiNx層32が露出すると共に保護絶縁層形成領域上にのみ感光性樹脂パターン82Cを選択的に形成することができる。上記酸素プラズマ処理ではパターン寸法の変化を抑制するため異方性を強めることは既に述べた通りである。そして図13(d)と図14(d)に示したように感光性樹脂パターン82Cをマスクとして第2のSiNx層32を選択的に食刻してゲート電極11Aよりも幅の細い第2のSiNx層32Aとするとともに第1の非晶質シリコン層31を露出する。この時に露出している走査線11の一部72は第2のSiNx層32の食刻ガスあるいは食刻薬液に晒されるので、走査線11の材質によっては走査線11の一部72の膜減りが生じることには注意が必要であるが、その対策も既に述べた通りである。40

#### 【0094】

引き続き前記感光性樹脂パターン82Cを除去し、PCVD装置を用いてガラス基板2の全面に不純物として例えば燐を含む第2の非晶質シリコン層33を例えば0.05μm程度の膜厚で被着した後、ガラス基板2の全面にSPT等の真空製膜装置を用いて膜厚0.1μm程度の耐熱金属層として例えばTi, Ta等の耐熱金属薄膜層34を、そして膜厚50

0.3 μm 程度の低抵抗配線層として AL 薄膜層 35 を順次被着する。そしてこれら 2 層の薄膜よりなるソース・ドレイン配線材と第 2 の非晶質シリコン層 33 と第 1 の非晶質シリコン層 31 とを微細加工技術により感光性樹脂パターン 86A, 86B を用いて順次食刻してゲート絶縁層 30 を露出し、ゲート絶縁層 30 上に 34A と 35A との積層よりなり絵素電極となる絶縁ゲート型トランジスタのドレイン電極 21 とソース配線も兼ねる信号線 12 とを選択的に形成し、ソース・ドレイン配線 12, 21 の形成と同時に開口部 63A 近傍の第 2 の非晶質シリコン層 33C を含んで走査線の電極端子 5 と信号線 12 の一部よりなる電極端子 6 も同時に形成する。この時、第 3 の実施形態と同様に信号線 12 上の 86A の膜厚が例えば 3 μm とドレイン電極 21 上と電極端子 5, 6 上の 86B の膜厚 1.5 μm よりも厚い感光性樹脂パターン 86A, 86B をハーフトーン露光技術により形成している。

10

#### 【0095】

ソース・ドレイン配線 12, 21 の形成後、酸素プラズマ等の灰化手段により上記感光性樹脂パターン 86A, 86B を 1.5 μm 以上膜減りさせると感光性樹脂パターン 86B が消失し、図 13(f) と図 14(f) に示したようにドレイン電極 21 と電極端子 5, 6 が露出すると共に信号線 12 上にのみ感光性樹脂パターン 86C を選択的に形成することができる。上記酸素プラズマ処理で感光性樹脂パターン 86C のパターン幅が細くならないよう異方性を強めてパターン寸法の変化を抑制することが望ましいことは既に述べた通りである。なおここでもソース・ドレイン配線 12, 21 の構成としては抵抗値の制約が緩いのであれば簡素化して Ta, Cr, Mo 等の单層とすることも可能である。

20

#### 【0096】

このようにして得られたアクティブ基板 2 とカラーフィルタを貼り合わせて液晶パネル化し、本発明の第 7 の実施形態が完了する。感光性樹脂パターン 86C にはノボラック系の樹脂を主成分とする通常の感光性樹脂ではなく、純度が高く主成分にアクリル樹脂やポリイミド樹脂を含む耐熱性の高い感光性有機絶縁層を用いる必然性があることは既に説明した通りである。蓄積容量 15 の構成に関しては図 13(f) に示したように対向電極(蓄積容量線) 16 と絵素電極(ドレイン電極) 21 とがゲート絶縁層 30 を介して重なっている領域 50(右下がり斜線部) が蓄積容量 15 を構成する場合を例示しており、ドレイン電極 21 と前段の走査線 11 とがゲート絶縁層 30 を介して蓄積容量 15 を構成することも可能であるが、ここではその詳細な説明は省略する。なお、図 13(f)においても走査線の電極端子 5 と信号線の電極端子 6 との間を高抵抗性部材、例えば OFF 状態の絶縁ゲート型トランジスタや細長い導電性線路で接続する静電気対策は特に図示しなかったが、開口部 63A が設けられ走査線 11 の一部を露出する工程が付与されているので静電気対策は容易であることは変わらない。

30

#### 【0097】

本発明の第 7 の実施形態では有機絶縁層を信号線上に形成することで製造工程の削減を推進しているが、有機絶縁層の厚みが 1 μm 以上あるので液晶セルのギャップ精度の確保に支障が出る懼れもある。そこで第 8 の実施形態では最小限度の工程数の追加で有機絶縁層に代わるパシベーション技術を提供するものである。

#### (第 8 の実施形態)

#### 【0098】

第 8 の実施形態では、図 15(d) と図 16(d) に示したように走査線 11 の電極端子形成領域に開口部 63A を形成して走査線 11 の一部 72 を露出するとともにエッチストップ層 32A を形成するまでは第 7 の実施形態とほぼ同一のプロセスで進行する。引き続き前記感光性樹脂パターン 82C を除去し、PCVD 装置を用いてガラス基板 2 の全面に不純物として例えば燐を含む第 2 の非晶質シリコン層 33 を例えば 0.05 μm 程度の膜厚で被着した後、ソース・ドレイン配線の形成工程では SPT 等の真空製膜装置を用いて膜厚 0.1 μm 程度の陽極酸化可能な耐熱金属層として例えば Ti, Ta 等の耐熱金属薄膜層 34 を、そして膜厚 0.3 μm 程度の同じく陽極酸化可能な低抵抗配線層として AL 薄膜層 35 を順次被着する。そしてこれら 2 層の薄膜よりなるソース・ドレイン配線材と

40

10

20

30

40

50

第2の非晶質シリコン層33と第1の非晶質シリコン層31とを微細加工技術により感光性樹脂パターン87A, 87Bを用いて順次食刻してゲート絶縁層30を露出し、図15(e)と図16(e)に示したようにゲート絶縁層30上に34Aと35Aとの積層によりなり絵素電極となる絶縁ゲート型トランジスタのドレイン電極21とソース配線も兼ねる信号線12とを選択的に形成し、ソース・ドレイン配線12, 21の形成と同時に開口部63A近傍の第2の非晶質シリコン層33Cを含んで走査線の電極端子5と信号線の一部よりなる電極端子6も同時に形成する。この時、電極端子5, 6上の87Aの膜厚(黒領域)が例えば3μmとソース・ドレイン配線12, 21に対応した領域87B(中間調領域)の膜厚1.5μmよりも厚い感光性樹脂パターン87A, 87Bをハーフトーン露光技術により形成しておくことが第8の実施形態の重要な特徴である。

10

### 【0099】

ソース・ドレイン配線12, 21の形成後、酸素プラズマ等の灰化手段により上記感光性樹脂パターン87A, 87Bを1.5μm以上膜減りさせると感光性樹脂パターン87Bが消失してソース・ドレイン配線12, 21が露出すると共に電極端子5, 6上にのみ感光性樹脂パターン87Cを選択的に形成することができる。そこで感光性樹脂パターン87Cをマスクとして光を照射しながら図15(f)と図16(f)に示したようにソース・ドレイン配線12, 21を陽極酸化して酸化層68, 69を形成するとともに、ソース・ドレイン配線12, 21の下側面に露出している第2の非晶質シリコン層33Aと第1の非晶質シリコン層31Aを陽極酸化して絶縁層である酸化シリコン層(SiO<sub>2</sub>)66, 67を形成する。

20

### 【0100】

陽極酸化終了後、感光性樹脂パターン87Cを除去すると図15(g)と図16(g)に示したように低抵抗薄膜層よりなる電極端子5, 6が露出する。なおソース・ドレイン配線12, 21の構成としては抵抗値の制約が緩いのであれば簡素化して陽極酸化可能なTa単層とすることも可能である。また図15(g)と図16(g)においては走査線の電極端子5と信号線の電極端子6との間を高抵抗性部材で接続する静電気対策は特に図示しなかったので信号線12の電極端子6はソース・ドレイン配線12, 21とは異なり側面にのみ絶縁層である陽極酸化層が形成されているが、静電気対策で電極端子5, 6間を適当な導電性部材で接続していると走査線の電極端子6の側面にも若干の陽極酸化層が形成されることは説明を要しない。このようにして得られたアクティブ基板2とカラーフィルタとを貼り合わせて液晶パネル化し、本発明の第8の実施形態が完了する。蓄積容量15の構成に関しては図15(g)に示したように対向電極(蓄積容量線)16と絵素電極21(ドレイン電極)21とがゲート絶縁層30を介して重なっている領域50(右下がり斜線部)が蓄積容量15を構成する場合を例示している。

30

### 【0101】

#### 【発明の効果】

以上述べたように本発明に記載の液晶表示装置では絶縁ゲート型トランジスタはチャネル上に保護絶縁層を有しているので、画像表示部内のソース・ドレイン配線上にのみまたは信号線上にのみ感光性有機絶縁層を選択的に形成するか、あるいは陽極酸化可能なソース・ドレイン配線材よりなるソース・ドレイン配線を陽極酸化して絶縁層を形成することでパシベーション機能が与えられる。このため格別な加熱工程を伴わず、非晶質シリコン層を半導体層とする絶縁ゲート型トランジスタに過度の耐熱性を必要としない。換言すればパシベーション形成で電気的な性能の劣化を生じない効果も付加されている。また、ソース・ドレイン配線の陽極酸化にあたり、ハーフトーン露光技術の導入により走査線や信号線の電極端子上を選択的に保護することが可能となり写真食刻工程数の増加を阻止できる効果が得られる。

40

### 【0102】

加えて、エッチストップ層の形成工程とゲート絶縁層への開口部形成工程とをハーフトーン露光技術の導入により1枚のフォトマスクで処理することを可能ならしめる工程削減、擬似絵素電極の導入により絵素電極と走査線を1枚のフォトマスクで処理する等の合理化

50

により、写真食刻工程数を従来の5回よりさらに削減できて4枚あるいは3枚のフォトマスクを用いて液晶表示装置を作製することが可能となった。これはアクティブ基板の製造工程数の削減がなされた結果であり、全体のコスト削減の観点からも特筆される最大の特徴である。しかもこれらの工程のパターン精度はさほど高くないので歩留や品質に大きな影響を与えない事も生産管理を容易なものとしてくれる。

### 【0103】

さらに、第5と第7の実施形態によるIPS型の液晶表示装置においては対向電極と絵素電極との間に生ずる電界はゲート絶縁層のみに印加され、また第6と第8の実施形態によるIPS型の液晶表示装置においてはゲート絶縁層と絵素電極の陽極酸化層に印加されるので従来の欠陥の多い劣悪なパシベーション絶縁層が介在せず、表示画像の焼付現象が生じにくい利点も見逃せないものである。なぜならばドレイン配線（絵素電極）の陽極酸化層は絶縁層というよりも高抵抗層として機能するため電荷の蓄積が生じないからである。

### 【0104】

なお本発明の要件は上記の説明からも明らかなように、エッチストップ型の絶縁ゲート型トランジスタにおいて陽極酸化可能なソース・ドレイン配線材を用いてソース・ドレイン配線表面を陽極酸化して絶縁層化した点にあり、それ以外の構成に関しては絵素電極、ゲート絶縁層等の材質や膜厚等が異なった表示装置用半導体装置、あるいはその製造方法の差異も本発明の範疇に属することは自明であり、反射型の液晶表示装置においても本発明の有用性は変らず、また絶縁ゲート型トランジスタの半導体層も非晶質シリコンに限定されるものでないことも明らかである。

### 【図面の簡単な説明】

【図1】本発明の第1の実施形態にかかる表示装置用半導体装置の平面図

【図2】本発明の第1の実施形態にかかる表示装置用半導体装置の製造工程断面図

【図3】本発明の第2の実施形態にかかる表示装置用半導体装置の平面図

【図4】本発明の第2の実施形態にかかる表示装置用半導体装置の製造工程断面図

【図5】本発明の第3の実施形態にかかる表示装置用半導体装置の平面図

【図6】本発明の第3の実施形態にかかる表示装置用半導体装置の製造工程断面図

【図7】本発明の第4の実施形態にかかる表示装置用半導体装置の平面図

【図8】本発明の第4の実施形態にかかる表示装置用半導体装置の製造工程断面図

【図9】本発明の第5の実施形態にかかる表示装置用半導体装置の平面図

【図10】本発明の第5の実施形態にかかる表示装置用半導体装置の製造工程断面図

【図11】本発明の第6の実施形態にかかる表示装置用半導体装置の平面図

【図12】本発明の第6の実施形態にかかる表示装置用半導体装置の製造工程断面図

【図13】本発明の第7の実施形態にかかる表示装置用半導体装置の平面図

【図14】本発明の第7の実施形態にかかる表示装置用半導体装置の製造工程断面図

【図15】本発明の第8の実施形態にかかる表示装置用半導体装置の平面図

【図16】本発明の第8の実施形態にかかる表示装置用半導体装置の製造工程断面図

【図17】液晶パネルの実装状態を示す斜視図

【図18】液晶パネルの等価回路図

【図19】従来の液晶パネルの断面図

【図20】従来例のアクティブ基板の平面図

【図21】従来例のアクティブ基板の製造工程断面図

【図22】合理化されたアクティブ基板の平面図

【図23】合理化されたアクティブ基板の製造工程断面図

### 【符号の説明】

1 液晶パネル

2 アクティブ基板（ガラス基板）

3 半導体集積回路チップ

4 T C P フィルム

5, 6 電極端子

10

20

30

40

50

- 9 カラーフィルタ(対向するガラス基板)

10 絶縁ゲート型トランジスタ

11 走査線(ゲート電極)

12 信号線(ソース配線、ソース電極)

16 共通容量線(IPS型においては対向電極)

17 液晶

19 偏光板

20 配向膜

21 ドレイン電極(IPS型においては絵素電極)

22 (透明導電性)絵素電極

30 ゲート絶縁層

31 不純物を含まない(第1の)非晶質シリコン層

32 チャネル保護絶縁層(エッチストップ層)

33 不純物を含む(第2の)非晶質シリコン層

34 (陽極酸化可能な)耐熱金属層

35 (陽極酸化可能な)低抵抗金属層(AL)

36 (陽極酸化可能な)中間導電層

37 パシベーション絶縁層

50, 51, 52 蓄積容量形成領域

62 (ドレイン電極上の)開口部

63, 63A (走査線上の)開口部

64 (信号線上の)開口部

65, 65A (対向電極上の)開口部

66 不純物を含む酸化シリコン層

67 不純物を含まない酸化シリコン層

68 陽極酸化層(酸化チタン, TiO<sub>2</sub>)

69 陽極酸化層(アルミナ, Al<sub>2</sub>O<sub>3</sub>)

70 陽極酸化層(5酸化タンタル, Ta<sub>2</sub>O<sub>5</sub>)

71 プラズマ保護層

72 走査線の一部

73 蓄積電極

83 (絵素電極形成のための通常の)感光性樹脂パターン

82, 84, 87 (ハーフトーン露光で形成された)感光性樹脂パターン

85, 86 (ハーフトーン露光で形成された)感光性有機絶縁層

91 透明導電層

92 第1の金属層

【図5】

【図6】

【図7】

【図8】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2-2】

【図2-3】

## フロントページの続き

F ターム(参考) 2H092 GA12 GA14 GA24 GA40 GA48 GA51 JA26 JA34 JA37 JA41

JA46 JB56 JB57 JB69 KA05 KA18 KA22 KB24 MA05 MA08

MA13 MA18 MA24 MA27 MA30 NA27 NA29 PA01 PA02 PA08

5F110 AA16 AA21 BB01 CC07 DD02 EE04 EE05 EE07 EE14 EE23

EE24 EE25 EE37 EE44 FF03 FF30 GG02 GG15 GG25 GG45

HK03 HK04 HK06 HK09 HK16 HK22 HK33 HK35 HM19 NN01

NN04 NN12 NN16 NN24 NN27 NN35 NN38 NN72 NN73 QQ02