(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6029538号

(P6029538)

(45) 発行日 平成28年11月24日(2016.11.24)

(24) 登録日 平成28年10月28日(2016.10.28)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 21/338 | (2006.01) |

| HO 1 L 29/778 | (2006.01) |

| HO 1 L 29/812 | (2006.01) |

| HO 1 L 21/336 | (2006.01) |

| HO 1 L 29/78  | (2006.01) |

|               |           |

| HO 1 L        | 29/80     |

| HO 1 L        | 29/78     |

| HO 1 L        | 21/20     |

| HO 1 L        | 21/205    |

請求項の数 6 (全 11 頁) 最終頁に続く

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2013-116030 (P2013-116030)  |

| (22) 出願日  | 平成25年5月31日 (2013.5.31)        |

| (65) 公開番号 | 特開2014-236080 (P2014-236080A) |

| (43) 公開日  | 平成26年12月15日 (2014.12.15)      |

| 審査請求日     | 平成28年1月19日 (2016.1.19)        |

|           |                                             |

|-----------|---------------------------------------------|

| (73) 特許権者 | 000106276<br>サンケン電気株式会社<br>埼玉県新座市北野3丁目6番3号  |

| (73) 特許権者 | 000190149<br>信越半導体株式会社<br>東京都千代田区大手町二丁目2番1号 |

| (74) 代理人  | 100102532<br>弁理士 好宮 幹夫                      |

| (72) 発明者  | 鹿内 洋志<br>埼玉県新座市北野3丁目6番3号 サンケン電気株式会社内        |

| (72) 発明者  | 佐藤 憲<br>埼玉県新座市北野3丁目6番3号 サンケン電気株式会社内         |

最終頁に続く

(54) 【発明の名称】 半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

シリコン系基板と、

前記シリコン系基板上に設けられ、A 1 組成を含む第一の層と、前記第一の層より A 1 の含有が少ない第二の層とが交互に積層された第一のバッファ層と、

前記第一のバッファ層上に設けられ、A 1 組成を含む第三の層と、前記第三の層より A 1 の含有が少ない第四の層とが交互に積層された第二のバッファ層と、

前記第二のバッファ層上に設けられ、A 1 組成を含む第五の層と、前記第五の層より A 1 の含有が少ない第六の層とが交互に積層された第三のバッファ層とを有し、

全体として、前記第二のバッファ層が、前記第一バッファ層及び前記第三バッファ層より A 1 の含有が多く、

前記第四の層は、臨界膜厚以上の厚さを有するものであり、且つ前記第二の層及び前記第六の層より転位が多いものであることを特徴とする半導体装置。

## 【請求項 2】

前記第三のバッファ層上に設けられた能動層をさらに有し、

前記第一の層は、A 1 組成を含む第一のサブ層と、前記第一のサブ層より A 1 の含有が少ない第二のサブ層とが繰り返し形成されたものであり、

前記第五の層は、A 1 組成を含む第三のサブ層と、前記第三のサブ層より A 1 の含有が少ない第四のサブ層とが繰り返し形成されたものあり、

前記第二のサブ層及び前記第四のサブ層は、前記臨界膜厚未満の厚さを有するものであ

10

20

り、

前記第二の層は、前記第一のサブ層より A 1 の含有が少なく、前記二のサブ層より厚いものであり、

前記第六の層は、前記第四のサブ層より A 1 の含有が少なく、前記第四のサブ層より厚いものであり、

前記第四の層は、前記二のサブ層及び前記第四のサブ層より厚く、前記第二の層及び前記第六の層より薄いことを特徴とする請求項 1 に記載の半導体装置。

#### 【請求項 3】

前記第二のサブ層、前記第二の層、前記第四の層、前記第四のサブ層、及び、前記第六の層は、GaN からなることを特徴とする請求項 2 に記載の半導体装置。 10

#### 【請求項 4】

前記第一のサブ層、前記第三の層、及び、前記第三のサブ層は、AlN からなることを特徴とする請求項 2 又は請求項 3 に記載の半導体装置。

#### 【請求項 5】

複数の前記第三の層の A 1 の含有が、前記第三のバッファ層に近いほど少なくなることを特徴とする請求項 1 又は請求項 2 に記載の半導体装置。

#### 【請求項 6】

前記第二のバッファ層を構成する複数の前記第三の層のうち、前記第二のバッファ層の中央部に配置された前記第三の層が、前記第二のバッファ層の上面側及び下面側に配置された前記第三の層と比較して、A 1 の含有が少ないことを特徴とする請求項 1 又は請求項 2 に記載の半導体装置。 20

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は、半導体装置に関し、特に窒化物半導体層を有する半導体装置に関する。

#### 【背景技術】

#### 【0002】

窒化物半導体層は安価なシリコン基板上やサファイア基板上に形成されることが一般的である。しかし、これらの基板の格子定数と窒化物半導体層の格子定数は大きく異なり、また、熱膨張係数も異なる。このため、基板上にエピタキシャル成長によって形成された窒化物半導体層に、大きな歪みエネルギーが発生する。その結果、窒化物半導体層にクラックの発生や結晶品質の低下が生じやすい。 30

#### 【0003】

上記問題を解決するために、シリコン基板と窒化物半導体からなる能動層との間に窒化物半導体層を積層したバッファ層を配置する方法が提案されている（例えば、特許文献 1 参照）。

#### 【0004】

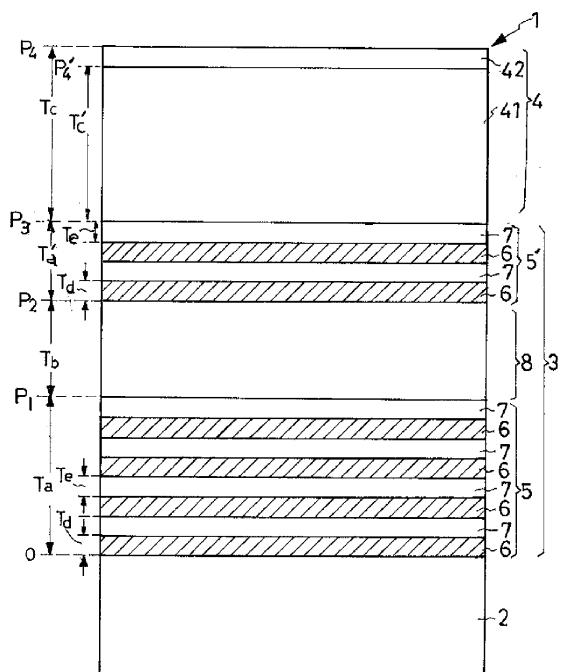

特許文献 1 のバッファ層を有する半導体ウェーハを図 4 に示す。

図 4において、バッファ層 3 は、シリコン基板 2 と能動層 4との間に設けられており、バッファ層 3 は、第一の多層構造バッファ領域 5 と、第一の多層構造バッファ領域 5 の上に設けられたGaN からなる第二の単層構造バッファ領域 8 と、第二の単層構造バッファ領域 8 の上に設けられた第二の多層構造バッファ領域 5' を有している。 40

さらに、第一の多層構造バッファ領域 5 及び第二の多層構造バッファ領域 5' は、サブ多層構造バッファ領域 6 と、GaN からなり第二の単層構造バッファ領域 8 より薄い第一の単層構造バッファ領域 7 とが繰り返し積層された多層構造を有している。

また、サブ多層構造バッファ領域 6 は、AlN からなる第一の層と、GaN からなる第二の層とが繰り返し積層された多層構造を有している。

#### 【0005】

特許文献 1においては、第一の層をアルミニウムを第 1 の割合で含む窒化物半導体で形 50

成し、第二の層、第一の単層構造バッファ領域7、及び、第二の単層構造バッファ領域8のアルミニウムの割合(ゼロを含む)を第1の割合よりも小さくすることで、半導体ウェーハの反りを低減させることができることが開示されている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2008-205117号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

上述したように、シリコン基板上やサファイア基板上に形成された窒化物半導体層の特性を改善するために、バッファ層を設けること、及び、バッファ層の構成を最適化することが行われてきた。

【0008】

しかしながら、本発明者らは、以下の問題点があることを見出した。

すなわち、バッファ層を一定の厚さのAlN/GaNが繰り返された多層バッファで構成し、多層バッファ層のGaN層を厚くした場合、バッファ層や能動層にクラックが生じたり、基板との熱膨張係数差で反りを調整できないという問題がある。

逆にバッファ層を構成するGaN層を薄くした場合に、バッファ層内のリーク電流が増加するという問題がある。

また、バッファ層をAlN/GaNの超格子構造とした場合も、バッファ層のトータル膜厚を厚くすると同様に反りの問題がある。

【0009】

また、特許文献1に開示されたバッファ構造では、厚いGaNからなる単層バッファ領域8があるため、バッファ層3の上面に凹凸が生じることで、能動層4の上面に凹凸が転写され、能動層4の上面の平坦性に問題が生じて、半導体装置の電気的特性にバラつきや特性の悪化の問題がある。

さらに、厚いGaNからなる単層構造バッファ領域8を挿入することで、バッファ層を厚く形成すると、膜形成装置内でバッファ層と基板との熱膨張係数差で反ってしまい、膜形成装置内から基板を取り出した時の基板と基板上の層の応力の調整が不十分で、反りやクラックが生じる場合がある。

【0010】

本発明は、上記問題点に鑑みてなされたものであって、バッファ層にかかる応力を低減しつつ、リークを抑制し、能動層上面の平坦性を改善することができる半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0011】

上記目的を達成するために、本発明は、シリコン系基板と、前記シリコン系基板上に設けられ、Al組成を含む第一の層と、前記第一の層よりAlの含有が少ない第二の層とが交互に積層された第一のバッファ層と、前記第一のバッファ層上に設けられ、Al組成を含む第三の層と、前記第三の層よりAlの含有が少ない第四の層とが交互に積層された第二のバッファ層と、前記第二のバッファ層上に設けられ、Al組成を含む第五の層と、前記第五の層よりAlの含有が少ない第六の層とが交互に積層された第三のバッファ層とを有し、全体として、前記第二のバッファ層が、前記第一バッファ層及び前記第三バッファ層よりAlの含有が多いことを特徴とする半導体装置を提供する。

【0012】

このように、バッファ層の中央部の層(第二のバッファ層)がバッファ層の上部の層(第三のバッファ層)及びバッファ層の下部の層(第一のバッファ層)よりAl含有が多いことで、バッファ層の中央部で格子緩和(ミスフィット転位)がより大きく生じて、バッファ層にかかる応力を小さくできる。

10

20

30

40

50

また、バッファ層の中央部の層（第二のバッファ層）をA1組成を含む層（第三の層）を含む多層構造にし、バッファ層全体のアルミ組成を高めることでリーク電流を低減させることができる。

また、バッファ層の中央部の層（第二のバッファ層）をA1組成を含む層（第三の層）を含む多層構造にすることで、バッファ層上面の平坦性を改善することができ、それによつて能動層上面の平坦性を改善することができる。

#### 【0013】

ここで、前記第三のバッファ層上に設けられた能動層をさらに有し、前記第一の層は、A1組成を含む第一のサブ層と、前記第一のサブ層よりA1の含有が少ない第二のサブ層とが繰り返し形成されたものであり、前記第五の層は、A1組成を含む第三のサブ層と、前記第三のサブ層よりA1の含有が少ない第四のサブ層とが繰り返し形成されたものであり、前記第二のサブ層及び前記第四のサブ層は、臨界膜厚未満の厚さを有するものであり、前記第二の層は、前記第一のサブ層よりA1の含有が少なく、前記二のサブ層より厚いものであり、前記第六の層は、前記第四のサブ層よりA1の含有が少なく、前記第四のサブ層より厚いものであり、前記第四の層は、前記二のサブ層及び前記第四のサブ層より厚く、前記第二の層及び前記第六の層より薄く、前記臨界膜厚以上の厚さを有するものであり、前記第四の層は、前記第二の層及び前記第六の層より転位が多いものであることが好ましい。

#### 【0014】

このように、バッファ層の中央部の層に含まれる第四の層を、バッファ層の下部の層に含まれる第二のサブ層及びバッファ層の上部の層に含まれる第四のサブ層より厚くすることで、バッファ層の中央部の層に含まれる第四の層において格子緩和（ミスフィット転位）が生じやすくなり、これにより、応力コントロールの幅がより広がり、バッファ層全体をより厚く形成することができる。

#### 【0015】

また、前記第二のサブ層、前記第二の層、前記第四の層、前記第四のサブ層、及び、前記第六の層を、GaNとすることができる。

バッファ層を構成する第二のサブ層、第二の層、第四の層、第四のサブ層、及び、第六の層として、上記のような材料を好適に用いることができる。

#### 【0016】

また、前記第一のサブ層、前記第三の層、及び、前記第三のサブ層を、AlNとすることができます。

バッファ層を構成する第一のサブ層、第三の層、及び、第三のサブ層として、上記のような材料を好適に用いることができる。

#### 【0017】

また、複数の前記第三の層のA1の含有は、前記第三のバッファ層に近いほど少なくすることが好ましい。

このように、バッファ層の中央部の層において、互いに隣接する第三の層と第四の層のA1組成比の差を、能動層に近いほど小さくすることで、下側では応力緩和効果を大きくし、上側では応力緩和効果よりも結晶性を良好にする効果を大きくすることができる。

#### 【0018】

また、前記第二のバッファ層を構成する複数の前記第三の層のうち、前記第二のバッファ層の中央部に配置された前記第三の層について、前記第二のバッファ層の上面側及び下面側に配置された前記第三の層と比較して、A1の含有を少なくすることが好ましい。

このように、バッファ層の中央部の層において、互いに隣接する第三の層と第四の層のA1組成比の差を、中央部で小さくすることで、下側および上側では応力緩和効果を大きくし、中央部では応力緩和効果よりも結晶性を良好にする効果を大きくすることができる。

#### 【発明の効果】

#### 【0019】

10

20

30

40

50

以上のように、本発明によれば、バッファ層にかかる応力を低減しつつ、リークを抑制し、能動層上面の平坦性を改善することができる半導体装置を提供することができる。

**【図面の簡単な説明】**

**【0020】**

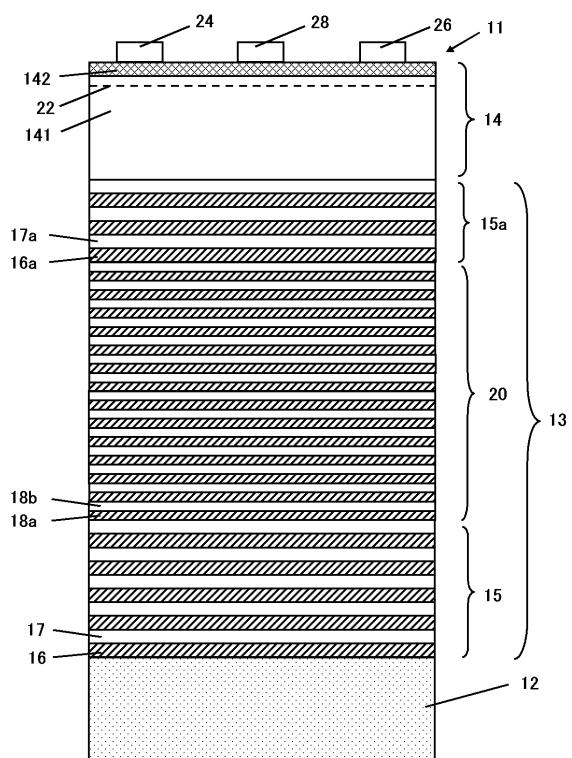

【図1】本発明の半導体装置の実施態様の一例を示す概略断面図である。

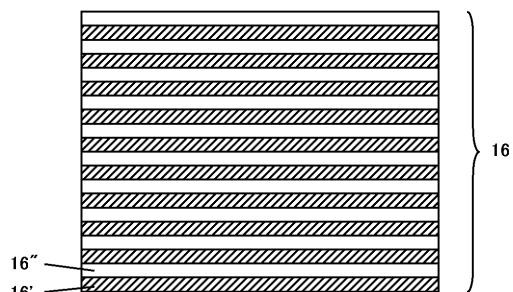

【図2】図1の第一の層の詳細を示す概略断面図である。

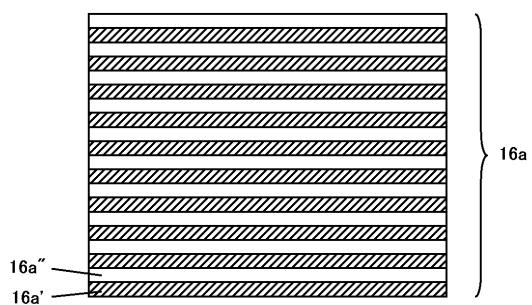

【図3】図1の第五の層の詳細を示す概略断面図である。

【図4】従来のバッファ層を有する半導体ウェーハの概略断面図である。

**【発明を実施するための形態】**

**【0021】**

以下、本発明について、実施態様の一例として、図を参照しながら詳細に説明するが、本発明はこれに限定されるものではない。

前述のように、従来のバッファ層においては、バッファ層の中央部側に、厚いGaNからなる単層バッファ領域を挿入しているため、バッファ層の上面に凹凸が生じることで、能動層の上面に凹凸が転写され、能動層の上面の平坦性に問題が生じて、半導体装置の電気的特性にバラつきや特性の悪化の問題がある。

さらに、バッファ層の中央部側に、厚いGaNからなる単層構造バッファ領域を挿入することで、バッファ層が厚くなると、膜形成装置内でバッファ層と基板との熱膨張係数差で反ってしまい、膜形成装置内から基板を取り出した時の基板と基板上の層の応力の調整が不十分で、反りやクラックが生じる場合がある。

**【0022】**

そこで、本発明者らは、バッファ層にかかる応力を低減しつつ、能動層上面の平坦性を改善することができる半導体装置について鋭意検討を重ねた。

その結果、バッファ層の中央部の層（第二のバッファ層）がバッファ層の上部の層（第三のバッファ層）及びバッファ層の下部の層（第一のバッファ層）よりAl含有が多く、バッファ層の中央部の層（第二のバッファ層）をAl組成を含む層（第三の層）を含む多層構造にすることで、バッファ層にかかる応力を小さくできるとともに、リーク電流を低減させることができ、さらに能動層上面の平坦性を改善することができることを見出し、本発明をなすに至った。

**【0023】**

図1は、本発明の半導体装置の一例を示す概略断面図である。

図1に示す本発明の半導体装置11は、シリコン系基板12と、シリコン系基板12上に設けられたバッファ層13と、バッファ層13上に設けられた能動層14と、能動層14上に設けられた第一電極24、第二電極26、及び、制御電極28を有している。

ここで、シリコン系基板12は、例えば、SiまたはSiCからなる基板である。

**【0024】**

バッファ層13は、第一のバッファ層15と、第一のバッファ層15上に設けられた第二のバッファ層20と、第二のバッファ層20上に設けられた第三のバッファ層15aを有している。

第一のバッファ層15は、Al組成を含む第一の層16と第一の層16よりAl含有が少ない第二の層17とが交互に積層されたものである。

第二のバッファ層20は、Al組成を含む第三の層18aと第三の層18aよりAl含有が少ない第四の層18bとが交互に積層されたものである。

第三のバッファ層15aは、Al組成を含む第五の層16aと第五の層16aよりAl含有が少ない第六の層17aとが交互に積層されたものである。

**【0025】**

能動層14はさらに、チャネル層141と、チャネル層141上に設けられたバリア層142を有している。

第一の電極24及び第二の電極26は、第一の電極24から、チャネル層141内に形成された二次元電子ガス22を介して、第二の電極26に電流が流れるように配置されて

10

20

30

40

50

いる。

第一の電極 24 と第二の電極 26 との間に流れる電流は、制御電極 28 に印可される電位によってコントロールすることができる。

#### 【0026】

バッファ層 13 の中央部の層である第二のバッファ層 20 が、全体として、第一バッファ層 15 及び第三バッファ層 15a より A1 の含有が多くなっている。

これにより、バッファ層 13 の中央部で格子緩和（ミスフィット転位）が大きく生じて、バッファ層 13 にかかる応力を小さくできる。

#### 【0027】

また、バッファ層 13 の中央部の層である第二のバッファ層 20 を A1 組成を含む層（第三の層 18a）を含む多層構造にし、バッファ層 13 全体のアルミ組成を高めることで、リーク電流を低減させることができる。 10

#### 【0028】

さらに、バッファ層 13 の中央部の層である第二のバッファ層 20 を A1 組成を含む層（第三の層 18a）を含む多層構造にすることで、バッファ層上面の平坦性を改善することができ、それによって能動層上面の平坦性を改善することができる。

#### 【0029】

第一の層 16 は、図 2 に拡大図を示すように、A1 組成を含む第一のサブ層 16' と、第一のサブ層 16' より A1 の含有が少ない第二のサブ層 16" とが繰り返し形成されたものとすることができます。 20

また、前記第 5 の層 16a は、図 3 に拡大図を示すように、A1 組成を含む第三のサブ層 16a' と、前記第三のサブ層より A1 の含有が少ない第四のサブ層 16a" とが繰り返し形成されたものとすることができます。

第二のサブ層 16" 及び第四のサブ層 16a" は、臨界膜厚（これ以上の膜厚であれば確実にミスフィット転位を生じさせることができる）未満の厚さを有するものとすることができます。

第二の層 17 は、第一のサブ層 16' より A1 の含有が少なく、第二のサブ層 16" より厚いものとすることができます。

第六の層 17a は、第四のサブ層 16a" より A1 の含有が少なく、第四のサブ層 16" より厚いものとすることができます。 30

第四の層 18b は、第二のサブ層 16" 及び第四のサブ層 16a" より厚く、第二の層 17 及び第六の層 17a より薄く、臨界膜厚以上の厚さを有するものとすることができます。

第二の層 17 及び第六の層 17a は、第四の層 18b より厚いため、層の下部で生じたミスフィット転位が層の途中で止る可能性が高くなるので、第四の層 18b は第二の層 17 及び前記第六の層 17a よりミスフィット転位が多くなる。

#### 【0030】

なお、第四の層 18b は、3.5 nm ~ 200 nm であることが好ましい。この範囲であれば、確実にミスフィット転位を生じさせることができます。

また、第四の層 18b は、5 nm ~ 50 nm であることがより好ましい。この範囲であれば、より確実にミスフィット転位を生じさせることができます。 40

#### 【0031】

したがって、バッファ層 13 の各層が上記の膜厚関係を有していれば、バッファ層の中央部の層に含まれる第四の層において格子緩和（ミスフィット転位）が生じやすくなり、これにより、応力コントロールの幅がより広がり、バッファ層全体をより厚く形成することができる。

#### 【0032】

第二のサブ層 16" 、第二の層 17 、第四の層 18b 、第四のサブ層 16a" 、及び、第六の層 17a は、例えば、GaN である。

第一のサブ層 16' 、第三の層 18a 、及び、第三のサブ層 16a' は、例えば AlN 50

である。

**【0033】**

また、第二のバッファ層20を構成する第三の層18aのA1の含有は、第三のバッファ層15aに近いほど、すなわち、能動層14に近いほど少なくすることが好ましい。

このように、バッファ層の中央部の層において、互いに隣接する第三の層18aと第四の層18bのA1組成比の差を、第三のバッファ層15aに近いほど、すなわち、能動層14に近いほど小さくすることで、下側では応力緩和効果を大きくし、上側では応力緩和効果よりも結晶性を良好にする効果を大きくすることができます。

**【0034】**

さらに、第二のバッファ層20を構成する複数の第三の層18aのうち、第二のバッファ層20の中央部に配置された第三の層について、第二のバッファ層の上面側及び下面側に配置された前記第三の層と比較して、A1の含有を少なくすることが好ましい。 10

このように、バッファ層の中央部の層において、互いに隣接する第三の層18aと第四の層18bのA1組成比の差を、中央部で小さくすることで、下側および上側では応力緩和効果を大きくし、中央部では応力緩和効果よりも結晶性を良好にする効果を大きくすることができます。

**【0035】**

次に、本発明の半導体装置の製造方法を説明する。

まず、シリコン系基板12上に、バッファ層13を構成する第一のバッファ層15を形成する。 20

具体的には、MOVPE(有機金属気相成長)法によって、AlNからなる第一のサブ層16' とGaNからなる第二のサブ層16"とを交互に成長させて形成した第一の層16と、GaNからなる第二の層17とを交互に成長させて、第一のバッファ層15を形成する。

第一のサブ層16'の膜厚は例えば、3~7nmであり、第二のサブ層16"の膜厚は例えば、2~5nmであり、第二の層17の膜厚は例えば、100~500nm、好ましくは、100~300nmである。

繰り返し形成される第一の層16及び第二の層17の数は、例えば、4~7とすることができます、繰り返し形成される第一のサブ層16'及び第二のサブ層16"の数は、例えば、1~15とすることができます。 30

**【0036】**

次に、第一のバッファ層15上に、バッファ層13を構成する第二のバッファ層20を形成する。

具体的には、MOVPE法によって、AlNからなる第三の層18aとGaNからなる第四の層18bとを交互に成長させて、第二のバッファ層20を形成する。

第三の層18aの膜厚は例えば、3~7nmであり、第四層18bの膜厚は例えば、3.5~200nmである。

繰り返し形成される第三の層18a及び第四の層18bの数は、例えば、10~100とすることができます。

**【0037】**

次に、第二のバッファ層20上に、バッファ層13を構成する第三のバッファ層15aを形成する。

具体的には、MOVPE法によって、AlNからなる第三のサブ層16a' とGaNからなる第四のサブ層16a"とを交互に成長させて形成した第五の層16aと、GaNからなる第六の層17aとを交互に成長させて、第三のバッファ層15aを形成する。

第三のサブ層16a'の膜厚は例えば、3~7nmであり、第四のサブ層16a"の膜厚は例えば、2~5nmであり、第六の層17aの膜厚は例えば、100~500nm、好ましくは、100~300nmである。

繰り返し形成される第五の層16a及び第六の層17aの数は、例えば、4~7とすることができます、繰り返し形成される第三のサブ層16a'及び第四のサブ層16a"の数は 50

20 ... 第二のバッファ層、 22 ... 二次元電子ガス、 24 ... 第一電極、

26 ... 第二電極、 28 ... 制御電極。

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 21/20 (2006.01)

H 01 L 21/205 (2006.01)

(72)発明者 後藤 博一

埼玉県新座市北野3丁目6番3号 サンケン電気株式会社内

(72)発明者 篠宮 勝

群馬県安中市磯部二丁目13番1号 信越半導体株式会社 半導体磯部研究所内

(72)発明者 土屋 慶太郎

群馬県安中市磯部二丁目13番1号 信越半導体株式会社 半導体磯部研究所内

(72)発明者 萩本 和徳

群馬県安中市磯部二丁目13番1号 信越半導体株式会社 半導体磯部研究所内

審査官 棚田 一也

(56)参考文献 特開2011-018844 (JP, A)

特開2010-219176 (JP, A)

特開2008-205117 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 338

H 01 L 21 / 20

H 01 L 21 / 205

H 01 L 21 / 336

H 01 L 29 / 778

H 01 L 29 / 78

H 01 L 29 / 812