(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4371732号

(P4371732)

(45) 発行日 平成21年11月25日(2009.11.25)

(24) 登録日 平成21年9月11日(2009.9.11)

(51) Int.Cl.

H01L 21/306 (2006.01)

F 1

H01L 21/306

B

H01L 21/306

R

請求項の数 2 (全 7 頁)

(21) 出願番号 特願2003-294375 (P2003-294375)

(22) 出願日 平成15年8月18日 (2003.8.18)

(65) 公開番号 特開2005-64326 (P2005-64326A)

(43) 公開日 平成17年3月10日 (2005.3.10)

審査請求日 平成18年8月8日 (2006.8.8)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100076428

弁理士 大塚 康徳

(74) 代理人 100112508

弁理士 高柳 司郎

(74) 代理人 100115071

弁理士 大塚 康弘

(74) 代理人 100116894

弁理士 木村 秀二

(74) 代理人 100130409

弁理士 下山 治

(74) 代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】半導体ウェハ加工における半導体ウェハのデバイス面保護膜形成方法

## (57) 【特許請求の範囲】

## 【請求項1】

半導体ウェハにデバイスを作成後のスピニエッティング工程で該半導体ウェハのデバイス面をエッティング液から保護するための保護膜を形成する半導体ウェハのデバイス面保護膜形成方法において、

前記デバイス面を、前記デバイス面と前記保護膜との密着性を向上させるための、ポリエーテルアミド樹脂を含む密着向上層で覆い、

前記保護膜としてコーティングによって膜形成し得る環化ゴム系のフォトレジストを用いて前記密着向上層を覆った後、前記保護膜を、フォトリソグラフィーを用いたパターニングによって、前記半導体ウェハの周囲より小さく且つ前記デバイスを覆うように形成し、

前記パターニングされた保護膜をマスクとして、前記密着向上層をドライエッティングを用いてパターニングすることを特徴とするデバイス面保護膜形成方法。

## 【請求項2】

デバイスを形成してなる半導体ウェハの一主面に、請求項1に記載のデバイス面保護膜形成方法により保護膜を形成した後に、前記保護膜の形成側と反対側の半導体ウェハの他主面をスピニエッティングすることを特徴とする半導体ウェハ研磨処理方法。

## 【発明の詳細な説明】

## 【技術分野】

【0001】

本発明は、半導体ウェハ裏面研磨処理工程（スピニエッティング工程）において、半導体ウェハのデバイス面（以下デバイス面と略す）をエッティング液から保護する半導体ウェハのデバイス面保護膜の形成方法に関する。

【背景技術】

【0002】

パーソナルコンピューター、ワードプロセッサーをはじめとする半導体装置は、小型化高密度化される傾向にある。これを構成する半導体パッケージ、チップも同様に小型化、薄型化してきている。その小型化の方法として、半導体チップの場合一般的には、半導体ウェハデバイス作成後の半導体ウェハ裏面を機械研磨し、薄くするバックグラインドを行う。更に、機械研磨時の応力を除去し抗折強度を向上させるために、裏面を化学的にエッティングする処理がなされる。この工程は一般にウェハを回転させながら行うことからスピニエッティングと呼ばれる。具体的には、回転テーブルに、エッティングするウェハの裏面を上にして固定し、約1000 rpmで回転させながら、フッ酸・硝酸系のエッティング液を滴下しながら所望の厚さまで化学的にエッティングする方法である。

10

【0003】

従来、これらの製造工程において、半導体ウェハやチップの表面を保護する場合、保護フィルムをデバイス面に形成し、裏面研磨処理工程を行う。その後、ダイシングの際に、この保護フィルムを剥離する。保護フィルムの役割としては、デバイス面の凹凸を吸収し、この工程中に発生する研磨屑やエッティング液等による半導体ウェハの汚染や破損を防止することである。

20

【0004】

半導体ウェハのデバイス面保護材として、ゴム系のテープやフィルムが挙げられる。しかし、ゴム系のテープやフィルムを使用した場合、保護膜のエッジがエッティング反応の熱によって収縮し、そこからエッティング液がしみ込むことがわかっている。それを防ぐために、例えば特許文献1に記載されているように、デバイス面側に窒素ガス等の冷却用流体を噴射する方法が挙げられる。しかし、スピニエッティングの際、デバイス面と保護フィルムの間へのエッティング液の浸み込みの発生が避けられない。このエッティング液の浸み込みにより、デバイス面にある電気素子等の回路が腐食したり、破壊されたりする問題が発生する。

【0005】

30

これをさらに改良したものに、保護テープをウェハの大きさよりも一回り小さい、いわゆるオーバーハングをつけたものを用いることも提案されている。例えば、特許文献2に記載の、バックグラインドの際に半導体ウェハデバイス面凹凸を吸収するための補強層とスピニエッティングの際にデバイス面にエッティング液が回りこまないようにウェハより一回り小さくプリカットされた保護層の2層からなる半導体ウェハデバイス面保護用フィルムを挙げることができる。このような方法は、スピニエッティング時の保護層として精度良くウェハより一回り小さく切れ目を入れておくことが困難であり、且つ上層のみを剥離することも困難である。

【特許文献1】特開平7 201805号公報

【特許文献2】特開平11 87282号公報

40

【発明の開示】

【発明が解決しようとする課題】

【0006】

上述したように、特許文献1の方法はスピニエッティングの際、デバイス面と保護フィルムの間へのエッティング液の浸み込みの発生が避けられず、特許文献2の方法はスピニエッティング時の保護層として精度良くウェハより一回り小さく切れ目を入れておくことが困難であり、且つ上層のみを剥離することも困難である。

【0007】

本発明はこれら従来技術の欠点に鑑みてなされたものであり、半導体ウェハの裏面をスピニエッティングするに際し、エッティング液の浸み込みを防止して、デバイス面を保護する

50

とともに、ウェハ外周部のバラツキをなくすことが可能な保護膜の形成方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明者は、上記の目的を達成するために、デバイス面保護材にコーティングによって被膜形成し得る高分子化合物を使用し、デバイス表面に前記デバイス面保護膜を形成後、ウェハの周囲の大きさよりも小さくなるように前記保護膜の外周部を精度良く除去することにより、エッティング液の浸み込みおよびウェハ外周部溜まりを防止出来ることを見出し、本発明に至った。

【0009】

10

すなわち、本発明の半導体ウェハのデバイス面保護膜形成方法は、半導体ウェハにデバイスを作成後のスピニエッティング工程で該半導体ウェハのデバイス面をエッティング液から保護するための保護膜を形成する半導体ウェハのデバイス面保護膜形成方法において、前記デバイス面を、前記デバイス面と前記保護膜との密着性を向上させるための、ポリエーテルアミド樹脂を含む密着向上層で覆い、前記保護膜としてコーティングによって膜形成し得る環化ゴム系のフォトレジストを用いて前記密着向上層を覆った後、前記保護膜を、フォトリソグラフィーを用いたパターニングによって、前記半導体ウェハの周囲より小さく且つ前記デバイスを覆うように形成し、前記パターニングされた保護膜をマスクとして、前記密着向上層をドライエッティングを用いてパターニングすることを特徴とする。

【0010】

20

保護膜としては、スピニエッティングに用いるフッ酸・硝酸系のエッティング液のような非常に反応性の高い薬品に侵されないような膜であることが望ましく、例えば環化ゴム系の樹脂を用いることができる。そして、この環化ゴムは感光性を有することが望ましい。

【0011】

本発明によれば、デバイス表面に環化ゴム等の保護膜を形成後、半導体ウェハの周囲の大きさよりも小さく、且つデバイス面よりも大きくなるようにパターニングすることで、保護膜の外周部を精度よく除去することができる。

【発明の効果】

【0012】

30

本発明によれば、エッティング液のデバイス表面への浸み込みおよびウェハ外周部溜まりを防止できるため、デバイスが損傷することはない。

【0013】

また、ウェハ外周部のバラツキもなくなり、チッピングが生じにくく、歩留まりが向上し、オリフラやノッチ部分にもバラツキを生じないことから、スピニエッティング後にパターン形成を行う場合においても、アライメント精度に影響を及ぼすこともなくなる。

【発明を実施するための最良の形態】

【0014】

次に、本発明の実施の形態について図面を用いて詳細に説明するが、本発明はこの実施の形態に限定されるものではない。

【0015】

40

(第1実施形態)

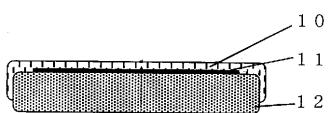

図1は本実施形態に係る半導体ウェハデバイス保護材が半導体ウェハデバイス面に形成された様子を示す断面図である。図1において、12は半導体ウェハ、11は半導体ウェハ12上のデバイス面、10はデバイス面11を保護するための保護材(保護膜)である。

保護材10の特性は、耐薬品性に優れ、形成後精度良く外周部のみ選択的に除去可能であり、研磨処理工程後容易に除去可能なものであることが好ましい。例えば、環化ゴム系の樹脂は常温でコーティングでき、エッティング液に対する耐性に優れているため好ましい。

【0016】

環化ゴム系の樹脂として、従来からフォトリソグラフィーで用いられているネガ型のフ

50

オトレジストを用いることができる。例えば、東京応化工業製のOMR 83（ネガレジスト）を挙げることが出来る。OMR 83を用いる場合、まずスピナーによりコーティングを行い、ついでオープンにより乾燥させることにより、エッティング保護膜が形成される。

【0017】

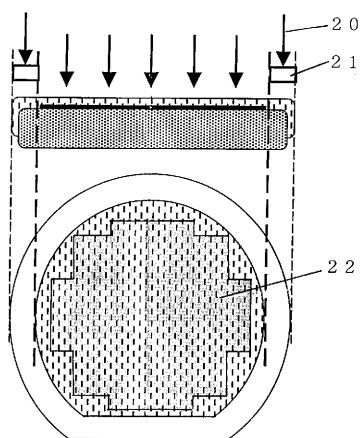

次に図2に示すように、デバイス面11よりも大きく、ウェハ外周部（周囲部）よりも内側に光20が当たるようなフォトマスク21を用いて、感光性環化ゴムを露光する。22はデバイス領域であり、その表面がデバイス面11である。

【0018】

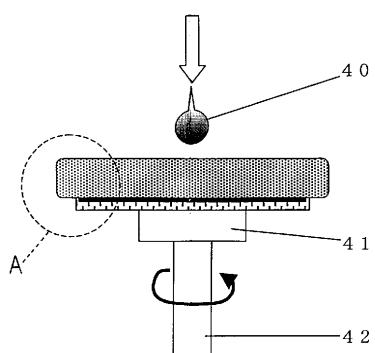

そして、OMR現像液（東京応化工業株式会社製）を用いて感光性環化ゴムを現像することで図3に示すように、半導体ウェハ12よりも一回り小さく、かつデバイス面を保護するように形成された環化ゴムが精度良く形成される。

【0019】

上述のようにして、半導体ウェハデバイス面11に半導体ウェハデバイス面保護材10を形成し、その裏面を研磨処理する。即ち、図4に示すように、この半導体ウェハ12を保護材側からウェハ固定台41となる真空チャックで保持した状態で回転軸42を1000 rpmで回転させ、半導体ウェハ裏面側からフッ酸、硝酸混合系のエッティング液40を滴下する。

【0020】

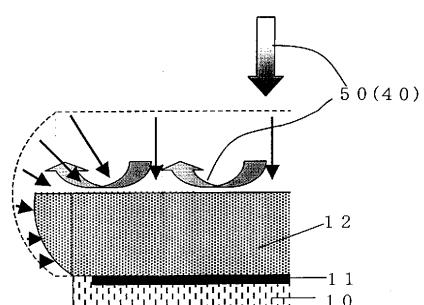

図5に示すように、半導体ウェハ12のデバイス面が形成された表面側を保護膜10が保護するため、エッティング液50（40）の浸み込みは発生しない。また、ウェハの厚みを極薄化した場合においても、ウェハのベベリング部分に保護材がないため、ウェハ外周部にエッティング液溜まりが起こらず、ウェハ外周部バラツキも発生しない。なお、図5は図4のエッティング後のA部を拡大した図に対応する。

【0021】

（第2実施形態）

図6は、本発明の第2実施形態の概略図である。本実施形態が第1実施形態と異なる点は、デバイス面保護層において、ウェハデバイス面とデバイス面保護層の密着性を向上させるために密着向上層70を有し、その上にデバイス面保護層10を形成する二層構造になっている点である。

【0022】

密着向上層70は、デバイス面に対して、後に形成されるデバイス面保護層10の密着性を向上させるために設けられたものであり、エッティング液に対して耐性があり、且つ、デバイス面と密着力が良好なものである。さらに、デバイス面保護層とも密着力が良好なものである。即ち、前述したデバイス面保護層として、環化ゴム1層を用いる場合と比較して、デバイス面との密着力をさらに向上させるものである。

【0023】

密着層の材料としては、上述の各所要求を満たすものであれば良いが、その中でも、ポリエーテルアミド樹脂は、酸・アルカリエッティング耐性に優れ、特に好ましいものである。

【0024】

ポリエーテルアミド樹脂としては、例えば、HIMAL HL 1200（日立化成工業製）を用いることができ、これをスピナーで2 μmの厚さでコーティングした後乾燥させ、その後デバイス面保護層である環化ゴムを形成する。

【0025】

環化ゴムの外周部を所望の形状に精度良くパターニングした後、それをマスクとして、密着向上層であるポリエーテルアミド樹脂のパターニングを行う。ポリエーテルアミド樹脂のパターニングは、ドライエッティングで行うことができる。

【0026】

このように、デバイス面保護膜を、密着性を向上させる機能を持つ層と耐薬品性に優れ

10

20

30

40

50

た層との2層構造にしても、第1実施形態の効果と同様の効果が得られる。

【産業上の利用可能性】

【0027】

本発明はエッティング液のデバイス表面への浸み込みおよびウェハ外周部溜まりを防止することが求められる半導体ウェハ、例えば、インク液を加熱し生じた気泡を利用するインクジェット方式のプリンタのヒータボードの作製に用いることができる。

【図面の簡単な説明】

【0028】

【図1】本発明の第1実施形態を解説する為の半導体ウェハデバイス面保護膜を形成する工程を概念的に示すものであり、保護膜塗布時の半導体ウェハの断面図である。

10

【図2】本発明の第1実施形態を解説する為の半導体ウェハデバイス面保護膜を形成する工程を概念的に示すものであり、保護膜露光工程を示す図である。

【図3】本発明の第1実施形態を解説する為の半導体ウェハデバイス面保護膜を形成する工程を概念的に示すものであり、保護膜現像時の半導体ウェハの断面図である。

【図4】本発明の第1実施形態を解説する為の半導体ウェハデバイス面保護膜を形成する工程を概念的に示すものであり、スピンエッティング工程を示す図である。

【図5】本発明の第1実施形態を解説する為の半導体ウェハデバイス面保護膜を形成する工程を概念的に示すものであり、スピンエッティング工程中のウェハ端部の様子を示す図である。

【図6】本発明の第2実施形態を解説する為の半導体ウェハデバイス面保護膜を概念的に示すものであり、保護膜現像時の半導体ウェハの断面図である。

20

【符号の説明】

【0029】

10 半導体ウェハデバイス面保護膜

11 デバイス面

12 半導体ウェハ

20 光

21 フォトマスク

22 デバイス領域

40 エッティング液

30

41 ウェハ固定台

42 回転軸

70 密着向上層

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

---

フロントページの続き

(72)発明者 加藤 雅隆

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 今井 拓也

(56)参考文献 特開2001-223202 (JP, A)

特開2000-351214 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/306