(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2005-500687

(P2005-500687A)

(43) 公表日 平成17年1月6日(2005.1.6)

(51) Int.Cl.<sup>7</sup>H01L 21/3205

C25F 3/22

C25F 3/30

H01L 21/304

F 1

H01L 21/88

C25F 3/22

C25F 3/30

H01L 21/304

テーマコード(参考)

5FO33

審査請求 未請求 予備審査請求 有 (全 58 頁)

(21) 出願番号 特願2003-522140 (P2003-522140)

(86) (22) 出願日 平成14年8月15日 (2002.8.15)

(85) 翻訳文提出日 平成16年2月16日 (2004.2.16)

(86) 国際出願番号 PCT/US2002/026167

(87) 国際公開番号 WO2003/017330

(87) 国際公開日 平成15年2月27日 (2003.2.27)

(31) 優先権主張番号 60/313,086

(32) 優先日 平成13年8月17日 (2001.8.17)

(33) 優先権主張国 米国(US)

(71) 出願人 501209759

エーシーエム リサーチ, インコーポレイ

ティド

アメリカ合衆国, カリフォルニア 945

38, フレモント, スイート 610, フ

レモント ブールバード 46520

(74) 代理人 100099759

弁理士 青木 篤

(74) 代理人 100077517

弁理士 石田 敏

(74) 代理人 100087413

弁理士 古賀 哲次

(74) 代理人 100111903

弁理士 永坂 友康

最終頁に続く

(54) 【発明の名称】平面化法と電解研磨との組み合わせを使用する半導体構造物の形成

## (57) 【要約】

くぼみ区域及び非くぼみ区域を有する誘電性層を半導体ウェーハ上に形成することを含む、半導体構造物上の導電性層を平面化し、電解研磨する方法。導電性層を誘電性層上に形成して、くぼみ区域及び非くぼみ区域を被覆する。次いで導電性層表面を平面化して、表面のトポロジーの変動を減少させる。次いで平面化された導電性層を電解研磨して、非くぼみ区域を露出させる。

**【特許請求の範囲】****【請求項 1】**

半導体構造物を形成する方法であって、

半導体ウェーハ上に誘電性層を形成すること、ここでこの誘電性層はくぼみ区域及び非くぼみ区域を含む、

誘電性層上に導電性層を形成してくぼみ区域及び非くぼみ区域を被覆すること、

導電性層の表面を平面化して導電性層の表面のトポロジーの変動を減少させること、及び

導電性層の表面を平面化した後、導電性層を電解研磨して非くぼみ区域を露出させること

、

の工程を含む方法。

10

**【請求項 2】**

導電性層の表面の平面化工程が導電性層の化学的機械的研磨 (C M P) を包含する、請求項 1 に記載の方法。

**【請求項 3】**

C M P が導電性層の非くぼみ区域を露出させないで導電性層の表面を平面化する、請求項 2 に記載の方法。

**【請求項 4】**

C M P が研磨パッドを含み、そしてこの研磨パッドが導電性層の非くぼみ区域と接触しない、請求項 2 に記載の方法。

**【請求項 5】**

C M P が無スラリー研磨プロセスを包含する、請求項 2 に記載の方法。

20

**【請求項 6】**

導電性層の表面を平面化する工程が

導電性層の表面上に犠牲物質を形成すること、ここで前記犠牲物質は平面化される、及び

犠牲物質と導電性層の一部分とをエッチングすることを含む、請求項 1 に記載の方法。

**【請求項 7】**

エッチング工程が犠牲物質と導電性層との間の選択性をもたない、請求項 6 に記載の方法

。

**【請求項 8】**

犠牲物質がスピinn - on - ガラス (spin - on - glass) である、請求項 6 に記載の方法。

30

**【請求項 9】**

導電性層の形成工程が導電性層の析出を包含する、請求項 1 に記載の方法。

**【請求項 10】**

導電性層の形成工程が導電性層の電気めつきを包含する、請求項 1 に記載の方法。

**【請求項 11】**

導電性層と誘電性層との間に配置されたシード層を形成する工程をさらに含む、請求項 1 に記載の方法。

**【請求項 12】**

電解研磨工程が非くぼみ区域からシード層の一部分を除去する、請求項 11 に記載の方法

。

40

**【請求項 13】**

電解研磨工程が電解質流体の流れを導電性層表面に向けることを含む、請求項 1 に記載の方法。

**【請求項 14】**

電解研磨工程が電解質流体中に導電性層の少なくとも一部分を浸漬することを含む、請求項 1 に記載の方法。

**【請求項 15】**

導電性層と誘電性層との間に配置された遮壁層を形成する工程をさらに含む、請求項 1 に記載の方法。

**【請求項 16】**

50

プラズマ乾式エッチングにより、遮壁層を誘電性層の非くぼみ区域から除去する、請求項 15 に記載の方法。

【請求項 17】

湿式エッチングにより、遮壁層を誘電性層の非くぼみ区域から除去する、請求項 15 に記載の方法。

【請求項 18】

導電性層が銅である、請求項 1 に記載の方法。

【請求項 19】

導電性層を第 1 高さに平面化し、第 2 高さに電解研磨し、ここで第 2 高さは第 1 高さより低い、請求項 1 に記載の方法。

10

【請求項 20】

第 2 高さは非くぼみ区域の高さと同一平面である、請求項 19 に記載の方法。

【請求項 21】

第 2 高さが非くぼみ区域の高さより低い、請求項 19 に記載の方法。

【請求項 22】

半導体デバイスの製造方法であって

半導体構造物上に誘電性層を形成すること、ここでこの誘電性層はくぼみ区域及び非くぼみ区域を含む、

導電性層を形成して誘電性層を被覆し、かつ非くぼみ区域を充填すること、

導電性層表面を半導体構造物よりも上の第 1 高さに平面化すること、ここで第 1 高さは非くぼみ区域の高さより大きい、及び

導電性層表面を半導体構造物よりも上の第 2 高さに電解研磨すること、ここで第 2 高さは第 1 高さより低い、の工程を含む方法。

20

【請求項 23】

第 2 高さが非くぼみ区域の高さと同一平面である、請求項 22 に記載の方法。

【請求項 24】

第 2 高さが非くぼみ区域の高さより低い、請求項 22 に記載の方法。

【請求項 25】

導電性層の平面化工程が導電性層の化学的機械的研磨 (C M P) を包含する、請求項 22 に記載の方法。

30

【請求項 26】

C M P が導電性層の下に横たわる構造物を露出しない、請求項 25 に記載の方法。

【請求項 27】

C M P が研磨パッドを含み、そして研磨パッドが導電性層の下に横たわる構造物と接触しない、請求項 25 に記載の方法。

【請求項 28】

C M P が無スラリー研磨プロセスを包含する、請求項 25 に記載の方法。

【請求項 29】

導電性層表面を平面化する工程が

導電性層表面上に犠牲物質を形成すること、ここで前記犠牲物質は平面化される、及び犠牲物質及び導電性層をエッチングすること、ここで犠牲物質と導電性層との間に選択性が存在しない、の工程を含む、請求項 22 記載の方法。

40

【請求項 30】

犠牲物質がスピンドル - オン - ガラスである、請求項 29 に記載の方法。

【請求項 31】

導電性層の形成工程が導電性層の析出を包含する、請求項 22 に記載の方法。

【請求項 32】

導電性層の形成工程が導電性層の電気めっきを包含する、請求項 22 に記載の方法。

【請求項 33】

導電性層と誘電性層との間に配置されたシード層を形成する工程をさらに含む、請求項 2

50

2に記載の方法。

【請求項34】

電解研磨工程が非くぼみ区域からシード層の一部分を除去する、請求項33に記載の方法。

【請求項35】

電解研磨工程が電解質流体の流れを導電性層表面に向けることを含む、請求項22に記載の方法。

【請求項36】

電解研磨工程が電解質流体の中に導電性層の少なくとも一部分を浸漬することを含む、請求項22に記載の方法。

【請求項37】

導電性層と誘電性層との間に配置された遮壁層を形成する工程をさらに含む、請求項22に記載の方法。

【請求項38】

プラズマ乾式エッチングにより、遮壁層を誘電性層の非くぼみ区域から除去する、請求項37に記載の方法。

【請求項39】

湿式エッチングにより、遮壁層を誘電性層の非くぼみ区域から除去する、請求項37に記載の方法。

【請求項40】

導電性層が銅である、請求項22に記載の方法。

【請求項41】

相互接続構造物を作る方法であって、

半導体構造物を形成すること、ここで半導体構造物は開口でパターン化され相互接続を形成する、

半導体構造物の上にかつ開口内に導電性層を形成すること、

導電性層表面を平面化して非平面変動を減少させること、及び

平面化された導電性層を電解研磨して、開口内の導電性層を隔離すること、の工程を含む方法。

【請求項42】

半導体構造物がその中に形成された開口を有する誘電性層を含む、請求項41に記載の方法。

【請求項43】

半導体構造物が誘電性層と導電性層との間に形成された遮壁層をさらに含む、請求項42に記載の方法。

【請求項44】

プラズマ乾式エッチングにより、遮壁層を誘電性層の一部分から除去する、請求項43に記載の方法。

【請求項45】

湿式エッチングにより、遮壁層を誘電性層の一部分から除去する、請求項43に記載の方法。

【請求項46】

導電性層と誘電性層との間に配置されたシード層を形成することをさらに含む、請求項42に記載の方法。

【請求項47】

電解研磨工程がシード層の一部分を除去する、請求項46に記載の方法。

【請求項48】

導電性層表面を平面化する工程が導電性層の化学的機械的研磨(CMP)を含む、請求項41に記載の方法。

【請求項49】

10

20

30

40

50

CMPが導電性層の下に横たわる構造物を露出しない、請求項48に記載の方法。

【請求項50】

CMPが研磨パッドを含み、そして研磨パッドが導電性層の下に横たわる構造物と接触しない、請求項48に記載の方法。

【請求項51】

CMPが無スラリー研磨プロセスを包含する、請求項48に記載の方法。

【請求項52】

導電性層表面を平面化する工程が、

導電性層表面上に犠牲物質を形成すること、ここで前記犠牲物質は平面化される、及び犠牲物質と導電性層の一部分とをエッチングすること、ここで犠牲物質と導電性層との間に選択性が存在しないの工程を含む、請求項41記載の方法。 10

【請求項53】

犠牲物質がスピンドル - オン - ガラスである、請求項52に記載の方法。

【請求項54】

導電性層の形成工程が導電性層の析出を包含する、請求項41に記載の方法。

【請求項55】

導電性層の形成工程が導電性層の電気めっきを包含する、請求項41に記載の方法。

【請求項56】

電解研磨工程が電解質流体の流れを導電性層表面に向けることを含む、請求項41に記載の方法。 20

【請求項57】

電解研磨工程が電解質流体の中に導電性層の少なくとも一部分を浸漬することを含む、請求項41に記載の方法。

【請求項58】

導電性層が銅である、請求項41に記載の方法。

【請求項59】

導電性層、及び

くぼみ区域及び非くぼみ区域を有する誘電性層、を含み、

ここで導電性層は非くぼみ区域を充填して相互接続ラインを形成し、そして

導電性層表面を平面化し、次いで導電性層表面を電解研磨することによって、非くぼみ区域が露出されている、半導体構造物。 30

【請求項60】

導電性層が化学的機械的研磨(CMP)により平面化されている、請求項59に記載の構造物。

【請求項61】

CMPが誘電性層の非くぼみ区域を露出しない、請求項60に記載の構造物。

【請求項62】

導電性層が、

導電性層表面上に平面の犠牲物質を形成すること、及び

犠牲物質と導電性層の一部分とをエッチングすること、によって平面化されている、請求項60に記載の構造物。 40

【請求項63】

エッチング工程が犠牲物質と導電性層との間の選択性をもたない、請求項62に記載の構造物。

【請求項64】

犠牲物質がスピンドル - オン - ガラスを包含する、請求項62に記載の構造物。

【請求項65】

犠牲物質がフォトレジストを包含する、請求項62に記載の構造物。

【請求項66】

犠牲物質が金属を包含する、請求項62に記載の構造物。 50

**【請求項 6 7】**

請求項 1 に記載の方法により形成された半導体構造物。

**【請求項 6 8】**

請求項 2 に記載の方法に従い形成された半導体デバイス。

**【請求項 6 9】**

請求項 4 に記載の方法により半導体ウェーハ上に形成された半導体構造物。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、一般に半導体デバイス、さらに詳しくは、平面化法と電解研磨との組み合わせ 10 を使用する金属のダマスカス構造物を平面化する方法に関する。

**【背景技術】****【0 0 0 2】**

半導体デバイスは、トランジスタ及び相互接続素子をつくるために、多数の異なる加工工程を使用して半導体ウェーハ上に製造又は製作される。半導体ウェーハに関するトランジスタ端子を電気的に接続するために、導電性(例えば、金属の)トレンチ、バイアス(vias)、及びその他が誘電物質の中に半導体デバイスの一部分として形成される。トレンチ及びバイアスは、トランジスタ、半導体デバイスの内部回路、及び半導体デバイスに対して外部の回路間の電気信号及び電力を結合する。

**【0 0 0 3】**

相互接続素子の形成において、半導体ウェーハを、例えばマスクし、エッチングし、析出させて、半導体デバイスの必要な電子回路を形成する。特に、多数のマスキング及びエッチング工程を実施して、相互接続ラインのためのトレンチ及びバイアスとして働く誘電性層を半導体ウェーハ上に形成することができる。次いで、析出プロセスを実施して金属層を半導体ウェーハ上に析出させて、トレンチ及びバイアスの両方の中に、また誘電性層の非くぼみ区域上に金属を析出させる。くぼみ区域のパターンを隔離しつつ相互接続素子を形成するために、半導体ウェーハの非くぼみ区域上に析出した金属を除去する。

**【0 0 0 4】**

半導体ウェーハ上の誘電性層の非くぼみ区域上に析出された金属を除去する慣用法は、例えば、化学的機械的研磨(CMP)を包含する。CMP法は、誘電性層の非くぼみ区域を有するトレンチ及びバイアス内の金属層を研磨及び平面化して相互接続ラインを形成するために、半導体産業において広く使用されている。

**【0 0 0 5】**

CMPプロセスにおいて、ウェーハアセンブリを定盤又はウェブ上に位置するCMPパッド上に位置決定する。ウェーハアセンブリは、1又は2以上の層及び/又は形状物、例えば、誘電性層の中に形成された相互接続素子を有する支持体を包含する。次いで力を加えてCMPパッドに対してウェーハアセンブリをプレスする。CMPパッド及び支持体アセンブリを互いに対してかつ互いに關して動かすと同時に、力を加えてウェーハ表面を研磨しつつ平面化する。研磨溶液(しばしば研磨スラリーと呼ばれる)をCMPパッド上に小出しする。典型的には、研磨スラリーは研磨剤を含有し、化学的に反応性であってウェーハから不必要な物質、例えば、金属層を他の物質、例えば、誘電物質よりも急速に除去する。

**【発明の開示】****【発明が解決しようとする課題】****【0 0 0 6】**

したがって、CMPを使用してウェーハ上の表面の全体的及び局所的平面化を達成することができる。さらに、物質層を除去して下に横たわる構造物又は層を露出させるために、CMPを使用することができる。しかしながら、CMP法は、関係する比較的強い機械的力のために、下に横たわる半導体構造物に対していくつかの有害作用を有することがある。例えば、相互接続の位置関係が13ミクロン以下に動くとき、導電性物質、例えば、銅及

10

20

30

40

50

び典型的なダマスカスプロセスにおいて使用する  $k$  の低い薄層の機械的性質間に大きい差が存在することがある。例えば、 $k$  の低い誘電体薄層のヤング率は銅のそれよりも10倍よりも大きいことがある。結局、なかでも、C M P プロセスにおいて誘電体薄層及び銅に加えられる比較的強い機械的力は、層剥離、中低そり、浸蝕、薄層の浮き、引掻き又はその他を包含する応力に関係する欠陥を半導体構造物について引き起こすことがある。

【課題を解決するための手段】

【0007】

1つの例において、半導体構造物を形成する方法が提供される。この方法は、半導体ウェーハ上に誘電性層を形成し、ここで誘電性層はくぼみ区域及び非くぼみ区域を含み、誘電性層上に導電性層を形成してくぼみ区域及び非くぼみ区域を被覆し、導電性層表面を平面化して導電性層表面のトポロジーの変動を減少させ、次いで導電性層を電解研磨して非くぼみ区域を露出させることを包含する。

添付図面及び特許請求の範囲と組み合わせて詳細な説明を考慮すると、本発明はいっそう十分に理解されるであろう。

【発明を実施するための最良の形態】

【0008】

本発明をいっそう完全に理解できるようにするために、多数の特定の詳細、例えば、特定の物質、パラメーター、及びその他を後述する。しかしながら、説明は本発明の範囲を限定することを意図せず、その代わりに典型的な態様のよりすぐれた説明を提供することを認識すべきである。

【0009】

化学的機械的研磨(C M P)は半導体表面を平面化し、研磨する既知の方法であるが、C M Pは下に横たわる構造物に対して応力に関係する欠陥、例えば、中低そり、腐蝕、薄層の浮き、引掻き又はその他を引き起こすことがある。対照的に、電解研磨は比較的応力を含まない研磨法を提供する金属(例えば、銅)を研磨する方法である。しかしながら、後述するように、電解研磨は高さの差にかかわらずほぼ同一の速度で金属層をエッチングすることにおいて、等方的エッチングプロセスである。こうして、電解研磨前に金属層のトポロジーの構造又は一般的形状が非平面である場合、金属層のトポロジーの非平面構造又は一般的形状は典型的には電解研磨後に残留する。

【0010】

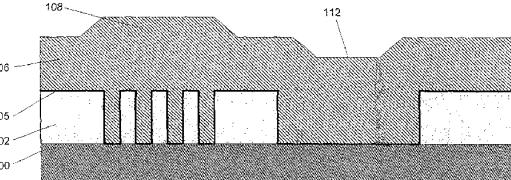

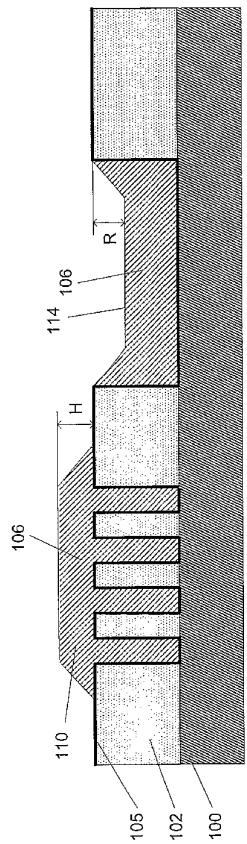

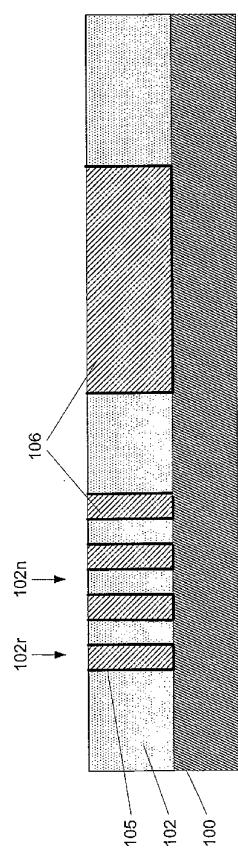

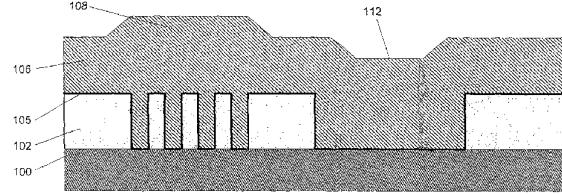

図1A及び図1Bは、非平面のトポロジーを有する半導体構造物を研磨する電解研磨法の典型的なプロセスフローを図解する。図1Aは、支持体100上に形成されたくぼみ区域及び非くぼみ区域でパターン化された誘電性層102を図解する。遮壁/シード層105は、誘電性層102及び支持体100上に形成されている。最後に、金属層106が、例えば、電気めっきにより、遮壁/シード層105上に析出されており、誘電性層102のくぼみ区域及び非くぼみ区域を被覆している。金属層106は、誘電性層中の種々の構造物上に位置するハンプ108及びくぼみ112を含む非平面のトポロジーを有する。金属層106の非平面のトポロジーは、例えば、電気めっきプロセスにおけるめっき化学により引き起こされることがある。

【0011】

次に図1Bを参照すると、くぼみ区域内の金属層106、すなわち、トレチングが隔離されて金属の相互接続ラインを形成するように、金属層106は典型的には非くぼみ区域の表面に研磨し戻される。一般に、くぼみ区域内の金属層106の上表面は、くぼみ区域内に形成された金属層106を取り囲む非くぼみ区域の上表面と同一平面であることが望ましい。

【0012】

平面に対する言及は、金属層106の上表面が非くぼみ区域の上表面と絶対的に同一平面であることを必要とするか、あるいは示唆することを意図せず、むしろ金属層106の上表面のレベルがくぼみ区域の上表面のレベルといっそう同一高さであることを知らせることを意図することを認識すべきである。こうして、金属層106の上表面のレベルとくぼみ区域の上表面のレベルとの間の変動を減少させることが一般に好都合である。

【0013】

10

20

30

40

50

この例において、金属層106を電解研磨することを仮定する。さらに、図1Aに描寫されているように、金属層106のトポロジーの構造又は一般的の形状は電解研磨前に非平面であることを仮定する。前述したように、電解研磨は等方的エッティングプロセスである。それ自体、図1Bに描寫されているように、金属層106のトポロジーの非平面構造又は一般的の形状は電解研磨後に残留することができる。

## 【0014】

さらに詳しくは、この例において、図1Aに描寫されているように、電解研磨前に、金属層106のトポロジーはハンプ108及びくぼんだ部分112を含むことを仮定する。図1Bに描寫されているように、電解研磨後に、ハンプ108及びくぼんだ部分112(図1A)は残留物110及びくぼみ114として残るることを仮定する。残留物110は誘電性層102より上の高さHである金属層106の領域である。残留物110は、残留物110より下のトレンチ領域中に形成した相互接続ライン間の電気短絡を引き起こすことがある。くぼみ114は金属層106中のくぼみ又はトレンチであり、ここでトレンチ内の金属層106の表面は誘電性層102の表面より下において深さRに存在する。くぼみ114はトレンチ内において金属及び銅を減少させ、これにより形成した相互接続ラインのコンダクタンスを低下させることができる。こうして、前述したように、非くぼみ区域の表面の上下における金属層106の表面高さの変動を減少させることが好都合である。

## 【0015】

したがって、1つの典型的な態様において、パターン化された誘電性層の上に形成された金属層を平面化した後、金属層を電解研磨して相互接続ラインを隔離する。電解研磨し戻す前に金属層を平面化する1つの利点は、慣用の平面化技術に比較して、金属層の下に横たわる構造物に対する損傷をより少なくし、こうして相互接続素子の信頼性を増加させて、金属の相互接続ラインを誘電性層中に形成することができる。なぜなら、構造物に対する大部分の損傷は、くぼみが形成された金属がCMPパッドに対して暴露されるとき、起こるからである。

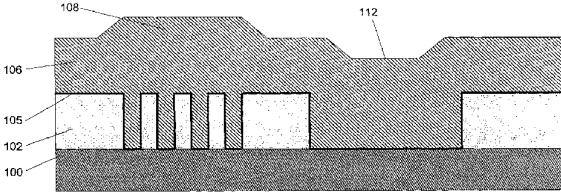

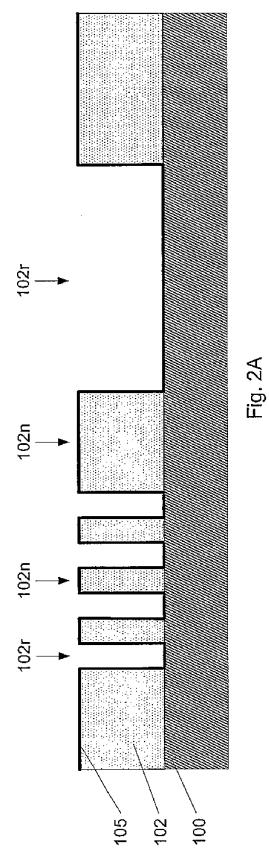

## 【0016】

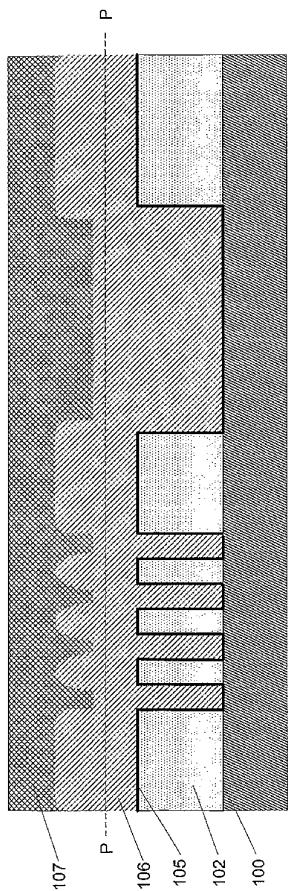

図2A～図2Dは、非平面のトポロジーを有する金属層106を含む典型的な半導体構造物を平面化し、電解研磨する方法の典型的なプロセスフローを図解する。図2Aは、誘電性層102中に形成されたくぼみ区域102r及び非くぼみ区域102nを有する典型的な半導体構造物の断面図を図解する。くぼみ区域102r及び非くぼみ区域102nは、誘電性層102中の相互接続ラインのパターンを形成する。任意の慣用の析出法、例えば、熱的又はプラズマ化学的気相成長法、スピinn - on、スパッタリング、又はその他を使用して、誘電性層102を支持体層100の上に好都合に析出し、形成することができる。さらに、既知のパターン化法、例えば、フォトマスキング、フォトリソグラフィー、マイクロリソグラフィー、又はその他により、誘電性層102をパターン化することができる。誘電物質は、例えば、二酸化ケイ素(SiO<sub>2</sub>)であることができる。多数の用途のために、低い誘電率を有する誘電性層物質(しばしば低“k”値物質と呼ばれる)を選択することが望ましい。低k値物質(すなわち、ほぼ3.0より低い)は、隣接ライン間のキャパシタンス結合及び「漏話」を減少させることによって、よりすぐれた相互接続ライン間の電気的隔離を提供する。このような低k値物質は、フッ化ケイ酸塩ガラス、ポリイミド、フッ化ポリイミド、ハイブリッド/複合体、シロキサン、有機ポリマー、[ ]-C:F、Si-O-C、パリレン/フッ化パリレン、ポリテトラフルオロエチレン、ナノ多孔質シリカ、ナノ多孔質有機物質、又はその他を包含する。

## 【0017】

誘電性層102を支持体層100上に形成する。支持体層100は、例えば、下に横たわる半導体ウェーハ、前もって形成された誘電性層、又は他の半導体構造物であることができる。支持体層100は、特定の用途に依存して、例えば、ケイ素及び/又は他の種々の半導体物質、又は、ヒ化ガリウム、又はその他を包含することができる。

## 【0018】

また、遮壁層がくぼみ区域102r内の誘電性層102の壁を含むパターン化された誘電性層102

10

20

30

40

50

を被覆するように、遮壁及び／又はシード層105を、種々の方法、例えば、化学的気相成長法(CVD)、物理的気相成長法(PVD)、原子層析出(ALD)、又はその他により析出させることができる。引き続いて金属層106が析出した後、遮壁層は金属(例えば、銅)が誘電性層102中に拡散するのを防止する働きをする(図2B)。誘電性層102の中への銅のいかなる拡散も、誘電性層102の誘電率を悪い方向に増加させる。遮壁／シード層105を、銅の拡散に對して抵抗性である適當な物質、例えば、チタン、タンタル、タングステン、窒化チタン、窒化タンタル、窒化タングステン、又は他の適當な物質から形成することができる。いくつかの用途において、遮壁層を省略することができる。例えば、誘電物質は金属層106の拡散に對して十分に抵抗性である場合、又は金属層106の拡散が半導体デバイスの性能に悪影響を及ぼさない場合、遮壁層を省略することができる。

10

#### 【0019】

例えば、金属層106が引き続いて誘電性層102上に電気めっきする場合、シード層が典型的には析出される。典型的には、シード層は金属層106をその上に電気めっきすることができる銅又は他の導電性物質の薄層である。さらに、遮壁／シード層105の單一層又は物質は遮壁層及びシード層の両方として働くことができる。

#### 【0020】

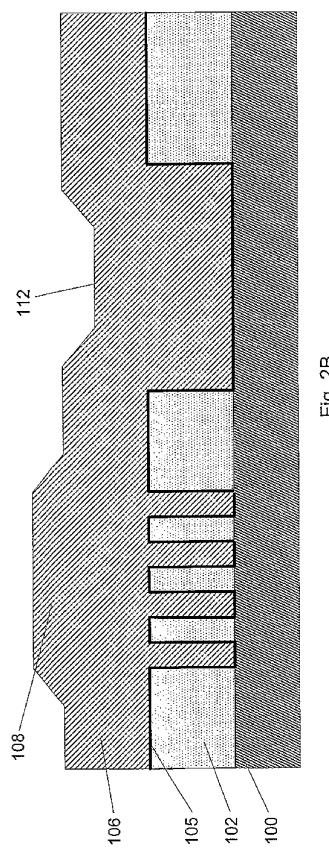

図2Bを次に参照すると、金属層106を遮壁／シード層105の表面上に、又は遮壁／シード層105を省略する場合、誘電性層102上に析出させる。金属層106はトレンチ又はくぼみ区域102rを充填し、また非くぼみ区域102nを被覆する。金属層106はPVD、CVD、ALD、電気めっき、無電解めっき、又は他の好都合な方法により析出させることができる。金属層106は、例えば、銅又は他の適當な導電性物質、例えば、アルミニウム、ニッケル、クロム、亜鉛、カドミウム、銀、金、ロジウム、パラジウム、白金、錫、鉛、鉄、インジウム、又はその他である。

20

#### 【0021】

図2Bに示すように、金属層106のトポロジーはそのトポロジーの変動と同一平面ではないことができる。例えば、金属層106の析出は誘電性層102の種々の形より上にハンプ108及び／又はくぼんだ部分112を生ずることがある。特に、金属層106を誘電性層102の上に電気めっきする場合、ハンプ108は誘電性層102の狭い高密度のトレンチ領域より上に形成することができ、そしてくぼんだ部分112は広い低密度のトレンチ領域より上に形成することができる。めっき化学のために、誘電性層102の上に金属層106を電気めっきする場合、この効果は特に支配的であることがある。しかしながら、ハンプ108及びくぼんだ部分112の形状及び位置は例示のみを目的とすること、及び金属層106の他の非平面トポロジーの特徴は第4A図及び第4B図に関して後述するように可能であることを認識すべきである。

30

#### 【0022】

次に図2Cを参照すると、金属層106を平滑に平面化するか、あるいはトポロジーの特徴を減少させる。例えば、化学的機械的研磨(CMP)プロセスを構造物に適用して、金属層106を研磨し、平面化することができる。CMP金属層106は、金属層106の電解研磨前に、金属層106のトポロジー、すなわち、ハンプ108、くぼみ112、及び他の非平面トポロジーの特徴を減少させて金属層106を平滑化する。例えば、CMPプロセスを実施して金属層106を下に横たわる支持体100より上の第1高さ“a”に研磨し、ここで“a”は誘電性層102の高さに等しい高さ“b”より高い。したがって、CMPプロセスは誘電性層102の非くぼみ区域102nからある距離を置いて金属層106を除去し、可能ならば誘電性層102との接触を防止する。むしろ、CMPプロセスは金属層106を研磨して金属層106を平面化し、そのトポロジーの変動を減少させる。

40

#### 【0023】

特別に金属層106を参照して、平面及び平面化に対する言及は、金属層106の表面が絶対的に平面であることを必要とするか、あるいは示唆することを意図せず、むしろ金属層106の表面がいっそう平滑又は平面であることを知らせることを意図することを認識すべきである。本質的に、金属層106の表面の平面化は、電解研磨前ににおける金属層106のトポロジーの変動を減少させる。

50

## 【0024】

CMP装置(図5)の研磨パッドは下に横たわる構造物、例えば、誘電性層102に直接接觸しないので、誘電性層102及び下に横たわる構造物の保存についてそれほど強調しないで、この典型的な方法のCMPプロセスは平面化効率について最適化可能である。例えば、下に横たわる誘電性層102を保存するように、研磨パッドの剛性又は硬度を調節することができる。この方法の例のCMP部分において、埋め込まれたダイヤモンド先端を有する剛性パッド又はその他を使用することができる。さらに、スラリー又は研磨剤を使用しない研磨プロセスを使用して、金属層106における引掻きを減少させることができる。

## 【0025】

研磨パッドの圧力は、特に銅及び低k誘電体膜を使用する統合スキームについて、パターン化された誘電性層102及び相互接続構造物に対する損傷の防除及び防止における1因子であることがある。典型的には、研磨パッドの圧力は0.1ポンド・力/平方インチ(PSI)~10PSIの範囲、例えば、5PSIである。CMPプロセス間に除去される金属層106の厚さは、少なくとも一部分、誘電性層102の上に形成された金属層106のトポロジー、及び使用するCMPプロセスの平面化効率に依存する。典型的には、除去される厚さは、金属層トポロジーの高い点と低い点との間の差より大きいか、あるいはそれに等しい。

## 【0026】

CMPプロセスは例示のみを目的としてここにおいて記載されることを認識すべきである。金属層106を平面化する別法を前述の典型的なCMPプロセスの代わりに、又はそれとともに使用することができる。例えば、犠牲物質を金属層106の上に添加して、金属層106より上の表面を平面化する。犠牲物質は導電性又は非導電性物質、例えば、スピノン・オン・ガラス(spin-on-glass)、フォトレジスト、金属合金、金属化合物、又はその他であることができる。次いで、例えば、犠牲物質と金属層106の一部分とをエッチング除去することによって、金属層106を平面化することができる。エッチングプロセスが犠牲層及び金属層106を同様な速度で除去するように、犠牲物質及び金属層106は同一又は同様なエッティング速度を有するべきである。平面化された金属層106及び犠牲層を同様な速度でエッティングして、犠牲層と金属層106の一部分とを除去すると、平面化された金属層106が生ずる。このプロセスの1例を図4Aに描写し、後述する。

## 【0027】

エッティングプロセスは、乾式エッティングプロセス又は湿式エッティングプロセスであることができる。乾式エッティングプロセスは、プラズマエッティング、化学的蒸気エッティング、及びその他を包含する。プラズマエッティング源は、高密度プラズマ源、例えば、ヘリコンプラズマ源、誘導結合プラズマ源(ICP)、及びその他を包含することができる。エッティングガスは、ハロゲングループ、例えば、塩素をベースとするガスを包含することができる。プラズマエッティングプロセスの条件の2例を下記表に詳述する：

## 【0028】

## 【表1】

## 高温プラズマエッティングプロセス

### の典型的なパラメーター

プラズマ電力 : 500~1500W、好ましくは800W

ガスの圧力 : 10~50 mTorr、好ましくは20 mTorr

ウェーハ温度 : 300~500 °C、好ましくは400 °C

エッティングガス : 塩素 (Cl<sub>2</sub>)

10

20

【 0 0 2 9 】

【表 2】

## 低温プラズマエッティングプロセス

### の典型的なパラメーター

工程1 :

プラズマ電力 : 500~1500W、好ましくは800W

30

ガスの圧力 : 10~50 mTorr、好ましくは20 mTorr

ウェーハ温度 : 100~100 °C、好ましくは50 °C

エッティングガス : 塩素 (Cl<sub>2</sub>)

40

【 0 0 3 0 】

工程1後、銅及び銅化合物の上部部分は塩化銅 (CuCl<sub>x</sub>) に変換されるであろう。

工程2 :

希薄HCl溶液を使用することによって、CuCl<sub>x</sub>化合物を湿式エッティングする。HCl濃度は1~6 wt%の範囲、好ましくは3 wt%であることができる。

【 0 0 3 1 】

選択的に、金属層106をめっきした後、アモルファスSi(a-Si)をガラス上でポリ-Siにアニールするために平坦なパネルディスプレイ産業において使用されている技術に類似する平面化技術に従い、レーザーを使用して銅を再流動化して、金属層106を緩和して平面化された表面を生じさせることができる。他の別法は、支持体100に対して平行な方向から

50

放射して、金属層106のより高い部分を蒸発により除去することができる、高い周波数の短いパルスのレーザーを包含する。レーザーの短いパルスを使用して、大部分の銅及び取り囲む誘電物質をレーザーにより発生した高温の作用から保護する、すなわち、熱電費を減少させる。レーザーは、固体レーザー、例えば、ルビーレーザー、Nd-ガラスレーザー、Nd:YAG(イットリウムアルミニウムガーネット、 $Y_3Al_5O_{12}$ )レーザー、気体レーザー、例えば、He-Neレーザー、CO<sub>2</sub>レーザー、HFレーザー、又はその他であることができる。レーザービームで支持体100の全表面上を走査して、金属層106を平面化する。さらに、このようなプロセスにおいて、非接触型表面トポロジーセンサーを終点検出器として使用することができる。この平面化プロセスの典型的な条件を下記表において詳述する：

【0032】

10

【表3】

### パルスドレーザー平面化プロセス

#### の典型的なパラメーター

平均レーザー電力： 100~5000W

20

パルス長さ： ピコ秒~マイクロ秒

ウェーハ温度： -100~20 °C

【0033】

次に図2Dを参照すると、金属層106を平面化した後、金属層106を電解研磨する。詳しくは、金属層106がくぼみ区域102r又はトレンチ内に隔離されて相互接続ラインを形成するよう、金属層106を誘電性層102の非くぼみ区域102nから電解研磨する。金属層106を非くぼみ区域と同一高さに研磨することができる。選択的に、金属層106を非くぼみ区域より下の高さに研磨することができる。電解質流体の流れ(図示せず)を金属層106に向ける電解研磨装置により、金属層106を電解研磨することができる(図6)。電解質流体は、例えば、任意の好都合な電解質流体、例えば、リン酸、オルトリン酸(H<sub>3</sub>PO<sub>4</sub>)、又はその他である。

30

【0034】

さらに、誘電性層102の非くぼみ区域102nの露出された領域から、遮壁/シード層105を除去する。層105がシード層であるか、あるいはそれを含む場合、例えば、金属層106を研磨する電解研磨プロセスはそれを除去することができる。層105が遮壁層であるか、あるいはそれを含む場合、例えば、プラズマ乾式エッティング、湿式エッティング又はその他はそれを除去することができる。さらに、金属層106を非くぼみ区域よりも低い高さに電解研磨した場合、非くぼみ区域をこの時においてエッティングして、表面を平面化することもできる。下記の表、表4は遮壁層を除去するプラズマ乾式エッティングプロセスにおいて使用できるパラメーターの典型的な範囲を提供する：

40

【0035】

【表4】

## プラズマ乾式エッチングプロセスの

### 典型的なパラメーター

プラズマ電力 : 500~2000W

真空 : 30~100 mTorr

ウェーハの温度 : ほぼ20 °C

気体及び流速 :  $SF_6 = 50 \text{ sccm}$  (又は $CF_4 = 50 \text{ sccm}$ 、又は $O_2 = 10 \text{ sccm}$ )

気体の圧力 : 0.1~50 mTorr

TaNの除去速度 : 250 nm/分

TiNの除去速度 : 300 nm/分

$SiO_2$ の除去速度 : 20 nm/分

10

20

30

30

40

### 【0036】

これらのパラメーターは、可能な誘電性層102物質である $SiO_2$ の除去速度よりも大きい、2つの可能な遮壁層105であるTaN及びTiNの除去速度を生ずる。遮壁層105の除去の間、下に横たわる誘電性層102のエッチング又は損傷を減少させるように、この方法において選択性を選択することができる。しかしながら、パラメーターを変化させることによって、他の選択性を得ることができますに注意すべきである。

### 【0037】

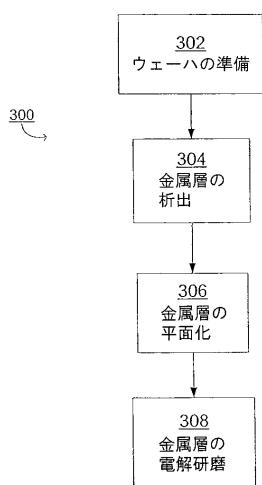

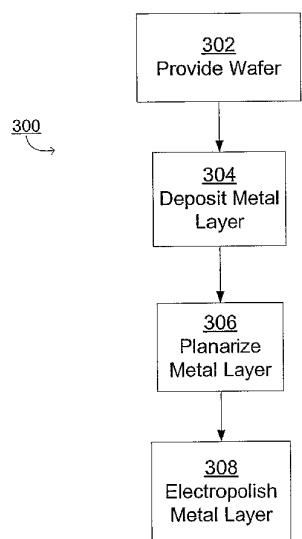

図3は、平面化プロセス及び電気めっきプロセスを包含する、典型的なダマスカスプロセス300を図解するフローチャートである。くぼみ区域及び非くぼみ区域を有するウェーハをプロック302において準備する。ウェーハ上に準備されたパターン化誘電性層は、くぼみ区域及び非くぼみ区域を定めることができる。他の前に形成された誘電性層、ウェーハ、又はその他を包含する、下に横たわる半導体構造物上に、パターン化誘電性層を形成することができる。さらに、加工の後の状態において個々の半導体デバイスに分離されるであろう、くぼみ区域及び非くぼみ区域を含む個々のダイスにウェーハを分割することができる。次いで、金属層が誘電性層内のくぼみ区域を充填し、ならびに誘電性層の非くぼみ区域を被覆するように、金属層をプロック304において析出させる。次いで、プロック306において金属層を平面化する。例えば、金属層をCMPプロセスに付して、金属層のトポロジーを平面化し、平滑化する。次いで、平面化された金属層をプロック308において電解研磨して、誘電性層の非くぼみ区域を露出させ、くぼみ区域内で金属層を隔離して金属の相互接続ラインを形成する。

### 【0038】

フローチャートに描写されている典型的なプロセス300に、多数の変更を加えることができるることを認識すべきである。例えば、遮壁ノシード層を必要に応じて加えた後、プロック304において金属層を析出させ、この場合において、非くぼみ区域を露出させた後、遮

40

50

壁 / シード層を誘電性層からエッティングする。さらに、図3における各ブロックは本明細書に明白に記載しなかった多数のプロセス、例えば、くぼみ区域を形成するマスキング及びエッティング、又は表面の平面化の前及び / 又は後における金属層のクレンジングを包含することができる。さらに、典型的なダマスカスプロセス300を单一及び二重のはめ込んだプロセスの両方に適用可能である。

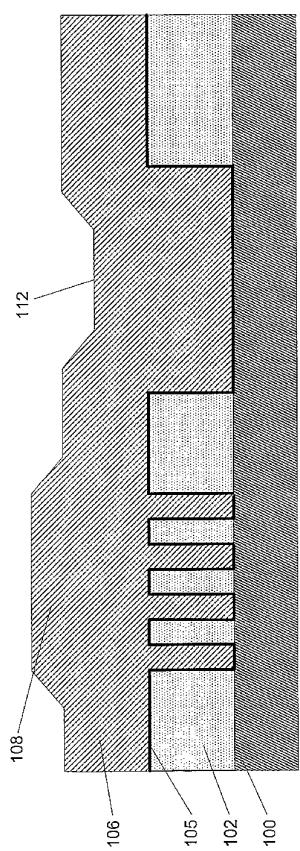

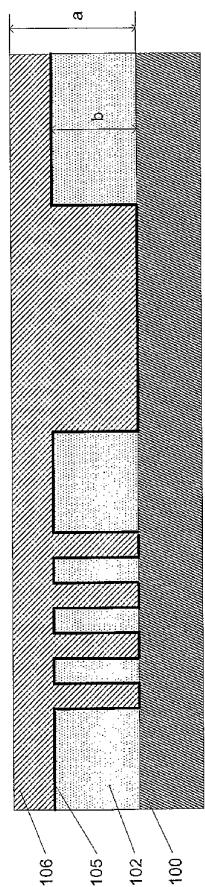

【0039】

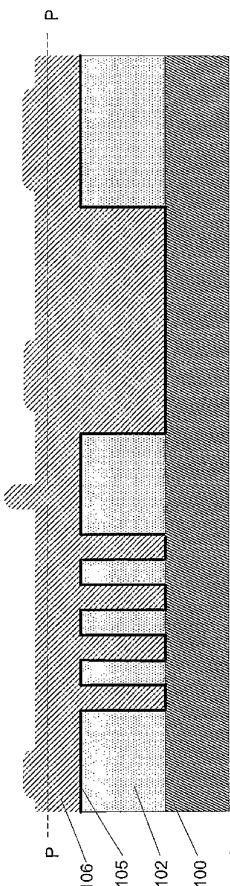

図4A及び図4Bは、平面化し、次いで電解研磨して相互接続構造物を形成することができる、金属層106の追加の典型的なトポロジーを図解する。図4Aを参照すると、金属層106は下に横たわる誘電性層102の形状に大よそ対応するトポロジーを有する。このようなトポロジーは、例えば、誘電性層102の上に金属層106をスパッタリングすることによってつくることができるであろう。次いで、犠牲物質107を添加し、次いで金属層106が破線“P”に平面化されるように、犠牲物質107と金属層106の一部分とをエッティングすることによって金属層106を平面化する。前述したように、犠牲物質107は金属、金属と溶媒との複合体、銅と溶媒との複合体、スピノン・オン・ガラス、フォトレジスト、又はその他であることができる。犠牲物質107は下に横たわる金属層106と同様なエッティング速度を有する任意の物質であることができ、そしてエッティングプロセスは犠牲物質107と金属層106との間の選択性をもたない、慣用の乾式又は湿式エッティングであることができる。

【0040】

ライン“P”的位置は例示のみを目的とし、用途及び平面化法に依存して上下に調節することができる。金属層106のトポロジーの特徴が平面化された後、図2Cと同様に、次いで図2Dに関して前述したように金属層106を電解研磨する。

【0041】

図4Bは、不規則の表面トポロジーを有する他の典型的な金属層106を図解する。金属層106の不規則な表面トポロジーは、析出法から下に横たわる構造物までの範囲の多数の原因のためであることがある。金属層106を図4Aと同様にまずライン“P”に表面を平面化し、犠牲物質を添加し、エッティングし戻し、金属層106をレーザー又はその他でしばらく加熱することによって研磨する。次いで金属層106を電解研磨する。図4A及び図4Bから、この方法により下に横たわる誘電性層102を不適当に損傷しないで多数の金属層を平面化し、電解研磨することができることを認識すべきである。

【0042】

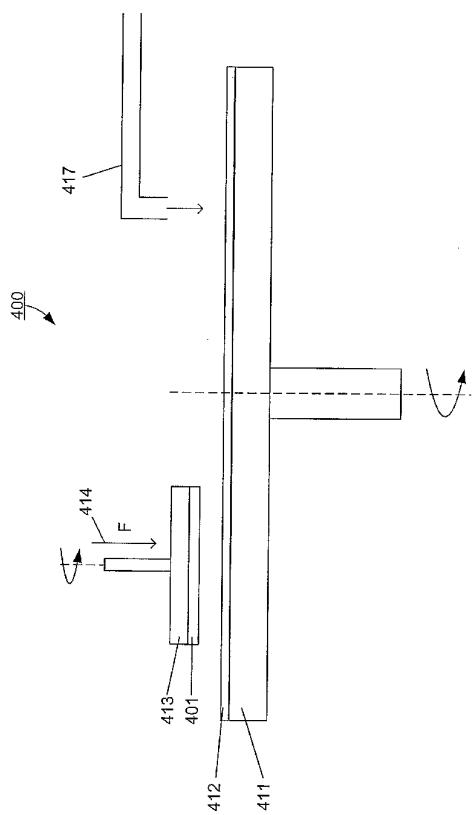

次に図5を参照すると、典型的なCMP装置400及びプロセスが記載されている。CMP装置400を使用して金属層106を平面化することができる。典型的なCMPプロセスは、ウェーハ表面を湿潤した研磨する表面に対してプレスし、回転することによって進行する。このプロセスはCMP装置400の化学的、圧力、及び温度の条件により制御される。典型的なCMP装置400は、回転可能な研磨定盤411と、研磨定盤411上に取り付けられた研磨パッド412とを含む。また、CMP装置400は回転可能なウェーハ担体413を含む。ウェーハ担体413はウェーハ401を位置決定し、矢印414で示す方向にウェーハ401に力を加える。ノズル417を通して化学的スラリーをCMP装置400に適用し、研磨パッド412上に小出しだす。化学的スラリーを、例えば、温度制御した貯蔵器(図示せず)からノズル417を通して供給する。さらに、化学的スラリーは研磨剤、例えば、アルミナ、シリカ、又はその他を含有し、これらは他の選択した化学物質とともに研磨剤として使用してウェーハ401の表面を研磨する。

【0043】

研磨速度に影響を与える主要なパラメーターは、研磨パッド414に対するウェーハ401上の下方向の圧力414、研磨定盤411及びウェーハ担体413の回転速度、化学的スラリーの組成及び温度、及び研磨パッド412の組成である。これらのパラメーターの調節は、研磨速度及びCMP装置400の平面化効率のコントロールを可能とする。

【0044】

図5を参照して記載したCMP装置400及びプロセスは例示のみを目的とする。他のCMP装置の立体配置及び構成を使用できることを認識すべきである。例えば、回転可能な研

10

20

30

40

50

磨定盤411及び研磨パッド412の代わりに、ウェーハ担体413に関して研磨パッド412を動かすベルトを使用することができる。また、認識されるように、研磨パッド412に関するウェーハ401の動きは、多数の方法で達成することができる。したがって、図5に描寫されているCMP装置400は、使用できるCMP装置又は方法の限定を意図しない。

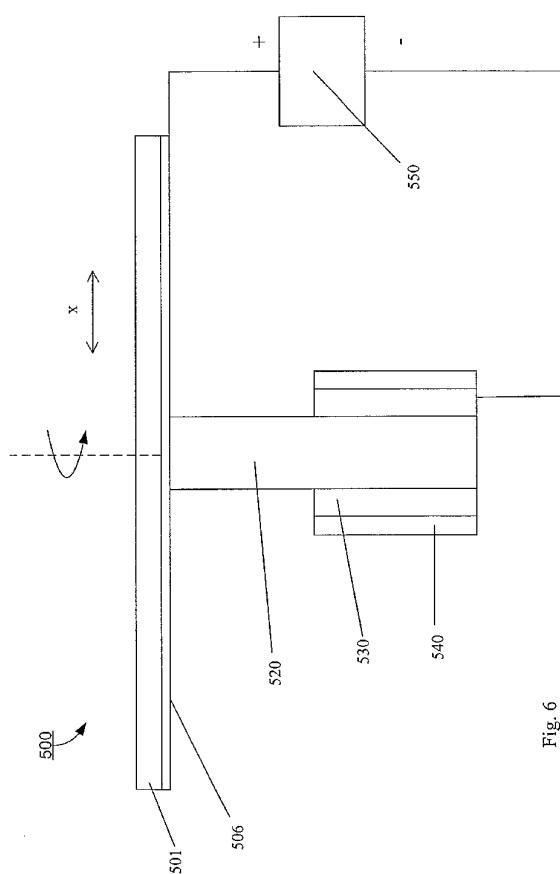

【0045】

図6は、半導体ウェーハ501上に形成された金属層506を電解研磨するために使用できる電解研磨装置500の典型的な断面図である。半導体ウェーハ501は、例えば、支持体層100、誘電性層102、及び遮壁／シード層105をさらに含むことができる(図2A～図2D)。さらに、金属層506のトポロジーは、電解研磨前に、例えば、CMP装置400(図5)により平面化されているであろう。

10

【0046】

電解研磨装置500のノズル540は、電解質流体520の流れを金属層506の表面に向ける。他の例において、ウェーハ501を電解質流体520中に完全に又は部分的に浸漬することができる。電解質流体520は、任意の慣用の電解研磨流体、例えば、リン酸、オルトリン酸( $H_3PO_4$ )、又はその他を包含する。例えば、1つの例において、電解質流体は約60wt%～約85wt%の濃度のオルトリン酸である。さらに、電解質流体520は、例えば、10～40%(酸の質量に対して)のグリコールを含むことができる。しかしながら、電解質流体の濃度及び組成は特定の用途に依存して変化させることを認識すべきである。

【0047】

電解研磨装置500が電解質流体520の流れを金属層506に向けるとき、電力供給装置550はノズル540中に位置決定された電極530(カソード)及び金属層506に結合された電極(アノード)に対抗する電荷を供給する。電力供給装置550は、例えば、一定電流又は一定電圧のモードで作動することができる。金属層506に関して電解質流体520を正に帯電させるように構成された電力供給装置550を使用して、金属層506の金属イオンを表面から除去する。この方法において、電解質流体520の流れはそれと接触する金属層506の部分を電解研磨する。

20

【0048】

さらに、図6に描寫されているように、ウェーハ501を回転しつつ軸Xに沿って並進させて、電解質流体520の流れ中に金属層506の表面を位置決定し、その表面を均一に電解研磨する。例えば、ウェーハ501を回転させると同時にX方向にウェーハ501を並進させることによって、電解質流体520は金属層506の表面に沿った螺旋状通路をたどることができる。選択的に、ウェーハ501を静止させて保持すると同時にノズル540を動かして、金属層506の必要な部分に電解質流体520の流れを適用する。さらに、ウェーハ501及びノズル540の両方を動かして、金属層506の必要な部分に電解質流体520の流れを適用することができる。電解研磨の方法及び装置の典型的な記載は下記の米国特許出願及び特許明細書に記載されている：米国特許出願No.09/497,894、発明の名称「半導体デバイス上の金属相互接続を電解研磨する方法及び装置」、2000年2月4日提出、及び米国特許No.6,395,152、発明の名称「半導体素子上の金属相互接続を電解研磨する方法及び装置」、1999年7月2日提出、それらの両方は引用することによって本明細書の一部とされる。

30

【0049】

さらに、他の電解研磨の方法及び装置を使用して金属層106を電解研磨できることを認識すべきである。例えば、金属層506を含む、ウェーハ501を電解質流体の浴内に部分的又は完全に浸漬することができる。

40

【0050】

上記説明は典型的な態様を例示するために提供され、限定を意図しない。当業者は理解するように、本発明の範囲内で多数の変更及び変形が可能である。例えば、单一又は二重のはめ込まれたダマスカス道具の中に形成された、多数の相互接続された構造物、例えば、誘電性層、遮壁層、シード層、及びマスク層の組み合わせを記載された方法に従い平面化し、電解研磨することができる。さらに、多数の平面化及び電解研磨の方法を組み合わせて、相互接続構造物を平面化及び電解研磨することができる。また、当業者にとって明らかにないように、本明細書に記載する理由以外の理由でつくられた、非平面のトポロジーを有

50

する金属層を、本明細書に記載した方法及び装置に従い、好都合に平面化及び電解研磨することができる。したがって、本発明は添付された特許請求の範囲により規定され、本明細書における記載により限定されない。

【図面の簡単な説明】

【0051】

【図1A-1B】半導体デバイスの典型的な電解研磨プロセスを図解する。

【図2A-2D】半導体デバイスの典型的な平面化及び電解研磨プロセスを図解する。

【図3】典型的なダマスカスプロセスのフローチャートを図解する。

【図4A-4B】平面化し、研磨することができる半導体構造物上に形成された金属層の典型的なトポロジーを図解する。

10

【図5】典型的な化学的機械的研磨装置の断面図を示す。

【図6】電解研磨装置の断面図を示す。

【図3】

Fig. 3

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

27 February 2003 (27.02.2003)

PCT

(10) International Publication Number

WO 03/017330 A2

(51) International Patent Classification: H01L (74) Agents: YIM, Peter, J. et al.; Morrison &amp; Foerster L.L.P., 435 Market Street, San Francisco, CA 94105-2482 (US).

(21) International Application Number: PCT/US02/20167

(81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, L.C, LK, LR, LS, LT, LU, LV, MA, MD, MG, MN, MW, MX, MZ, NO, NZ, OM, PII, PL, PT, RO, RU, SD, SE, SG, SI, SK, SL, TI, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VN, YU, ZA, ZM, ZW.

(22) International Filing Date: 15 August 2002 (15.08.2002)

(84) Designated States (regional): ARIPO patent (GII, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CTI, CY, CZ, DR, DK, EE, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data: 60/313,086 17 August 2001 (17.08.2001) US

(71) Applicant (for all designated States except US): ACM RESEARCH, INC. [US/US]; Suite 610, 46520 Fremont Boulevard, Fremont, CA 94538 (US).

(72) Inventors: and

(75) Inventors/Applicants (for US only): YAO, Xiang, Yu [US/US]; 1043 Ridgemont Drive, Milpitas, CA 95035 (US); CHANG, Ru, Kao [US/US]; 397 Preston Drive, Mountain View, CA 94040 (US); YIH, Peihaur [US]; 37171 Sycamore Street #824, Newark, CA 94560 (US); WANG, Hui [CN/US]; 38855 Litchfield Circle, Fremont, CA 94536 (US).

(80) Published: without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: FORMING A SEMICONDUCTOR STRUCTURE USING A COMBINATION OF PLANARIZING METHODS AND ELECTROPOLISHING

WO 03/017330 A2

(57) Abstract: A method for planarizing and electropolishing a conductive layer on a semiconductor structure includes forming a dielectric layer with recessed areas and non-recessed areas on the semiconductor wafer. A conductive layer is formed over the dielectric layer to cover the recessed areas and non-recessed areas. The surface of the conductive layer is then planarized to reduce variations in the topology of the surface. The planarized conductive layer is then electropolished to expose the non-recessed area.

**FORMING A SEMICONDUCTOR STRUCTURE USING A

COMBINATION OF PLANARIZING METHODS AND

ELECTROPOLISHING**

CROSS-REFERENCE TO RELATED APPLICATIONS

This present application claims priority of an earlier filed provisional application U.S. Serial No. 60/313,086, entitled A METHOD TO PLANARIZE COPPER DAMASCENE STRUCTURE USING A COMBINATION OF CMP AND ELECTRO-POLISHING, filed on August 17, 2001, the entire content of which is incorporated herein by reference.

BACKGROUND

1. Field

This invention relates generally to semiconductor devices, and more particularly to a method to planarize a metal damascene structure using a combination of planarizing methods and electropolishing.

2. Description of the Related Art

Semiconductor devices are manufactured or fabricated on semiconductor wafers using a number of different processing steps to create transistor and interconnection elements. To electrically connect transistor terminals associated with the semiconductor wafer, conductive (e.g., metal) trenches, vias, or the like are formed in dielectric materials as part of the semiconductor device. The trenches and vias couple electrical signals and power between transistors, internal circuit of the semiconductor devices, and circuits external to the semiconductor device.

In forming the interconnection elements the semiconductor wafer may undergo, for example, masking, etching, and deposition processes to form the desired electronic circuitry of the semiconductor devices. In particular, multiple masking and etching steps can be performed to form a pattern of recessed areas in a dielectric layer on a semiconductor wafer that serve as trenches and vias for the interconnection lines. A deposition process may then be performed to deposit a metal layer over the semiconductor wafer to deposit metal both in the trenches and vias and also on the non-recessed areas of the dielectric layer. To isolate the pattern of recessed areas and form interconnection elements, the metal deposited on the non-recessed areas of the semiconductor wafer is removed.

Conventional methods of removing the metal deposited on the non-recessed areas of the dielectric layer on the semiconductor wafer include, for example, chemical mechanical polishing (CMP). CMP methods are widely used in the semiconductor industry to polish and planarize the metal layer within the trenches and vias with the non-recessed areas of the dielectric layer to form interconnection lines.

In a CMP process, a wafer assembly is positioned on a CMP pad located on a platen or web. The wafer assembly includes a substrate having one or more layers and/or features, such as interconnection elements formed in a dielectric layer. A force is then applied to press the wafer assembly against the CMP pad. The CMP pad and the substrate assembly are moved against and relative to one another while applying the force to polish and planarize the surface of the wafer. A polishing solution, often referred to as polishing slurry, is dispensed on the CMP pad to facilitate the polishing. The polishing slurry typically contains an abrasive and is chemically reactive to selectively remove from the wafer the unwanted material, for example, a metal layer, more rapidly than other materials, for example, a dielectric material.

Accordingly, CMP may be used to achieve global and local planarization of a surface on the wafer. Furthermore, CMP may be used to remove a layer of material in order to expose an underlying structure or layer. CMP methods, however, can have several deleterious effects on the underlying semiconductor structure because of the relatively strong mechanical forces involved. For example, as interconnection geometries move to .13 microns and below, there can exist a large difference between the mechanical properties of the conductive materials, for example copper, and the low k films used in typical damascene processes. For instance, the Young Modulus of a low k dielectric film may be greater than 10 orders of magnitude lower than that of copper. Consequently, the relatively strong mechanical force applied on the dielectric films and copper in a CMP process, among other things, can cause stress related defects on the semiconductor structure that include delamination, dishing, erosion, film lifting, scratching, or the like.

#### BRIEF SUMMARY OF THE INVENTION

In one example, a method is provided for forming a semiconductor structure. The method includes forming a dielectric layer with recessed areas and non-recessed areas on the semiconductor wafer, forming a conductive layer over the dielectric layer to cover the recessed areas and non-recessed areas, planarizing the surface of the conductive layer to reduce variations in the topology of the surface of the conductive layer, and then electropolishing the conductive layer to expose the non-recessed areas.

The present invention is better understood upon consideration of the detailed description below in conjunction with the accompanying drawings and claims.

#### BRIEF DESCRIPTION OF THE DRAWINGS

Figs. 1A and 1B illustrate an exemplary electropolishing process of a semiconductor device;

Figs. 2A through 2D illustrate an exemplary planarizing and electropolishing process of a semiconductor device;

Fig. 3 illustrates a flow chart of an exemplary damascene process;

Figs. 4A and 4B illustrate exemplary topologies of a metal layer formed on a semiconductor structure that may be planarized and polished;

Fig. 5 illustrates a cross-sectional view of an exemplary chemical mechanical polishing apparatus;

Fig. 6 illustrates a cross-sectional view of an exemplary electropolishing apparatus.

#### DETAILED DESCRIPTION

In order to provide a more thorough understanding of the present invention, the following description sets forth numerous specific details, such as specific materials, parameters, and the like. It should be recognized, however, that the description is not intended as a limitation on the scope of the present invention, but is instead provided to enable a better description of the exemplary embodiments.

Chemical mechanical polishing (CMP) is a known method for planarizing and polishing a semiconductor surface, however, CMP can cause stress related defects to the underlying structures such as dishing, erosion, film lifting, scratching, or the like. In contrast, electropolishing is a process to polish metal (e.g., copper) that provides a relatively stress free polishing method. However, as

described below, electropolishing is an isotropic etching process, in that it etches a metal layer at approximately the same rate despite differences in height. Thus, if the profile or general shape of the topology of a metal layer is non-planar before being electropolished, then the non-planar profile or general shape of the topology of the metal layer typically remains after being electropolished.

Figs. 1A and 1B illustrate an exemplary process flow of an electropolishing method to polish a semiconductor structure that has a non-planar topology. Fig. 1A illustrates a dielectric layer 102 patterned with recessed and non-recessed areas formed over substrate 100. A barrier/seed layer 105 has been formed over the dielectric layer 102 and substrate 100. Finally, metal layer 106 has been deposited, for example, via electroplating, over barrier/seed layer 105 and covering the recessed and non-recessed areas of the dielectric layer 102. Metal layer 106 has a non-planar topology that includes a hump 108 and a recess 112 located over various structures in the dielectric layer. The non-planar topology of metal layer 106 can be caused, for example, by the plating chemistry in an electroplating process.

With reference now to Fig. 1B, metal layer 106 is typically polished back to the surface of the non-recessed areas such that metal layer 106 within the recessed areas, i.e., the trenches, is isolated to form metal interconnection lines. In general, it is desirable to have the top surface of metal layer 106 within the recessed area planar with the top surface of the non-recessed area surrounding metal layer 106 formed in the recessed area.

It should be recognized that references to planar are not intended to require or suggest that the top surface of metal layer 106 be absolutely planar with the top surface of the non-recessed area; rather, it is intended to convey that the level of the top surface of metal layer 106 is made more even with the level of the top surface of the recessed area. Thus, it is generally advantageous to reduce the

variation between the level of the top surface of metal layer 106 and the level of the top surface of the recessed area.

In this example, assume that metal layer 106 is electropolished. Additionally, as depicted in Fig. 1A, assume that the profile or general shape of the topology of metal layer 106 is non-planar prior to electropolishing. As noted above, electropolishing is an isotropic etching process. As such, as depicted in Fig. 1B, the non-planar profile or general shape of the topology of metal layer 106 can remain after electropolishing.

More particularly, in this example, as depicted in Fig. 1A, assume that the topology of metal layer 106 includes hump 108 and concave portion 112 prior to electropolishing. As depicted in Fig. 1B, assume that hump 108 and concave portion 112 (Fig. 1A) remain as residue 110 and recess 114 after electropolishing. Residue 110 is a region of metal layer 106 at a height H above the dielectric layer 102. Residue 110 can cause an electrical short circuit between interconnection lines formed in the trench regions below residue 110. Recess 114 is a recess or trench in metal layer 106 where the surface of metal layer 106 within the trench is at a depth R below the surface of the dielectric layer 102. Recess 114 results in metal or copper loss within the trench that can cause a reduction of the conductance of the formed interconnection lines. Thus, as noted above, it is advantageous to reduce the variation in the height of the surface of metal layer 106 above or below the surface of the non-recessed areas.

Accordingly, in one exemplary embodiment, a metal layer formed over a patterned dielectric layer is planarized prior to electropolishing the metal layer to isolate interconnection lines. One advantage to planarizing the metal layer prior to electropolishing the metal layer back is that the metal interconnection lines can be formed in the dielectric layer with less damage to the structure underlying the metal layer than conventional planarizing techniques, and thus increase the

reliability of the interconnection elements since most damage to the structure occurs when recessed metal is exposed to the CMP pad.

Figs. 2A through 2D illustrate an exemplary process flow of a method to planarize and electropolish an exemplary semiconductor structure including a metal layer 106 with a non-planar topology. Fig. 2A illustrates a cross-section view of an exemplary semiconductor structure with recessed areas 102r and non-recessed areas 102n formed in a dielectric layer 102. The recessed areas 102r and non-recessed areas 102n form a pattern of interconnection lines in dielectric layer 102. Dielectric layer 102 can be conventionally deposited and formed on substrate layer 100 using any conventional deposition method, such as thermal or plasma chemical vapor deposition, spin-on, sputtering, or the like. Further, dielectric layer 102 can be patterned through known patterning methods such as photomasking, photolithography, microlithography, or the like. The dielectric material may be, for example, silicon dioxide (SiO<sub>2</sub>). For many applications it is desired to select a dielectric layer material having a low dielectric constant, often referred to as a low "k" value material. Low k value materials (i.e., less than approximately 3.0) provide better electrical isolation between interconnection lines by reducing capacitance coupling and "cross-talk" between adjacent lines. Such low k value materials include fluorinated silicate glass, polyimides, fluorinated polyimides, hybrid/composites, siloxanes, organic polymers, [alpha]-C:F, Si-O-C, parylenes/fluorinated parylenes, polytetrafluoroethylene, nanoporous silica, nanoporous organic, or the like.

Dielectric layer 102 is formed on substrate layer 100. Substrate layer 100 may be, for example, an underlying semiconductor wafer, previously formed dielectric layers, or other semiconductor structures. Substrate layer 100 may include, for example, silicon and/or other various semiconductor materials, such as gallium arsenide, or the like depending on the particular application.

A barrier and/or seed layer 105 may also be deposited on the dielectric layer by various methods, such as chemical vapor deposition (CVD), physical vapor deposition (PVD), atomic layer deposition (ALD), or the like, such that the barrier layer covers the patterned dielectric layer 102 including the walls of dielectric layer 102 within the recessed areas 102r. A barrier layer serves to prevent metal (e.g., copper) from diffusing into the dielectric layer 102 after the subsequent metal layer 106 deposition (Fig. 2B). Any diffusion of copper into the dielectric layer 102 may adversely increase the dielectric constant of the dielectric layer 102. Barrier/seed layer 105 can be formed of a suitable conductive material that is resistant to the diffusion of copper, such as titanium, tantalum, tungsten, titanium-nitride, tantalum-nitride, tungsten-nitride, or other suitable material. In some applications, the barrier layer can be omitted. For example, if the dielectric material is sufficiently resistant to the diffusion of the metal layer 106, or if any diffusion of metal layer 106 will not adversely affect the performance of the semiconductor device, the barrier layer may be omitted.

A seed layer is typically deposited, for example, if metal layer 106 is subsequently electroplated over dielectric layer 102. A seed layer is typically a thin layer of copper or other conductive material that metal layer 106 can be electroplated onto. Further, a single layer or material of barrier/seed layer 105 may serve as both a barrier layer and a seed layer.

With reference now to Fig. 2B, metal layer 106 is deposited on the surface of the barrier/seed layer 105, or on the dielectric layer 102 if the barrier/seed layer 105 was omitted. Metal layer 106 fills the trenches or recessed areas 102r and also covers the non-recessed areas 102n. Metal layer 106 may be deposited by PVD, CVD, ALD, electroplating, electroless plating, or any other convenient method. Metal layer 106 is, for example, copper or other suitable conductive material such as aluminum, nickel, chromium, zinc, cadmium, silver, gold, rhodium, palladium, platinum, tin, lead, iron, indium, or the like.

As shown in Fig. 2B, the topology of metal layer 106 may be non-planar with variations in its topology. For example, the deposition of metal layer 106 can result in a hump 108 and/or concave portion 112 above various features of dielectric layer 102. In particular, if metal layer 106 is electroplated over the dielectric layer 102, a hump 108 can form above a narrow and high-density trench region, and a concave portion 112 can form above a wide low-density trench region of dielectric layer 102. The effects can be especially prevalent in the case of electroplating metal layer 106 over dielectric layer 102 because of the plating chemistry. It should be recognized, however, that the shape and location of hump 108 and concave portion 112 are illustrative only and that other non-planar topology features of metal layer 106 are possible as described below with respect to Figs. 4A and 4B.

With reference now to Fig. 2C, metal layer 106 is planarized to smooth or reduce features of the topology. For example, a chemical mechanical polishing (CMP) process is applied to the structure to polish and planarize metal layer 106. CMP metal layer 106 reduces the topology, i.e., hump 108, recess 112, and other non-planar topology features of the surface of metal layer 106 to smooth metal layer 106 prior to electropolishing metal layer 106. For example, the CMP process is performed to polish metal layer 106 to a first height "a" above the underlying substrate 100, where "a" is greater than a height "b," equal to the height of dielectric layer 102. Therefore, the CMP process stops short of removing metal layer 106 from the non-recessed areas 102n of dielectric layer 102 and possibly coming in contact with dielectric layer 102. Rather, the CMP process polishes metal layer 106 to planarize and reduce variations in the topology of metal layer 106.

It should be recognized that references to planar and planarizing, specifically in reference to metal layer 106, are not intended to require or suggest that the surface of metal layer 106 be absolutely planar; rather, it is intended to convey that the surface of metal layer 106 is made more smooth or planar.

Essentially, planarizing the surface of metal layer 106 reduces the variations in the topology of metal layer 106 prior to electropolishing.

The CMP process of this exemplary method can be optimized for planarization efficiency, with less emphasis placed on preserving dielectric layer 102 and the underlying structures because the polishing pad of the CMP apparatus (Fig. 5) does not directly contact the underlying structure, such as the dielectric layer 102. For example, the stiffness or hardness of a polishing pad may be adjusted to preserve underlying dielectric layer 102. A stiff pad with a diamond tip embedded therein or the like can be used in the CMP portion of this example of the method. Further, slurry free or abrasive-free polishing processes can be used to reduce scratches in metal layer 106.

The pressure of the polishing pad can be a factor in controlling and preventing damage to the patterned dielectric layer 102, and the interconnect structure, particularly for integration schemes with copper and low k dielectric films. Typically the pressure of the polishing pad ranges from 0.1 pound-force per square inch (PSI) to 10 PSI, for example 5 PSI. The thickness of metal layer 106 removed during the CMP process depends, at least in part, on the topography of the metal layer 106 formed over dielectric layer 102 and the planarization efficiency of the CMP process employed. Typically, the removal thickness is greater than or equal to the difference between a high and low point of the metal layer topology.

It should be recognized, however, that the CMP process is described herein for illustrative purposes only. Alternative methods of planarizing metal layer 106 may be used in place of, or with, the exemplary CMP process described above. For example, a sacrificial material may be added over metal layer 106 to planarize the surface above metal layer 106. The sacrificial material can be conductive or non-conductive such as spin-on-glass, photo-resist, metal alloy, metal compound, or the like. The metal layer 106 may then be planarized, for

example, by etching away the sacrificial material and portions of metal layer 106. The sacrificial material and metal layer 106 should have the same or similar etch rate such that an etching process removes the sacrificial layer and metal layer 106 at similar rates. Etching the planarized metal layer 106 and the sacrificial layer at similar rates to remove the sacrificial layer and portions of metal layer 106 will result in a planarized metal layer 106. An example of the process is depicted in Fig. 4A and described below.

The etching process can be a dry etching process or a wet etching process. A dry etching process includes plasma etching, chemical vapor etching, and the like. Plasma etching sources may include high-density plasma sources such as a helicon plasma source, inductive coupled plasma source (ICP), and the like. The etching gas may include a halogen group such as chlorine based gases. Two examples of the conditions for a plasma etching process are detailed in the following tables:

Table I

EXEMPLARY PARAMETERS OF HIGH TEMPERATURE

PLASMA ETCHING PROCESS

|                    |                                     |

|--------------------|-------------------------------------|

| Plasma power:      | 500 to 1500 W, preferably 800 W     |

| Gas pressure:      | 10 to 50 mTorr, preferably 20 mTorr |

| Wafer temperature: | 300 to 500 °C, preferably 400 °C    |

| Etching gases:     | Chlorine (Cl <sub>2</sub> )         |

Table II

EXEMPLARY PARAMETERS OF LOW TEMPERATURE

PLASMA ETCHING PROCESS

|                    |                                     |

|--------------------|-------------------------------------|

| Step 1:            |                                     |

| Plasma power:      | 500 to 1500 W, preferably 800 W     |

| Gas pressure:      | 10 to 50 mTorr, preferably 20 mTorr |

| Wafer temperature: | 20 to 100 °C, preferably 50 °C      |

| Etching gases:     | Chlorine (Cl <sub>2</sub> )         |

After Step 1 the top portion of copper and copper compound will be converted to copper chloride ( $\text{CuCl}_x$ ).

Step 2:

Wet etch  $\text{CuCl}_x$  compound by using dilute HCl solution. The concentration of HCl may be in the range of 1 to 6 percent by weight, preferably 3 percent.

Alternatively, a planarization technique similar to those used in the flat-panel display industry to anneal the amorphous Si (a-Si) to poly-Si on glass may be employed to reflow copper after plating metal layer 106 by using a laser to mollify metal layer 106 resulting in a planarized surface. Another alternative method includes a high frequency and short pulse laser that can be beamed from a direction parallel to the substrate 100 surface to remove higher portions of the topology of metal layer 106 by evaporation. The short pulse of the laser is used to protect bulk copper and surrounding dielectrics from the effects of high temperatures generated by the laser, i.e., reduce thermobudget. The laser can be a solid state laser such as a ruby laser, Nd-glass laser, Nd:YAG (yttrium aluminum garnet,  $\text{Y}_3\text{Al}_5\text{O}_{12}$ ) laser, gas laser, such as a He-Ne laser,  $\text{CO}_2$  laser, HF laser, or the like. The laser beam can be scanned over the entire surface of substrate 100 to planarize metal layer 106. Further, a non-contact type surface topography sensor can be used as an end-point detector in such a process. Exemplary conditions for this planarization process are detailed in the following table:

Table III

EXEMPLARY PARAMETERS OF PULSED LASER

PLANARIZATION PROCESS

|                      |                             |

|----------------------|-----------------------------|

| Average laser power: | 100 to 5000 W               |

| Pulse length:        | Picoseconds to microseconds |

| Wafer temperature:   | - 100 to 20 °C              |

With reference now to Fig. 2D, after metal layer 106 has been planarized, metal layer 106 is electropolished. Specifically, metal layer 106 is electropolished from the non-recessed areas 102n of dielectric layer 102 such that metal layer 106 is isolated within recessed areas 102r, or trenches, to form interconnection lines. Metal layer 106 can be polished to the same height as the non-recessed areas. Alternatively, metal layer 106 can be polished to a height below the non-recessed areas. Metal layer 106 can be electropolished by an electropolishing apparatus (Fig. 6) that directs a stream of electrolyte fluid (not shown) to metal layer 106. The electrolyte fluid is, for example, any convenient electropolishing fluid, such as phosphoric acid, orthophosphoric acid ( $H_3PO_4$ ), or the like.

Further, barrier/seed layer 105 is removed from the exposed regions of non-recessed areas 102n of dielectric layer 102. If layer 105 is, or includes, a seed layer, the electropolishing process that polishes metal layer 106 may remove it, for example. If layer 105 is, or includes, a barrier layer, plasma dry etching, wet etching, or the like may remove it, for example. Additionally, if the metal layer 106 was electropolished to a height less than the non-recessed areas, the non-recessed areas can also be etched at this time to planarize the surface. The following table, Table IV, provides an exemplary range of parameters that can be employed in a plasma dry etch process to remove the barrier layer:

Table IV

EXEMPLARY PARAMETERS OF PLASMA DRY ETCH

PROCESS

|                       |                                                                                       |

|-----------------------|---------------------------------------------------------------------------------------|

| Plasma Power:         | 500 to 2000 W                                                                         |

| Vacuum:               | 30 to 100 mTorr                                                                       |

| Temperature of Wafer: | approximately 20° C                                                                   |

| Gas and flow rate:    | SF <sub>6</sub> = 50 sccm (or CF <sub>4</sub> = 50 sccm, or O <sub>2</sub> = 10 sccm) |

| Gas pressure:         | 0.1 to 50 mTorr                                                                       |

| Removal rate of TaN:  | 250 nm/min                                                                            |

Removal rate of TiN: 300 nm/min

Removal rate of SiO<sub>2</sub>: 20 nm/min

These parameters result in a removal rate of TaN and TiN, two possible barrier layer 105 materials, greater than that of SiO<sub>2</sub>, a possible dielectric layer 102 material. The selectivity can be selected in this manner to reduce etching or damaging the underlying dielectric layer 102 during the removal of the barrier layer 105. It should be noted, however, that other selectivities can be obtained by varying the parameters.

Fig. 3 is a flow chart illustrating an exemplary damascene process 300 including a planarizing process and an electroplating process. A wafer having recessed and non-recessed areas is provided in block 302. A patterned dielectric layer provided on the wafer may define the recessed and non-recessed areas. The patterned dielectric layer may be formed on underlying semiconductor structures, including other previously formed dielectric layers, a wafer, or the like. Further, the wafer may be divided up into individual dice that include recessed and non-recessed areas that will be separated at a later state of the processing into individual semiconductor devices. A metal layer is then deposited in block 304, such that the metal layer fills the recessed areas within the dielectric layer as well as covers the non-recessed areas of the dielectric layer. The metal layer is then planarized in block 306. For example, the metal layer undergoes a CMP process to planarize and smooth the topography of the metal layer. The planarized metal layer is then electropolished in block 308 to expose the non-recessed areas of the dielectric layer and isolate the metal layer within the recessed areas to form metal interconnection lines.

It should be recognized that numerous modifications can be made to the exemplary process 300 depicted in the flow chart. For example, a barrier/seed layer can be optionally added prior to the deposition of the metal layer in block 304, in which case, after non-recessed areas are exposed, the barrier/seed layer is

etched from the dielectric layer. Additionally, each block in Fig. 3 can include many processes not explicitly described herein, such as masking and etching the wafer to form the recessed areas, or cleansing the metal layer before and/or after planarizing the surface. Further, the exemplary damascene process 300 is applicable to both single and dual inlaid applications.

Figs. 4A and 4B illustrate additional exemplary topologies of metal layer 106 that may be planarized and then electropolished to form interconnection structures. With regard to Fig. 4A, metal layer 106 has a topology that roughly corresponds to the shape of the underlying dielectric layer 102. Such a topology could be created, for example, by sputtering metal layer 106 over dielectric layer 102. Metal layer 106 is then planarized, for example, by adding a sacrificial material 107 and then etching back the sacrificial material 107 and a portion of metal layer 106 such that metal layer 106 is planarized to dotted line "P." As described above, sacrificial material 107 can be a metal, metal composites with solvent, such as copper with a solvent, spin-on glass, photo-resist, or the like. Sacrificial material 107 can be any material that has a similar etching rate as the underlying metal layer 106, and the etching process can be a conventional dry or wet etch with no selectivity between sacrificial material 107 and metal layer 106.

The location of line "P" is for illustrative purposes only, and can be adjusted up or down depending on the application and method of planarization. After the topology features of metal layer 106 have been planarized, similar to Fig. 2C, metal layer 106 is then electropolished as described above with regard to Fig. 2D.

Fig. 4B illustrates another exemplary metal layer 106 having an irregular surface topology. The irregular surface topology of metal layer 106 may be due to any number of causes ranging from the deposition method to the underlying structure. Metal layer 106 is polished similar to Fig. 4A by first planarizing the surface to line "P," by CMP polishing, adding a sacrificial material and etching

back, momentarily heating metal layer 106 with a laser or the like. Metal layer 106 is then electropolished. It should be recognized from Figs. 4A and 4B that numerous metal layer topologies can be planarized and electropolished by this method without undue damage to the underlying dielectric layer 102.

With reference now to Fig. 5, an exemplary CMP apparatus 400 and process are described. CMP apparatus 400 may be used to planarize metal layer 106. An exemplary CMP process proceeds by pressing and rotating the surface of a wafer against a wetted polishing surface. The process is controlled through the chemical, pressure, and temperature conditions of CMP apparatus 400. Exemplary CMP apparatus 400 includes a rotatable polishing platen 411 and a polishing pad 412 mounted on polishing platen 411. CMP apparatus 400 also includes a rotatable wafer carrier 413 that positions and applies a force to a wafer 401 in the direction indicated by arrow 414. A chemical slurry is supplied to CMP apparatus 400 through nozzle 417 and dispensed onto the polishing pad 412. The chemical slurry is, for example, supplied from a temperature-controlled reservoir (not shown) through nozzle 417. Further, the chemical slurry contains a polishing agent, such as alumina, silica, or the like that is used as an abrasive agent along with other selected chemicals to polish the surface of wafer 401.

The primary parameters that affect the polishing rate are the down pressure 414 on the wafer 401 against polishing pad 412, the rotational speeds of the polishing platen 411 and wafer carrier 413, the composition and temperature of the chemical slurry, and the composition of polishing pad 412. Adjustments of these parameters permit control of the polishing rate and the planarization efficiency of CMP apparatus 400.

CMP apparatus 400 and the process described with reference to Fig. 5, are for illustrative purposes only. It should be recognized that other CMP apparatus configurations and set-ups may be employed. For example, rotatable polishing platen 411 and polishing pad 412 can be replaced with a belt that moves polishing

pad 412 with respect to wafer carrier 413. Also, as will be recognized, the movement of wafer 401 with respect to polishing pad 412 can be achieved in numerous manners. Therefore, the CMP apparatus 400 depicted in Fig. 5 is not intended to be limiting of the CMP apparatus or method that may be used.

Fig. 6 illustrates an exemplary cross-sectional view of an electropolishing apparatus 500 that can be used to electropolish metal layer 506 formed on semiconductor wafer 501. Semiconductor wafer 501 may further include, for example, substrate layer 100, dielectric layer 102, and barrier/seed layer 105 (Figs. 2A through 2D). Further, the topology of metal layer 506 will have been planarized prior to the electropolishing, for example, by CMP apparatus 400 (Fig. 5).

A nozzle 540 of the electropolishing apparatus 500 directs a stream of electrolyte fluid 520 to the surface of metal layer 506. In other examples, wafer 501 can be completely or partially immersed in electrolyte fluid 502. Electrolyte fluid 520 includes any convenient electropolishing fluid, such as phosphoric acid, orthophosphoric acid ( $H_3PO_4$ ), or the like. For example, in one example the electrolyte fluid is orthophosphoric acid having a concentration between about 60 percent by weight and about 85 percent by weight. Additionally, electrolyte fluid 106 can include, for example, glycol at 10 to 40 percent (against weight of the acid). It should be recognized, however, that the concentration and composition of the electrolyte fluid can vary depending on the particular application.

As electropolishing apparatus 500 directs a stream of electrolyte fluid 520 to metal layer 506, a power supply 550 supplies opposing charges to an electrode 530 (the cathode) positioned in nozzle 540 and an electrode (the anode) coupled to metal layer 506. Power supply 550 can, for example, operate at a constant current or constant voltage mode. With power supply 550 configured to positively charge the electrolyte fluid 520 relative to metal layer 506, metal ions of metal layer 506 are removed from the surface. In this manner the stream of

electrolyte fluid 520 electropolishes the portion of metal layer 506 in contact with the stream of electrolyte fluid 520.

Further, as depicted in Fig. 6, wafer 501 is rotated and translated along axis X to position the entire surface of metal layer 506 in the stream of electrolyte fluid 520 and uniformly electropolish the surface. For example, the electrolyte fluid 520 can make a spiral path along the surface of metal layer 506 by rotating wafer 501 while simultaneously translating wafer 501 in the X direction.

Alternatively, wafer 501 can be held stationary while nozzle 540 is moved to apply the stream of electrolyte 520 to desired portions of metal layer 506.

Further, both wafer 501 and nozzle 540 can move to apply the stream of electrolyte 520 to desired portions of metal layer 506. Exemplary descriptions of electropolishing methods and apparatus may be found in U.S. Patent Application No. 09/497,894, entitled METHODS AND APPARATUS FOR ELECTROPOLEISHING METAL INTERCONNECTIONS ON SEMICONDUCTOR DEVICES, filed on February 4, 2000, and related U.S. Patent No. 6,395,152, entitled METHODS AND APPARATUS FOR ELECTROPOLEISHING METAL INTERCONNECTIONS ON SEMICONDUCTOR DEVICES, filed on July, 2, 1999, both of which are incorporated herein by reference in their entirety.

Additionally, it should be recognized that other electropolishing methods and apparatus can be employed to electropolish metal layer 106. For example, wafer 501, including metal layer 506, may be partially or fully immersed within a bath of electrolyte fluid.

The above detailed description is provided to illustrate exemplary embodiments and is not intended to be limiting. It will be apparent to those skilled in the art that numerous modifications and variations within the scope of the present invention are possible. For example, numerous interconnect structures, such as combinations of dielectric layers, conductive layers, barrier layers, seed

layers, and mask layers, formed in single or dual inlaid damascene implementations, can be planarized and electropolished with the methods described. Further, numerous methods of planarizing and electropolishing can be combined to planarize and electropolish the surface of the interconnection structures. It should also be apparent to those skilled in the art that metal layers with non-planar topologies, created for reasons other than those described herein, can be advantageously planarized and electropolished in accordance with the methods and apparatus described. Accordingly, the present invention is defined by the appended claims and should not be limited by the description herein.

## CLAIMS

We claim:

1. A method of forming a semiconductor structure, comprising:

- forming a dielectric layer on a semiconductor wafer, wherein the dielectric layer includes recessed areas and non-recessed areas;

- forming a conductive layer over the dielectric layer to cover the recessed areas and non-recessed areas;

- planarizing the surface of the conductive layer to reduce variations in the topology of the surface of the conductive layer; and

- electropolishing the conductive layer to expose the non-recessed areas after planarizing the surface of the conductive layer.

2. The method of claim 1, wherein the act of planarizing the surface of the conductive layer includes chemical mechanical polishing (CMP) the conductive layer.

3. The method of claim 2, wherein the CMP planarizes the surface of the conductive layer without exposing the non-recessed areas of the conductive layer.

4. The method of claim 2, wherein the CMP includes a polishing pad, and the polishing pad does not contact the non-recessed areas of the conductive layer.

5. The method of claim 2, wherein the CMP includes a slurry free polishing process.

6. The method of claim 1, wherein the act of planarizing the surface of the conductive layer includes:

forming a sacrificial material on the surface of the conductive layer, wherein said sacrificial material is planarized, and

etching the sacrificial material and a portion of the conductive layer.

7. The method of claim 6, wherein the act of etching has no selectivity between the sacrificial material and the conductive layer.

8. The method of claim 6, wherein the sacrificial material is spin-on-glass.

9. The method of claim 1, wherein forming a conductive layer includes depositing the conductive layer.

10. The method of claim 1, wherein forming a conductive layer includes electroplating the conductive layer.

11. The method of claim 1, further comprising forming a seed layer disposed between the conductive layer and the dielectric layer.

12. The method of claim 11, wherein the act of electropolishing removes portions of the seed layer from the non-recessed areas.

13. The method of claim 1, wherein the act of electropolishing includes directing a stream of electrolyte fluid to the surface of the conductive layer.

14. The method of claim 1, wherein the act of electropolishing includes immersing at least a portion of the conductive layer in electrolyte fluid.

15. The method of claim 1, further comprising forming a barrier layer disposed between the conductive layer and the dielectric layer.

16. The method of claim 15, wherein the barrier layer is removed from the non-recessed areas of the dielectric layer by plasma dry etching.

17. The method of claim 15, wherein the barrier layer is removed from the non-recessed areas of the dielectric layer by wet etching.

18. The method of claim 1, wherein the conductive layer is copper.

19. The method of claim 1, wherein the conductive layer is planarized to a first height and electropolished to a second height, wherein the second height is less than the first height.

20. The method of claim 19, wherein the second height is planar with a height of the non-recessed areas.

21. The method of claim 19, wherein the second height is less than a height of the non-recessed areas.

22. A method of making a semiconductor device, comprising:

forming a dielectric layer on a semiconductor structure, wherein the dielectric layer includes recessed areas and non-recessed areas;

forming a conductive layer to cover the dielectric layer and fill the non-recessed areas;

planarizing the conductive layer to a first height above the semiconductor structure, wherein the first height is greater than a height of the non-recessed areas; and

electropolishing the conductive layer to a second height above the semiconductor structure, wherein the second height is less than the first height.

23. The method of claim 22, wherein the second height is planar with the height of the non-recessed areas.

24. The method of claim 22, wherein the second height is less than the height of the non-recessed areas.

25. The method of claim 22, wherein the act of planarizing the conductive layer includes chemical mechanical polishing (CMP) the conductive layer.

26. The method of claim 25, wherein the CMP does not expose the structure underlying the conductive layer.

27. The method of claim 25, wherein the CMP includes a polishing pad, and the polishing pad does not contact the structure underlying the conductive layer.

28. The method of claim 25, wherein the CMP includes a slurry free polishing process.

29. The method of claim 22, wherein the act of planarizing the conductive layer includes:

forming a sacrificial material on the surface of the conductive layer, wherein said sacrificial material is planarized, and

etching the sacrificial material and the conductive layer with no selectivity between the sacrificial material and the conductive layer.

30. The method of claim 29, wherein the sacrificial material is spin-on-glass.

31. The method of claim 22, wherein forming a conductive layer includes depositing the conductive layer.

32. The method of claim 22, wherein forming a conductive layer includes electropolishing the conductive layer.

33. The method of claim 22, further comprising forming a seed layer disposed between the conductive layer and the dielectric layer.

34. The method of claim 33, wherein the act of electropolishing removes a portion of the seed layer from the non-recessed areas.

35. The method of claim 22, wherein the act of electropolishing includes directing a stream of electrolyte fluid to the surface of the conductive layer.

36. The method of claim 22, wherein the act of electropolishing includes immersing at least a portion of the conductive layer in electrolyte fluid.

37. The method of claim 22, further comprising forming a barrier layer disposed between the conductive layer and the dielectric layer.

38. The method of claim 37, wherein the barrier layer is removed from the non-recessed areas of the dielectric layer by plasma dry etching.

39. The method of claim 37, wherein the barrier layer is removed from the non-recessed areas of the dielectric layer by wet etching.

40. The method of claim 22, wherein the conductive layer is copper.

41. A method for making an interconnection structure, comprising:

- forming a semiconductor structure, wherein the semiconductor structure is patterned with openings to form interconnection lines;

- forming a conductive layer over the semiconductor structure and within the openings;

- planarizing the surface of the conductive layer to reduce non-planar variations; and

- electropolishing the planarized conductive layer to isolate the conductive layer within the openings.

42. The method of claim 41, wherein the semiconductor structure includes:

- a dielectric layer with openings formed therein.

43. The method of claim 42, wherein the semiconductor structure further includes:

- a barrier layer formed between the dielectric layer and the conductive layer.

44. The method of claim 43, wherein the barrier layer is removed from portions of the dielectric layer by plasma dry etching.

45. The method of claim 43, wherein the barrier layer is removed from portions of the dielectric layer by wet etching.

46. The method of claim 42, further comprising forming a seed layer disposed between the conductive layer and the dielectric layer.

47. The method of claim 46, wherein the act of electropolishing removes a portion of the seed layer.

48. The method of claim 41, wherein the act of planarizing the surface of the conductive layer includes chemical mechanical polishing (CMP) the conductive layer.

49. The method of claim 48, wherein the CMP does not expose the structure underlying the conductive layer.

50. The method of claim 48, wherein the CMP includes a polishing pad, and the polishing pad does not contact the structure underlying the conductive layer.

51. The method of claim 48, wherein the CMP includes a slurry free polishing process.

52. The method of claim 41, wherein the act of planarizing the surface of the conductive layer includes:

- forming a sacrificial material on the surface of the conductive layer, wherein said sacrificial material is planarized, and

- etching the sacrificial material and a portion of the conductive layer with no selectivity between the sacrificial material and the conductive layer.

53. The method of claim 52, wherein the sacrificial material is spin-on-glass.

54. The method of claim 41, wherein forming a conductive layer includes depositing the conductive layer.

55. The method of claim 41, wherein forming a conductive layer includes electroplating the conductive layer.

56. The method of claim 41, wherein the act of electropolishing includes directing a stream of electrolyte fluid to the surface of the conductive layer.

57. The method of claim 41, wherein the act of electropolishing includes immersing at least a portion of the conductive layer in electrolyte fluid.

58. The method of claim 41, wherein the conductive layer is copper.

59. A semiconductor structure, comprising:

- a conductive layer; and

- a dielectric layer having recessed areas and non-recessed areas,

- wherein the conductive layer fills the non-recessed areas to form interconnection lines, and

- the non-recessed areas are exposed by planarizing and then electropolishing the surface of the conductive layer.

60. The structure of claim 59, wherein the conductive layer is planarized by chemical mechanical polishing (CMP).

61. The structure of claim 60, wherein the CMP does not expose the non-recessed areas of the dielectric layer.

62. The structure of claim 60, wherein the conductive layer is planarized by:

- forming a planar sacrificial material on the surface of the conductive layer, and

- etching the sacrificial material and a portion of the conductive layer.

63. The structure of claim 62, wherein the act of etching has no selectivity between the sacrificial material and the conductive layer.

64. The method of claim 62, wherein the sacrificial material includes spin-on-glass.

65. The method of claim 62, wherein the sacrificial material includes photo-resist.

66. The method of claim 62, wherein the sacrificial material includes metal.

67. A semiconductor structure formed in accordance with the method of claim 1.

68. A semiconductor device formed in accordance with the method of claim 22.

69. An interconnect structure formed on a semiconductor wafer in accordance with the method of claim 41.

Fig. 1A

Fig. 1B

Fig. 2A

Fig. 2B

WO 03/017330

5/10

PCT/US02/26167

Fig. 2C

Fig. 2D

Fig. 3

WO 03/017330

8/10

PCT/US02/26167

Fig. 4A

Fig. 4B

Fig.5

WO 03/017330

10/10

PCT/US02/26167

Fig. 6

## 【国際公開パンフレット（コレクトバージョン）】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

27 February 2003 (27.02.2003)

PCT

(10) International Publication Number

WO 03/017330 A3(51) International Patent Classification: H01L 21/302,

21/461, 21/4763, 23/48, 23/52

(21) International Application Number: PCT/US02/26167

(22) International Filing Date: 15 August 2002 (15.08.2002)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

60/313,086 17 August 2001 (17.08.2001) US(71) Applicant (for all designated States except US): ACM

RESEARCH, INC. [US/US]; Suite 610, 46520 Fremont

Boulevard, Fremont, CA 94538 (US).

(72) Inventors: and

(75) Inventors/Applicants (for US only): YAO, Xiang, Yu

[US/US]; 1043 Ridgemond Drive, Milpitas, CA 95035

(US); CHANG, Ru, Kao [US/US]; 397 Preston Drive,

MOuntain View, CA 94040 (US); VITH, Pelhaar [—/US];

37171 Sycamore Street #824, Newark, CA 94560 (US);

WANG, Hui [CN/US]; 38855 Litchfield Circle, Fremont,

CA 94536 (US).(74) Agents: YIM, Peter, J. et al.: Morrison & Fosner LLP,

435 Market Street, San Francisco, CA 94105-2482 (US).(81) Designated States (national): A1, AG, A1, AM, AT, AU,

AZ, BA, BB, BG, BR, BY, BZ, CA, CI, CN, CO, CR, CU,

CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GI,

GM, IIR, IIU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC,

LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW,

MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SD, SE, SG,

SI, SK, SL, TI, TM, TN, TR, TT, TZ, UA, UG, US, UZ,

VN, YU, ZA, ZM, ZW.(84) Designated States (regional): ARIPO patent (GH, GM,

KE, LS, MW, MZ, SD, SI, SZ, TZ, UG, ZM, ZW),

Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM),

European patent (AL, BL, BG, CH, CY, CZ, DE, DK, EL,

ES, FI, FR, GR, HU, IT, LU, MC, NL, PT, SI, SK,

TR), OAPI patent (BJ, CN, CG, CI, CM, GA, GN, GQ,

GW, MI, MR, NE, SN, TD, TG).Published:

with international search report(88) Date of publication of the international search report:

24 July 2003

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(54) Title: FORMING A SEMICONDUCTOR STRUCTURE USING A COMBINATION OF PLANARIZING METHODS AND

ELECTROPOLISHING

WO 03/017330 A3

(57) Abstract: A method for planarizing and electropolishing a conductive layer on a semiconductor structure includes forming a dielectric layer with recessed areas and non-recessed areas on the semiconductor wafer. A conductive layer is formed over the dielectric layer to cover the recessed areas and non-recessed areas. The surface of the conductive layer is then planarized to reduce variations in the topology of the surface. The planarized conductive layer is then electropolished to expose the non-recessed area.

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                 | International application No.<br>PCT/US02/28167 |