(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) 。 Int. Cl.

G09G 3/20 (2006.01)

(45) 공고일자 2006년11월27일

(11) 등록번호 10-0650104

(24) 등록일자 2006년11월20일

|             |                   |             |                 |

|-------------|-------------------|-------------|-----------------|

| (21) 출원번호   | 10-2001-7002226   | (65) 공개번호   | 10-2001-0072838 |

| (22) 출원일자   | 2001년02월21일       | (43) 공개일자   | 2001년07월31일     |

| 심사청구일자      | 2004년07월06일       |             |                 |

| 번역문 제출일자    | 2001년02월21일       |             |                 |

| (86) 국제출원번호 | PCT/US1999/015588 | (87) 국제공개번호 | WO 2000/13167   |

| 국제출원일자      | 1999년07월08일       | 국제공개일자      | 2000년03월09일     |

EP 유럽특허 : 오스트리아, 벨기에, 스위스, 리히텐슈타인, 독일, 덴마크, 스페인, 프랑스, 영국, 그리스, 아일랜드, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투칼, 스웨덴, 핀란드, 사이프러스,

(30) 우선권주장 09/144,675 1998년08월31일 미국(US)

(73) 특히권자 켄데스센트 테크날러지스 코퍼레이션

미합중국 캘리포니아주 95153 산조스 바이어 텔 오르오 6580

모리스데이비드

미합중국켈리포니아주95132산죠스엘그랜드커트3644

스캔넬윌리엄

미합중국캘리포니아주94025멘로파크링우드1041

## 스핀디트크리스토퍼

미합중국캘리포니아주94025멘로파크힐사이드아벤툐115

## (74) 대리인 손창규

심사관 : 박부식

전체 청구항 수 : 총 5 항

#### (54) 전계 방출 디스플레이 장치의 조절을 위한 방법

### (57) 요약

본 발명은 새로 제작된 전계 방출 디스플레이에서 불순물 입자를 제거하는 방법에 관한 것이다. 불순물 입자는, a) 전계 방출 디스플레이(FED)의 양극(20)을 미리 정해진 전압으로 구동하고; b) 양극이 미리 정해진 전압에 도달한 뒤, FED의 방출 전류를 서서히 증가시키고; c) 방출된 전자들(40)에 의해 떨어져 나갔거나 달리 분리된 이온 및 입자들을 포획하기 위한 이온-포집 장치를 제공하는 단계들을 포함하는 조절 공정에 의해 제거된다. 양극을 미리 정해진 전압으로 구동하고 FED의 방출 전류를 서서히 증가시킴으로써, FED를 손상시킬 없이 불순물 입자가 효과적으로 제거된다. 본 발명은 또한 작동 및 정지 동안에 게이트로부터 방출체로의 전류를 방지하는 FED의 작동 방법을 제공하는바, 이는 a) 양극 디스플레이 스크린(20)을 동작하고; 및 b) 양극 디스플레이 스크린이 동작된 뒤, 전자-방출체(40)를 동작하는 단계들을 포함하는 것으로 구성되어 있다. 방출체가 동작하기 전에, 양극 디스플레이 스크린이 미리 정해진 전압에 도달하기에 충분한 시간을 허여함으로써, 방출된 전자들(40)은 양극(20)으로 이끌리게 된다.

## 내용도

도 5

## 특허청구의 범위

### 청구항 1.

- a) 전자 방출용 전자-방출 소자, 전자-방출 소자로부터의 전자 방출을 제어하기 위한 게이트 전극, 이온-포집 장치(ion-trapping device), 및 전자들을 모으는 디스플레이 스크린을 전계 방출 디스플레이에 제공하고;

- b) 미리 정해진 양극 전압을 디스플레이 스크린에 구동시켜, 디스플레이 스크린과 전자-방출 소자 사이에 전압 차동(voltage differential)을 이루도록 디스플레이 스크린을 동작하고;

- c) 디스플레이 스크린의 동작에 뒤이어, 전자들이 디스플레이 스크린쪽으로 향하고 전자들이 게이트 전극에 충돌하는 것을 실질적으로 방지할 수 있도록 전압 차동이 이루어질 때까지, 전자-방출 소자로부터의 실질적인 전자 방출을 지연시킨 뒤, 미리 정해진 게이트 전압을 게이트 전극에 구동시켜 게이트 전극을 동작하고;

- d) 게이트 전극의 동작에 뒤이어, 디스플레이 스크린의 전압을 미리 정해진 수준으로 낮추고;

- e) 디스플레이 스크린의 전압을 낮추는 것에 뒤이어, 게이트 전극의 전압을 증가시켜 방출 전류를 증가시키고; 및

- f) 디스플레이 스크린의 문턱 전압에 도달할 때까지 상기 단계(d)와 (e)를 반복하는;

것을 포함하는 것으로 구성된 전계 방출 디스플레이의 조절방법.

### 청구항 2.

제 1항에 있어서, 디스플레이 스크린이 양극으로 구성되어 있는 전계 방출 디스플레이의 조절방법.

### 청구항 3.

삭제

### 청구항 4.

삭제

### 청구항 5.

제 1항에 있어서, 전자-방출 소자가 원추형 전자 방출체(conical electron emitter)로 구성되는 전계 방출 디스플레이의 조절방법.

**청구항 6.**

제 5항에 있어서, 원추형 전자 방출체가 몰리브덴 팁(molybdenum tip)으로 구성되는 전계 방출 디스플레이의 조절방법.

**청구항 7.**

제 1항에 있어서,

g) 게이트 전극의 동작을 정지시켜 전자 방출을 더 방지하고; 및

h) 게이트 전극의 동작을 정지시킨데 뒤이어, 디스플레이 스크린의 동작을 정지시켜 전자들이 게이트 전극에 충돌하는 것을 방지하는 단계를 더 포함하는 전계 방출 디스플레이의 조절방법.

**청구항 8.**

삭제

**청구항 9.**

삭제

**청구항 10.**

삭제

**청구항 11.**

삭제

**청구항 12.**

삭제

**청구항 13.**

삭제

**청구항 14.**

삭제

**청구항 15.**

삭제

**청구항 16.**

삭제

**청구항 17.**

삭제

**청구항 18.**

삭제

**청구항 19.**

삭제

**청구항 20.**

삭제

**청구항 21.**

삭제

**청구항 22.**

삭제

**청구항 23.**

삭제

**청구항 24.**

삭제

**청구항 25.**

삭제

명세서

## 기술분야

본 발명은 평판 패널 디스플레이 스크린의 분야에 관련되어 있다. 더욱 구체적으로, 본 발명은 평판 패널 전계 방출 디스플레이 스크린(flat panel field emission display screen)의 분야에 관련되어 있다. 본 명세서에는 전계 방출 디스플레이 장치에서 작동(turning-on) 및 정지(turning-off) 요소를 위한 과정 및 장치가 개시되어 있다.

## 배경기술

표준 음극선관(CRT)처럼, 평판 패널 전계 방출 디스플레이(flat panel field emission display: FED)는 형광 스크린의 영상 요소(화소: pixel)에 고 에너지 전자를 충돌시켜 광을 발생시킨다. 그러면, 들뜬(excited) 형광물질은 전자 에너지를 가시 광으로 변경시킨다. 그러나, 형광 스크린을 가로질러 레스터 패턴(raster pattern)으로 주사하는 단일 또는 경우에 따라서는 세 개의 전자빔을 사용하는 통상적인 CRT 디스플레이와는 달리, FED는 각 화소의 각 색상 소자(color element)용 정적 전자빔(stationary electron beam)을 사용한다. 이것은 통상적인 CRT의 주사 전자빔용으로 요구되는 거리와 비교하여 매우 좁은 전자 소스로부터 스크린까지의 거리를 요구한다. 또한, FED는 CRT보다 훨씬 적은 전력을 소비한다. 이러한 요소들은 FED를 랩탑 컴퓨터, 포켓-TV, 개인 디지털 장비, 및 휴대용 전자 게임기 등과 같은 휴대용 전자 장치에 이상적인 것으로 만든다.

FED와 관련된 하나의 문제점은 FED 진공 튜브가 미세한 량의 불순물을 포함할 수 있다는 것인데, 이들은 전자-방출 소자(electron-emissive element), 전면판(faceplate), 게이트 전극(gate electrode: 유전층과 금속층을 포함) 및 공간벽(spacer wall)의 표면에 붙어있을 수 있다. 이러한 불순물은 충분한 에너지의 전자들에 의해 피폭되면(bombarded) 제거될 수도 있다. 따라서, 이들 불순물은, FED가 켜지거나(switch-on) 또는 꺼질(switch-off) 때, FED 진공 튜브내에서 높은 이온압(high ionic pressure)의 작은 구역(zone)들을 형성할 가능성이 매우 높다. 게이트가 방출체(emitter)에 대해 상대적으로 양(positive)이라는 사실과 더불어, 고 이온압의 존재는 방출체로부터 게이트 전극으로의 전자 방출을 용이하게 한다. 그 결과, 몇몇 전자는 디스플레이 스크린보다는 게이트 전극에 충돌할 수도 있다. 이러한 상황은 게이트 전극의 과열을 야기시킬 수 있다. 게이트 전극으로의 방출은 방출체와 게이트 전극 사이의 전압 차동(voltage differential)에 영향을 미칠

수도 있다. 더불어, 전자는 전자-방출 소자와 게이트 전극 사이의 이격거리를 뛰어넘기 때문에, 전류의 발광 방전(luminous discharge)이 관찰될 수도 있다. 정밀한 전자-방출체의 심각한 손상이 초래될 수도 있다. 자연히, "알킹(arcing)"으로 알려져 있는 이러한 현상은 매우 바람직하지 않다.

통상적으로, 알킹 문제를 피하는 하나의 방법은 FED 진공 튜브를 손으로 문질러서 불순 물질을 제거하는 것이다. 그러나, 그러한 방법으로 모든 불순물을 제거하는 것은 어렵다. 또한, 수동으로 문지르는 공정은 시간 소모적이고 노동 집약적이므로 FED 스크린의 제작비용을 불필요하게 상승시킨다.

따라서, 본 발명은 FED 스크린으로부터 불순물 입자들을 제거하는 향상된 방법을 제공한다. 본 발명은 또한 작동(turn-on) 및 정지(turn-off) 기간동안에 게이트로부터 방출체로의 전류(gate-to-emitter current)를 방지하기 위한 전계 방출 디스플레이의 향상된 작동방법을 제공한다. 앞에서 상세히 기술하지 않은 본 발명의 이들 잇점 및 기타 잇점은 이하 본 발명의 개시와 함께 분명해질 것이다.

## 발명의 상세한 설명

본 발명은 새로 제작된 전계 방출 디스플레이내의 불순 물질을 제거하는 방법을 제공한다. 본 발명의 하나의 실시예에 따르면, a) 전계 방출 디스플레이(FED)의 양극을 미리 정해진 전압으로 구동하고; b) 양극이 미리 정해진 전압에 도달한 후에 FED의 방출 전류를 서서히 증가시키며; 및, c) 방출 전자들에 의해 떨어진 이온 및 불순물을 포획하는 이온-포집 장치(ion-trapping device)를 제공하는 단계들을 포함하는 조절 공정(conditioning process)에 의해, 불순물 입자가 제거된다. 이러한 실시예에서, 양극을 미리 정해진 전압으로 구동하고 FED의 방출 전류를 서서히 증가시킴으로써, 불순물 입자들은 FED의 손상없이 효과적으로 제거된다.

본 발명은 또한 작동(turn-on) 및 정지(turn-off) 동안에 게이트로부터 방출체로의 전류(gate-to-emitter current)를 방지하는 FED의 작동방법을 제공한다. 이러한 실시예에서, 상기 방법은 a) 양극 디스플레이 스크린을 동작하고(enabling), b) 양극 디스플레이 스크린이 동작된 뒤, 전자-방출체를 미리 정해진 시간 동작하는 단계들을 포함한다. 이러한 실시예에서, 방출체가 동작하기 전에 양극 디스플레이 스크린이 미리 정해진 전압에 도달하도록 충분한 시간을 허여함으로써, 방출 전자는 양극으로 끌어당겨지게 될 것이다. 이러한 방법에서, 게이트로부터 방출체로의 전류는 FED가 작동될 때 효과적으로 제거된다. 본 실시예에서, 양극 디스플레이 스크린은 미리 정해진 고 전압을 디스플레이 스크린에 인가함으로써 동작되고, 전자-방출체는 FED의 게이트 전극과 방출체 전극에 적당한 전압을 구동함으로써 동작된다.

본 발명의 또 다른 실시예에서, 게이트로부터 방출체로의 전류를 방지하기 위한 전계 방출 디스플레이의 작동방법은, a) 방출체를 미리 정해진 시간동안 동작억제하고(disabling), b) 전자-방출체가 동작억제된 뒤, 양극 디스플레이 스크린을 동작억제하는 단계들을 포함한다. 이러한 실시예에서, 양극 디스플레이 스크린을 동작억제하기 전에 전자 방출체가 동작억제되도록 충분한 시간을 허여함으로써, 모든 잔류 전자는 양극으로 끌어당겨지게 될 것이다. 이러한 방법으로, 게이트로부터 방출체로의 전류는 FED의 정지 과정 동안에 제거된다. 본 실시예에서, 양극 디스플레이 스크린은 FED의 양극에 그라운드 전압(ground voltage)을 인가함으로써 동작억제되고, 전자 방출체는 게이트 전극과 방출체 전극을 그라운드 전압으로 구동함으로써 동작억제된다.

본 발명의 실시예들은 상기의 것을 포함하고, 전계 방출 디스플레이의 작동방법을 더 포함하는데, 이러한 작동방법은, 전자 방출을 위한 전자-방출 소자(electron-emissive element), 전자-방출 소자로부터의 전자 방출을 제어하기 위한 게이트 전극(gate electrode), 및 전자를 모으기 위한 디스플레이 스크린(display screen)을 전계 방출 디스플레이에 제공하고; 디스플레이 스크린과 전자-방출 소자 사이에 전압 차동(voltage differential)을 이루도록 디스플레이 스크린을 동작하고; 및, 디스플레이 스크린의 동작에 뒤이어, 전자들이 디스플레이 스크린을 향하도록 하고 전자들이 게이트 전극에 충돌하는 것을 실질적으로 방지하도록 전압 차동이 이루어질 때까지, 전자-방출 소자로부터의 실질적인 전자 방출을 지연시킴으로써 게이트 전극을 동작하는 단계들을 포함하는 것으로 구성된다.

본 발명의 실시예들은, 후면판(baseplate); 후면판상의 다수의 전자-방출 소자; 전자-방출 소자로부터의 전자 방출을 제어하기 위한 후면판상의 게이트 전극; 후면판으로부터 떨어져 있고 전자-방출 소자로부터 방출된 전자를 모으도록 구성되어, 이미지를 생성하는 디스플레이 스크린; 및, 전자-방출 소자로부터의 실질적인 전자 방출 이전에 디스플레이 스크린과 전자-방출 소자 사이에 전압 차동이 이루어지도록 하여, 전계 방출 디스플레이 장치의 작동 기간에 실질적인 게이트로부터 방출체로의 전류를 방지하는, 전자-방출 소자로의 전자 흐름을 제어하도록 구성된 제어회로;를 포함하는 것으로 구성된 전계 방출 디스플레이 장치를 더 포함한다.

## 실시예

본 발명의 하기 실시예를 참조하여 설명하는바, 실시예들은 첨부 도면에도 개시되어 있다. 본 발명은 본 실시예들과 관련하여 설명되는 반면에, 본 발명은 이들 실시예들에 한정되는 것으로 의도되지 말아야 한다. 한편, 본 발명은 대체, 변경, 등 가의 것을 포함하는데, 이들은 하기 청구범위에 의해 정의된 본 발명의 범주내에 포함될 수 있다. 또한, 하기 기재에는, 설명 목적으로, 본 발명의 완전한 이해를 제공하기 위하여 다수의 특정 예들이 개시되어 있다. 그러나, 본 발명의 당업자가 이러한 개시내용을 읽는다면, 본 발명이 이들 특정 예들에 대한 설명 없이도 실시될 있다는 것이 명백해 진다. 예로서, 본 발명의 본질이 흐려지는 것을 피하기 위하여 공지 구조 및 장치를 자세히 기재하지는 않는다.

### 전계 방출 디스플레이의 일반적인 설명

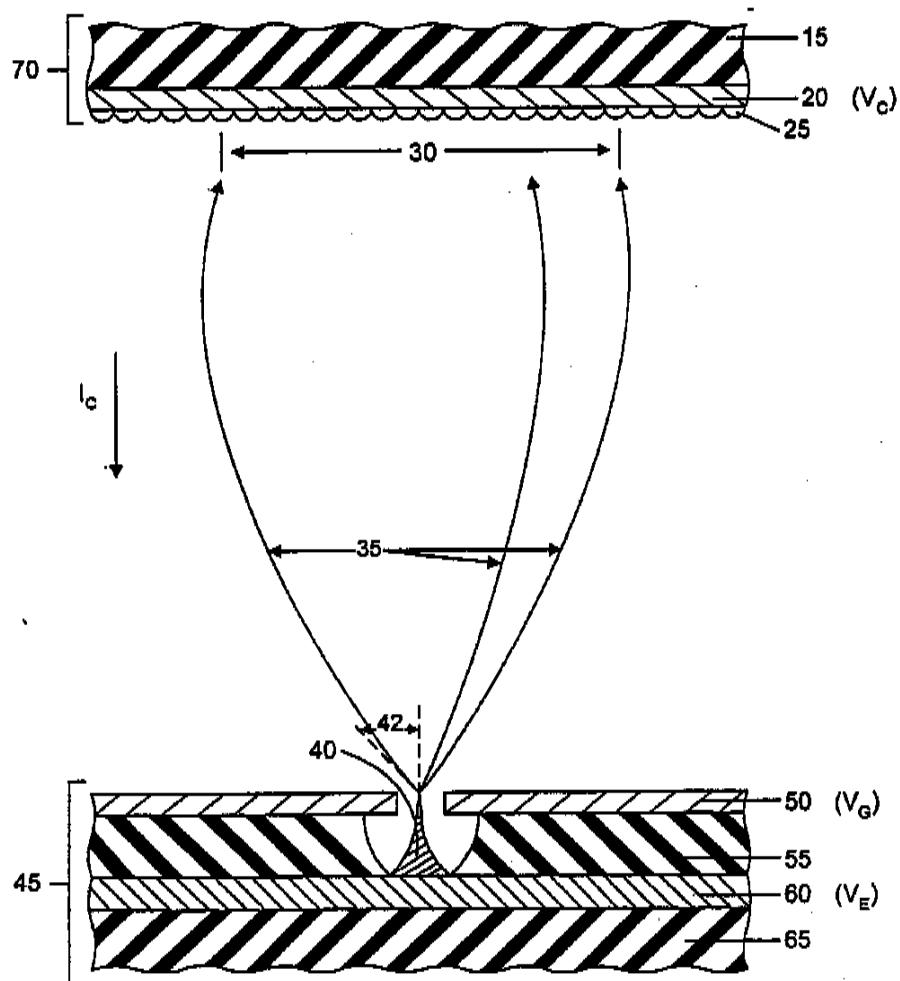

전계 방출 디스플레이의 일반적인 설명을 제공한다. 도 1은 FED 평판 패널 디스플레이의 일부분의 단면도인 다층 구조(multi-layer structure: 75)를 보여주고 있다. 다층 구조(75)는 기저판 구조(baseplate)로도 불리우는 전계 방출 후면판 구조(field-emission backplate structure: 45)와 전자-받게 전면판 구조(electron-receiving faceplate structure: 70)를 포함한다. 이미지는 전면판(70)상에 만들어진다. 후면판 구조(45)는 공통적으로 절연 후면판(65), 전기적 절연층(55), 방출체(emitter) (또는 음극) 전극(60), 패턴화된 게이트 전극(patterned gate electrode: 50), 및 절연층(55)을 통한 개구 내에 위치한 원추형 전자-방출 소자(conical electron-emissive element: 40)로 구성되어 있다. 전자-방출 소자(40)의 하나의 형태가 1997. 3. 4. 자로 트위첼 등에게 허여된 미국특허 제5,607,283호에 개시되어 있고, 또 다른 형태가 1997. 3. 4. 자로 스피츠 등에게 허여된 미국특허 제5,607,335호에 개시되어 있는바, 이들은 본 발명에 참조로서 합체된다. 전자-방출 소자(40)의 팁(tip)은 게이트 전극(50)내의 대응 개구를 통해 노출되어 있다. 방출체 전극(60)과 전자-방출 소자(40)는 함께 FED 평판 패널 디스플레이의 도면 부분(75)의 음극을 구성한다. 전면판 구조(70)는 전기적 절연 전면판(15), 양극(20), 및 형광물질 코팅(25)으로 형성되어 있다. 소자(40)로부터 방출된 전자는 형광부(30)에 의해 수령된다. 하나의 실시예로서, 전자-방출 소자(40)는 원추형 몰리브덴 팁(conical molybdenum tip)을 포함한다. 본 발명의 또 다른 실시예로서, 양극(20)은 형광물질(25)상에 위치하고, 방출체(40)는 필라멘트와 같은 다른 기하학적 형상을 포함할 수도 있다.

전자-방출 소자(40)로부터의 전자 방출은 게이트 전극(50)에 적당한 전압( $V_G$ )을 인가함으로써 제어된다. 또 다른 전압( $V_E$ )이 방출체 전극(60)을 통해 전자-방출 소자(40)에 직접 인가된다. 전자 방출은 게이트로부터 방출체로의 전압, 예를 들어,  $V_G - V_E$ , 또는  $V_{GE}$ 이 증가함에 따라 증가한다. 전자를 형광물질(25)로 인도하는 것은 양극(20)에 고 전압( $V_C$ )을 인가함으로써 실행된다. 적당한 게이트로부터 방출체로의 전압( $V_{GE}$ )이 인가되면, 전자는 다양한 값의 오프-정규 방출각 쎈타(off-normal emission angle theta: 42)로서 전자-방출 소자(40)로부터 방출된다. 방출된 전자는 도 1의 선(35)으로 표시된 비선형(예를 들어, 포물선) 궤적을 따르며, 형광물질(25)의 타겟부(30)에 충돌한다. 따라서,  $V_G$ 와  $V_E$ 는 방출 전류( $I_C$ )의 크기를 결정하는 반면에, 양극 전압( $V_C$ )은 주어진 각에서 방출된 주어진 전자를 위한 전자 궤적의 방향을 조정한다.

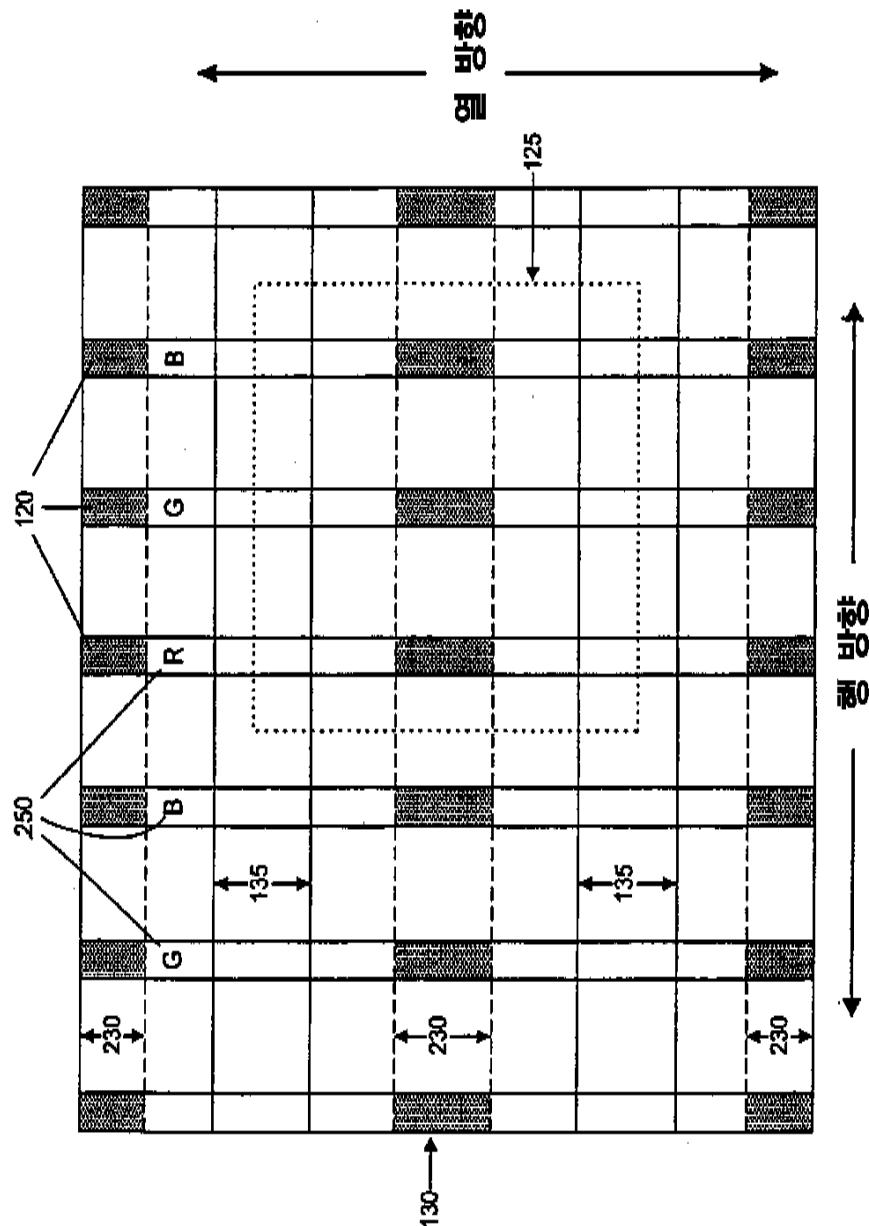

도 2는 예시적인 FED 스크린(100)의 일부를 보여주고 있다. FED 스크린(100)은 화소의 수평열 행(horizontally aligned row)과 수직열 열(vertically aligned column)의 배열로 세분된다. 각 화소(125)의 경계가 점선으로 표시되어 있다. 세 개의 각각의 행 라인(row line: 230)이 나타나 있다. 각각의 행 라인(230)은 배열상의 화소의 행들 중의 하나를 위한 행 전극이다. 하나의 실시예로서, 각각의 행 라인(230)은 전극과 관련된 특정 행의 각 방출체의 방출체 전극에 연결되어 있다. 다른 실시예에서, 공간벽(spacer wall: 135)은 각 행 사이에 있을 필요가 없다. 몇몇 실시예에서, 공간벽(135)은 존재하지 않을 수도 있다. 화소 행은 하나의 행 라인(230)을 따라 존재하는 모든 화소를 포함한다. 둘 또는 그 이상의 화소 행(24~100개의 화소 행)은 일반적으로 각 쌍의 인접 공간벽(135)들 사이에 위치한다.

컬러 디스플레이에 있어서, 화소들의 각각의 열(column)은 세 개의 열 라인(column line: 250)을 가지고 있다: (1) 붉은색의 첫번째, (2) 초록색의 두번째, 및 (3) 푸른색의 세번째. 또한, 각각의 화소 열은 총 세 개인 각각의 형광 스트립들(strips: 붉은색, 초록색, 푸른색) 중의 하나를 포함한다. 흑백 디스플레이에 있어서, 각각의 열은 오직 하나의 스트립만을 포함하고 있다. 본 실시예에서, 각각의 열 라인(125)은 관련 열의 각 방출체 구조의 게이트 전극에 연결된다. 또한, 본 실시예에서, 열 라인(250)은 열 드라이버 회로(column driver circuit: 도시하지 않음)로의 연결에 사용되고 행 라인(230)은 행 드라이버 회로(row driver circuit: 도시하지 않음)로의 연결에 사용된다.

작동시, 붉은색, 초록색 및 푸른색 형광 스트립은 방출체-음극(60/40)의 전압에 대해 상대적으로 높은 양 전압으로 유지된다. 대응 행 라인(230)과 열 라인(250)의 전압을 조절함으로써 전자-방출 소자 세트들 중의 하나를 적당히 들뜨게

(exciting) 하면, 그러한 세트상의 소자(40)는 대응 색상의 형광 타겟부(30)쪽으로 가속되는 전자를 방출한다. 그러면 뜰뜬 형광물질이 광을 발산한다. 스크린 플래임 리플래시 싸이클(screen frame refresh cycle: 하나의 실시예에서 대략 60Hz의 속도로 실행됨) 동안, 한번에 오직 하나의 행만이 활성(active)이고 열 라인들이 가압되어(energized) 온-타임(on-time) 기간 동안 화소들 중 하나의 행을 밝힌다(illuminate). 이 과정은 플래임을 디스플레이하기 위하여 모든 화소 행들이 밝혀질 때까지 행에서 행으로 시간상으로 연속하여 실행된다. 상기 FED 구조는 1996. 7. 30. 자로 두복 등에게 허여된 미국특허 제5,541,473호; 1996. 9. 24. 자로 스피츠 등에게 허여된 미국특허 제5,559,389호; 1996. 10. 15. 자로 스피츠 등에게 허여된 미국특허 제5,564,959호; 및 1996. 11. 26. 자로 하벤 등에게 허여된 미국특허 제5,578,899호에 더욱 상세히 개시되어 있는바, 이들은 참조로서 본 발명에 합체된다.

#### 본 발명의 하나의 실시예에 따른 FED 조절 과정

본 발명은 새로 제작된 FED를 조절하여 거기에 포함되어 있는 불순물을 제거하는 공정을 제공한다. 조절 공정(conditioning process)은 FED 장치가 정규 작동(normal operation)으로서 사용되기 전에 실행되고, 전형적으로는 제조 과정 중에 실행된다. 본 발명의 조절 공정동안, FED의 진공 튜브내에 포함되어 있는 불순물은 많은 양의 전자에 의해 피폭된다(bombarded). 피폭의 결과로서, 불순물은 떨어지고 가스-트래핑 장치(예를 들어, 게터: getter)에 의해 수집되게 된다. 새로 제작된 FED가 많은 양의 불순물을 포함하고 있기 때문에, 본 발명에 따른 조절 공정 동안에 알킹(arcing)이 발생하지 않도록 하기 위하여 주의 단계(precautious step)가 취해져야만 한다. 본 발명에 따르면, 조절 공정은 전자들이 양극으로 끌려오도록 보장하기 위하여, 양극을 미리 정해진 고 전압으로 구동하는 단계와 그런 다음 방출 음극을 동작하는 단계를 포함한다. 본 발명의 하나의 실시예로서, 방출 전류는 양극 전압이 미리 정해진 고 전압까지 도달한 뒤, 최고 값으로 서서히 증가한다.

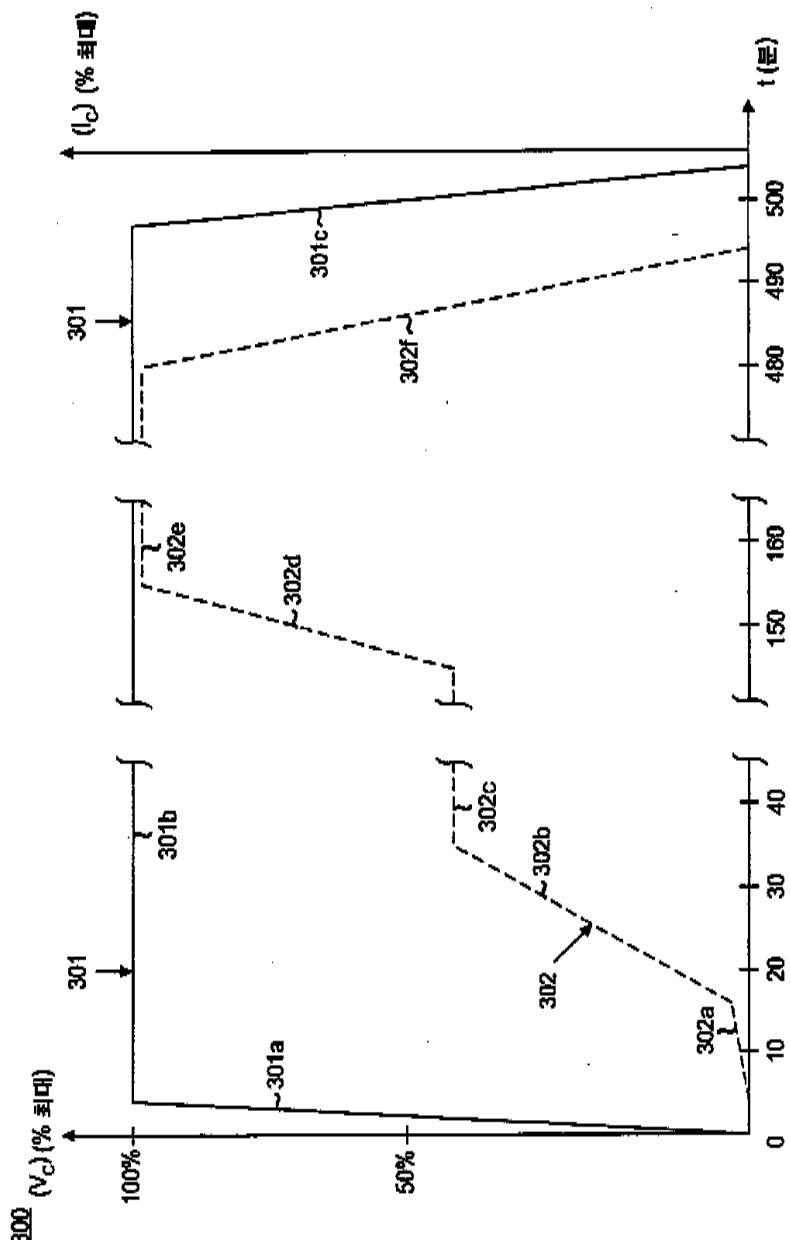

도 3은 본 실시예의 조절 공정 동안에 특정 FED의 양극 전압 수준과 방출 전류 수준에서의 변화를 보여주는 도표(300)를 개시하고 있다. 도표(301)는 양극 전압( $V_C$ )에서의 변화를 보여주고 있고, 도표(302)는 방출 전류( $I_C$ )에서의 변화를 보여주고 있다. 특히,  $V_C$ 는 드라이버 전자기술(driver electronics)에 의해 제공되는 최고 양극 전압의 백분율로 나타나 있다. 예를 들어, 고 전압 형광물질에 대해, 최고 양극 전압은 3,000V일 수 있다. 최고 양극 전압은 양극의 정규 작동 전압이 아닐 수도 있다는 것을 주목해야 한다. 예를 들어, 디스플레이 스크린의 정규 작동 전압은 최고 양극 전압의 25%에서 75%일 수 있다.  $I_C$ 는 FED의 드라이버 회로에 의해 제공되는 최고 방출 전류의 백분율로 나타나 있다. FED에 고 전압과 많은 전류를 제공하는 드라이버 전자기술과 전자 장비는 당업계에 공지되어 있으므로, 본 발명의 본질이 흐려지는 것을 피하기 위하여 본 명세서에서는 자세한 설명은 생략한다.

본 발명에 따르면, 도표(301)는 전압 경사부(301a), 일차 레벨부(301b), 및 전압 강하부(301c)를 포함하고, 도표(302)는 일차 전류 경사부(302a), 이차 전류 경사부(302b), 이차 레벨부(302c), 삼차 전류 경사부(302d), 삼차 레벨부(302e), 및 전류 강하부(302f)를 포함한다. 도시되어 있는 특정 실시예로서, 전압 경사부(301a)에서,  $V_C$ 는 거의 5분의 기간동안 최고 양극 전압의 0%에서 100%까지 증가한다. 특히, 전자들이 게이트 전극 대신에 디스플레이 스크린(양극)쪽으로 끌어당겨지는 것을 보장하기 위하여,  $V_C$ 가 증가함에 따라  $I_C$ 는 0%로 유지된다.

$V_C$ 가 최대 양극 전압의 100%에 도달한 뒤,  $V_C$ 는 대략 25분 동안 그러한 전압 수준에서 유지된다. 동시에,  $I_C$ 는 대략 10분에 걸쳐 최대 방출 전류의 0%에서 1%로 서서히 증가한다(일차 전류 경사부: 302a). 그런 다음,  $I_C$ 는 대략 20분에 걸쳐 최대 방출 전류의 50%로 서서히 증가하게 된다(이차 전류 경사부: 302b). 이후  $I_C$ 는 대략 10분 동안 50% 수준에서 유지된다(삼차 레벨부: 302c). 본 발명에 따르면,  $I_C$ 는 전자 방출체의 탈리(desorption)에 의해 생성되는 고 이온압 구역(hight ionic pressure zone)의 형성을 피하기 위하여 느린 속도로 증가된다. 탈리된 분자들은 고 이온압의 작은 구역들을 형성할 수도 있는데, 이것은 알킹 위험을 증가시킬 수 있다. 따라서, 방출 전류를 서서히 증가시킴으로써, 알킹 발생은 현저히 줄어든다.

도 3에 따르면,  $I_C$ 는 소킹("soaking") 발생을 위하여 대략 10분간 일정한 수준에서 유지된다(삼차 레벨부: 302c). 소킹은 불순물 입자가 가스-트래핑 장치에 의해 제거되는 과정을 말한다. 일반적으로 "게터(getter)"로 알려져 있는 가스-트래핑 장치가 조절 공정의 본 단계에서 본 발명에 의해 사용되고, 이는 당업계에 공지되어 있다.

하나의 실시예로서, 소킹 기간 이후,  $I_C$ 는 그것의 최대 수준의 100%로 연속하여 증가되며(삼차 전류 경사 302d), 그런 다음 거의 2시간동안 그 수준에서 유지된다(사차 레벨부: 302e). 동시에,  $V_C$ 는 그것의 최대 수준으로 유지된다. 그런 다음,

$V_C$  와  $I_C$ 는 이들 각각의 최대 값의 0%로 연속적으로 되돌아간다. 특히, 도 3의 부분들(302f와 301c)에 의해 보여지는 바와 같이,  $I_C$ 는  $V_C$ 가 정지되기 전에 정지된다. 이러한 방법으로, 모든 방출 전자는 디스플레이 스크린(양극)쪽으로 잡아당겨지고, 게이트로부터 방출체로의 전류가 방지되는 것을 보장한다.

본 발명의 조절 공정 동안에, 떨어졌거나 또는 탈리 분리된 불순물은 가스-트래핑 장치, 달리 "게터"로서 알려진 장치에 의해 수집된다. 상기 설명된 게터는 당업계에 공지되어 있다. 도 3에 개시된 특정 실시예에서, 전체 조절기간은 대략 6시간이다. 이러한 조절기간 이후, 불순물의 대부분은 떨어지게 되고 게터에 의해 수집되어, 새로 제작된 FED 스크린은 정규 작동을 위한 준비를 갖추게 된다.

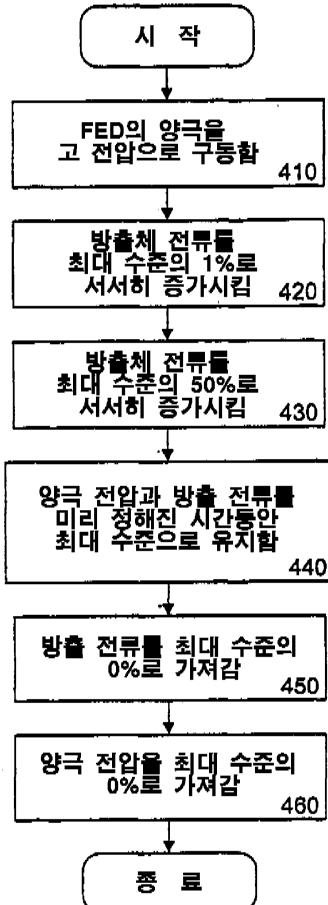

도 4는 본 발명에 따른 FED 조절 공정의 단계들을 보여주는 흐름도(400)이다. 본 발명의 논의를 수월하게 하기 위하여, 흐름도(400)는 도 1의 예시적인 FED 구조(75)와 관련지어 설명되고 있다. 도 1과 도 4를 참고로, 단계(410)에서, FED의 양극(20)은 고 전압으로 구동된다. 단계(410)에서, 방출 전류( $I_C$ )는 최대 수준의 0%로 유지되므로 오프 상태라는 것을 주목해야 한다. 본 발명의 하나의 실시예에서, 게이트 전극(50)과 방출체-음극(60/40)의 전압이 그라운드로 유지된다. 일단 방출된 전자들이 게이트 전극(50)보다는 양극(20)으로 끌리도록 하는 것을 보장하기 위하여, 방출 전류를 0%로 유지하는 동안, 양극 전압은 고 전압으로 구동된다.

도 4의 단계(420)에서, 방출 전류( $I_C$ )는 FED의 드라이버 전자기술에 의해 제공되는 최대 방출 전류의 1%로 서서히 증가한다. 본 발명의 하나의 실시예에서, 단계(420)를 완료하는데 대략 5분이 소요된다. 느린 경사 상승(ramp up)은 전자 방출체의 탈리에 의해 고 이온압의 지역적 구역들이 형성되지 않도록 보장한다. 또한, 본 실시예에 있어서, 방출 전류( $I_C$ )는 플로러-노르하임 이론(Fowler-Nordheim theory)에 의해 예견되는 바와 같이 게이트로부터 방출체로의 전압( $V_{GE}$ )에 비례한다. 따라서, 본 실시예에서, 방출 전류( $I_C$ )는 게이트로부터 방출체로의 전압( $V_{GE}$ )을 조정하여 제어할 수 있다.

도 4의 단계(430)에서, 방출 전류( $I_C$ )는 FED의 드라이버 전자기술에 의해 제공되는 최대 방출 전류의 대략 50%까지 경사진 상태로 상승한다. 하나의 실시예에서, 단계(430)를 완료하는데 대략 10분이 소요된다. 단계(420)에서처럼, 느린 경사 상승은 탈리된 분자들이 확산될 수 있도록 하는 충분한 시간을 허여하고, 고 이온압의 지역적 구역들이 형성되지 않는 것을 보장한다.

도 4의 단계(440)에서, 방출 전류( $I_C$ )와 음극 전압( $V_C$ )은 이들 각각의 최대 값의 100%로 유지됨으로써, 많은 양의 전자들이 방출되게 된다. 방출된 전자는 이전의 제작 공정에서 제거되지 않은 대부분의 느슨한 불순물을 피폭하여 떨어뜨린다. 떨어진 불순물은 게터와 같은 이온-포집 장치에 의해 연속적으로 포획된다. 앞서 논의된 바와 같이, 게터는 당업계에 공지되어 있으므로, 본 발명의 본질이 흐려지는 것을 피하기 위하여 본 명세서에서는 자세히 기재하지 않는다.

단계(450)에서, 방출 전류를 최대 값의 0%로 가져간다. 연속하여, 단계(460)에서, 양극 전압을 최대 값의 0%로 가져간다. 양극 전압을 정지하기 전에 방출 전류를 정지하여, 방출 전자들이 양극으로 끌리도록 하는 것은 중요하다. 이로써, 조절 공정(400)은 완료된다.

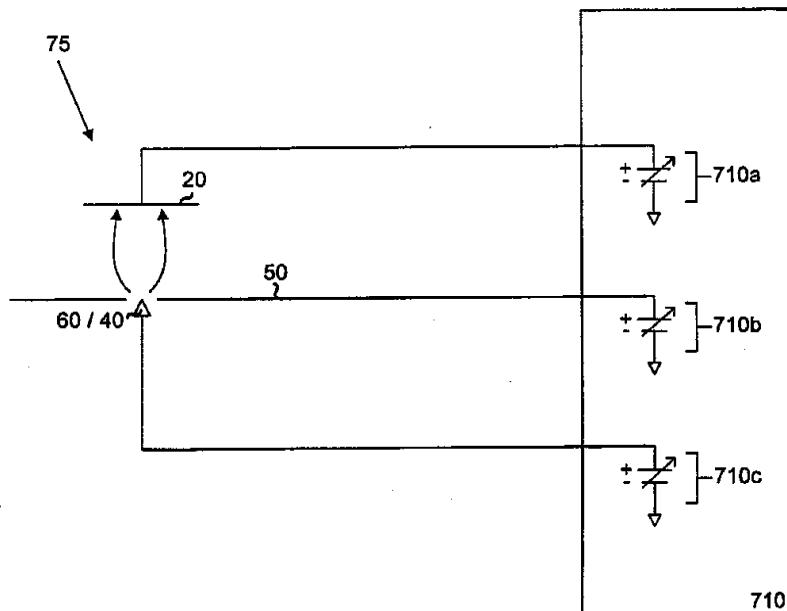

도 5는 본 발명의 하나의 실시예에 따른 조절 공정을 제어하기 위한 장치를 보여주는 블록 다이어그램(700)이다. 도 1의 FED(75)를 단순화한 다이어그램을 또한 보여주고 있다. 도 5에서, 장치는 FED(75)에 연결하기 위한 제어기 회로(controller circuit: 710)를 포함하고 있다. 특히, 제어기 회로(710)는 FED(75)의 양극(20)에 양극 전압을 공급하기 위한 일차 전압 제어회로(710a)를 포함하고 있다. 제어기 회로(710)는 또한 게이트 전극(50)에 게이트 전압을 공급하기 위한 이차 전압 제어회로(710b)와, 방출체 음극(60/40)에 방출체 전압을 공급하기 위한 삼차 전압 제어회로(710c)를 포함한다. 제어기 회로(710)는 예시적인 것이고, 제어기 회로(710)의 많은 다른 실현수단들도 사용될 수 있는 것으로 이해되어야 한다.

작동시, 전압 제어회로(710a-c)는 FED(75)의 양극(20), 게이트 전극(50) 및 방출체 전극(60/40)에 다양한 전압을 공급하여, 본 발명의 조절 공정동안 서로 다른 전압과 방출 전류를 공급한다. 본 발명의 하나의 실시예에서, 제어기 회로(710)는 매우 고 전압을 공급하기 위하여 본 조절 공정용으로 특별히 제작된 스탠드 얼론 전자장치(stand alone electronic equipment)이다. 그러나, 제어기 회로(710)가 FED내에서 실행되어 FED의 작동 및 정지 동안에 양극 전압과 방출 전류를 제어할 수도 있는 것으로 이해되어야 한다.

#### 본 발명의 FED 작동 및 정지 과정

본 발명은 또한 FED 유닛의 파워-온(power-on)과 파워-오프(power-off) 동안 알킹의 위험을 최소화하는 전계 방출 디스플레이의 작동방법을 제공한다. 특히, 본 발명의 하나의 실시예에 따르면, FED의 작동방법은, FED의 양극성 디스플레이 스크린을 작동한 뒤, 방출 음극을 작동하는 단계들을 포함한다. 본 발명의 또다른 실시예에 따르면, 알킹의 위험을 최소화하기 위한 FED의 작동방법은, 방출 음극을 정지한 뒤, 양극성 디스플레이 스크린을 정지하는 단계들을 포함한다. 본 발명에 따르면, 상기 단계들을 따름으로써 알킹의 발생이 실질적으로 줄어들게 된다.

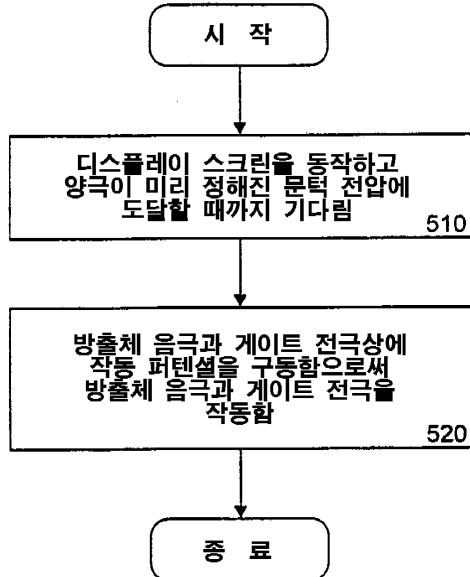

도 6은 본 발명의 또다른 실시예에 따른 FED 작동 과정내에서 단계들의 흐름도(500)를 보여주고 있다. 본 발명의 논의를 용이하게 하기 위하여, 도 1의 예시적 FED(75)와 관련지어 흐름도(500)를 설명한다. 도 1과 도 6을 참조로, 단계(510)에서, FED(75)가 켜지면 양극(20)이 동작한다. 본 실시예에서, 미리 정해진 문턱 전압(threshold voltage: 예를 들어, 300V)의 인가에 의해 양극이 동작한다. 또한, 본 발명에서, 양극(20)에 전원을 공급하는 전원 공급 회로(power supply circuit: 도시하지 않음)를 켜지게 함으로써 양극이 동작할 수 있다. FED에 대한 전원 공급은 당업계에 공지되어 있고, 공지된 많은 수의 전원 공급 장치가 본 발명에 사용될 수 있다.

단계(520)에서, FED(75)의 양극(20)이 동작한 뒤, 양극이 미리 정해진 문턱 전압에 도달된 다음, FED(75)의 방출체 음극(60/40)과 게이트 전극(50)이 동작한다. 본 발명에서, 양극(20)이 동작한 뒤, FED(75)의 방출체 음극(60/40)이 미리 정해진 기간동안 동작함으로써, 전자들이 양극(20)을 향하고 전자들이 게이트 전극(50)에 충돌하는 것을 방지한다. 하나의 실시예에서, 방출체 음극(60/40)과 게이트 전극(50)은 FED의 행 및 열 드라이버 회로(row and column driver circuit: 도시하지 않음)를 켜지게 함으로써 동작할 수 있다.

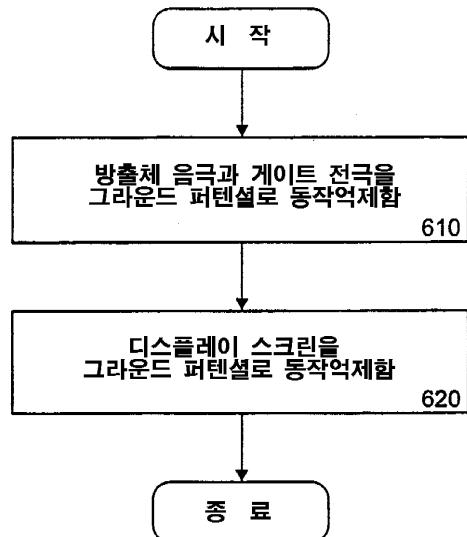

도 7은 본 발명의 또다른 실시예에 따른 FED 정지 과정의 단계들을 보여주는 흐름도(600)이다. 하기에서는, 도 1의 예시적 FED(75)와 관련지어 흐름도(600)를 설명한다. 도 1 및 도 7을 참조로, 단계(610)에서, FED가 꺼질 때, FED(75)의 방출체 음극(60/40)과 게이트 전극(50)이 동작억제된다(disabled). 동시에, 양극(20)은 고 전압으로 유지된다. 또한, 하나의 실시예에서, 행 드라이버와 열 드라이버(도시하지 않음)에 의해 각각 공급된 행 전압과 열 전압을 그라운드 퍼텐셜로 설정함으로써, 방출체 음극(60/40)과 게이트 전극(50)이 동작억제된다.

단계(620)에서, 방출체 음극(60/40)과 게이트 전극(50)이 동작억제된 뒤, FED의 양극(20)이 동작억제된다. 본 발명에 따르면, 방출 음극으로부터 방출된 모든 전자들이 양극성 디스플레이 스크린으로 끌리도록 하는 것을 보장하기 위하여 단계(620)는 단계(610) 후에 실행된다. 하나의 실시예에서, 양극(20)에 전원을 공급하는 전원 공급 회로(도시하지 않음)를 끈으로써, 양극(20)이 동작억제된다. 이러한 방법으로, FED내에서 알킹의 발생이 최소화된다.

#### 본 발명의 또다른 실시예에 따른 FED 조절 공정

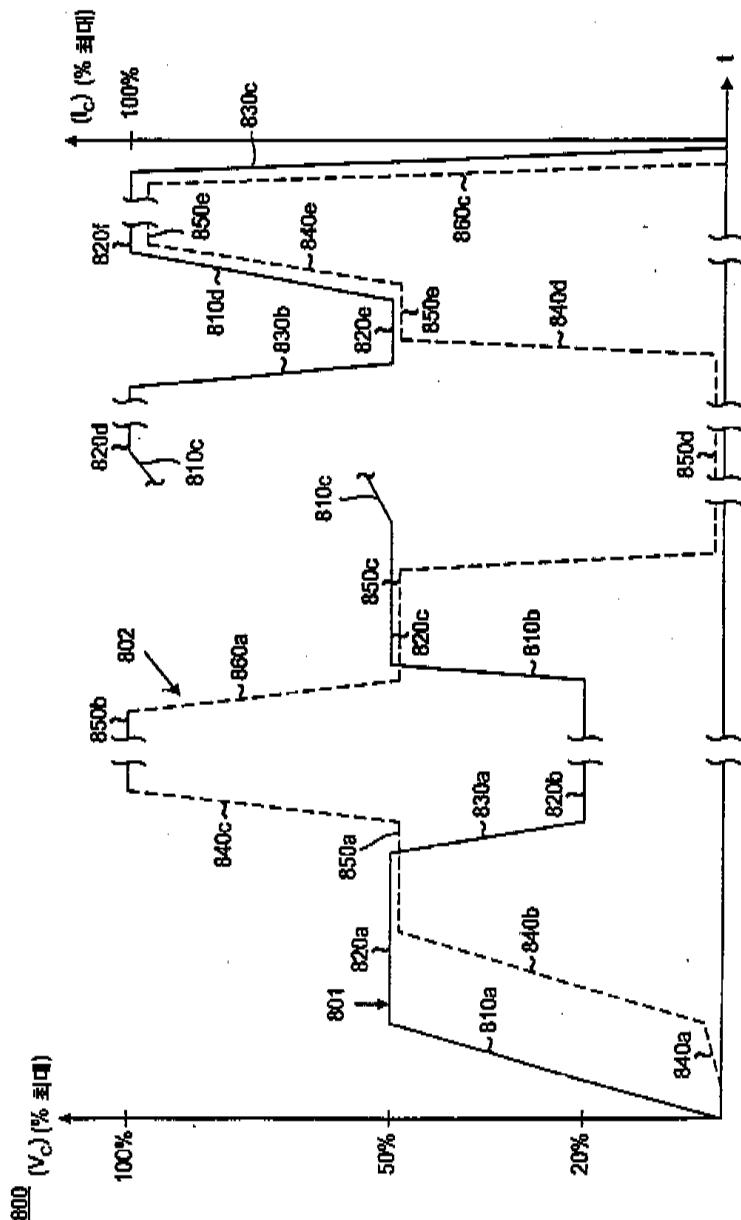

도 8은 본 발명의 또다른 실시예에 따른 특정 FED 장치를 조절하기 위한 전압 및 전류 인가 기술을 보여주는 도표(800)이다. 도표(801)는 양극 전압( $V_C$ )에서의 변화를 보여주고 있고, 도표(802)는 방출 전류( $I_C$ )에서의 변화를 보여주고 있다. 특히,  $V_C$ 는 드라이버 전자기술에 의해 제공되는 최대 양극 전압의 백분율로 나타나 있다.  $I_C$ 는 FED의 드라이버 회로에 의해 공급되는 최대 방출 전류의 백분율로 나타나 있다.

본 발명에 따르면, 도표 801은 전압 경사부들(810a-d), 일정 전압부들(820a-f), 전압 강하부들(830a-c)을 포함하고, 도표(802)는 전류 경사부들(840a-e), 일정 전류부들(850a-e) 및 전류 강하부들(860a-c)을 포함한다. 보는 바와 같은 특정 실시예로서, 전압 경사부(810a)에서,  $V_C$ 는 대략 10분의 기간에 걸쳐 최대 양극 전압의 0%에서 50%로 증가한다. 특히, 전자들이 게이트 전극 대신에 디스플레이 스크린(양극)쪽으로 끌어당겨지는 것을 보장하기 위하여  $V_C$ 가 상승함에 따라  $I_C$ 는 0%로 유지된다.

$V_C$ 가 최대 양극 전압의 50%에 도달한 뒤,  $V_C$ 는 대략 30분 동안 그러한 전압에서 유지된다(일정 전압부: 820a). 동시에,  $I_C$ 는 대략 10분에 걸쳐 최대 방출 전류의 0%에서 1%로 서서히 증가된다(전류 경사부: 840a). 그런 다음,  $I_C$ 는 대략 10분에 걸쳐 최대 방출 전류의 50%로 서서히 증가된다(전류 경사부: 840b).  $I_C$ 는 대략 10분에 걸쳐 50% 수준으로 유지된다(일정 전류부: 850a). 본 발명에 따르면, 전자 방출체의 탈리에 의해 생성된 고 이온압 구역의 형성을 피하기 위하여 느린 속도로  $I_C$ 가 증가한다. 탈리된 분자들은 고 이온압의 작은 구역들을 형성할 수 있으며, 이것은 알킹의 위험을 증가시킬 수 있다. 방출 전류를 느리게 증가시킴으로써, 가스-트래핑 장치(예를 들어, 계터)로 확산될 수 있도록 충분한 시간이 탈리 분자들에게 허여된다. 이러한 방법으로, 알킹의 발생이 현저히 줄어든다.

도 8에 따르면,  $V_C$ 는 50%에서 20% 수준으로 줄어들고(전압 강하부: 830a) 대략 30분 동안 20% 수준에서 유지된다(일정 전압부: 820b).  $V_C$ 가 20% 수준으로 도달된 뒤,  $I_C$ 는 100% 수준까지 서서히 증가하게 된다(전류 경사부: 840c), FED의 양극이 방출 전자들을 끌어당길 수 있도록 양극 전압이 최소 문턱 수준에 가깝도록 하기 위하여 20%가 선택되었음을 주목하여야 한다. 그런 다음,  $I_C$ 는 "소킹" 발생을 위하여 대략 20분간 일정한 수준으로 유지된다(일정 전류부: 820b).

본 실시예에서,  $I_C$ 는 그것의 최고 수준의 50%까지 실질적으로 감소하고(전류 강하부: 860a), 그 후 대략 20분간 그 수준에서 유지된다(일정 전류부: 850c).  $I_C$ 가 50% 수준에 도달한 뒤,  $V_C$ 는 50% 수준까지 증가하며(전압 경사부: 810b) 20분간 그 수준에서 유지된다(일정 전류부: 820c). 그런 다음,  $I_C$ 는 그것의 최고 값의 0%로 정지 된다(전류 강하부: 860b).

$I_C$ 가 정지된 뒤,  $V_C$ 는 대략 2.5 시간에 걸쳐 그것의 최고 수준의 100%로 서서히 상승하고(전압 경사부: 810c), 대략 1시간동안 최고 수준에서 유지된다(일정 전압부: 820d). 그런 다음,  $V_C$ 는 50% 수준으로 감소하고(전압 강하부: 830b) 대략 20분간 그 수준에서 유지된다(일정 전압부: 820e).  $V_C$ 가 50% 수준에 있을 때,  $I_C$ 는 0%로부터 50% 수준으로 서서히 증가한다(전류 경사부: 840d). 그 뒤,  $V_C$ 와  $I_C$ 는 이들 각각의 최고 값의 100%로 연속적으로 구동되며(전압 경사부: 810d 및 전류 경사부: 840e), 대략 1.5시간동안 그러한 수준에서 유지된다(일정 전압부: 820f 및 일정 전류부: 850e). 그런 다음,  $V_C$ 와  $I_C$ 는 0%로 되돌아온다(전압 강하부: 830c 및 전류 강하부: 860c).

특히, 도 8의 부분(810d 및 840e)에서 보는 바와 같이,  $V_C$ 가 최고 값으로 구동된 뒤  $I_C$ 가 최고 값으로 구동되며,  $V_C$ 가 정지된 뒤  $I_C$ 가 정지된다. 이러한 방식으로, 방출 전자들이 디스플레이 스크린(양극)쪽으로 끌리고 게이트로부터 방출체로의 전류가 방지되는 것을 보장하게 된다.

본 발명, 즉, FED에서 알킹 발생을 최소화하는 작동방법을 개시하였다. 본 발명을 실행하기 위한 전자 회로들, 특히, 문턱 전압 페텐셜이 이뤄질 때까지 방출 음극의 활성화를 지연시키기 위한 회로는 공지되어 있음을 이해하여야 한다. 예를 들어, 양극 전압이 문턱 값에 도달된 뒤, 양극 전압을 감지하고 행 및 열 드라이버로의 전원 공급을 작동 함에 있어서 전자 제어신호에 호응하는 제어회로가 사용될 수도 있다는 것이, 본 발명의 당업자가 본 개시내용을 읽는다면, 명료하여야 한다. 본 발명이 특정 실시예들에 기재되어 있지만, 본 발명이 그러한 실시예에 의해 한정되도록 해석되지 말아야 하며, 하기 청구범위에 따라 해석되어야 함이 또한 분명하여야 한다.

### 산업상 이용 가능성

본 발명의 방법에 따르면, FED의 손상없이 FED 스크린으로부터 불순물 입자들을 효과적으로 제거할 수 있다. 또한, 작동 및 정지 기간동안에 게이트로부터 방출체로의 전류(gate-to-emitter current)를 효과적으로 방지할 수 있다.

### 도면의 간단한 설명

본 명세서의 일부를 형성하며 또한 이에 합체되는 첨부 도면은 본 발명의 실시예를 보여주고 있으며, 발명의 상세한 설명과 더불어 본 발명의 원리를 설명하는 작용을 한다.

도 1은 행 라인과 열 라인의 교차부에 위치한 게이트화 전계 방출체를 사용하는 예시적인 평판 패널 FED 스크린의 일부 단면 구조도이고;

도 2는 본 발명의 하나의 실시예에 따른 예시적인 FED 스크린을 보여주고 있고;

도 3은 본 발명의 하나의 실시예에 따른 FED 장치를 작동 하기 위한 전압 및 전류 인가 기술을 보여주고 있고;

도 4는 본 발명의 하나의 실시예에 따른 FED 조절 공정의 단계들에 대한 흐름도를 보여주고 있고;

도 5는 본 발명의 하나의 실시예에 따른 FED를 조절하기 위한 시스템의 블록 다이어그램을 보여주고 있고;

도 6은 본 발명의 또다른 실시예에 따른 FED 작동 과정의 단계들의 흐름도를 보여주고 있고;

도 7은 본 발명의 또다른 실시예에 따른 FED 정지 과정의 단계들의 흐름도를 보여주고 있고;

도 8은 본 발명의 또다른 실시예에 따른 FED 장치를 작동 하기 위한 전압 및 전류 인가 기술을 보여주고 있다.

**도면**

**도면1**

**75**

도면2

도면3

## 도면4

400

## 도면5

700

도면6

500

도면7

600

도면8