(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5184724号

(P5184724)

(45) 発行日 平成25年4月17日(2013.4.17)

(24) 登録日 平成25年1月25日(2013.1.25)

|               |                    |

|---------------|--------------------|

| (51) Int.Cl.  | F 1                |

| HO 1 L 29/12  | (2006.01)          |

| HO 1 L 29/78  | (2006.01)          |

| HO 1 L 21/336 | (2006.01)          |

| HO 1 L 21/225 | (2006.01)          |

| HO 1 L 21/265 | (2006.01)          |

|               | HO 1 L 29/78 652 T |

|               | HO 1 L 29/78 301 B |

|               | HO 1 L 29/78 301 D |

|               | HO 1 L 29/78 658 A |

|               | HO 1 L 21/225 Z    |

請求項の数 14 (全 17 頁) 最終頁に続く

|               |                               |           |                                                                                                    |

|---------------|-------------------------------|-----------|----------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2000-553992 (P2000-553992)  | (73) 特許権者 | 592054856<br>クリー インコーポレイテッド<br>C R E E I N C.<br>アメリカ合衆国 ノースカロライナ州 2<br>7703 ダラム シリコン ドライブ<br>4600 |

| (86) (22) 出願日 | 平成11年6月7日(1999.6.7)           | (74) 代理人  | 110000855<br>特許業務法人浅村特許事務所                                                                         |

| (65) 公表番号     | 特表2002-518828 (P2002-518828A) | (74) 代理人  | 100066692<br>弁理士 浅村 瞥                                                                              |

| (43) 公表日      | 平成14年6月25日(2002.6.25)         | (74) 代理人  | 100072040<br>弁理士 浅村 肇                                                                              |

| (86) 國際出願番号   | PCT/US1999/012714             | (74) 代理人  | 100159525<br>弁理士 大日方 和幸                                                                            |

| (87) 國際公開番号   | W01999/065073                 |           |                                                                                                    |

| (87) 國際公開日    | 平成11年12月16日(1999.12.16)       |           |                                                                                                    |

| 審査請求日         | 平成18年6月6日(2006.6.6)           |           |                                                                                                    |

| 審判番号          | 不服2011-957 (P2011-957/J1)     |           |                                                                                                    |

| 審判請求日         | 平成23年1月14日(2011.1.14)         |           |                                                                                                    |

| (31) 優先権主張番号  | 09/093,207                    |           |                                                                                                    |

| (32) 優先日      | 平成10年6月8日(1998.6.8)           |           |                                                                                                    |

| (33) 優先権主張国   | 米国(US)                        |           |                                                                                                    |

最終頁に続く

(54) 【発明の名称】イオン注入及び側方拡散による炭化シリコンパワー・バイスの自己整列的な製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

空間的に隔たった一対のアルミニウムウェルを炭化シリコン基板の一表面におけるドリフト領域内に注入する工程と、

前記炭化シリコン基板の前記表面における前記ドリフト領域をマスクして、前記ドリフト領域上かつ前記一対のアルミニウムウェルの間に、第1の対の開口部を画定する工程と、

最初に、前記第1の対の開口部を通して前記炭化シリコン基板内にp型ドーパントを、

p型ドーパント濃度のピークが深い場所にある深いp型注入領域を形成する注入エネルギー及び注入量で注入する工程と、

次いで、前記第1の対の開口部を通して前記炭化シリコン基板内にn型ドーパントを、

前記深いp型注入領域と比較して浅いn型注入領域を形成する注入エネルギー及び注入量で注入する工程と、

そのそれぞれの前記深いp型注入領域を、そのそれぞれの前記浅いn型注入領域を囲む前記炭化シリコン基板の表面まで、それぞれの前記深いp型注入領域をそれぞれの浅いn型注入領域を通じて前記炭化シリコン基板の前記表面まで縦方向に拡散させることなく、側方拡散させる温度及び時間でアニールして、それによって前記炭化シリコン基板の前記表面において前記側方拡散したp型注入領域内に、かつ前記浅いn型注入領域の間に、一対のチャネル領域を形成する工程と、

前記炭化シリコン基板の前記表面において、前記一対のチャネル領域上かつそれらの間

に拡がるゲート絶縁領域を形成する工程と、

一対のソースコンタクトをそのそれぞれのソースコンタクトがそれぞれの前記浅いn型注入領域上かつそれに隣接する前記アルミニウムウェル上に拡がるように形成し、ゲートコンタクトを前記ゲート絶縁領域上に形成し、そしてドレインコンタクトを前記ドリフト領域とは反対の前記炭化シリコン基板の第2の表面上に形成する工程と、

を有することを特徴とする縦型炭化シリコンパワーMOSFETの製造方法。

#### 【請求項2】

前記最初にp型ドーパントを注入する工程は、前記炭化シリコン基板の前記表面における前記ドリフト領域内に前記第1の対の開口部を通してp型ドーパントを、p型ドーパント濃度のピークが深い場所にある深いp型注入領域を形成する複数の注入エネルギー及び注入量で注入する工程を含み、

10

前記次いでn型ドーパントを注入する工程は、前記炭化シリコン基板の前記表面における前記ドリフト領域内に前記第1の対の開口部を通してn型ドーパントを、前記深いp型注入領域と比較して浅いn型注入領域を形成する複数の注入エネルギー及び注入量で注入する工程を含むことを特徴とする請求項1に記載の縦型炭化シリコンパワーMOSFETの製造方法。

#### 【請求項3】

前記最初にp型ドーパントを注入する工程は、前記炭化シリコン基板の前記表面における前記ドリフト領域内に前記第1の対の開口部を通してホウ素を、p型ドーパント濃度のピークが深い場所にある深いp型注入領域を形成する複数の注入エネルギー及び注入量で注入する工程を含み、

20

前記次いでn型ドーパントを注入する工程は、前記炭化シリコン基板の前記表面における前記ドリフト領域内に前記第1の対の開口部を通して窒素を、前記深いp型注入領域と比較して浅いn型注入領域を形成する複数の注入エネルギー及び注入量で注入する工程を含むことを特徴とする請求項2に記載の縦型炭化シリコンパワーMOSFETの製造方法。

#### 【請求項4】

前記最初にp型ドーパントを注入する工程は、前記炭化シリコン基板の前記表面における前記ドリフト領域内に前記第1の対の開口部を通してベリリウムを、p型ドーパント濃度のピークが深い場所にある深いp型注入領域を形成する複数の注入エネルギー及び注入量で注入する工程を含み、

30

前記次いでn型ドーパントを注入する工程は、前記炭化シリコン基板の前記表面における前記ドリフト領域内に前記第1の対の開口部を通して窒素を、前記深いp型注入領域と比較して浅いn型注入領域を形成する複数の注入エネルギー及び注入量で注入する工程を含むことを特徴とする請求項2に記載の縦型炭化シリコンパワーMOSFETの製造方法。

#### 【請求項5】

前記最初にp型ドーパントを注入する工程はホウ素を注入する工程を含み、前記次いでn型ドーパントを注入する工程は窒素を注入する工程を含むことを特徴とする請求項1に記載の縦型炭化シリコンパワーMOSFETの製造方法。

40

#### 【請求項6】

前記最初にp型ドーパントを注入する工程はベリリウムを注入する工程を含み、前記次いでn型ドーパントを注入する工程は窒素を注入する工程を含むことを特徴とする請求項1に記載の縦型炭化シリコンパワーMOSFETの製造方法。

#### 【請求項7】

前記空間的に隔たった一対のアルミニウムウェルを注入する工程は、前記次いでn型ドーパントを注入する工程の後に実行され、前記一対のアルミニウムウェルが前記浅いn型注入領域の外側に注入されるよう構成されたことを特徴とする請求項1に記載の縦型炭化シリコンパワーMOSFETの製造方法。

#### 【請求項8】

50

空間的に隔たった一対のアルミニウムウェルを炭化シリコン基板の一表面におけるドリフト領域内に注入する工程と、

前記炭化シリコン基板の前記表面における前記ドリフト領域をマスクして、前記ドリフト領域上かつ前記一対のアルミニウムウェルの間に、第1の対の開口部を画定する工程と、

最初に、前記第1の対の開口部を通して前記炭化シリコン基板内にn型ドーパントを、浅いn型注入領域を形成する注入エネルギー及び注入量で注入する工程と、

前記n型ドーパントを電気的に活性化させる工程と、

次いで、前記第1の対の開口部を通して前記炭化シリコン基板内にp型ドーパントを、前記浅いn型注入領域と比較してp型ドーパント濃度のピークが深い場所にある深いp型注入領域を形成する注入エネルギー及び注入量で注入する工程と、

10

そのそれぞれの前記深いp型注入領域を、そのそれぞれの前記浅いn型注入領域を囲む前記炭化シリコン基板の表面まで、それぞれの前記深いp型注入領域をそれぞれの浅いn型注入領域を通って前記炭化シリコン基板の前記表面まで縦方向に拡散させることなく、側方拡散させる温度及び時間でアニールして、それによって前記炭化シリコン基板の前記表面において前記側方拡散したp型注入領域内に、かつ前記浅いn型注入領域の間に、一対のチャネル領域を形成する工程と、

前記炭化シリコン基板の前記表面において、前記一対のチャネル領域上かつそれらの間に拡がるゲート絶縁領域を形成する工程と、

一対のソースコンタクトをそのそれぞれのソースコンタクトがそれぞれの前記浅いn型注入領域上かつそれに隣接する前記アルミニウムウェル上に拡がるように形成し、ゲートコンタクトを前記ゲート絶縁領域上に形成し、そしてドレインコンタクトを前記ドリフト領域とは反対の前記炭化シリコン基板の第2の表面上に形成する工程と、

20

を有することを特徴とする縦型炭化シリコンパワーMOSFETの製造方法。

#### 【請求項9】

前記最初にn型ドーパントを注入する工程は、前記炭化シリコン基板の前記表面における前記ドリフト領域内に前記第1の対の開口部を通してn型ドーパントを、浅いn型注入領域を形成する複数の注入エネルギー及び注入量で注入する工程を含み、

前記次いでp型ドーパントを注入する工程は、前記炭化シリコン基板の前記表面における前記ドリフト領域内に前記第1の対の開口部を通してp型ドーパントを、前記浅いn型注入領域と比較してp型ドーパント濃度のピークが深い場所にある深いp型注入領域を形成する複数の注入エネルギー及び注入量で注入する工程を含むことを特徴とする請求項8に記載の縦型炭化シリコンパワーMOSFETの製造方法。

30

#### 【請求項10】

前記最初にn型ドーパントを注入する工程は、前記炭化シリコン基板の前記表面における前記ドリフト領域内に前記第1の対の開口部を通して窒素を、浅いn型注入領域を形成する複数の注入エネルギー及び注入量で注入する工程を含み、

前記次いでp型ドーパントを注入する工程は、前記炭化シリコン基板の前記表面における前記ドリフト領域内に前記第1の対の開口部を通してホウ素を、前記浅いn型注入領域と比較してp型ドーパント濃度のピークが深い場所にある深いp型注入領域を形成する複数の注入エネルギー及び注入量で注入する工程を含むことを特徴とする請求項9に記載の縦型炭化シリコンパワーMOSFETの製造方法。

40

#### 【請求項11】

前記最初にn型ドーパントを注入する工程は、前記炭化シリコン基板の前記表面における前記ドリフト領域内に前記第1の対の開口部を通して窒素を、浅いn型注入領域を形成する複数の注入エネルギー及び注入量で注入する工程を含み、

前記次いでp型ドーパントを注入する工程は、前記炭化シリコン基板の前記表面における前記ドリフト領域内に前記第1の対の開口部を通してベリリウムを、前記浅いn型注入領域と比較してp型ドーパント濃度のピークが深い場所にある深いp型注入領域を形成する複数の注入エネルギー及び注入量で注入する工程を含むことを特徴とする請求項9に記

50

載の縦型炭化シリコンパワーMOSFETの製造方法。

【請求項12】

前記最初にn型ドーパントを注入する工程は窒素を注入する工程を含み、前記次いでp型ドーパントを注入する工程はホウ素を注入する工程を含むことを特徴とする請求項8に記載の縦型炭化シリコンパワーMOSFETの製造方法。

【請求項13】

前記最初にn型ドーパントを注入する工程は窒素を注入する工程を含み、前記次いでp型ドーパントを注入する工程はベリリウムを注入する工程を含むことを特徴とする請求項8に記載の縦型炭化シリコンパワーMOSFETの製造方法。

【請求項14】

前記アルミニウムウェルを注入する工程は、前記n型ドーパントを注入する工程の後に実行され、前記アルミニウムウェルが前記浅いn型注入領域の外側に注入されるよう構成されたことを特徴とする請求項8に記載の縦型炭化シリコンパワーMOSFETの製造方法。

【発明の詳細な説明】

【0001】

発明の分野

本発明はパワーデバイス(power device)の製造方法、特に、炭化珪素パワーデバイスの製造方法に関する。

【0002】

発明の背景

パワーデバイスは大電流を運び、高電圧をサポートするために広く使用されている。今日のパワーデバイスは一般に単結晶シリコン半導体素材から製造される。ある1つの広く使用されているパワーデバイスはパワー酸化金属半導体電界効果トランジスター(MOSFET)である。パワーMOSFETでは、制御信号は、介在する例えはそれに限定はされないが二酸化シリコンなどの絶縁体により半導体表面から分離されたゲート電極に供給される。電流伝導は、バイポーラトランジスタの動作において使用される小数キャリア注入の存在なしに、多数キャリアの輸送によって生じる。パワーMOSFETはすぐれた安全動作領域を提供することができ、かつ、単位セル構造に匹敵することができる。

【0003】

当業者によく知られているように、パワーMOSFETは横型構造または縦型構造を含んでよい。横型構造では、ドレイン、ゲート及びソース端末は基板の同一表面上に存在する。それとは対照的に、縦型構造では、ソース及びドレインは基板の対向する表面上にある。

【0004】

ある一つの広く使用されているシリコンパワーMOSFETは二重拡散処理を使って製造される二重拡散型MOSFET(DMOSFET(double diffused MOSFET))である。これらのデバイスでは、pベース領域とn+ソース領域はマスクにおける共通の開口部を使って拡散される。pベース領域はn+ソースより深く形成される。pベース領域とn+ソース領域の間の側方拡散における相違によって表面チャネル領域が構成される。DMOSFETを含むパワーMOSFETの概要は、1996年にPWS出版社から出版されたB.J.バリヤ(B.J.Baliga)氏著の「パワー半導体デバイス」と題された教科書の第7章「パワーMOSFET」に見出される。詳細についてはそれを参照されたい。

【0005】

パワーデバイスにおける最近の開発の努力にはパワーデバイスに炭化シリコン(SiC)デバイスを使用することの調査も含まれている。炭化シリコンは、シリコンと比較して、広いバンドギャップ、高い融解点、低い誘電率、高い破壊電場強度、高い熱伝導率、そして高い飽和電子ドリフト速度を有する。これらの特性によって、炭化シリコンパワーデバイスは従来のシリコンを基礎とするパワーデバイスよりもより高い温度、より高い電力レベルにおいて、そしてより低い固有オン抵抗で、動作することが可能となる。シリコンデ

10

20

30

40

50

バイスに対する炭化シリコンデバイスの優越性の理論的な分析は、1993年に発行された電子デバイスに関するIEEEトランザクション第40巻の645-655ページ(IEEE Transactions on Electron Devices, Vol. 40, 1993, pp 645-655.)に記載されたブハットナーガ(Bhatnagar et al.)氏らによって著された「パワーデバイスに関する6H-SiC、3C-SiC及びSiの比較(Comparison of 6H-SiC, 3C-SiC and Si for Power Devices)」と題された論文に見出される。炭化シリコン内に製造されたパワーMOSFETはパルムア(Palmour)氏に与えられた「炭化シリコンにおけるパワーMOSFET(Power MOSFET in Silicon Carbide)」と題され、本願の譲受人に譲渡された米国特許第5,506,421号に記載されている。

## 【0006】

10

これらの潜在的な利点にもかかわらず、炭化シリコン内にMOSFETを含むパワーデバイスを製造することは困難である。例えば、すでに述べた二重拡散型MOSFET(DMOSFET)は一般に、pベース領域がn+ソースよりも深く形成される二重拡散処理を使用してシリコン内に製造される。不幸にも、炭化シリコン中では、従来のp型及びn型ドーパントの拡散係数はシリコンと比較して小さく、そのために受け入れ可能な拡散時間と温度を使用してpベース領域とn+ソース領域の必要とされる深さを得ることは困難な場合がある。イオン注入はpベースとn+ソースをインプラントするためにも使用されてよい。例えば、1997年3月に発行されたIEEE電子デバイスレター第18巻第3号の93-95ページ(IEEE Electron Device Letters, Vol. 18, No. 3, March 1997, pp. 93-95)に記載されたシェノイ(Shenoy)氏らによって著された「6H-SiCにおける二重注入された高電圧パワーMOSFET(High-Voltage Double-Implanted Power MOSFET's in 6H-SiC)」を参照されたい。しかしながら、イオン注入された領域の深さと横方向の拡張を制御することは困難なことがある。さらに、ソース領域を囲む表面チャネルを形成する必要において2つの別々の注入マスクが使用されることが要求されるかもしれない。そのときpベースとソース領域を互いに一列に並べることは困難かもしれない、それによりデバイス性能に打撃が与えられる可能性がある。

20

## 【0007】

発明の目的と概要

以上の説明から、本発明の目的は炭化シリコンパワーMOSFETを含む炭化シリコンパワーデバイスを製造するための改良された製造方法を提供することにある。

30

## 【0008】

本発明のもう一つの目的は、ソース領域とpベース領域を別々にマスクする必要のない炭化シリコンパワーMOSFETを含む、炭化シリコンパワーデバイスを製造するための製造方法を提供することにある。

## 【0009】

本発明のさらにもう一つの目的は、デバイスのソース領域と一列に並ぶことができるチャネル領域を形成することができる炭化シリコンパワーデバイスを製造することにある。

## 【0010】

これらの目的と他の目的は本発明による炭化シリコンパワーデバイスの製造方法によって実現できる。この製造方法によれば、p型ドーパントが炭化シリコン基板内にマスクの開口部を通して注入され、深いp型注入領域が形成される。次いでn型ドーパントがマスクの同じ開口部を通して注入され、前記p型注入領域と比較して浅いn型注入領域が形成される。その後、アニールが、深いp型注入領域を浅いn型注入領域を囲む炭化シリコン基板表面まで、その深いp型注入領域をその浅いn型注入領域を通して炭化シリコン基板表面まで縦方向に拡散させることなく、側方拡散させるのに十分な温度及び時間で実行される。従って、自己整列した浅い注入領域及び深い注入領域がイオン注入によって実現され、そして良く制御されたチャネルが、高い拡散率を有するp型ドーパントを十分に拡散させるアニールによって形成されるが、その一方で低い拡散率を有するn型ドーパントは比較的固定される。その結果、pベース領域はn型ソースの周りに形成される。

40

## 【0011】

50

本発明によれば、浅いn型注入領域が存在することによって深いp型注入領は浅いn型注入領域を囲む炭化シリコン基板表面へ側方拡散することがなお許されるものの、その深いp型注入領域がその浅いn型注入領域を通って炭化シリコン基板表面へ縦方向に拡散することが阻止できることが見出されている。特に、いかなる動作原理によってもしばられることは望まないが、窒素のn型注入はn型領域内の炭素空格子点 (carbon vacancies) を減少させて、アニールの間に深いp型注入領域がn型ソース領域内に拡散するのを抑制することができる。その結果、高性能の自己整列した炭化シリコンパワー・デバイスが形成可能である。

【0012】

P型ドーパントを注入する工程はn型ドーパントを注入する工程に先だって実行されてよいことは理解されよう。代わりに、n型ドーパントが最初に注入され、次いで、例えばアニールによって、電気的に活性化されてよい。次いでP型ドーパントが注入されてよい。炭化シリコンに対するn型ドーパントは一般に窒素を含むこと、そして炭化シリコンに対するP型ドーパントはホウ素 (boron) またはベリリウム (beryllium) を含んでよいことも理解されよう。ベリリウムは現在のところ本発明の深いP型注入領域にとって好ましい。その理由は、ベリリウムは、炭化シリコン基板と階段形接合 (abrupt junction) を作りつつ、深く注入できるからである。

10

【0013】

本発明のもう一つの側面によれば、アルミニウムウェル (well) が選択的に炭化シリコン基板の表面において注入 (インプラント) され、それは側方拡散した深いp型注入領域 (laterally diffused deep p-type implant) に電気的に接触する。その際、ニッケルコンタクトが、アルミニウムウェルと浅いn型注入領域に接触してオーム接觸を実現するためには使用されてよい。

20

【0014】

本発明によれば横型炭化シリコンパワーMOSFETは、アルミニウムウェルを炭化シリコン基板の一表面におけるドリフト領域内に注入することにより製造できる。その炭化シリコン基板表面におけるドリフト領域はマスクされ、アルミニウムウェルの対向する側にそれぞれ一つずつ開口部が存在するように第1の対 (ペア) の開口部が確定される。p型ドーパントが、第1の対の開口部を通して炭化シリコン基板内に、深いp型注入領域を形成する注入エネルギー及び注入量で注入される。N型ドーパントが、第1の対の開口部を通して炭化シリコン基板内に、p型注入領域と比較して浅いn型注入領域を形成する注入エネルギー及び注入量で注入される。最初にp型ドーパントが注入され、次いでn型ドーパントが注入されてよいことは理解されよう。代わりに、n型ドーパントが最初に注入、そして活性化され、その後にp型ドーパントが注入されてもよい。

30

【0015】

次いで炭化シリコン基板表面におけるドリフト領域がマスクされ、そのドリフト領域上に、そのそれぞれがそれぞれの浅いn型注入領域からは空間的に隔たっておりかつアルミニウムウェルに対向する第2の対の開口部が確定される。N型ドーパントが、第2の対の開口部を通して炭化シリコン基板内に注入され、一対のドレイン領域が確定される。アニールが、それぞれの深いp型注入領域を、それぞれの浅いn型注入領域を囲む炭化シリコン基板表面まで、それぞれの深いp型注入領域をそれぞれの浅いn型注入領域を通って炭化シリコン基板表面まで縦方向に拡散させることなく、側方拡散させるのに十分な温度及び時間で実行される。それによって一対のチャネル領域が、炭化シリコン基板表面において、側方拡散したp型注入領域内に、アルミニウムウェルの対向する側にそれぞれ一つずつチャネルが存在するように形成される。

40

【0016】

炭化シリコン基板表面におけるドリフト領域上に、そのそれぞれが前記一対のチャネル領域のそれぞれのチャネル領域に接觸する、一対のゲート絶縁領域が形成される。次いで共通のソースコンタクトが浅いn型注入領域上かつアルミニウムウェル上にそれらにわたって形成され、一対のドレインコンタクトがドレイン領域上に形成され、そして一対のゲー

50

トコンタクトが前記一対のゲート絶縁領域上に形成される。こうして、より大きなデバイスの単位セルを形成してよい共通ソースを有する一対の横型炭化シリコンパワーMOSFETが形成できる。

【0017】

p型ドーパントとn型ドーパントはそれぞれ唯一の注入エネルギー及び注入量での唯一の注入において注入されてよいことは理解されよう。代わりに、複数の注入エネルギー及び注入量が浅い注入領域及び/または深い注入領域を形成するために使用されてよい。すでに述べたように、窒素がn型ドーパントに使用されてよく、ホウ素、そして特にベリリウムがp型ドーパントに使用されてよい。

【0018】

当業者であればすでに述べた工程において、アルミニウムウェルは、浅いn型注入領域の間に注入されるよう、ドリフト領域がマスクされた後かつ浅い注入領域及び深い注入領域が注入された後に注入されてよいことも理解されよう。さらに、最初にp型ドーパントを注入する工程と、その後にn型ドーパントを注入する工程は、ドレイン領域のためにn型ドーパントを注入する工程の後に実行されてよい。換言すれば、ドレイン領域はソース領域が形成される前に形成されてよい。さらに代わりに、ソース領域のための浅いn型注入と、ドレイン領域のためのn型注入が同時に実行されてよい。

10

【0019】

本発明によれば縦型炭化シリコンパワーMOSFETは、空間的に隔たった一対のアルミニウムウェルを炭化シリコン基板の一表面におけるドリフト領域内に注入することにより製造できる。その炭化シリコン基板表面におけるドリフト領域はマスクされて、そのドリフト領域上において前記一対のアルミニウムウェルの間に、第1の対の開口部が確定される。P型ドーパントが第1の対の開口部を通して炭化シリコン基板内に注入され、深いp型注入領域が形成される。N型ドーパントが第1の対の開口部を通して炭化シリコン基板内に注入され、浅いn型注入領域が形成される。すでに述べたように、p型ドーパントがn型ドーパントに先立って注入されてよく、あるいはn型ドーパントが注入、そして活性化され、その後にp型ドーパントが注入されてよい。

20

【0020】

次いでアニールが、それぞれの深いp型注入領域を、そのそれぞれの浅いn型注入領域を囲む炭化シリコン基板表面まで、それぞれの深いp型注入領域をそれぞれの浅いn型注入領域を通って炭化シリコン基板表面まで縦方向に拡散させることなく、側方拡散させるのに十分な温度及び時間で実行される。それによって炭化シリコン基板表面において、側方拡散したp型注入領域内に、かつ浅いn型注入領域の間に、一対のチャネル領域が形成される。ゲート絶縁領域が、炭化シリコン基板表面において、前記一対のチャネル領域上かつそれらの間に拡がるように形成される。一対のソースコンタクトがそのそれぞれのソースコンタクトがそれぞれの浅いn型注入領域上かつそれに隣接するアルミニウムウェル上に拡がるように形成され、ゲートコンタクトがゲート絶縁領域上に形成され、そしてドレインコンタクトがドレイン領域に対向する炭化シリコン基板の第2の表面上に形成される。

30

【0021】

横型パワーMOSFETに関連して述べたように、注入領域に対して唯一の注入エネルギー及び注入量、あるいは複数の注入エネルギー及び注入量が使用されてよい。窒素がn型ドーパントに使用されてよく、ホウ素、そして特にベリリウムがp型ドーパントに使用されてよい。アルミニウムウェルは、第1の対の開口部の外側に注入されるよう、p型ドーパント及びn型ドーパントが注入された後に注入されてよい。以上の結果、自己整列的な製造方法によって、横型及び縦型のパワーMOSFETを含む、高性能炭化シリコンデバイスが製造できる。

40

【0022】

詳細な説明

以下、図面を参照しながら本発明の好ましい実施の態様について詳細に説明する。しかし

50

ながら本発明は、多くの異なった形態で実施されてよく、以下に説明される実施態様に限定されたものとして構成されるべきではない。むしろこれらの実施態様は本開示が徹底しておりかつ完全なものとなるように提供され、そして本発明の請求の範囲を当業者に明らかにするものである。図面では、層と領域の厚さは分かりやすくするために誇張されている。全体にわたり類似の符号が類似の要素に付与されている。層、領域または基板といった要素は他の要素の「上に」存在しているものとして引き合いに出されるとき、それはその他の要素の直接上に存在するか、あるいは仲介要素も存在できることは理解されよう。それと対照的に、要素が他の要素の「直接上に」存在しているものとして引き合いに出されるとき、仲介要素は一切存在しない。

## 【0023】

10

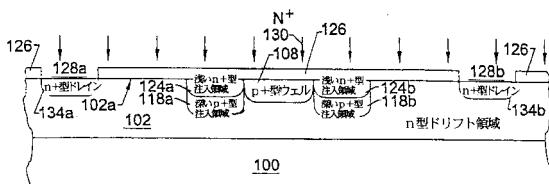

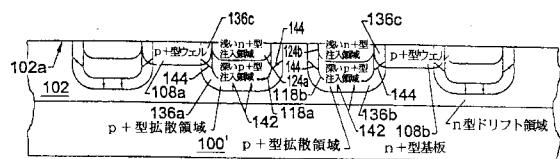

以下、図1A - 図1Gを参照して、本発明による一対(ペア)の横型パワーMOSFETの製造方法を説明する。横型パワーMOSFETは自己整列注入及び拡散を使用するので、炭化シリコンの横型パワーMOSFETは横方向注入拡散型MOSFETあるいはLID MOSFET (Lateral Implanted Diffused MOSFET)とも呼ばれている。

## 【0024】

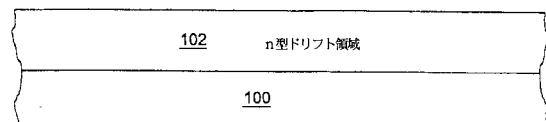

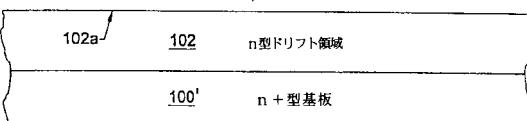

図1Aを参照すると、半絶縁性基板 (semi-insulating substrate) といった基板100にはその上にnドリフト領域 (n-drift region) 102が与えられている。当業者であれば、基板100はドープされたまたはドープされていない炭化シリコンあるいは炭化シリコンに格子整合するどれか他の素材 - ガリウム窒化物に限定されない - を含んでよい、ということは理解されよう。基板100は好ましくは、基板100を介在して隣接するデバイス間の縦方向の伝導性を抑制するために半絶縁的 (semi-insulating) である。

20

## 【0025】

Nドリフト領域102はエピタキシャル堆積 (epitaxial deposition)、イオン注入または他の従来技術により形成されてよい。基板100とnドリフト領域102の組合せもまとめて基板と呼ばれてよいことは理解されよう。Nドリフト領域102は約 $10^{12} \text{ cm}^{-3}$ から約 $10^{17} \text{ cm}^{-3}$ までのキャリア濃度を有してよく、約 $3 \mu\text{m}$ から約 $500 \mu\text{m}$ までの厚さを有してよい。基板100は $100 \mu\text{m}$ から約 $500 \mu\text{m}$ の厚さを有してよい。基板100とnドリフト領域102の製造法は当業者によく知られていて、ここではこれ以上説明される必要はない。

## 【0026】

30

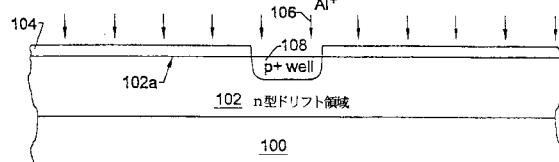

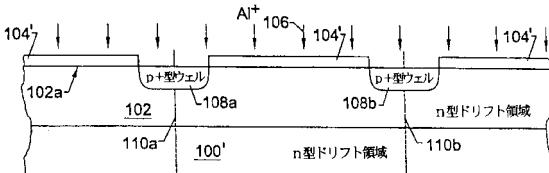

次に図1Bを参照すると、第1のマスク104はnドリフト領域102の表面102a上でかたどられる (patterned)。第1のマスク104は二酸化シリコンまたは他の従来のマスク素材で形成されてよい。図1Bに示されているように、第1のマスク104はnドリフト領域102の表面102aの一部を露出する開口部を確定する。同じく図1Bに示されているように、P型イオン、好ましくはアルミニウムイオン106は、選択的に表面102aを通して、ドリフト領域102に注入され、それにより、ドリフト領域102内に選択的なP+ウェル108を形成する。後で説明されるが、P+ウェル108はP型拡散領域とオーム接觸 (ohmic contact) する。その後、第1のマスク104は除去される。

## 【0027】

40

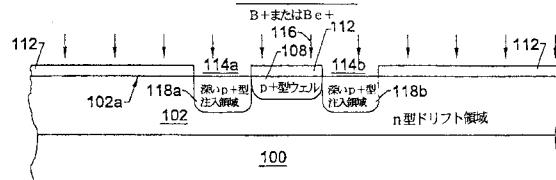

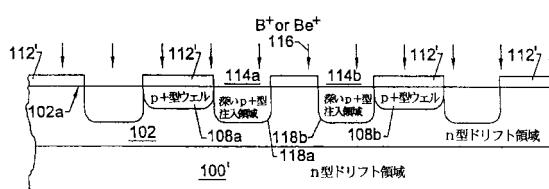

次に図1Cを参照すると、二酸化シリコンまたは他の従来のマスク素材で形成された第2のマスク112がnドリフト領域102上でかたどられ (patterned)、そのドリフト領域上に開口部114aと114bから成る第1の対が確定される。その対に属するそれぞれの開口部はP+ウェル108のそれぞれの対向する側にある。次いで、ホウ素あるいはベリリウムイオンのようなP型ドーパント116が前記一対の開口部114aと114bを通してnドリフト領域102内に注入され、P+ウェル108と対向する側に一対の深いP+注入領域118aと118bが形成される。後で説明されるが、ベリリウムは深いP+注入領域にとて好ましい。なぜならベリリウムはドリフト領域102と階段形接合を形成することができるからである。深いP+注入領域118aと118bは単一の注入エネルギー及び注入量を使用して、例えはホウ素イオンを $180 \text{ keV}$ のエネルギーと4

50

$\times 10^{15} \text{ cm}^{-2}$  の注入量において注入して約  $10^{16} \text{ cm}^{-3}$  のキャリア濃度を実現することによって、形成されてよいことは理解されよう。ベリリウムも  $40 \text{ keV}$  のエネルギーと  $3.2 \times 10^{15} \text{ cm}^{-2}$  の注入量において注入できる。代わりに、複数の注入量及び/またはエネルギーが使用されてよい。

【0028】

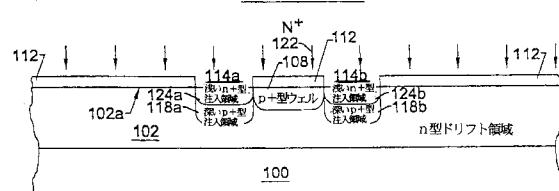

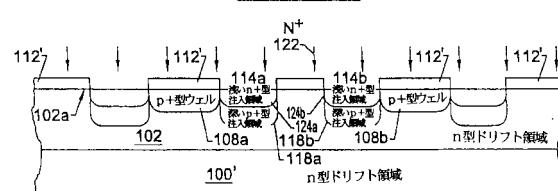

図1Dを参照すると、第2のマスク112は除去されず、そして窒素のようなn型イオン122が第1及び第2の開口部114a及び114bを通して注入され、一对の浅いn+注入領域124a、124bがインプラントされる。後に記述されるように、唯一あるいは複数の注入が使用されてよい。約  $10^{18} \text{ cm}^{-3}$  より大きなキャリア濃度が実現できる。同じ第2のマスク112が図1Cの深いp+注入領域と図1Dの浅いn+注入領域に対して使用されるので、これらの注入領域は互いに自己整列され得ることは理解されよう。

10

【0029】

次に図1Eを参照すると、第2のマスク112は除去され、そして第3のマスク126が形成される。図1Eに示されているように、この第3のマスク126は二酸化シリコンあるいは従来のマスク素材で形成されてよく、開口部の第2の対128a及び128bをドリフト領域102の表面102a上に確定する。開口部128a及び128bから成る第2の対はそれぞれの浅いn型注入領域124a、124bから空間的に隔てられ、p+ウェル108とは反対の位置にある。

【0030】

なお図1Eを参照すると、窒素のようなp型ドーパント130が前記開口部の第2の対128a及び128bを通してnドリフト領域102内に注入され、一对のドレイン領域134a、134bが形成される。その後、第3のマスク126が除去されてよい。

20

【0031】

当業者であれば、図1B、図1C、図1Dと図1Eの工程の順序は変更されてよいことは理解されよう。従って、例えば、図1Bのp+ウェル108は図1Cの深いp+注入領域118a、118bが形成された後に形成されてよく、また図1Dの浅いn+注入領域124a、124bが形成された後に形成されてもよい。図1Bのp+ウェルは図1Eのn+ドレイン領域134a、134bが形成された後に形成されてもよい。さらに、図1Cの深いp+注入領域118a、118bは図1Dの浅いn+注入領域124a、124bが形成された後に形成されてもよい。この場合、アニールは好ましくはマスクが耐えられ、n型ドーパントを電気的に活性化させるのに十分な温度と時間で、浅いn+注入領域124a、124bが注入された後に、実行される。

30

【0032】

図1Eのn+ドレイン領域134a、134bは、図1Dの浅いn+注入領域124a、124b、図1Cの深いp+注入領域118a、118b、そして/または図1Bのp+ウェル108が形成される前に、形成されてもよい。n+ドレイン領域134a、134bは図1Dの浅いn+領域124a、124bと同時にインプラントされてもよい。もし n+ドレイン領域134a、134bが浅いn+注入領域124a、124bと同時にインプラントされるなら、開口部の第2の対128a、128bは同時注入を可能にするために第2のマスク112に形成されてよい。

40

【0033】

次に図1F参照すると、アニールは、深いp型注入領域118a、118bを横方向へそれぞれの浅いn型注入領域124a、124bを囲む炭化シリコン基板の表面102aまで拡散させるのに十分な、またそれぞれの深いp型注入領域を縦方向にそれぞれの浅いn型注入領域124a、124bを通って炭化シリコン基板の表面まで拡散させることのない、温度と時間で実行される。例えば好ましくは、深いp型注入領域の浅いn型注入領域124a、124b内への、その浅いn型注入領域124a、124bの厚さの5%未満までの縦方向の拡散が生じる。アニールは、例えば5分間1600において生じて深いp型注入領域を約  $1 \mu\text{m}$  だけ拡散させる。しかしながら、他のアニール時間と温度が使用されてよい。例えば、約1500と約1600の間のアニール温度と、約1分と約3

50

0分の間のアニール時間が、ホウ素を深いp型注入領域から縦及び横方向へ約0.5μmと3μmの間の距離まで拡散させるのに使用されてよい。

【0034】

したがって、一対のp+拡散領域136a、136bは、p+ドーパントを深いp+注入領域118a、118bから矢印142に示されているように縦方向へ表面102aから離れるように拡散させ、かつ矢印144で示されているように横及び縦方向に表面102aに向かって拡散させることによって形成されてよい。同じく矢印144によって示されているように、側方拡散(lateral diffusion)は、浅いn+注入領域124a、124bの周りに、p+ウェル108とは反対のドリフト領域の表面102aへ拡散する。領域136cによって示されているように、p+ウェル108内への側方拡散も、さらにオーム接触を改善させるために生じてよい。

10

【0035】

最後に、図1Gを参照すると、絶縁されたゲートコンタクト及びソースコンタクトそしてドレインコンタクトが構成される。例えば、ソースコンタクト146と一対の空間的に隔てられたドレインコンタクト147a、147bは、ニッケルを層堆積(blanket deposit)させ、その後、層堆積したニッケルをかたどる(patterning)ことにより形成されてよい。ソースコンタクト146は図1GにおいてSでラベルされ、ドレインコンタクト147a、147bは図1GにおいてD1とD2でラベルされている。図1Gに示されているように、このソースコンタクトは、浅いn+注入領域124a、124b上及びp+ウェル108上に拡がる共通のソースコンタクトを提供する。ドレインコンタクト147a、147bは、それぞれn+ドレイン134a、134bに電気的に接触する。

20

【0036】

図1Gの説明を続けると、一対のゲート絶縁領域148a、148b、例えば二酸化シリコン、はnドリフト領域102の表面102a上に形成され、それぞれのゲート絶縁領域は、p+ウェル108の向こう側にnドリフト領域102の表面まで側方拡散したp+拡散領域136a、136bのそれぞれの部分に接触する。こうして、これらの領域は側方拡散したp型注入領域内で炭化シリコン基板の表面上に一対のチャネル領域150a、150bを形成する。その結果、ソース領域と並んだ自己配列チャネル領域が形成される。その後、一対のゲートコンタクト152a、152bが一対のそれぞれのゲート絶縁領域148a、148b上に形成される。ゲートコンタクトは図1GにおいてG1とG2でラベルされ、ニッケルを含んでよい。

30

【0037】

図1Gにおいて記述された絶縁領域とコンタクトの形成は説明された順序とは異なった順序で実行されてよいことも理解されよう。例えば、ゲートコンタクト152a、152bはソースコンタクト146とドレインコンタクト147a、147bと同時に形成されてよい。好ましくは、ゲートコンタクト152a、152bはソースコンタクト146とドレインコンタクト147a、147bが形成される前に形成されてよい。

【0038】

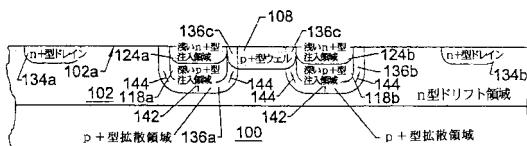

図2は、図1Gの完成したデバイスの平面図である。そこに示されているように、一対の共通ソース形LIDMOSFETが形成されている。一対の共通ソース形LIDMOSFETは炭化シリコン基板上で複製されて、一連の単位セルを形成してよい。さらに、もし共通ソースを含まない単位セルが望ましいなら、図1A-図1Gの左半分または右半分が複製されてもよい。

40

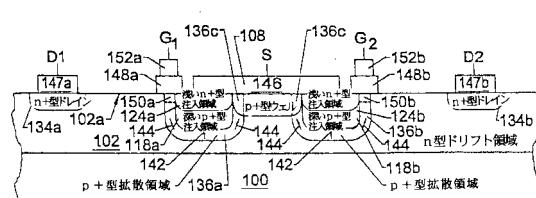

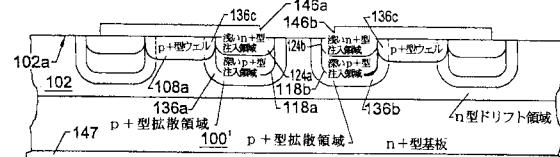

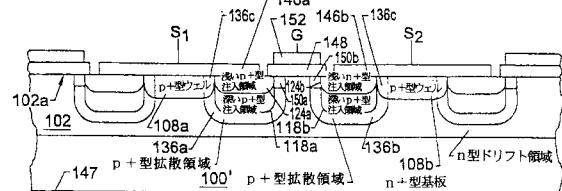

【0039】

次に図3A-図3Gを参照して、本発明による炭化シリコンの縦型パワーMOSFET(silicon carbide vertical power MOSFET)を形成する方法を説明する。これらの縦型パワーMOSFETは注入と拡散を使用して製造されるので、それらはここでは炭化シリコン縦方向注入拡散型MOSFET(VIDMOSFET(silicon carbide Vertical Implanted Diffused MOSFET))とも呼ばれる。

【0040】

50

図3Aを参照するとそこには、Nドリフト領域102を含む炭化ケイ素基板100'が与えられている。図3A-図3Gは基板を通しての導電性を有する縦型MOSFETの製造法を示しているので、基板100'は好ましくは、周知技術を使用して製造されるn+導電性炭化ケイ素基板である。n+導電性炭化シリコン基板は約 $10^{16}$ cm<sup>-3</sup>と約 $10^{19}$ cm<sup>-3</sup>の間のキャリア濃度を有してよい。Nドリフト領域102も図1Aで説明されたように製造されてよい。n+基板100'とnドリフト領域102の組合せもすでに述べたように基板と呼ばれてよいことも理解されよう。

#### 【0041】

次に図3Bを参照すると、一対の空間的に隔てられたp+ウェル108a、108bは炭化ケイ素基板の表面102aにおけるドリフト領域102内にインプラントされる。一対の空間的に隔てられたp+ウェル108a、108bは、図1Dに関連して説明されたような方法で一対の開口部を有する第1のマスク104'を使用して、ドリフト領域102の表面102aにインプラントされる。同じく説明されたように、p+ウェルは好ましくはアルミニウムイオン106を注入することによって形成される。

#### 【0042】

当業者であれば、縦型炭化シリコンMOSFETは一般に単位セルが複製されることは理解されよう。したがって、図3B-図3Gと図4を参照して、ライン110aと110bの間の単位セルを説明する。説明を簡明にするために、ライン110aと110bの外側の複製された単位セルにはラベルされないものとする。

#### 【0043】

次に図3Cを参照すると、一対の開口部114a、114bが、一対のアルミニウムウェル108a、108bの間にこれらの開口部を形成するために修正された第2のマスク112'が使用されることを除いては、図1Cに関連して説明されたように形成される。ホウ素イオン、より好ましくはベリリウムイオン116は図1Cに関連して説明されたように深いp+注入領域118a、118bを形成するために注入される。

#### 【0044】

次に図3Dを参照すると、同じ第2のマスク112'を使用して、深いn+注入領域124a、124bが図1Dに関連して説明されたように例えば窒素イオン122を使用してインプラントされる。

#### 【0045】

図3Eを次に参照すると、アニールが図1Fに関連してすでに説明された方法で実行される。図3A-図3Gは縦型MOSFETの製造を示しているので、図1Eに示されたような一対のn+ドレイン134a、134bの製造は省略されてよいことは理解されよう。p+ウェル108a、108b、深いp+注入領域118a、118bと深いn+注入領域124a、124bを製造する順序は、図1B-図1Fに関連してすでに説明されたように、変更されてよいことも理解されよう。

#### 【0046】

次に図3Fを参照すると、例えばニッケルを含む一対のソースコンタクト146a、146bは、図1Gに関連して説明されたように深いn型注入領域124a、124b上に形成され、そしてそれに隣接するpウェル108a、108b上に拡がる。ドレインコンタクト147はnドリフト領域102とは反対の炭化シリコン基板100の表面上に形成される。ドレインコンタクト147も好ましくはニッケルを含む。

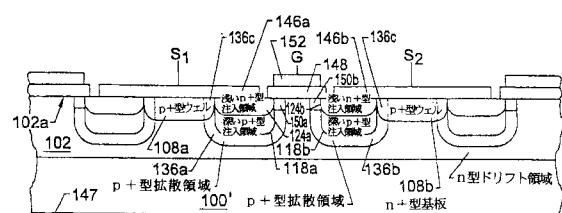

#### 【0047】

最後に図3Gに示されているように、ゲート絶縁領域148はドリフト領域102の表面102aにおいて形成され、それは炭化シリコン基板の表面へ拡散した、そのそれぞれがそれぞれの深いn型注入領域を囲む深いp型注入領域136a、136bの間かつその上に拡がる。したがって、これらの領域は、深いn型注入領域の間に炭化シリコン基板の表面102aにおいて、側方拡散したp型注入領域内に、一対のチャネル領域150a、150bを形成する。例えばニッケルを含むゲートコンタクト152が、ゲート絶縁領域148上に形成される。図1Gに関連して説明されたように、ゲート絶縁領域148とソ-

10

20

30

40

50

スコンタクト、ドレインコンタクト及びゲートコンタクトの形成順序は変更されてよい。

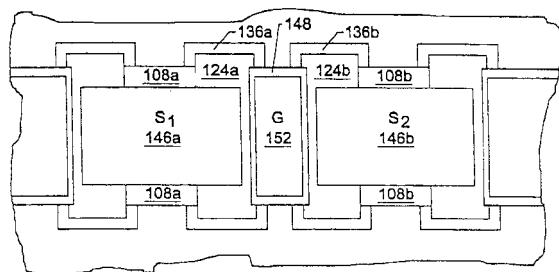

【0048】

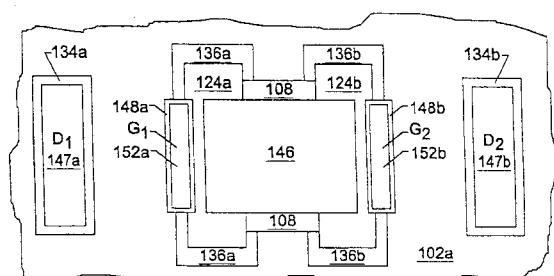

図4は完成された構造物の平面図である。最下表面上のドレインコンタクトは示されていない。

【0049】

本発明による炭化シリコンパワーデバイスの製造に関する追加の議論が以下記述される。

【0050】

図1B - 図1Gのp+ウェル108と図3B - 図3Gのp+ウェル108a, 108bは、25keVのエネルギーと $2 \times 10^{15} \text{ cm}^{-2}$ の注入量におけるアルミニウムの第1の注入と、90keVのエネルギーと $4 \times 10^{15} \text{ cm}^{-2}$ の注入量におけるアルミニウムの第2の注入を使用する室温または高温の注入によって $5 \times 10^{20} \text{ cm}^{-3}$ のキャリア濃度を有する深さ0.1μmのアルミニウムウェルを作り出すことによって形成されてよい。図1C - 図1Gと図3C - 図3Gの深いp+領域118a, 118bは、ホウ素を室温にて450keVの第1のエネルギーと $3.2 \times 10^{14} \text{ cm}^{-2}$ の注入量において、そして370keVの第2のエネルギーと $1.5 \times 10^{14} \text{ cm}^{-2}$ の注入量において注入して、0.4μmから1.0μmまでの深さにおいて $2 \times 10^{18} \text{ cm}^{-3}$ のキャリア濃度を作り出すことにより形成されてよい。最後に、図1D - 図1Gと図3D - 図3Gの浅いn+注入領域124a, 124bは、室温における窒素の4つの注入を使用して製造されてよい。第1の注入は25keVのエネルギーと $3 \times 10^{14} \text{ cm}^{-2}$ の注入量において実行される。第2、第3及び第4の注入は、それぞれ60keV, 120keV及び200keVのエネルギーにて、そしてそれぞれ $6 \times 10^{14} \text{ cm}^{-2}$ ,  $8 \times 10^{14} \text{ cm}^{-2}$ 及び $1 \times 10^{15} \text{ cm}^{-2}$ にて、実行されてよく、0μmから0.4μmまでの深さにおいて $1 \times 10^{20} \text{ cm}^{-3}$ のキャリア濃度を有するn+領域が作り出される。5分間1600のアニールの後に、図1Gと図3Gの基板表面102aにおいて幅0.3μmを有するチャネル領域150a, 150bが作り出される。p+拡散136a, 136bの深さは基板表面102aから1.5μmだけ拡がってよい。

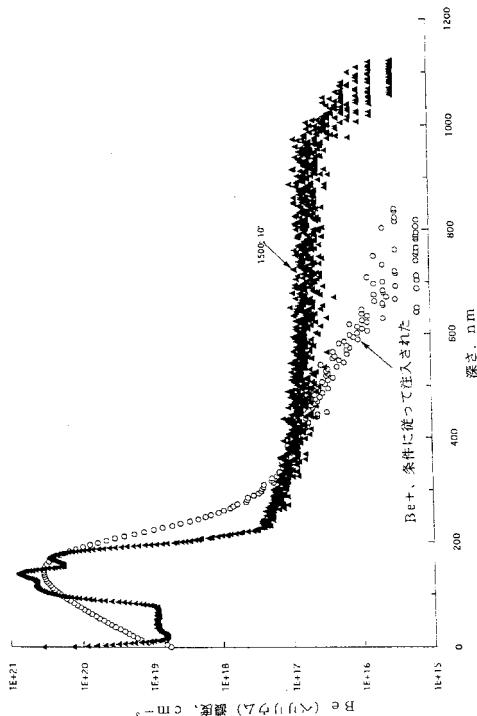

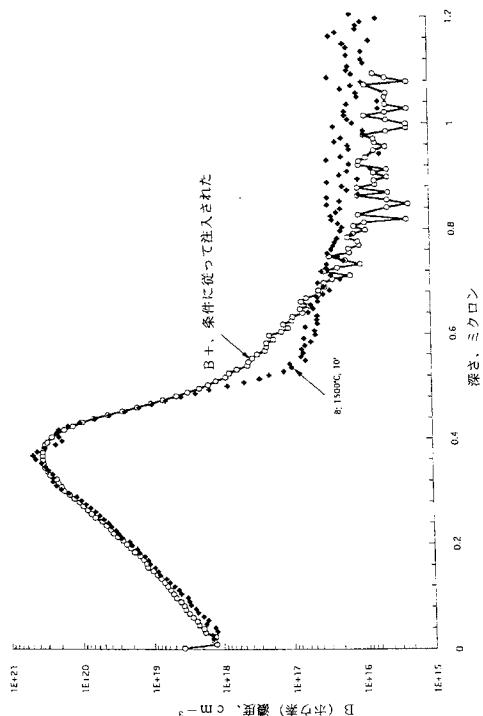

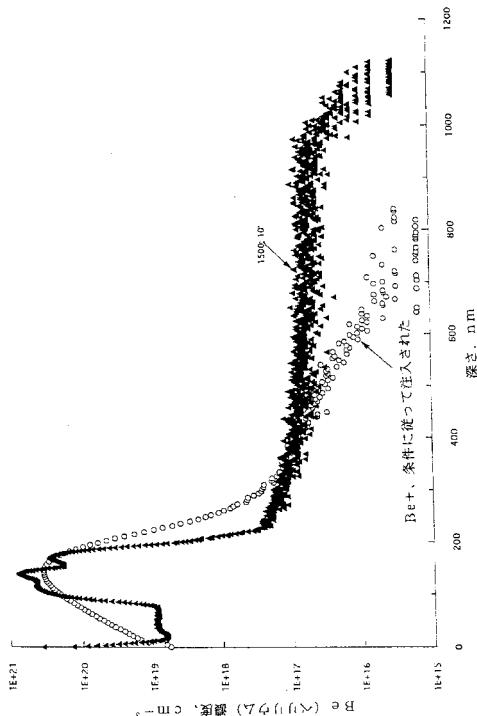

【0051】

すでに説明されたように、ベリリウムは深いp+注入領域にとって好ましい。なぜならベリリウムはドリフト領域102と階段形接合を形成することができるからである。図5と図6はそれぞれアニール後のホウ素とベリリウムの拡散を比較した図である。

【0052】

特に図5は、ホウ素が室温にて4H-SiC中に180keVのエネルギーと $4 \times 10^{15} \text{ cm}^{-2}$ の注入量において注入され、 $2.3 \times 10^{15} \text{ cm}^{-3}$ のホウ素キャリア濃度が実現される場合の、深さに対するホウ素濃度を示している。アニールは10分間1500において行われる。図5に示されているように、アニールの後に、前述のように注入されたホウ素(as-implanted boron)は拡散して、濃度は次第に減少するのみである。

【0053】

それとは対照的に、図6に示されるように、ベリリウムは室温にて4H-SiC基板内に40keVのエネルギーと $3.2 \times 10^{15} \text{ cm}^{-2}$ の注入量において注入され、 $1 \times 10^{19} \text{ cm}^{-3}$ のホウ素キャリア濃度が実現される。図6に示されているように、10分間1500においてアニールが行われた後、前述のように注入されたベリリウムは比較的に一定のキャリア濃度で拡散し、その濃度は約1000nmにおいて急速に減少する。したがって、ベリリウムでは、ホウ素と比較してより深いより一様な拡散が、ドリフト領域と階段形接合を形成しながら生じる。

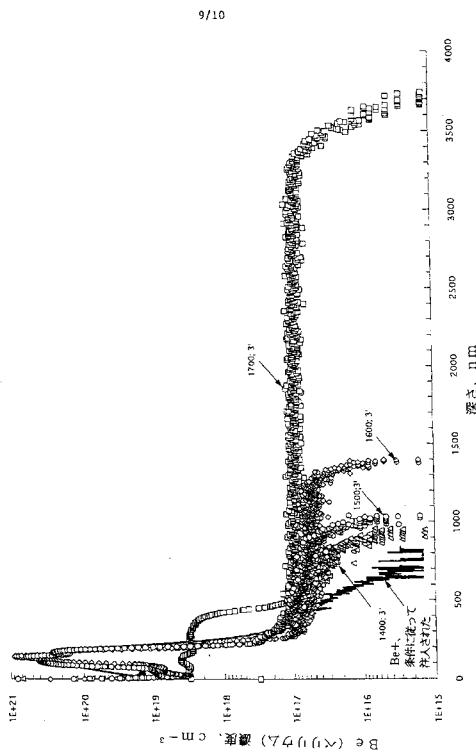

【0054】

図7はさらに、アニールの間の注入されたベリリウムの拡散を示している。ベリリウムは図6に関して記述された条件下で注入される。図7に示されるように、アニール温度が一定のアニール時間3分において1400から1700まで増大するに従って、拡散の深さが増加してもキャリア濃度は一様性を維持し、その後急激に減少する。したがって、ベリリウムはホウ素よりも好ましいかもしれない。

10

20

30

40

50

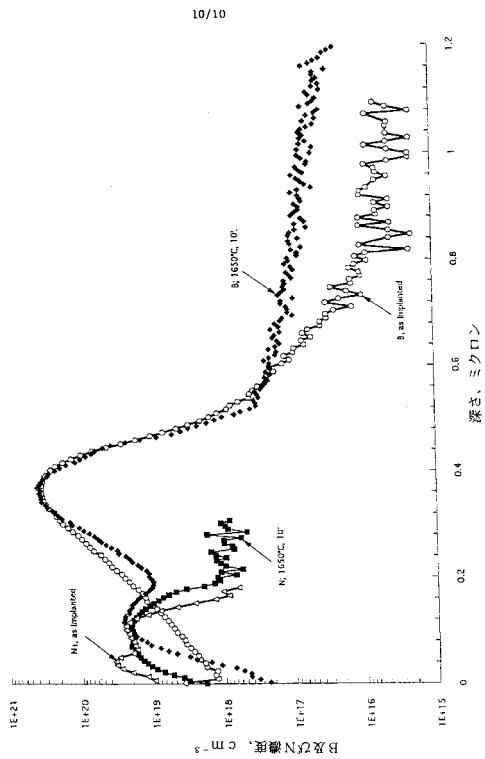

## 【0055】

次に図8には、1650において10分のアニールの間の注入されたホウ素と窒素の拡散が示されている。図8では、ホウ素は室温にて180keVのエネルギーと $4 \times 10^{15} \text{ cm}^{-2}$ の注入量において注入される。2つの窒素注入は、それぞれ25keVと60keVのエネルギー及び $1.5 \times 10^{14} \text{ cm}^{-2}$ と $2.5 \times 10^{14} \text{ cm}^{-2}$ の注入量において実行される。図8に示されているように、極めてわずかな窒素拡散が1650における10分のアニールの間に生じる。しかしながら、相当量のホウ素拡散がこのアニールの間に生じる。しかしながらホウ素は浅い窒素注入領域から離れてもっと深く拡散するけれども、ホウ素はその浅い窒素注入領域を通って炭化シリコン基板の表面まで拡散しない、ということは注意すべきである。

10

## 【0056】

それ故に、自己整列したソースとpベース領域、そして一様なpチャネルを備えた高性能炭化シリコンパワーデバイスが製造され得る。反転層は基板表面を横方向に横切るように形成できる。pベースの逆プロファイル( retrograde profile )によって、インプラン特されたn+ソースのより低い閾値電圧とより高い活性化が得られてよい。アルミニウムはpベース領域に使用される必要はないので、さらに閾値電圧を低下させることができるより高いクオリティでより薄いゲート酸化物領域が得られてよい。

## 【0057】

さらに、高電場がpベースに存在する必要はなく、その結果、散乱または電場集中に関係する問題は回避され得る。オン状態動作の間の熱電子注入の減少を可能にするために、鋭いコーナがn+領域内に存在する必要はない。拡散チャネルは、低い界面トラップ密度と固定電荷を与えることができる、反応性イオンエッチングのダメージのない炭化シリコン/二酸化シリコン界面を与える可能性があるので、チャネルにおける高移動度も与えられる可能性がある。

20

## 【0058】

最後に、少なくとも1つのマスクを排除して、そしてタイトな整列許容誤差の必要性を減少させる自己整列を実現することによって、単純化された製造法が提供され得る。従って、炭化シリコンパワーデバイスを製造する改良された方法が実現され得る。

## 【0059】

本図面及び本明細書において、本発明の典型的な好ましい実施態様が開示されてきた。特定の用語が使用されているけれども、それらは一般的かつ記述的な意味合いでのみ使用されており、限定目的のためではない。本発明の請求の範囲は以下の請求項によって示される。

30

## 【図面の簡単な説明】

【図1】 図1A-図1Gは、本発明による炭化シリコン横型パワーMOSFETを製造する方法を説明するための断面図である。

【図2】 図1Gの平面図である。

【図3】 図3A-図3Gは、本発明による炭化シリコンの縦型パワーMOSFETを製造する方法を説明するための断面図である。

【図4】 図3Gの平面図である。

40

【図5】 アニールの間のホウ素の拡散を示したグラフである。

【図6】 アニールの間のベリリウムの拡散を示したグラフである。

【図7】 アニールの間のベリリウムの拡散を示したグラフである。

【図8】 アニールの間の窒素及びホウ素の拡散を示したグラフである。

【図1】

FIG. 1A.

FIG. 1B.

FIG. 1C.

FIG. 1D.

FIG. 1E.

FIG. 1F.

FIG. 1G.

【図2】

FIG. 2.

【図3】

FIG. 3A.

FIG. 3B.

FIG. 3C.

FIG. 3D.

FIG. 3E.

FIG. 3F.

FIG. 3G.

【図 4】

FIG. 4.

【図 5】

【図 6】

Figure 5

Figure 6

【 义 7 】

【 四 8 】

Figure 8

---

フロントページの続き

(51)Int.Cl.

F I

|         |        |         |

|---------|--------|---------|

| H 0 1 L | 21/265 | F       |

| H 0 1 L | 21/265 | Z       |

| H 0 1 L | 21/265 | 6 0 2 A |

(74)代理人 100094673

弁理士 林 銘三

(72)発明者 スヴォロフ, アレクサンダー・ヴィ

アメリカ合衆国ノースカロライナ州 27713, ダーラム, シアワスター・ドライブ 100,

アパートメント・ケイ

(72)発明者 パーマー, ジョン・ダブリュー

アメリカ合衆国ノースカロライナ州 27606, ローリー, ハンターズ・ブラフ・ドライブ 29

20

(72)発明者 シング, ランビル

アメリカ合衆国ノースカロライナ州 27513, ケアリー, ローズダウン・ドライブ 100, ア

パートメント 2シー

## 合議体

審判長 北島 健次

審判官 恩田 春香

審判官 西脇 博志

(56)参考文献 国際公開第98/02916 (WO, A1)

米国特許第5510281 (US, A)

国際公開第97/36318 (WO, A1)

特表平9-503626 (JP, A)

Jayarama N. Shenoy et al., "High-Voltage Double-Implanted Power MOSFET's in 6H-SiC", IEEE ELECTRON DEVICE LETTERS VOL. 18, No. 3, MARCH 1997, pp. 93-95

(58)調査した分野(Int.Cl., DB名)

H01L29/78

H01L21/336