(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-141627

(P2012-141627A)

(43) 公開日 平成24年7月26日(2012.7.26)

| (51) Int.Cl.                | F 1            | テーマコード (参考) |

|-----------------------------|----------------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 J    | 3K107       |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 624B | 5C080       |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 611A | 5C380       |

| <b>H05B 33/14</b> (2006.01) | G09G 3/20 670K |             |

|                             | G09G 3/20 611H |             |

審査請求 有 請求項の数 3 O L (全 64 頁) 最終頁に続く

|              |                                     |            |                                                                                   |

|--------------|-------------------------------------|------------|-----------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2012-46227 (P2012-46227)          | (71) 出願人   | 000153878                                                                         |

| (22) 出願日     | 平成24年3月2日 (2012.3.2)                |            | 株式会社半導体エネルギー研究所                                                                   |

| (62) 分割の表示   | 特願2006-325736 (P2006-325736)<br>の分割 |            | 神奈川県厚木市長谷398番地                                                                    |

| 原出願日         | 平成18年12月1日 (2006.12.1)              | (72) 発明者   | 木村 肇                                                                              |

| (31) 優先権主張番号 | 特願2005-349165 (P2005-349165)        |            | 神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内                                               |

| (32) 優先日     | 平成17年12月2日 (2005.12.2)              | F ターム (参考) | 3K107 AA01 AA05 BB01 BB06 BB08<br>CC02 CC14 CC33 CC41 CC45<br>EE03 HH02 HH04 HH05 |

| (33) 優先権主張国  | 日本国 (JP)                            |            |                                                                                   |

最終頁に続く

(54) 【発明の名称】 半導体装置、及び表示装置

## (57) 【要約】

【課題】トランジスタのしきい値電圧のばらつきに起因する電流値のばらつきを抑制することを課題とする。また、ビデオ信号によって指定された輝度からのはずれが少なくかつデューティー比が高い表示装置を提供することを課題とする。

【解決手段】負荷と、前記負荷に供給する電流値を制御するトランジスタと、容量素子と、電源線と、第1のスイッチ乃至第3のスイッチとを有し、前記容量素子に前記トランジスタのしきい値電圧を保持させた後、ビデオ信号に応じた電位を入力し、前記しきい値電圧に前記電位を加算した電圧を保持させることで、トランジスタのしきい値電圧のばらつきに起因した電流値のばらつきを抑制することができる。そのため、発光素子をはじめとする負荷に所望の電流を供給することができる。また、電源線の電位を変動させることでデューティー比が高い表示装置を提供することができる。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

容量素子と、トランジスタと、第1のスイッチと、第2のスイッチと、第3のスイッチと、第4のスイッチと、を有し、

前記トランジスタのソースまたはドレインの一方は前記第4のスイッチを介して第1の配線に電気的に接続され、

前記トランジスタのゲートは前記第2のスイッチを介して前記第1の配線と電気的に接続され、

前記第1の配線と前記第2のスイッチとは、スイッチ及び素子を介すことなく接続され、

前記トランジスタのソースまたはドレインの他方は負荷と電気的に接続され、

前記トランジスタのソースまたはドレインの他方は前記第3のスイッチを介して第2の配線と電気的に接続され、

前記トランジスタのゲートは前記第1のスイッチを介して第3の配線と電気的に接続され、

前記第1のスイッチと前記トランジスタのゲートとは、スイッチ及び素子を介すことなく接続され、

前記トランジスタのソースまたはドレインの他方は前記容量素子を介して前記トランジスタのゲートと電気的に接続されていることを特徴とする半導体装置。

**【請求項 2】**

容量素子と、トランジスタと、第1のスイッチと、第2のスイッチと、第3のスイッチと、第4のスイッチと、を有し、

前記トランジスタのソースまたはドレインの一方は前記第4のスイッチを介して第1の配線に電気的に接続され、

前記トランジスタのゲートは前記第2のスイッチを介して前記第1の配線と電気的に接続され、

前記第1の配線と前記第2のスイッチとは、スイッチ及び素子を介すことなく接続され、

前記トランジスタのソースまたはドレインの他方は表示素子と電気的に接続され、

前記トランジスタのソースまたはドレインの他方は前記第3のスイッチを介して第2の配線と電気的に接続され、

前記トランジスタのゲートは前記第1のスイッチを介して第3の配線と電気的に接続され、

前記第1のスイッチと前記トランジスタのゲートとは、スイッチ及び素子を介すことなく接続され、

前記トランジスタのソースまたはドレインの他方は前記容量素子を介して前記トランジスタのゲートと電気的に接続されていることを特徴とする表示装置。

**【請求項 3】**

請求項7において、

前記表示素子は発光素子であることを特徴とする表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は負荷に供給する電流をトランジスタで制御する機能を設けた半導体装置に係り、信号によって輝度が変化する電流駆動型表示素子で形成された画素や、その画素を駆動させる信号線駆動回路や走査線駆動回路を含む表示装置に関する。また、その駆動方法に関する。また、その表示装置を表示部に有する電子機器に関する。

**【背景技術】****【0002】**

近年、画素をエレクトロルミネッセンス(EL：Electro Luminescence

10

20

30

40

50

n c e )などの発光素子を用いた自発光型の表示装置、いわゆる発光装置が注目を浴びている。このような自発光型の表示装置に用いられる発光素子としては、有機発光ダイオード(OLED(Organic Light Emitting Diode))、EL素子が注目を集めしており、ELディスプレイなどに用いられるようになってきている。これらの発光素子は自ら発光するため、液晶ディスプレイに比べて画素の視認性が高く、バックライトが不要である。また、応答速度が速い等の利点がある。なお、発光素子の輝度は、発光素子を流れる電流値によって制御されるものが多い。

#### 【0003】

また、発光素子の発光を制御するトランジスタが画素ごとに設けられたアクティブマトリクス型表示装置の開発が進められている。アクティブマトリクス型表示装置は、パッシブマトリクス型表示装置では困難な高精細、大画面の表示を可能とするだけでなく、パッシブマトリクス型表示装置を上回る低い消費電力で動作するため実用化が期待されている。

10

#### 【0004】

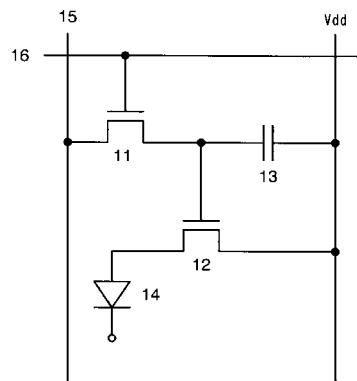

従来のアクティブマトリクス型表示装置の画素の構成を図46に示す(特許文献1)。図46に示した画素は、薄膜トランジスタ(Thin Film Transistor:TFT)11、TFT12、容量素子13、発光素子14を有し、信号線15及び走査線16に接続されている。なお、TFT12のソースもしくはドレイン電極のいずれか一方及び容量素子13の一方の電極には電源電位Vddが供給され、発光素子14の対向電極にはグランド電位が供給されている。

20

#### 【0005】

このとき、発光素子に供給する電流値を制御するTFT12、即ち駆動用TFTの半導体層にアモルファスシリコンを用いた場合、劣化等によりしきい値電圧(Vth)に変動が生じる。この場合、異なる画素に信号線15から同じ電位を印加したにもかかわらず、発光素子14に流れる電流は画素ごとに異なり、表示される輝度が画素によって不均一となる。なお、駆動用TFTの半導体層にポリシリコンを用いた場合においても、トランジスタの特性が劣化したり、ばらついたりする。

#### 【0006】

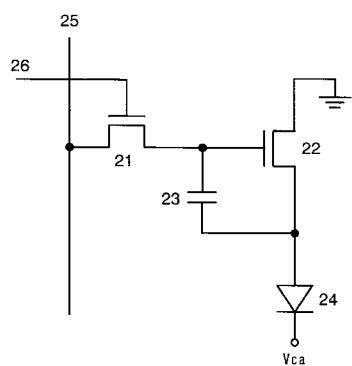

この問題を改善すべく、特許文献2において図47の画素を用いた動作方法が提案されている。図47に示した画素は、トランジスタ21、発光素子24に供給する電流値を制御する駆動用トランジスタ22、容量素子23、発光素子24を有し、画素は信号線25、走査線26に接続されている。なお、駆動用トランジスタ22はNMOSトランジスタであり、駆動用トランジスタ22のソース電極もしくはドレイン電極のいずれか一方にはグランド電位が供給され、発光素子24の対向電極にはVcaが供給される。

30

#### 【0007】

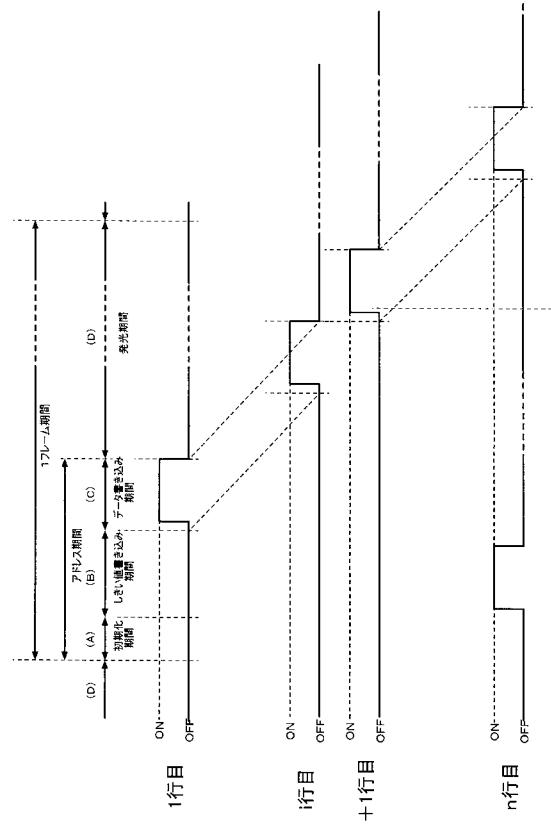

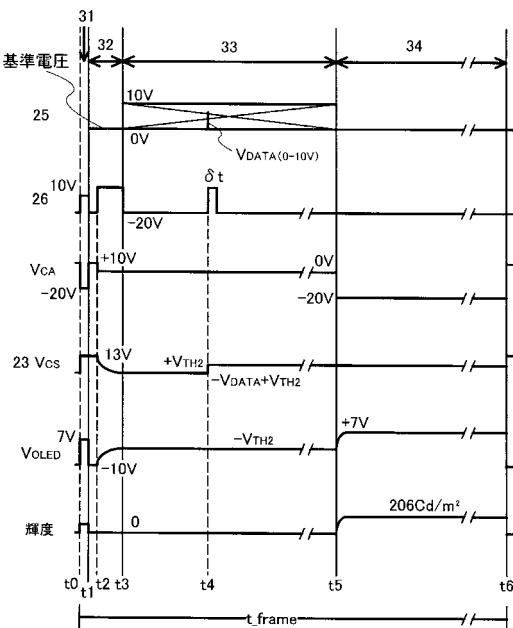

この画素の動作におけるタイミングチャートを図48に示す。図48において、1フレーム期間は、初期化期間31、しきい値(Vth)書き込み期間32、データ書き込み期間33及び発光期間34に分割される。なお、1フレーム期間とは1画面分の画像を表示する期間に相当し、初期化期間、しきい値(Vth)書き込み期間及びデータ書き込み期間をまとめてアドレス期間と呼ぶ。

40

#### 【0008】

まず、しきい値書き込み期間32において、駆動用トランジスタ22のしきい値電圧が容量素子に書き込まれる。その後、データ書き込み期間33において、画素の輝度を示すデータ電圧(Vdata)が容量素子に書き込まれ、Vdata + Vthが容量素子に蓄積される。そして、発光期間において駆動用トランジスタ22はオンとなり、Vcaを変化させることでデータ電圧によって指定された輝度で発光素子24が点灯する。このような動作により、駆動用トランジスタのしきい値の変動による輝度のばらつきを低減している。

#### 【0009】

特許文献3においても、駆動用TFTのしきい値電圧にデータ電位を加えた電圧がゲー

10

20

30

40

50

ト・ソース間電圧となり、TFTのしきい値電圧が変動した場合であっても流れる電流は変化しないことが開示されている。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開平8-234683号公報

【特許文献2】特開2004-295131号公報

【特許文献3】特開2004-280059号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

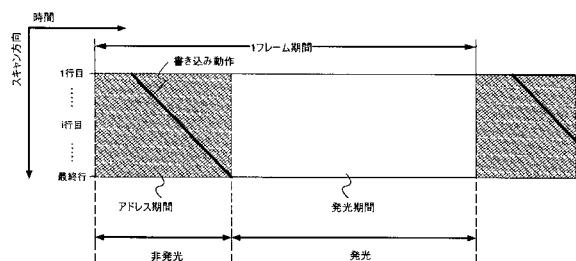

特許文献2及び3に記載されている動作方法はいずれの場合においても、V<sub>ca</sub>の電位を1フレーム期間当たりに数度と変化させることで上述した初期化、しきい値電圧の書き込み、発光を行っていた。これらの画素において、V<sub>ca</sub>が供給されている発光素子の一方の電極、即ち対向電極は画素領域全体に形成されているため、初期化及びしきい値電圧の書き込み以外にデータの書き込み動作を行っている画素がたとえ一つでもあると発光素子を発光させることができない。よって、図49に示すように、1フレーム期間における発光期間の割合（即ち、デューティー比）が小さくなってしまう。

【0012】

デューティー比が低いと発光素子や駆動用トランジスタに流す電流値を大きくする必要があるため、発光素子にかかる電圧が大きくなり消費電力が大きくなる。また、発光素子や駆動用トランジスタが劣化しやすくなるため、劣化前と同等の輝度を得るにはさらに大きな電力を要することになる。

【0013】

また、対向電極は全画素接続されているため、発光素子は容量の大きい素子として機能する。よって、対向電極の電位を変えるためには、高い消費電力が必要となる。

【0014】

上記問題を鑑み、本発明は、消費電力が低く、デューティー比の高い表示装置を提供することを課題とする。また、データ電位によって指定された輝度からのずれが少ない画素構成、半導体装置、及び表示装置を得ることを課題とする。

【0015】

なお、発光素子を有する表示装置のみが対象となるわけではなく、本発明はトランジスタのしきい値電圧のばらつきに起因する電流値のばらつきを抑制することを課題とする。よって、駆動用トランジスタにより制御された電流を供給する先は、発光素子に限定されない。

【課題を解決するための手段】

【0016】

本発明の一は、トランジスタと、第1のスイッチと、第2のスイッチとを含む画素を有し、前記トランジスタのソース電極及びドレイン電極の一方は前記第1のスイッチを介して前記トランジスタのゲート電極に電気的に接続され、前記トランジスタのソース電極及びドレイン電極の他方は画素電極に電気的に接続され、前記トランジスタのソース電極及びドレイン電極の他方は前記第2のスイッチに電気的に接続され、前記トランジスタのゲート電極には、前記画素の階調に従った信号を入力することを特徴とする半導体装置である。

【0017】

本発明の一は、保持容量と、トランジスタと、第1のスイッチと、第2のスイッチと、第3のスイッチとを有し、前記トランジスタのソース電極及びドレイン電極の一方は第1の配線に電気的に接続され、前記トランジスタのソース電極及びドレイン電極の他方は画素電極と電気的に接続され、前記トランジスタのソース電極及びドレイン電極の他方は前記第3のスイッチを介して第2の配線と電気的に接続され、前記トランジスタのゲート電

10

20

30

40

50

極は前記第1のスイッチを介して第3の配線と電気的に接続され、前記トランジスタのゲート電極は前記第2のスイッチを介して前記第1の配線と電気的に接続され、前記トランジスタのソース電極及びドレイン電極の他方は前記保持容量を介して前記ゲート電極と電気的に接続されていることを特徴とする半導体装置である。

【0018】

本発明の一は、容量素子と、トランジスタと、第1のスイッチと、第2のスイッチと、第3のスイッチとを有し、前記トランジスタのソース電極及びドレイン電極の一方は第1の配線に電気的に接続され、前記トランジスタのソース電極及びドレイン電極の他方は画素電極と電気的に接続され、前記トランジスタのソース電極及びドレイン電極の他方は前記第3のスイッチを介して第2の配線と電気的に接続され、前記トランジスタのゲート電極は前記第1のスイッチを介して第3の配線と電気的に接続され、前記トランジスタのゲート電極は前記第2のスイッチを介して前記第1の配線と電気的に接続され、前記トランジスタのソース電極及びドレイン電極の他方は前記容量素子を介して前記ゲート電極と電気的に接続されていることを特徴とする半導体装置である。

10

【0019】

本発明の一は、トランジスタと、容量素子と、第1のスイッチと、第2のスイッチと、第3のスイッチと、第4のスイッチとを有し、前記トランジスタのソース電極及びドレイン電極の一方は前記第4のスイッチを介して第1の配線に電気的に接続され、前記トランジスタのソース電極及びドレイン電極の他方は画素電極と電気的に接続され、前記トランジスタのソース電極及びドレイン電極の他方は前記第3のスイッチを介して第2の配線と電気的に接続され、前記トランジスタのゲート電極は前記第1のスイッチを介して第3の配線と電気的に接続され、前記トランジスタのゲート電極は前記第2のスイッチを介して前記第1の配線と電気的に接続され、前記トランジスタのソース電極及びドレイン電極の他方は前記容量素子を介して前記ゲート電極と電気的に接続されていることを特徴とする半導体装置である。

20

【0020】

本発明の一は、トランジスタと、容量素子と、第1のスイッチと、第2のスイッチと、第3のスイッチと、第4のスイッチとを有し、前記トランジスタのソース電極及びドレイン電極の一方は第1の配線に電気的に接続され、前記トランジスタのソース電極及びドレイン電極の他方は前記第4のスイッチを介して画素電極と電気的に接続され、前記トランジスタのソース電極及びドレイン電極の他方は前記第4のスイッチ及び前記第3のスイッチを介して第2の配線と電気的に接続され、前記トランジスタのゲート電極は前記第1のスイッチを介して第3の配線と電気的に接続され、前記トランジスタのゲート電極は前記第2のスイッチを介して前記第1の配線と電気的に接続され、前記トランジスタのソース電極及びドレイン電極の他方は前記第4のスイッチ及び前記容量素子を介して前記ゲート電極と電気的に接続されていることを特徴とする半導体装置である。

30

【0021】

前記第2の配線は、前記第3のスイッチを制御する配線と同一であってもよい。

【0022】

前記第2の配線は、前行もしくは次行の第1乃至第3のスイッチを制御する走査線のいずれかであってもよい。

40

【0023】

前記トランジスタは、Nチャネル型トランジスタであってもよい。また、前記トランジスタの半導体層は、非結晶性半導体膜からなることを特徴としてもよい。さらに、前記トランジスタの半導体層は、アモルファスシリコンからなることを特徴としてもよい。

【0024】

また、前記トランジスタの半導体層は、結晶性半導体膜からなることを特徴としてもよい。

【0025】

上記発明において、前記第1の配線に入力される電位はV1もしくはV2の二値であり

50

、前記第1のスイッチ乃至前記第3のスイッチが非導通状態のときのみV2の値をとり、V1は前記第2の配線に入力される電位よりも高い電位であり、その差分は前記トランジスタのしきい値電圧分より大きく、V2はV1より高い値であることを特徴としてもよい。

#### 【0026】

また、前記トランジスタは、Pチャネル型トランジスタであってもよい。その場合、上記発明において、前記第1の配線に入力される電位はV1もしくはV2の二値をとり、前記第1のスイッチ乃至前記第3のスイッチが非導通状態のときのみV2の値であり、V1は前記第2の配線に入力される電位よりも低い電位であり、その差分は前記トランジスタのしきい値電圧の絶対値分より大きく、V2はV1より低い値であることを特徴としてもよい。

10

#### 【0027】

本発明の一は、ソース電極及びドレイン電極の一方が第1の配線に電気的に接続され、ソース電極及びドレイン電極の他方が第2の配線に電気的に接続されるトランジスタと、前記トランジスタのゲートソース間電圧を保持する保持容量と、前記第1の配線に入力される第1の電位を前記トランジスタのゲート電極に印加し、なおかつ前記第2の配線に入力される第2の電位を前記トランジスタのソース電極に印加することにより、前記保持容量に第1の電圧を保持させる手段と、前記保持容量の電圧を第2の電圧まで放電させる手段と、前記第1の電位に第3の電圧を加算した電位を前記トランジスタのゲート電極に印加し、前記第2の電圧と第4の電圧とを加算した第5の電圧を前記保持容量に保持させる手段と、前記第1の配線に前記第1の電位とは異なる第3の電位を入力することにより前記トランジスタに設定された電流を負荷に供給する手段とを有することを特徴とする半導体装置である。

20

#### 【0028】

本発明の一は、ソース電極及びドレイン電極の一方が第1の配線に電気的に接続され、ソース電極及びドレイン電極の他方が第2の配線に電気的に接続されるトランジスタと、前記トランジスタのゲートソース間電圧を保持する保持容量と、前記第1の配線に入力される第1の電位を前記トランジスタのゲート電極に印加し、なおかつ前記第2の配線に入力される第2の電位を前記トランジスタのソース電極に印加することにより、前記保持容量に第1の電圧を保持させる手段と、前記保持容量の電圧を前記トランジスタのしきい値電圧まで放電させる手段と、前記第1の電位に第2の電圧を加算した電位を前記トランジスタのゲート電極に印加し、前記トランジスタのしきい値電圧と第3の電圧とを加算した第4の電圧を前記保持容量に保持させる手段と、前記第1の配線に前記第1の電位とは異なる第3の電位を入力することにより前記トランジスタに設定された電流を負荷に供給する手段とを有することを特徴とする半導体装置である。

30

#### 【0029】

前記トランジスタは、Nチャネル型トランジスタであってもよい。また、前記トランジスタの半導体層は、非結晶性半導体膜からなることを特徴としてもよい。さらに、前記トランジスタの半導体層は、アモルファスシリコンからなることを特徴としてもよい。

40

#### 【0030】

また、前記トランジスタの半導体層は、結晶性半導体膜からなることを特徴としてもよい。

#### 【0031】

上記発明において、前記第1の電位は前記第2の電位よりも高い電位であり、その差分は前記トランジスタのしきい値電圧分より大きく、なおかつ前記第1の電位は前記第3の電位より低い値であることを特徴としてもよい。

#### 【0032】

また、前記トランジスタは、Pチャネル型トランジスタであってもよい。この場合、前記第1の電位は前記第2の電位よりも低い電位であり、その差分は前記トランジスタのしきい値電圧の絶対値分より大きく、なおかつ前記第1の電位は前記第3の電位より高い値

50

であることを特徴としてもよい。

【0033】

また、本発明の一は、上記に記載した半導体装置を有する表示装置である。また、前記表示装置を表示部に有する電子機器である。

【0034】

なお、明細書に示すスイッチは、電流の流れを制御できるものなら、電気的スイッチでも機械的なスイッチでも特に限定されない。トランジスタでもよいし、ダイオードでもよいし、それらを組み合わせた論理回路でもよい。スイッチとしてトランジスタを用いる場合、そのトランジスタは、単なるスイッチとして動作するため、トランジスタの極性（導電型）は特に限定されない。ただし、オフ電流が少ない方の極性のトランジスタを用いることが望ましい。オフ電流が少ないトランジスタとしては、LDD領域を設けているものやマルチゲート構造にしているもの等がある。また、スイッチとして動作させるトランジスタのソース電極の電位が、低電位側電源（V<sub>ss</sub>、GND、0Vなど）に近い状態で動作する場合はNチャネル型を、反対に、ソース電極の電位が、高電位側電源（V<sub>dd</sub>など）に近い状態で動作する場合はPチャネル型を用いることが望ましい。なぜなら、ゲートソース間電圧の絶対値を大きくできるため、スイッチとして、動作しやすいからである。なお、Nチャネル型とPチャネル型の両方を用いて、CMOS型のスイッチにしてもよい。

10

【0035】

なお、本発明において接続されているとは、電気的に接続されていることと同義である。したがって、間に別の素子やスイッチなどが配置されていてもよい。

20

【0036】

なお、負荷は、何でもよい。例えば、EL素子（有機EL素子、無機EL素子又は有機物及び無機物を含むEL素子）、電子放出素子などの発光素子の他、液晶素子、電子インクなど、電気磁気的作用によりコントラストが変化する表示媒体を適用することができる。なお、電子放出素子を用いた表示装置としてはフィールドエミッショナディスプレイ（FED）、SED方式平面型ディスプレイ（SED：Surface-conducting Electron Emitter Display）などが挙げられる。また電子インクを用いた表示装置としては電子ペーパーがある。

30

【0037】

本発明において、適用可能なトランジスタの種類に限定はなく、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ（TFT）、半導体基板やSOI基板を用いて形成されるトランジスタ、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタ、有機半導体やカーボンナノチューブを用いたトランジスタ、その他のトランジスタを適用することができる。また、トランジスタが配置されている基板の種類に限定はなく、単結晶基板、SOI基板、ガラス基板、プラスチック基板などに配置することが出来る。

【0038】

なお、上述したように、本発明におけるトランジスタは、どのようなタイプのトランジスタでもよいし、どのような基板上に形成されていてもよい。したがって、回路の全てガラス基板上に形成されていてもよいし、プラスチック基板や単結晶基板に形成されていてもよいし、SOI基板上に形成されていてもよいし、どのような基板上に形成されていてもよい。あるいは、回路の一部が、ある基板に形成されており、回路の別の一部が、別の基板に形成されていてもよい。つまり、回路の全てが同じ基板上に形成されていてもよい。例えば、回路の一部は、ガラス基板上にTFTを用いて形成し、回路の別の一部は、単結晶基板上に形成し、そのICチップをCOG（Chip On Glass）で接続してガラス基板上に配置してもよい。あるいは、そのICチップをTAB（Tape Automated Bonding）やプリント基板を用いてガラス基板と接続してもよい。

40

【0039】

50

本明細書においては、一画素とは色要素を示すものとする。よって、R（赤）G（緑）B（青）の色要素からなるフルカラー表示装置の場合には、一画素とはRの色要素やGの色要素やBの色要素のいずれか一をいうものとする。

#### 【0040】

なお、本明細書において、画素がマトリクスに配置されているとは、縦縞と横縞を組み合わせたいわゆる格子状に配置されている場合はもちろんのこと、三色の色要素（例えばRGB）でフルカラー表示を行う場合に、1つの画像の最小要素を表す三つの色要素の画素がいわゆるデルタ配置されている場合も含むものとする。また、色要素毎にその画素の大きさが異なっていてもよい。

#### 【0041】

なお、本明細書において、半導体装置とは半導体素子（トランジスタやダイオードなど）を含む回路を有する装置をいう。また、表示装置とは、基板上に負荷を含む複数の画素やそれらの画素を駆動させる周辺駆動回路が形成された表示パネル本体だけではなく、それにフレキシブルプリントサーキット（FPC）やプリント配線基盤（PWB）が取り付けられたものも含む。

#### 【発明の効果】

#### 【0042】

本発明により、トランジスタのしきい値電圧のばらつきに起因する電流値のばらつきを抑制することができる。そのため、発光素子をはじめとする負荷に所望の電流を供給することができる。特に、負荷として発光素子を用いる場合、輝度のばらつきが少なくデューティー比が高い表示装置を提供することができる。

#### 【図面の簡単な説明】

#### 【0043】

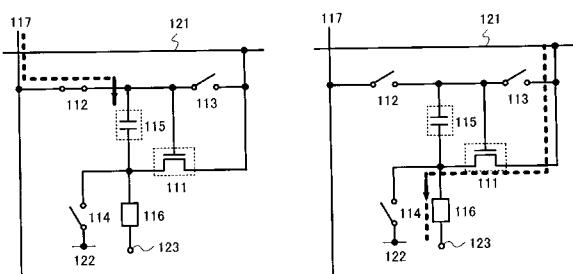

【図1】実施の形態1に示す画素構成を説明する図。

【図2】図1で示した画素の動作を説明するタイミングチャート。

【図3】図1で示した画素の動作を説明する図。

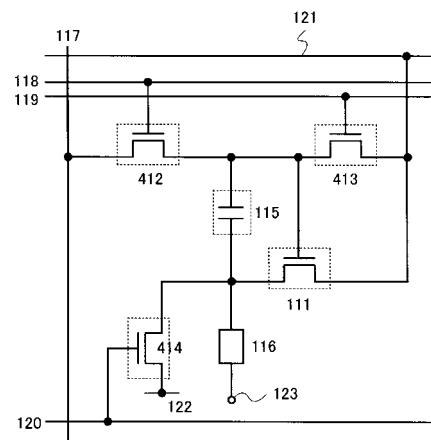

【図4】実施の形態1に示す画素構成を説明する図。

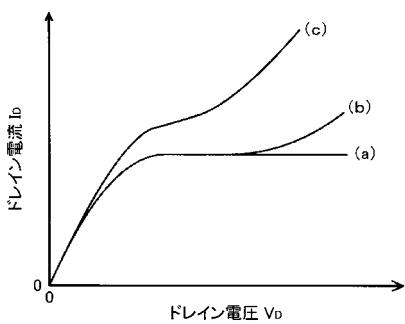

【図5】チャネル長変調による電圧-電流特性のモデル図。

【図6】実施の形態1に示す表示装置を説明する図。

【図7】実施の形態3に示す画素構成を説明する図。

【図8】実施の形態3に示す画素構成を説明する図。

【図9】実施の形態3に示す画素構成を説明する図。

【図10】実施の形態4に示す画素構成を説明する図。

【図11】実施の形態4に示す画素構成を説明する図。

【図12】実施の形態5に示す画素構成を説明する図。

【図13】図12で示した画素の動作を説明するタイミングチャート。

【図14】実施の形態7に示す画素構成を説明する図。

【図15】図14で示した画素の動作を説明するタイミングチャート。

【図16】図14で示した画素の動作を説明する図。

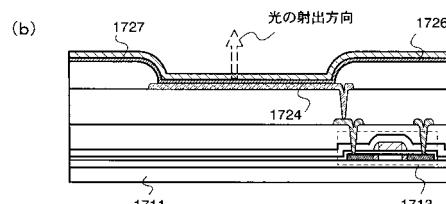

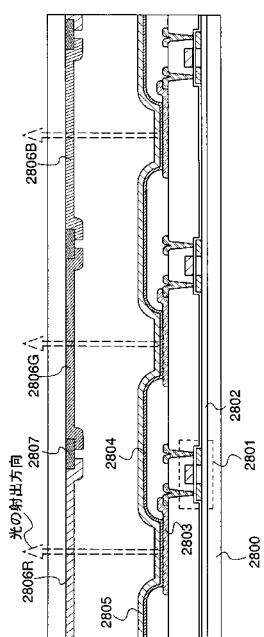

【図17】実施の形態8に示す画素の部分断面図。

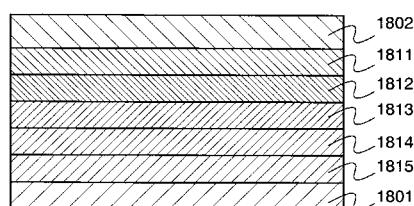

【図18】実施の形態8に示す発光素子を説明する図。

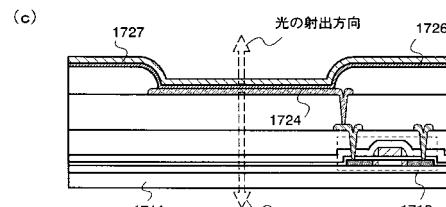

【図19】実施の形態8に示す光の取り出し方向を説明する図。

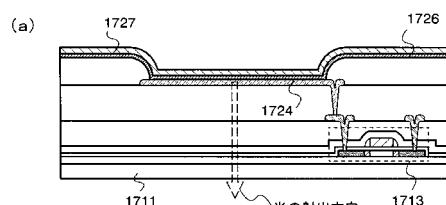

【図20】実施の形態8に示す画素の部分断面図。

【図21】実施の形態8に示す画素の部分断面図。

【図22】実施の形態8に示す画素の部分断面図。

【図23】実施の形態8に示す画素の部分断面図。

【図24】実施の形態8に示す画素の部分断面図。

【図25】実施の形態9に示す表示装置を説明する図。

【図26】実施の形態9に示す表示装置を説明する図。

【図27】実施の形態9に示す表示装置を説明する図。

10

20

30

40

50

- 【図28】実施の形態9に示す画素の部分断面図。

- 【図29】実施の形態6に示す画素構成を説明する図。

- 【図30】実施の形態6に示す画素構成を説明する図。

- 【図31】実施の形態6に示す画素構成を説明する図。

- 【図32】実施の形態7に示す画素構成を説明する図。

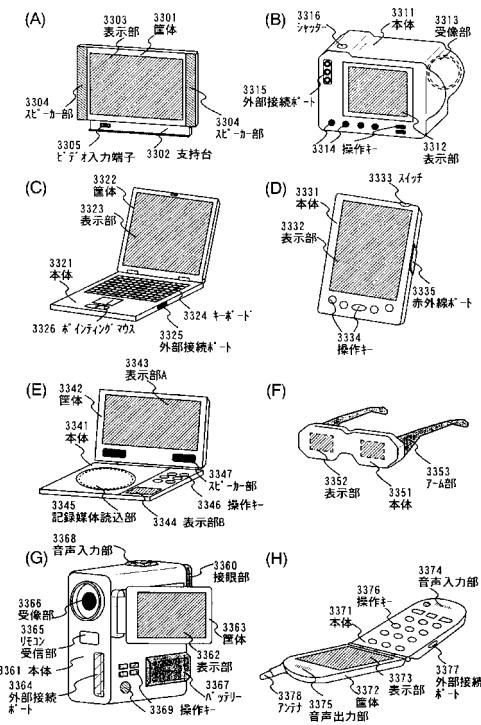

- 【図33】本発明を適用可能な電子機器を説明する図。

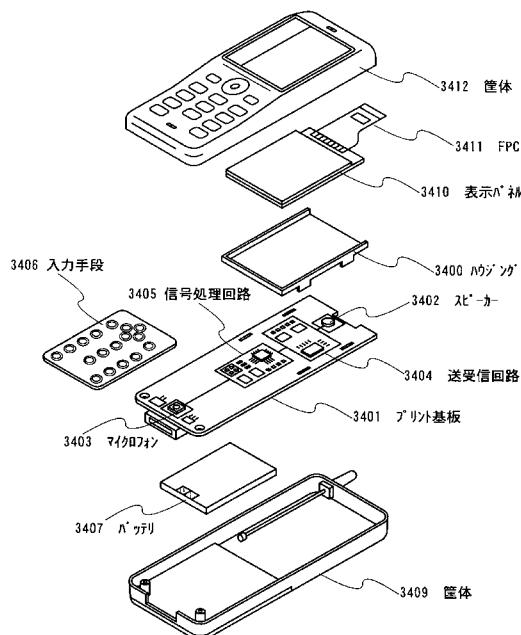

- 【図34】携帯電話機の構成例を示す図。

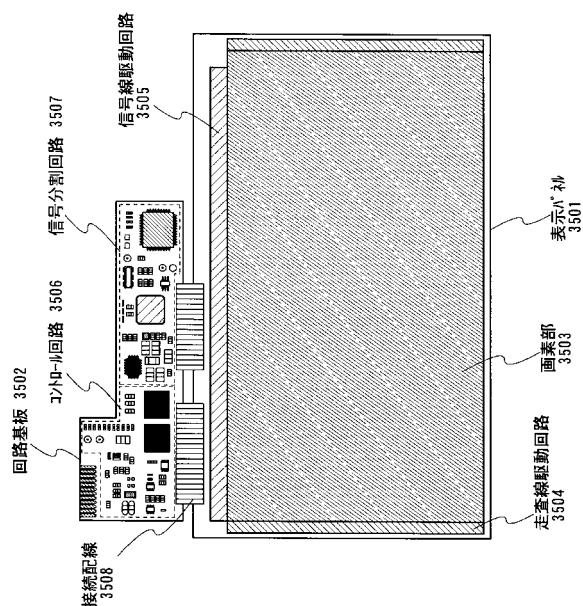

- 【図35】E Lモジュールの例を示す図。

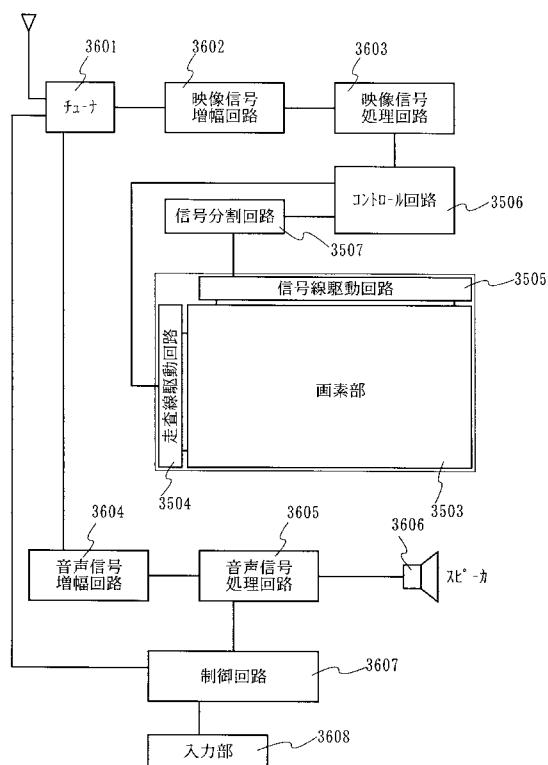

- 【図36】E Lテレビ受像器の主要な構成を示すブロック図。

- 【図37】実施の形態6に示す画素構成を説明する図。 10

- 【図38】図4に示す画素の上面図。

- 【図39】実施の形態2に示す画素構成を説明する図。

- 【図40】実施の形態1に示す表示装置の書き込み動作を説明する図。

- 【図41】実施の形態5に示す画素構成を説明する図。

- 【図42】デジタル階調方式と時間階調方式とを組み合わせた駆動方式を説明する図。

- 【図43】実施の形態6に示す画素構成を説明する図。

- 【図44】実施の形態6に示す画素構成を説明する図。

- 【図45】実施の形態1に記載した画素構成を説明する図。

- 【図46】従来技術の画素構成を説明する図。 20

- 【図47】従来技術の画素構成を説明する図。

- 【図48】従来技術に示した画素を動作させるタイミングチャート。

- 【図49】従来技術を用いた際の1フレーム期間における発光期間の割合を説明する図。

- 【発明を実施するための形態】

#### 【0044】

以下、本発明の一態様について説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いる。

#### 【0045】

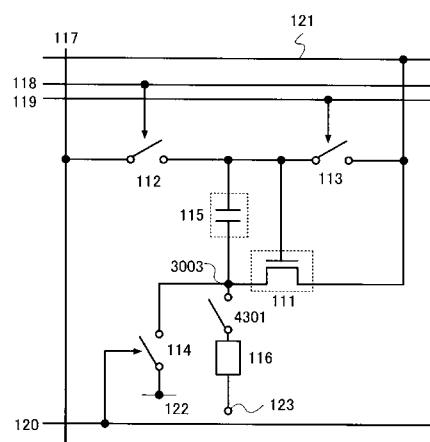

##### (実施の形態1)

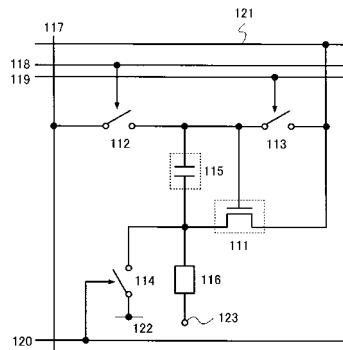

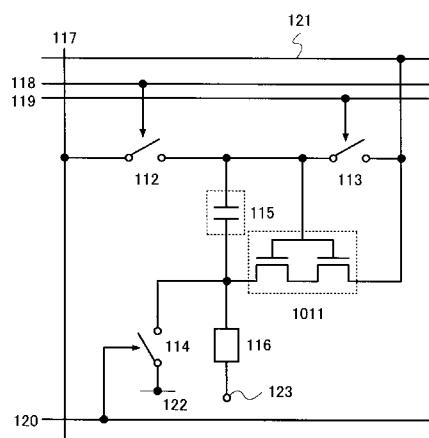

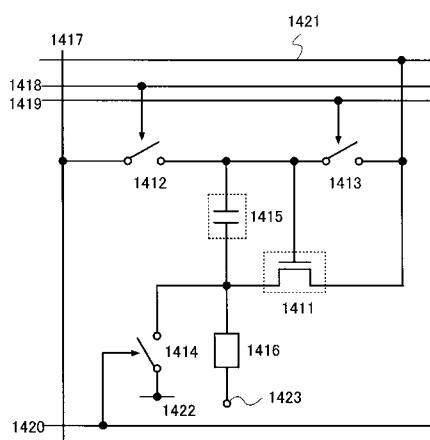

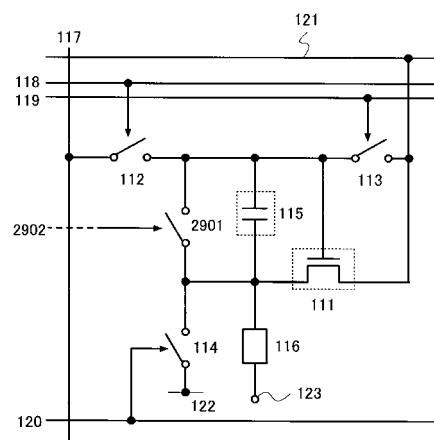

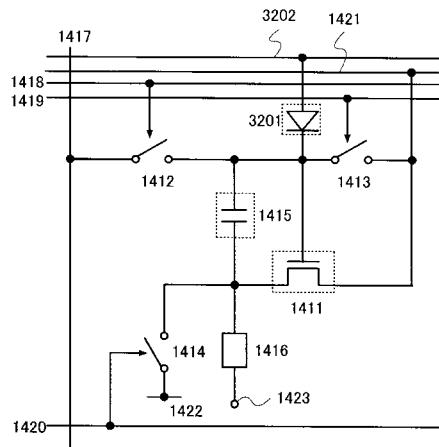

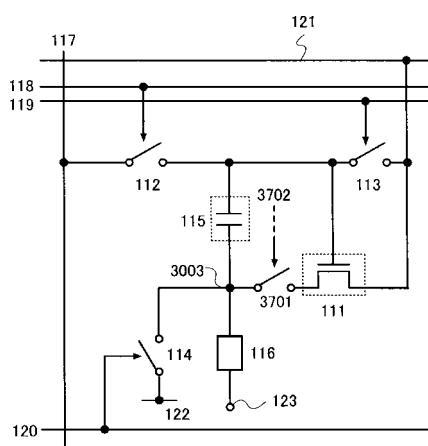

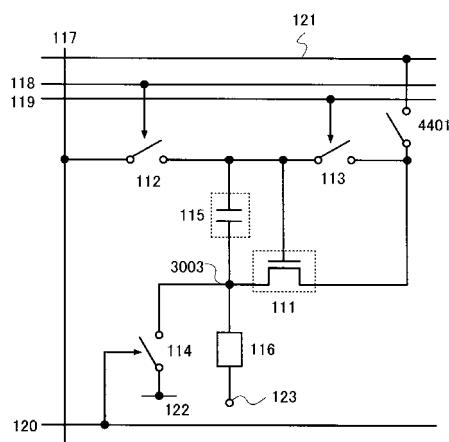

本発明の画素の基本構成について、図1を用いて説明する。図1に示す画素は、トランジスタ111、第1のスイッチ112、第2のスイッチ113、第3のスイッチ114、容量素子115、発光素子116を有する。なお、画素は、信号線117、第1の走査線118、第2の走査線119、第3の走査線120、電源線121及び電位供給線122に接続されている。本実施の形態において、トランジスタ111はNチャネル型トランジスタとし、そのゲート・ソース間電圧( $V_{g s}$ )がしきい値電圧( $V_{t h}$ )を上回ったとき、導通状態になるものとする。また、発光素子116の画素電極は陽極、対向電極123は陰極とする。なお、トランジスタのゲート・ソース間電圧は $V_{g s}$ 、ドレイン・ソース間電圧は $V_{d s}$ 、しきい値電圧は $V_{t h}$ 、容量素子に蓄積された電圧は $V_{c s}$ と記し、電源線121、電位供給線122、信号線117を、それぞれ第1の配線、第2の配線、第3の配線とも呼ぶ。 40

#### 【0046】

トランジスタ111の第1の電極(ソース電極及びドレイン電極の一方)は、発光素子116の画素電極に接続され、第2の電極(ソース電極及びドレイン電極の他方)は電源線121に接続され、ゲート電極は第2のスイッチ113を介して電源線121と接続されている。また、トランジスタ111のゲート電極は、第1のスイッチ112を介して信号線117とも接続されており、第1の電極は第3のスイッチ114を介して電位供給線122とも接続されている。

#### 【0047】

10

20

30

40

50

さらに、トランジスタ 111 のゲート電極と第 1 の電極との間に容量素子 115 が接続されている。つまり、容量素子 115 の第 1 の電極がトランジスタ 111 のゲート電極に、第 2 の電極がトランジスタ 111 の第 1 の電極に接続されている。容量素子 115 は、配線、半導体層や電極によって絶縁膜を挟むことで形成しても良いし、トランジスタ 111 のゲート容量を用いて省略することもできる。これらの電圧を保持する手段を保持容量と言う。

#### 【0048】

なお、第 1 の走査線 118、第 2 の走査線 119、第 3 の走査線 120 に信号を入力することにより、それぞれ第 1 のスイッチ 112、第 2 のスイッチ 113、第 3 のスイッチ 114 のオンオフが制御される。

10

#### 【0049】

信号線 117 には、ビデオ信号に相当する画素の階調に従った信号、即ち輝度データに応じた電位が入力される。

#### 【0050】

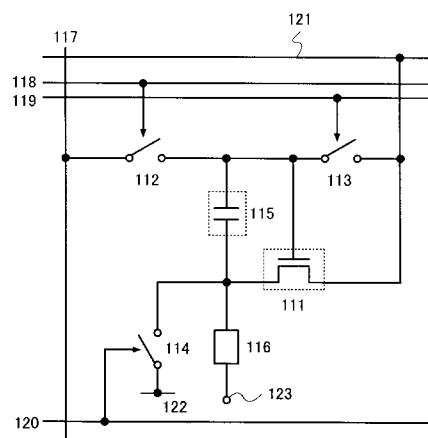

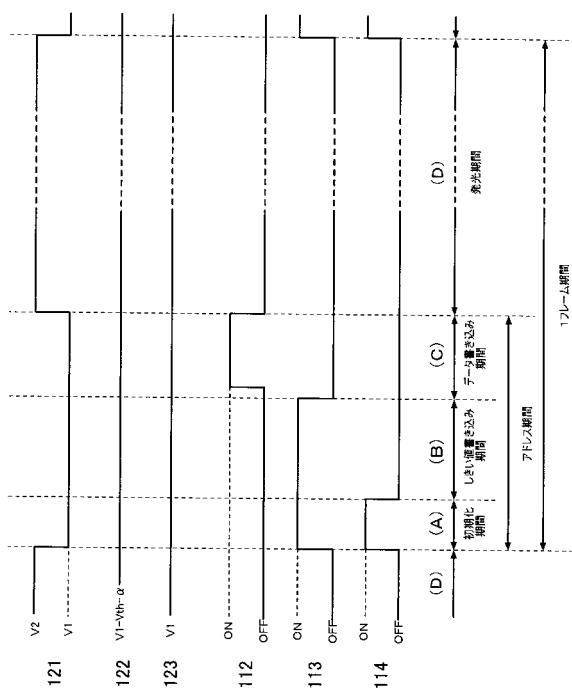

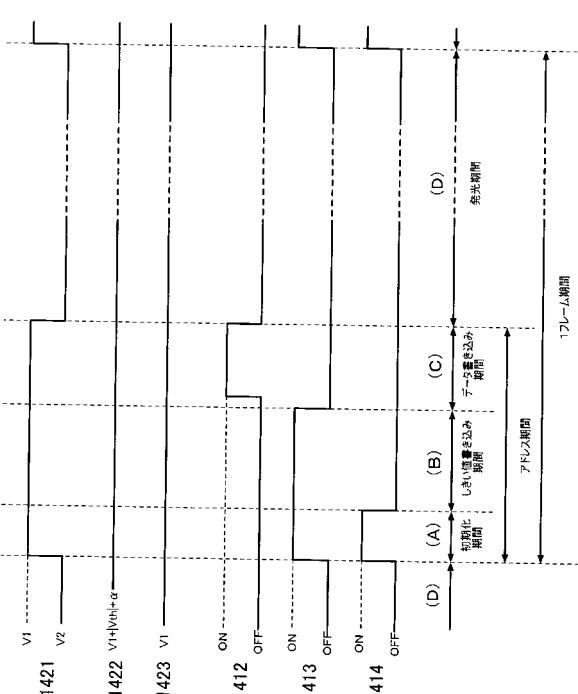

次に、図 1 で示した画素の動作について図 2 のタイミングチャート及び図 3 を用いて説明する。なお、図 2 において 1 画面分の画像を表示する期間に相当する 1 フレーム期間は、初期化期間、しきい値書き込み期間、データ書き込み期間及び発光期間に分割される。また、初期化期間、しきい値書き込み期間、データ書き込み期間をまとめてアドレス期間と呼ぶ。1 フレーム期間は特に限定はないが、画像を見る人がちらつき（フリッカ）を感じないように少なくとも 1 / 60 秒以下とすることが好ましい。

20

#### 【0051】

なお、発光素子 116 の対向電極 123 には V1 の電位が、電位供給線 122 には V1 - Vth - ( : 任意の正の数 ) の電位が入力される。また、電源線 121 には、アドレス期間は V1、発光期間では V2 の電位が入力される。ただし、V2 > V1 とする。

#### 【0052】

ここでは動作を説明するために、発光素子 116 の対向電極 123 の電位は、アドレス期間における電源線 121 の電位と同じであるとしたが、発光素子 116 が発光するために少なくとも必要とする電位差を VEL とすると対向電極 123 の電位は V1 - Vth -

VEL の電位より高い値であれば良い。また、発光期間における電源線 121 の電位 V2 は、対向電極 123 の電位と発光素子 116 が発光するために少なくとも必要とする電位差 ( VEL ) とを加算した値より大きい値であれば良いが、説明上ここでは対向電極 123 の電位を V1 としたため、V2 は V1 + VEL より大きい値であれば良いということになる。

30

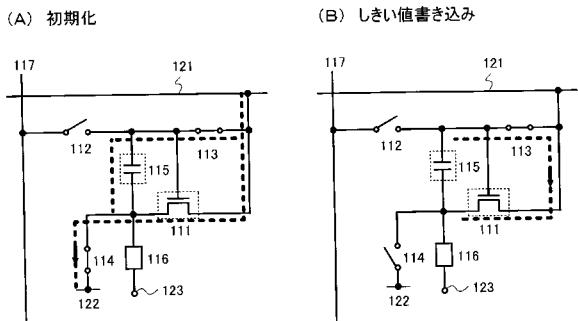

#### 【0053】

まず、図 2 (A) 及び図 3 (A) に示すように初期化期間では、第 1 のスイッチ 112 をオフとし、第 2 のスイッチ 113 及び第 3 のスイッチ 114 をオンとする。このとき、トランジスタ 111 の第 1 の電極はソース電極となり、その電位は電位供給線 122 と等しくなるため V1 - Vth - となる。一方、ゲート電極の電位は V1 となる。よって、トランジスタ 111 のゲート・ソース間電圧 Vgs は Vth+ となり、トランジスタ 111 は導通状態となる。そして、トランジスタ 111 のゲート電極と第 1 の電極との間に設けられた容量素子 115 に Vth+ が保持される。つまり、電位供給線 122 はトランジスタ 111 がオンとなる電位であれば良く、第 3 のスイッチ 114 はトランジスタ 111 がオンとなる電位をトランジスタの第 1 の電極に供給するか否かを選択する機能があれば良い。

40

#### 【0054】

次に、図 2 (B) 及び図 3 (B) に示すしきい値書き込み期間では、第 3 のスイッチ 114 をオフとする。そのため、トランジスタ 111 の第 1 の電極即ちソース電極の電位は次第に上昇し V1 - Vth となったところ、つまりトランジスタ 111 のゲート・ソース間電圧 Vgs がしきい値電圧 ( Vth ) となったところで、トランジスタ 111 は非導通状態となる。よって、容量素子 115 に保持される電圧は Vth となる。

50

## 【0055】

その後の図2(C)及び図3(C)に示すデータ書き込み期間においては、第2のスイッチ113をオフとした後、第1のスイッチ112をオンとし、信号線117より輝度データに応じた電位( $V_{1+} + V_{data}$ )を入力する。このときに、容量素子115に保持される電圧 $V_{cs}$ は、容量素子115及び発光素子116の静電容量をそれぞれ $C_1$ 、 $C_2$ とすると式(1)のように表すことができる。

## 【数1】

$$V_{cs} = V_{th} + V_{data} \times \frac{C_2}{C_1+C_2} \quad \dots(1)$$

## 【0056】

10

ただし、発光素子116は容量素子115に比べ膜厚が薄いえ電極面積が大きいため、 $C_2 >> C_1$ となる。よって、 $C_2 / (C_1 + C_2) \rightarrow 1$ より容量素子115に保持される電圧 $V_{cs}$ は式(2)となり、トランジスタ111は導通状態になる。なお、 $V_{data} = 0$ の電位を入力した場合には、非導通状態となり非発光とすることができる。

## 【数2】

$$V_{cs} = V_{th} + V_{data} \quad \dots(2)$$

## 【0057】

20

次に、図2(D)及び図3(D)に示す発光期間では、第1のスイッチ112をオフとし、電源線121の電位を $V_2$ とする。このとき、トランジスタ111のゲート・ソース間電圧は $V_{gs} = V_{th} + V_{data}$ であり、これに応じた電流がトランジスタ111及び発光素子116に流れ、発光素子116が発光する。

## 【0058】

なお、発光素子に流れる電流 $I$ は、トランジスタ111を飽和領域で動作させた場合、式(3)で表される。

## 【数3】

$$\begin{aligned} I &= \frac{1}{2} \left( \frac{W}{L} \right) \mu C_{ox} (V_{gs} - V_{th})^2 \\ &= \frac{1}{2} \left( \frac{W}{L} \right) \mu C_{ox} (V_{th} + V_{data} - V_{th})^2 \\ &= \frac{1}{2} \left( \frac{W}{L} \right) \mu C_{ox} (V_{data})^2 \quad \dots(3) \end{aligned}$$

30

## 【0059】

また、トランジスタ111を線形領域で動作させた場合、発光素子に流れる電流 $I$ は式(4)で表される。

## 【数4】

$$\begin{aligned} I &= \left( \frac{W}{L} \right) \mu C_{ox} [(V_{gs} - V_{th})V_{ds} - \frac{1}{2} V_{ds}^2] \\ &= \left( \frac{W}{L} \right) \mu C_{ox} [(V_{th} + V_{data} - V_{th})V_{ds} - \frac{1}{2} V_{ds}^2] \\ &= \left( \frac{W}{L} \right) \mu C_{ox} [(V_{data})V_{ds} - \frac{1}{2} V_{ds}^2] \quad \dots(4) \end{aligned}$$

40

## 【0060】

ここで、 $W$ はトランジスタ111のチャネル幅、 $L$ はチャネル長、 $\mu$ は移動度、 $C_{ox}$ は蓄積容量を指す。

## 【0061】

式(3)及び式(4)より、トランジスタ111の動作領域が飽和領域、線形領域のい

50

ずれの場合においても、発光素子 116 に流れる電流は、トランジスタ 111 のしきい値電圧 ( $V_{th}$ ) に依存しない。よって、トランジスタ 111 のしきい値電圧のばらつきに起因した電流値のばらつきを抑制し、輝度データに対応した電流値を発光素子 116 に供給することができる。

#### 【0062】

以上のことから、トランジスタ 111 のしきい値電圧のばらつきに起因した輝度のばらつきを抑制することができる。また、対向電極の電位を一定として動作させるため消費電力を低くすることが可能である。

#### 【0063】

さらに、トランジスタ 111 を飽和領域で動作させた場合においては、発光素子 116 の劣化による輝度のばらつきも抑制できる。発光素子 116 が劣化すると、発光素子 116 の  $V_{EL}$  は増大し、トランジスタ 111 の第 1 の電極、即ちソース電極の電位は上昇する。このとき、トランジスタ 111 のソース電極は容量素子 115 の第 2 の電極に、トランジスタ 111 のゲート電極は容量素子 115 の第 1 の電極に接続されており、なおかつゲート電極側は浮遊状態となっている。そのため、ソース電位の上昇に伴い、同じ電位だけトランジスタ 111 のゲート電位も上昇する。よって、トランジスタ 111 の  $V_{gs}$  は変化しないため、たとえ発光素子が劣化してもトランジスタ 111 及び発光素子 116 に流れる電流に影響しない。なお、式(3)においても発光素子に流れる電流  $I$  はソース電位やドレイン電位に依存しないことがわかる。

#### 【0064】

よって、トランジスタ 111 を飽和領域で動作させた場合においては、トランジスタ 111 のしきい値電圧のばらつき及び発光素子 116 の劣化に起因したトランジスタ 111 に流れる電流のばらつきを抑制することができる。

#### 【0065】

なお、トランジスタ 111 を飽和領域で動作させた場合、チャネル長  $L$  が短いほど、降伏現象によりドレイン電圧を著しく増大させると電流が大量に流れやすい。

#### 【0066】

また、ドレイン電圧をピンチオフ電圧より増大させるとピンチオフ点がソース側に移動し、実質チャネルとして機能する実効的なチャネル長は減少する。これにより、電流値が増大する。この現象をチャネル長変調と呼ぶ。なお、ピンチオフ点とはチャネルが消滅していくゲート下においてチャネルの厚さが 0 となる境界箇所であり、ピンチオフ電圧とはピンチオフ点がドレイン端となる時の電圧を指す。この現象も、チャネル長  $L$  が短いほど起こり易い。例えば、チャネル長変調による電圧 - 電流特性のモデル図を図 5 に示す。なお、図 5において、トランジスタのチャネル長  $L$  は (a) > (b) > (c) である。

#### 【0067】

以上のことから、トランジスタ 111 を飽和領域で動作させる場合、ドレイン・ソース間電圧  $V_{ds}$  に対して電流  $I$  が一定なら上述したように発光素子 116 の劣化の影響をより小さくできることを考慮に入れると、ドレイン・ソース間電圧  $V_{ds}$  に対する電流  $I$  はより一定に近い方が好ましい。よって、トランジスタ 111 のチャネル長  $L$  は長い方がより好ましい。たとえば、トランジスタのチャネル長  $L$  はチャネル幅  $W$  より大きい方が好ましい。また、チャネル長  $L$  は  $10 \mu m$  以上  $50 \mu m$  以下、より望ましくは  $15 \mu m$  以上  $40 \mu m$  以下が好ましい。ただし、チャネル長  $L$  及びチャネル幅  $W$  はこれに限定されない。

#### 【0068】

また、初期化期間において発光素子 116 に逆方向のバイアス電圧を印加しているため、発光素子における短絡箇所を絶縁化したり、発光素子の劣化を抑制することができる。よって、発光素子の寿命を延ばすことができる。

#### 【0069】

なお、トランジスタのしきい値電圧のばらつきに起因する電流値のばらつきを抑制することができるため、そのトランジスタによって制御された電流の供給先は特に限定されない。そのため、図 1 に示した発光素子 116 は、EL 素子(有機 EL 素子、無機 EL 素子

10

20

30

40

50

又は有機物及び無機物を含む E L 素子)、電子放出素子、液晶素子、電子インクなどを適用することができる。

#### 【0070】

また、トランジスタ 111 は発光素子 116 に供給する電流値を制御する機能を有していれば良く、トランジスタの種類は特に限定されない。そのため、結晶性半導体膜を用いた薄膜トランジスタ(TFT)、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ、半導体基板やSOI 基板を用いて形成されるトランジスタ、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタ、有機半導体やカーボンナノチューブを用いたトランジスタ、その他のトランジスタを適用することができます。

10

#### 【0071】

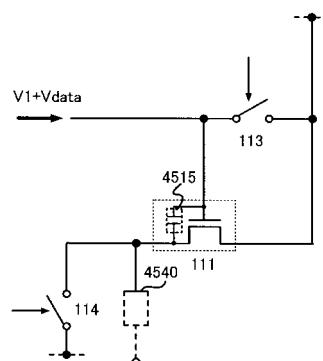

第1のスイッチ 112 は画素の階調に従った信号を容量素子に入力するタイミングを選択し、トランジスタ 111 のゲート電極に供給する信号を制御するものであり、第2のスイッチ 113 はトランジスタ 111 のゲート電極に所定の電位を与えるタイミングを選択し、トランジスタ 111 のゲート電極に所定の電位を供給するか否かを制御するものであり、第3のスイッチ 114 は容量素子 115 に書き込まれた電位を初期化するための所定の電位を与えるタイミングを選択したり、トランジスタ 111 の第1の電極の電位を低くするものである。そのため、第1のスイッチ 112、第2のスイッチ 113、第3のスイッチ 114 は、上記機能を有していれば特に限定されない。たとえば、トランジスタやダイオードでもよいし、それらを組み合わせた論理回路でもよい。なお、第1乃至第3のスイッチは、上記のタイミングで信号もしくは電位を画素に与えることができれば特に必要はない。例えば、画素の階調に従った信号をトランジスタ 111 のゲート電極に入力することができる場合には、図 45 に示すように第1のスイッチ 112 を設けなくても良い。図 45 に示す画素は、トランジスタ 111、第2のスイッチ 113、第3のスイッチ 114、画素電極 4540 を有する。そして、トランジスタ 111 の第1の電極(ソース電極及びドレイン電極の一方)は画素電極 4540 と第3のスイッチ 114 とに接続され、ゲート電極は第2のスイッチ 113 を介してトランジスタ 111 の第2の電極と接続されている。なお、トランジスタ 111 のゲート容量 4515 を保持容量として利用しているため、図 1 における容量素子 115 を特に設ける必要はない。このような画素においても、図 2 に示すタイミングチャートに従って各スイッチを動作させ、それぞれの電極に所望の電位を供給することで、トランジスタ 111 のしきい値電圧のばらつきに起因した電流値のばらつきを抑制することができる。よって、画素電極 4540 に所望の電流を供給することができる。

20

30

#### 【0072】

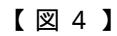

次に、図 4 に第1のスイッチ 112、第2のスイッチ 113、第3のスイッチ 114 に N チャネル型のトランジスタを適用した場合について示す。なお、図 1 の構成と共通するところは共通の符号を用いてその説明を省略する。

#### 【0073】

第1のスイッチングトランジスタ 412 が第1のスイッチ 112 に相当し、第2のスイッチングトランジスタ 413 が第2のスイッチ 113 に相当し、第3のスイッチングトランジスタ 414 が第3のスイッチ 114 に相当する。なお、トランジスタ 111 のチャネル長は、第1のスイッチングトランジスタ 412、第2のスイッチングトランジスタ 413 及び第3のスイッチングトランジスタ 414 のいずれのトランジスタのチャネル長より長い方が好ましい。

40

#### 【0074】

第1のスイッチングトランジスタ 412 のゲート電極は第1の走査線 118 に接続され、第1の電極が信号線 117 に接続され、第2の電極が容量素子 115 の第1の電極及びトランジスタ 111 のゲート電極に接続されている。

#### 【0075】

また、第2のスイッチングトランジスタ 413 はゲート電極が第2の走査線 119 に接

50

続され、第1の電極が容量素子115の第1の電極及びトランジスタ111のゲート電極に接続され、第2の電極が電源線121及びトランジスタ111の第2の電極と接続されている。

#### 【0076】

第3のスイッチングトランジスタ414はゲート電極が第3の走査線120に接続され、第1の電極が容量素子115の第2の電極、トランジスタ111の第1の電極及び発光素子116の画素電極に接続され、第2の電極が電位供給線122に接続されている。

#### 【0077】

各々のスイッチングトランジスタは、それぞれの走査線に入力される信号がHレベルのときにオンとなり、入力される信号がLレベルのときにオフとなる。

10

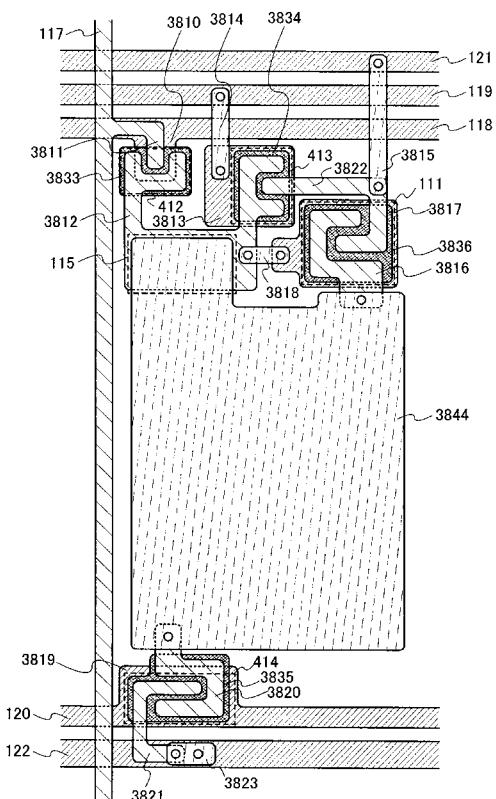

#### 【0078】

図4に示した画素の上面図の一形態を図38に示す。導電層3810は、第1の走査線118と第1のスイッチングトランジスタ412のゲート電極として機能する部分を含み、導電層3811は信号線117と第1のスイッチングトランジスタ412の第1の電極として機能する部分を含む。また、導電層3812は第1のスイッチングトランジスタ412の第2の電極として機能する部分と、容量素子115の第1の電極として機能する部分と第2のスイッチングトランジスタ413の第1の電極として機能する部分を含む。導電層3813は第2のスイッチングトランジスタ413のゲート電極として機能する部分を含み、配線3814を介して第2の走査線119と接続されている。導電層3822は第2のスイッチングトランジスタ413の第2の電極として機能する部分とトランジスタ111の第2の電極として機能する部分を含み、配線3815を介して電源線121と接続されている。導電層3816はトランジスタ111の第1の電極として機能する部分を含み、発光素子の画素電極3844と接続されている。導電層3817はトランジスタ111のゲート電極として機能する部分を含み、配線3818を介して導電層3812と接続されている。また、導電層3819は第3の走査線120と第3のスイッチングトランジスタ414のゲート電極として機能する部分を含む。導電層3820は第3のスイッチングトランジスタ414の第1の電極として機能する部分を含み、画素電極3844と接続されている。また、第3のスイッチングトランジスタ414の第2の電極として機能する部分を含む導電層3821は配線3823を介して電位供給線122と接続されている。

20

30

#### 【0079】

なお、各々の導電層のうち第1のスイッチングトランジスタ412のゲート電極、第1の電極及び第2の電極として機能する部分は半導体層3833と重なって形成されている部分であり、第2のスイッチングトランジスタ413のゲート電極、第1の電極及び第2の電極として機能する部分は半導体層3834と重なって形成されている部分であり、第3のスイッチングトランジスタ414のゲート電極、第1の電極及び第2の電極として機能する部分は半導体層3835と重なって形成されている部分である。また、トランジスタ111のゲート電極、第1の電極及び第2の電極として機能する部分は半導体層3836と重なって形成されている導電層部分である。容量素子115は、導電層3812と画素電極3844が重なっている部分に形成されている。

40

#### 【0080】

図4の画素構成においても、図1と同様の動作方法によりトランジスタ111のしきい値電圧のばらつきに起因した電流値のばらつきを抑制することができる。よって、輝度データに対応した電流を発光素子116に供給することができ、輝度のばらつきを抑制することができる。また、トランジスタ111を飽和領域で動作させた場合においては、発光素子116の劣化に起因した輝度のばらつきも抑制することができる。

#### 【0081】

また、Nチャネル型のトランジスタのみで画素を構成することができるため、製造工程の簡略化を図ることができる。また、画素を構成するトランジスタの半導体層にアモルファス半導体やセミアモルファス半導体（若しくは微結晶半導体ともいう）などの非晶質半

50

導体を用いることができる。例えば、アモルファス半導体としてアモルファスシリコン( $a\text{-Si:H}$ )が挙げられる。これら非晶質半導体を用いることにより、さらに製造工程の簡略化が可能である。したがって、製造コストの削減や歩留まりの向上を図ることができる。

#### 【0082】

なお、第1のスイッチングトランジスタ $412$ 、第2のスイッチングトランジスタ $413$ 及び第3のスイッチングトランジスタ $414$ は、単なるスイッチとして動作させるため、トランジスタの極性(導電型)は特に限定されない。ただし、オフ電流が少ないトランジスタを用いることが望ましい。オフ電流が少ないトランジスタとしては、LDD領域を設けているものやマルチゲート構造にしているものなどがある。また、Nチャネル型とPチャネル型の両方を用いて、CMOS型のスイッチにしてもよい。10

#### 【0083】

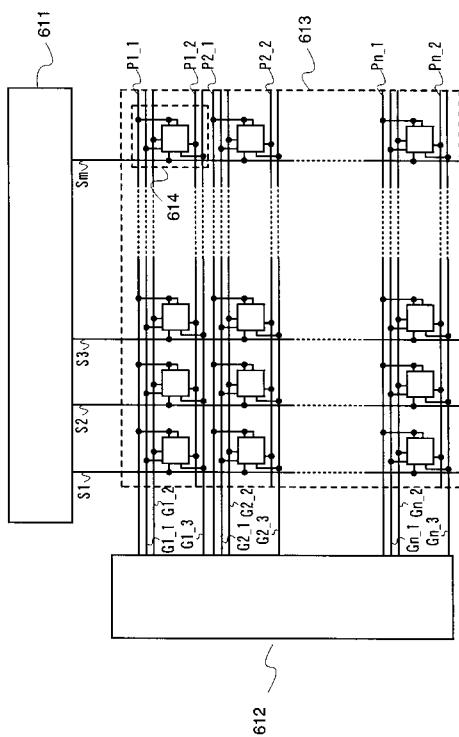

続いて、本発明の画素を有する表示装置について図6を用いて説明する。

#### 【0084】

表示装置は、信号線駆動回路 $611$ 、走査線駆動回路 $612$ 及び画素部 $613$ を有し、画素部 $613$ には、信号線駆動回路 $611$ から列方向に伸張して配置された複数の信号線 $S_1 \sim S_m$ と、走査線駆動回路 $612$ から行方向に伸張して配置された複数の第1の走査線 $G_{1 \sim 1} \sim G_{n \sim 1}$ 、第2の走査線 $G_{1 \sim 2} \sim G_{n \sim 2}$ 、第3の走査線 $G_{1 \sim 3} \sim G_{n \sim 3}$ 及び電源線 $P_{1 \sim 1} \sim P_{n \sim 1}$ と、信号線 $S_1 \sim S_m$ に対応してマトリクスに配置された複数の画素 $614$ とを有する。また、第1の走査線 $G_{1 \sim 1} \sim G_{n \sim 1}$ と平行に複数の電位供給線 $P_{1 \sim 2} \sim P_{n \sim 2}$ を有している。そして、各画素 $614$ は、信号線 $S_j$ (信号線 $S_1 \sim S_m$ のうちいずれか一)、第1の走査線 $G_{i \sim 1}$ (走査線 $G_{1 \sim 1} \sim G_{n \sim 1}$ のうちいずれか一)、第2の走査線 $G_{i \sim 2}$ 、第3の走査線 $G_{i \sim 3}$ 、電源線 $P_{i \sim 1}$ 、電位供給線 $P_{i \sim 2}$ と接続されている。20

#### 【0085】

なお、信号線 $S_j$ 、第1の走査線 $G_{i \sim 1}$ 、第2の走査線 $G_{i \sim 2}$ 、第3の走査線 $G_{i \sim 3}$ 、電源線 $P_{i \sim 1}$ 、電位供給線 $P_{i \sim 2}$ は、それぞれ図1の信号線 $117$ 、第1の走査線 $118$ 、第2の走査線 $119$ 、第3の走査線 $120$ 、電源線 $121$ 、電位供給線 $122$ に相当する。

#### 【0086】

走査線駆動回路 $612$ から出力される信号により、動作させる画素の行を選択すると共に同行に属するそれぞれの画素に対し同時に図2に示した動作を行う。なお、図2のデータ書き込み期間においては、選択された行の画素に信号線駆動回路 $611$ から出力されたビデオ信号を書き込む。このとき、それぞれの画素の輝度データに応じた電位が各信号線 $S_1 \sim S_m$ に入力される。30

#### 【0087】

図40に示すように、例えば $i$ 行目のデータ書き込み期間を終えると $i+1$ 行目に属する画素へ信号の書き込みを行う。なお、図40には、各行におけるデータ書き込み期間を表すためにこれを忠実に表すことができる図2の第1のスイッチ $112$ の動作のみを抜き出して記載している。また、 $i$ 行目においてデータ書き込み期間を終えた画素は、発光間に移り、その画素へ書き込まれた信号にしたがって発光する。40

#### 【0088】

よって、各行におけるデータ書き込み期間さえ重複しなければ、各行自由に初期化開始時期を設定することができる。また、各画素は自身のアドレス期間を除き発光することができるため、1フレーム期間における発光期間の割合(即ち、デューティー比)を非常に大きくでき、おおむね $100\%$ にすることも可能となる。よって、輝度のばらつきが少なくデューティー比が高い表示装置を得ることができる。

#### 【0089】

また、しきい値書き込み期間を長く設定することも可能であるため、トランジスタのしきい値電圧をより正確に容量素子に書き込むことができる。よって、表示装置としての信50

頼性が向上する。

**【0090】**

なお、図6に示した表示装置の構成は一例であって本発明はこれに限定されない。例えば、電位供給線P1\_2～Pn\_2は第1の走査線G1\_1～Gn\_1と平行に配置されている必要はなく、信号線S1～Smに平行に配置されていても良い。

**【0091】**

また、しきい値電圧のばらつきには、画素間における各トランジスタのしきい値電圧の違いのほか、1つのトランジスタに注目した場合において経時的なしきい値電圧の変化も含むものとする。さらに、各トランジスタのしきい値電圧の違いは、トランジスタの作製時におけるトランジスタ特性の違いによるものも含まれるものとする。なお、ここでいうトランジスタは発光素子等の負荷に電流を供給する機能を有するトランジスタを指す。

10

**【0092】**

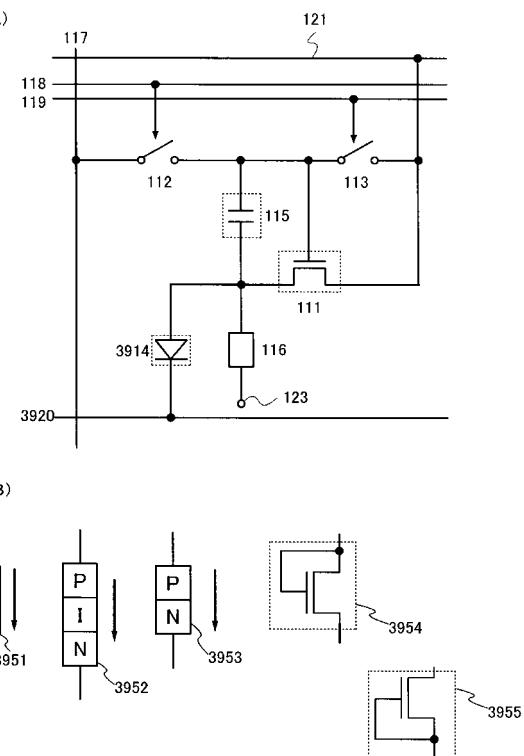

(実施の形態2)

本実施形態では、実施の形態1とは異なる構成の画素を図39に示す。なお、実施の形態1と同様のものに関しては共通の符号を用いて示し、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

**【0093】**

図39(A)に示す画素は、トランジスタ111、第1のスイッチ112、第2のスイッチ113、整流素子3914、容量素子115、発光素子116を有する。なお、画素は、信号線117、第1の走査線118、第2の走査線119、第3の走査線3920及び電源線121に接続されている。図39(A)に示した画素は、図1における第3のスイッチ114に整流素子3914を用いた構成となっており、容量素子115の第2の電極、トランジスタ111の第1の電極及び発光素子116の画素電極は、整流素子3914を介して第3の走査線3920と接続されている。つまり、整流素子3914はトランジスタ111の第1の電極から第3の走査線3920に電流が流れるように接続されている。もちろん、実施の形態1に示したように第1のスイッチ112及び第2のスイッチ113については、トランジスタ等を用いてもよい。また、整流素子3914には、図39(B)に示すショットキー・バリア型3951、PIN型3952、PN型3953のダイオードの他、ダイオード接続されているトランジスタ3954、3955等を用いることができる。ただし、トランジスタ3954及びトランジスタ3955は、電流を流す方向によってトランジスタの極性を適宜選択する必要がある。

20

**【0094】**

整流素子3914は、第3の走査線3920にHレベルの信号が入力されたときには電流が流れず、Lレベルの信号が入力されたときには整流素子3914に電流が流れる。よって、図39の画素を図1と同様に動作させる際には、初期化期間において第3の走査線3920にLレベルの信号を入力し、それ以外の期間においてはHレベルの信号を入力する。ただし、Lレベルの信号は、整流素子3914にただ電流が流れるだけではなく容量素子115の第2の電極の電位をV1-Vth-（：任意の正の数）にまで下げる必要があるためV1-Vth--（：任意の正の数）の電位であることとする。なお、-は整流素子3914の順方向におけるしきい値電圧を指す。

30

**【0095】**

上記事項を考慮し、図39の画素構成においても図1と同様に動作させることによりトランジスタ111のしきい値電圧のばらつきに起因した電流値のばらつきを抑制することができる。よって、輝度データに対応した電流を発光素子116に供給することができ、輝度のばらつきを抑制することが可能となる。また、トランジスタ111を飽和領域で動作させた場合においては、発光素子116の劣化に起因した輝度のばらつきも抑制することができる。さらに、整流素子3914を用いることで、配線数を減らすことが可能となり、開口率を向上させることができる。

40

**【0096】**

さらに、図6の表示装置に本実施形態で示した画素を適用することができる。実施の形

50

態1と同様、各行におけるデータ書き込み期間さえ重複しなければ、各行自由に初期化開始時期を設定することができる。また、各画素は自身のアドレス期間を除き発光することが可能であるため、1フレーム期間における発光期間の割合（即ち、デューティー比）を非常に大きくでき、おおむね100%にすることもできる。よって、輝度のばらつきが少なくデューティー比が高い表示装置を得ることができる。

#### 【0097】

また、しきい値書き込み期間を長く設定することも可能であるため、発光素子に流れる電流値を制御するトランジスタのしきい値電圧をより正確に容量素子に書き込むことができる。よって、表示装置としての信頼性が向上する。

#### 【0098】

また、本実施形態は、上述した図1以外にもその他の実施の形態に示した画素構成とも自由に組み合わせることができる。つまり、整流素子3914は、他の実施形態に示した画素にも適用することが可能である。

#### 【0099】

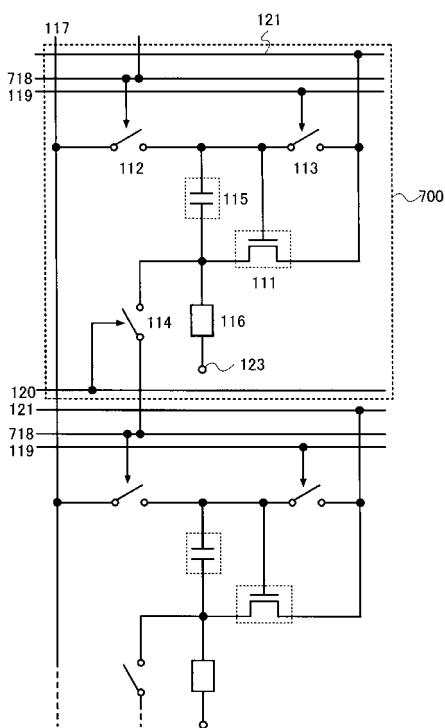

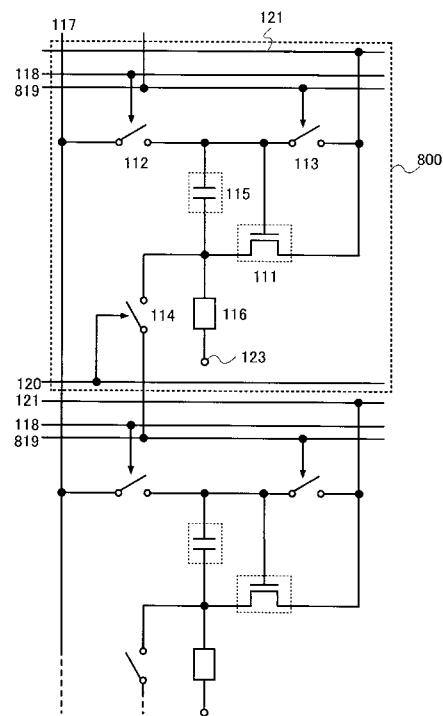

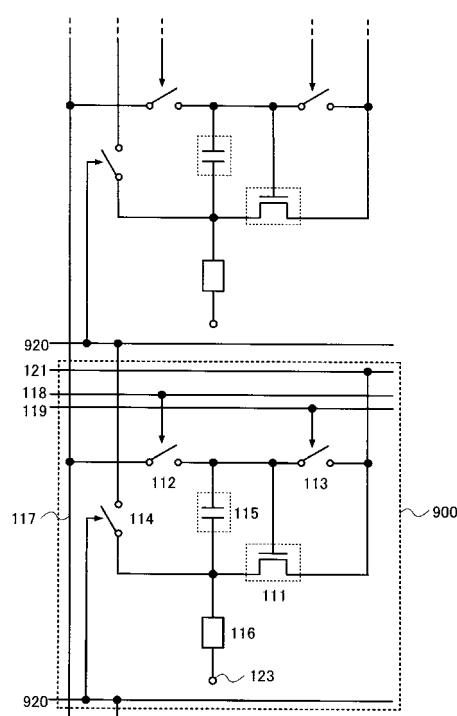

##### （実施の形態3）

本実施形態では、実施の形態1とは異なる構成の画素を図7乃至9に示す。なお、実施の形態1と同様のものに関しては共通の符号を用いて示し、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

#### 【0100】

図7に示す画素700は、トランジスタ111、第1のスイッチ112、第2のスイッチ113、第3のスイッチ114、容量素子115、発光素子116を有する。なお、画素700は、信号線117、第1の走査線718、第2の走査線119、第3の走査線120、電源線121及び次行の第1の走査線718に接続されている。

#### 【0101】

実施の形態1に示した図1の画素ではトランジスタ111の第1の電極は第3のスイッチ114を介して電位供給線122に接続していたのに対し、図7では次行の第1の走査線718に接続することができる。これは、電位供給線122に限らず、初期化期間においてトランジスタ111の第1の電極に所定の電位を供給できれば良いからである。そのため、初期化期間において所定の電位をトランジスタ111の第1の電極に供給できれば供給する配線はたえず一定の電位である必要はない。よって、電位供給線のかわりに次行の第1の走査線718を用いることができる。このように、次行と配線を共有することで配線数を減らすことが可能となり、開口率を向上させることができる。

#### 【0102】

なお、図7に示した画素構成においても、実施の形態1と同様の動作をさせることにより、トランジスタ111のしきい値電圧のばらつきに起因した電流値のばらつきを抑制することができる。よって、輝度データに対応した電流を発光素子116に供給することができ、輝度のばらつきを抑制することが可能となる。また、対向電極の電位を一定として動作させるため消費電力を低くすることが可能である。なお、トランジスタ111の動作領域は特に限定されないが、飽和領域の場合の方が効果は顕著にあらわれる。さらに、トランジスタ111を飽和領域で動作させた場合には、発光素子116の劣化に起因したトランジスタ111に流れる電流のばらつきを抑制することができる。

#### 【0103】

ただし、第1の走査線718において第1のスイッチ112をオフさせる信号はV1-Vth-（：任意の正の数）の電位となる。そのため、V1-Vth-（：任意の正の数）の電位でオフとなる第1のスイッチ112を使用する必要がある。また、画素700が属する行の初期化期間は配線を共有した行のデータ書き込み期間と重ならないように動作させる必要がある。

#### 【0104】

なお、第3のスイッチ114にNチャネル型トランジスタを用いた場合、第3の走査線120において第3のスイッチ114をオフさせる電位は、第1の走査線718において

第1のスイッチ112をオフさせる信号であるV1-Vth- の電位より下げてもよく、この場合トランジスタがオフとなる際のゲート・ソース間電圧を負の値とすることが可能となる。よって、第3のスイッチ114がオフした際の電流漏れを少なくすることができる。

#### 【0105】

また、図8の画素800に示すように図1の電位供給線122を次行の第2の走査線819と共有しても良い。画素800においても、実施の形態1と同様の動作をさせることができる。ただし、第2の走査線819において第2のスイッチ113をオフさせる信号はV1-Vth- ( : 任意の正の数 ) の電位となる。そのため、V1-Vth- ( : 任意の正の数 ) の電位でオフとなる第2のスイッチ113を使用する必要がある。また、画素800が属する行の初期化期間は配線を共有した行のしきい値書き込み期間と重ならないように動作させる必要がある。10

#### 【0106】

なお、第3のスイッチ114にNチャネル型トランジスタを用いた場合、第3の走査線120において第3のスイッチ114をオフさせる信号は、第2の走査線819において第2のスイッチ113をオフさせる信号であるV1-Vth- の電位より下げてもよく、この場合第3のスイッチ114がオフした際の電流漏れを少なくすることができる。

#### 【0107】

また、図9の画素900に示すように図1の電位供給線122を前行の第3の走査線920と共有しても良い。画素900においても、実施の形態1と同様の動作をさせることができる。ただし、第3の走査線920において第3のスイッチ114をオフさせる信号はV1-Vth- ( : 任意の正の数 ) の電位となる。そのため、V1-Vth- ( : 任意の正の数 ) の電位でオフとなる第3のスイッチ114を使用する必要がある。また、画素900が属する行の初期化期間は配線を共有した行の初期化期間と重ならないように動作させる必要があるが、初期化期間がデータ書き込み期間より短く設定されている場合には特に問題はない。20

#### 【0108】

なお、本実施形態では図1の電位供給線122が次行もしくは前行の走査線と共有する場合について示したが、初期化期間にV1-Vth- ( : 任意の正の数 ) の電位を供給することが可能な配線であればそれ以外でも良い。30

#### 【0109】

さらに、本実施形態で示した画素を図6の表示装置に適用することができる。なお、表示装置において、図7乃至図9に記載した画素ごとの動作の制約及び各行におけるデータ書き込み期間が重複しない範囲内で、各行自由に初期化開始時期を設定することができる。また、各画素は自身のアドレス期間を除き発光することができるため、1フレーム期間における発光期間の割合(即ち、デューティー比)を非常に大きくでき、おおむね100%にすることも可能となる。よって、輝度のばらつきが少なくデューティー比が高い表示装置を得ることができる。

#### 【0110】

また、しきい値書き込み期間を長く設定することも可能であるため、発光素子に流れる電流値を制御するトランジスタのしきい値電圧をより正確に容量素子に書き込むことができる。よって、表示装置としての信頼性が向上する。40

#### 【0111】

また、本実施の形態は、上述した図1以外の実施の形態1及び2に示した画素構成とも自由に組み合わせることができる。

#### 【0112】

##### (実施の形態4)

本実施形態では、実施の形態1とは異なる構成の画素について図10に示す。なお、実施の形態1と同様のものに関しては共通の符号を用いて示し、同一部分又は同様な機能を有する部分の詳細な説明は省略する。50

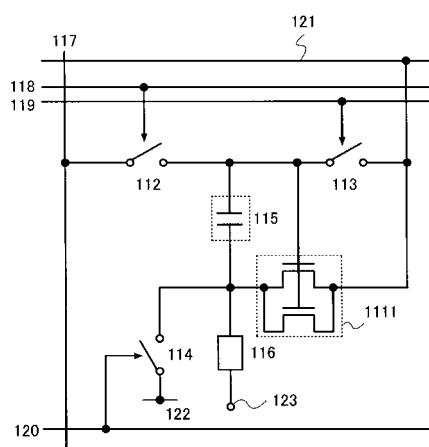

## 【0113】

図10に示す画素は、トランジスタ1011、第1のスイッチ112、第2のスイッチ113、第3のスイッチ114、容量素子115、発光素子116を有する。なお、画素は、信号線117、第1の走査線118、第2の走査線119、第3の走査線120、電源線121及び電位供給線122に接続されている。

## 【0114】

本実施形態におけるトランジスタ1011は、トランジスタを2つ直列に接続したマルチゲート型トランジスタであり、実施の形態1のトランジスタ111と同じ位置に設けられている。ただし、直列に接続されるトランジスタの数は特に限定されない。

## 【0115】

実施の形態1と同様に図10に示した画素を動作させることにより、トランジスタ1011のしきい値電圧のばらつきに起因した電流値のばらつきを抑制することができる。よって、輝度データに対応した電流を発光素子116に供給することができ、輝度のばらつきを抑制することが可能となる。また、対向電極の電位を一定として動作させるため消費電力を低くすることが可能である。なお、トランジスタ1011の動作領域は特に限定されないが、飽和領域の場合の方が効果は顕著にあらわれる。

10

## 【0116】

さらに、トランジスタ1011を飽和領域で動作させた場合には、発光素子116の劣化に起因したトランジスタ1011に流れる電流のばらつきを抑制することができる。

20

## 【0117】

本実施形態におけるトランジスタ1011のチャネル長Lは、直列に接続された2つのトランジスタのチャネル幅が等しい場合、各トランジスタのチャネル長の合計として作用する。よって、飽和領域においてドレイン・ソース間電圧Vdsにかかわらず、より一定に近い電流値を得られやすい。特に、トランジスタ1011は長いチャネル長Lを有するトランジスタの作製が困難な場合に有効である。なお、2つのトランジスタの接続部は抵抗として機能する。

## 【0118】

なお、トランジスタ1011は発光素子116に供給する電流値を制御する機能を有していれば良く、トランジスタの種類は特に限定されない。そのため、結晶性半導体膜を用いた薄膜トランジスタ(TFT)、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ、半導体基板やSOI基板を用いて形成されるトランジスタ、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタ、有機半導体やカーボンナノチューブを用いたトランジスタ、その他のトランジスタを適用することができる。

30

## 【0119】

また、図10に示した画素は、図1に示した画素と同様、第1のスイッチ112、第2のスイッチ113、第3のスイッチ114はトランジスタを用いることができる。

## 【0120】

さらに、図6の表示装置に本実施形態で示した画素を適用することができ、実施の形態1と同様、各行におけるデータ書き込み期間さえ重複しなければ、各行自由に初期化開始時期を設定することができる。また、各画素は自身のアドレス期間を除き発光することができるため、1フレーム期間における発光期間の割合(即ち、デューティー比)を非常に大きくでき、おおむね100%にすることも可能となる。よって、輝度のばらつきが少なくデューティー比が高い表示装置を得ることができる。

40

## 【0121】

また、しきい値書き込み期間を長く設定することも可能であるため、発光素子に流れる電流値を制御するトランジスタのしきい値電圧をより正確に容量素子に書き込むことができる。よって、表示装置としての信頼性が向上する。

## 【0122】

なお、トランジスタ1011は直列に接続されたトランジスタに限らず、図11のトランジ

50

ンジスタ 11111 に示すような並列にトランジスタが接続された構成であっても良い。トランジスタ 11111 により、より大きな電流を発光素子 116 に供給することができる。また、並列に接続した 2 つのトランジスタによってトランジスタの特性が平均化されるため、トランジスタ 11111 を構成するトランジスタ本来の特性ばらつきをより小さくすることができる。ばらつきが小さいと図 2 に示した動作によりトランジスタのしきい値電圧のばらつきに起因する電流値のばらつきをより抑制しやすくなることができる。

#### 【0123】

また、本実施の形態は、上述した図 1 に限らずその他の実施の形態に示した画素構成にも適用することが可能である。

#### 【0124】

##### (実施の形態 5)

本実施形態では、本発明の画素において、発光素子に供給する電流値を制御するトランジスタを期間毎に切り替えることにより、トランジスタの経時的な劣化を平均化する画素構成について図 12 を用いて説明する。

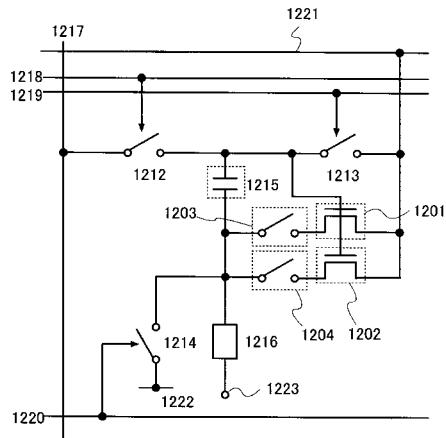

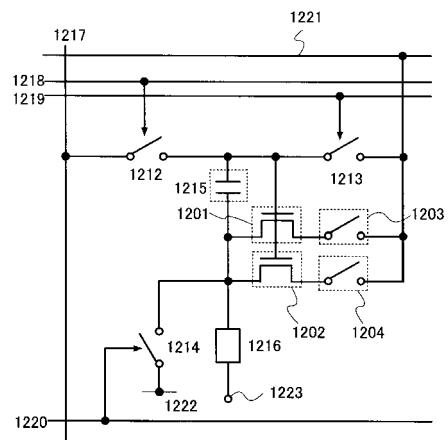

#### 【0125】

図 12 に示す画素は、第 1 のトランジスタ 1201、第 2 のトランジスタ 1202、第 1 のスイッチ 1212、第 2 のスイッチ 1213、第 3 のスイッチ 1214、第 4 のスイッチ 1203、第 5 のスイッチ 1204、容量素子 1215、発光素子 1216 を有する。なお、画素は、信号線 1217、第 1 の走査線 1218、第 2 の走査線 1219、第 3 の走査線 1220、電源線 1221 及び電位供給線 1222 に接続されている。さらに、図 12 には図示していないが、第 4 のスイッチ 1203 及び第 5 のスイッチ 1204 のオン、オフを制御する第 4 及び第 5 の走査線にも接続されている。本実施形態において、第 1 のトランジスタ 1201 及び第 2 のトランジスタ 1202 は N チャネル型トランジスタとし、それぞれのトランジスタはゲート・ソース間電圧 ( $V_{g s}$ ) がしきい値電圧を上回ったとき、導通状態になるものとする。また、発光素子 1216 の画素電極は陽極、対向電極 1223 は陰極とする。なお、トランジスタのゲート・ソース間電圧は  $V_{g s}$ 、容量素子に蓄積された電圧は  $V_{c s}$  と記す。また、第 1 のトランジスタ 1201 のしきい値電圧を  $V_{t h 1}$ 、第 2 のトランジスタ 1202 のしきい値電圧を  $V_{t h 2}$  と記す。電源線 1221、電位供給線 1222、信号線 1217 を、それぞれ第 1 の配線、第 2 の配線、第 3 の配線とも呼ぶ。

#### 【0126】

第 1 のトランジスタ 1201 は、第 1 の電極が第 4 のスイッチ 1203 を介して発光素子 1216 の画素電極に接続され、第 2 の電極が電源線 1221 に接続され、ゲート電極が第 2 のスイッチ 1213 を介して電源線 1221 と接続されている。また、第 1 のトランジスタ 1201 は、ゲート電極が第 1 のスイッチ 1212 を介して信号線 1217 とも接続されており、第 1 の電極が第 4 のスイッチ 1203 及び第 3 のスイッチ 1214 を介して電位供給線 1222 とも接続されている。

#### 【0127】

第 2 のトランジスタ 1202 は、第 1 の電極が第 5 のスイッチ 1204 を介して発光素子 1216 の画素電極に接続され、第 2 の電極が電源線 1221 に接続され、ゲート電極が第 2 のスイッチ 1213 を介して電源線 1221 と接続されている。また、第 2 のトランジスタ 1202 はゲート電極が第 1 のスイッチ 1212 を介して信号線 1217 とも接続されており、第 1 の電極が第 5 のスイッチ 1204 及び第 3 のスイッチ 1214 を介して電位供給線 1222 とも接続されている。なお、第 1 のトランジスタ 1201 と第 2 のトランジスタ 1202 のゲート電極、及び第 1 のトランジスタ 1201 と第 2 のトランジスタ 1202 の第 2 の電極はそれぞれ接続されており、第 1 のトランジスタ 1201 と第 2 のトランジスタ 1202 の第 1 の電極においても第 4 のスイッチ 1203 及び第 5 のスイッチ 1204 を介して接続されている。

#### 【0128】

さらに、接続された第 1 のトランジスタ 1201 と第 2 のトランジスタ 1202 のゲー

10

20

30

40

50

ト電極は、容量素子 1215 及び第4のスイッチ 1203 を介して第1のトランジスタ 1201 の第1の電極に接続され、さらに容量素子 1215 及び第5のスイッチ 1204 を介して第2のトランジスタ 1202 の第1の電極と接続されている。つまり、容量素子 1215 の第1の電極が第1のトランジスタ 1201 及び第2のトランジスタ 1202 のゲート電極に、第2の電極が各々のスイッチを介して第1のトランジスタ 1201 及び第2のトランジスタ 1202 の第1の電極に接続されている。なお、容量素子 1215 は、配線、半導体層や電極によって絶縁膜を挟むことで形成しても良いし、第1のトランジスタ 1201 及び第2のトランジスタ 1202 のゲート容量を用いて省略することもできる。

#### 【0129】

なお、第1の走査線 1218、第2の走査線 1219、第3の走査線 1220 に信号を入力することにより、それぞれ第1のスイッチ 1212、第2のスイッチ 1213、第3のスイッチ 1214 のオンオフが制御される。図 12においては、第4のスイッチ 1203 及び第5のスイッチ 1204 のオン、オフを制御する走査線は省略している。

#### 【0130】

信号線 1217 には、ビデオ信号に相当する画素の階調に従った信号、即ち輝度データに応じた電位が入力される。

#### 【0131】

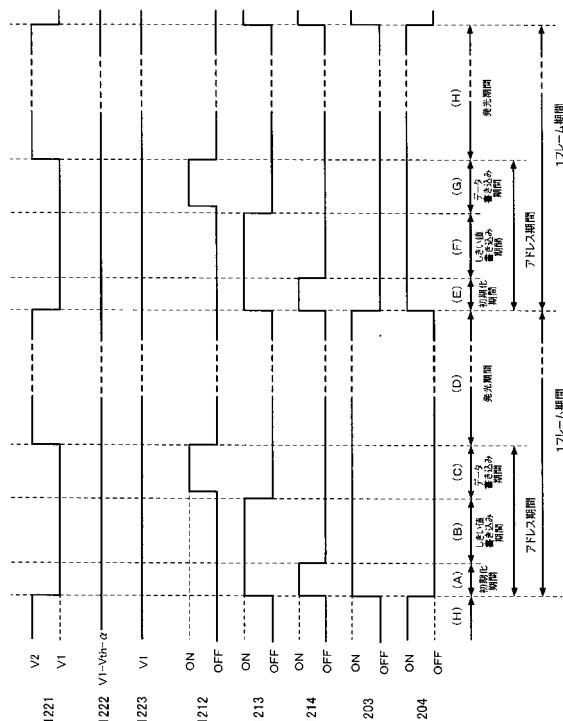

次に、図 12 で示した画素の動作について図 13 のタイミングチャートを用いて説明する。なお、図 13において1画面分の画像を表示する期間に相当する1フレーム期間は、初期化期間、しきい値書き込み期間、データ書き込み期間及び発光期間に分割される。

#### 【0132】

なお、発光素子 1216 の対向電極 1223 には  $V_1$  の電位が供給され、 $V_{th1}$  と  $V_{th2}$  の大きい方の値を  $V_{th}$  とした時、電位供給線 1222 には  $V_1 - V_{th} -$  ( $: \text{任意の正の数}$ ) の電位が供給される。また、電源線 1221 には、アドレス期間は  $V_1$ 、発光期間では  $V_2$  の電位が供給される。ただし、 $V_2 > V_1$  とする。

#### 【0133】

ここでは動作を説明するために、発光素子 1216 の対向電極 1223 の電位は、アドレス期間における電源線 1221 の電位と同じであるとしたが、発光素子 1216 が発光するために少なくとも必要とする電位差を  $V_{EL}$  とすると対向電極 1223 の電位は  $V_1 - V_{th} - V_{EL}$  の電位より高い値であれば良い。また、発光期間における電源線 1221 の電位  $V_2$  は、対向電極 1223 の電位と発光素子 1216 が発光するために少なくとも必要とする電位差 ( $V_{EL}$ ) とを加算した値より大きい値であれば良いが、説明上ここでは対向電極 1223 の電位を  $V_1$  としたため、 $V_2$  は  $V_1 + V_{EL}$  より大きい値であれば良いということになる。

#### 【0134】

まず、図 13 (A) に示すように初期化期間では、第1のスイッチ 1212 及び第5のスイッチ 1204 をオフとし、第2のスイッチ 1213、第3のスイッチ 1214 及び第4のスイッチ 1203 をオンとする。このとき、第1のトランジスタ 1201 の第1の電極はソース電極となり、その電位は  $V_1 - V_{th} -$  である。一方、ゲート電極の電位は  $V_1$  となる。よって、第1のトランジスタ 1201 のゲート・ソース間電圧  $V_{gs}$  は  $V_{th} +$  となり、第1のトランジスタ 1201 は導通状態となる。そして、第1のトランジスタ 1201 のゲート電極と第1の電極との間に配置された容量素子 1215 に  $V_{th} +$  が保持される。

#### 【0135】

次に、図 13 (B) に示すしきい値書き込み期間では、第3のスイッチ 1214 をオフとする。そのため、第1のトランジスタ 1201 の第1の電極即ちソース電極の電位は次第に上昇し  $V_1 - V_{th} 1$  となったところで、第1のトランジスタ 1201 は非導通状態となる。よって、容量素子 1215 に保持される電圧は  $V_{th} 1$  となる。

#### 【0136】

その後、図 13 (C) に示すデータ書き込み期間においては、第2のスイッチ 1213

10

20

30

40

50

をオフとした後、第1のスイッチ1212をオンとし、信号線1217より輝度データに応じた電位( $V_1 + V_{data}$ )を入力する。このときに、容量素子1215に保持される電圧 $V_{cs}$ は $V_{th1} + V_{data}$ となり、第1のトランジスタ1201は導通状態になる。なお、 $V_{data} = 0$ の電位を入力した場合には、非導通状態となり非発光とすることができる。

#### 【0137】

次に、図13(D)に示す発光期間では、第1のスイッチ1212をオフとし、電源線1221の電位を $V_2$ とする。このとき、第1のトランジスタ1201のゲート・ソース間電圧は $V_{gs} = V_{th1} + V_{data}$ であり、これに応じた電流が第1のトランジスタ1201及び発光素子1216に流れ、発光素子1216が発光する。

10

#### 【0138】

このような動作により、発光素子1216に流れる電流は、第1のトランジスタ1201の動作領域が飽和領域、線形領域のいずれの場合においても、第1のトランジスタ1201のしきい値電圧( $V_{th1}$ )に依存しない。

#### 【0139】

さらに、図13(E)に示す次の1フレーム期間における初期化期間では、第4のスイッチ1203をオフとし、第2のスイッチ1213、第3のスイッチ1214及び第5のスイッチ1204をオンとする。このとき、第2のトランジスタ1202の第1の電極はソース電極となり、その電位は $V_1 - V_{th-}$ である。一方、ゲート電極の電位は $V_1$ となる。よって、第2のトランジスタ1202のゲート・ソース間電圧 $V_{gs}$ は $V_{th+}$ となり、第2のトランジスタ1202は導通状態となる。そして、第2のトランジスタ1202のゲート電極と第1の電極との間に配置された容量素子1215に $V_{th+}$ が保持される。

20

#### 【0140】

次に、図13(F)に示すしきい値書き込み期間では、第3のスイッチ1214をオフとする。そのため、第2のトランジスタ1202の第1の電極即ちソース電極の電位は次第に上昇し $V_1 - V_{th2}$ となったところで、第2のトランジスタ1202は非導通状態となる。よって、容量素子1215に保持される電圧は $V_{th2}$ となる。

#### 【0141】

その後、図13(G)に示すデータ書き込み期間においては、第2のスイッチ1213をオフとした後、第1のスイッチ1212をオンとし、信号線1217より輝度データに応じた電位( $V_1 + V_{data}$ )を入力する。このときに、容量素子1215に保持される電圧 $V_{cs}$ は $V_{th2} + V_{data}$ となり、第2のトランジスタ1202は導通状態になる。

30

#### 【0142】

次に、図13(H)に示す発光期間では、第1のスイッチ1212をオフとし、電源線1221の電位を $V_2$ とする。このとき、第2のトランジスタ1202のゲート・ソース間電圧は $V_{gs} = V_{th2} + V_{data}$ であり、これに応じた電流が第2のトランジスタ1202及び発光素子1216に流れ、発光素子1216が発光する。

40

#### 【0143】

また、第2のトランジスタ1202の動作領域が飽和領域、線形領域のいずれの場合においても、発光素子1216に流れる電流はしきい値電圧( $V_{th2}$ )に依存しない。

#### 【0144】

よって、第1のトランジスタ1201、第2のトランジスタ1202のいずれのトランジスタを用いて発光素子に供給する電流を制御してもトランジスタのしきい値電圧のばらつきに起因した電流値のばらつきを抑制し、輝度データに対応した電流値を発光素子1216に供給することができる。なお、第1のトランジスタ1201、第2のトランジスタ1202を切り替えて用いることにより一つのトランジスタに加わる負荷を軽くすることによりトランジスタの経時的なしきい値の変化を小さいものとすることができます。

#### 【0145】

50

以上のことから、第1のトランジスタ1201、第2のトランジスタ1202のしきい値電圧に起因した輝度のばらつきを抑制することができる。また、対向電極の電位を一定とするため消費電力を低くすることが可能である。

#### 【0146】

さらに、第1のトランジスタ1201、第2のトランジスタ1202を飽和領域で動作させた場合においては、発光素子1216の劣化による各々のトランジスタに流れる電流のばらつきも抑制できる。

#### 【0147】

なお、第1のトランジスタ1201、第2のトランジスタ1202を飽和領域で動作させた場合、これらトランジスタのチャネル長Lは長い方がより好ましい。

10

#### 【0148】

また、初期化期間において発光素子1216に逆方向のバイアス電圧を印加しているため、発光素子における短絡箇所を絶縁化したり、発光素子の劣化を抑制することができる。よって、発光素子の寿命を延ばすことができる。

#### 【0149】

なお、トランジスタのしきい値電圧のばらつきに起因する電流値のばらつきを抑制することができるため、そのトランジスタによって制御された電流の供給先は特に限定されない。そのため、図12に示した発光素子1216は、EL素子（有機EL素子、無機EL素子又は有機物及び無機物を含むEL素子）、電子放出素子、液晶素子、電子インクなどを適用することができる。

20

#### 【0150】

また、第1のトランジスタ1201、第2のトランジスタ1202は発光素子1216に供給する電流値を制御する機能を有していれば良く、トランジスタの種類は特に限定されない。そのため、結晶性半導体膜を用いた薄膜トランジスタ（TFT）、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ、半導体基板やSOI基板を用いて形成されるトランジスタ、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタ、有機半導体やカーボンナノチューブを用いたトランジスタ、その他のトランジスタを適用することができる。

#### 【0151】

第1のスイッチ1212は画素の階調に従った信号を容量素子に入力するタイミングを選択するものであり、第2のスイッチ1213は第1のトランジスタ1201もしくは第2のトランジスタ1202のゲート電極に所定の電位を与えるタイミングを選択するものであり、第3のスイッチ1214は容量素子1215に書き込まれた電位を初期化するための所定の電位を与えるタイミングを選択するものである。そのため、第1のスイッチ1212、第2のスイッチ1213、第3のスイッチ1214は、上記機能を有していれば特に限定されない。たとえば、トランジスタやダイオードでもよいし、それらを組み合わせた論理回路でもよい。なお、第1乃至第3のスイッチは、上記のタイミングで信号もしくは電位を画素に与えることができれば特に必要はない。また、第4のスイッチ1203及び第5のスイッチ1204についても特に限定されず、たとえば、トランジスタやダイオードでもよいし、それらを組み合わせた論理回路でもよい。

30

#### 【0152】

第1のスイッチ1212、第2のスイッチ1213、第3のスイッチ1214、第4のスイッチ1203、第5のスイッチ1204にNチャネル型のトランジスタを用いた場合、Nチャネル型のトランジスタのみで画素を構成することができるため、製造工程の簡略化を図ることができる。また、画素を構成するトランジスタの半導体層にアモルファス半導体やセミアモルファス半導体（若しくは微結晶半導体ともいう）などの非晶質半導体を用いることができる。例えば、アモルファス半導体としてアモルファスシリコン（a-Si:H）が挙げられる。これら非晶質半導体を用いることにより、さらに製造工程の簡略化が可能である。したがって、製造コストの削減や歩留まりの向上を図ることができる。

40

#### 【0153】

50

なお、第1のスイッチ1212、第2のスイッチ1213、第3のスイッチ1214、第4のスイッチ1203、第5のスイッチ1204にトランジスタを用いた場合、トランジスタの極性（導電型）は特に限定されない。ただし、オフ電流が少ないトランジスタを用いることが望ましい。

#### 【0154】

また、第1のトランジスタ1201と第4のスイッチ1203及び第2のトランジスタ1202と第5のスイッチ1204は、図41に示すようにそれぞれ入れ替わっていても良い。つまり、第1のトランジスタ1201及び第2のトランジスタ1202の第1の電極は容量素子1215を介して第1のトランジスタ1201及び第2のトランジスタ1202のゲート電極に接続されている。また、第1のトランジスタ1201の第2の電極は第4のスイッチ1203を介し電源線1221と接続され、第2のトランジスタ1202の第2の電極は第5のスイッチ1204を介して電源線1221と接続されている。

10

#### 【0155】

また、図12及び図41ではトランジスタとスイッチをセットにして、つまり第1のトランジスタ1201と第4のスイッチ1203、第2のトランジスタ1202と第5のスイッチ1204をセットにして並列数が2の場合について記載したが、並列に配置する数は特に限定されない。

#### 【0156】

また、図6の表示装置に本実施形態で示した画素を適用することで、実施の形態1と同様、各行におけるデータ書き込み期間さえ重複しなければ、各行自由に初期化開始時期を設定することができる。また、各画素は自身のアドレス期間を除き発光することができるため、1フレーム期間における発光期間の割合（即ち、デューティー比）を非常に大きくでき、おおむね100%にすることも可能となる。よって、輝度のばらつきが少なくデューティー比が高い表示装置を得ることができる。

20

#### 【0157】

また、しきい値書き込み期間を長く設定することも可能であるため、発光素子に流れる電流値を制御するトランジスタのしきい値電圧をより正確に容量素子に書き込むことができる。よって、表示装置としての信頼性が向上する。

#### 【0158】

なお、実施の形態3と同様、電位供給線1222は他の行の配線と共有することができる。また、実施の形態4と同様、第1のトランジスタ1201及び第2のトランジスタ1202のそれぞれに、トランジスタが直列に接続されたマルチゲート型トランジスタや並列に配置されたトランジスタを用いても良い。これらに限らず、本実施の形態は、実施の形態1乃至4に示した画素構成にも適用することができる。

30

#### 【0159】

##### （実施の形態6）

本実施形態では、実施の形態1とは異なる構成の画素を示す。実施の形態1と同様のものに関しては共通の符号を用いて示し、同一部分又は同様な機能を有する部分の詳細な説明は省略する。なお、これらは実施の形態1と同様に動作させるものとする。

#### 【0160】

本実施形態では、発光素子116に強制的に電流が流れないようにする画素構成について説明する。つまり、非発光状態を強制的に作ることにより、残像が見えにくく、動画特性に優れた表示装置を得ることを目的とする。

40

#### 【0161】

このような画素構成の一つを図29に示す。図29に示す画素は、図1の画素が有するトランジスタ111、第1のスイッチ112、第2のスイッチ113、第3のスイッチ114、容量素子115、発光素子116の他に、第4のスイッチ2901を有する。また、画素は、信号線117、第1の走査線118、第2の走査線119、第3の走査線120、電源線121及び電位供給線122の他、第4の走査線2902にも接続されている。

50

**【 0 1 6 2 】**

図29において、第4のスイッチ2901は、容量素子115と並列に接続されている。そのため、第4のスイッチ2901がオンになるとトランジスタ111のゲート電極と第1の電極間が短絡する。すると、容量素子115に保持されていたトランジスタ111のゲートソース間電圧を0Vにすることができるため、トランジスタ111がオフとなり、発光素子116を非発光とすることができます。なお、第4のスイッチ2901におけるオンオフの制御は、第4の走査線2902に入力される信号によって画素一行ずつ走査する。

**【 0 1 6 3 】**

このような動作により、画素に書き込まれた信号を消去する。よって、次の初期化期間までは強制的に非発光の状態となる消去期間が設けられる。つまり、黒表示が挿入されることになる。よって、残像が見えにくくなり、動画特性の向上を図ることができる。

10

**【 0 1 6 4 】**

ところで、表示装置の階調を表現する駆動方式には、アナログ階調方式とデジタル階調方式がある。アナログ階調方式には、発光素子の発光強度をアナログ制御する方式と発光素子の発光時間をアナログ制御する方式がある。アナログ階調方式においては発光素子の発光強度をアナログ制御する方がよく用いられている。一方、デジタル階調方式はデジタル制御で発光素子をオンオフさせ、階調を表現している。デジタル階調方式の場合、デジタル信号で処理できるためノイズに強いというメリットがあるが、発光・非発光の2状態しかないので、このままでは2階調しか表現できない。そこで、別の手法を組み合わせて、多階調化を図ることが行われている。多階調化のための手法としては、画素の発光面積に重みをつけてその選択により階調表示を行う面積階調方式と、発光時間に重みをつけてその選択により階調表示を行う時間階調方式がある。

20

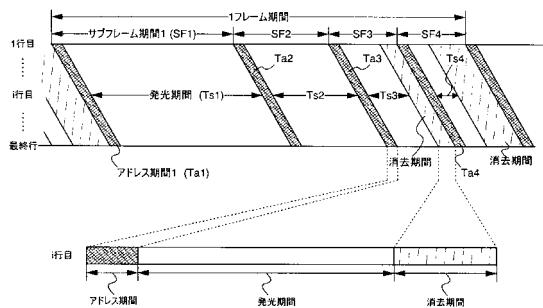

**【 0 1 6 5 】**

このデジタル階調方式と時間階調方式とを組み合わせた場合、図42に示すように、1フレーム期間を複数のサブフレーム期間(SFn)に分割する。各サブフレーム期間は、初期化期間、しきい値書き込み期間及びデータ書き込み期間を有するアドレス期間(Ta)と、発光期間(Ts)とを有する。なお、サブフレーム期間は表示ビット数nに応じた数を1フレーム期間に設ける。また、各サブフレーム期間における発光期間の長さの比を $2^{(n-1)} : 2^{(n-2)} : \dots : 2 : 1$ とし、各発光期間で発光素子の発光、もしくは非発光を選択し、発光素子が発光している1フレーム期間中の合計時間の差を利用して階調表現を行う。1フレーム期間において、発光している合計時間が長ければ輝度が高く、短ければ輝度が低くなる。なお、図42においては4ビット階調の例を示しており、1フレーム期間は4つのサブフレーム期間に分割され、発光期間の組み合わせによって、 $2^4 = 16$ 階調を表現できる。なお、発光期間の長さの比は、特に2のべき乗の比としなくとも、階調表現は可能である。また、あるサブフレーム期間をさらに分割していくても良い。

30

**【 0 1 6 6 】**

なお、上記のように時間階調方式を用いて多階調化を図る場合、下位ビットの発光期間の長さは短いため、発光期間の終了後直ちに次のサブフレーム期間のデータ書き込み動作を開始しようとすると、前のサブフレーム期間のデータ書き込み動作と重複してしまい、正常な動作ができなくなる。そのため、サブフレーム期間内に上記のような消去期間を設けることで、全行に要するデータ書き込み期間より短い発光も表現することができる。即ち、発光期間を自由に設定することができる。

40

**【 0 1 6 7 】**

本発明は、アナログ階調において特に有効であることはもちろん、デジタル階調方式と時間階調方式とを組み合わせた方式においても、発光期間を自由に設定することができるので、消去期間を設けることは有効である。

**【 0 1 6 8 】**

また、電源線121からトランジスタ111を介して発光素子116の画素電極までの

50

間の電流の経路に新たにスイッチを設け、一行ずつ画素を走査してそのスイッチをオフにより消去期間を設けても良い。

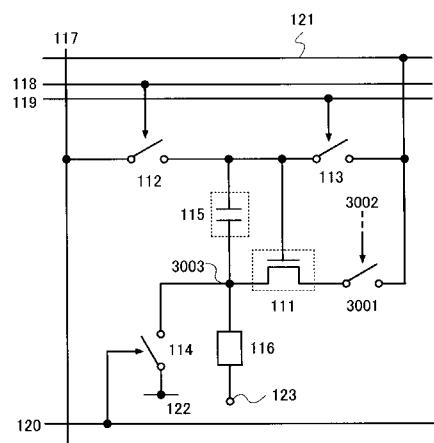

#### 【0169】

このような構成の一つを図30に示す。図30の構成は、図1の画素構成に加え、第4のスイッチ3001がトランジスタ111の第2の電極と電源線121との間に接続されている。そして、第4のスイッチ3001のオンオフは、第4の走査線3002に入力される信号によって制御される。

#### 【0170】

また、トランジスタ111の第1の電極と発光素子116の画素電極との接続点をノード3003とすると、図37に示すように第4のスイッチ3701をノード3003とトランジスタ111の第1の電極との間に接続しても良い。第4のスイッチ3701のオンオフは第4の走査線3702に入力される信号によって制御される。

10

#### 【0171】

よって、第4のスイッチをオフにより消去期間を設けることが可能である。また、実施の形態1と同様に図30及び図37に示す画素を動作させる際に、初期化期間において第4のスイッチをオフすることにより消費電力を低減することも可能である。

#### 【0172】

なお、図30および図37に限らず、図43に示すようにノード3003と発光素子116の画素電極との間に第4のスイッチ4301を接続しても消去期間を設けることは可能である。また、図44に示すように、トランジスタ111の第2の電極と第2のスイッチ113との接続点と、電源線121との間に第4のスイッチ4401を接続しても消去期間を設けることは可能である。

20

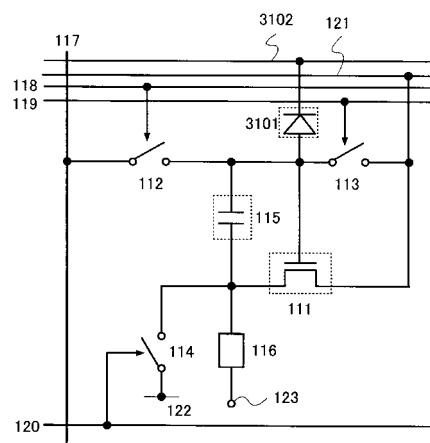

#### 【0173】

また、トランジスタ111のゲート電極に電位を入力することで強制的に消去期間を設けても良い。

#### 【0174】

このような構成の一つを図31に示す。図31の構成は、図1の画素構成に加え整流素子3101を有し、その整流素子3101を介してトランジスタ111のゲート電極と第4の走査線3102とが接続されている。なお、トランジスタ111がNチャネル型トランジスタであるとすると、整流素子3101はトランジスタ111のゲート電極から第4の走査線3102に電流が流れるように接続されている。第4の走査線3102はトランジスタ111を強制的にオフにするときのみLレベルの信号が入力され、それ以外はHレベルの信号を入力する。すると、第4の走査線がHレベルのときには、整流素子3101には電流が流れず、Lレベルになるとトランジスタ111から第4の走査線3102へ電流が流れる。このように第4の走査線3102へ電流を流すことにより、容量素子115に保持される電圧をトランジスタ111のしきい値電圧(Vth)以下にし、トランジスタ111を強制的にオフにする。なお、Lレベルの電位は、トランジスタ111のゲート電極の電位がLレベルの電位より整流素子3101の順方向しきい値電圧分高い電位以下にならないことを考慮し、決定しなければならない。また、このLレベルの電位で第1のスイッチ112及び第2のスイッチ113がオフするものを各々のスイッチに用いている場合には、第4の走査線3102を第1の走査線118もしくは第2の走査線119で代用しても良い。

30

#### 【0175】

なお、画素構成は強制的に非発光にする手段を有していれば黒表示が挿入されることにより残像が見えにくくすることができるため、上記の構成に特に限定されない。

#### 【0176】

なお、整流素子3101には、図39(B)に示したショットキー・バリア型、PIN型、PN型のダイオードの他、ダイオード接続されているトランジスタ等を用いることができる。

40

#### 【0177】

50

なお、本実施形態に示した消去期間を設けるためのスイッチは、上述した図1に限らずその他の実施の形態に示した画素構成にも適用することが可能である。

#### 【0178】

また、このようなスイッチを設けなくても初期化期間を長く設定することで、初期化期間は消去期間を兼ねることができる。よって、実施の形態1乃至5に記載した画素を動作する際、残像が見えにくくするために黒表示させたい期間を初期化期間の長さと設定することで、動画特性の向上を図ることができる。また、発光期間において電源線121の電位を対向電極123の電位と同一にすることにより黒表示を挿入しても良い。

#### 【0179】

なお、図30に示した画素構成においては、データ書き込み期間にトランジスタ111が導通状態となった場合、第4のスイッチ3001をオフにすることによりトランジスタ111への電流を遮断することができる。よって、トランジスタ111のソース電極と接続されている容量素子115の第2の電極の電位の変動を抑制することができるため、より正確に容量素子115にVth+Vdataの電圧を保持させることができるとなる。したがって、輝度データに応じたより正確な電流を発光素子116に供給することができる。

#### 【0180】

また、図37に示した画素構成においても、データ書き込み期間に第4のスイッチ3701をオフとすることにより容量素子115の第2の電極の電位の変動を抑制することができるため、より正確に容量素子115にVth+Vdataの電圧を保持させることができるとなる。よって、輝度データに応じたより正確な電流を発光素子116に供給することができる。

#### 【0181】

なお、本実施形態で示した画素は、実施の形態1において示した表示装置に適用することができる。以上のことから、輝度のばらつきが少なく、かつ動画特性に優れた表示装置を得ることができる。

#### 【0182】

##### (実施の形態7)

本実施形態では、発光素子に供給する電流値を制御するトランジスタにPチャネル型トランジスタを適用した場合について図14を用いて説明する。

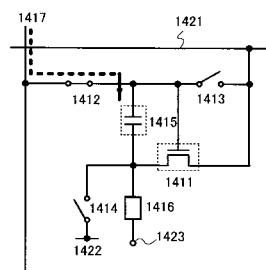

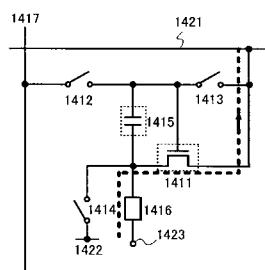

#### 【0183】

図14に示す画素は、トランジスタ1411、第1のスイッチ1412、第2のスイッチ1413、第3のスイッチ1414、容量素子1415、発光素子1416を有する。なお、画素は、信号線1417、第1の走査線1418、第2の走査線1419、第3の走査線1420、電源線1421及び電位供給線1422に接続されている。本実施の形態において、トランジスタ1411はPチャネル型トランジスタとし、そのゲート・ソース間電圧の絶対値(|Vgs|)がしきい値電圧(|Vth|)を上回ったとき(VgsがVthを下回ったとき)、導通状態になるものとする。また、発光素子1416の画素電極は陰極、対向電極1423は陽極とする。なお、トランジスタのゲート・ソース間電圧の絶対値を|Vgs|、しきい値の絶対値を|Vth|と記し、電源線1421及び電位供給線1422、信号線1417を、それぞれ第1の配線、第2の配線、第3の配線とも呼ぶ。

#### 【0184】

トランジスタ1411の第1の電極(ソース電極及びドレイン電極の一方)は、発光素子1416の画素電極に接続され、第2の電極(ソース電極及びドレイン電極の他方)は電源線1421に接続され、ゲート電極は第2のスイッチ1413を介して電源線1421と接続されている。また、トランジスタ1411のゲート電極は、第1のスイッチ1412を介して信号線1417とも接続されており、第1の電極は第3のスイッチ1414を介して電位供給線1422とも接続されている。

#### 【0185】

10

20

30

40

50

さらに、トランジスタ 1411 のゲート電極と第 1 の電極との間に容量素子 1415 が接続されている。つまり、容量素子 1415 の第 1 の電極がトランジスタ 1411 のゲート電極に、第 2 の電極がトランジスタ 1411 の第 1 の電極に接続されている。なお、容量素子 1415 は、配線、半導体層や電極によって絶縁膜を挟むことで形成しても良いし、トランジスタ 1411 のゲート容量を用いて省略することもできる。

#### 【0186】

なお、第 1 の走査線 1418、第 2 の走査線 1419、第 3 の走査線 1420 に信号を入力することにより、それぞれ第 1 のスイッチ 1412、第 2 のスイッチ 1413、第 3 のスイッチ 1414 のオンオフが制御される。

#### 【0187】

信号線 1417 には、ビデオ信号に相当する画素の階調に従った信号、即ち輝度データに応じた電位が入力される。

#### 【0188】

次に、図 14 で示した画素の動作について図 15 のタイミングチャート及び図 16 を用いて説明する。なお、図 14 において 1 画面分の画像を表示する期間に相当する 1 フレーム期間は、初期化期間、しきい値書き込み期間、データ書き込み期間及び発光期間に分割される。また、初期化期間、しきい値書き込み期間、データ書き込み期間をまとめてアドレス期間と呼ぶ。1 フレーム期間は特に限定はないが、画像を見る人がちらつき（フリッカ）を感じないように少なくとも 1 / 60 秒以下とすることが好ましい。

#### 【0189】

なお、発光素子 1416 の対向電極 1423 には  $V_1$  の電位が、電位供給線 1422 には  $V_1 + | V_{th} | +$  ( $\cdot$  : 任意の正の数) の電位が入力される。また、電源線 1421 には、アドレス期間は  $V_1$ 、発光期間では  $V_2$  の電位が入力される。ただし、 $V_2 < V_1$  とする。

#### 【0190】

ここでは動作を説明するために、発光素子 1416 の対向電極 1423 の電位は、アドレス期間における電源線 1421 の電位と同じであるとしたが、発光素子 1416 が発光するために少なくとも必要とする電位差を  $V_{EL}$  とすると対向電極 1423 の電位は  $V_1$  以上かつ  $V_1 + | V_{th} | + V_{EL}$  の電位より低い値であれば良い。また、発光期間における電源線 1421 の電位  $V_2$  は、対向電極 1423 の電位から発光素子 1416 が発光するために少なくとも必要とする電位差 ( $V_{EL}$ ) を引いた値より小さい値であれば良いが、説明上ここでは対向電極 1423 の電位を  $V_1$  としたため、 $V_2$  は  $V_1 - V_{EL}$  より小さい値であれば良いということになる。

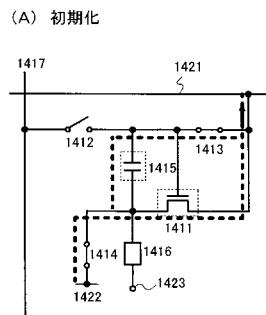

#### 【0191】

まず、図 15 (A) 及び図 16 (A) に示すように初期化期間では、第 1 のスイッチ 1412 をオフとし、第 2 のスイッチ 1413 及び第 3 のスイッチ 1414 をオンとする。このとき、トランジスタ 1411 の第 1 の電極はソース電極となり、その電位は電位供給線 1422 と等しくなるため  $V_1 + | V_{th} | +$  となる。一方、ゲート電極の電位は  $V_1$  となる。よって、トランジスタ 1411 のゲート・ソース間電圧の絶対値  $| V_{gs} |$  は  $| V_{th} | +$  となり、トランジスタ 1411 は導通状態となる。そして、トランジスタ 1411 のゲート電極と第 1 の電極との間に設けられた容量素子 1415 に  $| V_{th} | +$  が保持される。

#### 【0192】

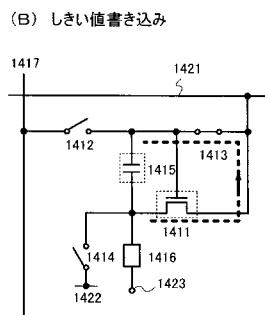

次に、図 15 (B) 及び図 16 (B) に示すしきい値書き込み期間では、第 3 のスイッチ 1414 をオフとする。そのため、トランジスタ 1411 の第 1 の電極即ちソース電極の電位は次第に下降し  $V_1 + | V_{th} |$  となったところで、トランジスタ 1411 は非導通状態となる。よって、容量素子 1415 に保持される電圧は  $| V_{th} |$  となる。

#### 【0193】

その後の図 15 (C) 及び図 16 (C) に示すデータ書き込み期間においては、第 2 のスイッチ 1413 をオフとした後、第 1 のスイッチ 1412 をオンとし、信号線 1417

10

20

30

40

50

より輝度データに応じた電位 ( $V_{1-Vdata}$ ) を入力する。このときに、容量素子 1415 に保持される電圧  $V_{cs}$  は、容量素子 1415 及び発光素子 1416 の静電容量をそれぞれ  $C_1$ 、 $C_2$  とすると式 (5) のように表すことができる。

【数 5】

$$V_{cs} = \left| -|V_{th}| - V_{data} \times \frac{C_2}{C_1+C_2} \right| \dots(5)$$

【0194】

ただし、発光素子 1416 は容量素子 1415 に比べ膜厚が薄いうえ電極面積が大きいため、 $C_2 > C_1$  となる。よって、 $C_2 / (C_1 + C_2) < 1$  より容量素子 1415 に保持される電圧  $V_{cs}$  は式 (6) となり、トランジスタ 1411 は導通状態になる。

10

【数 6】

$$V_{cs} = \left| -|V_{th}| - V_{data} \right| \dots(6)$$

【0195】

次に、図 15 (D) 及び図 16 (D) に示す発光期間では、第 1 のスイッチ 1412 をオフとし、電源線 1421 の電位を  $V_2$  とする。このとき、トランジスタ 1411 のゲート・ソース間電圧は  $V_{gs} = -V_{data} - |V_{th}|$  であり、これに応じた電流がトランジスタ 1411 及び発光素子 1416 に流れ、発光素子 1416 が発光する。

【0196】

なお、発光素子に流れる電流  $I$  は、トランジスタ 1411 を飽和領域で動作させた場合、式 (7) で表される。

20

【数 7】

$$\begin{aligned} I &= \frac{1}{2} \left( \frac{W}{L} \right) \mu C_{ox} (V_{gs} - V_{th})^2 \\ &= \frac{1}{2} \left( \frac{W}{L} \right) \mu C_{ox} (-V_{data} - |V_{th}| - V_{th})^2 \quad \dots(7) \end{aligned}$$

【0197】

トランジスタ 1411 は P チャネル型のトランジスタであるため、 $V_{th} < 0$  である。よって、式 (7) は式 (8) に変形できる。

30

【数 8】

$$I = \frac{1}{2} \left( \frac{W}{L} \right) \mu C_{ox} (-V_{data})^2 \quad \dots(8)$$

【0198】

また、トランジスタ 1411 を線形領域で動作させた場合、発光素子に流れる電流  $I$  は式 (9) で表される。

【数 9】

$$\begin{aligned} I &= \left( \frac{W}{L} \right) \mu C_{ox} [(V_{gs} - V_{th})V_{ds} - \frac{1}{2} V_{ds}^2] \\ &= \left( \frac{W}{L} \right) \mu C_{ox} [(-V_{data} - |V_{th}| - V_{th})V_{ds} - \frac{1}{2} V_{ds}^2] \quad \dots(9) \end{aligned}$$

40

【0199】

$V_{th} < 0$  より、式 (9) は式 (10) に変形できる。

【数 10】

$$I = \left( \frac{W}{L} \right) \mu C_{ox} [(-V_{data})V_{ds} - \frac{1}{2} V_{ds}^2] \quad \dots(10)$$

50

## 【0200】

ここで、Wはトランジスタ1411のチャネル幅、Lはチャネル長、μは移動度、Cxは蓄積容量を指す。

## 【0201】

式(8)及び式(10)より、トランジスタ1411の動作領域が飽和領域、線形領域のいずれの場合においても、発光素子1416に流れる電流は、トランジスタ1411のしきい値電圧( $V_{th}$ )に依存しない。よって、トランジスタ1411のしきい値電圧のばらつきに起因した電流値のばらつきを抑制し、輝度データに対応した電流値を発光素子1416に供給することができる。

## 【0202】

以上のことから、トランジスタ1411のしきい値電圧のばらつきに起因した輝度のばらつきを抑制することができる。また、対向電極の電位を一定とするため消費電力を低くすることが可能である。

10

## 【0203】

さらに、トランジスタ1411を飽和領域で動作させた場合においては、発光素子1416の劣化による輝度のばらつきも抑制できる。発光素子1416が劣化すると、発光素子1416の $V_{EL}$ は増大し、トランジスタ1411の第1の電極、即ちソース電極の電位は減少する。このとき、トランジスタ1411のソース電極は容量素子1415の第2の電極に、トランジスタ1411のゲート電極は容量素子1415の第1の電極に接続されており、なおかつゲート電極側は浮遊状態となっている。そのため、ソース電位の減少に伴い、同じ電位だけトランジスタ1411のゲート電位も減少する。よって、トランジスタ1411の $V_{gs}$ は変化しないため、たとえ発光素子が劣化してもトランジスタ1411及び発光素子1416に流れる電流に影響しない。なお、式(8)においても発光素子に流れる電流Iはソース電位やドレイン電位に依存しないことがわかる。

20

## 【0204】

よって、トランジスタ1411を飽和領域で動作させた場合においては、トランジスタ1411のしきい値電圧のばらつき及び発光素子1416の劣化に起因した輝度のばらつきを抑制することができる。

## 【0205】

なお、トランジスタ1411を飽和領域で動作させた場合、降伏現象やチャネル長変調による電流量の増加を抑制するために、トランジスタ1411のチャネル長Lは長い方がより好ましい。

30

## 【0206】

また、初期化期間において発光素子1416に逆方向のバイアス電圧を印加しているため、発光素子における短絡箇所を絶縁化したり、発光素子の劣化を抑制することができる。よって、発光素子の寿命を延ばすことができる。

## 【0207】

なお、図14に示した発光素子1416は、特に限定されず、EL素子(有機EL素子、無機EL素子又は有機物及び無機物を含むEL素子)、電子放出素子、液晶素子、電子インクなどを適用することができる。

40

## 【0208】

また、トランジスタ1411は発光素子1416に供給する電流値を制御する機能を有していれば良く、トランジスタの種類は特に限定されない。そのため、結晶性半導体膜を用いた薄膜トランジスタ(TFT)、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ、半導体基板やSOI基板を用いて形成されるトランジスタ、MOS型トランジスタ、接合型トランジスタ、バイポーラトランジスタ、有機半導体やカーボンナノチューブを用いたトランジスタ、その他のトランジスタを適用することができる。

## 【0209】

第1のスイッチ1412は画素の階調に従った信号を容量素子に入力するタイミングを

50

選択するものであり、第2のスイッチ1413はトランジスタ1411のゲート電極に所定の電位を与えるタイミングを選択するものであり、第3のスイッチ1414は容量素子1415に書き込まれた電位を初期化するための所定の電位を与えるタイミングを選択するものである。そのため、第1のスイッチ1412、第2のスイッチ1413、第3のスイッチ1414は、上記機能を有していれば特に限定されない。トランジスタやダイオードでもよいし、それらを組み合わせた論理回路でもよい。

#### 【0210】

なお、トランジスタを用いた場合、その極性（導電型）は特に限定されない。ただし、オフ電流が少ないトランジスタを用いることが望ましい。オフ電流が少ないトランジスタとしては、LDD領域を設けているものやマルチゲート構造にしているものなどがある。また、Nチャネル型とPチャネル型の両方を用いて、CMOS型のスイッチにしてもよい。

10

#### 【0211】

たとえば、第1のスイッチ1412、第2のスイッチ1413、第3のスイッチ1414にPチャネル型のトランジスタを適用した場合、それぞれのスイッチのオンオフを制御する走査線にはオンさせたいときにはLレベルの信号が、オフさせたいときにはHレベルの信号が入力される。

#### 【0212】

この場合、Pチャネル型のトランジスタのみで画素を構成することができるため、製造工程の簡略化を図ることができる。

20

#### 【0213】

さらに、図6の表示装置に本実施形態で示した画素を適用することでき、実施の形態1と同様、各行におけるデータ書き込み期間さえ重複しなければ、各行自由に初期化開始時期を設定することができる。また、各画素は自身のアドレス期間を除き発光することができるため、1フレーム期間における発光期間の割合（即ち、デューティー比）を非常に大きくでき、おおむね100%にすることもできる。よって、輝度のばらつきが少なくデューティー比が高い表示装置を得ることができる。

#### 【0214】

また、しきい値書き込み期間を長く設定することも可能であるため、発光素子に流れる電流値を制御するトランジスタのしきい値電圧をより正確に容量素子に書き込むことができる。よって、表示装置としての信頼性が向上する。

30

#### 【0215】

なお、実施の形態3と同様に、電位供給線1422は他の行の配線と共有することができる。また、トランジスタ1411を実施の形態4及び5で示したトランジスタの構成を適用することができる。その他、実施の形態6に示した構成及び動作を適用することも可能である。これらに限らず、本実施形態は、実施の形態1乃至6に示した画素構成にトランジスタ1411を適用することが可能である。

#### 【0216】

ただし、消去期間を設けるために整流素子を用いた場合、発光素子に流れる電流を制御するトランジスタの極性によって整流素子に流れる電流の向きを異ならせる必要がある。図32を用いて説明する。

40

#### 【0217】

トランジスタ1411がPチャネル型トランジスタである場合には、整流素子3201は第4の走査線3202からトランジスタ1411のゲート電極に電流が流れるように接続されている。第4の走査線3202はトランジスタ1411を強制的にオフにするときのみHレベルの信号が入力され、それ以外はLレベルの信号を入力する。すると、第4の走査線3202がLレベルのときには、整流素子3201には電流が流れず、Hレベルになるとトランジスタ1411から第4の走査線3202へ電流が流れ。このように第4の走査線3202へ電流を流すことにより、容量素子1415に保持される電位をトランジスタ1411のしきい値電圧の絶対値（|Vth|）以下にし、トランジスタ1411

50

を強制的にオフにする。なお、Hレベルの電位は、トランジスタ1411のゲート電極の電位がHレベルの電位より整流素子3201の順方向しきい値電圧分低い電位以上にならないことを考慮し、決定しなければならない。このような動作により、黒表示が挿入され残像が見えにくくなり、動画特性を向上させることができる。

#### 【0218】

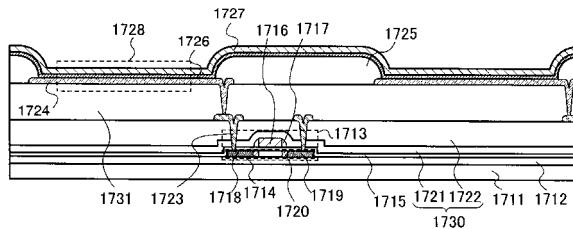

##### (実施の形態8)

本実施形態では、本発明の画素の部分断面図の一形態について図17を用いて説明する。なお、本実施形態における部分断面図に示されているトランジスタは、発光素子に供給する電流値を制御する機能を有するトランジスタである。

#### 【0219】

まず、絶縁表面を有する基板1711上に下地膜1712を形成する。絶縁表面を有する基板1711としては、ガラス基板、石英基板、プラスチック基板(ポリイミド、アクリル、ポリエチレンテレフタレート、ポリカーボネート、ポリアリレート、ポリエーテルスルホン等)、セラミックス基板等の絶縁性基板の他、金属基板(タンタル、タングステン、モリブデン等)や半導体基板等の表面に絶縁膜を形成したものも用いることができる。ただし、少なくともプロセス中に発生する熱に耐えうる基板を使用する必要がある。

#### 【0220】

下地膜1712としては、酸化珪素膜、窒化珪素膜または酸化窒化珪素膜( $\text{SiO}_x\text{N}_y$ )等の絶縁膜を用い、これら絶縁膜を単層又は2以上の複数層で形成する。なお、下地膜1712は、スパッタ法、CVD法等を用いて形成すればよい。本実施形態では下地膜1712を単層としているが、もちろん2以上の複数層でも構わない。

#### 【0221】

次に、下地膜1712上にトランジスタ1713を形成する。トランジスタ1713は、少なくとも半導体層1714と、半導体層1714上に形成されたゲート絶縁膜1715と、半導体層1714上にゲート絶縁膜1715を介して形成されたゲート電極1716から構成されており、半導体層1714は、ソース領域及びドレイン領域を有する。

#### 【0222】

半導体層1714は、アモルファスシリコン(a-Si:H)の他、シリコン、シリコン・ゲルマニウム(SiGe)等を主成分とする非晶質半導体、非晶質状態と結晶状態とが混在したセミアモルファス半導体、及び非晶質半導体中に0.5nm~20nmの結晶粒を観察することができる微結晶半導体から選ばれたいずれかの非結晶性状態を有する膜(即ち、非結晶性半導体膜)やポリシリコン(p-Si:H)等の結晶性半導体膜を用いることができる。なお、0.5nm~20nmの結晶粒を観察することができる微結晶状態はいわゆるマイクロクリスタルと呼ばれている。なお、半導体層1714に非結晶性半導体膜を用いる場合には、スパッタ法、CVD法等を用いて形成すれば良く、結晶性半導体膜を用いる場合には、例えば非結晶性半導体膜を形成した後さらに結晶化すれば良い。また、必要があればトランジスタのしきい値を制御するために上記主成分の他に、微量の不純物元素(リン、ヒ素、ボロン等)が含まれていても良い。

#### 【0223】

次に、半導体層1714を覆ってゲート絶縁膜1715を形成する。ゲート絶縁膜1715には、例えば酸化珪素、窒化珪素または窒化酸化珪素等を用いて単層または複数の膜を積層させて形成する。なお、成膜方法には、CVD法、スパッタ法等を用いることができる。

#### 【0224】

続いて、半導体層1714の上方にゲート絶縁膜1715を介してそれぞれゲート電極1716を形成する。ゲート電極1716は単層で形成してもよいし、複数の金属膜を積層して形成してもよい。なお、ゲート電極は、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)等から選ばれた金属元素の他にも、前記元素を主成分とする合金材料若しくは化合物材料で形成することができる。例えば、第1の導電層として窒化タンタル(TaN)を用

10

20

30

40

50

い、第2の導電層としてタンゲステン(W)を用いた、第1の導電膜と第2の導電膜からなるゲート電極としてもよい。

#### 【0225】

次に、ゲート電極1716またはレジストを形成し所望の形状にしたものをマスクとして用い、半導体層1714にn型またはp型の導電性を付与する不純物を選択的に添加する。このようにして、半導体層1714に、チャネル形成領域および不純物領域(ソース領域、ドレイン領域、GOLD領域、LDD領域を含む)が形成される。また、添加される不純物元素の導電型によりNチャネル型トランジスタ、またはPチャネル型トランジスタとを区別して作製することができる。

#### 【0226】

なお、図17は、LDD領域1720を自己整合的に作製するために、ゲート電極1716を覆うようにシリコン化合物、例えば、酸化シリコン膜、窒化シリコン膜若しくは酸化窒化シリコン膜を形成した後、エッチバックしてサイドウォール1717を形成する。その後、半導体層1714に導電性を付与する不純物を添加することにより、ソース領域1718、ドレイン領域1719及びLDD領域1720を形成することができる。そのため、LDD領域1720はサイドウォール1717の下部に位置する。なお、サイドウォール1717は、LDD領域1720を自己整合的に形成するために設けるのであって、必ずしも設けなくてもよい。なお、導電性を付与する不純物としてはリン、ヒ素、ボロン等が用いられる。

#### 【0227】

次に、ゲート電極1716を覆って、第1の層間絶縁膜1730として第1の絶縁膜1721、第2の絶縁膜1722を積層し形成する。第1の絶縁膜1721、第2の絶縁膜1722としては、酸化珪素膜、窒化珪素膜または酸化窒化珪素膜(SiO<sub>x</sub>N<sub>y</sub>)等の無機絶縁膜、もしくは低誘電率の有機樹脂膜(感光性や非感光性の有機樹脂膜)を用いることができる。また、シロキサンを含む膜を用いてもよい。なお、シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される材料であり、置換基としては、有機基(例えばアルキル基、芳香族炭化水素)が用いられる。また、置換基にフルオロ基を含んでいても良い。

#### 【0228】

なお、第1の絶縁膜1721、第2の絶縁膜1722に同一材料の絶縁膜を用いても良い。本実施形態では第1の層間絶縁膜1730を2層の積層構造としたが、1層としても良いし、3層以上の積層構造としても良い。

#### 【0229】

なお、第1の絶縁膜1721、第2の絶縁膜1722は、スパッタ法、CVD法、スピノコーティング法等を用いて形成すればよく、有機樹脂膜やシロキサンを含む膜を用いる場合には塗布法を用いて形成すればよい。

#### 【0230】

その後、第1の層間絶縁膜1730上にソース電極及びドレイン電極1723を形成する。なお、ソース電極及びドレイン電極1723は、それぞれコンタクトホールを介してソース領域1718、ドレイン領域1719に接続されている。

#### 【0231】

なお、ソース電極及びドレイン電極1723は、銀(Ag)、金(Au)、銅(Cu)、ニッケル(Ni)、白金(Pt)、パラジウム(Pd)、イリジウム(Ir)、ロジウム(Rh)、タンゲステン(W)、アルミニウム(Al)、タンタル(Ta)、モリブデン(Mo)、カドミウム(Cd)、亜鉛(Zn)、鉄(Fe)、チタン(Ti)、珪素(Si)、ゲルマニウム(Ge)、ジルコニア(Zr)、バリウム(Ba)等の金属又はその合金、若しくはその金属窒化物、又はこれらの積層膜を用いることができる。

#### 【0232】

次に、ソース電極及びドレイン電極1723を覆って第2の層間絶縁膜1731を形成する。第2の層間絶縁膜1731としては、無機絶縁膜や、樹脂膜、又はこれらの積層を

10

20

30

40

50

用いることができる。無機絶縁膜としては、窒化珪素膜、酸化珪素膜、酸化窒化珪素膜又はこれらを積層した膜を用いることができる。樹脂膜としては、ポリイミド、ポリアミド、アクリル、ポリイミドアミド、エポキシなどを用いることができる。

### 【0233】

第2の層間絶縁膜1731上には画素電極1724を形成する。次に、画素電極1724の端部を覆うように絶縁物1725を形成する。絶縁物1725は、後に形成される発光物質を含む層1726の成膜を良好なものとするため、絶縁物1725の上端部または下端部が曲率を有する曲面となるように形成することが好ましい。例えば、絶縁物1725の材料としてポジ型の感光性アクリルを用いた場合、絶縁物1725の上端部のみに曲率半径(0.2μm~3μm)を有する曲面を持たせることが好ましい。また、絶縁物1725として、感光性の光によってエッチャントに不溶解性となるネガ型、あるいは光によってエッチャントに溶解性となるポジ型のいずれも使用することができる。さらには、絶縁物1725の材料として有機物に限らず酸化珪素、酸窒化珪素等の無機物も用いることできる。

10

### 【0234】

次に、画素電極1724及び絶縁物1725上に発光物質を含む層1726及び対向電極1727を形成する。

### 【0235】

なお、画素電極1724と対向電極1727とにより発光物質を含む層1726が挟まれた領域では発光素子1728が形成されている。

20

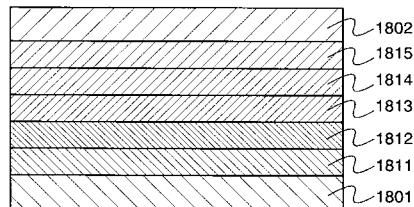

### 【0236】

次に、発光素子1728の詳細について図18を用いて説明する。なお、図17における画素電極1724及び対向電極1727は、それぞれ図18の画素電極1801、対向電極1802に相当する。また、図18(a)においては、画素電極を陽極、対向電極を陰極とする。

20

### 【0237】

図18(a)に示すように、画素電極1801と対向電極1802との間には、発光層1813の他、正孔注入層1811、正孔輸送層1812、電子輸送層1814、電子注入層1815等も設けられている。これらの層は、画素電極1801の電位が対向電極1802の電位よりも高くなるように電圧を印加したときに、画素電極1801側から正孔が注入され対向電極1802側から電子が注入されるように積層されている。

30

### 【0238】

このような発光素子において、画素電極1801から注入された正孔と、対向電極1802から注入された電子とは、発光層1813において再結合し、発光物質を励起状態にする。そして、励起状態の発光物質が基底状態に戻るときに発光する。なお、発光物質とは、ルミネセンス(エレクトロルミネセンス)が得られる物質であれば良い。

### 【0239】

発光層1813を形成する物質について特に限定はなく、発光物質のみから形成された層であっても良いが、濃度消光を生じる場合には発光物質が有するエネルギーギャップよりも大きいエネルギーギャップを有する物質(ホスト)からなる層中に発光物質が分散するように混合された層であることが好ましい。これによって、発光物質の濃度消光を防ぐことができる。なお、エネルギーギャップとは最低空分子軌道(LUMO: Lowest Unoccupied Molecular Orbital)準位と最高被占分子軌道(HOMO: Highest Occupied Molecular Orbital)準位とのエネルギー差をいう。

40

### 【0240】

また、発光物質についても特に限定はなく、所望の発光波長の発光をし得る物質を用いればよい。例えば、赤色系の発光を得たいときには、4-ジシアノメチレン-2-イソブロピル-6-[2-(1,1,7,7-テトラメチルジュロリジン-9-イル)エテニル]-4H-ピラン(略称:DCJTI)、4-ジシアノメチレン-2-メチル-6-[2

50

- (1, 1, 7, 7 - テトラメチルジュロリジン - 9 - イル) エテニル] - 4 H - ピラン(略称: DCJT)、4 - ジシアノメチレン - 2 - tert - ブチル - 6 - [2 - (1, 1, 7, 7 - テトラメチルジュロリジン - 9 - イル) エテニル] - 4 H - ピラン(略称: DCJTB)やペリフランテン、2, 5 - ジシアノ - 1, 4 - ビス[2 - (10 - メトキシ - 1, 1, 7, 7 - テトラメチルジュロリジン - 9 - イル) エテニル]ベンゼン等、600 nmから680 nmに発光スペクトルのピークを有する発光を呈する物質を用いることができる。また、緑色系の発光を得たいときは、N, N' - ジメチルキナクリドン(略称: DMQd)、クマリン6やクマリン545T、トリス(8 - キノリノラト)アルミニウム(略称: Alq)、N, N' - ジフェニルキナクリドン(略称: DPQd)等、500 nmから550 nmに発光スペクトルのピークを有する発光を呈する物質を用いることができる。また、青色系の発光を得たいときは、9, 10 - ビス(2 - ナフチル) - tert - ブチルアントラセン(略称: t - BuDNA)、9, 9' - ピアントリル、9, 10 - ジフェニルアントラセン(略称: DPA)や9, 10 - ビス(2 - ナフチル)アントラセン(略称: DNA)、ビス(2 - メチル - 8 - キノリノラト) - 4 - フェニルフェノラト - ガリウム(BGaq)、ビス(2 - メチル - 8 - キノリノラト) - 4 - フェニルフェノラト - アルミニウム(BAlq)等、420 nmから500 nmに発光スペクトルのピークを有する発光を呈する物質を用いることができる。

10

#### 【0241】

発光物質を分散状態にするために用いる物質についても特に限定はなく、例えば、9, 10 - ジ(2 - ナフチル) - 2 - tert - ブチルアントラセン(略称: t - BuDNA)等のアントラセン誘導体、または4, 4' - ビス(N - カルバゾリル)ビフェニル(略称: CBP)等のカルバゾール誘導体の他、ビス[2 - (2 - ヒドロキシフェニル)ビリジナト]亜鉛(略称: Znpp<sub>2</sub>)、ビス[2 - (2 - ヒドロキシフェニル)ベンゾオキサゾラト]亜鉛(略称: ZnBOX)等の金属錯体等を用いることができる。

#### 【0242】

画素電極1801を形成する陽極材料は特に限定はされないが、仕事関数の大きい(仕事関数4.0 eV以上)金属、合金、電気伝導性化合物、及びこれらの混合物などを用いることが好ましい。このような陽極材料の具体例としては、金属材料の酸化物として、インジウム錫酸化物(略称: ITO)、酸化珪素を含有するITO、酸化インジウムに2~20[w t %]の酸化亜鉛(ZnO)を混合したターゲットを用いて形成されるインジウム亜鉛酸化物(略称: IZO)の他、金(Au)、白金(Pt)、ニッケル(Ni)、タンゲステン(W)、クロム(Cr)、モリブデン(Mo)、鉄(Fe)、コバルト(Co)、銅(Cu)、パラジウム(Pd)、または金属材料の窒化物(例えば、TiN)等を挙げることができる。

#### 【0243】

一方、対向電極1802を形成する物質としては、仕事関数の小さい(仕事関数3.8 eV以下)金属、合金、電気伝導性化合物、及びこれらの混合物などを用いることができる。このような陰極材料の具体例としては、周期表の1族または2族に属する元素、すなわちリチウム(Li)やセシウム(Cs)等のアルカリ金属またはマグネシウム(Mg)、カルシウム(Ca)、ストロンチウム(Sr)等のアルカリ土類金属、及びこれらを含む合金(Mg:Ag, Al:Li)が挙げられる。また、対向電極1802と発光層1813との間に、電子注入性に優れた層を当該対向電極と積層して設けることにより、仕事関数の大小に関わらず、Al、Ag、ITOや、酸化珪素を含有するITO等の画素電極1801の材料として挙げた材料も含めた様々な導電性材料を対向電極1802として用いることができる。また、後述する電子注入層1815に、特に電子を注入する機能に優れた材料を用いることにより同様の効果を得ることができる。

#### 【0244】

なお、発光した光を外部に取り出すために、画素電極1801と対向電極1802のいずれか一方または両方がITO等の透明電極、または可視光が透過出来るような数~数十nmの厚さで形成された電極であることが好ましい。

10

20

30

40

50

## 【0245】

画素電極1801と発光層1813との間には、図18(a)に示すように正孔輸送層1812を有する。正孔輸送層とは、画素電極1801から注入された正孔を発光層1813へ輸送する機能を有する層である。このように、正孔輸送層1812を設け、画素電極1801と発光層1813とを離すことによって、発光が金属に起因して消光することを防ぐことができる。

## 【0246】

なお、正孔輸送層1812には、正孔輸送性の高い物質を用いて形成することが好ましく、特に $1 \times 10^{-6} \text{ cm}^2 / \text{Vs}$ 以上の正孔移動度を有する物質を用いて形成することが好ましい。なお、正孔輸送性の高い物質とは、電子よりも正孔の移動度が高い物質をいう。正孔輸送層1812を形成するのに用いることができる物質の具体例としては、4,4'-ビス[N-(1-ナフチル)-N-フェニルアミノ]ビフェニル(略称:NPB)、4,4'-ビス[N-(3-メチルフェニル)-N-フェニルアミノ]ビフェニル(略称:TPD)、4,4',4'''-トリス(N,N-ジフェニルアミノ)トリフェニルアミン(略称:T DATA)、4,4',4'''-トリス[N-(3-メチルフェニル)-N-フェニルアミノ]トリフェニルアミン(略称:MT DATA)、4,4'-ビス{N-[4-(N,N-ジ-m-トリルアミノ)フェニル]-N-フェニルアミノ}ビフェニル(略称:DNTPD)、1,3,5-トリス[N,N-ジ(m-トリル)アミノ]ベンゼン(略称:m-MT DAB)、4,4',4'''-トリス(N-カルバゾリル)トリフェニルアミン(略称:T CTA)、フタロシアニン(略称:H<sub>2</sub>Pc)、銅フタロシアニン(略称:CuPc)、バナジルフタロシアニン(略称:VOPc)等が挙げられる。また、正孔輸送層1812は、以上に述べた物質から成る層を二以上組み合わせて形成した多層構造の層であってもよい。

10

20

30

40

50

## 【0247】

また、対向電極1802と発光層1813との間には、図18(a)に示すように電子輸送層1814を有していてもよい。ここで、電子輸送層とは、対向電極1802から注入された電子を発光層1813へ輸送する機能を有する層である。このように、電子輸送層1814を設け、対向電極1802と発光層1813とを離すことによって、発光が金属に起因して消光することを防ぐことができる。

## 【0248】

電子輸送層1814について特に限定はなく、トリス(8-キノリノラト)アルミニウム(略称:A1q)、トリス(4-メチル-8-キノリノラト)アルミニウム(略称:A1mq<sub>3</sub>)、ビス(10-ヒドロキシベンゾ[h]-キノリナト)ベリリウム(略称:BeBq<sub>2</sub>)、ビス(2-メチル-8-キノリノラト)-4-フェニルフェノラト-アルミニウム(略称:BAlq)など、キノリン骨格またはベンゾキノリン骨格を有する金属錯体等によって形成されたものを用いることができる。この他、ビス[2-(2-ヒドロキシフェニル)-ベンゾオキサゾラト]亜鉛(略称:Zn(BOX)<sub>2</sub>)、ビス[2-(2-ヒドロキシフェニル)-ベンゾチアゾラト]亜鉛(略称:Zn(BTZ)<sub>2</sub>)などのオキサゾール系、チアゾール系配位子を有する金属錯体等によって形成されたものであってもよい。また、2-(4-ビフェニリル)-5-(4-tert-ブチルフェニル)-1,3,4-オキサジアゾール(略称:PB D)や、1,3-ビス[5-(p-tert-ブチルフェニル)-1,3,4-オキサジアゾール-2-イル]ベンゼン(略称:OXD-7)、3-(4-tert-ブチルフェニル)-4-フェニル-5-(4-ビフェニリル)-1,2,4-トリアゾール(略称:TAZ)、3-(4-tert-ブチルフェニル)-4-(4-エチルフェニル)-5-(4-ビフェニリル)-1,2,4-トリアゾール(略称:p-Et TAZ)、バソフェナントロリン(略称:BPhen)、バソキュプロイン(略称:BCP)等を用いて形成されたものであってもよい。電子輸送層1814は、以上に記載したような正孔の移動度よりも電子の移動度が高い物質を用いて形成することが好ましい。また、電子輸送層1814は、 $10^{-6} \text{ cm}^2 / \text{Vs}$ 以上の電子移動度を有する物質を用いて形成することがより好ましい。なお、電子輸送層1814は、以

上に述べた物質から成る層を二以上組み合わせて形成した多層構造であってもよい。

#### 【0249】

さらに、画素電極1801と正孔輸送層1812との間には、図18(a)に示すように、正孔注入層1811を有していてもよい。ここで、正孔注入層とは、陽極として機能する電極から正孔輸送層1812へ正孔の注入を促す機能を有する層である。

#### 【0250】

正孔注入層1811について特に限定はなく、モリブデン酸化物(MoO<sub>x</sub>)やバナジウム酸化物(VO<sub>x</sub>)、ルテニウム酸化物(RuO<sub>x</sub>)、タングステン酸化物(WO<sub>x</sub>)、マンガン酸化物(MnO<sub>x</sub>)等の金属酸化物によって形成されたものを用いることができる。この他、フタロシアニン(略称:H<sub>2</sub>Pc)や銅フタロシアニン(CuPc)等のフタロシアニン系の化合物、4,4'-ビス(N-(4-(N,N-ジ-m-トリルアミノ)フェニル)-N-フェニルアミノ)ビフェニル(略称:DNTPD)等の芳香族アミン系の化合物、或いはポリ(エチレンジオキシチオフェン)/ポリ(スチレンスルホン酸)水溶液(PEDOT/PPS)等の高分子等によっても正孔注入層1811を形成することができる。10

#### 【0251】

また、前記金属酸化物と、正孔輸送性の高い物質とを混合したものを、画素電極1801と正孔輸送層1812との間に設けても良い。このような層は、厚膜化しても駆動電圧の上昇を伴わないため、層の膜厚を調整することでマイクロキャビティ効果や光の干渉効果を利用した光学設計を行うことができる。そのため、色純度に優れ、視野角に依存する色変化などが小さい高品質な発光素子を作製することができる。また、画素電極1801の表面に成膜時に発生する凹凸や電極表面に残った微少な残渣の影響で画素電極1801と対向電極1802がショートすることを防ぐ膜厚を選ぶことができる。20

#### 【0252】

また、対向電極1802と電子輸送層1814との間には、図18(a)に示すように、電子注入層1815を有していてもよい。ここで、電子注入層とは、陰極として機能する電極から電子輸送層1814へ電子の注入を促す機能を有する層である。なお、電子輸送層を特に設けない場合は、陰極として機能する電極と発光層との間に電子注入層を設け、発光層への電子の注入を補助してもよい。

#### 【0253】

電子注入層1815について特に限定はなく、フッ化リチウム(LiF)、フッ化セシウム(CsF)、フッ化カルシウム(CaF<sub>2</sub>)等のようなアルカリ金属又はアルカリ土類金属の化合物を用いて形成されたものを用いることができる。この他、Alqまたは4,4'-ビス(5-メチルベンズオキサゾル-2-イル)スチルベン(BzOs)等のように電子輸送性の高い物質と、マグネシウムまたはリチウム等のようにアルカリ金属又はアルカリ土類金属とを混合したものも、電子注入層1815として用いることができる。30

#### 【0254】

なお、正孔注入層1811、正孔輸送層1812、発光層1813、電子輸送層1814、電子注入層1815は、それぞれ、蒸着法、インクジェット法、または塗布法等、いずれの方法で形成しても構わない。また、画素電極1801または対向電極1802についても、スパッタ法または蒸着法等、いずれの方法を用いて形成しても構わない。40

#### 【0255】

また、発光素子の層構造は、図18(a)に記載したものに限定されず、図18(b)に示すように陰極として機能する電極から順に作製してもよい。つまり、画素電極1801を陰極とし、画素電極1801上に電子注入層1815、電子輸送層1814、発光層1813、正孔輸送層1812、正孔注入層1811、対向電極1802の順で積層しても良い。なお、対向電極1802は陽極として機能する。

#### 【0256】

なお、発光素子は、発光層が一層のものについて記載したが、複数の発光層を有するものであってもよい。複数の発光層を設け、それぞれの発光層からの発光を混合することで50

、白色光を得ることができる。たとえば2層の発光層を有する発光素子の場合、第1の発光層と第2の発光層との間には、間隔層や、正孔を発生する層及び電子を発生する層を設けることが好ましい。このような構成により、外部に射出したそれぞれの発光は、視覚的に混合され、白色光として視認される。よって、白色光を得ることができる。

#### 【0257】

また、発光は、図17において画素電極1724または対向電極1727のいずれか一方または両方を通して外部に取り出される。従って、画素電極1724または対向電極1727のいずれか一方または両方は、透光性を有する物質で成る。

#### 【0258】

対向電極1727のみが透光性を有する物質からなる場合、図19(a)に示すように発光は対向電極1727を通して基板と逆側から取り出される。また、画素電極1724のみが透光性を有する物質からなる場合、図19(b)に示すように発光は画素電極1724を通して基板側から取り出される。画素電極1724および対向電極1727がいずれも透光性を有する物質からなるものである場合、図19(c)に示すように発光は画素電極1724および対向電極1727を通して、基板側および基板と逆側の両方から取り出される。

#### 【0259】

次に、トランジスタ1713に非結晶性の半導体膜を半導体層に用いた順スタガ構造のトランジスタについて説明する。画素の部分断面図を図20に示す。なお、図20では、順スタガ構造のトランジスタを記すと共に、画素が有する容量素子についても合わせて説明する。

#### 【0260】

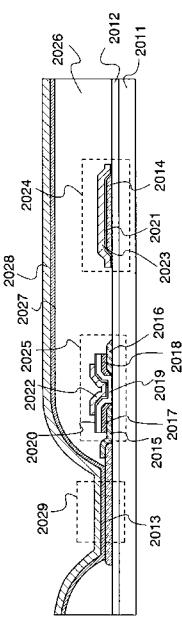

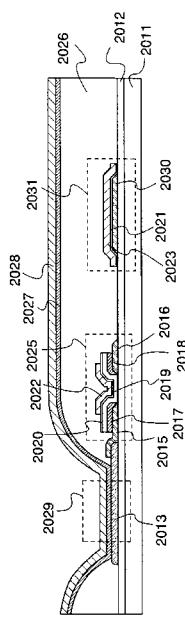

図20に示すように、基板2011上に下地膜2012が形成されている。さらに下地膜2012上に画素電極2013が形成されている。また、画素電極2013と同層に同じ材料からなる第1の電極2014が形成されている。

#### 【0261】

さらに、下地膜2012上に配線2015及び配線2016が形成され、画素電極2013の端部は配線2015で覆われている。配線2015及び配線2016の上部にN型の導電型を有するN型半導体層2017及びN型半導体層2018が形成されている。また、配線2015と配線2016の間であって、下地膜2012上に半導体層2019が形成されている。そして、半導体層2019の一部はN型半導体層2017及びN型半導体層2018上にまで延長されている。なお、この半導体層はアモルファスシリコン(a-Si:H)等の非晶質半導体、セミアモルファス半導体、微結晶半導体等の非結晶性の半導体膜で形成されている。また、半導体層2019上にゲート絶縁膜2020が形成されている。また、ゲート絶縁膜2020と同層の同じ材料からなる絶縁膜2021が第1の電極2014上にも形成されている。

#### 【0262】

さらに、ゲート絶縁膜2020上に、ゲート電極2022が形成され、トランジスタ2025が形成されている。また、ゲート電極2022と同層に同じ材料でなる第2の電極2023が第1の電極2014上に絶縁膜2021を介して形成され、絶縁膜2021が第1の電極2014と第2の電極2023とで挟まれた構成の容量素子2024が形成されている。また、画素電極2013の端部、トランジスタ2025及び容量素子2024を覆って、層間絶縁膜2026が形成されている。

#### 【0263】

層間絶縁膜2026及びその開口部に位置する画素電極2013上に発光物質を含む層2027及び対向電極2028が形成され、発光物質を含む層2027が画素電極2013と対向電極2028とで挟まれた領域で発光素子2029が形成されている。

#### 【0264】

また、図20(a)に示す第1の電極2014を図20(b)に示すように配線2015及び2016と同層の同一材料で形成し、絶縁膜2021が第1の電極2030と第2

10

20

30

40

50

の電極 2023 とで挟まれた構成の容量素子 2031 としても良い。また、図 20 において、トランジスタ 2025 に N チャネル型トランジスタを用いたが、P チャネル型トランジスタでも良い。

#### 【0265】

基板 2011、下地膜 2012、画素電極 2013、ゲート絶縁膜 2020、ゲート電極 2022、層間絶縁膜 2026、発光物質を含む層 2027 及び対向電極 2028 に用いられる材料は、図 17 説明した基板 1711、下地膜 1712、画素電極 1724、ゲート絶縁膜 1715、ゲート電極 1716、層間絶縁膜 1730 及び 1731、発光物質を含む層 1726 及び対向電極 1727 と同様の材料をそれぞれ用いることができる。また、配線 2015、配線 2016 は、図 17 におけるソース電極及びドレイン電極 1723 と同様の材料を用いれば良い。

10

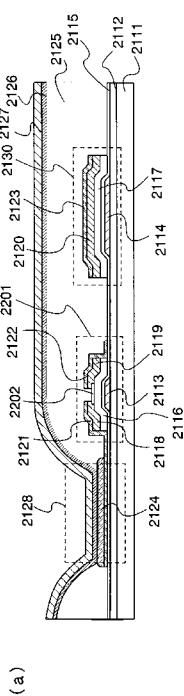

#### 【0266】

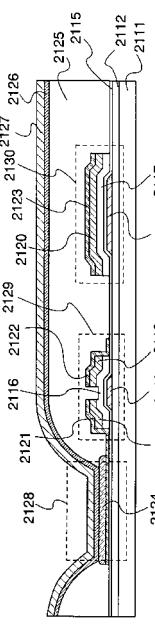

次に、半導体層に非結晶性の半導体膜を用いたトランジスタの他の構成として、基板と半導体層の間にゲート電極が挟まれた構造、つまり半導体層の下にゲート電極が位置するボトムゲート型のトランジスタを有する画素の部分断面図を図 21 に示す。

#### 【0267】

基板 2111 上に下地膜 2112 が形成されている。さらに下地膜 2112 上にゲート電極 2113 が形成されている。また、ゲート電極 2113 と同層に同じ材料からなる第 1 の電極 2114 が形成されている。ゲート電極 2113 の材料には図 17 におけるゲート電極 1716 に使用される材料の他、リンが添加された多結晶シリコンや金属とシリコンの化合物であるシリサイドでもよい。

20

#### 【0268】

また、ゲート電極 2113 及び第 1 の電極 2114 を覆うようにゲート絶縁膜 2115 が形成されている。

#### 【0269】

ゲート絶縁膜 2115 上に、半導体層 2116 が形成されている。また、半導体層 2116 と同層に同じ材料からなる半導体層 2117 が第 1 の電極 2114 上に形成されている。なお、この半導体層はアモルファスシリコン (a-Si : H) 等の非晶質半導体、セミアモルファス半導体、微結晶半導体等の非結晶性の半導体膜で形成されている。

30

#### 【0270】

半導体層 2116 上には N 型の導電型を有する N 型半導体層 2118 及び N 型半導体層 2119 が形成され、半導体層 2117 上には N 型半導体層 2120 が形成されている。

#### 【0271】

N 型半導体層 2118 及び N 型半導体層 2119 上にはそれぞれ配線 2121、配線 2122 が形成され、トランジスタ 2129 が形成された。また、N 型半導体層 2120 上には配線 2121 及び配線 2122 と同層の同一材料からなる導電層 2123 が形成され、この導電層 2123 と、N 型半導体層 2120 と、半導体層 2117 とで第 2 の電極を構成している。なお、この第 2 の電極と第 1 の電極 2114 とでゲート絶縁膜 2115 が挟まれた構成の容量素子 2130 が形成されている。

40

#### 【0272】

また、配線 2121 の一方の端部は延在し、その延在した配線 2121 上部に接して画素電極 2124 が形成されている。

#### 【0273】

また、画素電極 2124 の端部、トランジスタ 2129 及び容量素子 2130 を覆うように絶縁物 2125 が形成されている。

#### 【0274】

画素電極 2124 及び絶縁物 2125 上には発光物質を含む層 2126 及び対向電極 2127 が形成され、画素電極 2124 と対向電極 2127 とで発光物質を含む層 2126 が挟まれた領域では発光素子 2128 が形成されている。

50

#### 【0275】

容量素子 2130 の第 2 の電極の一部となる半導体層 2117 及び N 型半導体層 2120 は特に設けなくても良い。つまり、第 2 の電極を導電層 2123 とし、第 1 の電極 2114 と導電層 2123 とでゲート絶縁膜 2115 が挟まれた構造の容量素子としてもよい。

#### 【0276】

また、トランジスタ 2129 に N チャネル型トランジスタを用いたが、 P チャネル型トランジスタでも良い。

#### 【0277】

なお、図 21 (a)において、配線 2121 を形成する前に画素電極 2124 を形成することで、図 21 (b)に示すような画素電極 2124 と同層の同一材料からなる第 2 の電極 2131 と第 1 の電極 2114 とでゲート絶縁膜 2115 が挟まれた構成の容量素子 2132 を形成することもできる。

10

#### 【0278】

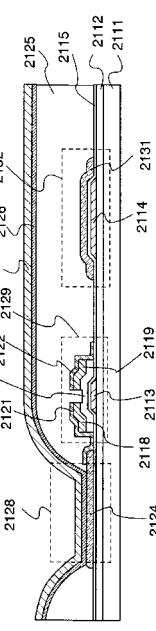

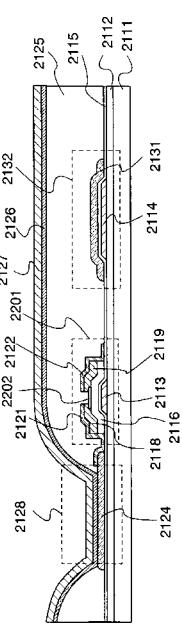

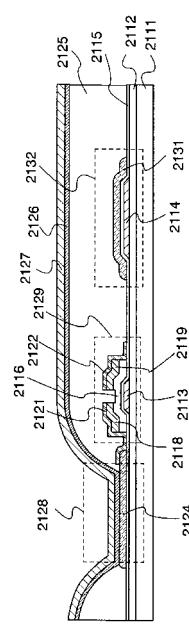

逆スタガ型のチャネルエッチ構造のトランジスタについて示したが、もちろんチャネル保護構造のトランジスタでも良い。次に、チャネル保護構造のトランジスタの場合について図 22 を用いて説明する。なお、図 22 において、図 21 と同様のものに関しては共通の符号を用いて示す。

#### 【0279】

図 22 (a) に示すチャネル保護型構造のトランジスタ 2201 は、図 21 (a) に示したチャネルエッチ構造のトランジスタ 2129 とは半導体層 2116 においてチャネルが形成される領域上にエッティングのマスクとなる絶縁物 2202 が設けられている点で異なる。

20

#### 【0280】

同様に、図 22 (b) に示すチャネル保護型構造のトランジスタ 2201 は、図 21 (b) に示したチャネルエッチ構造のトランジスタ 2129 とは半導体層 2116 においてチャネルが形成される領域上にエッティングのマスクとなる絶縁物 2202 が設けられている点で異なる。

20

#### 【0281】

本発明の画素を構成するトランジスタの半導体層に非結晶性の半導体膜を用いることで、製造コストを削減することができる。なお、各材料には図 17 において説明したもの用いることができる。

30

#### 【0282】

また、トランジスタの構造や容量素子の構成は上述したものに限られず、さまざまな構造もしくは構成のトランジスタや容量素子を用いることができる。

#### 【0283】

また、トランジスタの半導体層にはアモルファスシリコン (a-Si:H) 等の非晶質半導体、セミアモルファス半導体、微結晶半導体等の非結晶性の半導体膜の他、ポリシリコン (p-Si:H) 等の結晶性半導体膜を用いても良い。

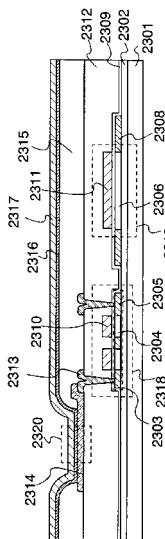

#### 【0284】

図 23 に、半導体層に結晶性半導体膜を用いたトランジスタを有する画素の部分断面図を示し、以下に説明する。なお、図 23 に示すトランジスタ 2318 は、図 10 で示したマルチゲート型のトランジスタである。

40

#### 【0285】

図 23 に示すように、基板 2301 上に下地膜 2302 が形成され、その上に半導体層 2303 が形成されている。なお、半導体層 2303 は、結晶性半導体膜を所望の形状にパターニングし形成する。

#### 【0286】

結晶性半導体膜の作製方法の一例を以下に記す。まず、基板 2301 上にスパッタ法、CVD 法等によりアモルファスシリコン膜を成膜する。成膜材料は、アモルファスシリコン膜に限定する必要はなく、非晶質半導体、セミアモルファス半導体、微結晶半導体等の

50

非結晶性半導体膜であれば良い。また、非晶質シリコンゲルマニウム膜などの非晶質構造を含む化合物半導体膜を用いても良い。

#### 【0287】

そして、成膜したアモルファスシリコン膜を熱結晶化法、レーザー結晶化法、またはニッケルなどの触媒元素を用いた熱結晶化法等を用いて結晶化し、結晶性半導体膜を得る。なお、これらの結晶化方法を組み合わせて結晶化しても良い。

#### 【0288】

熱結晶化法により結晶性半導体膜を形成する場合には、加熱炉、レーザ照射、若しくはRTA (Rapid Thermal Annealing)、又はこれらを組み合わせて用いることができる。

10

#### 【0289】

また、レーザー結晶化法により結晶性半導体膜を形成する場合には、連続発振型のレーザビーム (CWレーザビーム) やパルス発振型のレーザビーム (パルスレーザビーム) を用いることができる。ここで用いることができるレーザビームは、Arレーザ、Krレーザ、エキシマレーザなどの気体レーザ、単結晶のYAG、YVO<sub>4</sub>、フォルステライト (Mg<sub>2</sub>SiO<sub>4</sub>)、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶 (セラミック) のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザ、ガラスレーザ、ルビーレーザ、アレキサンドライトレーザ、Ti:サファイアレーザ、銅蒸気レーザまたは金蒸気レーザのうち一種または複数種から発振されるものを用いることができる。このようなレーザビームの基本波、及びこれらの基本波の第2高調波から第4高調波のレーザビームを照射することで、大粒径の結晶を得ることができる。例えば、Nd:YVO<sub>4</sub>レーザ (基本波1064nm) の第2高調波 (532nm) や第3高調波 (355nm) を用いることができる。このときレーザのエネルギー密度は0.01~100MW/cm<sup>2</sup>程度 (好ましくは0.1~10MW/cm<sup>2</sup>) 必要である。そして、走査速度を10~2000cm/sec程度として照射する。

20

#### 【0290】

なお、単結晶のYAG、YVO<sub>4</sub>、フォルステライト (Mg<sub>2</sub>SiO<sub>4</sub>)、YAlO<sub>3</sub>、GdVO<sub>4</sub>、若しくは多結晶 (セラミック) のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザ、Arイオンレーザ、またはTi:サファイアレーザは、連続発振をさせることができ、Qスイッチ動作やモード同期などを行うことによって10MHz以上の発振周波数でパルス発振をさせることも可能である。10MHz以上の発振周波数でレーザビームを発振させると、半導体膜がレーザによって溶融してから固化するまでの間に、次のパルスが半導体膜に照射される。従って、発振周波数が低いパルスレーザを用いる場合と異なり、半導体膜中において固液界面を連続的に移動させることができるために、走査方向に向かって連続的に成長した結晶粒を得ることができる。

30

#### 【0291】

また、ニッケルなどの触媒元素を用いた熱結晶化法により結晶性半導体膜を形成する場合には、結晶化後にニッケルなどの触媒元素を除去するゲッタリング処理を行うことが好ましい。

40

#### 【0292】

上述した結晶化によって、非晶質半導体膜に部分的に結晶化された領域が形成される。この部分的に結晶化された結晶性半導体膜を所望の形状にパターニングして島状の半導体膜を形成する。この半導体膜をトランジスタの半導体層2303に用いる。

#### 【0293】

また、結晶性半導体層は、トランジスタ2318のチャネル形成領域2304及びソース領域又はドレイン領域となる不純物領域2305に用いられる他、容量素子2319の下部電極となる半導体層2306及び不純物領域2308にも用いられる。なお、不純物

50

領域 2308 は特に設ける必要はない。また、チャネル形成領域 2304 及び半導体層 2306 にはチャネルドープが行われていても良い。

#### 【0294】

次に、半導体層 2303 及び容量素子 2319 の下部電極上にはゲート絶縁膜 2309 が形成されている。さらに、半導体層 2303 上にはゲート絶縁膜 2309 を介してゲート電極 2310 が、容量素子 2319 の半導体層 2306 上にはゲート絶縁膜 2309 を介してゲート電極 2310 と同層に同じ材料からなる上部電極 2311 が形成されている。このようにして、トランジスタ 2318 及び容量素子 2319 が作製される。

#### 【0295】

次に、トランジスタ 2318 及び容量素子 2319 を覆って層間絶縁膜 2312 が形成され、層間絶縁膜 2312 上にはコンタクトホールを介して不純物領域 2305 と接する配線 2313 が形成されている。そして、配線 2313 に接して層間絶縁膜 2312 上には画素電極 2314 が形成され、画素電極 2314 の端部及び配線 2313 を覆って絶縁物 2315 が形成されている。さらに、画素電極 2314 上に発光物質を含む層 2316 及び対向電極 2317 が形成され、画素電極 2314 と対向電極 2317 とで発光物質を含む層 2316 が挟まれた領域では発光素子 2320 が形成されている。

10

#### 【0296】

また、半導体層にポリシリコン (p-Si:H) 等の結晶性半導体膜を用いたボトムゲート型のトランジスタを有する画素の部分断面を図 24 に示す。

20

#### 【0297】

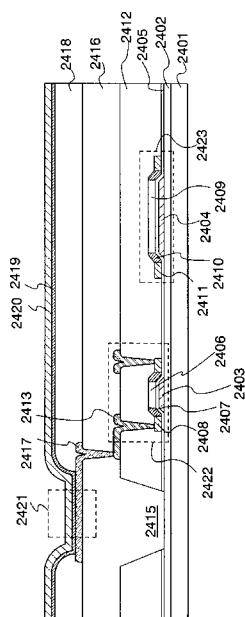

基板 2401 上に下地膜 2402 が形成され、その上にゲート電極 2403 が形成されている。また、ゲート電極 2403 と同層に同じ材料からなる容量素子 2423 の第 1 の電極 2404 が形成されている。

#### 【0298】

また、ゲート電極 2403 及び第 1 の電極 2404 を覆うようにゲート絶縁膜 2405 が形成されている。

30

#### 【0299】

また、ゲート絶縁膜 2405 上に、半導体層が形成されている。なお、半導体膜は、非晶質半導体、セミアモルファス半導体、微結晶半導体等の非結晶性半導体膜を熱結晶化法、レーザー結晶化法、またはニッケルなどの触媒元素を用いた熱結晶化法等を用いて結晶化し、所望の形状にパターニングして半導体層を形成する。

30

#### 【0300】

なお、半導体層を用いてトランジスタ 2422 のチャネル形成領域 2406、LDD 領域 2407 及びソース領域又はドレイン領域となる不純物領域 2408、並びに容量素子 2423 の第 2 の電極となる領域 2409、不純物領域 2410 及び不純物領域 2411 が形成される。なお、不純物領域 2410 及び不純物領域 2411 は特に設けなくても良い。また、チャネル形成領域 2406 及び領域 2409 は不純物が添加されていても良い。

30

#### 【0301】

なお、容量素子 2423 はゲート絶縁膜 2405 が第 1 の電極 2404 及び半導体層から形成された領域 2409 等からなる第 2 の電極で挟まれた構成である。

40

#### 【0302】

次に、半導体層を覆って第 1 の層間絶縁膜 2412 が形成され、第 1 の層間絶縁膜 2412 上にコンタクトホールを介して不純物領域 2408 と接する配線 2413 が形成されている。

40

#### 【0303】

また、第 1 の層間絶縁膜 2412 には開口部 2415 が形成されている。トランジスタ 2422、容量素子 2423 及び開口部 2415 を覆うように第 2 の層間絶縁膜 2416 が形成され、第 2 の層間絶縁膜 2416 上にコンタクトホールを介して、配線 2413 と接続された画素電極 2417 が形成されている。また、画素電極 2417 の端部を覆って

50

絶縁物 2418 が形成されている。そして、画素電極 2417 上に発光物質を含む層 2419 及び対向電極 2420 が形成され、画素電極 2417 と対向電極 2420 とで発光物質を含む層 2419 が挟まれた領域では発光素子 2421 が形成されている。なお、発光素子 2421 の下部に開口部 2415 が位置している。つまり、発光素子 2421 からの発光を基板側から取り出すときには第 1 の層間絶縁膜 2412 に開口部 2415 を有するため透過率を高めることができる。

#### 【0304】

本発明の画素を構成するトランジスタの半導体層に結晶性半導体膜を用いることで、例えば、図 6 における走査線駆動回路 612 及び信号線駆動回路 611 を画素部 613 と一体形成することが容易になる。

10

#### 【0305】

なお、半導体層に結晶性半導体膜を用いたトランジスタにおいても構造は上述したものに限らず、さまざまな構造をとることができる。なお、容量素子においても同様である。また、本実施形態において、特に断りがない限り図 17 における材料を適宜使用することができます。

#### 【0306】

本実施形態で示したトランジスタは、実施の形態 1 乃至 7 に記載した画素において発光素子に供給する電流値を制御するトランジスタとして利用することができる。よって、実施の形態 1 乃至 7 に記載したように画素を動作させることで、トランジスタのしきい値電圧のばらつきに起因した電流値のばらつきを抑制することができる。よって、輝度データに対応した電流を発光素子に供給することができ、輝度のばらつきを抑制することが可能となる。また、対向電極の電位を一定として動作させるため消費電力を低くすることが可能である。

20

#### 【0307】

また、このような画素を図 6 の表示装置に適用することにより、各画素は自身のアドレス期間を除き発光することができるため、1 フレーム期間における発光期間の割合(即ち、デューティー比)を非常に大きくでき、おおむね 100% にすることもできる。よって、輝度のばらつきが少なくデューティー比が高い表示装置を得ることができる。

#### 【0308】

また、しきい値書き込み期間を長く設定することも可能であるため、発光素子に流れる電流値を制御するトランジスタのしきい値電圧をより正確に容量素子に書き込むことができる。よって、表示装置としての信頼性が向上する。

30

#### 【0309】

##### (実施の形態 9)

本実施の形態では、本発明の表示装置の一形態について図 25 を用いて説明する。

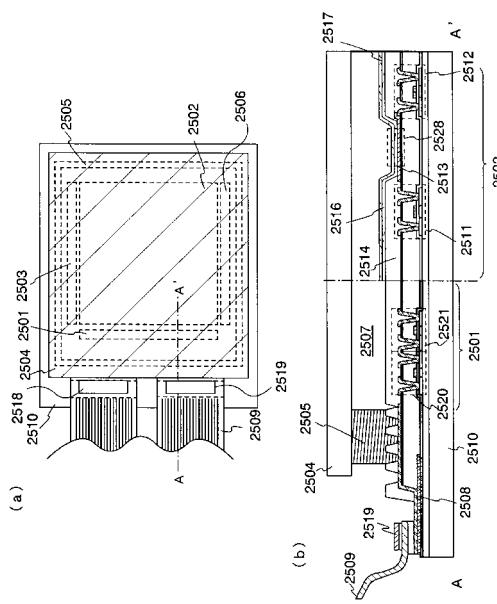

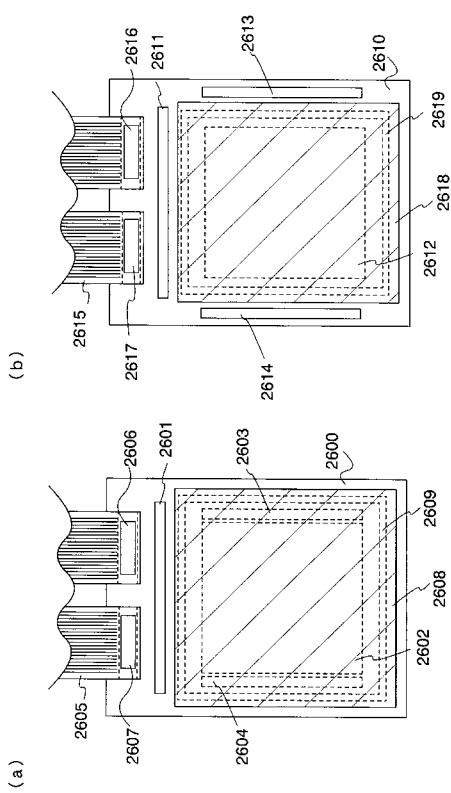

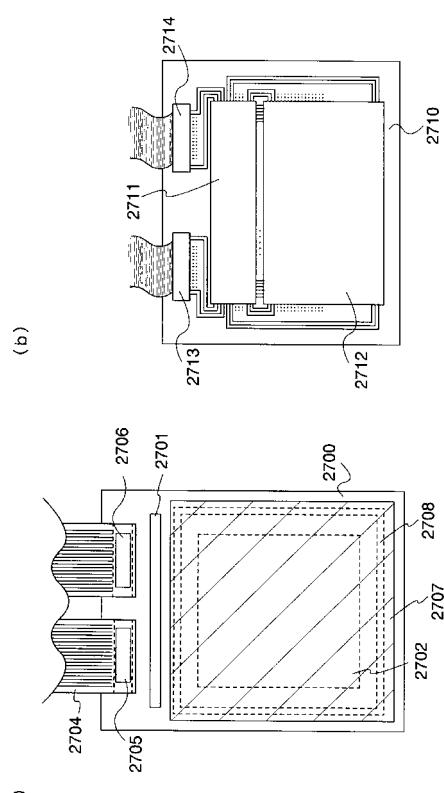

#### 【0310】

図 25(a) は、表示装置を示す上面図、図 25(b) は図 25(a) 中 A - A' 線断面図(A - A' で切断した断面図)である。表示装置は、基板 2510 上に図中において点線で示された信号線駆動回路 2501、画素部 2502、第 1 の走査線駆動回路 2503、第 2 の走査線駆動回路 2506 を有する。さらに、封止基板 2504、シール材 2505 を有し、これらで囲まれた表示装置の内側は、空間 2507 となっている。

40

#### 【0311】

なお、配線 2508 は第 1 の走査線駆動回路 2503、第 2 の走査線駆動回路 2506 及び信号線駆動回路 2501 に入力される信号を伝送するための配線であり、外部入力端子となる FPC(フレキシブルプリントサーキット) 2509 からビデオ信号、クロック信号、スタート信号等を受け取る。FPC 2509 と表示装置との接続部上には I C チップ(メモリ回路や、バッファ回路などが形成された半導体チップ) 2518 及び 2519 が COG(Chip On Glass) 等で実装されている。なお、ここでは FPC しか図示していないが、この FPC にはプリント配線基盤(PWB) が取り付けられていてもよい。本発明の表示装置とは、表示装置本体だけでなく、FPC もしくは PWB が取り

50

付けられた状態も含むものとする。また、I Cチップなどが実装されたものを含むものとする。

### 【0312】

断面構造について図25(b)を用いて説明する。基板2510上には画素部2502とその周辺駆動回路(第1の走査線駆動回路2503、第2の走査線駆動回路2506及び信号線駆動回路2501)が形成されているが、ここでは、信号線駆動回路2501と、画素部2502が示されている。

### 【0313】