(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2012년03월22일

(11) 등록번호 10-1121694

(24) 등록일자 2012년01월30일

- (51) 국제특허분류(Int. Cl.)

*H04B 1/04* (2006.01) *H04L 7/02* (2006.01)

*H04L 27/00* (2006.01)

- (21) 출원번호 10-2005-0003164

- (22) 출원일자 2005년01월13일

심사청구일자 2010년01월12일

- (65) 공개번호 10-2005-0074917

- (43) 공개일자 2005년07월19일

- (30) 우선권주장

JP-P-2004-00006864 2004년01월14일 일본(JP)

- (56) 선행기술조사문헌

EP01089428 A2\*

US20020058486 A1\*

- \*는 심사관에 의하여 인용된 문헌

- (73) 특허권자

가부시키가이샤 히타치세이사쿠쇼

일본국 도쿄도 치요다구 마루노우치 1초메 6반 6

고

- (72) 발명자

스즈끼메이

일본 도쿄도 고가네이시 미도리마찌 3-5-12 9-405

고시쓰

호리가즈유끼

일본 도쿄도 나카노구 야마토? 1-61-13

야노다까시

일본 사이타마Ken 도쿄로자와시 마쓰가오까 1-26-2

- (74) 대리인

이중희, 장수길

전체 청구항 수 : 총 12 항

심사관 : 복상문

## (54) 발명의 명칭 송신 회로, 무선 통신 장치, 및 송신 회로의 타이밍 조정 방법

**(57) 요약**

무선 통신 장치에 있어서, 직교 변조 방식의 I신호와 Q신호, EER 방식의 r신호와 θ신호와 같이, 다른 지연량을 갖는 경로를 통해 변조된 후에 합성되는 2개의 신호 패스의 지연차를 보정함으로써, 송신 신호의 선형성을 개선 한다. 입력된 디지털 신호로부터 분리된 2개의 신호 또는 분리되어 입력된 2개의 디지털 신호를 각각 아날로그 신호로 변환하는 DA 변환 회로와, 상기 DA 변환 회로에서 변환된 상기 아날로그 신호를 합성하는 합성 회로와, 상기 합성된 신호의 일부를 피드백 신호로서 추출하는 분배 회로와, 상기 피드백 신호를 디지털 신호로 변환하는 AD 변환 회로와, 상기 각 DA 변환 회로 및 상기 AD 변환 회로에 동작 클럭 신호를 공급하는 발진 회로와, 상기 AD 변환 회로에서 변환된 피드백 신호를 2개의 신호로 분리하는 제1 분리 회로와, 상기 분리된 입력 신호와, 상기 제1 분리 회로에서 분리된 피드백 신호를 비교하는 비교 회로를 가지고, 상기 발진 회로는 비교 회로에 의한 비교 결과에 기초하여 그 출력을 제어한다.

**대 표 도**

## 특허청구의 범위

### 청구항 1

입력된 디지털 신호를 분리함으로써 취득된 2개의 디지털 신호 또는 분리되어 입력된 2개의 디지털 신호를, 각각 아날로그 신호로 변환하는 2개의 DA 변환 회로와,

상기 2개의 DA 변환 회로에서 변환된 2개의 상기 아날로그 신호를 합성하는 합성 회로와,

상기 합성된 신호의 일부를 피드백 신호로서 추출하는 분배 회로와,

상기 피드백 신호를 디지털 신호로 변환하는 AD 변환 회로와,

상기 2개의 DA 변환 회로 및 상기 AD 변환 회로에 동작 클럭 신호를 공급하는 3개의 발진 회로와,

상기 AD 변환 회로에서 변환된 피드백 신호를 2개의 신호로 분리하는 제1 분리 회로와,

상기 입력된 디지털 신호를 분리함으로써 취득된 2개의 디지털 신호 중 적어도 하나, 또는 상기 분리되어 입력된 2개의 디지털 신호 중 적어도 하나와, 상기 제1 분리 회로에서 분리된 피드백 신호를 비교함으로써, 상기 비교된 신호의 타이밍 차를 판정하는 비교 회로를 가지고,

상기 3개의 발진 회로는, 상기 비교 회로에 의한 비교 결과에 기초하여, 상기 타이밍 차가 적어지도록, 출력하는 상기 클럭 신호를 제어하는 것을 특징으로 하는 송신 회로.

### 청구항 2

제1항에 있어서,

입력된 디지털 신호를 상기 2개의 디지털 신호로 분리하는 제2 분리 회로를 가지고,

상기 2개의 DA 변환 회로는, 제1 DA 변환 회로와 제2 DA 변환 회로에 의해 구성되고,

상기 비교 회로는, 상기 제2 분리 회로에서 분리된 디지털 신호와, 상기 제1 분리 회로에서 분리된 피드백 신호를 비교하고, 양 신호의 타이밍 차를 판정하고,

상기 3개의 발진 회로는,

상기 제1 DA 변환 회로, 상기 제2 DA 변환 회로 및 상기 AD 변환 회로에 클럭 신호를 공급하고,

상기 제1 DA 변환 회로, 상기 제2 DA 변환 회로 및 상기 AD 변환 회로 중 어느 하나에 공급되는 클럭 신호를 기준으로 하여, 다른 2개에 공급되는 클럭 신호를, 상기 타이밍 차가 적어지도록 제어하는 것을 특징으로 하는 송신 회로.

### 청구항 3

제2항에 있어서,

상기 제2 분리 회로는, 상기 입력된 디지털 신호의 진폭 성분과 위상 성분을 상기 2개의 디지털 신호로서 분리하고,

상기 제1 DA 변환 회로는, 상기 진폭 성분을 아날로그 신호로 변환하고,

상기 제2 DA 변환 회로는, 상기 위상 성분을 아날로그 신호로 변환하고,

상기 합성 회로는 상기 아날로그 신호로 변환된 진폭 성분과, 상기 아날로그 신호로 변환된 위상 성분을 합성하는 증폭 회로에 의해 구성되고,

상기 제1 분리 회로는, 상기 피드백 신호의 진폭 성분과 위상 성분을 상기 2개의 신호로서 분리하고,

상기 비교 회로는,

상기 제2 분리 회로에서 분리된 디지털 신호의 진폭 성분과, 상기 제1 분리 회로에서 분리된 피드백 신호의 진폭 성분을 비교하고, 양 신호의 타이밍 차를 판정하는 제1 비교기와,

상기 제2 분리 회로에서 분리된 디지털 신호의 위상 성분과, 상기 제1 분리 회로에서 분리된 피드백 신호의 위상 성분을 비교하고, 양 신호의 타이밍 차를 판정하는 제2 비교기에 의해 구성되고,

상기 3개의 발진 회로는,

상기 AD 변환 회로에 클럭 신호를 공급하는 기준 발진 회로와,

상기 제1 DA 변환 회로에 클럭 신호를 공급하는 제1 가변 발진 회로와,

상기 제2 DA 변환 회로에 클럭 신호를 공급하는 제2 가변 발진 회로에 의해 구성되고,

상기 제1 가변 발진 회로의 출력은 상기 제1 비교기의 비교 결과에 기초하여 제어되고, 상기 제2 가변 발진 회로의 출력은 상기 제2 비교기의 비교 결과에 기초하여 제어됨으로써, 상기 증폭 회로에 입력되는 진폭 성분과 위상 성분과의 타이밍을 정합시키는 것을 특징으로 하는 송신 회로.

#### 청구항 4

제2항에 있어서,

상기 제2 분리 회로는, 상기 입력된 디지털 신호의 진폭 성분과 위상 성분을 상기 2개의 디지털 신호로서 분리하고,

상기 제1 DA 변환 회로는, 상기 진폭 성분을 아날로그 신호로 변환하고,

상기 제2 DA 변환 회로는, 상기 위상 성분을 아날로그 신호로 변환하고,

상기 합성 회로는 상기 아날로그 신호로 변환된 진폭 성분과, 상기 아날로그 신호로 변환된 위상 성분을 합성하는 증폭 회로에 의해 구성되고,

상기 제1 분리 회로는, 상기 피드백 신호의 진폭 성분과 위상 성분을 상기 2개의 신호로서 분리하고,

상기 비교 회로는,

상기 제2 분리 회로에서 분리된 디지털 신호의 진폭 성분과, 상기 제1 분리 회로에서 분리된 피드백 신호의 진폭 성분을 비교하고, 양 신호의 타이밍 차를 판정하는 제1 비교기와,

상기 제2 분리 회로에서 분리된 디지털 신호의 위상 성분과, 상기 제1 분리 회로에서 분리된 피드백 신호의 위상 성분을 비교하고, 양 신호의 타이밍 차를 판정하는 제2 비교기에 의해 구성되고,

상기 3개의 발진 회로는,

상기 AD 변환 회로에 클럭 신호를 공급하는 제2 가변 발진 회로와,

상기 제1 DA 변환 회로에 클럭 신호를 공급하는 제1 가변 발진 회로와,

상기 제2 DA 변환 회로에 클럭 신호를 공급하는 기준 발진 회로에 의해 구성되고,

상기 제1 가변 발진 회로의 출력은, 상기 제1 비교기의 비교 결과에 기초하여 제어되고,

상기 제2 가변 발진 회로의 출력은, 상기 제2 비교기의 비교 결과에 기초하여 제어됨으로써, 상기 증폭 회로에 입력되는 진폭 성분과 위상 성분과의 타이밍을 정합시키는 것을 특징으로 하는 송신 회로.

#### 청구항 5

제1항에 있어서,

상기 2개의 DA 변환 회로는,

상기 2개의 디지털 신호 중 하나로서 입력된 디지털 신호의 I성분을 아날로그 신호로 변환하는 제1 DA 변환 회로와,

상기 2개의 디지털 신호 중 다른 하나로서 입력된 디지털 신호의 Q성분을 아날로그 신호로 변환하는 제2 DA 변환 회로에 의해 구성되고,

상기 합성 회로는, 상기 아날로그 신호로 변환된 I성분과, 상기 아날로그 신호로 변환된 Q성분을 이용하여 직교

변조를 하는 변조 회로에 의해 구성되고,

상기 제1 분리 회로는 상기 피드백 신호의 I성분과 Q성분을 상기 2개의 신호로서 분리하고,

상기 비교 회로는,

상기 AD 변환 회로에서 변환된 피드백 신호의 I성분과, 상기 입력된 디지털 신호의 I성분을 비교하고, 각 신호의 타이밍 차를 판정하는 제1 비교기와,

상기 AD 변환 회로에서 변환된 피드백 신호의 Q성분과, 상기 입력된 디지털 신호의 Q성분을 비교하고, 각 신호의 타이밍 차를 판정하는 제2 비교기에 의해 구성되고,

상기 3개의 발진 회로는,

상기 AD 변환 회로에 클럭 신호를 공급하는 기준 발진 회로와,

상기 제1 DA 변환 회로에 클럭 신호를 공급하는 제1 가변 발진 회로와,

상기 제2 DA 변환 회로에 클럭 신호를 공급하는 제2 가변 발진 회로에 의해 구성되고,

상기 제1 가변 발진 회로의 출력은, 상기 제1 비교기의 비교 결과에 기초하여 제어되고,

상기 제2 가변 발진 회로의 출력은, 상기 제2 비교기의 비교 결과에 기초하여 제어됨으로써, 상기 변조 회로에 입력되는 I성분과 Q성분과의 타이밍을 정합시키는 것을 특징으로 하는 송신 회로.

## 청구항 6

제3항에 있어서,

상기 제1 가변 발진 회로 또는 제2 가변 발진 회로로부터 클럭 신호가 공급되는 상기 DA 변환 회로 및/또는 상기 AD 변환 회로에 입출력되는 디지털 신호를 유지하는 데이터 유지 회로를 구비하는 것을 특징으로 하는 송신 회로.

## 청구항 7

제1항의 송신 회로를 구비하는 것을 특징으로 하는 무선 통신 장치.

## 청구항 8

입력된 디지털 신호를 분리함으로써 취득된 2개의 디지털 신호 또는 분리되어 입력된 2개의 디지털 신호를, 각각 아날로그 신호로 변환하는 제1 단계와,

상기 제1 단계에서 변환된 상기 아날로그 신호를 합성하는 제2 단계와,

상기 제2 단계에서 합성된 신호의 일부를 피드백 신호로서 추출하는 제3 단계와,

상기 제3 단계에서 추출된 피드백 신호를 디지털 신호로 변환하는 제4 단계와,

상기 제4 단계에서 디지털 신호로 변환된 피드백 신호를 2개의 신호로 분리하는 제5 단계와,

상기 입력된 디지털 신호를 분리함으로써 취득된 2개의 디지털 신호 중 적어도 하나, 또는 상기 분리되어 입력된 2개의 디지털 신호 중 적어도 하나와, 상기 제5 단계에서 분리된 피드백 신호를 비교함으로써, 상기 비교된 신호의 타이밍 차를 판정하는 제6 단계와,

상기 제6 단계에서의 비교 결과에 기초하여, 상기 타이밍 차가 적어지도록, 상기 제1 단계에서의 2개의 디지털 신호의 디지털?아날로그 변환 및 상기 제4 단계에서의 아날로그?디지털 변환 중 적어도 하나의 클럭 신호를 제어하는 제7 단계를 갖는 것을 특징으로 하는 송신 회로의 타이밍 조정 방법.

## 청구항 9

제8항에 있어서,

입력된 디지털 신호를 상기 2개의 디지털 신호로 분리하는 제8 단계를 가지고,

상기 제6 단계는, 상기 제8 단계에서 분리된 디지털 신호와, 상기 제5 단계에서 분리된 피드백 신호를

비교하고, 상기 비교된 신호의 타이밍 차를 판정하고,

상기 제7 단계는, 상기 제6 단계에서의 비교 결과에 기초하여, 상기 타이밍 차가 적어지도록, 상기 제1 단계에서의 2개의 디지털 신호의 디지털?아날로그 변환 및 상기 제4 단계에서의 아날로그?디지털 변환의 클럭 신호 중 어느 하나를 기준으로 하여, 다른 2개를 제어하는 것을 특징으로 하는 송신 회로의 타이밍 조정 방법.

### 청구항 10

제9항에 있어서,

상기 제8 단계는, 상기 입력된 디지털 신호의 진폭 성분과 위상 성분을 상기 2개의 디지털 신호로서 분리하고,

상기 제1 단계는, 상기 진폭 성분을 아날로그 신호로 변환함과 함께, 상기 위상 성분을 아날로그 신호로 변환하고,

상기 제2 단계는, 상기 아날로그 신호로 변환된 진폭 성분과, 상기 아날로그 신호로 변환된 위상 성분을 증폭 회로로 합성하고,

상기 제5 단계는 상기 피드백 신호의 진폭 성분과 위상 성분을 상기 2개의 신호로서 분리하고,

상기 제6 단계는,

상기 제8 단계에서 분리된 디지털 신호의 진폭 성분과, 상기 제5 단계에서 분리된 피드백 신호의 진폭 성분을 비교하고, 양 신호의 타이밍 차를 판정함과 함께,

상기 제8 단계에서 분리된 디지털 신호의 위상 성분과, 상기 제5 단계에서 분리된 피드백 신호의 위상 성분을 비교하고, 양 신호의 타이밍 차를 판정하고,

상기 제7 단계는,

상기 제6 단계의 진폭 성분의 비교 결과에 기초하여, 상기 제2 단계에서의 상기 진폭 성분을 아날로그 신호로 변환할 때에 이용되는 클럭 신호를 제어하고,

상기 제6 단계의 위상 성분의 비교 결과에 기초하여, 상기 제2 단계에서의 상기 위상 성분을 아날로그 신호로 변환할 때에 이용되는 클럭 신호를 제어함으로써, 상기 증폭 회로에 입력되는 진폭 성분과 위상 성분과의 타이밍을 정합시키는 것을 특징으로 하는 송신 회로의 타이밍 조정 방법.

### 청구항 11

제9항에 있어서,

상기 제8 단계는, 상기 입력된 디지털 신호의 진폭 성분과 위상 성분을 상기 2개의 디지털 신호로서 분리하고,

상기 제1 단계는, 상기 진폭 성분을 아날로그 신호로 변환함과 함께, 상기 위상 성분을 아날로그 신호로 변환하고,

상기 제2 단계는, 상기 아날로그 신호로 변환된 진폭 성분과, 상기 아날로그 신호로 변환된 위상 성분을 증폭 회로로 합성하고,

상기 제5 단계는, 상기 피드백 신호의 진폭 성분과 위상 성분을 상기 2개의 신호로서 분리하고,

상기 제6 단계는,

상기 제8 단계에서 분리된 디지털 신호의 진폭 성분과, 상기 제5 단계에서 분리된 피드백 신호의 진폭 성분을 비교하고, 양 신호의 타이밍 차를 판정함과 함께,

상기 제8 단계에서 분리된 디지털 신호의 위상 성분과, 상기 제5 단계에서 분리된 피드백 신호의 위상 성분을 비교하고, 양 신호의 타이밍 차를 판정하고,

상기 제7 단계는,

상기 제6 단계의 진폭 성분의 비교 결과에 기초하여, 상기 제2 단계에서의 상기 진폭 성분을 아날로그 신호로 변환할 때에 이용되는 클럭 신호를 제어하고,

상기 제6 단계의 위상 성분의 비교 결과에 기초하여, 상기 제4 단계에서의 피드백 신호를 디지털 신호로 변환할

때에 이용되는 클럭 신호를 제어함으로써, 상기 증폭 회로에 입력되는 진폭 성분과 위상 성분과의 타이밍을 정합시키는 것을 특징으로 하는 송신 회로의 타이밍 조정 방법.

## 청구항 12

제8항에 있어서,

상기 제1 단계는,

상기 2개의 디지털 신호 중 하나로서 입력된 디지털 신호의 I성분을 아날로그 신호로 변환함과 함께, 상기 2개의 디지털 신호 중 다른 하나로서 입력된 디지털 신호의 Q성분을 아날로그 신호로 변환하고,

상기 제2 단계는 상기 아날로그 신호로 변환된 I성분과, 상기 아날로그 신호로 변환된 Q성분을 직교 변조 회로에 의해 합성하고,

상기 제5 단계는 상기 피드백 신호의 I성분과 Q성분을 상기 2개의 신호로서 분리하고,

상기 제6 단계는,

상기 제4 단계에서 변환된 피드백 신호의 I성분과, 상기 입력된 디지털 신호의 I성분을 비교하고, 각 신호의 타이밍 차를 판정함과 함께,

상기 제4 단계에서 변환된 피드백 신호의 Q성분과, 상기 입력된 디지털 신호의 Q성분을 비교하고, 각 신호의 타이밍 차를 판정하고,

상기 제7 단계는,

상기 제6 단계의 I성분의 비교 결과에 기초하여, 상기 제2 단계에서의 상기 I성분을 아날로그 신호로 변환할 때에 이용되는 클럭 신호를 제어하고,

상기 제6 단계의 Q성분의 비교 결과에 기초하여, 상기 제2 단계에서의 상기 Q성분을 아날로그 신호로 변환할 때에 이용되는 클럭 신호를 제어함으로써, 상기 변조 회로에 입력되는 I성분과 Q성분과의 타이밍을 정합시키는 것을 특징으로 하는 송신 회로의 타이밍 조정 방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

[0048] 본 발명은, 폐 류프의 피드백 제어에 의해 송신 신호의 타이밍을 조정하는 기능을 구비하는 송수신기에 관한 것으로, 특히, EER 방식을 채용하고, r(진폭) 성분과 θ(위상) 성분의 송신 타이밍을 조정하는 송수신기에 관한 것이다.

[0049] 휴대 전화를 비롯한 무선 통신 시스템의 기지국 및 단말에 탑재되는 송신기에서는, 송신 신호를 2계통으로 분리하고, 각각에 처리를 행한 후, 다시 합성하여 송신 출력으로 하는 방법이 개발되어 있다. 이와 같은 방법으로서는, 예를 들면 송신 신호를 I신호와 Q신호로 분리하여 처리하는 방법이나, r(진폭) 성분과 θ(위상) 성분으로 분리하여 처리하는 EER(Envelope Elimination and Restoration) 방식이 알려져 있다.

[0050] 그러나 이와 같은 신호를 2계통으로 분리하여 처리하는 경우, 처리 회로의 배치상, 각 처리 계통의 신호 경로 길이에 차가 있으면 신호 전파 지연 시간에 차가 발생한다. 또한 분리된 각 신호의 처리 회로가 다르면, 신호 처리 시간에 차가 발생한다. 이에 따라, 신호를 다시 합성할 때의 타이밍이 어긋나게 되고, 신호 품질이 열화 한다.

[0051] 특히, EER 방식은, r신호에 대해서는 전원 전압 변조를 행하고, θ신호에 대해서는 주파수 변환을 행한 후, 효율이 높은 포화형의 전력 증폭기(파워 앤프)에서 다시 합성한다(비특허 문헌1). 통신 장치 전체의 소비 전력 중에서, 송신 신호를 증폭하는 파워 앤프의 소비 전력이 차지하는 비율이 매우 크기 때문에, 파워 앤프를 고효율화하는 것이 기술 과제로 되어 있지만, EER 방식은 효율이 높은 포화형의 파워 앤프를 사용하기 때문에, 이

과제를 해결하고, 통신 장치의 소형?저비용?저전력화를 실현할 수 있을 것으로 생각된다.

[0052] 그러나 EER 방식은 지연량에 차가 발생하기 쉽다는 문제가 있었다.  $r$  성분의 전원 전압 변조 회로가, 예를 들면 직류-직류 변환기(DC-DC 컨버터) 등에 의해 구성되는데 반해,  $\Theta$  신호의 주파수 변환 회로가, 예를 들면 디지털 등에 의해 구성되고, 각각에 사용되고 있는 회로 소자가 크게 다르기 때문에, 신호 처리의 과정에서 발생하는 지연에 의해, 신호를 다시 합성할 때의 타이밍이 어긋나게 되고, 신호 품질이 현저하게 열화한다.

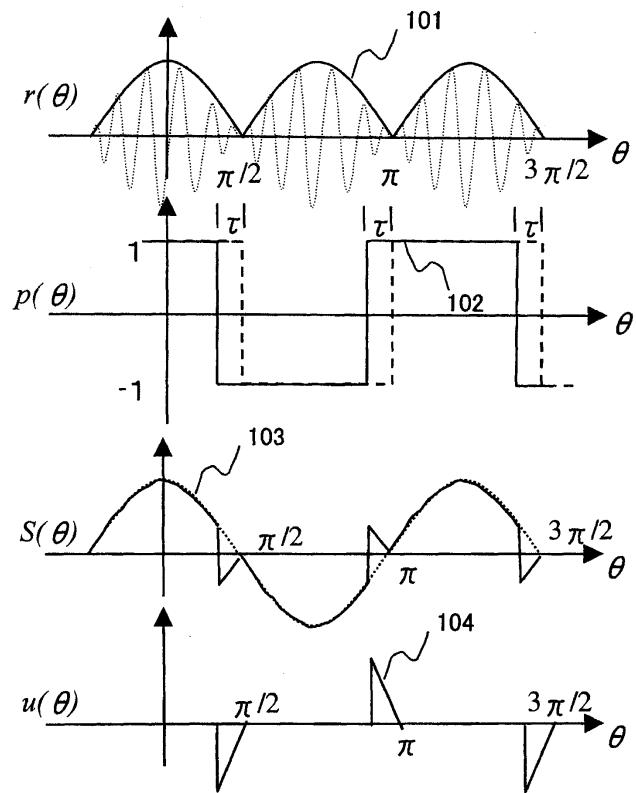

[0053] 도 7은 EER 방식에서  $r$  신호와  $\Theta$  신호의 지연이 송신 신호 품질을 열화시키는 원리를 도시한 과정도이다.

[0054] EER 방식의 송신기에 정현파를 입력하면, 진폭 성분  $r(\Theta)(101)$ 은 정현파를 x축을 따라서 되돌아온 파형으로 되고, 위상 성분  $p(\Theta)(102)$ 는 방형파로 된다. 본래,  $r(\Theta)(101)$ 의 반환 타이밍과  $p(\Theta)(102)$ 의 위상 반전 타이밍은 동기해야 하나,  $p(\Theta)(102)$ 의 타이밍이  $\tau$  만큼 지연된 경우를 생각한다. 이 때 양자를 재합성한 신호  $S(\Theta)(103)$ 는  $\tau$  동안 만큼 위상이 불연속적으로 반전하고, 여러 신호  $u(\Theta)(104)$ 에 날카로운 퍼크를 발생시킨다. 이 여러 신호 성분이 출력 스피리어스(노이즈)로 되어 신호 품질을 열화시키기 때문에, 원하는 신호 품질을 얻기 위해서는, 어떠한 방법으로  $r$  신호와  $\Theta$  신호의 지연차를 조정하고, 양자의 타이밍을 맞출 필요가 있다.

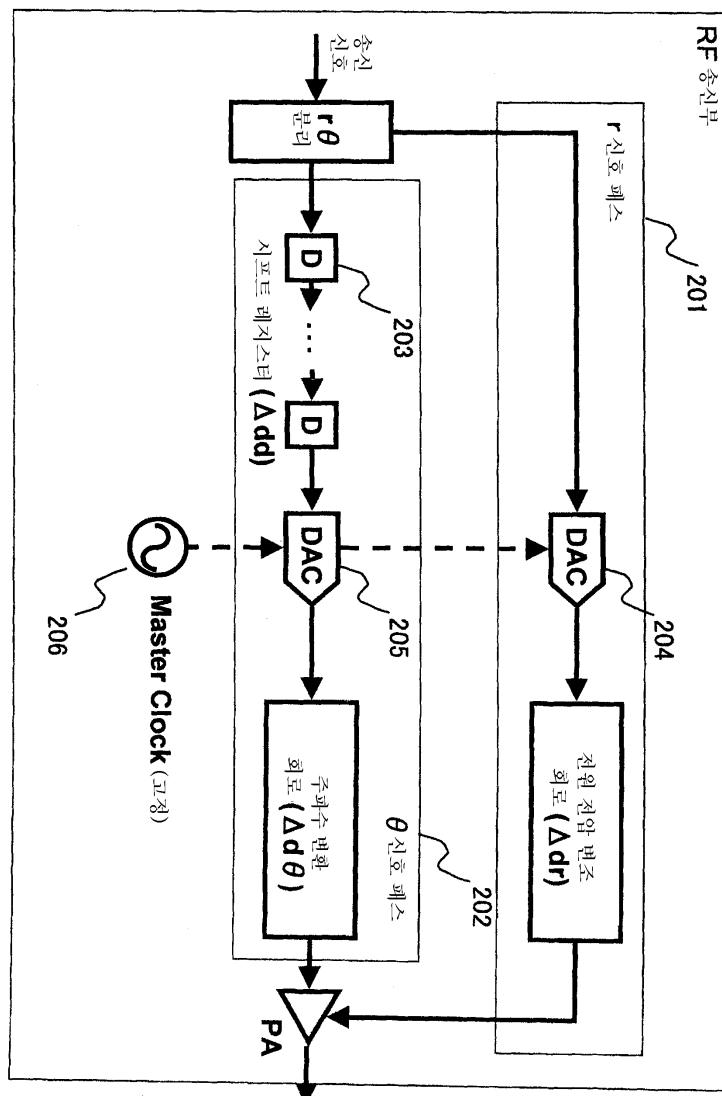

[0055] 도 8은 EER 방식의 송수신기에서의 종래의 타이밍 조정 방법을 설명하는 블록도이다. 도 8에서,  $r$  신호 패스(201)와  $\Theta$  신호 패스(202) 중, 회로 소자에 의한 지연이 적은 쪽(여기서는,  $\Delta dr > \Delta d\Theta$ 로 가정하고,  $\Theta$  측)의 패스에 지연차  $\Delta dr - \Delta d\Theta$ 에 상당하는 지연  $\Delta dd$ 를 삽입하고, 양 패스의 지연량을 맞춘다. 도 8에서는,  $\Delta dd$ 는 디지털 영역에서 삽입되고,  $\Delta dd$ 가 클럭 주기의 정수배이면, 시프트 레지스터 회로(203) 등을 이용하여 단순히  $n$  클럭 만큼 지연시킴으로써 조정할 수 있다.

[0056] 그러나 통상, 지연은 1클럭 미만의 미세한 단위에서도 발생하며, 온도 변화 등의 외적 요인에 의해 시간적으로 변동한다. 비특허 문헌 1에는, 송신 신호를 선형보간하는 디지털 필터에 의해 1/2 클럭 정밀도로 지연을 조정하는 방법이 제안되어 있다. 이 구성에서는, 도 8에 도시한 바와 같이, 양 패스의 디지털/아날로그 변환기(DAC) 204 및 205는 단일의 마스터 클럭원(206)(주파수 고정)에 의해 구동된다.

[0057] 다음으로, EER 이외의 방식의 송수신기에서의 피드백(Fb) 회로를 이용한 타이밍 조정 방법의 예를 설명한다.

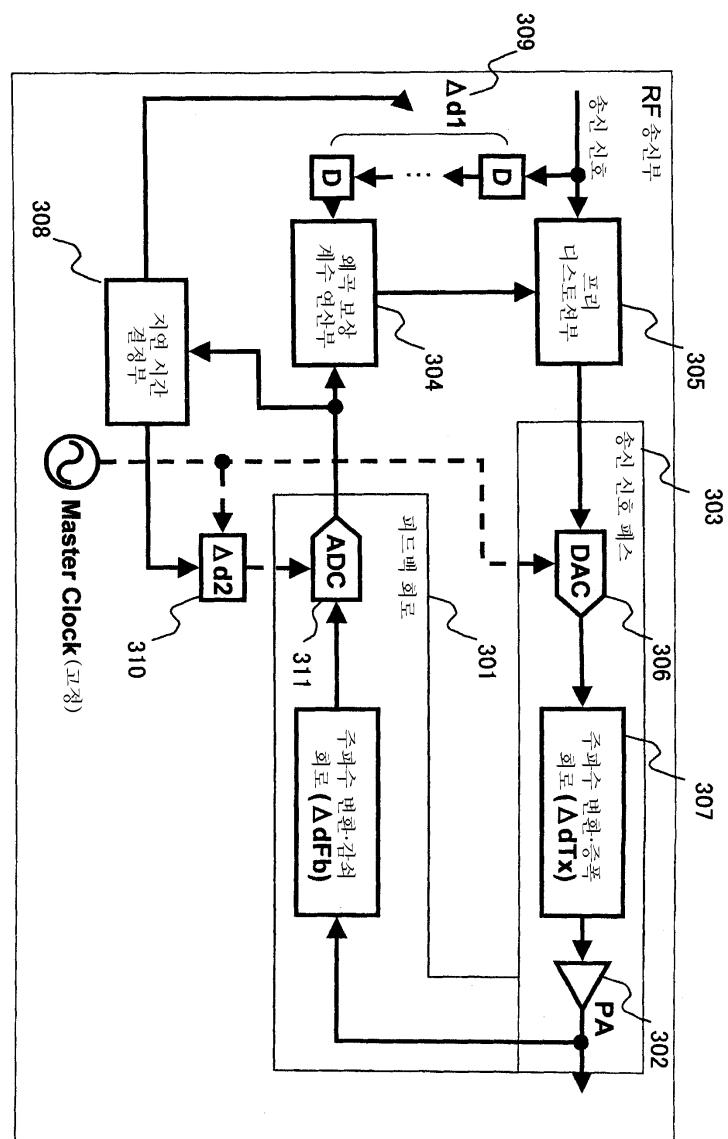

[0058] 도 9는 프리디스토션(왜곡 보상)방식의 송신기에서, 송신 신호와 피드백 신호의 타이밍을 조정하는 방법을 도시한 블록도이다(특허 문헌 1 참조).

[0059] 도 9에서, 피드백 회로(301)는 파워 앰프(PA)(302)에서 증폭된 후의 신호를 수신하고, 원래의 송신 신호와 비교함으로써, 파워 앰프(302)를 포함하는 송신 신호 패스(303)에서 발생하는 비선형 왜곡의 양을 측정한다. 그리고 왜곡 보상 계수 연산부(304)는 그 비선형 왜곡을 취소하는 역 특성의 왜곡을 제공하기 위한 계수를 구하고, 프리디스토션부(305)에 설정한다. 프리디스토션부(305)는 설정된 계수에 맞추어 송신 신호에 비선형 왜곡을 제거하고, DAC(306)를 통해서 주파수 변환 회로(307)로 보낸다.

[0060] 한편, 지연 시간 결정부(308)는 송신 신호와 피드백 신호를 비교할 때의 타이밍을 맞추기 위해, 양자의 지연차를 검출하고, 시프트 레지스터 회로(309)( $\Delta d1$ ) 및 가변 지연 소자(310)( $\Delta d2$ )의 지연량을 결정한다.  $\Delta d1(309)$ 은 송신 신호의 타이밍을 클럭 주기의 정수배만큼 지연시키고,  $\Delta d2(310)$ 은 피드백 신호를 디지털 신호로 변환하는 아날로그/디지털 변환기(ADC)(311)의 클럭 위상을 1/n 클럭 단위로 지연시킨다. 또, 이 구성에서, DAC(306)는 ADC(311)를 구동하는 것과 동일한 마스터 클럭원에 의해 구동되고, 그 클럭 위상을 고정이다.

[0061] (비)특허 문헌 1) Je-Kuan Jau, "Linear Interpolation Scheme for Compensation of Path-Delay Difference in an Envelope Elimination and Restoration Transmitter", pp1072-1075, Proceedings of APMC2001

[0062] (특허 문헌 1) 특개 2001-189685호 공보

### 발명이 이루고자 하는 기술적 과제

[0063] 도 8에 도시한 방법을 이용하면, 1클럭 미만의 단위로 발생하는 지연도 조정 할 수 있지만, 조정량이 연속적이지 않기 때문에, 조정량에 양자화 오차가 남는데다가, 필터의 군지연 특성의 영향으로 지연량이 주파수에 의해 변동되고, 신호 품질이 열화된다는 문제가 있다.  $\Delta dd$ 를 아날로그 영역에서 지연선에 의해 삽입할 수도 있지만, 지연량을 정확하게 발생시키는 것은 곤란하고, 온도 변화 등의 외적 요인에 의한 아날로그 소자의 특성 변동이 크기 때문에, 성능은 좋지 않다. 또한 삽입하는 지연량을 불연속적으로 변화시키면, 그 순간에 송신 신호 파형에 불연속인 변화가 발생하고, 송신 신호의 출력 스피리어스 특성의 악화가 우려된다.

[0064] 도 9에 도시한 방법에서는, 도 8에 도시한 방법과 마찬가지로, 지연량에 양자화 오차가 남는다. 또한 이는 송

신 신호와 피드백 신호의 타이밍을 맞추기 위한 기능으로서, 송신 신호의 2개의 성분 사이의 지연차를 조정하는 기능은 갖지 않기 때문에, 상기의 EER 방식의 과제를 해결할 수는 없다.

[0065] 본 발명은, 상기의 문제점을 감안하여 이루어진 것으로, EER 방식의 송수신기에서, r신호와 Θ신호의 지연차를 간이한 회로로, 또한 고정밀도로 조정하는 방법을 제공하는 것을 목적으로 한다. 또한 EER 방식 이외의 송수신기에서도, I신호와 Q신호와 같이, 다른 지연량을 갖는 경로를 통해 변조된 후, 다시 합성되는 2개의 신호 패스의 지연차를 조정하는 방법을 제공하는 것을 목적으로 한다.

### 발명의 구성 및 작용

[0066] 본 발명은, 입력된 디지털 신호로부터 분리된 2개의 신호 또는 분리되어 입력된 2개의 디지털 신호를, 각각 아날로그 신호로 변환하는 DA 변환 회로와, 상기 DA 변환 회로에서 변환된 상기 아날로그 신호를 합성하는 합성 회로와, 상기 합성된 신호의 일부를 피드백 신호로서 추출하는 분배 회로와, 상기 피드백 신호를 디지털 신호로 변환하는 AD 변환 회로와, 상기 각 DA 변환 회로 및 상기 AD 변환 회로에 동작 클럭 신호를 공급하는 발진 회로와, 상기 AD 변환 회로에서 변환된 피드백 신호를 2개의 신호로 분리하는 제1 분리 회로와, 상기 분리된 입력 신호와, 상기 제1 분리 회로에서 분리된 피드백 신호를 비교하는 비교 회로를 가지고, 상기 발진 회로는 비교 회로에 의한 비교 결과에 기초하여 그 출력을 제어하는 것을 특징으로 한다.

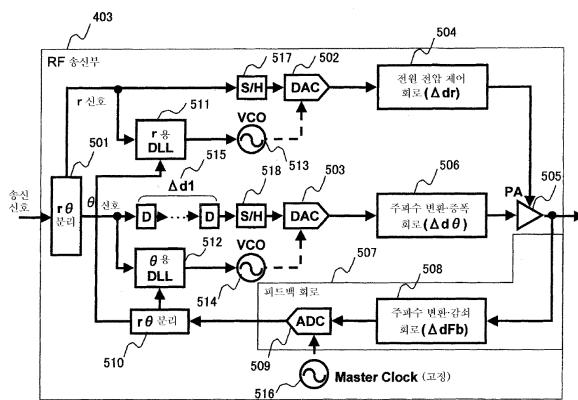

[0067] 도 1은 무선 기지국의 송수신기의 일반적인 구성을 도시한 블록도이다.

[0068] 송수신기는 공중 교환 전화망 또는 패킷 교환 데이터망과 접속되는 인터페이스부(401), 디지털 변복조 처리를 행하는 기저 대역부(402), 송신 신호를 디지털 신호로부터 아날로그 신호로 변환하고, 기저 대역으로부터 고주파(RF) 대역으로 주파수 변환하며, 출력 전력을 증폭하는 RF 송신부(403), 필터와 듀플렉스 등에 의해 구성되는 프론트 엔드부(404), 안테나(405) 및 RF 대역으로부터 기저 대역으로 주파수 변환하고, 필터에서 대역 외 노이즈 성분을 제거한 후, 디지털 신호로 변환하는 RF 수신부(406)에 의해 구성된다. 본 발명은, 특히 RF 송신부(403)의 구성에 관한 것이다.

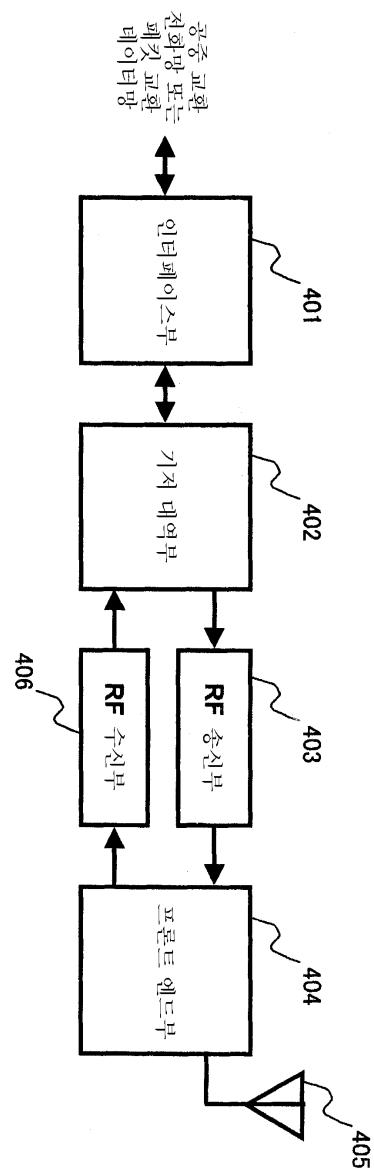

[0069] 도 2는 본 발명의 제1 실시 형태에 의한 RF 송신부(403)의 구성을 도시한 블록도이다.

[0070] 기저 대역부(402)로부터 입력되는 송신 신호는, rΘ 분리 회로(501)에서 r(진폭) 성분과 Θ(위상) 성분으로 분리되고, 각각이 디지털/아날로그 변환기(DAC)(502, 503)에서 아날로그 신호로 변환된다. r신호는 전원 전압 제어 회로(504)에서 파워 앰프(PA)(505)의 전원 전압을 제어하는 신호로 변환되고, 파워 앰프(505)의 전원 단자에 입력된다. 그 결과, 파워 앰프(505)의 출력 신호의 포락선은, r신호의 닮은꼴로 된다. Θ신호는 주파수 변환?증폭 회로(506)로 RF 대역에 주파수 변환(업 컨버트)되고, 전력이 증폭된 후, 파워 앰프(505)의 신호 입력 단자에 입력된다.

[0071] 파워 앰프(505)의 출력의 일부는 분배기(커플러 등, 도시 생략)에 의해 피드백 회로(507)에 분배된다. 피드백 회로(507)에서는 주파수 변환?감쇠 회로(508)에서 전력이 약해진 후, 기저 대역으로 주파수 변환(다운 컨버트)되고, 아날로그/디지털 변환기(ADC)(509)에 의해 디지털 신호로 변환된다. 그 후, 피드백 신호는 다시 rΘ 분리 회로(510)에서 r(진폭) 성분과 Θ(위상) 성분으로 분리되고, r성분은 r신호용 DLL(Delay Locked Loop) 회로(511)에서 송신 신호의 r성분과 비교되고, Θ성분은 Θ신호용 DLL 회로(512)에서 송신 신호의 Θ성분과 비교된다.

[0072] DLL 회로(511 및 512)는, 후술하는 회로 구성에 의해, 송신 신호의 위상과 피드백 신호의 위상 중 어느 쪽이 빠른가(또는, 지연되고 있는가)를 판정하고, r신호용 DAC(502)에 클럭 신호를 공급하는 발진기(VCO)(513) 및 Θ신호용 DAC(503)에 클럭 신호를 공급하는 발진기(VCO)(514)의 출력 위상을, 상기 판정 결과가 수속하는(송신 신호와 피드백 신호의 타이밍이 일치하는) 방향으로 제어한다. 또한 피드백 신호용 ADC(509)의 클럭은 출력 주파수가 고정된 발진기(마스터 클럭원)(516)로부터 공급된다.

[0073] 또, r신호의 경로와 Θ신호의 경로의 지연차가 1클럭 이상인 경우, 그 정수 부분(도 2의 예에서는,  $\Delta dr > \Delta d\Theta$ )로 가정하고,  $\Delta dr - \Delta d\Theta$ 를 클럭 주기로 계산했을 때의 몫에 상당)은 시프트 레지스터 회로(515)에서 조정하고, 상기 VCO(513 및 514)를 제어하여  $\Delta dr - \Delta d\Theta$ 의 잉여 부분을 조정한다. 이 때문에, VCO(513 및 514)의 위상(주파수)의 제어 범위를 넓힐 필요가 없고, VCO의 출력 신호 특성(예를 들면, C/N)을 향상시킬 수 있다.

[0074] 또한 DAC(502 및 503)은, 각각의 입력 신호가 변화하는 타이밍과 무관하게, VCO(513 및 514)에 의해 생성된 클럭 신호로 동작하기 때문에, 입력 신호가 변화하는 타이밍에서 그 입력 신호를 수신하는 경우가 있다. 이 때, 입력 신호의 각 비트가 동시에 변화한다고는 할 수 없으며, 수신하는 타이밍에 따라서는 잘못된 데이터를 수신

하는 경우가 있다. 이를 방지하기 위해, r신호 패스와 θ신호 패스의 DAC(502 및 503)의 입력측에는, 샘플?홀드 회로(S/H)(517 및 518)을 설치하고, 샘플 ?홀드 회로(517 및 518)에서 데이터를 유지함으로써, DAC(502 및 503)에 입력되는 클럭 타이밍이 변하더라도, DAC(502 및 503)에 입력되는 데이터가 빠져나가지 않도록 하고 있다.

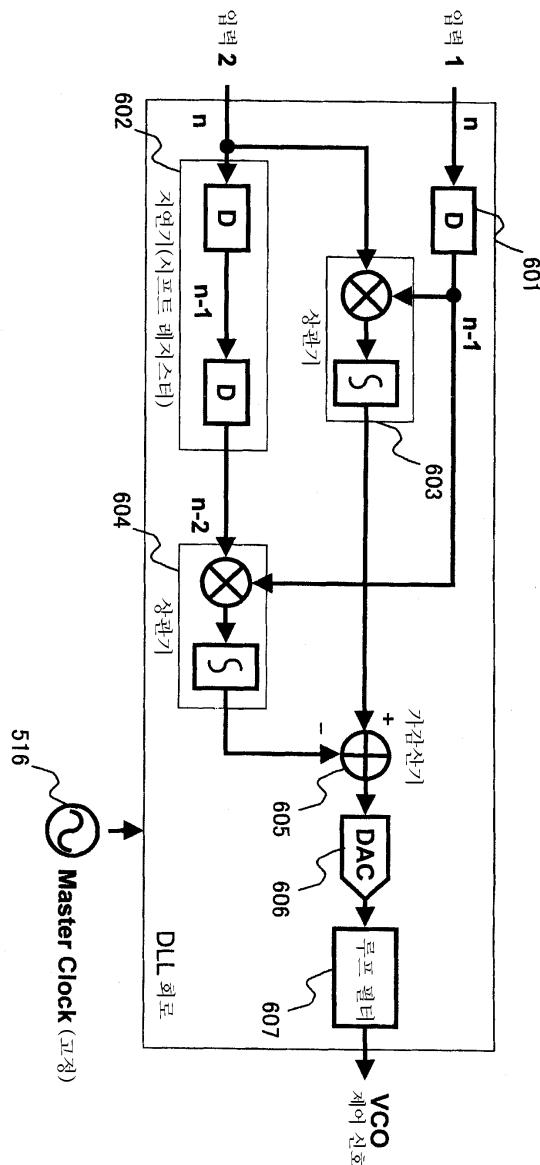

[0075] 도 3은 본 발명에서 사용하는 DLL 회로(511 및 512)의 구성을 도시한 블록도이다. 이 회로 구성은, 예를 들면 특개 2003-273663호 공보에 개시되어 있다.

[0076] DLL 회로(511)에서는 입력 1이 송신 신호의 r성분, 입력 2가 피드백 신호의 r성분에 상당하고, VCO 제어 신호 출력은 VCO(513)에 접속된다. DLL 회로(512)에서는 입력 1이 송신 신호의 θ성분, 입력 2가 피드백 신호의 θ성분에 상당하며, VCO 제어 신호 출력은 VCO(514)에 접속된다.

[0077] DLL 회로에서는 마스터 클럭원(516)에 동기하여 동작하는 시프트 레지스터(601 및 602)를 이용하여 입력 신호를 지연시킨다. 상관기(603)에서는 입력 1의 (n-1)번째의 샘플(도 4의 701)과 입력 2의 n번째의 샘플(도 4의 702)의 전력값을 승산하고, 그 결과를 소정의 구간에 걸쳐 적분한다. 상관기(604)에서는 입력 1의 (n-1)번째의 샘플(도 4의 701)과 입력 2의 (n-2)번째의 샘플(도 4의 703)의 전력값을 승산하고, 그 결과를 소정의 구간에 걸쳐 적분한다. 그 후, 가감산기(605)에서 각각의 적분 결과의 차를 구하여, DAC(606)에서 그 차를 아날로그 신호로 변환하고, 루프 필터(607)를 통해서 VCO(513 또는 514)에 입력한다.

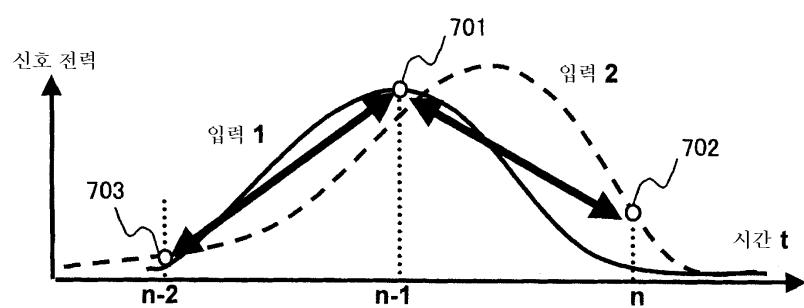

[0078] 도 4는 입력 1 및 입력 2의 신호 전력의 시간 변화의 예를 도시한 과정도이다.

[0079] 가감산기(605)에서 각각의 적분 결과의 차를 구하면, 샘플(701)의 값은 양자에 공통으로, 샘플 702과 703을 비교하면, 702쪽의 값이 크기 때문에, 상관기(603)의 연산 결과가 크게 되고, 가감산기(605)의 출력은 플러스 값이 된다. 이것은 도 4에 도시한 바와 같이, 입력 1의 송신 타이밍이 입력 2의 송신 타이밍에 비교하여 지연되어 있음을 의미한다. 이 때문에, DLL 회로(511, 512)의 출력 전압(VCO 제어 신호의 전압)을 올리고, VCO(513 및 514)의 출력 주파수를 높게 한다. 이것에 의해, DAC(502, 503)이 입력 1(송신 신호의 r신호, θ신호)을 수신하는 타이밍을 빠르게 하고, 입력 2(피드백 신호의 r신호, θ신호)의 타이밍에 가까워지는 방향으로 제어할 수 있다.

[0080] 제1 실시 형태에 의하면, r신호의 송신 타이밍과 θ신호의 송신 타이밍이 2개의 VCO의 출력 위상에 의해 독립적으로 제어되기 때문에, 서로의 안정성에 영향을 미치기 어렵다. 한편으로, 동일한 피드백 신호의 타이밍을 제어 목표로 하기 때문에, 결과적으로 양자의 타이밍을 정합할 수 있다.

[0081] 또한 종래의 지연량을 미리 설정하는 방법에 비교하여, 온도 변화, 경년 변화에 의한 변화가 있더라도 지연량을 정합할 수 있다.

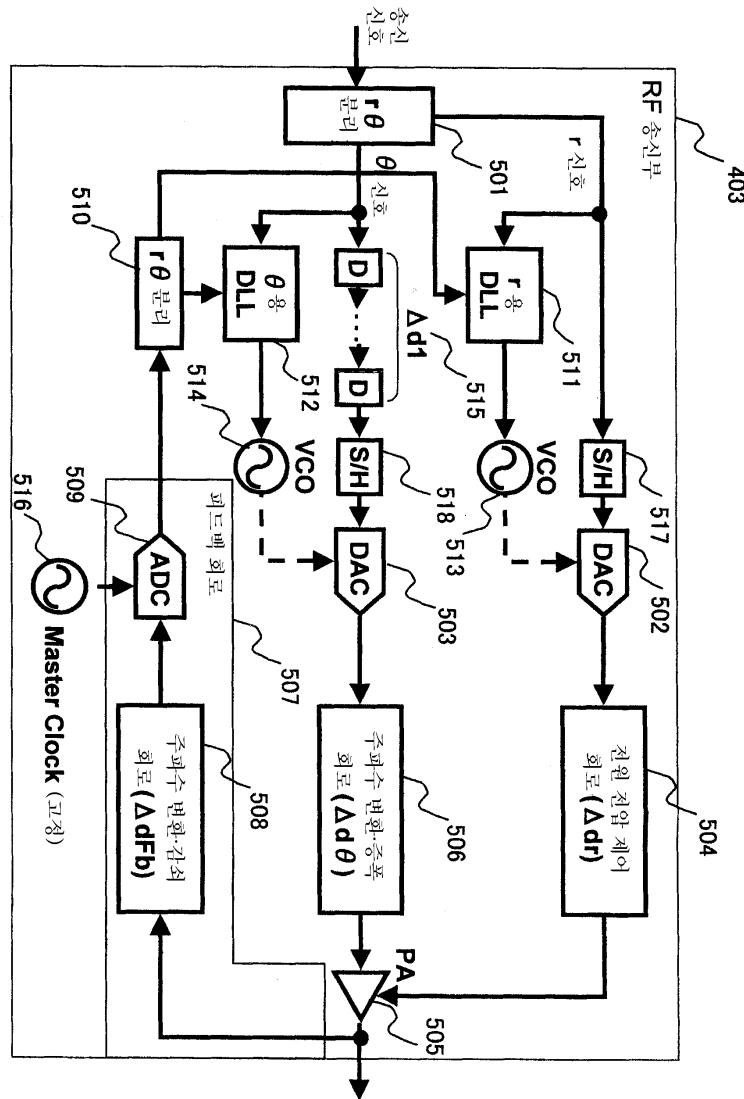

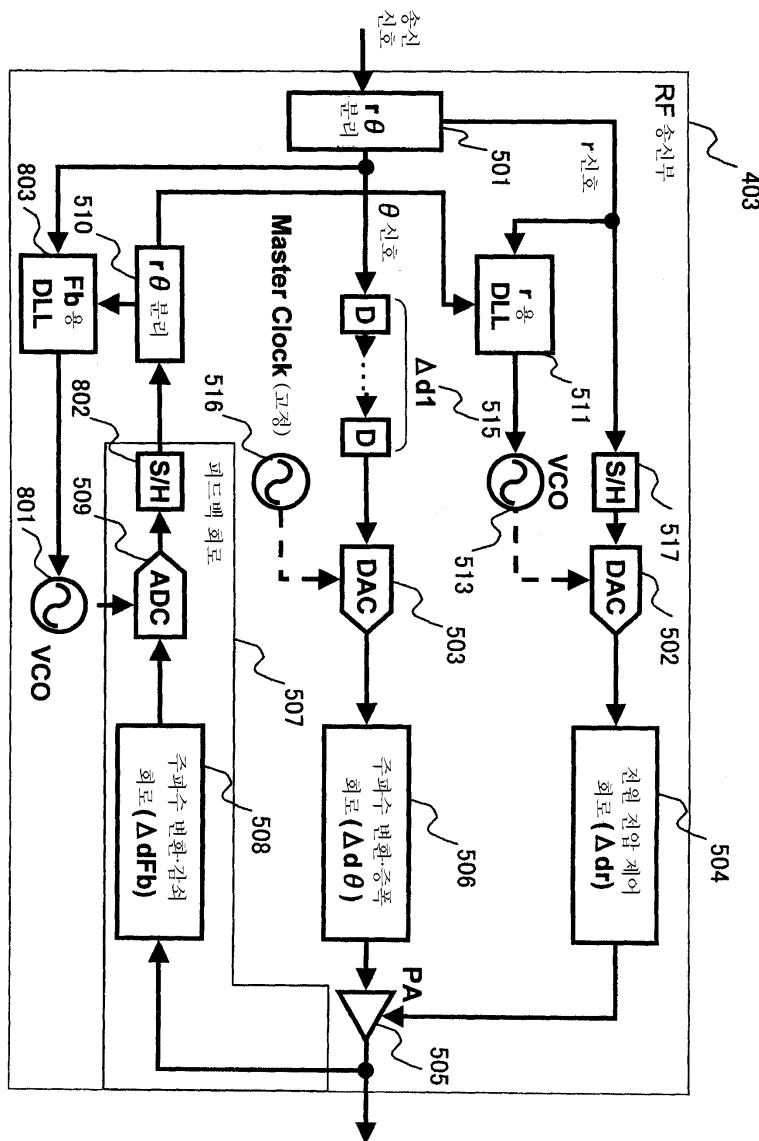

[0082] 도 5는 본 발명의 제2 실시 형태에 의한 RF 송신부(403)의 구성을 도시한 블록도이다.

[0083] 본 실시의 형태에서는, θ신호의 송신 타이밍을 기준으로 피드백 신호의 타이밍을 조정하고, 그 피드백 신호의 타이밍을 기준으로 r신호의 타이밍을 조정한다. 본 실시의 형태의 RF 송신부(403)의 타이밍 조정 회로 이외의 기본 구성은 상술한 제1 실시 형태(도 2)와 공통된다. 본 실시의 형태 중, 제1 실시 형태와 공통되는 부분에 대해서는, 상세한 설명을 생략한다.

[0084] 본 실시의 형태에서는, θ신호용 DAC(503)의 클럭 신호를 마스터 클럭원(516)으로부터 공급하고, r신호용 DAC(502) 및 피드백 신호용 ADC(509)의 클럭 신호를 각각 VCO(513), VCO(801)로부터 공급한다. 피드백 신호는 ADC(509)에서 샘플링하여 디지털화한 후, 샘플?홀드 회로(802)에서 값을 유지하고, 마스터 클럭으로 동작하는 r θ 분리 회로(510)가 잘못된 값을 수신하지 않도록 한다.

[0085] 그 후, rθ 분리 회로(510)에서 r(진폭) 성분과 θ(위상) 성분으로 나누어지고, r성분은 r신호용 DLL 회로(511)에서 송신 신호의 r성분과 비교되고, θ성분은 피드백 신호용 DLL 회로(803)에서 송신 신호의 θ성분과 비교된다.

[0086] DLL 회로(511 및 803)은, 전술한 회로 구성에 의해 송신 신호의 위상과 피드백 신호의 위상 중 어느 쪽이 빠른가(또는, 지연되고 있는가)를 판정하고, r신호용 DAC(502)에 클럭 신호를 공급하는 VCO(513) 및 피드백 신호용 ADC(509)에 클럭 신호를 공급하는 VCO(801)의 출력 위상을, 상기 판정 결과가 수속하는(송신 신호와 피드백 신호의 타이밍이 일치하는) 방향으로 제어한다. 또한 θ신호용 DAC(503)의 클럭은 출력 주파수가 고정된 마스터 클럭원(516)으로부터 공급된다.

- [0087] 또, 제1 실시 형태와 마찬가지로, r신호의 경로와 θ신호의 경로의 지연차가 1클럭 이상인 경우, 그 정수 부분(도 5의 예에서는,  $\Delta dr > \Delta d\theta$ 로 가정하고,  $\Delta dr - \Delta d\theta$ 를 클럭 주기로 계산했을 때의 몫에 상당)은 시프트 레지스터 회로(515)에서 조정하고, 상기 VCO(513 및 801)을 제어하여  $\Delta dr - \Delta d\theta$ 의 잉여 부분을 조정한다. 이 때문에, VCO(513 및 514)의 위상(주파수)의 제어 범위를 넓힐 필요가 없고, VCO의 출력 신호 특성(예를 들면, C/N)을 향상시킬 수 있다.

- [0088] DLL 회로(511 및 803)의 구성은, 제1 실시 형태와 마찬가지이다(도 3 참조). 여기서, DLL 회로(511)에서는 입력 1이 송신 신호의 r성분, 입력 2가 피드백 신호의 r성분에 상당하고, VCO 제어 신호 출력은 VCO(513)에 접속된다. DLL 회로(803)에서는, 입력 1이 송신 신호의 θ성분, 입력 2가 피드백 신호의 θ성분에 상당하고, VCO 제어 신호 출력은 VCO(801)에 접속된다.

- [0089] 또, 본 실시의 형태는 θ신호용 DAC(503)의 클럭을 마스터 클럭원(516)으로부터 공급하고, r신호용 DAC(502)의 클럭을 VCO(513)로부터 공급하는 구성으로 했지만, r신호용 DAC(502)의 클럭을 마스터 클럭원(516)으로부터 공급하고, θ신호용 DAC(503)의 클럭을 VCO(513)로부터 공급하는 구성으로 해도 된다. 그러나 일반적으로 r성분의 변동량보다 θ성분의 변동량이 작기 때문에, 도 5에 도시한 구성이 이 변형에보다 높은 안정도를 얻을 수 있다. 이 경우, DLL(511)에는 송신 신호로부터 분리한 θ신호와, 피드백 신호로부터 분리한 θ신호를 입력하고, DLL(803)에는 송신 신호로부터 분리한 r신호와, 피드백 신호로부터 분리한 r신호를 입력한다.

- [0090] 본 실시의 형태에 의하면, 변동량이 작은 θ성분을 기준으로 하여 피드백 신호의 타이밍을 조정함으로써, 피드백 신호의 복조 정밀도가 향상된다. 또한 송신 신호의 일축(바람직하게는 변동량이 작은 θ신호)에 마스터 클럭을 공급하기 때문에, 안정도가 높아진다.

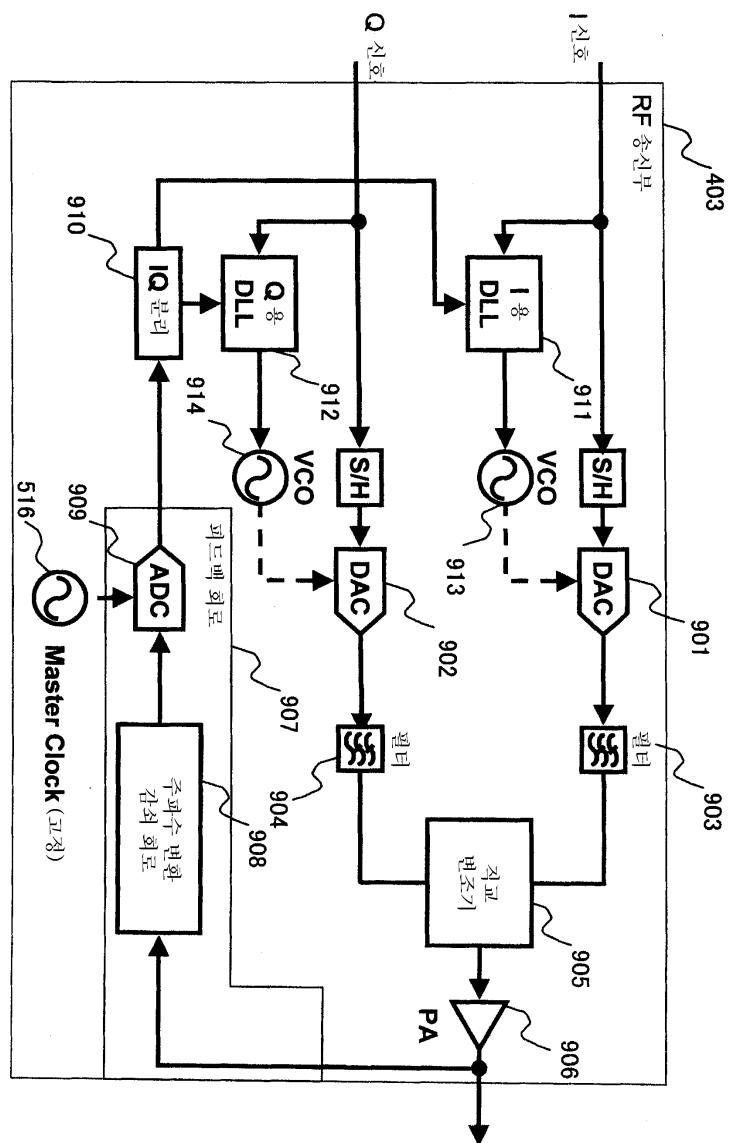

- [0091] 도 6은 본 발명의 제3 실시 형태에 의한 RF 송신부(403)의 구성을 도시한 블록도이다.

- [0092] 본 실시의 형태는, EER 방식 이외의 송수신기에서 I신호와 Q신호가 다른 지연량을 갖는 경로를 통해 변조되는 경우에, 2개의 신호 패스의 지연차를 조정하는 방법의 하나이며, 본 발명이 EER 방식 이외의 송신기에도 적용할 수 있음을 나타낸다. 본 실시의 형태의 RF 송신부(403) 이외의 부분의 구성은, 제1 실시 형태와 공통된다(도 1 참조). 본 실시의 형태 중, 제1 실시 형태와 공통되는 부분에 대해서는, 상세한 설명을 생략한다.

- [0093] 기저 대역부(402)로부터 수취한 I신호와 Q신호는, DAC(901 및 902)에서 아날로그 신호로 변환되고, 필터(903 및 904)를 통해서 직교 변조기(905)에서 직교 변조되어 I신호와 Q신호가 합성되고, 주파수 변환되며, 파워 앰프(906)의 신호 입력 단자에 입력된다. 파워 앰프(906)의 출력의 일부는 분배기(커플러 등, 도시 생략)에 의해 피드백 회로(907)에 분배된다. 피드백 회로(907)에서는 주파수 변환?감쇠 회로(908)에서 전력이 약해진 후, 기저 대역으로 주파수 변환(다운 컨버트)되고, ADC(909)에서 디지털 신호로 변환된다. 이 피드백 신호는 다시 IQ 분리 회로(910)에서 직교 복조되고, I성분은 I신호용 DLL 회로(911)에서 송신 신호의 I성분과 비교되고, Q성분은 Q신호용 DLL 회로(912)에서 송신 신호의 Q성분과 비교된다.

- [0094] DLL 회로(911 및 912)는, 전술한 회로 구성에 의해 송신 신호와 피드백 신호 중 어느 쪽이 빠른가(또는 지연되고 있는가)를 판정하고, I신호용 DAC(901)에 클럭 신호를 공급하는 발진기(VCO)(913) 및 Q신호용 DAC(902)에 클럭 신호를 공급하는 VCO(914)의 출력 위상을, 상기 판정 결과가 수속하는(송신 신호와 피드백 신호의 타이밍이 일치하는) 방향으로 제어한다. 또한 피드백 신호용 ADC(909)의 클럭은 출력 주파수가 고정된 발진기(마스터 클럭원)(516)로부터 공급된다.

- [0095] 또한 DAC(901 및 902)의 입력측에는 각각의 입력 신호를 유지하는 샘플?홀드(S/H) 회로가 설치된다.

- [0096] DLL 회로(911 및 912)의 구성은, 제1 실시 형태와 마찬가지이다(도 3 참조). 여기서, DLL 회로(911)에서는 입력 1이 송신 신호의 I성분, 입력 2가 피드백 신호의 I성분에 상당하고, VCO 제어 신호 출력은 VCO(913)에 접속된다. DLL 회로(912)에서는 입력 1이 송신 신호의 Q성분, 입력 2가 피드백 신호의 Q성분에 상당하고, VCO 제어 신호 출력은 VCO(914)에 접속된다.

- [0097] 일반적으로, I성분과 Q성분과의 지연차는 EER 방식에서의 r신호와 θ신호의 지연차에 비교하면 작고, 무선 통신 시스템에 따라서는 문제가 되지 않는 경우도 많다. 그러나 최근에 광대역화에 수반하여, 64QAM(Quadrature Amplitude Modulation)을 비롯한 다수 변조가 많이 이용되게 되면, IQ 변조 방식에서도 한층 선형성을 높일 필요가 생기고, 본 실시의 형태의 중요성이 증가할 것으로 생각된다.

## 발명의 효과

- [0098] 본 발명에 의하면, 종래의 방법과 같이 r신호와 θ신호의 지연차를 직접 측정하는 대신에, 송신 신호와 피드백 신호의 타이밍의 상대 관계(지연/빠름)를 판단하기 위해, 비교 수단을 간소한 구성으로 실현할 수 있다.

- [0099] 또한 클럭 신호 발생 수단을 VCO(Voltage Controlled Oscillator)로 함으로써, 지연량의 변화에 연속적으로 추종할 수 있기 때문에, 종래의 방법과 비교하여 송신 신호의 출력 스펙트리어스 특성을 개선할 수 있다.

- [0100] 그 결과, EER 방식의 송수신기의 출력 신호 품질을 개선하고, 파워 앰프의 고효율화를 실현한다. 또한 EER 방식 이외의 송수신기에서도, 제어 회로의 면적이나 소비 전력을 낮게 억제하면서, 출력 신호 품질을 개선할 수 있다.

- [0101] 본 발명은, 휴대 전화를 비롯한 무선 통신 시스템의 기지국 또는 단말의 송수신기에 이용할 수 있으며, 출력 신호의 과형 품질(선형성) 향상에 기여한다. 신호의 품질 향상에 수반하여, 효율이 높은 EER 방식 또는 포화성이 높은 파워 앰프를 채용할 수 있기 때문에, 소비 전력의 저감에 기여한다.

### 도면의 간단한 설명

- [0001] 도 1은 무선 통신 시스템에 사용되는 송수신기의 일반적인 시스템 구성을 도시한 블록도.

- [0002] 도 2는 본 발명의 제1 실시 형태에 의한 RF 송신부(403)의 구성을 도시한 블록도.

- [0003] 도 3은 본 발명에서 사용하는 DLL 회로(511 및 512)의 구성을 도시한 블록도.

- [0004] 도 4는 DLL 회로의 입력 1 및 입력 2의 신호 전력의 시간 변화의 예를 도시한 과형도.

- [0005] 도 5는 본 발명의 제2 실시 형태에 의한 RF 송신부(403)의 구성을 도시한 블록도.

- [0006] 도 6은 본 발명의 제3 실시 형태에 의한 RF 송신부(403)의 구성을 도시한 블록도.

- [0007] 도 7은 EER 방식에서 r신호와 θ신호의 지연차가 송신 신호 품질을 열화시키는 원리를 도시한 과형도.

- [0008] 도 8은 종래의 EER 방식의 송수신기의 구성을 도시한 블록도.

- [0009] 도 9는 종래의 프리디스토션 방식의 송신기의 구성을 도시한 블록도.

- [0010] <도면의 주요 부분에 대한 부호의 설명>

- [0011] 101 : 전폭 과형

- [0012] 102 : 위상 과형

- [0013] 103 : 출력 과형(합성 후)

- [0014] 104 : 에러 신호

- [0015] 201 : r신호 패스

- [0016] 202 : θ신호 패스

- [0017] 203, 309, 515, 601, 602 : 시프트 레지스터 회로

- [0018] 204, 205, 306, 502, 503, 606, 901, 902 : 디지털/아날로그 변환기(DAC)

- [0019] 206, 516 : 마스터 클럭원

- [0020] 301, 507, 907 : 피드백 회로

- [0021] 302, 505, 906 : 파워 앰프(PA)

- [0022] 303 : 송신 신호 패스

- [0023] 304 : 왜곡 보상 계수 연산부

- [0024] 305 : 프리디스토션부

- [0025] 307, 506 : 주파수 변환?증폭 회로

- [0026] 308 : 지연 시간 결정부

- [0027] 310 : 가변 지연 소자

- [0028] 401 : 인터페이스부

- [0029] 402 : 기저 대역부

- [0030] 403 : RF 송신부

- [0031] 404 : 프론트 엔드부

- [0032] 405 : 안테나

- [0033] 406 : RF 수신부

- [0034] 501, 510 : rθ 분리 회로

- [0035] 504 : 전원 전압 제어 회로

- [0036] 508, 908 : 주파수 변환?감쇠 회로

- [0037] 509, 909 : 아날로그/디지털 변환기(ADC)

- [0038] 511, 512, 803, 911, 912 : DLL 회로

- [0039] 513, 514, 801, 913, 914 : VCO

- [0040] 517, 518, 802 : 샘플 홀드(S/H) 회로

- [0041] 603, 604 : 상관기

- [0042] 605 : 가감산기

- [0043] 607 : 루프 필터

- [0044] 701, 702, 703 : 비교 대상이 되는 샘플

- [0045] 903, 904 : 필터

- [0046] 905 : 직교 변조기

- [0047] 910 : IQ 분리 회로

도면

도면1

도면2

도면3

도면4

도면5

도면6

## 도면7

도면8

도면9