(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3545472号

(P3545472)

(45) 発行日 平成16年7月21日(2004.7.21)

(24) 登録日 平成16年4月16日(2004.4.16)

(51) Int.C1.<sup>7</sup>

F 1

H 03 K 3/037

H 03 K 3/037

Z

請求項の数 2 (全 5 頁)

(21) 出願番号 特願平6-310211

(22) 出願日 平成6年12月14日(1994.12.14)

(65) 公開番号 特開平8-167833

(43) 公開日 平成8年6月25日(1996.6.25)

審査請求日 平成13年9月26日(2001.9.26)

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100080001

弁理士 筒井 大和

(74) 代理人 100075096

弁理士 作田 康夫

(72) 発明者 篠崎 雅雄

茨城県日立市大みか町七丁目1番1号

株式会社 日立製作所 日立

研究所内

(72) 発明者 岩村 ▲将▼弘

茨城県日立市大みか町七丁目1番1号

株式会社 日立製作所 日立

研究所内

最終頁に続く

(54) 【発明の名称】 ラッチ回路

## (57) 【特許請求の範囲】

## 【請求項 1】

クロック信号を遅延させる第1の遅延回路と、

二つに分流された入力データの一方を遅延させる第2の遅延回路と、

前記二つに分流された入力データの他方の前記入力データと前記第2の遅延回路によって

遅延された入力データを入力とし、前記第1の遅延回路によって遅延されたクロック信号

により入力を選択するセレクタ回路と、

前記セレクタ回路の出力をデータ入力とし、前記遅延されたクロック信号をクロック入力

として用いるD型フリップフロップとを有し、

前記セレクタ回路は前記D型フリップフロップに入力されるクロック信号と同じクロック

信号により入力データを選択するラッチ回路。

## 【請求項 2】

請求項1において、前記クロック信号の遅延を0としたラッチ回路。

## 【発明の詳細な説明】

## 【0001】

## 【産業上の利用分野】

本発明はラッチ回路に係り、特に、セットアップタイムおよびホールドタイムを短くできるラッチ回路に関する。

## 【0002】

## 【従来の技術】

ラッチ回路では、クロック変化以前にラッチ回路に入力が確定している必要があり、これに必要な時間はセットアップタイムと呼ばれる。一方、クロック変化後にもホールドタイムと呼ばれる所定時間入力データを保持しなければならない。このセットアップタイムとホールドタイムを合わせた期間がラッチ回路に対する入力データの有効な期間となる。

#### 【0003】

##### 【発明が解決しようとする課題】

高速システムでは、この入力データの有効な期間は短くすることが要求されるが、セットアップタイムとホールドタイムの最小値はラッチ回路の方式、温度、電源電圧の変動、デバイスばらつきなどにより決定されるものであり、セットアップタイムとホールドタイムがともに短いラッチ回路を実現することは困難であった。

10

#### 【0004】

本発明の目的はセットアップタイムおよびホールドタイムの短いラッチ回路を提供することにある。

#### 【0005】

##### 【課題を解決するための手段】

本発明の特徴は、D型フリップフロップの入力として入力データ信号と遅延された入力データ信号を入力としたセレクタ回路の出力を用いる点にある。

#### 【0006】

##### 【作用】

入力データ信号と遅延された入力データ信号をクロックにより選択してラッチすることができる。

20

#### 【0007】

##### 【実施例】

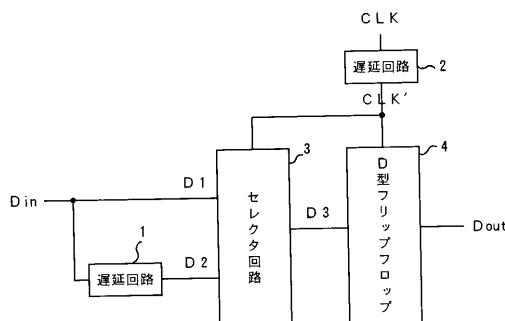

以下、本発明について図面を用いて説明する。図1は第一の実施例の回路図である。入力信号Dinは二つに分流され、セレクタ回路入力信号D1は入力データ信号Dinがそのまま入力され、セレクタ回路入力信号D2には入力データ信号Dinが遅延回路1により遅延されて入力される。セレクタ回路3の出力はD型フリップフロップ4に入力される。入力クロック信号CLKは遅延回路2により遅延され、遅延されたクロック信号CLKはセレクタ回路3とD型フリップフロップ4のクロックに用いられる。

#### 【0008】

30

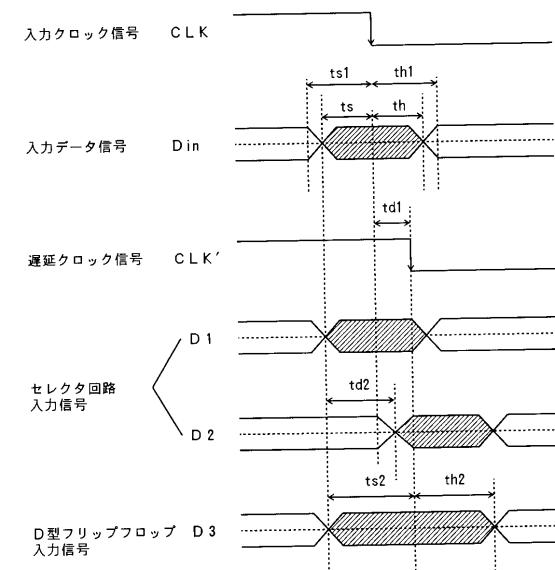

図2は本発明の動作を説明するタイミングチャートである。入力クロック信号CLKに対し、入力データ信号Dinがセットアップタイムtsおよびホールドタイムthを満たすことを必要とする。いまD型フリップフロップ4のセットアップタイムts1およびホールドタイムth1より短い、すなわちts1 > ts, th1 > thである場合を考える。入力クロック信号CLKはクロックの遅延時間td1だけ遅延され遅延クロック信号CLKが作られる。セレクタ回路では遅延クロック信号CLKがH-Lに変化するまではセレクタ回路入力信号D1がセレクタ回路出力信号D3として出力される。一方遅延クロックの変化後は入力信号Dinからtd2遅延されたセレクタ回路入力信号D2がセレクタ回路出力信号D3として出力される。セレクタ回路出力信号D3はD型フリップフロップ4に入力され、クロック信号CLKによってラッチされる。D3

40

が確定してからクロック信号CLKの変化までの時間ts2はts2 = ts + td1、クロック信号CLKの変化後データをホールドする時間th2はth2 = th + td2 - td1となる。td1, td2をts2 > ts1, th2 > th1となるように適当に選べばD型フリップフロップ4はラッチ動作が可能となる。したがってD型フリップフロップ4の特性で決まるセットアップタイムおよびホールドタイムより短いセットアップタイムおよびホールドタイムのラッチ回路を実現することができる。

#### 【0009】

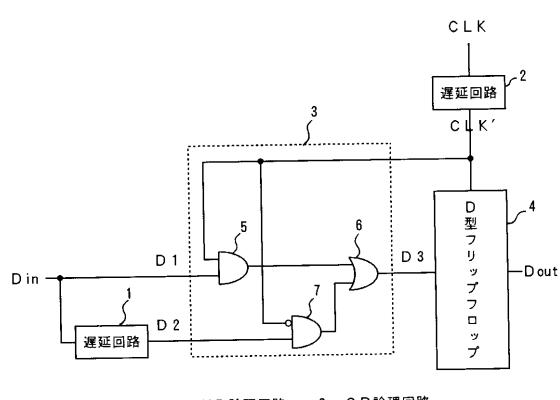

図3は本発明の実施例の一例である。セレクタ回路3はセレクタ回路入力信号D1と遅延クロック信号CLKを入力とするAND論理回路5と、セレクタ回路入力信号D2と遅延クロック信号CLKの反転を入力とするAND論理回路7と、それらの出力を入

50

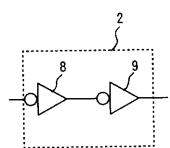

力とするOR論理回路6によって構成されている。遅延クロックCLKがHの期間はAND論理回路5の出力はD1、AND論理回路7の出力はLとなり、反対に遅延クロックCLKがLの期間はAND論理回路5の出力はL、AND論理回路7の出力はD2となり、二つの出力の和D3がD型フリップフロップ4の入力となる。また遅延回路は、例えば、図4のように直列に接続された二つの反転型論理回路によって実現することが可能である。

#### 【0010】

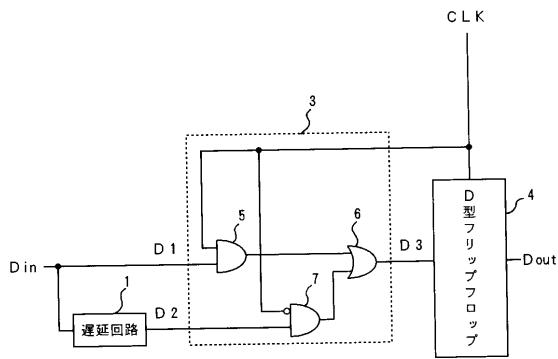

図5は本発明の第二の実施例である。セットアップタイム $t_s$ が十分長い場合、すなわち $t_s > t_{s1}, t_h < t_{h1}$ の場合では遅延回路2は省略することが可能である。

#### 【0011】

10

#### 【発明の効果】

本発明によれば、従来のラッチ回路よりも短いセットアップタイムおよびホールドタイムのラッチ回路を実現することが可能である。

#### 【図面の簡単な説明】

【図1】本発明の第一実施例のブロック図。

【図2】本発明の動作を説明したタイミングチャート。

【図3】本発明の一実施例の回路図。

【図4】遅延回路の実施例の回路図。

【図5】本発明の第二実施例の回路図。

#### 【符号の説明】

20

1, 2...遅延回路、3...セレクタ回路、4...D型フリップフロップ、5, 7...AND論理回路、6...OR論理回路、8, 9...反転型論理回路。

【図1】

図1

【図2】

図2

【図3】

図3

5, 7 … AND論理回路 6 … OR論理回路

【図5】

図5

【図4】

図4

8, 9 … 反転型論理回路

---

フロントページの続き

審査官 江嶋 清仁

(56)参考文献 特開平04-002977(JP,A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H03K 3/037