(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7622397号

(P7622397)

(45)発行日 令和7年1月28日(2025.1.28)

(24)登録日 令和7年1月20日(2025.1.20)

(51)国際特許分類

H 0 1 S 5/022(2021.01)

F I

H 0 1 S 5/022

請求項の数 8 (全14頁)

(21)出願番号 特願2020-186793(P2020-186793)

(22)出願日 令和2年11月9日(2020.11.9)

(65)公開番号 特開2022-76389(P2022-76389A)

(43)公開日 令和4年5月19日(2022.5.19)

審査請求日 令和5年8月21日(2023.8.21)

(73)特許権者 000002130

住友電気工業株式会社

大阪府大阪市中央区北浜四丁目5番33号

(74)代理人 100088155

弁理士 長谷川 芳樹

(74)代理人 100113435

弁理士 黒木 義樹

(74)代理人 100136722

弁理士 高木 邦夫

(74)代理人 100174399

弁理士 寺澤 正太郎

(74)代理人 100182006

弁理士 湯本 譲司

(72)発明者 板橋 直樹

最終頁に続く

(54)【発明の名称】 光半導体モジュール

## (57)【特許請求の範囲】

## 【請求項1】

伝送線路を有し、半導体レーザ素子が載置された基板と、

前記基板の絶縁体の誘電率よりも小さい誘電率を有する低誘電率材料によって形成され

、インダクタが載置されたブロックと、

前記基板及び前記ブロックを収容する筐体と、

を備え、

前記伝送線路は、並走するグランド配線と一定距離を保ちながら第1方向に延伸する高

周波配線を含み、

前記インダクタは、前記高周波配線に第1ワイヤを介して接続され、

前記半導体レーザ素子は、前記高周波配線に第2ワイヤを介して接続され、

前記第1ワイヤのインダクタンスは、前記第2ワイヤのインダクタンスより大きい、

光半導体モジュール。

## 【請求項2】

半導体レーザ素子が載置された基板と、

前記基板の絶縁体の誘電率よりも小さい誘電率を有する低誘電率材料によって構成され

、伝送線路を有し、インダクタが載置されたブロックと、

前記基板及び前記ブロックを収容する筐体と、

を備え、

前記伝送線路は、並走するグランド配線と一定距離を保ちながら第1方向に延伸する高

周波配線を含み、

前記インダクタは、前記高周波配線に第1ワイヤを介して接続され、

前記半導体レーザ素子は、前記高周波配線に第2ワイヤを介して接続され、

前記第1ワイヤのインダクタンスは、前記第2ワイヤのインダクタンスより大きい、

光半導体モジュール。

【請求項3】

前記ブロックは、前記インダクタに並列に接続された抵抗を更に有する、

請求項1または請求項2に記載の光半導体モジュール。

【請求項4】

R C直列回路を更に有し、

前記インダクタは、前記R C直列回路と前記伝送線路の高周波配線との間に接続されて

いる、

請求項1から請求項3のいずれか一項に記載の光半導体モジュール。

【請求項5】

前記ブロックは、前記基板に隣接して前記筐体の内部に配置されている、

請求項1から請求項4のいずれか一項に記載の光半導体モジュール。

【請求項6】

前記ブロックは、石英によって形成される、

請求項1から請求項5のいずれか一項に記載の光半導体モジュール。

【請求項7】

前記第1ワイヤのインダクタンスは、前記第2ワイヤのインダクタンスの2倍以上とな

っている、

請求項1から請求項6のいずれか一項に記載の光半導体モジュール。

【請求項8】

前記筐体は、前記第1方向に長手方向を有する、

請求項1から請求項7のいずれか一項に記載の光半導体モジュール。

【発明の詳細な説明】

【技術分野】

【0001】

本開示は、光半導体モジュールに関するものである。

30

【背景技術】

【0002】

特許文献1には、基板上に作製されたレーザ部及び光変調器部を有する半導体モジュ

ールが記載されている。半導体モジュールは、DFBレーザとEA変調器を集積した半導体

レーザと、コプレーナ配線である高周波配線を有するサブキャリアとを備える。半導体レ

ーザは、裏面にグランド電極を有する。サブキャリアの上面には、上段及び下段からなる

段差が形成されており、サブキャリアの下面是平坦状とされている。高周波配線は、サブ

キャリアの上面の上段に形成されるコプレーナ線路を有する。コプレーナ線路は、グラン

ド配線と、信号配線とを備える。サブキャリアの上面の下段には、グランド電極が形成さ

れている。半導体レーザは、裏面に設けられたグランド電極がサブキャリアのグランド電

極に接するように配置される。

40

【先行技術文献】

【特許文献】

【0003】

【文献】特開2017-107920号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところで、光半導体モジュールは、半導体レーザ、又は半導体レーザを駆動するドライ

バI Cにバイアスを供給するバイアスティー（バイアスT）を有することがある。バイア

50

ス T では、高周波線路へワイヤを接続する方式が採用される。しかしながら、この場合、ワイヤのインダクタンスと寄生容量とによって生じる周波数特性（透過特性）上のディップ（透過ディップ）が問題となりうる。例えば、透過ディップによって高周波線路を伝搬する高周波信号が劣化すると、光半導体モジュールから出力される光送信信号の波形品質が劣化する。従って、光送信信号において良好な波形品質を得るために、バイアス T がある場合でも高周波信号が劣化しないよう透過ディップの広帯域化を実現させることが求められる。

【 0 0 0 5 】

本開示は、広帯域化を実現させることができる光半導体モジュールを提供することを目的とする。

10

【課題を解決するための手段】

【 0 0 0 6 】

開示の一側面に係る光半導体モジュールは、伝送線路を有し、半導体レーザ素子が載置された基板と、低誘電率材料によって形成され、インダクタが載置されたブロックと、基板及びブロックを収容する筐体と、を備え、インダクタは、伝送線路に第 1 ワイヤを介して接続され、半導体レーザ素子は、伝送線路に第 2 ワイヤを介して接続され、第 1 ワイヤのインダクタンスは、第 2 ワイヤのインダクタンスより大きい。

【 0 0 0 7 】

本開示の別の側面に係る光半導体モジュールは、半導体レーザ素子が載置された基板と、低誘電率材料によって構成され、伝送線路を有し、インダクタが載置されたブロックと、基板及びブロックを収容する筐体と、を備え、インダクタは、伝送線路に第 1 ワイヤを介して接続され、半導体レーザ素子は、伝送線路に第 2 ワイヤを介して接続され、第 1 ワイヤのインダクタンスは、第 2 ワイヤのインダクタンスより大きい。

20

【発明の効果】

【 0 0 0 8 】

本開示によれば、広帯域化を実現させることができる。

【図面の簡単な説明】

【 0 0 0 9 】

【図 1】図 1 は、実施形態に係る光半導体モジュールの内部構造を模式的に示す平面図である。

30

【図 2】図 2 は、光半導体モジュールにおける半導体レーザ素子が搭載された基板、及びインダクタが搭載されたブロックを模式的に示す平面図である。

【図 3】図 3 は、ブロックの上に搭載されたインダクタを模式的に示す側面図である。

【図 4】図 4 は、図 2 とは別の光半導体モジュールにおける半導体レーザ素子が搭載された基板、及びインダクタが搭載されたブロックを模式的に示す平面図である。

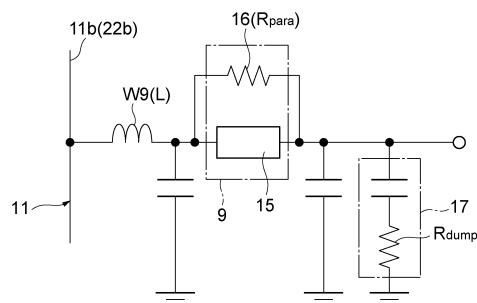

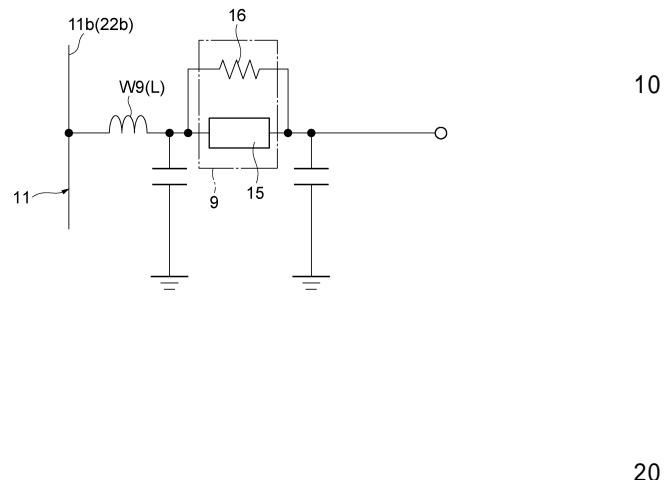

【図 5】図 5 は、例示的な光半導体モジュールの等価回路を示す図である。

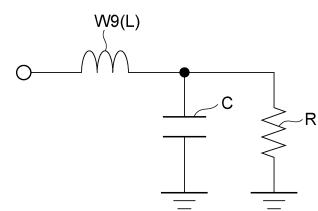

【図 6】図 6 は、図 5 の等価回路を簡略化した等価回路を示す図である。

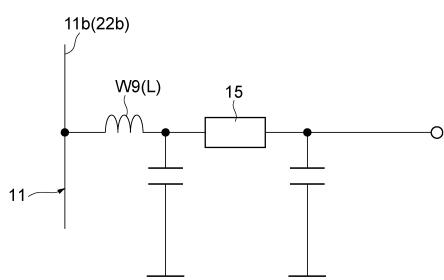

【図 7】図 7 は、参考例に係る光半導体モジュールの等価回路を示す図である。

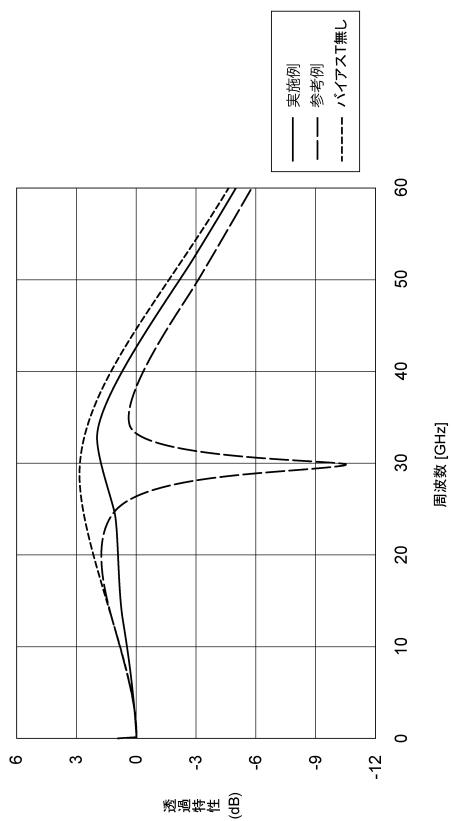

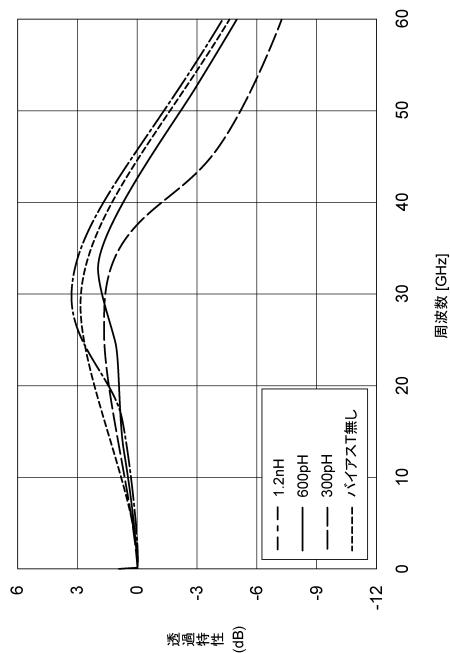

【図 8】図 8 は、周波数と透過特性との関係の例を示すグラフである。

【図 9】図 9 は、周波数と透過特性との関係の例を示すグラフである。

40

【図 10】図 10 は、変形例に係る光半導体モジュールの等価回路を示す図である。

【発明を実施するための形態】

【 0 0 1 0 】

[ 本願発明の実施形態の説明 ]

最初に、本開示の実施形態の内容を列記して説明する。本開示の一実施形態に係る光半導体モジュールは、伝送線路を有し、半導体レーザ素子が載置された基板と、低誘電率材料によって形成され、インダクタが載置されたブロックと、基板及びブロックを収容する筐体と、を備え、インダクタは、伝送線路に第 1 ワイヤを介して接続され、半導体レーザ素子は、伝送線路に第 2 ワイヤを介して接続され、第 1 ワイヤのインダクタンスは、第 2 ワイヤのインダクタンスより大きい。

50

## 【0011】

この光半導体モジュールでは、基板が伝送線路を有し、ブロックにはインダクタが載置されている。半導体レーザ素子は基板に搭載されている。ブロックは低誘電率材料によって構成されている。従って、寄生容量を低減させることができる。また、インダクタと伝送線路とを互いに接続する第1ワイヤのインダクタンスは、半導体レーザ素子と伝送線路とを互いに接続する第2ワイヤのインダクタンスよりも大きい。インダクタと伝送線路とを互いに接続する第1ワイヤのインダクタンスが大きいことにより、バイアスTがある状態でも広帯域化を実現させることができる。

## 【0012】

本開示の別の形態に係る光半導体モジュールは、半導体レーザ素子が載置された基板と、低誘電率材料によって構成され、伝送線路を有し、インダクタが載置されたブロックと、基板及びブロックを収容する筐体と、を備え、インダクタは、伝送線路に第1ワイヤを介して接続され、半導体レーザ素子は、伝送線路に第2ワイヤを介して接続され、第1ワイヤのインダクタンスは、第2ワイヤのインダクタンスより大きい。

10

## 【0013】

この光半導体モジュールでは、ブロックが伝送線路を有し、このブロックにインダクタが載置されている。半導体レーザ素子は基板に載置されている。前述した光半導体モジュールと同様、ブロックは低誘電率材料によって構成されているので、寄生容量を低減させることができる。また、インダクタと伝送線路とを互いに接続する第1ワイヤのインダクタンスは、半導体レーザ素子と伝送線路とを互いに接続する第2ワイヤのインダクタンスよりも大きい。従って、バイアスTがある状態でも広帯域化を実現させることができる。

20

## 【0014】

ブロックは、インダクタに並列に接続された抵抗を更に有してもよい。この場合、寄生容量に伴うディップを低減させることができる。

## 【0015】

光半導体モジュールは、RC直列回路を更に有し、インダクタは、RC直列回路と伝送線路との間に接続されてもよい。この場合、透過ディップを更に低減させることができる。

30

## 【0016】

ブロックは、基板に隣接して前記筐体の内部に配置されていてもよい。この場合、インダクタが載置されたブロックを基板の隣接位置に配置することが可能となる。

## 【0017】

低誘電率材料の誘電率は、基板の絶縁体の誘電率よりも小さくてもよい。この場合、ブロックの低誘電率材料の誘電率が基板の絶縁体の誘電率よりも小さいことにより、寄生容量をより低減させることができる。

## 【0018】

第1ワイヤのインダクタンスは、第2ワイヤのインダクタンスの2倍以上となっていてもよい。この場合、更なる広帯域化を実現させることができる。

## 【0019】

## [本開示の実施形態の詳細]

40

本開示の実施形態に係る光半導体モジュールの具体例を、図面を参照しながら説明する。なお、本発明は、これらの例示に限定されるものではなく、特許請求の範囲によって示され、特許請求の範囲と均等の範囲内での全ての変更が含まれることが意図される。図面の説明において、同一又は相当する要素には同一の符号を付し、重複する説明を適宜省略する。また、図面は、理解の容易化のため、一部を簡略化又は誇張して描いており、寸法比率等は図面に記載のものに限定されない。

## 【0020】

## (第1実施形態)

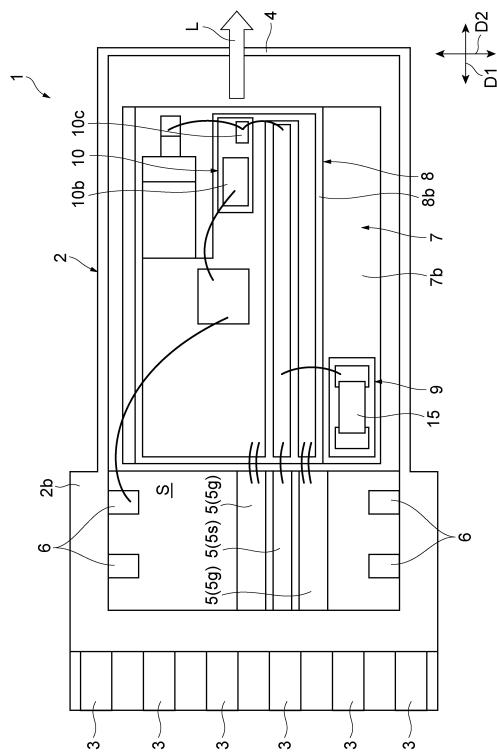

図1は、第1実施形態に係る光半導体モジュール1の内部構造を模式的に示す平面図である。光半導体モジュール1は、例えば、矩形状の筐体2と、筐体2の長手方向である方

50

向 D 1 の一端に設けられた外部端子 3 とを備える。外部端子 3 は、筐体 2 の方向 D 1 の一端において筐体 2 の幅方向である方向 D 2 に沿って並んでいる。外部端子 3 は、例えば、高速電気信号を外部から受ける端子、レーザダイオードの駆動電流を受ける端子、TEC の駆動電流を受ける端子、レーザダイオードの温度を検出するためのモニタ端子、及び、グランド電位（基準電位）を与える端子などを含む。筐体 2 は、筐体 2 の内部空間 S を画成する内壁 2 b を有する。筐体 2 の方向 D 1 における外部端子 3 と反対側の端部には、光 L（光送信信号）を出力する光出力部 4 が設けられる。

#### 【 0 0 2 1 】

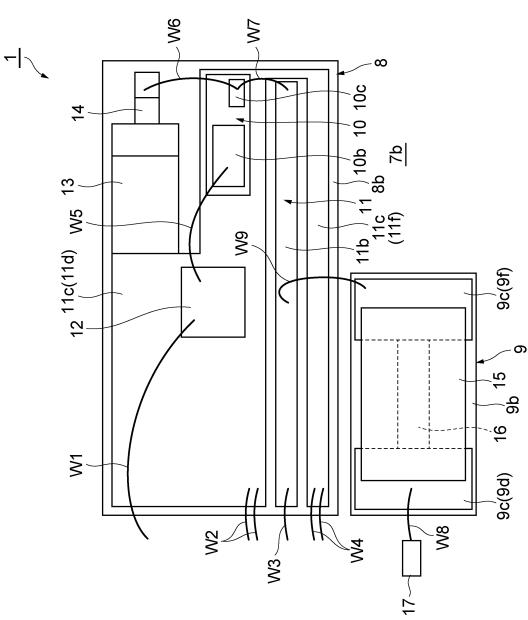

光半導体モジュール 1 は、筐体 2 の内部空間 S に、例えば、伝送線路 5 と、DC 用パッドであるパッド 6 と、温度制御用素子である TEC (Thermo Electric Cooler) 7 とを備える。図 2 は、TEC 7 の上部構造を拡大した模式的な平面図である。図 1 及び図 2 に示されるように、光半導体モジュール 1 は、TEC 7 と、半導体レーザ素子 10 が搭載された AlN (Aluminum Nitride) 基板 8 (基板) と、インダクタ 15 が載置されたブロック 9 とを備える。伝送線路 5 およびパッド 6 は、筐体 2 の内面に形成されている。伝送線路 5 およびパッド 6 は、内壁 2 b を貫通する配線によって外部端子 3 と接続されている。伝送線路 5 およびパッド 6 のそれぞれと外部端子 3 とを接続する配線は、例えば、金属メッキ又は蒸着によって形成される。伝送線路 5 は、並走するグランド配線 5 g と一定距離をおいて一方向に延伸する信号配線 5 s を含んでいる。

#### 【 0 0 2 2 】

例えば、AlN 基板 8 は TEC 7 の上に積層されている。筐体 2 は、内部空間 S 内に、例えば、TEC 7、AlN 基板 8、ブロック 9、半導体レーザ素子 10 及びインダクタ 15 を収容する。TEC 7 は、温度制御面 7 b を有する。温度制御面 7 b は、TEC 7 が筐体 2 に実装されるヒートシンク面 7 a と反対に位置する。例えば、ヒートシンク面 7 a および温度制御面 7 b は、方向 D 1 および方向 D 2 に平行な平面である。より詳細には、AlN 基板 8 は、例えば、温度制御面 7 b に接して温度制御面 7 b 上に搭載されている。AlN 基板 8 は、TEC 7 と反対側の第 1 面 8 b を有し、第 1 面 8 b の上に半導体レーザ素子 10 が載置される。ブロック 9 は、TEC 7 の上に AlN 基板 8 と並置されている。TEC 7 は、例えば、半導体レーザ素子 10 の温度制御を行う。例えば、TEC 7 に所定の電流を流すと、温度制御面 7 b において吸熱が行われ、吸熱された熱量がヒートシンク面 7 a において排熱される。このとき、半導体レーザ素子 10 は、AlN 基板 8 を介して冷却される。また、例えば、TEC 7 に上記所定の電流と反対方向に電流を流すと、ヒートシンク面 7 a において吸熱が行われ、吸熱された熱量が温度制御面 7 b において排熱される。このとき、半導体レーザ素子 10 は AlN 基板 8 を介して加熱される。ブロック 9 は、低誘電率材料によって構成されている。例えば、ブロック 9 は石英によって形成される。AlN 基板 8 は、例えば、絶縁体を含んでおり、ブロック 9 の低誘電率材料の比誘電率は AlN 基板 8 の絶縁体の比誘電率よりも小さい。半導体レーザ素子 10 は、例えば、電界吸収型変調器集積レーザ (EML : Electro-absorption Modulator integrated Laser) である。例えば、半導体レーザ素子 10 は、レーザダイオード 10 b と、光変調器 10 c (変調器) とを備える。

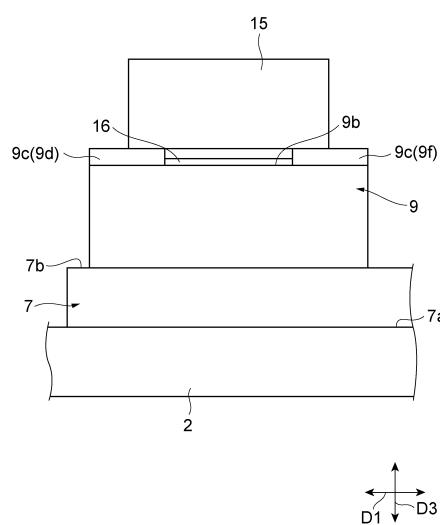

#### 【 0 0 2 3 】

図 3 は、ブロック 9 及びインダクタ 15 を模式的に示す側面図である。図 2 及び図 3 に示されるように、ブロック 9 はインダクタ 15 に対向する第 2 面 9 b を有し、第 2 面 9 b には配線 9 c が形成されている。ブロック 9 は、例えば、TEC 7 の温度制御面 7 b に接して温度制御面 7 b の上に載置されている。ブロック 9 は、ヒートシンク面 7 a が筐体 2 の内面に接して筐体 2 の内面上に載置されている。第 2 面 9 b は、例えば、方向 D 1 および方向 D 2 に平行な平面である。配線 9 c は、例えば外部端子 3 側に設けられる第 1 配線 9 d と、光出力部 4 側に設けられる第 2 配線 9 f とを含む。第 1 配線 9 d と第 2 配線 9 f とは、互いに絶縁されている。また、第 2 面 9 b には抵抗 16 が搭載されており、抵抗 16 は、例えば、第 1 配線 9 d 及び第 2 配線 9 f の間に配置されている。また、抵抗 16 は、第 1 配線 9 d 及び第 2 配線 9 f の間に電気的に接続されている。インダクタ 15 は、第

10

20

30

40

50

1配線9d及び第2配線9fの間に電気的に接続されている。すなわち、インダクタ15の一端は第1配線9dに接続され、インダクタ15の他端は第2配線9fに接続されている。従って、抵抗16は、インダクタ15と並列に接続されている。更に、光半導体モジュール1はRC直列回路17を備えており、インダクタ15はRC直列回路17と後述する伝送線路11との間に配置されている。インダクタ15は、例えば、バイアスTとして機能する。バイアスTは、伝送線路11にバイアス(直流電位)を供給する。バイアスは、伝送線路11を伝搬する高周波信号の基準電位となる。バイアスTは、伝送線路11から見たときに高周波において高インピーダンスを有し、高周波信号への影響は小さく抑えられている。インダクタ15は、第1配線9d及び第2配線9fに搭載されている。例えば、インダクタ15の一端の電極は、第1配線9dにハンダで接合され、インダクタ15の他端の電極は、第2配線9fにハンダで接合される。RC直列回路は、例えば、筐体2の内面に抵抗を実装するためのパッド6と、キャパシタを実装するためのパッド6とを形成し、それらのパッドを配線でつないで構成しても良い。それらのパッドをつなぐ配線は、メッキあるいは蒸着で形成してもよい。

#### 【0024】

A1N基板8は、TEC7の反対側の第1面8bに伝送線路11を有する。伝送線路11は、並走するグランド配線11cと一定距離を保ちながら一方向(D1方向)に延伸する高周波配線11bを含む。例えば、グランド配線11cは、ダイ12、チップ13及び抵抗14が搭載された第1グランド配線部11dと、高周波配線11bから見て第1グランド配線部11dの反対側に位置する第2グランド配線部11fとを含む。なお、グランド配線11cは、伝送線路11のように一方向に延びる配線でなくてもよく、伝送線路との間に一定の距離を保つ部分を有する幅の広い配線パターンであってもよい。

#### 【0025】

ダイ12、第1グランド配線部11d、高周波配線11b及び第2グランド配線部11fのそれぞれからは、ワイヤW1、ワイヤW2、ワイヤW3及びワイヤW4のそれぞれが延び出している。例えば、光半導体モジュール1は、更に、ダイ12及びレーザダイオード10bを互いに接続するワイヤW5と、抵抗14の一端及び変調器10cを互いに接続するワイヤW6と、高周波配線11b及び変調器10cを互いに接続するワイヤW7とを備える。

#### 【0026】

更に、光半導体モジュール1は、RC直列回路17及びインダクタ15を互いに接続するワイヤW8と、インダクタ15及び伝送線路11を互いに接続するワイヤW9とを備える。ワイヤW1, W2, W3, W4, W5, W6, W7, W8、およびW9は、例えば、ボンディングワイヤである。ワイヤW1, W2, W3, W4, W5, W6, W7, W8, W9の直径は、例えば、18μm、25μm又は50μmである。その場合に、ワイヤW1, W2, W3, W4, W5, W6, W7、W8、およびW9のそれぞれの直径は、全て同じ値でもよく、互いに異なる値であってもよい。なお、ワイヤW1, W2, W3, W4, W5, W6, W7, W8、およびW9は、ボンディングワイヤに代えて、リボンワイヤを使用してもよい。リボンワイヤは、例えば、ボンディングワイヤのような円形の断面ではなく、扁平な断面を有する。例えば、断面の厚さに対して断面の横幅は厚さの2倍以上となっている。ワイヤW9はインダクタ15と伝送線路11とを互いに接続する第1ワイヤに相当する。ワイヤW7は半導体レーザ素子10と伝送線路11とを互いに接続する第2ワイヤに相当する。ワイヤW9のインダクタンスは、ワイヤW7のインダクタンスよりも大きい。例えば、ワイヤW9はワイヤW7より長くてもよい。また、ワイヤW9の断面積(一例として直径)がワイヤW7の断面積より小さくてもよい。

#### 【0027】

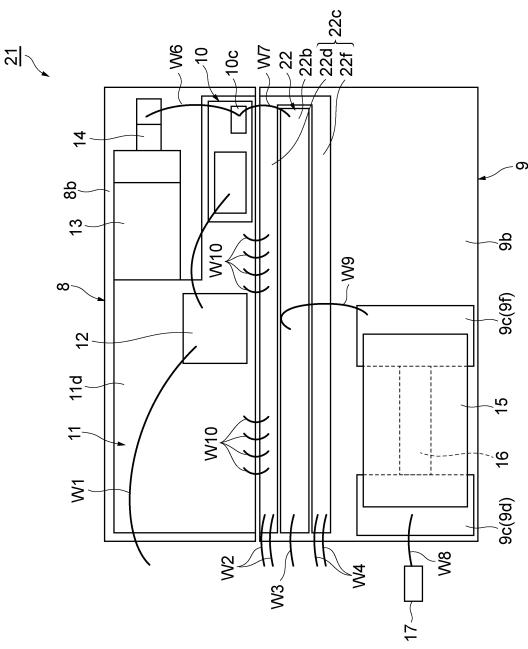

##### (第2実施形態)

次に、第2実施形態に係る光半導体モジュール21について図4を参照しながら説明する。第2実施形態に係る光半導体モジュール21の一部の構成は、前述した光半導体モジュール1の一部の構成と重複するため、光半導体モジュール1と重複する説明については

10

20

30

40

50

光半導体モジュール 1 の要素と同一の符号を付して説明を適宜省略する。図 4 に示されるように、光半導体モジュール 2 1 では、ブロック 9 が第 2 面 9 b に伝送線路 2 2 を有する。伝送線路 2 2 は、並走するグランド配線 2 2 c と一定距離をおいて一方向に延伸する高周波配線 2 2 b を含む。グランド配線 2 2 c は、例えば、第 3 グランド配線部 2 2 d と、高周波配線 2 2 b から見て第 3 グランド配線部 2 2 d の反対側に位置する第 4 グランド配線部 2 2 f とを含む。例えば、光半導体モジュール 2 1 では、A 1 N 基板 8 が第 1 グランド配線部 1 1 d のみを有する。

#### 【 0 0 2 8 】

光半導体モジュール 2 1 は、例えば、ブロック 9 に形成された第 3 グランド配線部 2 2 d と、A 1 N 基板 8 に形成された第 1 グランド配線部 1 1 d とを互いに接続するワイヤ W 1 0 を更に備える。また、光半導体モジュール 2 1 では、インダクタ 1 5 から伸び出すワイヤ W 9 が伝送線路 2 2 に接続されており、ワイヤ W 7 は高周波配線 2 2 b 及び変調器 1 0 c を互いに接続している。前述した光半導体モジュール 1 と同様、ワイヤ W 9 のインダクタンスは、ワイヤ W 7 のインダクタンスよりも大きい。

#### 【 0 0 2 9 】

次に、前述した各実施形態に係る光半導体モジュール 1 , 2 1 から得られる作用効果について説明する。まず、第 1 実施形態に係る光半導体モジュール 1 では、図 2 に例示されるように、A 1 N 基板 8 が伝送線路 1 1 を有し、ブロック 9 にはインダクタ 1 5 が搭載されている。半導体レーザ素子 1 0 は A 1 N 基板 8 に搭載されている。ブロック 9 は低誘電率材料によって構成されている。従って、第 2 面 9 b に形成されている配線 9 c の寄生容量を低減させることができる。また、インダクタ 1 5 と伝送線路 1 1 とを互いに接続するワイヤ W 9 のインダクタンスは、半導体レーザ素子 1 0 と伝送線路 1 1 とを互いに接続するワイヤ W 7 のインダクタンスよりも大きい。インダクタ 1 5 と伝送線路 1 1 とを互いに接続するワイヤ W 9 のインダクタンスが大きいことにより、インダクタ 1 5 がある状態でも高周波配線 1 1 b を伝搬する高周波信号に対する影響を抑えることができ、光半導体モジュール 1 の広帯域化を実現させることができる。

#### 【 0 0 3 0 】

第 2 実施形態に係る光半導体モジュール 2 1 では、図 4 に例示されるように、ブロック 9 が伝送線路 2 2 を有し、ブロック 9 にインダクタ 1 5 が載置されている。半導体レーザ素子 1 0 は A 1 N 基板 8 に載置されている。光半導体モジュール 2 1 では、光半導体モジュール 1 と同様、ブロック 9 が低誘電率材料によって構成されているので、第 2 面 9 b に形成されている配線 9 c の寄生容量を低減させることができる。また、インダクタ 1 5 と伝送線路 2 2 とを互いに接続するワイヤ W 9 のインダクタンスは、半導体レーザ素子 1 0 と伝送線路 2 2 とを互いに接続するワイヤ W 7 のインダクタンスより大きい。従って、インダクタ 1 5 がある状態でも高周波配線 2 2 b を伝搬する高周波信号に対する影響を抑えることができ、光半導体モジュール 2 1 の広帯域化を実現させることができる。

#### 【 0 0 3 1 】

図 5 は、光半導体モジュール 1 ( 又は光半導体モジュール 2 1 ) のバイアス T に関する等価回路を示す図である。バイアス T は、例えば、ワイヤ W 9 、インダクタ 1 5 、抵抗 1 6 、および R C 直列回路 1 7 を含む。図 6 は、図 5 の等価回路を簡略化した等価回路である。図 5 及び図 6 に示されるように、ワイヤ W 9 のインダクタンスを L 、抵抗 1 6 の抵抗を R para 、 R C 直列回路 1 7 の抵抗を R dump 、として、更に、  $R = R_{para} + R_{dump}$  とすると、このインダクタンス L と R C 並列回路との直列回路の共振周波数  $\omega_0$  は、式 ( 1 ) のように表される。

#### 【 数 1 】

$$\omega_0 = \sqrt{\frac{1}{LC} - \frac{1}{(CR)^2}} \quad \dots (1)$$

式 ( 1 ) において、 R  $\quad$  とすると、  $\omega_0$  はインダクタンス L とキャパシタンス C との

10

20

30

40

50

直列 L C 共振回路における共振周波数と等しい。一方、共振周波数  $\omega_0$  におけるインピーダンス  $Z$  ( $\omega = \omega_0$ ) は式 (2) のように表される。

【数 2】

$$Z(\omega = \omega_0) = \frac{R}{1 + (\omega_0 CR)^2} \quad \dots \quad (2)$$

光半導体モジュール 1 (又は光半導体モジュール 2 1) では、R が 0 ではないためインピーダンス  $Z$  ( $\omega = \omega_0$ ) は 0 にならず、且つ、 $\omega_0$  が小さい (L が大きい) ほどインピーダンス  $Z$  が高くなる。従って、式 (1) 及び式 (2) におけるキャパシタンス C と抵抗 R との積 C R の値が一定であるという条件下においては、L の値が大きいほど共振周波数でのインピーダンスの低下を抑制できる。従って、前述したように、インダクタ 1 5 から伸び出すワイヤ W 9 のインダクタンス L が大きい場合、インダクタ 1 5 がある条件下において伝送線路 1 1 の広帯域化を実現させることができる。

10

【0 0 3 2】

本実施形態において、ブロック 9 は、インダクタ 1 5 に並列に接続された抵抗 1 6 を更に有する。従って、抵抗 1 6 のダンピング効果によって寄生容量に伴うディップを低減させることができる。

【0 0 3 3】

本実施形態において、光半導体モジュール 1 (又は光半導体モジュール 2 1) は、R C 直列回路 1 7 を更に有し、インダクタ 1 5 は、R C 直列回路 1 7 と伝送線路 1 1 (又は伝送線路 2 2) との間に接続されている。この場合、透過ディップを更に低減させることができる。

20

【0 0 3 4】

本実施形態において、ブロック 9 は、A 1 N 基板 8 に隣接して T E C 7 の温度制御面 7 b に配置されている。従って、インダクタ 1 5 が載置されたブロック 9 を A 1 N 基板 8 の隣接位置に配置することが可能となる。それにより、A 1 N 基板 8 上に形成されている伝送線路 1 1 に近接してインダクタ 1 5 を配置することができる。また、ブロック 9 の第 2 面 9 b 上に伝送線路 2 2 が形成されていてもよい。その場合、伝送線路 2 2 に近接してインダクタ 1 5 を配置することができる。なお、A 1 N 基板 8 およびブロック 9 は、例えば、T E C 7 の温度制御面 7 b の上に実装されているが、半導体レーザ素子 1 0 が温度制御を必要としない場合には、A 1 N 基板 8 およびブロック 9 は、筐体 2 の内面上に直接実装されていてもよい。

30

【0 0 3 5】

本実施形態において、ブロック 9 の低誘電率材料の誘電率は、A 1 N 基板 8 の絶縁体の誘電率よりも小さい。従って、ブロック 9 の低誘電率材料の誘電率が A 1 N 基板 8 の絶縁体の誘電率よりも小さいことにより、寄生容量をより低減させることができる。このとき、A 1 N 基板 8 の厚さをブロック 9 の厚さとほぼ同じにしてもよい。それにより、A 1 N 基板 8 の上にインダクタ 1 5 を搭載した場合と比べて確実にインダクタ 1 5 に接続される配線の寄生容量を低減することができる。

【0 0 3 6】

40

本実施形態において、ワイヤ W 9 のインダクタンスは、ワイヤ W 7 のインダクタンスの 2 倍以上となっていてもよい。この場合、更なる広帯域化を実現させることができる。

【0 0 3 7】

次に、実施例について説明する。本発明は、以下の実施例には限定されない。実施例に係る光半導体モジュールは、前述した光半導体モジュール 1 であり、図 5 に示されるように、インダクタ 1 5 に並列に配置された抵抗 1 6、及び R C 直列回路 1 7 を備える。図 7 は、参考例に係る光半導体モジュールのバイアス T に関する等価回路を示す。図 7 に示されるように、参考例に係る光半導体モジュールは、抵抗 1 6 及び R C 直列回路 1 7 に相当する構成を有しない。

【0 0 3 8】

50

以上の実施例及び参考例のそれぞれの光半導体モジュールにおける伝送線路 11 の透過特性についてシミュレーションした結果を図 8 に示す。図 8 に示されるように、抵抗 16 及び R C 直列回路 17 を有しない参考例に係る光半導体モジュールでは、周波数が 30 GHz 付近において大きな共振ディップ（透過ディップ）が出現した。これに対し、実施例に係る光半導体モジュールでは、バイアス T を有しない場合と同様、共振ディップが殆ど生じないことが分かった。なお、バイアス T は、伝送線路を伝搬する高周波信号の基準電位を与えるために必要であり、バイアス T を有していてもバイアス T を有しない場合と比較して等価特性が劣化しないことは実施例が参考例よりも有用なことを示す一例である。

#### 【 0 0 3 9 】

図 9 は、実施例に係る光半導体モジュールにおいて、ワイヤ W 9 のインダクタンスを変更した場合における透過特性をシミュレーションした結果を示している。図 9 に示されるように、ワイヤ W 9 のインダクタンスが 300 pH である場合には、若干のディップ及び高周波ロスが生じた。これに対し、ワイヤ W 9 のインダクタンスが 600 pH 以上（600 pH 又は 1.2 nH）である場合には、バイアス T を有しない場合と同様、ディップ及び高周波ロスが殆ど生じないことが分かった。

#### 【 0 0 4 0 】

以上、本開示に係る光半導体モジュールの実施形態及び実施例について説明した。しかしながら、本発明は、前述した実施形態又は実施例に限定されない。すなわち、本発明が特許請求の範囲に記載した要旨の範囲内において種々の変形及び変更が可能であることは当業者によって容易に認識される。

#### 【 0 0 4 1 】

例えば、前述の実施形態では、図 5 に例示されるように、抵抗 16 及び R C 直列回路 17 を備える光半導体モジュール 1 及び光半導体モジュール 2 1 について説明した。しかしながら、例えば図 10 に示されるように、R C 直列回路 17 を有しない光半導体モジュールであってもよい。このように、抵抗 16 及び R C 直列回路 17 の少なくともいずれかを省略することも可能である。

#### 【 0 0 4 2 】

また、前述の実施形態では、伝送線路 11 の上にダイ 12、チップ 13 及び抵抗 14 が載置される例について説明した。しかしながら、伝送線路 11 の上に載置される素子の種類及び数は上記の例に限られず適宜変更可能である。また、前述の実施形態では、半導体レーザ素子 10 が EML である例について説明した。しかしながら、半導体レーザ素子は、EML 以外の半導体レーザ素子であってもよい。

#### 【 0 0 4 3 】

また、前述の実施形態では、基板が AlN 基板 8 であり、ブロック 9 が石英基板である例について説明した。しかしながら、基板の材料は AlN 以外のものであってもよい。ブロックは、アルミナ、FPC 又はポリイミドによって構成されていてもよい。すなわち、ブロック 9 の低誘電率材料の誘電率が基板の絶縁体の誘電率よりも小さくなっている限り基板及びブロックの材料は特に限定されない。

#### 【 符号の説明 】

#### 【 0 0 4 4 】

1, 2 1 ... 光半導体モジュール

2 ... 筐体

2 b ... 内壁

3 ... 外部端子

4 ... 光出力部

5 ... 伝送線路

6 ... パッド

7 ... TEC

7 a ... ヒートシンク面

7 b ... 温度制御面

10

20

30

40

50

|                                                                     |    |

|---------------------------------------------------------------------|----|

| 8 ... A 1 N 基板 ( 基板 )                                               |    |

| 8 b ... 第 1 面                                                       |    |

| 9 ... ブロック                                                          |    |

| 9 b ... 第 2 面                                                       |    |

| 9 c ... 配線                                                          |    |

| 9 d ... 第 1 配線                                                      |    |

| 9 f ... 第 2 配線                                                      |    |

| 1 0 ... 半導体レーザ素子                                                    |    |

| 1 0 b ... レーザダイオード                                                  |    |

| 1 0 c ... 変調器                                                       | 10 |

| 1 1 , 2 2 ... 伝送線路                                                  |    |

| 1 1 b , 2 2 b ... 高周波配線                                             |    |

| 1 1 c , 2 2 c ... グランド配線                                            |    |

| 1 1 d ... 第 1 グランド配線部                                               |    |

| 1 1 f ... 第 2 グランド配線部                                               |    |

| 1 2 ... ダイ                                                          |    |

| 1 3 ... チップ                                                         |    |

| 1 4 ... 抵抗                                                          |    |

| 1 5 ... インダクタ                                                       |    |

| 1 6 ... 抵抗                                                          | 20 |

| 1 7 ... R C 直列回路                                                    |    |

| 2 2 d ... 第 3 グランド配線部                                               |    |

| 2 2 f ... 第 4 グランド配線部                                               |    |

| D 1 , D 2 ... 方向                                                    |    |

| L ... 光                                                             |    |

| S ... 内部空間                                                          |    |

| W 1 , W 2 , W 3 , W 4 , W 5 , W 6 , W 7 , W 8 , W 9 , W 1 0 ... ワイヤ |    |

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

10

20

【図 7】

【図 8】

30

40

50

【図 9】

【図 10】

30

40

50

---

フロントページの続き

大阪府大阪市中央区北浜四丁目5番33号 住友電気工業株式会社内

審査官 佐藤 美紗子

(56)参考文献 特開2004-088026 (JP, A)

(58)調査した分野 (Int.Cl., DB名)

H01S 5/00 - 5/50