(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4302194号

(P4302194)

(45) 発行日 平成21年7月22日(2009.7.22)

(24) 登録日 平成21年5月1日(2009.5.1)

|                       |                 |

|-----------------------|-----------------|

| (51) Int.Cl.          | F 1             |

| HO1L 21/336 (2006.01) | HO1L 29/78 627A |

| HO1L 29/786 (2006.01) | GO2F 1/1368     |

| GO2F 1/1368 (2006.01) | HO1L 29/78 612Z |

|                       | HO1L 29/78 619A |

請求項の数 5 (全 19 頁)

|           |                         |           |                                                |

|-----------|-------------------------|-----------|------------------------------------------------|

| (21) 出願番号 | 特願平9-123001             | (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日  | 平成9年4月25日(1997.4.25)    | (72) 発明者  | 平形 吉晴<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (65) 公開番号 | 特開平10-303428            | (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (43) 公開日  | 平成10年11月13日(1998.11.13) |           |                                                |

| 審査請求日     | 平成16年4月23日(2004.4.23)   | 審査官       | 綿引 隆                                           |

| 前置審査      |                         |           |                                                |

最終頁に続く

(54) 【発明の名称】 半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の半導体素子上に設けられた第1の層間絶縁膜に対して第1の平坦化処理を行い、前記第1の層間絶縁膜上に第2の層間絶縁膜を形成し、前記第2の層間絶縁膜に対して第2の平坦化処理を行い、前記第2の層間絶縁膜上に複数の反射画素電極を形成し、前記第2の層間絶縁膜上及び前記複数の反射画素電極上に絶縁膜を形成し、前記絶縁膜の研磨若しくはエッチバックを行うことによって、前記複数の反射画素電極の隙間に埋込絶縁層を形成するとともに、前記複数の反射画素電極の表面に対して第3の平坦化処理を行い、

前記複数の反射画素電極の表面に接してカラーフィルターを設けることを特徴とする半導体装置の作製方法。

## 【請求項 2】

複数の半導体素子上に設けられた第1の層間絶縁膜に対して第1の平坦化処理を行い、前記第1の層間絶縁膜上に、高密度プラズマソースを用いて形成された酸化珪素膜からなる第2の層間絶縁膜を形成し、前記第2の層間絶縁膜に対してCMP研磨による第2の平坦化処理を行い、前記第2の層間絶縁膜上に複数の反射画素電極を形成し、前記第2の層間絶縁膜上及び前記複数の反射画素電極上に絶縁膜を形成し、前記絶縁膜の研磨若しくはエッチバックを行うことによって、前記複数の反射画素電極

10

20

の隙間に埋込絶縁層を形成するとともに、前記複数の反射画素電極の表面に対して第3の平坦化処理を行い、

前記複数の反射画素電極の表面に接してカラーフィルターを設けることを特徴とする半導体装置の作製方法。

【請求項3】

請求項1又は請求項2において、

前記カラーフィルター上に、液晶材料を設け、

前記埋込絶縁層の材料は、前記液晶材料よりも比誘電率が低い材料を用いることを特徴とする半導体装置の作製方法。

【請求項4】

10

請求項1乃至請求項3のいずれか一項において、

前記埋込絶縁層の材料は、遮光性を有する材料を用いることを特徴とする半導体装置の作製方法。

【請求項5】

請求項1乃至請求項4のいずれか一項において、

前記複数の画素電極の表面と前記埋込絶縁層の表面とが同一平面をなすように前記研磨若しくは前記エッチバックを行うことを特徴とする半導体装置の作製方法。

【発明の詳細な説明】

【0001】

20

【発明が属する技術分野】

本願発明は、液晶表示装置（LCD）の作製方法に関する。特に、半導体薄膜を利用したアクティブマトリクス型液晶表示装置（以下、AM-LCDと呼ぶ）の作製方法に関する。また、本願発明はその様な表示装置を具備した電気光学装置に応用することが可能である。

【0002】

なお、本明細書中において「半導体装置」とは、半導体を利用して機能することで機能する装置全てを指している。従って、上記表示装置および電気光学装置も半導体装置の範疇に含まれる。ただし、明細書中では区別しやすい様に表示装置や電気光学装置といった言葉を使い分けることにする。

【0003】

30

【従来の技術】

近年、AM-LCDを投射型表示ディスプレイとして用いたプロジェクター等の開発が活発に進められている。また、モバイルコンピュータやビデオカメラ用の直視型表示ディスプレイとしての需要も高まっている。

【0004】

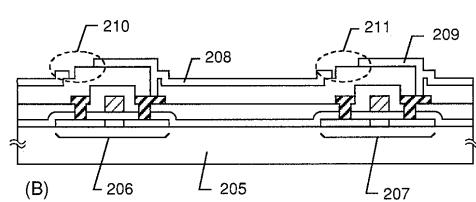

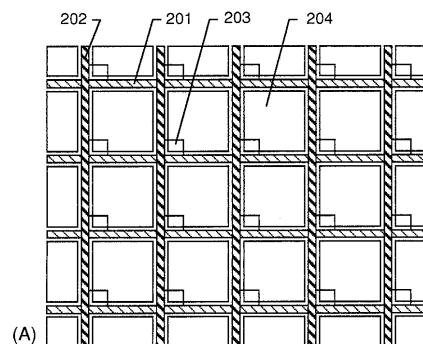

ここで従来のアクティブマトリクス型表示装置における画素マトリクス回路の構成の概略を図2（A）、（B）に示す。なお、画素マトリクス回路とは液晶に印加される電界を制御するための薄膜トランジスタ（TFT）をマトリクス状に配置した回路であり、AM-LCDの画像表示領域を構成する。

【0005】

40

図2（A）に示すのは、画素マトリクス回路を上面から見た図である。ここでは水平方向に設けられた複数のゲイト線201と垂直方向に設けられた複数のソース線202とで囲まれた領域が画素領域となる。そして、複数のゲイト線201および複数のソース線202の各交差部にはそれぞれTFT203が形成されている。また、各TFTにはそれぞれに画素電極204が接続されている。

【0006】

従って、画素マトリクス回路は複数のゲイト線201および複数のソース線202とで囲まれてマトリクス状に形成された複数の画素領域からなり、個々の画素領域にはTFT203と画素電極204とが設けられた構成となっている。

【0007】

50

また、画素マトリクス回路の断面構造を図2(B)に示す。図2(B)において、205は絶縁表面を有する基板、206、207は基板205上に形成された画素TFTであり、図2(A)のTFT203に相当する。

【0008】

また、画素TFT206、207にはそれぞれ画素電極208、209が接続されている。この画素電極208、209は図2(A)の画素電極204に相当する。この画素電極208、209は通常1枚の金属薄膜をパターニングすることにより得られる。

【0009】

従って、従来構造の画素マトリクス回路は、画素電極間に電極の境界部(以下、単に境界部と呼ぶ)210、211が必ず存在する。即ち、必然的に画素電極の膜厚分に相当する段差が形成されてしまうのである。この様な段差では液晶材料の配向不良が生じて表示画像が乱れる。また、段差部での入射光の乱反射がコントラストを低下させたり、光の利用効率を低下させる原因となる。

10

【0010】

また、図2(B)からも明らかな様に、半導体素子や各配線の交差部の上方ではその形状を反映した状態で画素電極208、209が形成される。この様な段差も上記問題を生じる原因となる。

【0011】

特に、プロジェクターなどに用いる投射型ディスプレイは、1~2inch程度の極めて高精細な小型ディスプレイを拡大投影するため、上述の問題が顕在化してしまう。

20

【0012】

【発明が解決しようとする課題】

以上の様な問題に対して、従来はブラックマスク(またはブラックマトリクス)によって画像の乱れる領域を遮蔽してコントラスト比を高めていた。また、近年では素子の微細化が進み、高開口率を目的とした遮蔽領域の制御性が求められる様になったためTFT側基板にブラックマスクを設ける構成が主流となってきた。

【0013】

しかしながら、TFT側基板にブラックマスクを設ける構成とした場合、パターニング工程の増加、寄生容量の増加、開口率の低下等の諸問題が生じてしまう。この様なことから、前述の諸問題を起こさずにコントラスト比を確保する技術が望まれている。

30

【0014】

本願発明は上記問題点を解決し、簡易な手段により極めて高精細なアクティブマトリクス型表示装置を形成するための手段を開示するものである。

【0015】

【課題を解決するための手段】

本明細書で開示する発明の構成は、

絶縁表面を有する基板上に形成された絶縁膜を平坦化する工程と、

前記絶縁膜上に複数の電極を形成する工程と、

前記複数の電極を覆う絶縁層を形成する工程と、

前記複数の電極の表面および前記絶縁層の表面を両表面が同一平面をなす様に平坦化し、前記複数の電極の境界部を前記絶縁層で埋め込む工程と、

40

前記平坦化は、前記電極の厚さの20%以下の精度でもって行われることを特徴とする特徴とする。

【0016】

また、他の発明の構成は、

第1の基板および透光性を有する第2の基板と、

前記第1の基板と前記第2の基板との間に挟持された液晶層と、

を少なくとも含む半導体装置の作製方法であって、

前記第1の基板上に形成された絶縁膜を平坦化する工程と、

前記絶縁膜上にストライプ状の電極を形成する工程と、

50

前記ストライプ状の電極を覆う絶縁層を形成する工程と、

前記ストライプ状の電極の表面および前記絶縁層の表面を両表面が同一平面をなす様に平坦化し、前記ストライプ状の電極の境界部を前記絶縁層で埋め込む工程と、

前記平坦化は、前記電極の厚さの 20 %以下の精度でもって行われることを特徴とする。

## 【0017】

また、他の発明の構成は、

絶縁表面を有する基板上に複数の半導体素子を形成する工程と、

層間絶縁膜を形成する工程と、

前記層間絶縁膜を平坦化する工程と、

前記層間絶縁膜上に前記半導体素子と電気的に接続する画素電極を形成する工程と、

前記画素電極を覆う絶縁層を形成する工程と、

前記画素電極の表面および前記絶縁層の表面を両表面が同一平面をなす様に平坦化し、前記画素電極の境界部を前記絶縁層で埋め込む工程と、

前記平坦化は、前記電極の厚さの 20 %以下の精度でもって行われることを特徴とする。

## 【0018】

また、他の発明の構成は、

マトリクス状に形成された複数の半導体素子および該複数の半導体素子の各々に接続された複数の画素電極を有する基板と、

前記基板上に保持された液晶層と、

を少なくとも含む半導体装置の作製方法であって、

層間絶縁膜を形成する工程と、

前記層間絶縁膜を平坦化する工程と、

前記層間絶縁膜上に前記半導体素子と電気的に接続する画素電極を形成する工程と、

前記画素電極を覆う絶縁層を形成する工程と、

前記画素電極の表面および前記絶縁層の表面を両表面が同一平面をなす様に平坦化し、前記画素電極の境界部を前記絶縁層で埋め込む工程と、

前記平坦化は、前記電極の厚さの 20 %以下の精度でもって行われることを特徴とする。

## 【0019】

上記構成において、液晶層が保持された状態の典型例としては、複数の画素電極を有する基板（第1の基板）と第1の基板に対向する対向基板（第2の基板）との間に液晶層が挟持されている状態を言う。なお、液晶層として P D L C (ポリマ分散型液晶) を使用する場合、液晶層自体が固体化するので第2の基板を必要としない場合もありうる。

## 【0020】

また、半導体素子としては薄膜トランジスタ（TFT）が代表的であるが、その他にも絶縁ゲイト型電界効果トランジスタ（IGFET）、薄膜ダイオード、MIM (Metal-Insulator-Metal) 素子、バリスタ素子等でも良い。

## 【0021】

平坦化を電極の厚さの 20 %以内とすることで、液晶層の厚さに凹凸が影響をすることを抑制することができる。特に反射型の液晶パネルの場合には、液晶層の厚さに不均一性起因する表示の不良が顕在化するので、本明細書で開示する発明を利用することは有用である。

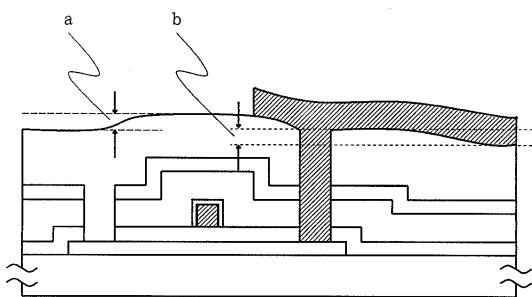

## 【0022】

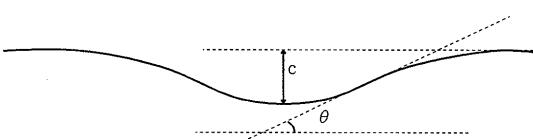

一般に画素電極の膜厚は 100 ~ 300 nm 程度である。従って、絶縁膜や配向膜の平坦性は 20 ~ 60 nm 程度以下に抑えればよい。例えば、図 12 に示すような構造において、a や b で示される値を 20 ~ 60 nm とすればよい。

## 【0023】

平坦化は画素電極の厚さの 20 %以内とすることが好ましいが、実用上は画素電極の 50 %以内とするのでも効果がある。

## 【0024】

また、平坦性の程度としては、図 13 示すような表面状態を得るとして、の値が 15

10

20

30

40

50

。以内となるような平坦性を実現すればよい。このようにすることでその上に形成される反射画素電極で反射される光を光学変調に有効に利用することができる。勿論、図13に示す状態において、cの値を20~60nm以下とすることが重要である。

#### 【0025】

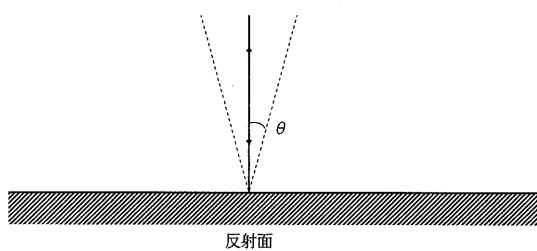

また、平坦性の程度を示すパラメータの望ましい限定条件としては、図14に示すように反射電極の反射面で反射される光の光量が光軸方向からの15°のぶれの円錐形状の中において、70%（入射光量に対して）以上あるようにすることは有効である。

#### 【0026】

これらの限定条件は、他のパラメータと組み合わせることにより、さらに有用となる。即ち、これらのパラメータの限定条件、あるいは各パラメータの限定条件を組み合わせたもの上で規定される条件を満たすように平坦性を確保することで、発明の効果をより高いものとして得ることができる。10

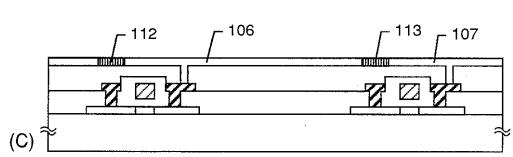

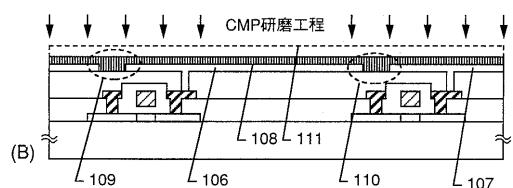

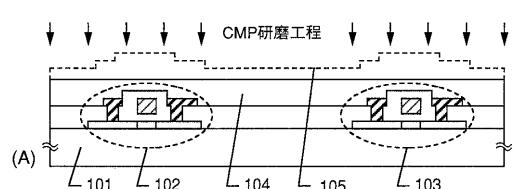

#### 【0027】

##### 【発明の実施の形態】

ここでは本願発明についての簡単な説明を図1を用いて行う。図1(A)において、101は絶縁表面を有する基板、102は基板101上に形成された第1の画素TFT、103は第2の画素TFTである。さらに、第1および第2の画素TFT102、103は層間絶縁膜104に覆われている。層間絶縁膜104は後に形成する画素電極とTFTとを電気的に絶縁するための絶縁膜である。

#### 【0028】

本発明の第1の特徴は、予め層間絶縁膜104を厚めに堆積しておいて、平坦化工程（特に機械的な研磨による平坦化）を施すことにある。この層間絶縁膜104の研磨工程は、後述するが後に画素電極を形成する際に重要な役割を果たす。なお、図1(A)において105で示される点線は、研磨工程前の層間絶縁膜104の形状を示しており、機械的な研磨工程によって層間絶縁膜104の凹凸が平坦化されることを表している。20

#### 【0029】

この平坦化は、残存する凹凸が画素電極の厚さの10%以内となるように行なうことが重要である。

#### 【0030】

なお、機械的な研磨としては代表的にはCMP（化学機械研磨）技術が挙げられる。CMP技術は薬液による化学的なエッチングと研磨材（砥粒）による機械的な研磨によって薄膜表面を平坦化する技術である。30

#### 【0031】

また、機械的な研磨以外にもドライエッチング法を利用したエッチバック技術を用いる事もできる。エッチバック技術は平坦度ではCMP技術に見劣りするが、装置の増設を特に必要としない点、処理中にパーティクル（ゴミ）を発生しない点などの利点を有する。

#### 【0032】

次に、平坦化された層間絶縁膜104上に金属薄膜（図示せず）を成膜し、パターニングを施して画素電極106、107を形成する。本発明では層間絶縁膜104を平坦化してあるため、形成された画素電極106、107は極めて平坦な表面を有する。（図1(B))40

#### 【0033】

画素電極106、107は、それぞれ画素TFT102、103とコンタクトホールを介して接続する。また、画素電極106、107は絶縁層108で覆われている。この時、絶縁層108を厚めに堆積することで境界部109、110は完全に埋め込まれた状態となる。

#### 【0034】

そして、本発明の第2の特徴は、絶縁層108に対して機械的な研磨を施して境界部109、110のみに絶縁層108が残存せることにある。そして、この工程により図1(C)に示す様な状態で埋め込み絶縁層112、113を形成する。なお、図1(B)にお50

いて 111 で示される点線は、研磨工程前の絶縁層 108 の形状を示しており、機械的な研磨工程によって絶縁層 108 が削られていく様子を表している。

#### 【0035】

この様にして絶縁層 108 を研磨していくと、やがて画素電極 106、107 の表面が現れる。この状態で研磨を止めても図 1 (C) に示す状態を得ることはできるが、さらに研磨を進行させて画素電極表面も同時に平坦化することは有効である。この場合、研磨処理の条件を適宜変更（砥粒を細かくする等）して画素電極表面が最も好ましい状態となる様にすれば良い。

#### 【0036】

図 1 (C) に示す様な最終的な状態では、画素電極間に形成される境界部 109、110 10 は完全に埋め込み絶縁層 112、113 で埋め込まれた状態となる。この時、画素電極 106、107 の表面と埋め込み絶縁層 112、113 の表面とは同一平面を成している。

#### 【0037】

この時、前述の様に本発明の第 1 の特徴とした層間絶縁膜 104 の研磨工程が重要な役割を果たしている。その事について以下に説明する。

#### 【0038】

例えば層間絶縁膜 104 の研磨工程を行わなかった場合、105 で示される形状がそのまま画素電極 106、107 および絶縁層 108 の形状に反映してしまうことになる。また、境界部 109、110 は、一般的には開口率を稼ぐため必然的に TFT 上（ソース配線 20 上）に形成される。そのため、境界部 109、110 は実効的な画素電極面（TFT や配線と重ならない最も平坦な面）よりも高い位置に形成される。

#### 【0039】

従って、この状態で絶縁層 108 を機械的に研磨していくと、まず TFT 上に位置する画素電極表面が最も早く露出する。そのため、上述の実効的な画素電極面を研磨する頃には TFT 上の画素電極および埋め込み絶縁層の研磨がかなり進行し、均一な研磨処理が困難なものとなってしまう。

#### 【0040】

また、層間絶縁膜 104 を厚く堆積して TFT 等による凹凸を平坦化することも考えられるが、層間絶縁膜 104 を成膜しただけでは必ず表面にうねりなどの凹凸が少なからず存在する。その場合、うねりを平坦化するためには後に形成する絶縁層 108 を厚めに形成し、機械的な研磨工程も長めに行う必要があり、スループットの低下、発生するパーティクルの増加等の問題を招くことになる。

#### 【0041】

以上の様に、画素電極を形成する前に予め機械的な研磨工程によって層間絶縁膜を平坦化しておくことは非常に有効な手段である。即ち、本発明は図 1 (B) に示す研磨工程によって図 1 (C) に示す状態を得ることが最大の目的であるが、図 1 (B) に示す研磨工程を効率的に行うために図 1 (A) に示す研磨工程を施すことに特徴がある。

#### 【0042】

そして、図 1 (C) に示す様に画素電極間の隙間（境界部）を埋め込み絶縁層によって埋め込み、不要な段差を排除する。この様にすることで従来の様な液晶材料の配向不良や段差部での光の乱反射等の問題を生じない極めて高精細なアクティブラチカル型表示装置を得ることができる。

#### 【0043】

##### 【実施例】

###### 【実施例 1】

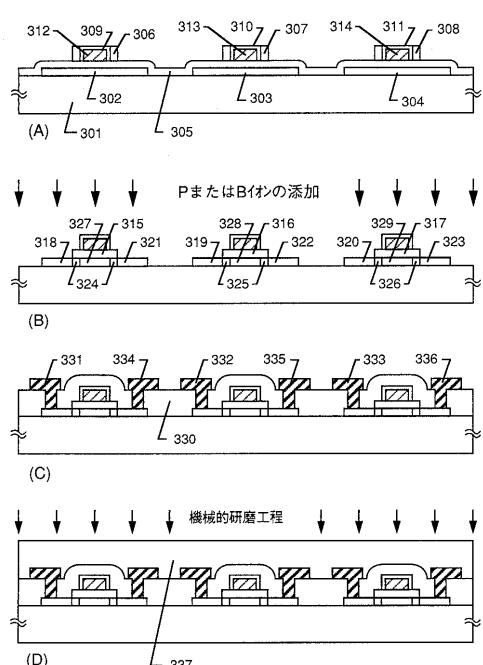

本実施例では本発明を利用して反射型 LCD の画素マトリクス回路を作製する工程例を図 3、4 を用いて説明する。なお、本発明は画素の平坦化に関する技術であるため、TFT 構造自体は本実施例に限定されるものではない。

#### 【0044】

まず、絶縁表面を有する基板 301 を用意する。本実施例ではガラス基板上に下地膜とし 50

て酸化珪素膜を形成する。基板 301 の上には結晶性珪素膜でなる活性層 302～304 を形成する。なお、本実施例では 3 つの TFT のみ記載することになるが実際には 100 万個以上の TFT が画素マトリクス回路内に形成される。

#### 【0045】

本実施例では非晶質珪素膜を熱結晶化させて結晶性珪素膜を得ている。そして、その結晶性珪素膜を通常にフォトリソ工程でパターニングして活性層 302～304 を得る。なお、本実施例では結晶化の際に結晶化を助長する触媒元素（ニッケル）を添加している。この技術については特開平7-130652号公報に詳細に記載されている。

#### 【0046】

次に、ゲイト絶縁膜 305 として 150 nm の厚さの酸化珪素膜を形成し、その上に 0.2wt% のスカンジウムを含有させたアルミニウム膜（図示せず）を成膜し、パターニングによりゲイト電極の原型となる島状パターンを形成する。10

#### 【0047】

本実施例では、ここで特開平7-135318号公報に記載された技術を利用する。なお、詳細は同公報を参考にすると良い。

#### 【0048】

まず、上記島状パターン上にパターニングで使用したレジストマスクを残したまま、3 % のシュウ酸水溶液中で陽極酸化を行う。この時、白金電極を陰極として 2～3 mV の化成電流を流し、到達電圧は 8 V とする。こうして、多孔質状の陽極酸化膜 306～308 が形成される。20

#### 【0049】

その後、レジストマスクを除去した後に 3 % の酒石酸のエチレングリコール溶液をアンモニア水で中和した溶液中で陽極酸化を行う。この時、化成電流は 5～6 mV とし、到達電圧は 100 V とすれば良い。こうして、緻密な陽極酸化膜 309～311 が形成される。

#### 【0050】

そして、上記工程によってゲイト電極 312～314 が画定する。なお、画素マトリクス回路ではゲイト電極の形成と同時に 1 ライン毎に各ゲイト電極を接続するゲート線も形成されている。（図 3 (A)）

#### 【0051】

次に、ゲイト電極 312～314 をマスクとしてゲイト絶縁膜 305 をエッチングする。30 エッチングは CF<sub>4</sub> ガスを用いたドライエッチング法により行う。これにより 315～317 で示される様な形状のゲイト絶縁膜が形成される。

#### 【0052】

そして、この状態で一導電性を付与する不純物イオンをイオン注入法またはプラズマドーピング法により添加する。この場合、画素マトリクス回路を N 型 TFT で構成するならば P (リン) イオンを、P 型 TFT で構成するならば B (ボロン) イオンを添加すれば良い。40

#### 【0053】

なお、上記不純物イオンの添加工程は 2 度に分けて行う。1 度目は 80 keV 程度の高加速電圧を行い、ゲイト絶縁膜 315～317 の端部（突出部）の下に不純物イオンのピークがくる様に調節する。そして、2 度目は 5 keV 程度の低加速電圧で行い、ゲイト絶縁膜 315～317 の端部（突出部）の下には不純物イオンが添加されない様に調節する。

#### 【0054】

こうして TFT のソース領域 318～320、ドレイン領域 321～323、低濃度不純物領域（LDD 領域とも呼ばれる）324～326、チャネル形成領域 327～329 が形成される。（図 3 (B)）

#### 【0055】

この時、ソース / ドレイン領域は 300～500 / のシート抵抗が得られる程度に不純物イオンを添加することが好ましい。また、低濃度不純物領域は TFT の性能に合わせて最適化を行う必要がある。また、不純物イオンの添加工程が終了したら熱処理を行い、不純物イオンを活性化する。50

物イオンの活性化を行う。

**【0056】**

次に、第1の層間絶縁膜330として酸化珪素膜を400nmの厚さに形成し、その上にソース電極331～333、ドレイン電極334～336を形成する。（図3（C））

**【0057】**

次に、第2の層間絶縁膜337として酸化珪素膜を0.5～1μmの厚さに形成する。なお、高密度プラズマソース等を利用して緻密な酸化珪素膜を形成すると、後のCMP研磨の際の平坦度が向上するので好ましい。また、CMP研磨の条件さえ最適化すれば第2の層間絶縁膜337として有機性樹脂膜を用いることも可能である。有機性樹脂膜としては、ポリイミド、ポリアミド、ポリイミドアミド、アクリル等を用いることができる。

10

**【0058】**

そして、第2の層間絶縁膜337を形成したら、1回目のCMP研磨工程を行う。この工程により第2の層間絶縁膜337は平坦化され、凹凸のない平坦面を得ることができる。この平坦化は、残存する凹凸の高さ（山の頂上と谷の底の間の鉛直方向の距離）が後に形成される画素電極の厚さの10%以内となる条件で行う。（図3（D））

**【0059】**

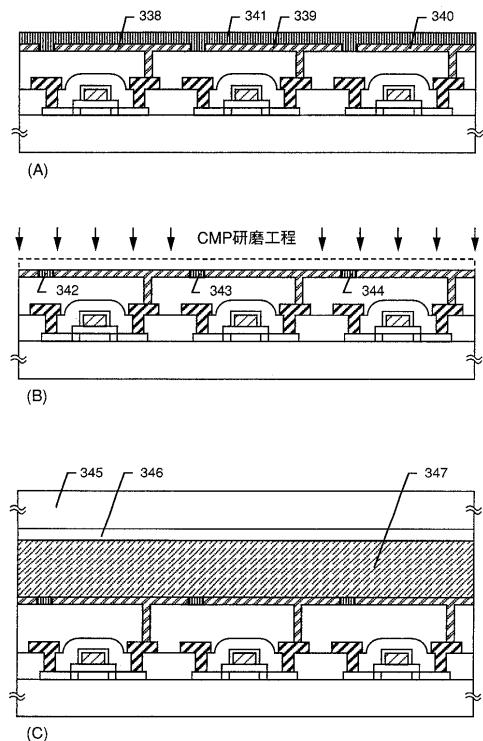

次に、1wt%のチタンを添加したアルミニウム膜を100nmの厚さに成膜し、パターニングにより画素電極338～340を形成する。勿論、他の金属材料を用いても構わない。

**【0060】**

次に、画素電極338～340を覆って絶縁層341を形成する。なお、本実施例の様にソース配線331～333上に境界部が形成される様に画素電極を形成すると、ソース配線331～333がブラックマスクとして機能するので、絶縁層341が透光性であっても構わない。

20

**【0061】**

しかしながら、より確実な遮光機能を確保するために、絶縁層341としては黒色顔料またはカーボンを分散させた有機性樹脂膜（PSG等の溶液塗布系酸化珪素膜でも良い）等の様に遮光性を有する絶縁膜を用いることが望ましい。こうすることでソース配線が細くなったり場合や斜め方向からの光に対しても確実な遮光機能を果たすことができる。

**【0062】**

また、使用する液晶材料よりもできるだけ比誘電率の低い材料を用いることで、画素電極間ににおける横方向電界の形成を抑制することもできる。

30

**【0063】**

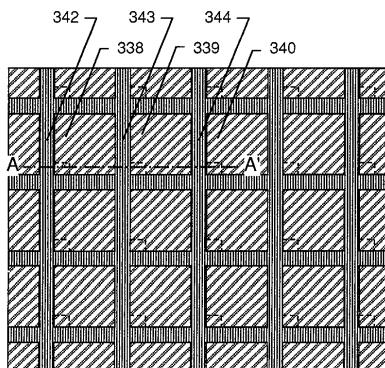

こうして図4（A）に示す状態が得られる。図4（A）に示す状態が得られたら、2回目のCMP研磨工程を行い、画素電極338～340の隙間に埋め込まれた埋め込み絶縁層342～344を形成する。この時、画素電極338～340の表面と埋め込み絶縁層342～344の表面とがほぼ一致するので、優れた平坦面を得ることができる。（図4（B））

**【0064】**

この状態を上面から見た図を図6に示す。図6は画素マトリクス回路に注目した簡略図であり、図4（B）の構造は図6においてA-A'で切った断面図に相当する。また、図6における各符号は図4（A）、（B）で用いた符号に対応している。

40

**【0065】**

図6に示す様に、画素電極はマトリクス状に配置され、その隙間（境界部）が埋め込み絶縁層342～344で埋め込まれる。従って、埋め込み絶縁層342～344はそれぞれ符号を付けてあるが、実際にはマトリクス状に一体化している。

**【0066】**

以上の様にして、画素マトリクス回路が完成する。実際には画素TFTを駆動する駆動回路等も同一基板上に同時形成される。この様な基板は通常TFT側基板またはアクティブマトリクス基板と呼ばれる。本明細書中ではアクティブマトリクス基板のことを第1の基板と呼ぶことにする。

50

**【 0 0 6 7 】**

第1の基板が完成したら、透光性基板345に対向電極346を形成した対向基板（本明細書中ではこの基板を第2の基板と呼ぶことにする）を貼り合わせ、それらの間に液晶層347を挟持する。こうして図4（C）に示す様な反射型LCDが完成する。

**【 0 0 6 8 】**

なお、このセル組み工程は公知の方法に従って行えば良い。また、液晶層に二色性色素を分散させたり、対向基板にカラーフィルターを設けたりすることも可能である。その様な液晶層の種類、カラーフィルターの有無等はどの様なモードで液晶を駆動するかによって変化するので実施者が適宜決定すれば良い。

**【 0 0 6 9 】**

本実施例では示さなかったが、画素電極の上面にカラーフィルターを配置した構成おしてもよい。

10

**【 0 0 7 0 】**

本実施例に示すような作製工程で得られる液晶パネルは、反射画素電極の平坦性が優れているので、画素電極の上にカラーフィルターを配置する構成が有効なものとなる。また、誘電体膜を単層または多層に配置し、特定の波長帯域や特定の偏光状態の光を選択的に反射するような構造としてもよい。この構成は、ダイクロイックミラーや偏光ビームスプリッタに利用されているものと同じ原理である。

**【 0 0 7 1 】**

一般に反射電極の表面に平坦性に問題がある場合、反射電極の表面にカラーフィルターを配置することは、色ムラや不鮮明な表示の要因となる好ましくない。

20

**【 0 0 7 2 】****〔実施例2〕**

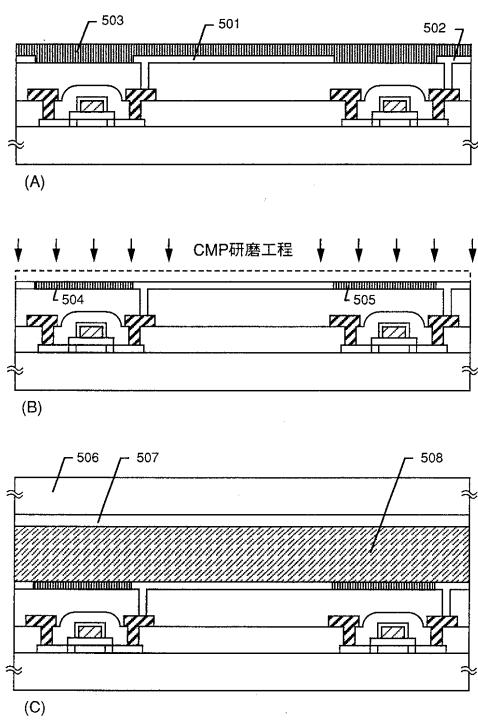

本実施例では本発明を利用して透過型LCDの画素マトリクス回路を作製する工程例を図5を用いて説明する。なお、途中までは実施例1に示した反射型LCDの作製工程と同一であるので、ここでは異なる点のみについて説明する。

**【 0 0 7 3 】**

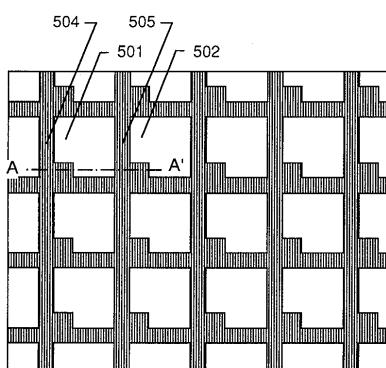

図3（D）に示す様な1回目のCMP研磨工程まで終了したら、図5に示す様に画素電極501、502を形成する。本実施例では画素電極501、502の材料として透明導電膜（ITO、SnO<sub>2</sub>等）を用いる。また、この時、画素電極501、502はTFT上に重ならない様に形成しておく。

30

**【 0 0 7 4 】**

次に、画素電極501、502を覆って絶縁層503を形成する。なお、本実施例では絶縁層503として黒色顔料を分散させたポリイミド等を用いる。透過型の場合、TFTの活性層も遮光する必要があるため、遮光性を有する絶縁膜を用いることが好ましい。（図5（A））

**【 0 0 7 5 】**

次に、2回目のCMP研磨工程を行い、画素電極501、502と同一平面をなす埋め込み絶縁層504、505を形成する。（図5（B））

40

**【 0 0 7 6 】**

この状態を上面から見た図を図7に示す。図7は画素マトリクス回路に注目した簡略図であり、図5（B）の構造は図7においてA-A'で切った断面図に相当する。また、図7における各符号は図5（A）、（B）で用いた符号に対応している。

**【 0 0 7 7 】**

図7に示す様に、複数の画素電極はマトリクス状に配置され、その境界部が一体化した埋め込み絶縁層で埋め込まれる。また、本実施例では、埋め込み絶縁層がTFT上にも形成されるため、活性層に光があたって抵抗が変化することを抑制する効果も得られる。

**【 0 0 7 8 】**

以上の様にして、透過型LCDのTFT側基板が完成する。TFT側基板が完成したら、通常のセル組み工程によって透光性基板506、対向電極507でなる対向基板とTFT

50

側基板との間に液晶層 508 を挟持する。こうして図 5 (C) に示す様な透過型 LCD が完成する。

#### 【0079】

なお、本実施例において、画素電極 338～340 自体を機械的に研磨して平坦化することも有効である。その際、直視型ディスプレイとするならば微細な凹凸を有した表面状態とし、投射型ディスプレイとするならば表面を鏡面状態とすすることが好ましい。

#### 【0080】

##### 〔実施例 3〕

実施例 1 で示した作製工程では、第 2 の層間絶縁膜 337 および埋め込み用の絶縁層 341 のみを平坦化する例を示した。しかし、本発明では第 1 の層間絶縁膜 330 に対して平坦化工程を行っても構わない。10

#### 【0081】

また、層間絶縁膜を積層構造で構成する場合に、各層の形成ごとに平坦化工程を行っても良い。

#### 【0082】

本発明は、画素電極を形成する前に十分な平坦度を確保しておき、さらに画素電極を埋め込み絶縁層で埋め込むことで画素電極表面の平坦度も高めている。従って、平坦化工程の回数が多い分には何ら問題はなく、むしろ好ましい。

#### 【0083】

##### 〔実施例 4〕

本実施例では、アクティブマトリクス駆動を行うための半導体素子として、実施例 1 で示した TFT とは異なる構造の TFT を利用する場合の例について説明する。なお、本実施例で説明する構造の TFT は実施例 2 に対しても容易に適用することができる。20

#### 【0084】

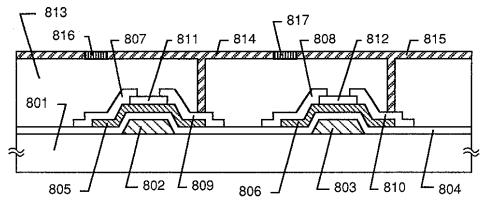

実施例 1 では代表的なトップゲイト型 TFT であるコプレナー型 TFT を一例として記載したが、ボトムゲイト型 TFT であっても構わない。図 8 に示すのはボトムゲイト型 TFT の代表例である逆スタガ型 TFT を用いた例である。

#### 【0085】

図 8 において、801 はガラス基板、802、803 はゲイト電極、804 はゲイト絶縁膜、805、806 は活性層である。活性層 805、806 は意図的に不純物を添加しない珪素膜で構成される。30

#### 【0086】

また、807、808 はソース電極、809、810 はドレイン電極であり、811、812 はチャネルストッパー（またはエッティングストッパー）となる窒化珪素膜である。即ち、活性層 805、806 のうち、チャネルストッパー 811、812 の下に位置する領域が実質的にチャネル形成領域として機能する。

#### 【0087】

以上までが逆スタガ型 TFT の基本構造である。本実施例では、この様な逆スタガ型を有機性樹脂膜でなる層間絶縁膜 813 で覆って平坦化し、その上に画素電極 814、815 を形成する構成とする。勿論、画素電極間の隙間は本発明を利用して埋め込み絶縁層 816、817 によって埋め込まれる。40

#### 【0088】

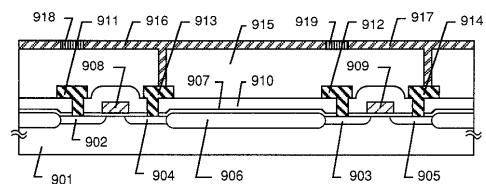

また、次に本発明の半導体素子として絶縁ゲイト型電界効果トランジスタ (IGFET) を形成した場合の例について説明する。なお、IGFET は MOSFET とも呼ばれ、シリコンウェハー上に形成されたトランジスタを指す。

#### 【0089】

図 9 において、901 はガラス基板、902、903 はソース領域、904、905 はドレイン領域である。ソース / ドレイン領域はイオン注入で不純物を添加し、熱拡散させることで形成できる。なお、906 は素子分離用の酸化物であり、通常の LOCOS 技術を用いて形成できる。50

**【 0 0 9 0 】**

次に、907はゲイト絶縁膜、908、909はゲイト電極、910は第1の層間絶縁膜、911、912はソース電極、913、914はドレイン電極である。その上を第2の層間絶縁膜915で平坦化し、その平坦面上に画素電極916、917を形成する。画素電極間の隙間は本発明を利用して埋め込み絶縁層918、919によって埋め込まれる。

**【 0 0 9 1 】**

なお、本実施例で示したIGFET、トップゲイト型またはボトムゲイト型TFT以外にも、薄膜ダイオード、MIM素子、バリスタ素子等を用いたアクティブマトリクスディスプレイに対しても本発明は適用できる。

**【 0 0 9 2 】**

以上、本実施例に示した様に、本発明はあらゆる構造の半導体素子を用いた反射型LCDまたは透過型LCDに対して適用可能である。

**【 0 0 9 3 】**

特に、反射型液晶LCDは半導体素子上を平坦化してその上に画素電極を形成することでき、画素面積を最大限に活用できる利点を有する。本発明はその利点をさらに効果的に利用する上で有効な技術である。そのため、本発明を利用した反射型LCDは高い解像度と高い開口率を実現することができる。

**【 0 0 9 4 】****〔 実施例 5 〕**

本願発明は、単純マトリクス型の液晶表示装置に対しても適用することが可能である。この場合、一対の基板の各々にストライプ状の電極を形成し、互いの電極が直交する様に基板を貼り合わせて液晶層を挟持する。

**【 0 0 9 5 】**

なお、この場合、一方を透光性基板とすれば他方は透光性でも遮光性でも構わない。ただし、透光性基板側に形成するストライプ状の電極は透明導電膜で構成する必要がある。

**【 0 0 9 6 】**

本実施例では、透光性基板と対をなす基板側にアルミニウムまたはアルミニウムを主成分とする材料でストライプ状の電極を形成し、ストライプ状に延在する電極間の隙間を絶縁層で埋め込む。

**【 0 0 9 7 】**

単純マトリクス型LCDに本発明を適用した場合、絶縁層として液晶層よりも比誘電率の低い材料(有機性樹脂材料等)を用いることで隣接する電極間のクロストークを低減する効果も得られる。

**【 0 0 9 8 】****〔 実施例 6 〕**

本発明を適用して形成される反射型LCDでは様々な液晶の表示モードを利用することができる。例えば、ECB(電界制御複屈折)モード、PCHG(相転移型ゲスト・ホスト)モード、OCBモード、HANモード、PDLCL型ゲスト・ホストモードが挙げられる。

**【 0 0 9 9 】**

ECBモードは液晶層に印加する電圧を変化させて液晶の配向を変え、その時生じる液晶層の複屈折の変化を一対の偏光板で検出してカラー表示を行う表示モードである。この場合、カラーフィルターを利用しない方式もとれるため、明るい表示が可能である。

**【 0 1 0 0 】**

また、PCHGモードはホスト液晶に対して二色性色素をゲスト分子に混合し、液晶に印加する電圧によって液晶分子の配向状態を変化させ、液晶層の光吸収率を変化させる表示モードである。この場合、偏光板を用いない方がとれるため、高いコントラストを得ることができる。

**【 0 1 0 1 】**

また、PDLCLモードは液晶中に高分子を分散させた(または高分子中に液晶を分散させ

10

20

30

40

50

た) ポリマー分散型液晶を用いる表示モードである。この場合、偏光板が不要であるため明るい表示が可能である。また、固体のポリマー分散型液晶を利用すれば対向側にガラス基板を用いない構成とすることも可能である。

#### 【0102】

これらの様々な表示モードは、その特徴に応じて偏光板の有無、カラーフィルターの有無を自由に設定することができる。例えば、P C G H モードの場合には偏光板が不要なので、カラーフィルターを用いた単板式としても明るい表示を実現することができる。

#### 【0103】

##### 〔実施例7〕

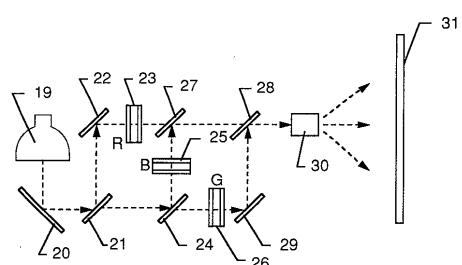

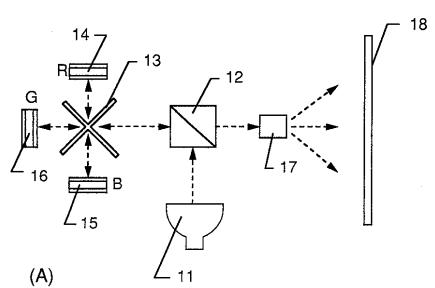

本実施例では、本発明を表示ディスプレイとして用いた電気光学装置の一例について説明する。まず、実施例1に示した反射型LCDを三板式プロジェクターに適用した場合について、図10(A)を用いて説明する。

10

#### 【0104】

図10(A)において、メタルハライドランプ、ハロゲンランプ等の光源11から出力されたR(赤)、B(青)、G(緑)を含む光は、偏光ビームスプリッタ12で反射され、クロスダイクロイックミラー13に進む。

#### 【0105】

なお、偏光ビームスプリッタとは光の偏光方向によって反射したり透過したりする機能を有した光学フィルターである。この場合、光源11からの光は偏光ビームスプリッタ12で反射される様な偏光を与えてある。

20

#### 【0106】

この時、クロスダイクロイックミラー13では、Rに対応する液晶パネル14の方向にR成分光が反射され、Bに対応する液晶パネル15の方向にB成分光が反射される。また、G成分光はクロスダイクロイックミラー13を透過し、Gに対応する液晶パネル16に入射する。

#### 【0107】

各液晶パネルは14~16は、画素がオフ状態にある時は入射光の偏光方向を変化させないで反射する様に液晶分子が配向している。また、画素がオン状態にある時は液晶層の配向状態が変化し、入射光の偏光方向もそれに伴って変化する様に構成されている。

#### 【0108】

30

これらの液晶パネル14~16で反射された光は再びクロスダイクロイックミラー13で反射(G成分光だけは透過)して合成され、再び偏光ビームスプリッタ12へと入射する。

#### 【0109】

この時、オン状態にある画素領域で反射された光は偏光方向が変化するため偏光ビームスプリッタ12を透過する。一方、オフ状態にある画素領域で反射された光は偏光方向が変化しないため偏光ビームスプリッタ13で反射される。

#### 【0110】

この様に、画素マトリクス回路にマトリクス状に配置された画素領域を複数の半導体素子でオン/オフ制御することによって、特定の画素領域で反射された光のみが偏光ビームスプリッタ12を透過できる様になる。この動作は各液晶パネル14~16に共通である。

40

#### 【0111】

以上の様にして偏光ビームスプリッタ12を透過した画像情報を含む光は投影レンズ等で構成される光学系レンズ17で拡大投影されてスクリーン18上に映し出される。

#### 【0112】

本発明を利用した反射型LCDは、画素電極間を埋め込むことで高い解像度と高い開口率とを実現している。また、画素電極の平坦化を行った場合には高い反射率を実現している。そのため、図10(A)の投射型プロジェクターの様に画像を拡大投影する電気光学装置においても優れた表示性能を実現できる。

#### 【0113】

50

次に、実施例 2 に示した透過型 LCD を三板式プロジェクターに適用した場合について図 10 (B) を用いて説明する。

【0114】

図 10 (B)において、19 はハロゲンランプ等の光源、20 はリフレクターである。RGB 成分を含んだ光はまずダイクロイックミラー 21 に入射し、ここで R 成分光のみ反射される。そして、R 成分光はリフレクター 22 で反射され、R に対応する液晶パネル 23 へ入射する。

【0115】

また、ダイクロイックミラー 21 を透過した光はダイクロイックミラー 24 に入射し、ここで B 成分光のみが反射される。反射された B 成分光は B に対応する液晶パネル 25 へ入射する。また、ダイクロイックミラー 24 を透過した G 成分光は G に対応する液晶パネル 26 へと入射する。

【0116】

そして、R 成分光はダイクロイックミラー 27 で B 成分光と合成され、ダイクロイックミラー 28 へ入射する。また、G 成分光はリフレクター 29 で反射されてダイクロイックミラー 28 へと入射する。ここで RGB 全ての成分光が合成され、投影レンズ 30 によって拡大投影されてスクリーン 31 に映し出される。

【0117】

本発明を利用した透過型 LCD も高い解像度と高い開口率とを実現しているため、優れた表示性能を有する電気光学装置を構成することができる。特に、開口率が高いという点は本発明の透過型 LCD の最も大きな利点である。

【0118】

〔実施例 8〕

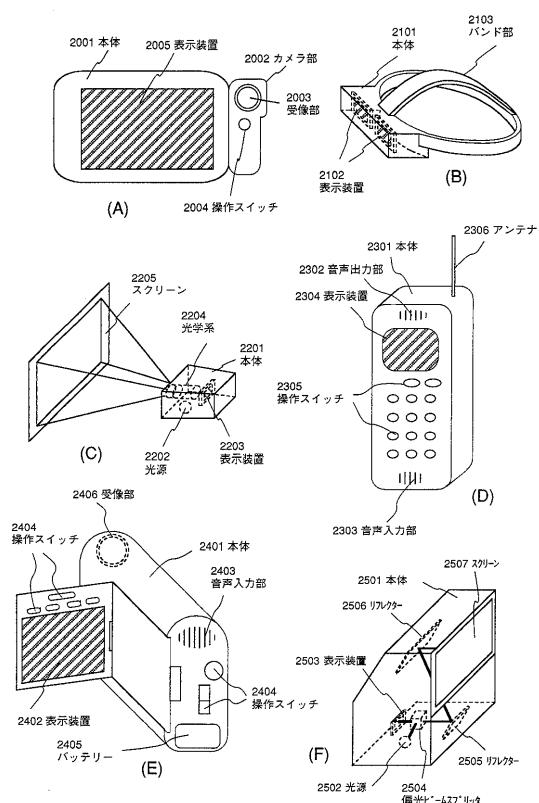

本実施例では、本発明による液晶表示装置を適用しうる応用製品（電気光学装置）について図 11 を用いて説明する。本発明を利用した電気光学装置としてはビデオカメラ、スチルカメラ、プロジェクター、ヘッドマウントディスプレイ、カーナビゲーション、パソコン用コンピュータ、携帯情報端末（モバイルコンピュータ、携帯電話等）などが挙げられる。

【0119】

図 11 (A) はモバイルコンピュータ（モービルコンピュータ）であり、本体 2001、カメラ部 2002、受像部 2003、操作スイッチ 2004、表示装置 2005 で構成される。本発明の反射型 LCD を表示装置 2005 に適用すると、さらに小型化および低消費電力化が図れる。

【0120】

図 11 (B) はヘッドマウントディスプレイであり、本体 2101、表示装置 2102、バンド部 2103 で構成される。本発明の反射型 LCD を表示装置 2102 に適用することで大幅に装置の小型化が図れる。

【0121】

図 11 (C) はフロント型プロジェクターであり、本体 2201、光源 2202、表示装置 2203、光学系 2204、スクリーン 2205 で構成される。表示装置 2203 に本発明の透過型 LCD を採用することで高精細な画像が実現される。

【0122】

図 11 (D) は携帯電話であり、本体 2301、音声出力部 2302、音声入力部 2303、表示装置 2304、操作スイッチ 2305、アンテナ 2306 で構成される。本発明を表示装置 2304 に適用することで視認性に優れた表示モニタを搭載することができる。

【0123】

図 11 (E) はビデオカメラであり、本体 2401、表示装置 2402、音声入力部 2403、操作スイッチ 2404、バッテリー 2405、受像部 2406 で構成される。本発明を表示装置 2402 に適用することで、屋外での撮影にも十分に耐えうる表示性能が実

10

20

30

40

50

現できる。

**【0124】**

図11(F)はリア型プロジェクターであり、本体2501、光源2502、表示装置2503、偏光ビームスプリッタ2504、リフレクター2505、2506、スクリーン2507で構成される。本発明の反射型LCDを表示装置2402に適用することで、装置の薄型化および高精細な画像を実現できる。

**【0125】**

なお、図11(A)、(B)、(D)、(E)に示す様に直視型ディスプレイとする場合、画素電極表面に凹凸を形成することは有効である。これにより光の散乱効果が高まり、視野角、視認性が向上する。逆に、図11(C)、(F)に示す様に投射型ディスプレイとする場合、画素電極表面を鏡面状態にすることが好ましい。これにより光の乱反射が低減され、色ずれや解像度の低下が抑えられる。10

**【0126】**

以上の様に、本発明の応用範囲は極めて広く、あらゆる分野の表示媒体に適用することが可能である。特に、液晶表示装置をプロジェクターの様な投射型表示装置に用いる場合には、非常に高い解像度が要求される。その様な場合において、本発明は非常に有効な技術である。

**【0127】**

また、モバイルコンピュータ、携帯電話、ビデオカメラに代表される携帯情報端末機器は装置の小型化および低消費電力化が望まれる。その様な場合において、バックライトの不要な本発明の反射型LCDは有効である。20

**【0128】**

**【発明の効果】**

本発明を利用した液晶表示装置は、マトリクス状に配置された個々の画素電極の隙間(画素と画素との切れ間)が埋め込み絶縁層で埋め込まれた構成となる。この時、画素電極表面と埋め込み絶縁層の表面とは概略一致するため、画素電極間の隙間に生じる段差部はほぼ完全に平坦化する。

**【0129】**

従って、上記段差部に起因する液晶材料の配向不良、入射光の乱反射によるコントラスト低下といった諸問題が解決される。また、予め画素電極の下地となる層間絶縁膜を平坦化してあるので画素電極は完全に平坦な状態となる。30

**【0130】**

以上により、高い開口率および反射率を有した高精細な表示性能を有する液晶表示装置を実現することが可能である。

**【図面の簡単な説明】**

**【図1】** 本発明の概略を説明するための図。

**【図2】** 従来の画素マトリクス回路の構成を示す図。

**【図3】** 反射型LCDの作製工程を示す図。

**【図4】** 反射型LCDの作製工程を示す図。

**【図5】** 透過型LCDの作製工程を示す図。

40

**【図6】** 画素マトリクス回路を上面から見た図。

**【図7】** 画素マトリクス回路を上面から見た図。

**【図8】** アクティブマトリクス基板の構造を示す図。

**【図9】** アクティブマトリクス基板の構造を示す図。

**【図10】** プロジェクタの構成を示す図。

**【図11】** 本発明の応用製品の一例を説明するための図。

**【図12】** 平坦性を説明する図。

**【図13】** 平坦性を説明する図。

**【図14】** 平坦性を説明する図。

**【符号の説明】**

50

|         |                    |

|---------|--------------------|

| 101     | ガラス基板              |

| 102、103 | 画素 TFT             |

| 104     | 層間絶縁膜              |

| 105     | 研磨工程前の層間絶縁膜の形状     |

| 106、107 | 画素電極               |

| 108     | 埋め込み用の絶縁層          |

| 109、110 | 境界部                |

| 111     | 研磨工程前の埋め込み用の絶縁層の形状 |

| 112、113 | 埋め込み絶縁層            |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

(B)

【図 11】

【図 12】

【図 13】

【図 1 4】

---

フロントページの続き

(56)参考文献 特開平06-347828(JP,A)

特開平07-294958(JP,A)

特開平08-122761(JP,A)

特開平08-160463(JP,A)

特開平07-211634(JP,A)

特開平07-128688(JP,A)

特開平03-138618(JP,A)

(58)調査した分野(Int.Cl., DB名)

G02F 1/1368

H01L 21/336

H01L 27/12

H01L 29/786