등록특허 10-2323385

(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2021년11월05일

(11) 등록번호 10-2323385

(24) 등록일자 2021년11월02일

(51) 국제특허분류(Int. Cl.)

*H03H 7/18* (2006.01) *H01P 1/18* (2006.01)

*H01Q 1/24* (2006.01) *H01Q 3/38* (2006.01)

*H03H 7/20* (2006.01) *H04L 25/02* (2006.01)

(52) CPC특허분류

*H03H 7/185* (2013.01)

*H01P 1/184* (2013.01)

(21) 출원번호 10-2016-7022214

(22) 출원일자(국제) 2014년12월22일

심사청구일자 2019년12월06일

(85) 번역문제출일자 2016년08월12일

(65) 공개번호 10-2016-0108509

(43) 공개일자 2016년09월19일

(86) 국제출원번호 PCT/US2014/071898

(87) 국제공개번호 WO 2015/112299

국제공개일자 2015년07월30일

(30) 우선권주장

14/160,159 2014년01월21일 미국(US)

## (56) 선행기술조사문현

JP2010183192 A\*

JP4031367 B2

JP2008187661 A

\*는 심사관에 의하여 인용된 문현

전체 청구항 수 : 총 13 항

심사관 : 조성찬

## (54) 발명의 명칭 패시브 스위치-기반 위상 시프터

## (57) 요약

본 개시내용의 특정 양상들은, 입력 신호에 관해 위상 차이를 가질 수 있는 출력 신호를 생성하기 위한 장치를 제공한다. 그러한 출력 신호를 생성하기 위한 일 예시적인 위상 시프팅 회로는 일반적으로, 제 1 및 제 2 포인트들(421, 422)을 갖는 송신 라인(406<sub>2</sub>), 노드(424) 및 기준 전압 레벨(426)과 연결되는 임피던스(408<sub>1</sub>), 송신

(뒷면에 계속)

## 대 표 도

라인의 제 1 포인트 및 노드와 연결되는 제 1 스위치(SW1), 및 송신 라인의 제 2 포인트 및 노드와 연결되는 제 2 스위치(SW2)를 포함하며, 여기서, 송신 라인의 제 1 포인트에 입력되는 제 1 신호는, 제 1 및 제 2 스위치들이 개방인 경우, 송신 라인의 하나 또는 그 초과의 속성들에 기초하여, 제 2 포인트로부터 출력되는 제 2 신호와의 위상 차이를 갖는다.

(52) CPC특허분류

*H01Q 1/246* (2013.01)

*H01Q 3/38* (2013.01)

*H03H 7/20* (2013.01)

*H04L 25/0298* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

위상 시프팅(phase shifting) 회로로서,

제 1 포인트 및 제 2 포인트를 갖는 송신 라인;

노드와 그리고 기준 전압 레벨과 연결되는 임피던스;

상기 송신 라인의 상기 제 1 포인트와 그리고 상기 노드와 연결되는 제 1 스위치; 및

상기 송신 라인의 상기 제 2 포인트와 그리고 상기 노드와 연결되는 제 2 스위치를 포함하고,

상기 송신 라인의 상기 제 1 포인트에 입력되는 제 1 신호는, 상기 제 1 스위치 및 상기 제 2 스위치가 개방인 경우, 상기 송신 라인의 하나 이상의 속성들에 기초하여, 상기 제 2 포인트로부터 출력되는 제 2 신호와의 위상 차이를 가지며,

상기 위상 시프팅 회로는, 상기 제 1 스위치 및 상기 제 2 스위치가 폐쇄되는 경우, 인덕터-커패시터(LC) 공진 회로로서 동작(behavior)하도록 구성되는, 위상 시프팅 회로.

#### 청구항 2

제 1 항에 있어서,

상기 제 1 포인트 또는 상기 제 2 포인트 중 적어도 하나는 상기 송신 라인의 종단(end)인, 위상 시프팅 회로.

#### 청구항 3

제 1 항에 있어서,

상기 제 1 스위치는 상기 송신 라인의 상기 제 1 포인트와 직접 연결되고 그리고 상기 노드와 직접 연결되는, 위상 시프팅 회로.

#### 청구항 4

제 3 항에 있어서,

상기 제 2 스위치는 상기 송신 라인의 상기 제 2 포인트와 직접 연결되고 그리고 상기 노드와 직접 연결되는, 위상 시프팅 회로.

#### 청구항 5

제 1 항에 있어서,

상기 송신 라인의 상기 제 1 포인트에 입력되고 그리고 상기 LC 공진 회로의 중심 주파수와 동일한 신호 주파수를 갖는 상기 제 1 신호는, 상기 제 2 포인트로부터 출력되는 상기 제 2 신호와의 어떠한 위상 차이도 갖지 않는, 위상 시프팅 회로.

#### 청구항 6

제 1 항에 있어서,

상기 제 1 스위치 및 상기 제 2 스위치는 쌍극 단투(DPST; double-pole, single-throw) 스위치로서 구현되며, 상기 DPST 스위치의 개폐 동작은 단일 디지털 제어 라인에 의해 제어되는, 위상 시프팅 회로.

#### 청구항 7

제 1 항에 있어서,

상기 기준 전압 레벨은 전기 접지이고, 상기 임피던스는 유도성 엘리먼트를 포함하며, 상기 송신 라인의 각각의 절반은 전기 접지에 대한 커페시터로 동작하는, 위상 시프팅 회로.

#### 청구항 8

디지털 위상 시프터(shifter)로서,

각각이 제 1 항의 위상 시프팅 회로를 포함하는, 복수의 위상 시프팅 스테이지들; 및

상기 복수의 위상 시프팅 스테이지들 내의 스위치들을 선택적으로 제어하기 위한 복수의 디지털 제어 라인들을 포함하는, 디지털 위상 시프터.

#### 청구항 9

제 8 항에 있어서,

상기 송신 라인은 상기 복수의 위상 시프팅 스테이지들 각각에서 상이한 길이를 갖는, 디지털 위상 시프터.

#### 청구항 10

제 8 항에 있어서,

상기 복수의 위상 시프팅 스테이지들은, 밀리미터 단위의(on the order of millimeters) 과장들을 갖는 신호들 상에서 동작하도록 구성되는, 디지털 위상 시프터.

#### 청구항 11

제 8 항에 있어서,

상기 복수의 위상 시프팅 스테이지들은 2개의 위상 시프팅 스테이지들을 포함하는, 디지털 위상 시프터.

#### 청구항 12

무선 통신들을 위한 장치로서,

하나 이상의 송신, 수신, 또는 트랜시빙(transceiving) 회로들; 및

상기 하나 이상의 송신, 수신, 또는 트랜시빙 회로들로부터 데이터를 수신하거나 또는 상기 하나 이상의 송신, 수신, 또는 트랜시빙 회로들에 상기 데이터를 전송하도록 구성되는 프로세싱 시스템을 포함하고,

상기 회로들 각각은:

안테나;

상기 안테나와 연결되는 증폭기; 및

상기 증폭기와 연결되는 디지털 위상 시프터

를 포함하고,

상기 디지털 위상 시프터는:

각각이 제 1 항의 위상 시프팅 회로를 포함하는, 하나 이상의 위상 시프팅 스테이지들; 및

상기 하나 이상의 위상 시프팅 스테이지들 내의 스위치들을 선택적으로 제어하기 위한 하나 이상의 디지털 제어 라인들

을 포함하는, 무선 통신들을 위한 장치.

#### 청구항 13

제 12 항에 있어서,

상기 송신 라인은 상기 하나 이상의 위상 시프팅 스테이지들 각각에서 상이한 길이를 갖는, 무선 통신들을 위한 장치.

청구항 14

삭제

청구항 15

삭제

청구항 16

삭제

청구항 17

삭제

청구항 18

삭제

청구항 19

삭제

청구항 20

삭제

청구항 21

삭제

청구항 22

삭제

청구항 23

삭제

청구항 24

삭제

청구항 25

삭제

청구항 26

삭제

청구항 27

삭제

청구항 28

삭제

청구항 29

삭제

청구항 30

삭제

### 발명의 설명

#### 기술 분야

[0001] 35 U.S.C. § 119 하의 우선권 주장

[0002] [0001] 본 출원은, 2014년 1월 21일자로 출원된 미국 특허 출원 일련번호 제 14/160,159호를 우선권으로 주장하며, 상기 출원은 그 전체가 인용에 의해 본원에 통합된다.

[0003] [0002] 본 개시내용의 특정 양상들은 일반적으로 전자 회로들에 관한 것으로, 더 상세하게는, 패시브 위상 시프팅(passive phase shifting) 회로들에 관한 것이다.

#### 배경 기술

[0004] [0003] 무선 통신 네트워크들은 텔레포니(telephony), 비디오, 데이터, 메시징, 브로드캐스트들 등과 같은 다양한 통신 서비스들을 제공하기 위해 널리 배치되어 있다. 일반적으로 다중 액세스 네트워크들인 이러한 네트워크들은 이용가능한 네트워크 자원들을 공유함으로써 다수의 사용자들에 대한 통신들을 지원한다. 예를 들어, 하나의 네트워크는, EVDO(Evolution-Data Optimized), 1xRTT(1 times Radio Transmission Technology, 또는 단순히 1x), 광대역 코드 분할 다중 액세스(W-CDMA), UMTS-TDD(Universal Mobile Telecommunications System – Time Division Duplexing), HSPA(High Speed Packet Access), GPRS(General Packet Radio Service), 또는 EDGE(Enhanced Data rates for Global Evolution)를 포함하는 다양한 3G 라디오 액세스 기술(RAT; radio access technology)들 중 임의의 것을 통해 네트워크 서비스를 제공할 수 있는 3G(제 3 세대의 모바일 폰 표준들 및 기술) 시스템일 수 있다. 3G 네트워크는, 음성 호(call)들에 부가하여, 고속 인터넷 액세스 및 비디오 텔레포니를 통합하도록 발전된 광역 셀룰러 텔레폰 네트워크이다. 또한, 3G 네트워크는 다른 네트워크 시스템들보다 더 잘 설정될 수 있고 그리고 더 큰 커버리지 영역들을 제공할 수 있다. 이러한 다중 액세스 네트워크들은 또한, 코드 분할 다중 액세스(CDMA; code division multiple access) 시스템들, 시분할 다중 액세스(TDMA; time division multiple access) 시스템들, 주파수 분할 다중 액세스(FDMA; frequency division multiple access) 시스템들, 직교 주파수 분할 다중 액세스(OFDMA; orthogonal frequency division multiple access) 시스템들, 단일-캐리어 FDMA(SC-FDMA) 네트워크들, 3세대 파트너쉽 프로젝트(3GPP; 3rd Generation Partnership Project) LTE(Long Term Evolution) 네트워크들, 및 LTE-A(Long Term Evolution Advanced) 네트워크들을 포함할 수 있다.

[0005] [0004] 무선 통신 네트워크는, 다수의 모바일 스테이션들에 대한 통신을 지원할 수 있는 다수의 기지국들을 포함할 수 있다. 모바일 스테이션(MS)은 다운링크 및 업링크를 통해 기지국(BS)과 통신할 수 있다. 다운링크(또는 순방향 링크)는 기지국으로부터 모바일 스테이션으로의 통신 링크를 지칭하고, 업링크(또는 역방향 링크)는 모바일 스테이션으로부터 기지국으로의 통신 링크를 지칭한다. 기지국은 다운링크 상에서 모바일 스테이션에 데이터 및 제어 정보를 송신할 수 있고 그리고/또는 모바일 스테이션으로부터 업링크 상에서 데이터 및 제어 정보를 수신할 수 있다.

#### 발명의 내용

[0006] [0005] 본 개시내용의 특정한 양상들은 일반적으로, 종래의 패시브 위상 시프팅 회로들보다 더 낮은 손실 및 더 낮은 그룹 지연을 갖는 패시브 위상 시프팅 회로들에 관한 것이다. 그러한 위상 시프팅 회로들은, 무선 통신들을 위한 라디오 주파수(RF) 송신기들, 수신기들, 또는 트랜시버들에서 사용되는 것들과 같은 범포밍(beamforming) 회로들에서 사용될 수 있다.

[0007] [0006] 본 개시내용의 특정 양상들은 위상 시프팅 회로를 제공한다. 회로는 일반적으로, 제 1 및 제 2 포인트들(예컨대, 종단(end)들 또는 송신 라인을 따라 로케이팅되는 다른 포인트들)을 갖는 송신 라인, 노드 및 기준 전압 레벨과 연결되는 임피던스, 송신 라인의 제 1 포인트 및 노드와 연결되는 제 1 스위치, 및 송신 라인의 제 2 포인트 및 노드와 연결되는 제 2 스위치를 포함한다.

[0008] [0007] 특정 양상들에 따르면, 제 1 포인트 또는 제 2 포인트 중 적어도 하나는 송신 라인의 종단이다.

[0009] [0008] 특정 양상들에 따르면, 제 1 스위치는, 송신 라인의 제 1 포인트와 직접 연결되고 그리고/또는 노드와 직접 연결된다. 특정 양상들에 대해, 제 2 스위치는, 송신 라인의 제 2 포인트와 직접 연결되고 그리고/또는 노드와 직접 연결된다.

[0010] [0009] 특정 양상들에 따르면, 송신 라인의 제 1 포인트에 입력되는 제 1 신호는, 제 1 및 제 2 스위치들이 개방인 경우, 송신 라인의 하나 또는 그 초과의 속성들에 기초하여, 제 2 포인트로부터 출력되는 제 2 신호와의 위상 차이를 갖는다.

[0011] [0010] 특정 양상들에 따르면, 위상 시프팅 회로는, 제 1 및 제 2 스위치들이 폐쇄된 경우, 인덕터-커패시터 (LC) 공진(resonant) 회로로서 거동(behavior)하도록 구성된다. 이러한 경우에서, 송신 라인의 제 1 포인트에 입력되고 그리고 LC 공진 회로의 중심 주파수와 동일한 신호 주파수를 갖는 제 1 신호는, 송신 라인의 제 2 포인트로부터 출력되는 제 2 신호와의 어떠한 위상 차이도 갖지 않을 수 있다.

[0012] [0011] 특정 양상들에 따르면, 임피던스는 유도성 엘리먼트를 포함한다(그리고 특정 양상들에 대해서는 인덕터만을 포함할 수 있음). 특정 양상들에 대해, 제 1 및 제 2 스위치들은 쌍극 단투(DPST; double-pole, single-throw) 스위치의 일부이다. 특정 양상들에 대해, 기준 전압 레벨은 전기 접지이다.

[0013] [0012] 본 개시내용의 특정 양상들은 디지털 위상 시프터를 제공한다. 디지털 위상 시프터는 일반적으로, 복수의 위상 시프팅 스테이지들 및 복수의 디지털 제어 라인들을 포함한다. 각각의 위상 시프팅 스테이지는 통상적으로, 제 1 및 제 2 포인트들을 갖는 송신 라인, 노드 및 기준 전압 레벨과 연결되는 임피던스, 송신 라인의 제 1 포인트 및 노드와 연결되는 제 1 스위치, 및 송신 라인의 제 2 포인트 및 노드와 연결되는 제 2 스위치를 포함한다. 복수의 디지털 제어 라인들은, 복수의 위상 시프팅 스테이지들 내의 스위치들을 선택적으로 제어하도록 구성될 수 있다.

[0014] [0013] 특정 양상들에 따르면, 제 1 스위치는, 송신 라인의 제 1 포인트와 직접 연결되고 그리고/또는 노드와 직접 연결된다. 특정 양상들에 대해, 제 2 스위치는, 송신 라인의 제 2 포인트와 직접 연결되고 그리고/또는 노드와 직접 연결된다.

[0015] [0014] 특정 양상들에 따르면, 송신 라인의 제 1 포인트에 입력되는 제 1 신호는, 제 1 및 제 2 스위치들이 개방인 경우, 송신 라인의 하나 또는 그 초과의 속성들에 기초하여, 제 2 포인트로부터 출력되는 제 2 신호와의 위상 차이를 갖는다.

[0016] [0015] 특정 양상들에 따르면, 각각의 위상 시프팅 스테이지는, 제 1 및 제 2 스위치들이 폐쇄된 경우, LC 공진 회로로서 거동하도록 구성된다. 이러한 경우에서, 송신 라인의 제 1 포인트에 입력되고 그리고 LC 공진 회로의 중심 주파수와 동일한 신호 주파수를 갖는 제 1 신호는, 제 2 포인트로부터 출력되는 제 2 신호와의 어떠한 위상 차이도 갖지 않을 수 있다.

[0017] [0016] 특정 양상들에 따르면, 송신 라인은, 복수의 위상 시프팅 스테이지들 각각에서 상이한 길이를 갖는다.

[0018] [0017] 특정 양상들에 따르면, 임피던스는 유도성 엘리먼트를 포함한다(그리고 특정 양상들에 대해서는 단일 인덕터만을 포함할 수 있음). 특정 양상들에 대해, 제 1 및 제 2 스위치들은 쌍극 단투(DPST) 스위치의 일부이다. 특정 양상들에 대해, 기준 전압 레벨은 전기 접지이다.

[0019] [0018] 특정 양상들에 따르면, 복수의 위상 시프팅 스테이지들은, 대략 밀리미터 단위의 좌표들을 갖는 신호들을 통해 동작하도록 구성된다. 특정 양상들에 대해, 복수의 위상 시프팅 스테이지들은 2개의 위상 시프팅 스테이지들을 포함한다.

[0020] [0019] 본 개시내용의 특정 양상들은, 액세스 포인트(AP) 또는 사용자 단말(UT)과 같은 무선 통신들을 위한 장치를 제공한다. 장치는 일반적으로, 하나 또는 그 초과의 송신 회로, 수신 회로, 또는 트랜시빙(transceiving) 회로, 및 하나 또는 그 초과의 송신 회로, 수신 회로, 또는 트랜시빙 회로에 데이터를 전송하거나 또는 그로부터 데이터를 수신하도록 구성되는 프로세싱 시스템을 포함한다. 각각의 회로는 통상적으로, 안테나, 안테나에 연결되는 증폭기, 및 증폭기에 연결되는 디지털 위상 시프터를 포함한다. 디지털 위상 시프터는 통상적으로, 하나 또는 그 초과의 위상 시프팅 스테이지들 및 하나 또는 그 초과의 디지털 제어 라인들을 포함한다. 각각의 위상 시프팅 스테이지는 일반적으로, 제 1 및 제 2 포인트들을 갖는 송신 라인, 노드 및 기준 전압 레벨과 연결되는 임피던스, 송신 라인의 제 1 포인트 및 노드와 연결되는 제 1 스위치, 및 송신 라인의 제 2 포인트 및 노드와 연결되는 제 2 스위치를 포함한다. 디지털 제어 라인들은, 위상 시프팅 스테이지(들) 내의 스위치들을 선택적으로 제어하도록 구성될 수 있다.

[0021] [0020] 특정 양상들에 따르면, 디지털 제어 라인들은, 프로세싱 시스템이 위상 시프팅 스테이지(들) 내의 스위치들을 효과적으로 제어하도록, 프로세싱 시스템으로부터 출력된다.

### 도면의 간단한 설명

[0022] [0021] 본 개시내용의 위에 인용된 특성들이 상세하게 이해될 수 있는 방식으로, 위에서 간략하게 요약되는 더 구체적인 설명은 양상들을 참조하여 행해질 수 있는데, 이러한 양상들 중 일부는 첨부된 도면들에서 예시된다. 그러나, 이 설명은 다른 동등하게 효과적인 양상들에 대해 허용될 수 있기 때문에, 첨부된 도면들은 단지 본 개시의 특정한 통상적인 양상들만을 예시하며, 따라서, 본 개시내용의 범위에 대한 제한으로 고려되어서는 안됨이 유의되어야 한다.

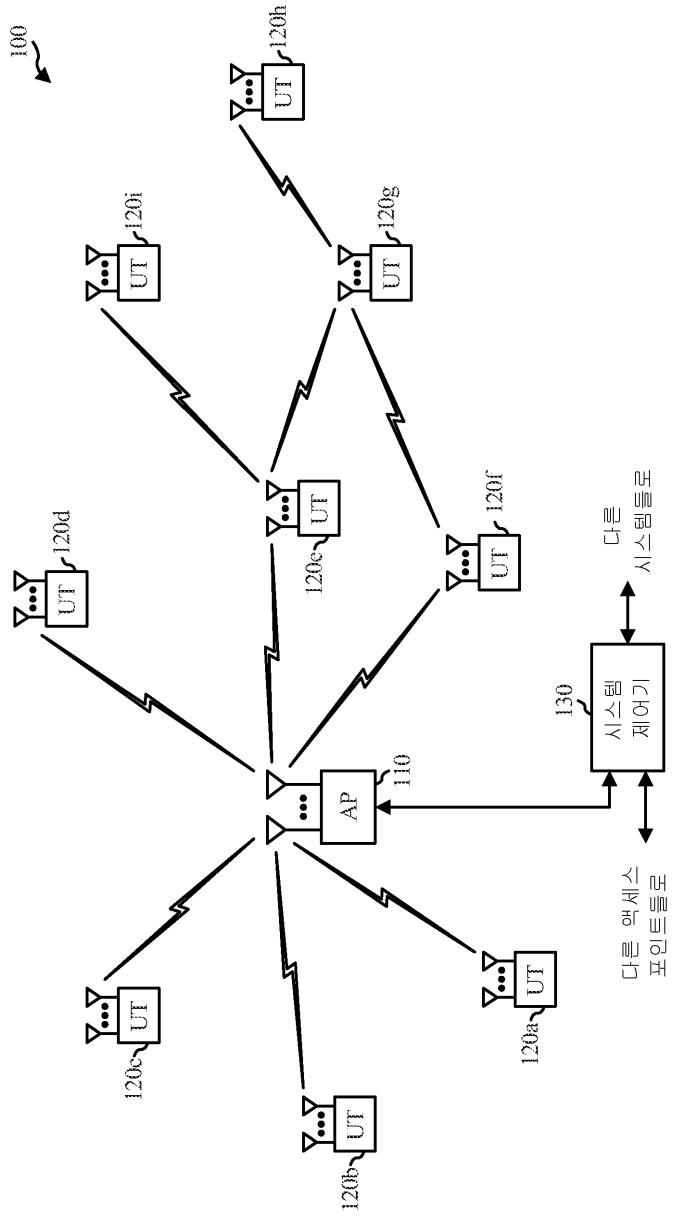

[0022] 도 1은, 본 개시내용의 특정 양상들에 따른 예시적인 무선 통신 네트워크의 도면이다.

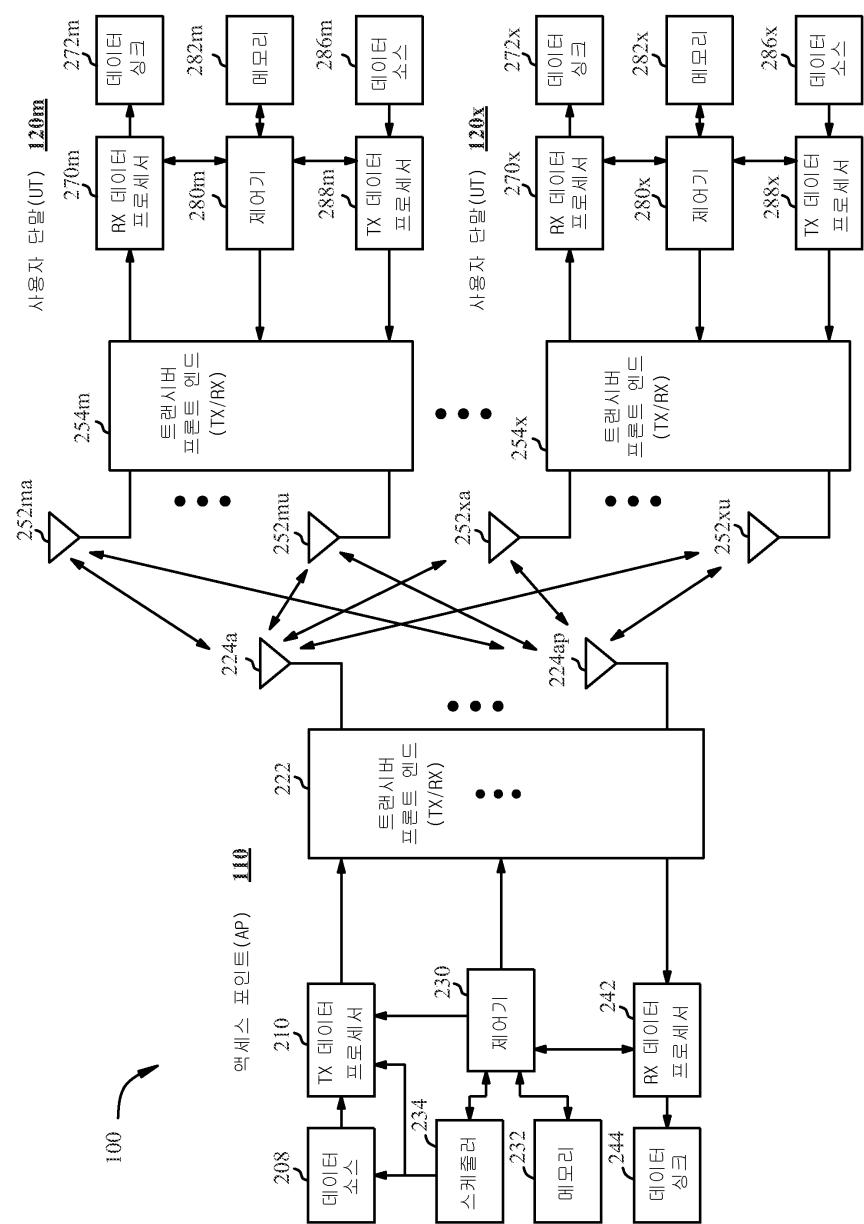

[0023] 도 2는, 본 개시내용의 특정 양상들에 따른 라디오 주파수 프론트 엔드(RFFE; radio frequency front end)를 예시하는 예시적인 액세스 포인트(AP) 및 예시적인 사용자 단말들의 블록도이다.

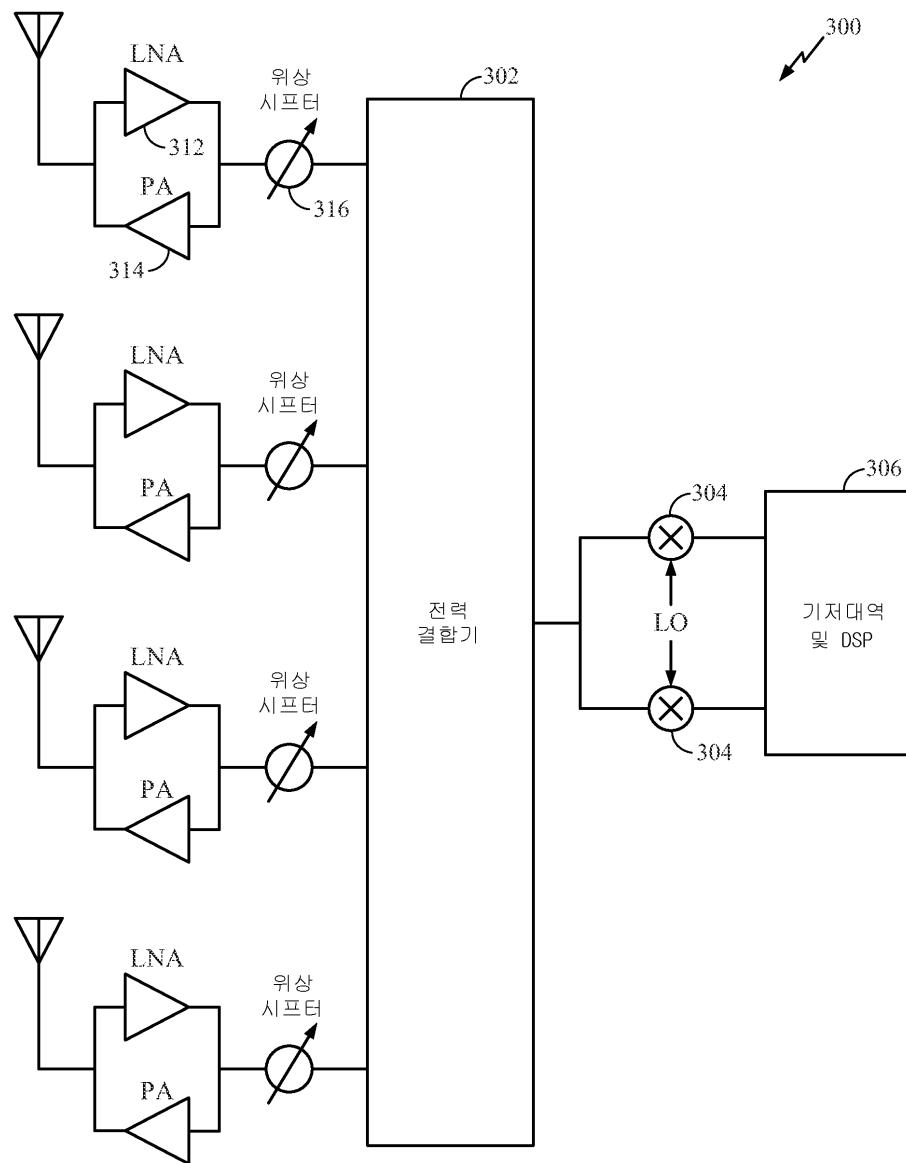

[0024] 도 3은 본 개시내용의 특정 양상들에 따른, 위상 시프터들을 사용하여 범포밍하는 것이 가능한 예시적인 RFFE의 블록도이다.

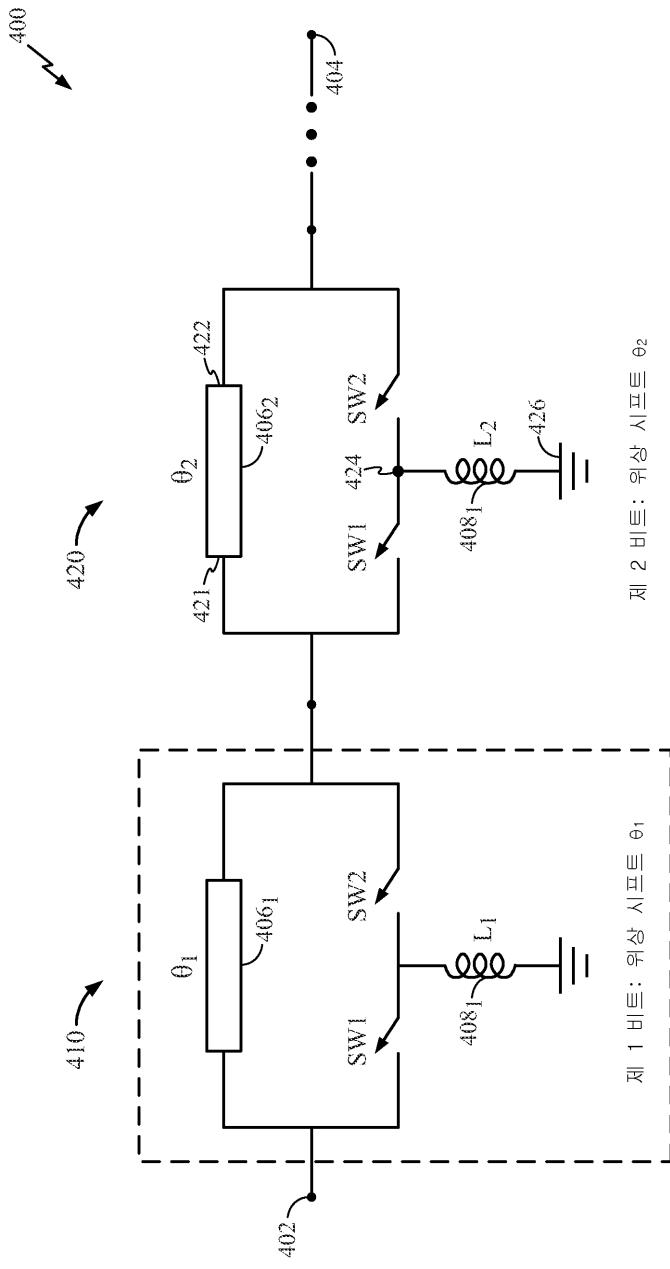

[0025] 도 4는 본 개시내용의 특정 양상들에 따른, 다수의 패시브 위상 시프팅 스테이지들을 갖는 예시적인 디지털 방식-제어 위상 시프터의 블록도이다.

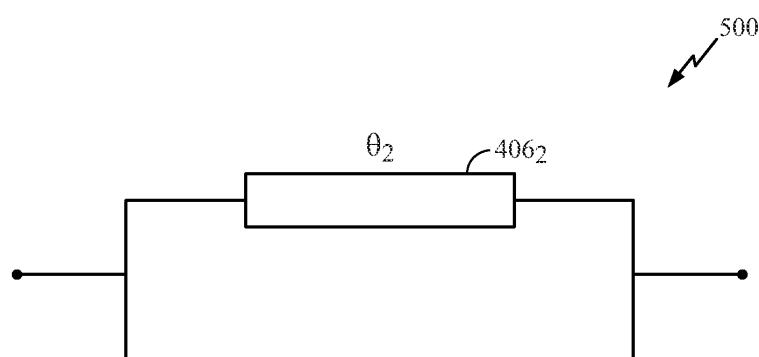

[0026] 도 5a는 본 개시내용의 특정 양상들에 따른, 스위치들 둘 모두가 개방인 경우의 도 4의 위상 시프팅 스테이지의 유효 블록도이다.

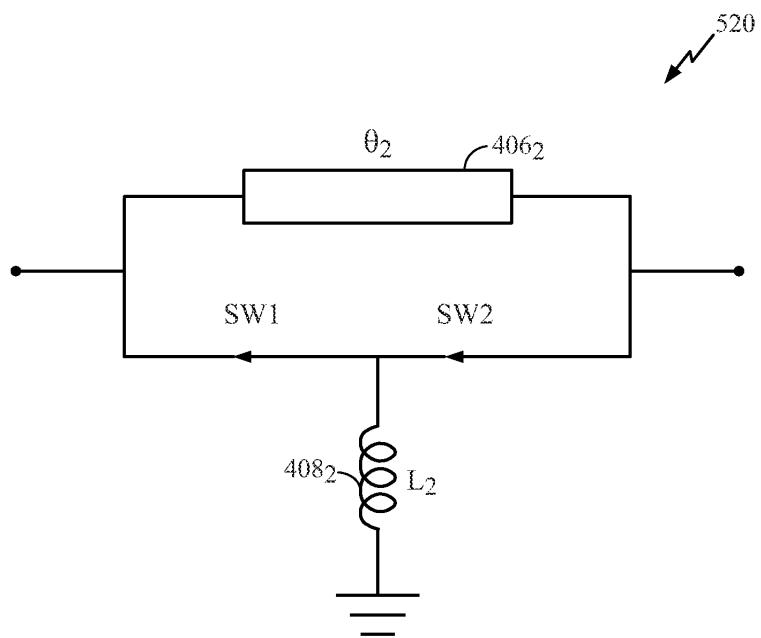

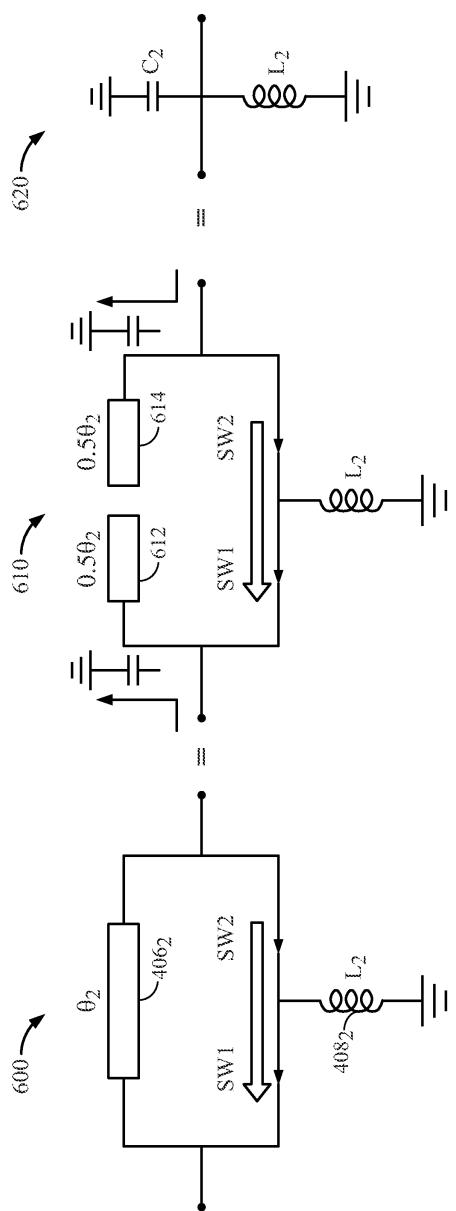

[0027] 도 5b는 본 개시내용의 특정 양상들에 따른, 스위치들 둘 모두가 폐쇄된 경우의 도 4의 위상 시프팅 스테이지의 유효 블록도이다.

[0028] 도 6은 본 개시내용의 특정 양상들에 따른, 스위치들 둘 모두가 폐쇄된 경우의 도 4의 위상 시프팅 스테이지에 대한 등가 회로들을 예시한다.

[0029] 도 7a 및 도 7b는 각각, 본 개시내용의 특정 양상들에 따른 예시적인 위상 시프팅 회로에서의 위상 시프트 대 주파수 및 그룹 지연 대 주파수의 그래프들이다.

### 발명을 실시하기 위한 구체적인 내용

[0030] [0023] 본 개시내용의 다양한 양상들이 아래에 설명된다. 본원에서의 교시들은 광범위하게 다양한 형태들로 구현될 수 있고, 본원에 개시되는 임의의 특정한 구조, 기능, 또는 둘 모두는 단지 견본일 뿐이라는 것이 명백 할 것이다. 본원에서의 교시들에 기초하여, 당업자는, 본원에 개시된 일 양상이 임의의 다른 양상들과 독립적으로 구현될 수 있고, 그리고 이들 양상들 중 2개 또는 그 초과가 다양한 방식들로 결합될 수 있다는 것을 인식 할 것이다. 예를 들어, 본원에 기재된 양상들 중 임의의 수의 양상들을 사용하여 장치가 구현될 수 있거나 또는 방법이 실시될 수 있다. 또한, 본원에 기술된 양상들 중 하나 또는 그 초과의 양상들에 부가하여 또는 그 이외의 다른 구조, 기능, 또는 구조 및 기능을 사용함으로써, 그러한 장치가 구현될 수 있거나 또는 그러한 방법이 실시될 수 있다. 또한, 양상은 청구항의 적어도 하나의 엘리먼트를 포함할 수 있다.

[0031] 용어 “예시적인”은, “예, 예증 또는 예시로서 기능하는” 것을 의미하도록 본원에서 사용된다. 본원에서 “예시적인” 것으로 설명되는 임의의 양상은 반드시 다른 양상들에 비해 바람직하거나 또는 유리한 것으로 해석될 필요는 없다.

[0032] [0025] 본원에 설명되는 기술들은, 코드 분할 다중 액세스(CDMA), 직교 주파수 분할 멀티플렉싱(OFDM), 시분할 다중 액세스(TDMA), 공간 분할 다중 액세스(SDMA), 단일 캐리어 주파수 분할 다중 액세스(SC-FDMA) 등과 같은 다양한 무선 기술들과 결합하여 사용될 수 있다. 다수의 사용자 단말들은, 상이한, (1) CDMA에 대한 직교 코드 채널들, (2) TDMA에 대한 시간 슬롯들, 또는 (3) OFDM에 대한 서브-대역들을 통해 데이터를 동시에 송신/수신할 수 있다. CDMA 시스템은, IS-2000, IS-95, IS-856, 광대역-CDMA(W-CDMA), 또는 일부 다른 표준들을 구현할 수 있다. OFDM 시스템은, IEEE(Institute of Electrical and Electronics Engineers) 802.11, IEEE 802.16, LTE(Long Term Evolution), 또는 일부 다른 표준들을 구현할 수 있다. TDMA 시스템은 GSM 또는 일부 다른 표준들을 구현할 수 있다. 이를 다양한 표준들은 당업계에 알려져 있다.

## [0026] 예시적인 무선 시스템

[0033] 도 1은, 액세스 포인트들 및 사용자 단말들을 갖는 무선 통신 시스템(100)을 예시한다. 단순화를 위해, 오직 하나의 액세스 포인트(110)가 도 1에 도시되어 있다. 액세스 포인트(AP)는 일반적으로, 사용자 단말들과 통신하는 고정 스테이션이고, 또한 기지국(BS), 이별브드 노드 B(eNB; evolved Node B), 또는 일부 다른 용어로 지칭될 수 있다. 사용자 단말은(UT) 고정식이거나 또는 이동식일 수 있고, 또한 모바일 스테이션(MS), 액세스 단말, 사용자 장비(UE), 스테이션(STA), 클라이언트, 무선 디바이스 또는 일부 다른 용어로 지칭될 수 있다. 사용자 단말은, 무선 디바이스, 이를테면 셀룰러 폰, 개인 휴대 정보 단말(PDA), 핸드헬드(handheld) 디바이스, 무선 모뎀, 랙톱 컴퓨터, 태블릿, 개인용 컴퓨터 등일 수 있다.

[0034] 액세스 포인트(110)는 임의의 주어진 순간에 다운링크 및 업링크를 통해 하나 또는 그 초파의 사용자 단말들(120)과 통신할 수 있다. 다운링크(즉, 순방향 링크)는 액세스 포인트로부터 사용자 단말들로의 통신 링크이고, 업링크(즉, 역방향 링크)는 사용자 단말들로부터 액세스 포인트로의 통신 링크이다. 사용자 단말은 또한 다른 사용자 단말과 피어-투-피어로 통신할 수 있다. 시스템 제어기(130)는 액세스 포인트들에 커플링되고, 액세스 포인트들에 대한 조정 및 제어를 제공한다.

[0035] 시스템(100)은 다운링크 및 업링크를 통한 데이터 송신을 위해 다수의 송신 및 다수의 수신 안테나들을 이용한다. 액세스 포인트(110)는, 다운링크 송신들에 대한 송신 다이버시티(diversity) 및/또는 업링크 송신들에 대한 수신 다이버시티를 달성하기 위해 다수( $N_{ap}$ )의 안테나들을 구비한다. 선택된 사용자 단말들(120)의 세트( $N_u$ )는, 다운링크 송신들을 수신하고 업링크 송신들을 송신할 수 있다. 각각의 선택된 사용자 단말은 액세스 포인트에 사용자-특정 데이터를 송신하고 그리고/또는 액세스 포인트로부터 사용자-특정 데이터를 수신한다. 일반적으로, 각각의 선택된 사용자 단말은 하나 또는 다수의 안테나들(즉,  $N_{ut} \geq 1$ )을 구비할 수 있다.  $N_u$ 개의 선택된 사용자 단말들은 동일한 수 또는 상이한 수의 안테나들을 가질 수 있다.

[0036] 무선 시스템(100)은 시분할 듀플렉스(TDD) 시스템 또는 주파수 분할 듀플렉스(FDD) 시스템일 수 있다. TDD 시스템의 경우, 다운링크 및 업링크는 동일한 주파수 대역을 공유한다. FDD 시스템의 경우, 다운링크 및 업링크는 상이한 주파수 대역들을 이용한다. 시스템(100)은 또한 송신을 위해 단일 캐리어 또는 다수의 캐리어들을 활용할 수 있다. 각각의 사용자 단말은 (예를 들어, 비용을 절감하기 위해) 단일 안테나 또는 (예를 들어, 부가적인 비용이 지원될 수 있는 경우) 다수의 안테나들을 구비할 수 있다.

[0037] 도 2는 무선 시스템(100)에서의 액세스 포인트(110) 및 2개의 사용자 단말들(120m 및 120x)의 블록도를 도시한다. 액세스 포인트(110)는  $N_{ap}$ 개의 안테나들(224a 내지 224ap)을 구비한다. 사용자 단말(120m)은  $N_{ut,m}$ 개의 안테나들(252ma 내지 252mu)을 구비하고, 사용자 단말(120x)은  $N_{ut,x}$ 개의 안테나들(252xa 내지 252xu)을 구비한다. 액세스 포인트(110)는 다운링크에 대해서는 송신 엔티티이고 업링크에 대해서는 수신 엔티티이다. 각각의 사용자 단말(120)은 업링크에 대해서는 송신 엔티티이고 다운링크에 대해서는 수신 엔티티이다. 본원에서 사용되는 바와 같이, "송신 엔티티"는 주파수 채널을 통해 데이터를 송신하는 것이 가능한 독립적으로 동작되는 장치 또는 디바이스이고, "수신 엔티티"는 주파수 채널을 통해 데이터를 수신하는 것이 가능한 독립적으로 동작되는 장치 또는 디바이스이다. 다음의 설명에서, 아래첨자 "dn"은 다운링크를 나타내고, 아래첨자 "up"은 업링크를 나타내고,  $N_{up}$ 개의 사용자 단말들은 업링크를 통한 동시 송신을 위해 선택되고,  $N_{dn}$ 개의 사용자 단말들은 다운링크를 통한 동시 송신을 위해 선택되고,  $N_{up}$ 는  $N_{dn}$ 과 동일할 수 있거나 또는 동일하지 않을 수 있고,  $N_{up}$  및  $N_{dn}$ 은 정적 값들이거나, 또는 각각의 스케줄링 인터벌(interval)에 대해 변할 수 있다. 액세스 포인트 및 사용자 단말에서 빔-스티어링(steering) 또는 일부 다른 공간 프로세싱 기술이 이용될 수 있다.

[0038] 업링크 상에서, 업링크 송신을 위해 선택된 각각의 사용자 단말(120)에서, TX 데이터 프로세서(288)는 데이터 소스(286)로부터 트래픽 데이터 및 제어기(280)로부터 제어 데이터를 수신한다. TX 데이터 프로세서(288)는 사용자 단말에 대해 선택된 레이트와 연관되는 코딩 및 변조 방식들에 기초하여 사용자 단말에 대한 트래픽 데이터  $\{d_{up}\}$ 를 프로세싱(예를 들어, 인코딩, 인터리빙 및 변조)하고,  $N_{ut,m}$ 개의 안테나들 중 하나에 데이터 심볼 스트림  $\{s_{up}\}$ 를 제공한다. 트랜시버 프론트 엔드(TX/RX)(254)(라디오 주파수 프론트 엔드(RFFE)로 또한 알려져 있음)는 각각의 심볼 스트림을 수신 및 프로세싱(예를 들어, 아날로그로 변환, 증폭, 필터링 및 주파수 상향변환)하여, 업링크 신호를 생성한다. 트랜시버 프론트 엔드(254)는 또한, 예를 들어, RF 스위치를 통해서, 송신 다이버시티를 위해  $N_{ut,m}$ 개의 안테나들 중 하나로 업링크 신호를 라우팅(route)할 수 있다. 제어기(280)는

트랜시버 프론트 엔드(254) 내의 라우팅을 제어할 수 있다.

[0033] [0039] 다수( $N_{ap}$ )의 사용자 단말들이 업링크를 통한 동시 송신을 위해 스케줄링될 수 있다. 이 사용자 단말들 각각은 자신의 프로세싱된 심볼 스트림의 세트를 업링크를 통해 액세스 포인트에 송신한다.

[0034] [0040] 액세스 포인트(110)에서,  $N_{ap}$ 개의 안테나들(224a 내지 224ap)은 업링크를 통해 송신하는 모든  $N_{ap}$ 개의 사용자 단말들로부터 업링크 신호들을 수신한다. 수신 다이버시티의 경우, 트랜시버 프론트 엔드(222)는, 프로세싱을 위해 안테나들(224) 중 하나로부터 수신되는 신호들을 선택할 수 있다. 본 개시내용의 특정 양상들의 경우, 다수의 안테나들(224)로부터 수신되는 신호들의 결합이 향상된 수신 다이버시티를 위해 결합될 수 있다. 액세스 포인트의 트랜시버 프론트 엔드(222)는 또한, 사용자 단말의 트랜시버 프론트 엔드(254)에 의해 수행되는 것과 상보적인 프로세싱을 수행하고, 복원된 업링크 데이터 심볼 스트림을 제공한다. 복원된 업링크 데이터 심볼 스트림은 사용자 단말에 의해 송신되는 데이터 심볼 스트림  $\{s_{up}\}$ 의 추정치이다. RX 데이터 프로세서(242)는 복원된 업링크 데이터 심볼 스트림을 그 스트림에 대해 사용된 레이트에 따라 프로세싱(예를 들어, 복조, 디인터리빙(deinterleave) 및 디코딩)하여, 디코딩된 데이터를 획득한다. 각각의 사용자 단말에 대해 디코딩된 데이터는 저장을 위해 데이터 싱크(244)에 제공될 수 있고, 그리고/또는 추가적 프로세싱을 위해 제어기(230)에 제공될 수 있다.

[0035] [0041] 다운링크 상에서, 액세스 포인트(110)에서, TX 데이터 프로세서(210)는, 다운링크 송신을 위해 스케줄링된  $N_{dn}$ 개의 사용자 단말들에 대한 데이터 소스(208)로부터 트래픽 데이터를, 제어기(230)로부터 제어 데이터를, 그리고 스케줄러(234)로부터 가능한 다른 데이터를 수신한다. 다양한 타입들의 데이터가 상이한 전송 채널들을 통해 전송될 수 있다. TX 데이터 프로세서(210)는 각각의 사용자 단말에 대해 선택된 레이트에 기초하여 각각의 사용자 단말에 대한 트래픽 데이터를 프로세싱(예를 들어, 인코딩, 인터리빙 및 변조)한다. TX 데이터 프로세서(210)는,  $N_{ap}$ 개의 안테나들 중 하나로부터 송신될,  $N_{dn}$ 개의 사용자 단말들 중 하나 또는 그 초과에 대한 다운링크 데이터 심볼 스트림들을 제공할 수 있다. 트랜시버 프론트 엔드(222)는, 심볼 스트림을 수신하고 프로세싱(예컨대, 아날로그로 변환, 증폭, 필터링, 및 주파수 상향변환)하여 다운링크 신호를 생성한다. 트랜시버 프론트 엔드(222)는 또한, 예를 들어, RF 스위치를 통해서, 송신 다이버시티를 위해  $N_{ap}$ 개의 안테나들(224) 중 하나 또는 그 초과로 다운링크 신호를 라우팅할 수 있다. 제어기(230)는 트랜시버 프론트 엔드(222) 내의 라우팅을 제어할 수 있다.

[0036] [0042] 각각의 사용자 단말(120)에서,  $N_{ut,m}$ 개의 안테나들(252)은 액세스 포인트(110)로부터  $N_{ap}$ 개의 다운링크 신호들을 수신한다. 사용자 단말(120)에서의 수신 다이버시티의 경우, 트랜시버 프론트 엔드(254)는 프로세싱을 위해 안테나들(252) 중 하나로부터 수신되는 신호들을 선택할 수 있다. 본 개시내용의 특정 양상들의 경우, 다수의 안테나들(252)로부터 수신되는 신호들의 결합이 향상된 수신 다이버시티를 위해 결합될 수 있다. 사용자 단말의 트랜시버 프론트 엔드(254)는 또한, 액세스 포인트의 트랜시버 프론트 엔드(222)에 의해 수행되는 것과 상보적인 프로세싱을 수행하고, 복원된 다운링크 데이터 심볼 스트림을 제공한다. RX 데이터 프로세서(270)는 복원된 다운링크 데이터 심볼 스트림을 프로세싱(예를 들어, 복조, 디인터리빙 및 디코딩)하여, 사용자 단말에 대한 디코딩된 데이터를 획득한다.

[0037] [0043] 당업자들은, TDMA, SDMA 직교 주파수 분할 다중 액세스(OFDMA), CDMA, SC-FDMA, 및 이들의 결합들과 같은 다중 액세스 방식들 중 임의의 타입을 이용하는 시스템들에 본원에 설명되는 기술들이 일반적으로 적용될 수 있다는 것을 인지할 것이다.

[0038] 예시적인 위상 시프팅 회로

[0039] [0044] 밀리미터 파장(예컨대, 60 Ghz, 77 Ghz, 또는 79 Ghz)에서 동작하는 대부분의 무선 링크들은, 송신(TX) 및 수신(RX) 둘 모두에서 빔포밍을 이용한다. 이러한 애플리케이션들 중 거의 전부는, 라디오 주파수들(RF)에서의 빔포밍을 선호한다. RF 빔포밍은 통상적으로, 도 3의 예시적인 라디오 주파수 프론트 엔드(RFFE)(300)에서 예시되는 바와 같은 위상 시프터들로 달성된다.

[0040] [0045] RFFE는 통상적으로, 하나 또는 그 초과의 송신, 수신, 또는 트랜시빙 체인들(4개의 트랜시빙 체인들이 도 3의 RFFE(300)에 도시됨); 전력 결합기/분할기(302); 막서(304); 및 기저대역 및 디지털 신호 프로세싱을 위한 프로세싱 시스템(306)을 포함한다. 각각의 송신, 수신, 또는 트랜시빙 체인은, 안테나(308), 하나 또는 그 초과의 증폭기들(예컨대, 신호 수신을 위한 저 잡음 증폭기(LNA)(310) 또는 신호 송신을 위한 전력 증폭기(PA)(312)), 및 위상 시프터(316)를 포함할 수 있다. 도 3에 도시되진 않았지만, 각각의 체인은 또한, 듀플렉

서들, 디이플렉서(diplexer)들, 커플러들, 스위치들 등과 같은 다양한 적절한 부가적인 컴포넌트들 중 임의의 것을 포함할 수 있다.

[0041] 위상 시프터들(316)은, 위상 시프터로부터 출력되는 신호가 입력 신호에 대해 위상 차이를 갖도록, 위상 시프터에 (특정 주파수로) 입력되는 신호의 위상을 시프팅하기 위해 사용된다. 다양한 RF 체인들에서 상이한 양들의 위상 시프트를 사용함으로써, 폐이징(phase)된 어레이가 생성되며, 이는, 무선 통신들에 대한 빔포밍에 대해 이용될 수 있다. 또한, RF 체인들에서 가변적 위상 시프터들을 이용함으로써, 복수의 안테나들(310)로부터의 빔포밍이 원하는 바와 같이 조정될 수 있다.

[0042] 위상 시프터들은 패시브 또는 액티브(active)일 수 있다. 패시브 위상 시프터들은 TX/RX 간에 공유될 수 있으며, 이는 상당한 실면적(real estate)을 절약한다. 부가하여, 패시브 위상 시프터들은 전력 소모가 거의 없으며, 이는 mm-파 회로들이 전력 소비적(power hungry)인 것에 기인하는 셀 폰 애플리케이션들에 대한 중대한 문제를 극복한다. 패시브 위상 시프터들은 또한 더 양호한 선형성 및 잡음 성능을 갖는다. 그러나, 패시브 위상 시프터들에 대한 가장 큰 문제들은 삽입 손실(insertion loss) 및 그룹 지연이다.

[0043] 따라서, 패시브 위상 시프팅 회로들이 필요로 하는 것은 낮은 삽입 손실 및 낮은 그룹 지연이다.

[0044] 본 개시내용의 특정 양상들은 일반적으로, 종래의 패시브 위상 시프터들과 비교하여 더 낮은 손실 및 더 낮은 그룹 지연을 갖는 패시브 위상 시프터를 제공한다.

[0050] 도 4는 본 개시내용의 특정 양상들에 따른, 다수의 패시브 위상 시프팅 스테이지들(410, 420)을 갖는 예시적인 디지털 방식-제어 위상 시프터(400)의 블록도이다. 오직 2개의 위상 시프팅 스테이지들(410, 420)만이 도 4에 도시되지만, 위상 시프터는, 단일 스테이지를 비롯하여 임의의 원하는 개수의 위상 시프팅 스테이지들을 가질 수 있다. 위상 시프팅 스테이지들(410, 420)은 직렬로 연결되고, 각각의 위상 시프팅 스테이지는 상이한 양의 위상 시프트( $\Theta$ )(예컨대,  $180^\circ$ ,  $90^\circ$ ,  $45^\circ$ ,  $22.5^\circ$  등)를 제공할 수 있다. 이러한 방식에서, 위상 시프터(400)에 대한 상이한 양들의 전체 위상 시프트가 디지털 제어 라인들을 사용함으로써 선택되어, 각각의 위상 시프팅 스테이지의 동작을 개별적으로 제어할 수 있다.

[0051] 예를 들어, 위상 시프터(400)는, 2개의 디지털 제어 라인들을 사용하여 동작하는 2-비트 위상 시프터일 수 있다. 이러한 경우에서, 제 1 위상 시프팅 스테이지(410)는, 제 1 디지털 제어 라인에 따라,  $0^\circ$  (즉, 유효하게는 어떠한 위상 시프트도 없음) 또는  $\Theta_1 = 180^\circ$  중 어느 하나로 (위상 시프터(400)의 입력 단자(402)에 도달하는) 입력 신호를 위상 시프팅할 수 있다. 제 2 위상 시프팅 스테이지(420)는, 제 2 디지털 제어 라인에 따라,  $0^\circ$  또는  $\Theta_2 = 90^\circ$  중 어느 하나로 제 1 스테이지(410)로부터의 출력 신호를 위상 시프팅하여, 위상 시프터(400)의 출력 단자(404)에서 신호를 출력할 수 있다. 이러한 방식에서,  $0^\circ$ ,  $90^\circ$ ,  $180^\circ$ , 및  $270^\circ$  ( $180^\circ$  위상 시프트에  $90^\circ$  위상 시프트가 후속함)의 위상 시프트를 사이에서 선택하는데 2개의 비트들이 사용될 수 있다.

[0052] 각각의 위상 시프팅 스테이지는, 송신 라인(406), 제 1 스위치(SW1), 제 2 스위치(SW2), 및 인더터(408)와 같은 임피던스를 포함할 수 있다. 송신 라인(406)은 제 1 및 제 2 종단들(421, 422)을 갖는다. 임피던스는 노드(424) 및 기준 전압 레벨(426)(이는, 도시된 바와 같이 전기 접지일 수 있음)과 연결된다. 제 1 스위치(SW1)는 송신 라인(406)의 제 1 종단(421) 및 노드(424)와 연결될 수 있고, 제 2 스위치(SW2)는 송신 라인(406)의 제 2 종단(422) 및 노드(424)와 연결될 수 있다. 사실, 송신 라인에 따른 임의의 2개의 포인트들이 (다양한 양들의 위상 변경과의) 연결에 대해 사용될 수 있지만, 설명의 용이성을 위해, 본 개시내용의 나머지에서는 송신 라인의 종단들(421, 422)을 사용하여 설명할 것이다.

[0053] 송신 라인(406)은, 마이크로스트립 또는 당업자들에게 알려져 있는 다양한 다른 적절한 송신 라인 균등물들 중 임의의 것을 사용하여 형성될 수 있다. 각각의 위상 시프팅 스테이지에서의 위상 시프트( $\Theta$ )는, 송신 라인(406)의 속성들(예컨대, 길이)에 의해 좌우된다. 위상 시프팅 스테이지에서의 스위치들 SW1 및 SW2는, 쌍극 단투(DPST) 스위치로서 구현될 수 있으며, 이러한 스위치의 폐쇄 및 개방 동작들은 단일 디지털 제어 라인에 의해 제어된다. 각각의 스테이지의 임피던스는, 아래에 상세히 설명되는 바와 같이, 송신 라인(406)의 위상-대-주파수 거동에 대응하도록 선택될 수 있다.

[0054] 도 4에 도시된 2-비트 위상 시프터의 경우, 예를 들어, 6dB 미만의 삽입 손실 및 3 ps 미만의 그룹 지연이 mm 파들에서 달성된다. 이를 값들 둘 모두는 종래의 패시브 위상 시프터들보다 훨씬 더 낮다.

[0055] 도 5a는 본 개시내용의 특정 양상들에 따른, 스위치들 SW1 및 SW2 둘 모두가 개방인 경우의 위상 시프

팅 스테이지(420)의 등가 회로(500)이다. 주어진 위상 시프팅 스테이지에서 스위치들 둘 모두가 개방이면, 이러한 스테이지는 송신 라인의 속성들에 기초하여 위상 차이를 갖는다.

[0051] 도 5b는 본 개시내용의 특정 양상들에 따른, 스위치들 둘 모두가 폐쇄된 경우의 위상 시프팅 스테이지(420)의 등가 회로(520)이다. 주어진 위상 시프팅 스테이지에서 스위치들 둘 모두가 폐쇄된 경우, 이러한 스테이지는, 도 6의 등가 회로들(600, 610, 및 620)에 의해 설명되는 바와 같이, 인덕터-커패시터(LC) 공진기로서 거동한다. 등가 회로(600)는 도 5b의 등가 회로(520)와 동일하다. 스위치들 SW1 및 SW2 둘 모두가 폐쇄된 경우, 송신 라인(406)은 유효하게 2개의 절반들(612, 614)로 분할되는 것으로서 고려될 수 있다. 이것은 도 6의 등가 회로(610)에서 도시된다. 송신 라인(406)의 각각의 절반(612, 614)이 커패시터로서 거동함으로써, 등가 회로(620)에 도시된 바와 같이, 스위치들 SW1 및 SW2 둘 모두가 폐쇄된 경우에는 위상 시프팅 스테이지는 LC 공진기와 같이 작동한다.

[0052] LC 공진기는 송신 라인의 위상-대-주파수 거동을 모방(mimic)한다(즉, 주파수 대 위상 변동의 양은 LC 공진기 및 송신 라인 둘 모두에 대해 동일함). 이상적인 경우에서, 중심 주파수에서의 LC 공진기의 입력과 출력 사이의 위상 차이는 0일 것이다. 주파수가 변하는 경우, 공진기 및 송신 라인의 위상 변동은 동일할 것이다. 이러한 방식에서, 스위치들 SW1 및 SW2 둘 모두가 폐쇄된 경우, 위상 시프팅 스테이지에 걸쳐 어떠한 위상 시프트도 없다(또는 거의 없음).

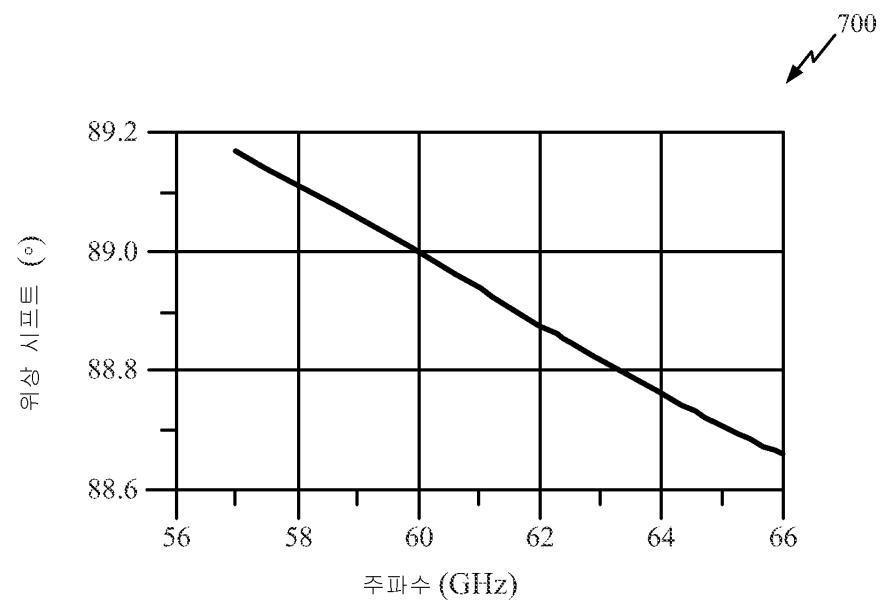

[0053] [0058] 도 7a는 본 개시내용의 특정 양상들에 따른, 도 4의 2-비트 위상 시프터(400)에서의 위상 시프트 대 주파수의 예시적인 그래프(700)이다. 그래프(700)에서 표현된 바와 같이, 위상 시프트 변동은 9 GHz에 걸쳐 대략적으로 0.5 %이다.

[0054] [0059] 도 7b는 본 개시내용의 특정 양상들에 따른, 도 4의 2-비트 위상 시프터(400)에서의 그룹 지연 대 주파수의 예시적인 그래프(710)이다. 그래프(710)에서 도시된 바와 같이, 최대 그룹 지연은 약 0.17 ps이다.

[0055] [0060] 위에 설명된 다양한 동작들 또는 방법들은 대응하는 기능들을 수행하는 것이 가능한 임의의 적절한 수단에 의해 수행될 수 있다. 이 수단은, 회로, 주문형 집적 회로(ASIC) 또는 프로세서를 포함하는(그러나, 이에 제한되지는 않는) 다양한 하드웨어 및/또는 소프트웨어 컴포넌트(들) 및/또는 모듈(들)을 포함할 수 있다. 일반적으로, 도면들에 예시된 동작들이 존재하는 경우, 이 동작들은 유사한 넘버링을 갖는 상응하는 대응 수단 + 기능(means-plus-function) 컴포넌트들을 가질 수 있다.

[0056] [0061] 예를 들어, 송신하기 위한 수단은, 송신기(예컨대, 도 2에 도시된 사용자 단말(120)의 트랜시버 프론트 엔드(254) 또는 도 2에 도시된 액세스 포인트(110)의 트랜시버 프론트 엔드(222)) 및/또는 안테나(예컨대, 도 2에 표현된 사용자 단말(120m)의 안테나들(252ma 내지 252mu) 또는 도 2에 예시된 액세스 포인트(110)의 안테나들(224a 내지 224ap))를 포함할 수 있다. 수신하기 위한 수단은, 수신기(예컨대, 도 2에 도시된 사용자 단말(120)의 트랜시버 프론트 엔드(254) 또는 도 2에 도시된 액세스 포인트(110)의 트랜시버 프론트 엔드(222)) 및/또는 안테나(예컨대, 도 2에 표현된 사용자 단말(120m)의 안테나들(252ma 내지 252mu) 또는 도 2에 예시된 액세스 포인트(110)의 안테나들(224a 내지 224ap))를 포함할 수 있다. 프로세싱하기 위한 수단 또는 결정하기 위한 수단은, 도 2에 예시된 사용자 단말(120)의 RX 데이터 프로세서(270), TX 데이터 프로세서(288) 및/또는 제어기(280)와 같은 하나 또는 그 초과의 프로세서들을 포함할 수 있는 프로세싱 시스템을 포함할 수 있다.

[0057] [0062] 본원에서 사용되는 용어 "결정"은 광범위한 동작들을 포함한다. 예를 들어, "결정"은 계산, 컴퓨팅, 프로세싱, 유도, 검사, 검색(예를 들어, 표, 데이터베이스 또는 다른 데이터 구조에서의 검색), 확인 등을 포함할 수 있다. 또한, "결정"은 수신(예를 들어, 정보 수신), 액세스(예를 들어, 메모리 내의 데이터에 액세스) 등을 포함할 수 있다. 또한, "결정"은 해결, 선택, 선정, 설정 등을 포함할 수 있다.

[0058] [0063] 본원에서 사용되는 바와 같이, 아이템들의 리스트 "중 적어도 하나"로 지칭되는 구문은 단일 멤버들을 포함하여 그 아이템들의 임의의 조합을 지칭한다. 예로서, "a, b, 또는 c 중 적어도 하나"는, a, b, c, a-b, a-c, b-c, 및 a-b-c를 커버하도록 의도된다.

[0059] [0064] 본 개시내용과 관련하여 설명되는 다양한 예시적인 로직 블록들, 모듈들, 및 회로들이 범용 프로세서, 디지털 신호 프로세서(DSP), 주문형 집적회로(ASIC), 필드 프로그래머블 게이트 어레이(FPGA) 또는 다른 프로그래머블 논리 디바이스(PLD), 이산 게이트 또는 트랜지스터 로직, 이산 하드웨어 컴포넌트들 또는 본원에 설명된 기능들을 수행하도록 설계된 이들의 임의의 결합으로 구현되거나 또는 수행될 수 있다. 범용 프로세서는 마이크로프로세서일 수도 있지만, 대안으로 프로세서는 임의의 상업적으로 이용가능한 프로세서, 제어기, 마이크로 제어기 또는 상태 머신일 수도 있다. 프로세서는 또한 컴퓨팅 디바이스들의 조합, 예를 들어 DSP 및 마이크로

프로세서의 조합, 복수의 마이크로프로세서들, DSP 코어와 결합된 하나 또는 그 초과의 마이크로프로세서들, 또는 임의의 다른 이러한 구성으로서 구현될 수 있다.

[0060] [0065] 본원에 개시된 방법들은 설명된 방법을 달성하기 위한 하나 또는 그 초과의 단계들 또는 동작들을 포함한다. 방법 단계들 및/또는 동작들은 청구항들의 범위를 벗어나지 않고 서로 교환될 수 있다. 즉, 단계들 또는 동작들의 특정 순서가 명시되지 않으면, 특정 단계들 및/또는 동작들의 순서 및/또는 사용은 청구항들의 범위를 벗어나지 않으면서 변형될 수 있다.

[0061] [0066] 설명된 기능들은 하드웨어, 소프트웨어, 펌웨어, 또는 이들의 임의의 결합으로 구현될 수 있다. 하드웨어로 구현되는 경우, 예시적인 하드웨어 구성은 무선 노드 내의 프로세싱 시스템을 포함할 수 있다. 프로세싱 시스템은 버스 아키텍처를 통해 구현될 수 있다. 버스는 프로세싱 시스템의 특정 애플리케이션 및 전체적인 설계 제약들에 따라, 임의의 개수의 상호접속 버스들 및 브리지들을 포함할 수 있다. 버스는 프로세서, 메인-판독가능 매체, 및 버스 인터페이스를 포함하는 다양한 회로들을 함께 링크시킬 수 있다. 버스 인터페이스는, 그 중에서도, 버스를 통해 프로세싱 시스템에 네트워크 어댑터를 연결시키는데 사용될 수 있다. 네트워크 어댑터는 PHY 계층의 신호 프로세싱 기능들을 구현하는데 사용될 수 있다. 사용자 단말(120)(도 1 참조)의 경우에서, 사용자 인터페이스(예컨대, 키패드, 디스플레이, 마우스, 조이스틱 등)는 또한 버스에 연결될 수 있다. 버스는 또한, 당업계에 잘 알려져 있어서 그에 따라 더 이상 추가로 설명되지 않을, 타이밍 소스들, 주변기기들, 전압 조정기들, 전력 관리 회로들 등과 같은 다양한 다른 회로들을 링크할 수 있다.

[0062] [0067] 프로세싱 시스템은, 프로세서 기능성을 제공하는 하나 또는 그 초과의 마이크로프로세서들 그리고 메인-판독가능 매체들의 적어도 일부를 제공하는 외부 메모리를 가지며 이를 모두가 외부 버스 아키텍처를 통해 다른 지원 회로와 함께 링크되는, 범용 프로세싱 시스템으로서 구성될 수 있다. 대안적으로, 프로세싱 시스템은 프로세서, 버스 인터페이스, (액세스 단말의 경우) 사용자 인터페이스, 지원 회로, 및 단일 칩으로 통합되는 메인-판독가능 매체의 적어도 일부분을 가지는 ASIC(Application Specific Integrated Circuit)를 이용하여 구현되거나, 또는 하나 또는 그 초과의 FPGA들(Field Programmable Gate Arrays), PLD들(Programmable Logic Devices), 제어기들, 상태 메인들, 게이트 로직(gated logic), 이산 하드웨어 컴포넌트들, 또는 임의의 다른 적절한 회로, 또는 이 개시내용 전반에 걸쳐 설명된 다양한 기능성을 수행할 수 있는 회로들의 임의의 결합을 이용하여 구현될 수 있다. 당업자는 전체 시스템에 부과된 전체 설계 제약들 및 특정 애플리케이션에 따라 프로세싱 시스템에 대해 설명된 기능성을 최상으로 구현하는 방법을 인지할 것이다.

[0063] [0068] 청구항들이 위에서 예시된 정확한 구성 및 컴포넌트들에 제한되지 않는다는 것이 이해될 것이다. 다양한 수정들, 변경들 및 변형들이 청구항들의 범위로부터 벗어나지 않으면서 위에 설명된 방법들 및 장치의 어레인지먼트(arrangement), 동작, 및 세부사항들에서 이루어질 수 있다.

도면

도면1

## 도면2

## 도면3

도면4

도면5a

도면5b

도면6

도면7a

도면7b