(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第6991832号**

**(P6991832)**

(45)発行日 令和4年1月13日(2022.1.13)

(24)登録日 令和3年12月10日(2021.12.10)

(51)国際特許分類

H 0 2 M      3/28 (2006.01)

G 0 3 G      21/00 (2006.01)

F I

H 0 2 M      3/28

G 0 3 G      21/00

H

3 9 8

請求項の数 10 (全19頁)

(21)出願番号 特願2017-209347(P2017-209347)

(22)出願日 平成29年10月30日(2017.10.30)

(65)公開番号 特開2019-83617(P2019-83617A)

(43)公開日 令和1年5月30日(2019.5.30)

審査請求日 令和2年10月5日(2020.10.5)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100123559

弁理士 梶 俊和

100177437

弁理士 中村 英子

(72)発明者 大島 光則

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

審査官 土井 悠生

最終頁に続く

(54)【発明の名称】 電源装置及び画像形成装置

**(57)【特許請求の範囲】****【請求項1】**

交流電源からの交流電圧を整流、平滑して入力電圧を生成する整流平滑手段と、

一次巻線、二次巻線及び補助巻線を有するトランスと、

前記入力電圧が印加される前記トランスの前記一次巻線に接続された第一のスイッチング

素子と、

前記トランスの前記二次巻線に誘起される出力電圧に応じたフィードバック電圧を出力す

るフィードバック手段と、

前記トランスの前記補助巻線に誘起される電圧に基づいて、前記入力電圧を検知する電圧

検知手段と、

前記フィードバック電圧及び前記電圧検知手段により検知した前記交流電源の電圧値に基

づいて、前記第一のスイッチング素子のオン、オフを行って前記出力電圧を制御する制御

手段と、

を備え、

前記制御手段は、前記電圧検知手段により検知した前記交流電源の電圧値が第一の閾電圧

以上の場合には、前記フィードバック電圧に基づいて前記出力電圧が第一の出力電圧とな

るように前記第一のスイッチング素子を制御する第一の状態に移行し、前記電圧検知手段

により検知した前記交流電源の電圧値が前記第一の閾電圧よりも小さい第二の閾電圧未満

の場合には、前記出力電圧が前記第一の出力電圧よりも小さい第二の出力電圧になるよう

に前記第一のスイッチング素子を制御する第二の状態に移行することを特徴とする電源装

置。

**【請求項 2】**

前記制御手段は、前記第二の状態のときには、前記第一のスイッチング素子のスイッチング動作を行う第一の期間と、前記第一のスイッチング素子のスイッチング動作を停止する第二の期間と、を交互に繰り返す間欠動作を行うことで、前記出力電圧を前記第二の出力電圧に制御することを特徴とする請求項 1 に記載の電源装置。

**【請求項 3】**

前記制御手段は、前記第一の期間では、前記第一のスイッチング素子のオン、オフを少なくとも 1 回以上、行うことを特徴とする請求項 2 に記載の電源装置。

**【請求項 4】**

前記制御手段は、前記第二の状態において、前記第一の期間に、前記電圧検知手段により前記交流電源の電圧値の検知を行うことを特徴とする請求項 3 に記載の電源装置。

10

**【請求項 5】**

前記制御手段は、前記第一の状態のときには、前記フィードバック電圧に基づいて前記第一のスイッチング素子のオンデューティを制御することを特徴とする請求項 1 から請求項 4 のいずれか 1 項に記載の電源装置。

**【請求項 6】**

前記電源装置は、前記第一のスイッチング素子のオンデューティに比例して、前記出力電圧を制御可能な電源装置であり、

前記制御手段は、前記第二の状態において、前記第一のスイッチング素子のオンデューティを低く制御することで、前記出力電圧を前記第二の出力電圧にすることを特徴とする請求項 2 から請求項 5 のいずれか 1 項に記載の電源装置。

20

**【請求項 7】**

前記制御手段は、前記第二の状態の前記第一の期間において、前記電圧検知手段の検知結果に基づき、前記第一のスイッチング素子のオンデューティを制御した後に、前記電圧検知手段によって前記交流電源の電圧値を検知することを特徴とする請求項 6 に記載の電源装置

**【請求項 8】**

前記第一のスイッチング素子は、前記トランスの一次巻線に直列に接続され、

前記制御手段は、前記第一の状態において、前記出力電圧が前記第一の出力電圧になるように、前記第一のスイッチング素子のオンデューティを制御することを特徴とする請求項 6 又は請求項 7 記載の電源装置。

30

**【請求項 9】**

前記トランスの一次巻線に並列に接続された第二のスイッチング素子と、

前記第二のスイッチング素子に直列に接続され、前記第二のスイッチング素子とともに前記トランスの一次巻線に並列に接続されるコンデンサと、

を有し、

前記制御手段は、前記第一のスイッチング素子及び前記第二のスイッチング素子がともにオフ状態となる期間を介して、前記第一のスイッチング素子及び前記第二のスイッチング素子を交互にオン状態又はオフ状態に設定し、

前記第一の状態のときには前記出力電圧が前記第一の出力電圧となり、前記第二の状態のときには前記出力電圧が前記第二の出力電圧となるように、前記第一のスイッチング素子のオンデューティを制御することを特徴とする請求項 8 に記載の電源装置。

40

**【請求項 10】**

記録材に画像形成を行う画像形成手段と、

請求項 1 から請求項 9 のいずれか 1 項に記載の電源装置と、

を備えることを特徴とする画像形成装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

50

本発明は、絶縁トランスを用いた電源装置及び画像形成装置に関し、特に入力電圧の異常時の制御に関する。

【背景技術】

【0002】

商用交流電源等から入力される交流電圧を直流電圧に変換するスイッチング電源では、商用交流電源から定格外の低電圧の交流電圧が入力された場合には、故障したり、正常に直流電圧が出力されない状態が生じる場合がある。例えば、入力電圧が所定の電圧よりも低い電圧のときにスイッチング電源が起動され、その後、スイッチング電源の出力側負荷が大きい状態になると、負荷に電力を供給することができず、再びスイッチング電源が停止してしまう状態となる場合がある。更に、スイッチング電源が起動状態と停止状態を繰り返すことにより、スイッチング電源から電力供給される負荷側のCPU等が誤動作を起こしてしまう場合がある。このような状態が発生することを防止するために、例えば特許文献1では、低電圧検知回路を用いて、入力電圧が低い場合にはスイッチング電源の出力を停止する方法が提案されている。10

【先行技術文献】

【特許文献】

【0003】

【文献】特開2007-20392号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

スイッチング電源に低電圧検知回路を設けることにより、入力電圧が低いことが検知された場合にはスイッチング電源の出力を停止させることができる。しかしながら、低電圧検知回路を設けることにより、スイッチング電源の消費電力が増えてしまうという課題が生じる。また、低電圧検知回路のインピーダンスを高くすると、低電圧検知回路における消費電力を低減することはできる。ところが、インピーダンスが高くすることにより時定数が大きくなり、その結果、低電圧検知回路の電圧検知時の応答性が低下してしまうという課題が生じる。

【0005】

本発明は、このような状況のもとでなされたもので、入力電圧が低い場合の故障や不具合を防ぐとともに、低電圧検知回路の消費電力を低減し、電圧検知時の応答性を改善することを目的とする。30

【課題を解決するための手段】

【0006】

前述の課題を解決するために、本発明は、以下の構成を備える。

【0007】

(1) 交流電源からの交流電圧を整流、平滑して入力電圧を生成する整流平滑手段と、一次巻線、二次巻線及び補助巻線を有するトランスと、前記入力電圧が印加される前記トランスの前記一次巻線に接続された第一のスイッチング素子と、前記トランスの前記二次巻線に誘起される出力電圧に応じたフィードバック電圧を出力するフィードバック手段と、前記トランスの前記補助巻線に誘起される電圧に基づいて、前記入力電圧を検知する電圧検知手段と、前記フィードバック電圧及び前記電圧検知手段により検知した前記交流電源の電圧値に基づいて、前記第一のスイッチング素子のオン、オフを行って前記出力電圧を制御する制御手段と、を備え、前記制御手段は、前記電圧検知手段により検知した前記交流電源の電圧値が第一の閾電圧以上の場合には、前記フィードバック電圧に基づいて前記出力電圧が第一の出力電圧となるように前記第一のスイッチング素子を制御する第一の状態に移行し、前記電圧検知手段により検知した前記交流電源の電圧値が前記第一の閾電圧よりも小さい第二の閾電圧未満の場合には、前記出力電圧が前記第一の出力電圧よりも小さい第二の出力電圧となるように前記第一のスイッチング素子を制御する第二の状態に移行することを特徴とする電源装置。40

**【0008】**

(2) 記録材に画像形成を行う画像形成手段と、前記(1)に記載の電源装置と、を備えることを特徴とする画像形成装置。

**【発明の効果】****【0009】**

本発明によれば、入力電圧が定格外の低電圧の状態において、スイッチング電源の出力電圧を、2次側CPU等の制御部が動作しない低い電圧に制御することで、スイッチング電源や2次側制御部の故障や不具合を防ぐことができるとともに、低電圧検知回路の消費電力を低減し、且つ、電圧検知回路の応答性を改善することができる。

**【図面の簡単な説明】****【0010】**

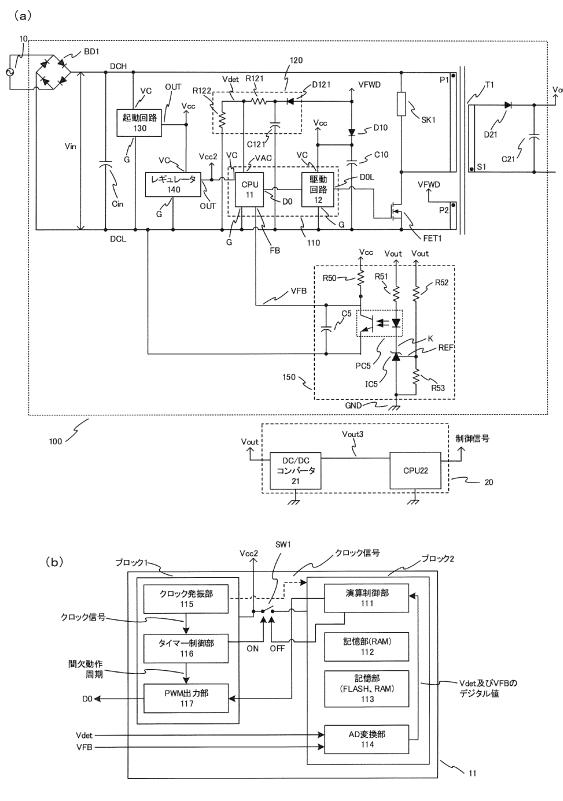

【図1】実施例1のスイッチング電源の構成を示す回路図、及びCPUの内部構成を示すプロック図

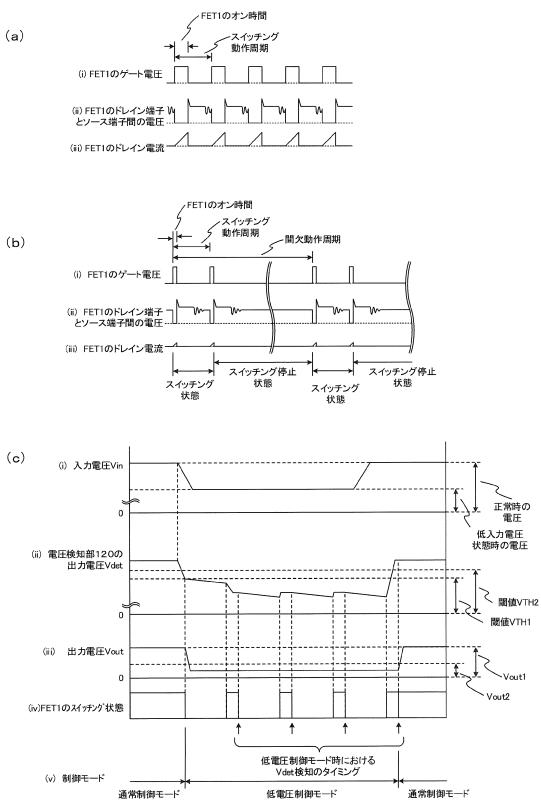

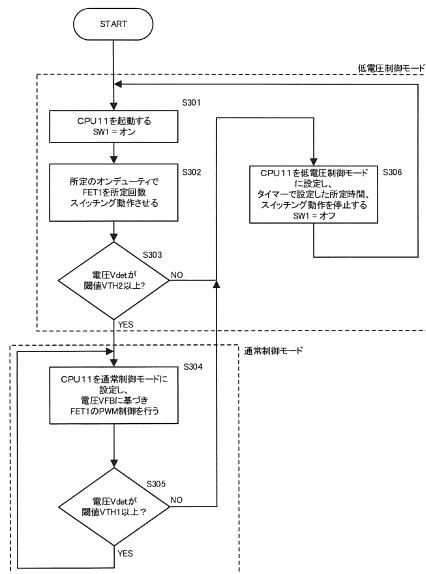

**【図2】実施例1のスイッチング電源の制御を説明するタイミングチャート****【図3】実施例1のスイッチング電源の制御シーケンスを示すフローチャート**

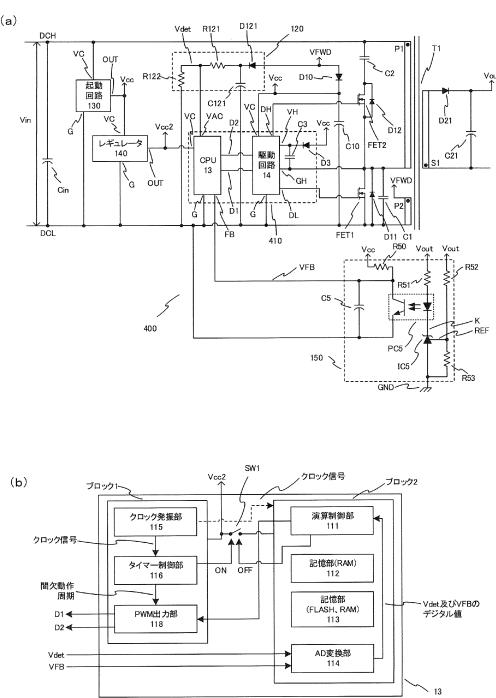

【図4】実施例2のスイッチング電源の構成を示す回路図、及びCPUの内部構成を示すプロック図

**【図5】実施例2のスイッチング電源の制御を説明するタイミングチャート****【図6】実施例2のスイッチング電源の制御シーケンスを示すフローチャート****【図7】実施例3の画像形成装置を示す図****【発明を実施するための形態】****【0011】**

以下に、図面を参照して本発明の実施の形態について詳細に説明する。

**【実施例1】****【0012】****[スイッチング電源の構成]**

図1(a)は、実施例1のスイッチング電源100の構成を示す回路図である。スイッチング電源100には、商用電源である交流電源10から交流電圧が入力され、整流平滑手段であるブリッジダイオードBD1及び平滑用のコンデンサCinで整流、平滑され、入力電圧Vinが生成される。なお、コンデンサCinの低電位側をDCL、高電位側をDCHとする。スイッチング電源100は、コンデンサCinに充電された入力電圧VinをトランジスタT1の一次側に入力し、絶縁されたトランジスタT1の二次側に出力電圧Voutを出力する。スイッチング電源100は、出力電圧Voutの電圧値が一定電圧になるように、例えば通常動作時には出力電圧Voutの電圧値を所定の電圧である電圧Vout1(第一の出力電圧)になるように制御する。なお、本実施例のスイッチング電源100の通常動作時の電圧Vout1は、一例として5Vとする。

**【0013】**

スイッチング電源100の出力電圧Voutは、負荷であるスイッチング電源100が搭載された装置(不図示)の制御部20に供給される。制御部20は、DC/DCコンバータ21及びCPU22から構成され、CPU22は、制御信号を出力してスイッチング電源100が搭載された装置(不図示)の制御を行う。DC/DCコンバータ21は、スイッチング電源100から供給された出力電圧Voutにより、電源電圧Vout3(出力電圧Vout3ともいう)を生成し、CPU22に供給するスイッチング電源である。なお、本実施例では、電源電圧Vout3の電圧の一例は、3.3Vとする。DC/DCコンバータ21は降圧コンバータであり、スイッチング電源100から出力される出力電圧Voutの電圧値が電源電圧Vout3以下の場合には、CPU22への電源電圧Vout3の出力を停止する。

**【0014】**

次に、スイッチング電源100の回路構成について説明をする。スイッチング電源100は、絶縁型のトランジスタT1と、トランジスタT1の一次側には、上述したブリッジダイオード

10

20

30

40

50

B D 1 及び平滑用のコンデンサ C i n の他に、次のような部品を有している。すなわち、第一のスイッチング素子である電界効果トランジスタ（以下、F E T という）1、電源制御部 1 1 0 、電圧検知部 1 2 0 、起動回路 1 3 0 、レギュレータ 1 4 0 、フィードバック部 1 5 0 を有している。なお、トランス T 1 の一次巻線に並列に接続されている S K 1 は、例えはダイオード等で構成される電圧クランプ回路である。一方、トランス T 1 の二次側には、トランス T 1 の出力電圧の整流、平滑を行うダイオード D 2 1 及びコンデンサ C 2 1 を有している。

#### 【 0 0 1 5 】

フライバック型のトランス T 1 は、一次巻線 P 1 、補助巻線 P 2 、二次巻線 S 1 を備えている。二次巻線 S 1 には、トランス T 1 の一次巻線 P 1 から、後述する F E T 1 のスイッチング動作によってエネルギーが供給される。補助巻線 P 2 に誘起されるフォワード電圧 V F W D は、電圧検知部 1 2 0 に供給される。また、フォワード電圧 V F W D は、整流平滑手段であるダイオード D 1 0 及びコンデンサ C 1 0 によって整流、平滑され、電源電圧 V c c として電源制御部 1 1 0 及びレギュレータ 1 4 0 に供給される。

10

#### 【 0 0 1 6 】

電源制御部 1 1 0 は、F E T 1 を制御するための回路であり、C P U 1 1 及び駆動回路 1 2 から構成される。C P U 1 1 は、クロック信号で動作する演算部を備えたワンチップのマイクロコンピュータである。C P U 1 1 は、電圧検知部 1 2 0 からの出力電圧 V d e t 及びフィードバック部 1 5 0 からのフィードバック電圧 V F B （以下、電圧 V F B という）を検知し、検知結果に基づいて駆動回路 1 2 に P W M 信号である制御信号 D 0 を出力する。駆動回路 1 2 は、C P U 1 1 から出力された制御信号 D 0 に応じて、F E T 1 のゲート端子に出力する駆動信号 D 0 L を生成する回路である。駆動回路 1 2 の V C 端子には、電源電圧 V c c が供給される。駆動回路 1 2 は、C P U 1 1 からの制御信号 D 0 がハイレベルの場合には、F E T 1 のゲート端子にハイレベルの駆動信号 D 0 L を出力し、これにより F E T 1 はオン状態となる。また、駆動回路 1 2 は、C P U 1 1 からの制御信号 D 0 がローレベルの場合には、F E T 1 のゲート端子にローレベルの駆動信号 D 0 L を出力し、これにより F E T 1 はオフ状態となる。

20

#### 【 0 0 1 7 】

電圧検知部 1 2 0 は、補助巻線 P 2 に誘起されるフォワード電圧 V F W D を整流、平滑し、抵抗分圧した電圧 V d e t を C P U 1 1 に出力する回路である。電圧検知部 1 2 0 は、フォワード電圧 V F W D を整流平滑するためのダイオード D 1 2 1 及びコンデンサ C 1 2 1 、フォワード電圧 V F W D を分圧する分圧抵抗 R 1 2 1 、R 1 2 2 によって構成される。フォワード電圧 V F W D は、コンデンサ C i n の両端に生成される入力電圧 V i n と、トランス T 1 の一次巻線 P 1 の巻数 N 1 と、補助巻線 P 2 の巻数 N 2 を用いて、以下の（式 1 ）により表すことができる。

30

$$V F W D = (N_2 / N_1) \times V_{i n} \dots \text{ (式 1)}$$

電圧検知部 1 2 0 は、フォワード電圧 V F W D を整流平滑した電圧を、分圧抵抗 R 1 2 1 、R 1 2 2 で分圧した電圧 V d e t を C P U 1 1 に出力する。一次巻線 P 1 の巻数 N 1 、補助巻線 P 2 の巻数 N 2 、及び分圧抵抗 R 1 2 1 、R 1 2 2 の抵抗値は予め決められている。そのため、C P U 1 1 は、電圧 V d e t の電圧値により、入力電圧 V i n の電圧値を検知することができる。

40

#### 【 0 0 1 8 】

起動回路 1 3 0 は、3 端子レギュレータ又は降圧型スイッチング電源であり、起動回路 1 3 0 の V C 端子に入力されたスイッチング電源 1 0 0 の入力電圧 V i n から電源電圧 V c c を生成し、O U T 端子に出力する。なお、起動回路 1 3 0 は、補助巻線 P 2 から供給されるフォワード電圧 V F W D が所定の電圧値以下の場合にのみ動作する回路であり、スイッチング電源 1 0 0 の起動時のみ、電源電圧 V c c を供給する。

#### 【 0 0 1 9 】

レギュレータ 1 4 0 は、3 端子レギュレータ又は降圧型スイッチング電源であり、V C 端子に入力された電源電圧 V c c から、C P U 1 1 を駆動する電源電圧 V c c 2 を生成し、

50

O U T 端子から C P U 1 1 の V C 端子に出力する。

#### 【 0 0 2 0 】

フィードバック手段であるフィードバック部 1 5 0 は、出力電圧  $V_{out}$  を所定の電圧値に制御するために、トランジスタ T 1 の二次側に出力された出力電圧  $V_{out}$  の電圧値に応じた情報を一次側にフィードバックする。出力電圧  $V_{out}$  の電圧は、分圧抵抗 R 5 2、R 5 3 により分圧され、シャントレギュレータ I C 5 のリファレンス端子 R E F に入力される。出力電圧  $V_{out}$  の電圧が高くなると、シャントレギュレータ I C 5 のカソード電流が増加し、出力電圧  $V_{out}$  からプルアップ抵抗 R 5 1 を介してフォトカプラ P C 1 の 2 次側ダイオードに流れる電流が増加する。これにより、フォトカプラ P C 5 の一次側フォトトランジスタに流れる電流が増加するため、コンデンサ C 5 から電荷が放電される。その結果、C P U 1 1 の F B 端子に入力される電圧  $V_{FB}$  が低下する。一方、出力電圧  $V_{out}$  が低くなると、シャントレギュレータ I C 5 のカソード電流が減少し、出力電圧  $V_{out}$  からプルアップ抵抗 R 5 1 を介してフォトカプラ P C 1 の 2 次側ダイオードを流れる電流が減少する。これにより、フォトカプラ P C 5 の一次側フォトトランジスタに流れる電流が減少するため、電源電圧  $V_{cc}$  から抵抗 R 5 0 を介してコンデンサ C 5 に電流が流れ、コンデンサ C 5 が充電され、C P U 1 1 の F B 端子に入力される電圧  $V_{FB}$  が上昇する。このように、フィードバック部 1 5 0 は、出力電圧  $V_{out}$  の電圧値の変動に応じて、C P U 1 1 の F B 端子に入力される電圧  $V_{FB}$  を変化させる。

10

#### 【 0 0 2 1 】

##### [ C P U の内部構成 ]

図 1 ( b ) は、C P U 1 1 の内部構成を示す機能ブロック図である。C P U 1 1 は、ワンチップのマイクロコンピュータであり、C P U 1 1 の内部はブロック 1 とブロック 2 に分割された構成となっている。ブロック 1 は、クロック発振部 1 1 5、タイマー制御部 1 1 6、P W M 出力部 1 1 7 を備えている。一方、ブロック 2 は、演算制御部 1 1 1、記憶部 1 1 2、記憶部 1 1 3、A D 変換部 1 1 4 を備えている。

20

#### 【 0 0 2 2 】

演算制御部 1 1 1 は、クロック発振部 1 1 5 から供給されるクロック信号に基づいて演算制御を行う制御部である。演算制御部 1 1 1 は、フラッシュ ( F L A S H ) メモリや R O M から構成される記憶部 1 1 3 に記憶された制御プログラム及びデータを、一旦、R A M で構成される記憶部 1 1 2 に読み込む。その後、演算制御部 1 1 1 は、記憶部 1 1 2 に設定された制御プログラム及びデータに基づいて逐次演算を行う。また、演算制御部 1 1 1 には、A D 変換部 1 1 4 に入力された、電圧検知部 1 2 0 から端子 V A C に入力された電圧  $V_{det}$  及び F B 端子に入力された電圧  $V_{FB}$  を A / D 変換したデジタル値が入力される。演算制御部 1 1 1 は、電圧  $V_{det}$  及び電圧  $V_{FB}$  に基づいて、P W M 出力部 1 1 7 が D 0 端子から出力する P W M 信号の設定値 ( 制御開始タイミング、周期、デューティ ) を制御し、F E T 1 のスイッチング制御を行う。なお、電圧  $V_{det}$  と制御信号 D 0 との関係については後述する。

30

#### 【 0 0 2 3 】

タイマー制御部 1 1 6 は、クロック発振部 1 1 5 から供給されるクロック信号により、後述する低電圧制御モードにおける間欠動作時の F E T 1 のスイッチング停止期間の長さを制御するタイマーの制御を行う。後述するスイッチング停止期間では、C P U 1 1 は、P W M 出力部 1 1 7 からの制御信号 D 0 の出力を停止することにより、F E T 1 のスイッチング停止状態を維持する。

40

#### 【 0 0 2 4 】

C P U 1 1 には、レギュレータ 1 4 0 より電源電圧  $V_{cc}$  が供給されている。ブロック 1 には、常に電源電圧  $V_{cc}$  が供給されているが、ブロック 2 には、スリープ制御用のスイッチ S W 1 を介して、電源電圧  $V_{cc}$  が供給される。そのため、ブロック 1 のクロック発振部 1 1 5、タイマー制御部 1 1 6、P W M 出力部 1 1 7 は、スイッチ S W 1 がオフ状態であっても、動作を継続することができる。一方、ブロック 2 の演算制御部 1 1 1 、記憶部 1 1 2 、記憶部 1 1 3 、A D 変換部 1 1 4 は、スイッチ S W 1 がオン状態で、電

50

源電圧  $V_{cc2}$  が供給されるときに限り、動作することができる。そのため、スイッチ  $S_{W1}$  がオフ状態（後述する  $CPU11$  のスリープ状態）のときには、ブロック 2 に電源電圧  $V_{cc2}$  が供給されないため、演算制御部 111、記憶部 112、記憶部 113、及び A/D 変換部 114 は動作停止の状態となる。これにより、 $CPU11$  は、スリープ状態ではブロック 2 に配置された演算制御部 111、記憶部 112、記憶部 113、A/D 変換部 114 の消費電力を低減することができる。なお、スイッチ  $S_{W1}$  がオフ状態に設定され、 $CPU11$  がスリープ状態となる条件については後述する。 $CPU11$  のブロック 2 の消費電力を低減する方法として、上述した方法に限られるものではなく、例えば、次のような方法でもよい。クロック発振部 115 から  $CPU11$  のブロック 2 に供給するクロック信号を、スイッチ  $S_{W1}$  と同様のスイッチを介して供給する構成とし、 $CPU11$  のスリープ時には、スイッチをオフ状態に設定し、クロック信号の供給を遮断する方法でもよい。

10

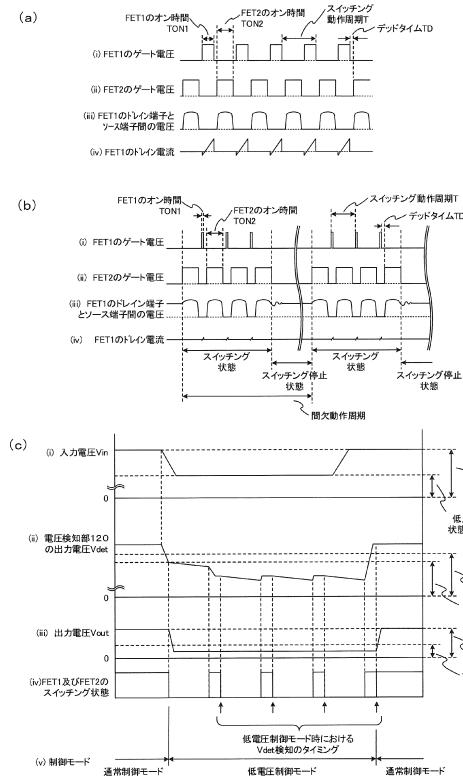

#### 【0025】

##### [FET1のスイッチング制御]

図 2 は、交流電源 10 の電圧値が正常な状態と、低電圧の異常状態における図 1(a)の FET1 のスイッチング制御を説明するタイミングチャートである。図 2(a)は、交流電源 10 の電圧値が定格内の正常な電圧値の場合の制御である通常制御モード（第一の状態）を説明する図である。図 2(a)において、(i) は FET1 のゲート端子の入力電圧（ゲート電圧）の電圧波形を示しており、(ii) は FET1 のドレイン端子とソース端子間の電圧の電圧波形を示している。また、(iii) は FET1 のドレイン端子に流れるドレイン電流の波形を示している。なお、図 2(a)の横軸は時間を示す。通常制御モードでは、電源制御部 110 の CPU11 がフィードバック部 150 からの電圧  $V_{FB}$  に基づいて、FET1 のオンデューティを制御することで、出力電圧  $V_{out}$  を所定の出力電圧である電圧  $V_{out1}$  に維持する。

20

#### 【0026】

図 2(b)では、交流電源 10 の電圧値が定格よりも低い低電圧状態の場合の制御である低電圧制御モード（第二の状態）を説明する図である。図 2(b)において、(i)、(ii)、(iii) は、図 2(a)と同様の電圧波形、電流波形であり、ここでの説明を省略する。なお、図 2(b)の横軸は時間を示す。また、括弧内の(i)～(iii)は、図 2(b)(i)～図 2(b)(iii)を指す。本実施例では、CPU11 は、電圧検知部 120 の出力電圧  $V_{det}$  に基づき、入力電圧  $V_{in}$  の電圧値が定格外の低電圧状態であることを検知すると、スイッチング電源 100 の制御を通常制御モードから低電圧制御モードに移行する。CPU11 は、低電圧制御モードでは、出力電圧  $V_{out}$  を、電圧  $V_{out2}$ （第二の出力電圧）を超えないように制御しつつ、電圧検知部 120 から出力される電圧  $V_{det}$  に基づいて、交流電源 10 の電圧値を監視する。

30

#### 【0027】

低電圧制御モードにおいて、電圧検知部 120 で入力電圧  $V_{in}$  の状態を検知するため、CPU11 は、FET1 のスイッチング動作を行う。その際、CPU11 は、出力電圧  $V_{out}$  の電圧値が電圧  $V_{out2}$  を超えないように、FET1 をスイッチング制御するスイッチング状態の期間と、スイッチング停止状態の期間と、を間欠動作周期((i))で繰り返す間欠動作を行う((iii))。本実施例における電圧  $V_{out2}$  は 2V とする。出力電圧  $V_{out}$  の電圧値が電圧  $V_{out2}$  以下のときには、電圧  $V_{out2}$  は上述した電圧  $V_{out3}$  (= 3.3V) よりも低い電圧である ( $V_{out2} < V_{out3}$ ) ため、DC/DC コンバータ 21 は出力電圧  $V_{out3}$  の出力を停止する。これにより、制御部 20 の CPU22 は電源電圧  $V_{out3}$  が供給されないため、動作停止状態となる。出力電圧  $V_{out}$  を電圧  $V_{out3}$  よりも低い電圧  $V_{out2}$  にしているのは、DC/DC コンバータ 21 からの電源電圧  $V_{out3}$  の出力を確実に停止させることで、低電圧状態において CPU22 が動作することを防ぐためである。なお、低電圧制御モードでは、出力電圧  $V_{out}$  の電圧値が、0V 以上で、かつ電圧  $V_{out2}$  (= 2V) の電圧値を超えない範囲であれば、間欠動作中の FET1 のスイッチング回数及びスイッチング停止状態

40

50

の期間は任意である。例えば、図2(b)(i)に示すように、間欠動作周期のうちのスイッチング状態におけるFET1のスイッチング回数は2回であるが、スイッチング回数は任意であり、少なくとも1回以上であればよい。なお、間欠動作周期((i))は、FET1がスイッチング状態である期間(第一の期間)((i i i))と、FET1がスイッチング停止状態である期間(第二の期間)((i i i))とを加算した時間である。また、低電圧制御モードにおいて、出力電圧Voutが通常制御モード時の出力電圧である電圧Vout1を超えないように、CPU11は、FET1のオンデューティ(オン時間)を通常制御モード時(図2(a)(i))よりも小さく制御している(i)。なお、低電圧制御モードにおけるFET1のスイッチング動作は、FET1のスイッチング動作により補助巻線P2に誘起される電圧VFWOに基づいて、入力電圧Vinを検知するために行われる。

10

#### 【0028】

図2(c)は、入力電圧Vinが正常な定格内の電圧状態から低電圧状態に遷移し、再び定格内の電圧状態に戻る場合の電圧検知部120の出力電圧Vdet、FET1のスイッチング状態、出力電圧Vout、制御モードの遷移を説明する図である。(i)はコンデンサCinの端子間電圧である入力電圧Vinの電圧を示す電圧波形であり、(i i)は、電圧検知部120の出力電圧Vdetの電圧を示す電圧波形であり、(i i i)は、出力電圧Voutの電圧を示す電圧波形である。また、(i v)は、FET1のスイッチング状態(図中、パルスが立ち上がった状態は、スイッチング動作をしている状態を示す)を示す図であり、(v)は、CPU11の制御モードを示している。なお、横軸は、時間20を示す。なお、括弧内の(i)~(v)は、図2(c)(i)~図2(c)(v)を指す。

20

#### 【0029】

交流電源10の電圧値が定格内の正常な電圧値のときは、入力電圧Vinも正常時の電圧である(i)。このとき、電圧検知部120の出力電圧Vdetは、入力電圧Vinが定格外の低電圧状態であることを検知するための閾値である電圧VTH1、及び入力電圧Vinが定格内の正常な電圧の状態であると判断する閾値である電圧VTH2よりも高い(i i)。そして、電圧Vdetが閾値VTH1よりも高い状態の間は、FET1はCPU11により、図2(a)で説明した通常制御モードによりスイッチング制御され(i v)、出力電圧Voutの電圧値は、所定電圧の電圧Vout1となる(i i i)。

30

#### 【0030】

次に、交流電源10の電圧値が低下し低電圧状態になると、入力電圧Vin((i))及び出力電圧Vdet((i i))も低下する。出力電圧Vdetが閾値である電圧VTH1未満(第二の閾電圧未満)であると、電源制御部110のCPU11は低電圧状態であることを検知し、図2(b)で説明した低電圧制御モード((v))に移行し、FET1を間欠動作させる(i v)。これにより、CPU11は、出力電圧Voutの電圧値が電圧Vout2を超えないように制御する(i i i)。

#### 【0031】

交流電源10の低電圧状態が継続する間は、CPU11は低電圧制御モードを維持し((v))、電圧検知部120からの出力電圧Vdetに基づいて入力電圧Vinの電圧検知を続ける(i i)、(i v)。CPU11は、電圧検知部120からの出力電圧Vdetが閾値の電圧VTH2以上(第一の閾電圧以上)であることを検知すると(i i)、入力電圧Vinが正常な電圧値であると判断し制御モードを低電圧制御モードから通常制御モードに戻す(v)。本実施例では、入力電圧Vinが正常状態に復帰したことを検知するための閾値である電圧VTH2を、入力電圧Vinの低電圧状態を検知する閾値である電圧VTH1より大きい電圧に設定している(i i)。これにより、制御モードの切替えにヒステリシス性を持たせている。

40

#### 【0032】

ところで、低電圧制御モードでは、FET1がスイッチング停止状態の間は、トランジスタ1の補助巻線P2には電圧が誘起されないため、フォワード電圧VFWOの電圧が0Vと

50

なる。その結果、コンデンサ C 1 2 1 に充電された電荷は放電され、電圧検知部 1 2 0 が C P U 1 1 に出力する出力電圧 V d e t の電圧値は低下し続ける((i i))。そのため、F E T 1 がスイッチング動作を行っていないときに、電源制御部 1 1 0 の C P U 1 1 が電圧 V d e t の読み込みを行うと、入力電圧 V i n の電圧値は上述した(式1)により算出される電圧値よりも低い電圧値が検知されてしまう。一方、F E T 1 がスイッチング動作状態の間は、(式1)で表されるフォワード電圧 V F W D が電圧検知部 1 2 0 に供給される。そのため、F E T 1 のスイッチング動作状態においては、電圧検知部 1 2 0 から C P U 1 1 に出力される電圧 V d e t は、入力電圧 V i n に応じた電圧値となる。そこで、低電圧制御モードでは、C P U 1 1 は、F E T 1 を所定期間、スイッチングした後に、電圧検知部 1 2 0 から出力される電圧 V d e t を検知すること((i v))で、入力電圧 V i n の電圧検知の精度を上げている。なお、本実施例では、F E T 1 がスイッチング動作を行う場合には、図2(b)(i)に示すように、複数回(2回)スイッチングを行うこととしている。図2(c)(i v)に、低電圧制御モード時における電圧 V d e t を検知するタイミングを矢印で示す。

#### 【0033】

また、F E T 1 のスイッチング停止期間中は、F E T 1 のスイッチング動作が行われないため、補助巻線 P 2 に電圧が誘起されず、フォワード電圧 V F W D が 0 V になる。そのため、レギュレータ 1 4 0 及び C P U 1 1 の動作により電力が消費され、コンデンサ C 1 0 に充電された電荷は減少し続け、電源電圧 V c c は低下する。したがって、スイッチング停止期間中に C P U 1 1 の消費電力を低減させない場合には、レギュレータ 1 4 0 が C P U 1 1 に電源電圧 V c c 2 を供給できなくなり、C P U 1 1 が動作停止することになる。そこで、本実施例では、C P U 1 1 は、スイッチ S W 1 を制御して、低電圧制御モードのスイッチング停止期間においてブロック 2 への電源電圧の供給を停止することで、C P U 1 1 の消費電力を低減させている。スイッチ S W 1 は、間欠動作のスイッチング停止期間の開始時に、演算制御部 1 1 1 によってオフ(OFF)状態に設定される(図1(b)参照)。C P U 1 1 は、F E T 1 のスイッチング動作停止期間が終了するタイミングで、タイマー制御部 1 1 6 によってスイッチ S W 1 をオン(ON)状態に設定する(図1(b)参照)。そして、演算制御部 1 1 1 が P W M 出力部 1 1 8 を制御して F E T 1 のスイッチング動作を行い、C P U 1 1 が電圧検知部 1 2 0 からの出力電圧 V d e t の検知を終了する。C P U 1 1 は、低電圧状態であることを検知すると、再びスイッチング停止状態に移行する際に、スイッチ S W 1 をオフ状態に設定する。C P U 1 1 は、低電圧制御モードの間、上述したスイッチ S W 1 の制御、及び F E T 1 のスイッチング制御を繰り返す。

#### 【0034】

##### [電圧制御モードの制御シーケンス]

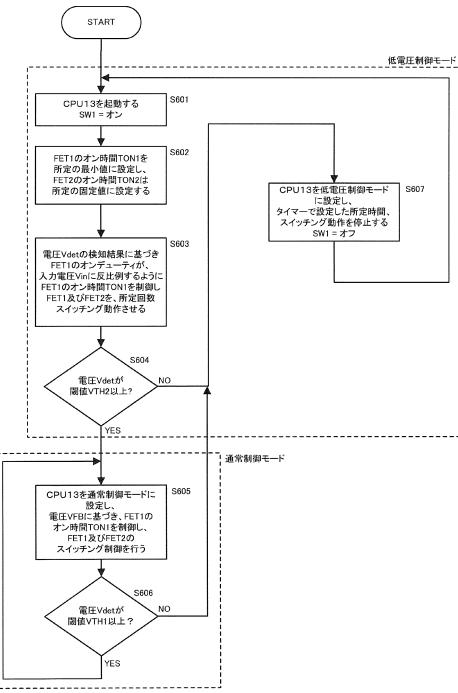

図3は、本実施例の電源制御部 1 1 0 の C P U 1 1 がスイッチング電源 1 0 0 を制御するときの制御モードの制御シーケンスを示すフローチャートである。図3に示す処理は、スイッチング電源 1 0 0 に交流電源 1 0 が印加されると起動され、スイッチング電源 1 0 0 を制御する電源制御部 1 1 0 の C P U 1 1 により実行される。

#### 【0035】

ステップ(以下、S とする)3 0 1 では、C P U 1 1 が起動し、パラメータの初期設定等の起動時の処理を行うことで、C P U 1 1 がスイッチング電源 1 0 0 を制御可能な状態にする。S 3 0 2 では、C P U 1 1 は、演算制御部 1 1 1 により P W M 出力部 1 1 8 を制御して、所定のオンドューティで F E T 1 のスイッチング動作を所定回数(例えば2回)を行う。そして、C P U 1 1 は、演算制御部 1 1 1 により A D 変換部 1 1 4 を経由して、電圧検知部 1 2 0 からの出力電圧 V d e t を取得する。

#### 【0036】

S 3 0 3 では、C P U 1 1 は、S 3 0 2 で取得した、電圧検知部 1 2 0 からの出力電圧 V d e t の電圧値が通常制御モードの閾値である電圧 V T H 2 以上かどうかを判断する。C P U 1 1 は、演算制御部 1 1 1 により電圧 V d e t の電圧値が電圧 V T H 2 以上であると判断した場合には処理を S 3 0 4 に進め、電圧 V d e t の電圧値が電圧 V T H 2 未満であ

ると判断した場合には処理を S 3 0 6 に進める。

#### 【 0 0 3 7 】

S 3 0 4 では、 C P U 1 1 は、 演算制御部 1 1 1 により A D 変換部 1 1 4 を経由して、 F B 端子に入力されたフィードバック部 1 5 0 から出力される電圧 V F B を取得する。そして C P U 1 1 は、 演算制御部 1 1 1 により P W M 出力部 1 1 8 を制御して、 F E T 1 のスイッチング動作 ( P W M 制御 ) を行う。すなわち、 演算制御部 1 1 1 は、 P W M 出力部 1 1 8 を制御して、 出力電圧 V o u t の電圧値が所定の電圧である電圧 V o u t 1 になるように、 電圧 V F B に基づいて、 F E T 1 のオンデューティを制御して、 F E T 1 のスイッチング動作 ( P W M 制御 ) を行う。

#### 【 0 0 3 8 】

S 3 0 5 では、 C P U 1 1 は、 演算制御部 1 1 1 により A D 変換部 1 1 4 を経由して、 電圧検知部 1 2 0 からの出力電圧 V d e t を取得し、 電圧 V d e t の電圧値が通常制御モードの閾値である電圧 V T H 1 以上かどうかを判断する。C P U 1 1 は、 演算制御部 1 1 1 により電圧 V d e t の電圧値が電圧 V T H 1 以上であると判断した場合には処理を S 3 0 4 に戻す。一方、 C P U 1 1 は、 演算制御部 1 1 1 により電圧 V d e t の電圧値が電圧 V T H 1 未満であると判断した場合には、 入力電圧 V i n が低電圧状態であると判断し、 処理を S 3 0 6 に進める。

#### 【 0 0 3 9 】

S 3 0 6 では、 C P U 1 1 は、 演算制御部 1 1 1 によりスイッチ S W 1 をオフ状態に設定した後に、 タイマー制御部 1 1 6 に設定した所定時間の間、 処理を停止する。その後、 タイマー制御部 1 1 6 に設定した所定時間が経過すると、 S 3 0 1 の処理が起動される。

#### 【 0 0 4 0 】

上述した S 3 0 1 、 S 3 0 2 、 S 3 0 3 、 S 3 0 6 の処理は、 低電圧制御モードの処理である。S 3 0 1 、 S 3 0 2 、 S 3 0 3 、 S 3 0 6 の処理を繰り返すことで、 図 2 ( c ) ( i i i ) で説明したように、 出力電圧 V o u t の電圧値を 0 V 以上で、 かつ電圧 V o u t 2 以下の、 C P U 2 2 が起動しない電圧に制御することができる。また、 上述した S 3 0 4 、 S 3 0 5 の処理は、 通常制御モード時の制御シーケンスである。以上説明した制御シーケンスにより、 スイッチング電源 1 0 0 の C P U 1 1 は、 トランジスタ T 1 の補助巻線 P 2 を利用して入力電圧 V i n の電圧値検知を行う。そして、 定格外の低電圧入力時には、 C P U 1 1 は、 出力電圧 V o u t の電圧値を電圧 V o u t 2 以下の電圧に制御することで、 スイッチング電源 1 0 0 の負荷である C P U 2 2 の動作を停止させる。

#### 【 0 0 4 1 】

ところで、 本実施例のスイッチング電源 1 0 0 では、 補助巻線 P 2 に誘起されるフォワード電圧 V F W D を利用して、 入力電圧 V i n の電圧値を検知している。入力電圧 V i n の電圧値を検知する方法には、 例えば入力電圧 V i n を抵抗分圧することで、 C P U 1 1 で入力電圧 V i n を検知する方法もある。しかしながら、 入力電圧 V i n は、 電圧検知部 1 2 0 に入力されるフォワード電圧 V F W D と比べて、 電圧値が大きい。そのため、 入力電圧 V i n を抵抗分圧で直接検知する方法を用いた場合には、 分圧抵抗に求められる電力定格が大きくなり、 その結果、 電圧検知回路の回路規模、 及び消費電力が大きくなってしまうことになる。また、 電圧検知回路の消費電力を低減するために、 入力電圧 V i n を抵抗分圧で検知する電圧検知回路の抵抗値を高くすると、 時定数が大きくなり、 電圧検知回路の応答性が下がる。その結果、 入力電圧 V i n を抵抗分圧で直接検知する場合には、 交流電源 1 0 からの交流電圧が低電圧状態になってから、 スイッチング電源 1 0 0 の出力電圧 V o u t の電圧値を電圧 V o u t 2 以下に低下させるまでに要する時間が長くなってしまうことになる。

#### 【 0 0 4 2 】

一方、 本実施例のスイッチング電源 1 0 0 は、 トランジスタ T 1 の補助巻線 P 2 に誘起されたフォワード電圧 V F W D に基づいて、 入力電圧 V i n の電圧検知を行っている。フォワード電圧 V F W D は、 前述した ( 式 1 ) に示すように、 トランジスタ T 1 の補助巻線 P 2 の巻数 N 2 を、 トランジスタ T 1 の一次巻線 P 1 の巻数 N 1 よりも小さくすることで、 フォワード電

10

20

30

40

50

圧 V F W D を入力電圧 V i n よりも小さくすることができる。そのため、電圧検知部 120 の分圧抵抗 R 121、R 122 に必要な電力定格も小さくすることができ、電圧検知回路の回路規模も小さくすることができる。その結果、本実施例では、電圧検知部 120 の消費電力の低減と、電圧検知応答性の両立を実現することができる。

#### 【 0 0 4 3 】

以上説明したように、本実施例によれば、低入力電圧状態において、スイッチング電源の出力電圧を低く制御でき、且つ、低電圧検知回路の消費電力を低減し、電圧検知時の応答性を改善することができる。

#### 【 実施例 2 】

#### 【 0 0 4 4 】

実施例 1 では、フライバック型のトランスを備えたスイッチング電源を用いた実施例について説明した。実施例 2 では、フライバック型のトランスにアクティブクランプ回路が実装されたスイッチング電源を用いた実施例について説明する。

#### 【 0 0 4 5 】

##### [ スイッチング電源の構成 ]

図 4 ( a ) は、実施例 2 のスイッチング電源 400 の構成を示す回路図である。本実施例のスイッチング電源 400 は、実施例 1 で説明したスイッチング電源 100 に対して、F E T 2 ( 第二のスイッチング素子 ) 及び電圧共振用のコンデンサ C 2 を用いたアクティブクランプ回路を追加した点が異なる。また、本実施例では、電源制御部 110 の代わりに電源制御部 410 を用いており、F E T ( F E T 1 及び F E T 2 ) の制御方法が、スイッチング電源 100 とは異なる。以下では、実施例 1 のスイッチング電源 100 と異なる構成のアクティブクランプ回路、及び電源制御部 410 について説明することとし、実施例 1 と同様の回路構成については、同一の符号を用いることにより、ここでの説明を省略する。なお、図 4 ( a ) では、交流電源 10 及びスイッチング電源 400 のブリッジダイオード B D 1 を省略している。また、スイッチング電源 400 の出力電圧 V o u t は、負荷であるスイッチング電源 400 が搭載された装置 ( 不図示 ) の制御部 20 に供給されることとし、制御部 20 の構成については、実施例 1 と同様とし、ここでの説明は省略する。

#### 【 0 0 4 6 】

トランス T 1 の一次巻線 P 1 には、一次巻線 P 1 に直列に接続された F E T 1 と、一次巻線 P 1 に並列に接続され、コンデンサ C 2 と F E T 2 が直列に接続されたアクティブクランプ回路と、が設けられている。スイッチング電源 400 はアクティブクランプ回路により、F E T 1 がオフする際に F E T 1 のドレイン端子とソース端子間に生じるサージ電圧を抑えることができるため、一般に、スイッチング電源 100 と比べて、大電力を出力することが可能である。なお、F E T 1 と並列に接続された電圧共振用コンデンサ C 1 は、F E T 1 及び F E T 2 のオフ時の損失を低減するために設けられている。また、ダイオード D 1 1 は F E T 1 のボディダイオードであり、ダイオード D 1 2 は F E T 2 のボディダイオードである。

#### 【 0 0 4 7 】

電源制御部 410 は、F E T 1 及び F E T 2 を制御するための回路であり、C P U 13 及び駆動回路 14 から構成される。C P U 13 は、実施例 1 の C P U 11 と同様に、クロック信号で動作する演算部を備えたワンチップのマイクロコンピュータである。C P U 13 は、電圧検知部 120 からの電圧 V d e t 及びフィードバック部 150 からの電圧 V F B を検知し、検知結果に基づいて駆動回路 14 に P W M 信号である制御信号 D 1 、D 2 を出力する。C P U 13 は、F E T 1 に加えて F E T 2 の制御を行っている点が、実施例 1 の C P U 11 と異なる。駆動回路 14 は、実施例 1 の駆動回路 12 と同様に、C P U 13 から出力された制御信号 D 1 、D 2 に応じて、F E T 1 、F E T 2 のゲート端子に出力する駆動信号 D L 、D H を生成する回路である。駆動回路 14 には、F E T 1 に加えて F E T 2 も駆動するために、コンデンサ C 3 及びダイオード D 3 で構成されるチャージポンプ回路によって、V H 端子に電源電圧が供給されている。

#### 【 0 0 4 8 】

10

20

30

40

50

### [CPUの内部構成]

図4(b)は、CPU13の内部構成を示す機能ブロック図である。CPU13は、ワンチップのマイクロコンピュータであり、CPU13の内部は、実施例1のCPU11と同様に、ブロック1とブロック2に分割された構成となっている。ブロック1は、クロック発振部115、タイマー制御部116、PWM出力部118を備えている。一方、ブロック2は、演算制御部111、記憶部112、記憶部113、AD変換部114を備えている。なお、CPU13では、実施例1のCPU11のPWM出力部117の代わりに、PWM出力部118を用いている。PWM出力部118は、FET1の制御信号D1に加え、FET2の制御信号D2を出力する。CPU13のその他の構成については、実施例1のCPU11と同様であり、同じ構成には同じ符号を付することで、ここでの説明を省略する。

10

### [0049]

#### [FET1のスイッチング制御]

図5は、交流電源10の電圧値が正常な状態と、低電圧の異常状態における図4(a)のFET1及びFET2のスイッチング制御を説明するタイミングチャートである。図5(a)は、交流電源10の電圧値が定格内の正常な電圧値の場合の制御である通常制御モードを説明する図である。図5(a)では、(i)はFET1のゲート端子の入力電圧(ゲート電圧)の電圧波形を示し、(ii)はFET2のゲート端子の入力電圧(ゲート電圧)の電圧波形を示し、(iii)はFET1のドレイン端子とソース端子間の電圧の電圧波形を示している。また、図5(a)において、(iv)はFET1のドレイン端子に流れるドレイン電流の波形を示している。なお、図5(a)の横軸は時間を示す。

20

### [0050]

次に、スイッチング電源400の通常制御モード時のスイッチング動作について説明する。スイッチング電源400では、電源制御部410がFET1とFET2を、FET1及びFET2がオフ状態となるデッドタイムTDを設けて交互にオン、オフさせる制御を行う。スイッチング電源400の出力電圧Voutは、FET1のオンデューティによって制御される。スイッチング電源400では、出力電圧Voutは、次の(式2)のように表すことができる。

$$V_{out} = V_{in} \times (N_2 / N_1) \times (T_{ON1} / T) \dots \quad (\text{式2})$$

### [0051]

ここで、Vinは入力電圧、N1はトランスT1の一次巻線P1の巻数、N2はトランスT1の二次巻線S1の巻数、TON1はFET1のオン時間、TはFET1のスイッチング動作周期(FET2のスイッチング動作周期でもある)である。

30

### [0052]

図5(a)の通常制御モードでは、電源制御部410のCPU13は、FET2を一定のオン時間TON2でスイッチングし、FB端子に入力される電圧VFBに基づいてFET1のオン時間TON1を変えることで、FET1のオンデューティを制御している。これにより、CPU13は、フィードバック部150の電圧VFBに基づいて、出力電圧Voutを所定の電圧値である電圧Vout1となるように制御する。

40

### [0053]

図5(b)では、交流電源10の電圧値が定格よりも低い低電圧状態の場合の制御である低電圧制御モードを説明する図である。図2(b)において、(i)、(ii)、(iii)、(iv)は、図5(a)と同様の電圧波形、電流波形であり、ここでの説明を省略する。なお、図5(b)の横軸は時間を示す。また、括弧内の(i)～(iv)は、図5(b)(i)～図5(b)(iv)を指す。

### [0054]

本実施例では、CPU13は、電圧検知部120の出力電圧Vdetに基づき、入力電圧Vinの電圧値が定格外の低電圧状態であることを検知すると、スイッチング電源400の制御を通常制御モードから低電圧制御モードに移行する。CPU13は、低電圧制御モードにおいて、電圧Vdetに基づき、FET1のオン時間TON1を変えることでFE

50

T1のオンデューティを制御し、出力電圧Voutが電圧Vout2を超えないように制御している。

#### 【0055】

CPU13は、フィードバック部150の出力電圧VFBに基づき、FET1のオンデューティを制御することで、出力電圧Voutを、設定された所定の電圧に制御することができる。更に、CPU13は電圧Vdetに基づき入力電圧Vinを検知することで、(式2)に示すように出力電圧に応じたFET1のオンデューティを算出することができ、入力電圧Vinに応じた適切なオン時間TON1でFET1をスイッチングすることができる。また、低電圧制御モードにおいて、電源制御部410は、FET1及びFET2を間欠動作させている((iv))。本実施例における電圧Vout2は、一例として、2Vとする。出力電圧Voutの電圧値が電圧Vout2以下のときには、電圧Vout2は上述した電圧Vout3(=3.3V)よりも低い電圧である(Vout2 < Vout3)ため、DC/DCコンバータ21は出力電圧Vout3の出力を停止する。これにより、CPU22は電源電圧Vout3が供給されないため、動作停止状態となる。なお、低電圧制御モードにおいて、間欠動作中のFET1及びFET2のスイッチング回数とスイッチング停止状態の期間は任意である。例えば、図5(b)(i)、(ii)に示すように、間欠動作周期のうちのスイッチング状態におけるFET1及びFET2のスイッチング回数は3回である。なお、間欠動作周期は、FET1及びFET2がスイッチング状態である期間と、FET1及びFET2がスイッチング停止状態である期間とを加えた時間である((iv))。なお、低電圧制御モードにおけるFET1のスイッチング動作は、FET1のスイッチング動作により電圧検知部120から出力される電圧Vdetに基づいて入力電圧Vinを検知するためである。

10

20

30

#### 【0056】

以上説明したように、電源制御部410のCPU13は、低電圧制御モードにおいて、電圧Vdetに基づいてFET1のオン時間TON1を変えることで、FET1のオンデューティを制御し出力電圧Voutが電圧Vout2を超えないように制御している。図5(c)は、入力電圧Vinが定格内の電圧状態から低電圧状態に遷移し、再び定格内の電圧状態に戻る場合の電圧検知部120の出力電圧Vdet、FET1及びFET2のスイッチング状態、出力電圧Vout、制御モードの遷移を説明する図である。(i)はコンデンサCinの端子間電圧である入力電圧Vinの電圧を示す電圧波形であり、(ii)は、電圧検知部120の出力電圧Vdetの電圧を示す電圧波形であり、(iii)は、出力電圧Voutの電圧を示す電圧波形である。また、(iv)は、FET1及びFET2のスイッチング状態(図中、パルスが立ち上がった状態はスイッチング動作している状態を示す)を示す図であり、(v)は、CPU13の制御モードを示している。なお、横軸は、時間を示す。低電圧制御モードでは、CPU13は、FET1及びFET2を所定期間、スイッチングした後に、電圧検知部120から出力される電圧Vdetを検知すること(iv)で、入力電圧Vinの電圧検知の精度を上げている。なお、制御モードの遷移は、実施例1の図2(c)で説明したスイッチング電源100の制御モードの遷移と同様のため、詳細な説明は省略する。

40

#### 【0057】

##### [電圧制御モードの制御シーケンス]

図6は、本実施例の電源制御部410のCPU13がスイッチング電源400を制御するときの制御モードの制御シーケンスを示すフローチャートである。図6に示す処理は、スイッチング電源400がオンされると起動され、スイッチング電源400を制御する電源制御部410のCPU13により実行される。

#### 【0058】

S601では、CPU13が起動し、パラメータの初期設定等の起動時の処理を行うことで、スイッチング電源400の制御が可能な状態にする。S602では、CPU13は、演算制御部111によりFET1のオン時間TON1を所定の最小値に設定し、FET2のオン時間TON2を所定の固定値に設定する。CPU13は、FET1のオン時間TON1を所定の最大値に設定する。

50

N1を最小値に設定することで、入力電圧V<sub>in</sub>の電圧値が高い場合においても、出力電圧V<sub>out</sub>の電圧値が電圧V<sub>out2</sub>より大きい電圧値になることを防止することができる。

#### 【0059】

S603では、CPU13は、演算制御部111によりPWM出力部118を制御して、S602で設定されたFET1の最小のオン時間TON1及びFET2の所定のオン時間TON2に基づき、FET1及びFET2のスイッチング制御を開始する。そして、CPU13は、演算制御部111によりAD変換部114を経由して、電圧検知部120からの出力電圧V<sub>det</sub>を取得する。CPU13は、FET1のオンデューティが、取得した電圧V<sub>det</sub>に基づいて算出した入力電圧V<sub>in</sub>の値に反比例するように、FET1のオン時間TON1を制御しつつ、所定回数、FET1及びFET2のスイッチング制御を継続する。

10

#### 【0060】

S604では、CPU13は、演算制御部111によりAD変換部114を経由して、FET1の所定回数の最後のスイッチング動作時の電圧検知部120から取得した電圧V<sub>det</sub>の電圧値が電圧V<sub>TH2</sub>以上かどうかを判断する。CPU13は、演算制御部111により電圧V<sub>det</sub>の電圧値が電圧V<sub>TH2</sub>以上であると判断した場合には処理をS605に進め、電圧V<sub>det</sub>の電圧値が電圧V<sub>TH2</sub>未満であると判断した場合には処理をS607に進める。

#### 【0061】

S605では、CPU13は、演算制御部111によりAD変換部114を経由して、FB端子に入力されたフィードバック部150から出力される電圧V<sub>FB</sub>を取得する。そしてCPU13は、演算制御部111によりPWM出力部118を制御して、FET1及びFET2のスイッチング制御を行う。すなわち、演算制御部111は、PWM出力部118を制御して、出力電圧V<sub>out</sub>の電圧値が所定の電圧である電圧V<sub>out1</sub>になるように、電圧V<sub>FB</sub>に基づいて、FET1のオン時間TON1を制御しFET1及びFET2のスイッチング制御を行う。

20

#### 【0062】

S606では、CPU13は、演算制御部111によりAD変換部114を経由して、電圧検知部120からの出力電圧V<sub>det</sub>を取得し、電圧V<sub>det</sub>の電圧値が通常制御モードの閾値である電圧V<sub>TH1</sub>以上かどうかを判断する。CPU13は、演算制御部111により電圧V<sub>det</sub>の電圧値が電圧V<sub>TH1</sub>以上であると判断した場合には処理をS605に戻す。一方、CPU13は、演算制御部111により電圧V<sub>det</sub>の電圧値が電圧V<sub>TH1</sub>未満であると判断した場合には、入力電圧V<sub>in</sub>が低電圧状態であると判断し、処理をS607に進める。

30

#### 【0063】

S607では、CPU13は、演算制御部111によりスイッチSW1をオフ状態に設定した後に、タイマー制御部116に設定した所定時間の間、処理を停止する。その後、タイマー制御部116により設定された所定時間が経過すると、S601の処理が起動される。

40

#### 【0064】

上述したS601、S602、S603、S604、S607の処理は、低電圧制御モードの処理である。S601、S602、S603、S604、S607の処理を繰り返すことで、図5(c)(iii)に示すように、出力電圧V<sub>out</sub>の電圧値を0V以上で、かつ電圧V<sub>out2</sub>以下の、CPU22が起動されない電圧に制御することができる。また、上述したS605、S606の処理は、通常制御モード時の制御シーケンスである。

#### 【0065】

ところで、本実施例のスイッチング電源400において、FET1のオン時間TON1が短すぎると、トランジistor1に供給されるエネルギーが不足する。そのため、FET1のオン時間TON1が短すぎると、補助巻線P2から出力されるフォワード電圧V<sub>FWD</sub>は、

50

上述した（式1）で表される電圧値より小さい電圧値になり、入力電圧 $V_{in}$ の検知精度が下がってしまう。一方、FET1のオン時間TON1が長すぎると、低電圧制御モード時の出力電圧 $V_{out}$ の電圧値が電圧 $V_{out2}$ 以上の電圧値になる。その結果、負荷側の制御部20のDC/DCコンバータ21から電源電圧 $V_{out3}$ がCPU22に供給され、CPU22が動作してしまう。したがって、低電圧制御モードでは、入力電圧 $V_{in}$ に応じてFET1のオン時間TON1を適切な値に制御することで、CPU22を動作させてしまうことなく、且つ、精度の高い入力電圧 $V_{in}$ の電圧検知が可能となる。

#### 【0066】

本実施例のスイッチング電源400は、入力電圧 $V_{in}$ と、FET1のオンデューティによって出力電圧 $V_{out}$ が決まるため、低電圧制御モードにおいても同様に、出力電圧 $V_{out}$ の電圧値が電圧 $V_{out2}$ を超えないように予測して制御することができる。その結果、FET1のオンデューティが入力電圧 $V_{in}$ に反比例するように、FET1のオン時間TON1を電圧 $V_{det}$ に基づいて制御することで、低電圧制御モードから通常制御モードに復帰する際に、入力電圧 $V_{in}$ の電圧検知精度を高めることができる。

10

#### 【0067】

以上説明したように、本実施例によれば、低入力電圧状態において、スイッチング電源の出力電圧を低く制御でき、且つ、低電圧検知回路の消費電力を低減し、電圧検知時の応答性を改善することができる。

#### 【実施例3】

20

#### 【0068】

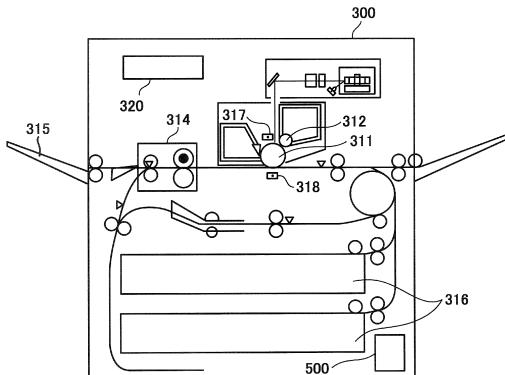

実施例1、2で説明した電源装置であるスイッチング電源回路は、例えば画像形成装置の低圧電源、即ちコントローラ（制御部）やモータ等の駆動部へ電力を供給する電源として適用可能である。以下に、実施例1、2の電源装置が適用される画像形成装置の構成を説明する。

#### 【0069】

##### [画像形成装置の構成]

画像形成装置の一例として、レーザビームプリンタを例に挙げて説明する。図7に電子写真方式のプリンタの一例であるレーザビームプリンタの概略構成を示す。レーザビームプリンタ300は、静電潜像が形成される像担持体としての感光ドラム311、感光ドラム311を一様に帯電する帯電部317（帯電手段）、感光ドラム311に形成された静電潜像をトナーで現像する現像部312（現像手段）を備えている。そして、感光ドラム311に現像されたトナー像をカセット316から供給された記録材としてのシート（不図示）に転写部318（転写手段）によって転写して、シートに転写したトナー像を定着器314で定着してトレイ315に排出する。この感光ドラム311、帯電部317、現像部312、転写部318が画像形成部である。また、レーザビームプリンタ300は、実施例1、2で説明したスイッチング電源100、400に対応する電源装置500を備えている。なお、実施例1、2の電源装置500を適用可能な画像形成装置は、図7に例示したものに限定されず、例えば複数の画像形成部を備える画像形成装置であってもよい。更に、感光ドラム311上のトナー像を中間転写ベルトに転写する一次転写部と、中間転写ベルト上のトナー像をシートに転写する二次転写部を備える画像形成装置であってもよい。

30

#### 【0070】

レーザビームプリンタ300は、画像形成部による画像形成動作や、シートの搬送動作を制御する、実施例1、2の制御部20のCPU22に相当するコントローラ320を備えている。コントローラ320は、実施例1、2に記載のスイッチング電源100、400である電源装置500から、実施例1、2の制御部20のDC/DCコンバータ21を経由して電力を供給される。また、実施例1、2に記載のスイッチング電源100、400である電源装置500は、感光ドラム311を回転するため、又はシートを搬送する各種ローラ等を駆動するためのモータ等の駆動部に電力を供給する。更に、実施例1、2に記載のスイッチング電源100、400である電源装置500は、交流電源からの交流電圧

40

50

が下がり、入力電圧  $V_{in}$  が所定の電圧よりも低い定電圧状態になると、制御モードが通常制御モードから低電圧制御モードに移行する。そして、電源装置 500 は、低電圧制御モードでは、実施例 1、2 の制御部 20 の DC / DC コンバータ 21 が電源電圧  $V_{out}$  3 の出力を停止し、その結果、コントローラ 320 が動作停止する出力電圧  $V_{out}$  が電圧  $V_{out}$  2 となる制御を行う。また、電源装置 500 は、交流電源からの交流電圧が正常な通常時の電圧に戻り、入力電圧  $V_{in}$  が所定の電圧よりも高い通常の電圧状態になると、制御モードを低電圧制御モードから通常制御モードに移行する。そして、電源装置 500 は、通常制御モードでは、実施例 1、2 の制御部 20 の DC / DC コンバータ 21 が電源電圧  $V_{out}$  3 を出力し、その結果、コントローラ 320 が動作可能となる出力電圧  $V_{out}$  の電圧  $V_{out}$  1 となる制御を行う。

10

#### 【0071】

以上説明したように、本実施例によれば、低入力電圧状態において、スイッチング電源の出力電圧を低く制御でき、且つ、低電圧検知回路の消費電力を低減し、電圧検知時の応答性を改善することができる。

#### 【符号の説明】

#### 【0072】

T 1 トランス

1 F E T

1 1 C P U

1 2 0 電圧検知部

1 5 0 フィードバック部

20

30

40

50

【図面】

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

10

20

30

【図 7】

40

50

---

フロントページの続き

(56)参考文献 特開2010-288334(JP,A)

特開2017-112797(JP,A)

特開2017-028783(JP,A)

特開2017-017846(JP,A)

米国特許出願公開第2016/0087519(US,A1)

(58)調査した分野 (Int.Cl., DB名)

H02M 1/00 - 7/98

G03G 13/34

G03G 15/00

G03G 15/36

G03G 21/00 - 21/02

G03G 21/14

G03G 21/20