(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6666043号

(P6666043)

(45) 発行日 令和2年3月13日(2020.3.13)

(24) 登録日 令和2年2月25日(2020.2.25)

(51) Int.Cl.

F 1

HO4N 5/378 (2011.01)

HO3M 1/56 (2006.01)HO4N 5/378

HO3M 1/56

請求項の数 42 (全 28 頁)

(21) 出願番号 特願2016-83424 (P2016-83424)

(22) 出願日 平成28年4月19日 (2016.4.19)

(65) 公開番号 特開2017-55382 (P2017-55382A)

(43) 公開日 平成29年3月16日 (2017.3.16)

審査請求日 平成31年3月13日 (2019.3.13)

(31) 優先権主張番号 特願2015-178255 (P2015-178255)

(32) 優先日 平成27年9月10日 (2015.9.10)

(33) 優先権主張国・地域又は機関

日本国 (JP)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100094112

弁理士 岡部 譲

(74) 代理人 100101498

弁理士 越智 隆夫

(74) 代理人 100106183

弁理士 吉澤 弘司

(74) 代理人 100128668

弁理士 斎藤 正巳

(72) 発明者 戸塚 洋史

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

最終頁に続く

(54) 【発明の名称】撮像装置及び撮像システム

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の列をなすように配列され、光電変換により入射光に応じた画素信号を出力する複数の画素を備え、前記画素信号を前記列ごとに A/D 変換してデジタル値を得る撮像装置であって、

前記複数の列の各々に対応して設けられ、同一の前記画素信号に対して、第 1 の A/D 変換を行って得られた前記デジタル値を保持する第 1 メモリ群及び第 2 の A/D 変換を行って得られた前記デジタル値を保持する第 2 メモリ群を有し、

前記第 1 メモリ群は、N + 1 ビット (N は自然数) のビット幅を有し、前記第 1 の A/D 変換によって得られた前記デジタル値のうちの最下位ビットから第 N + 1 ビットまでを保持し、

前記第 2 メモリ群は、N + 1 ビットより大きい M ビット (M は自然数) のビット幅を有し、前記第 2 の A/D 変換によって得られた前記デジタル値のうちの最下位ビットから第 M ビットまでを保持する

ことを特徴とする撮像装置。

## 【請求項 2】

前記複数の列の各々に対応して設けられ、前記画素信号と、逐次比較動作のための電圧信号とを比較して二分探索を逐次行うことにより、前記第 1 の A/D 変換及び前記第 2 の A/D 変換を行う逐次比較型 A/D 変換回路を更に有することを特徴とする請求項 1 に記載の撮像装置。

**【請求項 3】**

前記第1メモリ群に保持された前記デジタル値から、前記第2メモリ群に保持された前記デジタル値のうちの最下位ビットから第 $N + 1$ ビットまでの値を減算した差分値を取得し、

前記第2メモリ群に保持された前記デジタル値の2倍と、前記差分値とを加算して得られた値を出力する

ことを特徴とする請求項1又は2に記載の撮像装置。

**【請求項 4】**

前記第1メモリ群に保持された前記デジタル値から、前記第2メモリ群に保持された前記デジタル値のうちの最下位ビットから第 $N + 1$ ビットまでの値を減算した差分値を取得し、

前記差分値が、 $- (2^N - 1) [LSB]$ 以上であり、かつ $2^N - 1 [LSB]$ 以下の場合は、前記第2メモリ群に保持された前記デジタル値の2倍と、前記差分値とを加算して得られた値を出力し、

前記差分値が、 $2^N - 1 [LSB]$ より大きい場合は、前記第2メモリ群に保持された前記デジタル値の2倍と、前記差分値とを加算し、前記加算の結果から $2^{N+1}$ を減算して得られた値を出力し、

前記差分値が、 $- (2^N - 1) [LSB]$ より小さい場合は、前記第2メモリ群に保持された前記デジタル値の2倍と、前記差分値とを加算し、前記加算の結果に $2^{N+1}$ を加算して得られた値を出力する

ことを特徴とする請求項1又は2に記載の撮像装置。

**【請求項 5】**

複数の列をなすように配列され、光電変換により入射光に応じた画素信号を出力する複数の画素と、

前記複数の列の各々に対応して設けられ、前記画素信号と、時間に応じて変化する参照信号との大小関係の比較を行い、前記大小関係が反転したことに応じて制御信号を出力する比較器と、

前記参照信号の変化が開始してからの経過時間を示すカウント値を出力するカウンタと、

前記複数の列の各々に対応して設けられ、前記制御信号が出力された時点における前記カウント値を保持する第1メモリ群及び第2メモリ群と、を有し、

前記比較器は、同一の前記画素信号に対して、第1の比較及び第2の比較を含む複数回の前記比較を行い、

前記第1メモリ群及び前記第2メモリ群は、前記第1の比較により得られた前記カウント値及び前記第2の比較により得られた前記カウント値をそれぞれ保持し、

前記第1メモリ群は、 $N + 1$ ビット( $N$ は自然数)のビット幅を有し、前記第1の比較によって得られた前記カウント値のうちの最下位ビットから第 $N + 1$ ビットまでを保持し、

前記第2メモリ群は、 $N + 1$ ビットより大きいMビット( $M$ は自然数)のビット幅を有し、前記第2の比較によって得られた前記カウント値のうちの最下位ビットから第 $M$ ビットまでを保持する

ことを特徴とする撮像装置。

**【請求項 6】**

前記カウント値は、複数のビットを含むグレイコードであることを特徴とする請求項5に記載の撮像装置。

**【請求項 7】**

前記カウンタは、前記比較器の各々に対して共通の前記カウント値を出力することを特徴とする請求項5又は6に記載の撮像装置。

**【請求項 8】**

前記比較器は、前記複数の列の各々に対応して1個ずつ設けられることを特徴とする請

10

20

30

40

50

求項 5 乃至 7 のいずれか 1 項に記載の撮像装置。

**【請求項 9】**

前記比較器は、前記複数の列の各々に対応して複数個ずつ設けられることを特徴とする

請求項 5 乃至 7 のいずれか 1 項に記載の撮像装置。

**【請求項 10】**

前記複数の列のうちの同一の列に対応する複数の前記比較器は、互いに異なる入力オフ

セット電圧を有することを特徴とする請求項 9 に記載の撮像装置。

**【請求項 11】**

前記第 1 の比較の際に前記カウンタが出力する前記カウント値は、 $N + 1$  ビットのグレ

イコードであり、

10

前記第 2 の比較の際に前記カウンタが出力する前記カウント値は、 $M$  ビットのグレイコ

ードである

ことを特徴とする請求項 5 乃至 10 のいずれか 1 項に記載の撮像装置。

**【請求項 12】**

前記第 1 の比較の際に前記カウンタが出力するカウント値と、前記第 2 の比較の際に前

記カウンタが出力するカウント値とは同一である

ことを特徴とする請求項 5 乃至 10 のいずれか 1 項に記載の撮像装置。

**【請求項 13】**

前記第 2 メモリ群は、

$N + 1$  ビットのビット幅を有し、前記第 2 の比較によって得られた前記カウント値のう

ちの最下位ビットから第  $N + 1$  ビットまでを保持する複数のメモリと、

20

$M - (N + 1)$  ビットのビット幅を有し、前記第 2 の比較によって得られた前記カウン

ト値と前記第 1 の比較によって得られた前記カウント値との差分に相当するカウント値の

うちの第  $N + 2$  ビットから第  $M$  ビットまでを保持するリップルカウンタと

を有することを特徴とする請求項 5 乃至 12 のいずれか 1 項に記載の撮像装置。

**【請求項 14】**

前記比較器は、前記第 1 の比較及び前記第 2 の比較の際に、同一の前記参照信号を用い

て前記比較を行い、

前記第 1 の比較及び前記第 2 の比較は、互いに異なる期間に行われる

ことを特徴とする請求項 5 乃至 13 のいずれか 1 項に記載の撮像装置。

30

**【請求項 15】**

前記比較器は、

前記第 1 の比較の際に、前記画素信号と、第 1 の参照信号との大小関係を比較し、

前記第 2 の比較の際に、前記画素信号と、前記第 1 の参照信号とは異なる第 2 の参照信

号との大小関係を比較する

ことを特徴とする請求項 5 乃至 14 のいずれか 1 項に記載の撮像装置。

**【請求項 16】**

前記第 1 メモリ群に保持された前記カウント値から、前記第 2 メモリ群に保持された前

記カウント値のうちの最下位ビットから第  $N + 1$  ビットまでの値を減算した差分値を取得

し、

40

前記第 2 メモリ群に保持された前記カウント値の 2 倍と、前記差分値とを加算して得ら

れた値を出力する

ことを特徴とする請求項 5 乃至 15 のいずれか 1 項に記載の撮像装置。

**【請求項 17】**

前記第 1 メモリ群に保持された前記カウント値から、前記第 2 メモリ群に保持された前

記カウント値のうちの最下位ビットから第  $N + 1$  ビットまでの値を減算した差分値を取得

し、

前記差分値が、 $- (2^N - 1) [LSB]$  以上であり、かつ  $2^N - 1 [LSB]$  以下の

場合は、前記第 2 メモリ群に保持された前記カウント値の 2 倍と、前記差分値とを加算し

て得られた値を出力し、

50

前記差分値が、 $2^N - 1$  [ LSB ] より大きい場合は、前記第 2 メモリ群に保持された前記カウント値の 2 倍と、前記差分値とを加算し、前記加算の結果から $2^{N+1}$  を減算して得られた値を出力し、

前記差分値が、 $- (2^N - 1)$  [ LSB ] より小さい場合は、前記第 2 メモリ群に保持された前記カウント値の 2 倍と、前記差分値とを加算し、前記加算の結果に $2^{N+1}$  を加算して得られた値を出力する

ことを特徴とする請求項 5 乃至 15 のいずれか 1 項に記載の撮像装置。

#### 【請求項 18】

複数の列をなすように配列され、光電変換により入射光に応じた画素信号を出力する複数の画素と、

10

前記複数の列の各々に対応して設けられ、各々が前記画素信号に対して A/D 変換を行う複数の A/D 変換回路であって、前記複数の A/D 変換回路の各々は、1 つの前記画素信号に対して第 1 の A/D 変換及び第 2 の A/D 変換を含む複数の A/D 変換を行う、複数の A/D 変換回路と、

前記第 1 の A/D 変換により得られた第 1 のデジタル値と、前記第 2 の A/D 変換により得られた第 2 のデジタル値とを加算及び / 又は平均する信号処理回路と、を有し、

前記信号処理回路は、前記第 1 のデジタル値の最下位ビットから第 N + 1 ビットまでと、前記第 2 のデジタル値の最下位ビットから第 M ビットまでとを用いるよう構成されており、N は自然数であり、M は N + 1 よりも大きい自然数であり、前記第 1 のデジタル値の少なくとも第 M ビットは前記加算及び前記平均のいずれにも用いられない、

20

ことを特徴とする撮像装置。

#### 【請求項 19】

前記複数の A/D 変換回路の各々は、前記画素信号と、逐次比較動作のための電圧信号とを比較して二分探索を逐次行うことにより、前記第 1 の A/D 変換及び前記第 2 の A/D 変換を行う逐次比較型 A/D 変換回路を更に有することを特徴とする請求項 18 に記載の撮像装置。

#### 【請求項 20】

前記信号処理回路は、

前記第 1 のデジタル値から前記第 2 のデジタル値のうちの最下位ビットから第 N + 1 ビットまでの値を減算した差分値を取得し、

30

前記第 2 のデジタル値の 2 倍と、前記差分値とを加算して得られた値を出力する

ことを特徴とする請求項 18 又は 19 に記載の撮像装置。

#### 【請求項 21】

前記信号処理回路は、

前記第 1 のデジタル値から、前記第 2 のデジタル値のうちの最下位ビットから第 N + 1 ビットまでの値を減算した差分値を取得し、

前記差分値が、 $- (2^N - 1)$  [ LSB ] 以上であり、かつ $2^N - 1$  [ LSB ] 以下の場合は、前記第 2 のデジタル値の 2 倍と、前記差分値とを加算して得られた値を出力し、

前記差分値が、 $2^N - 1$  [ LSB ] より大きい場合は、前記第 2 のデジタル値の 2 倍と、前記差分値とを加算し、前記加算の結果から $2^{N+1}$  を減算して得られた値を出力し、

40

前記差分値が、 $- (2^N - 1)$  [ LSB ] より小さい場合は、前記第 2 のデジタル値の 2 倍と、前記差分値とを加算し、前記加算の結果に $2^{N+1}$  を加算して得られた値を出力する

ことを特徴とする請求項 18 又は 19 に記載の撮像装置。

#### 【請求項 22】

複数の列の各々に対応して設けられ、各々が光電変換により入射光に応じて生成されたアナログ信号に対して A/D 変換を行う複数の A/D 変換回路であって、前記複数の A/D 変換回路の各々は、1 つの前記アナログ信号に対して第 1 の A/D 変換及び第 2 の A/D 変換を含む複数の A/D 変換を行う、複数の A/D 変換回路と、

前記第 1 の A/D 変換により得られた第 1 のデジタル値と、前記第 2 の A/D 変換により得

50

られた第 2 のデジタル値とを加算及び / 又は平均する信号処理回路と、を有し、

前記信号処理回路は、前記第 1 のデジタル値の最下位ビットから第 N + 1 ビットまでと

、前記第 2 のデジタル値の最下位ビットから第 M ビットまでとを用いるよう構成されてお

り、N は自然数であり、M は N + 1 よりも大きい自然数であり、前記第 1 のデジタル値の

少なくとも第 M ビットは前記加算及び前記平均のいずれにも用いられない、

ことを特徴とする信号処理装置。

**【請求項 2 3】**

前記複数の A/D 変換回路の各々は、前記アナログ信号と、逐次比較動作のための電圧信号とを比較して二分探索を逐次行うことにより、前記第 1 の A/D 変換及び前記第 2 の A/D 変換を行う逐次比較型 A/D 変換回路を更に有することを特徴とする請求項 2 2 に記載の信号処理装置。

10

**【請求項 2 4】**

前記信号処理回路は、

前記第 1 のデジタル値から前記第 2 のデジタル値のうちの最下位ビットから第 N + 1 ビットまでの値を減算した差分値を取得し、

前記第 2 のデジタル値の 2 倍と、前記差分値とを加算して得られた値を出力することを特徴とする請求項 2 2 又は 2 3 に記載の信号処理装置。

**【請求項 2 5】**

前記信号処理回路は、

前記第 1 のデジタル値から、前記第 2 のデジタル値のうちの最下位ビットから第 N + 1 ビットまでの値を減算した差分値を取得し、

20

前記差分値が、 $- (2^N - 1) [LSB]$  以上であり、かつ  $2^N - 1 [LSB]$  以下の場合は、前記第 2 のデジタル値の 2 倍と、前記差分値とを加算して得られた値を出力し、

前記差分値が、 $2^N - 1 [LSB]$  より大きい場合は、前記第 2 のデジタル値の 2 倍と、前記差分値とを加算し、前記加算の結果から  $2^{N+1}$  を減算して得られた値を出力し、

前記差分値が、 $- (2^N - 1) [LSB]$  より小さい場合は、前記第 2 のデジタル値の 2 倍と、前記差分値とを加算し、前記加算の結果に  $2^{N+1}$  を加算して得られた値を出力する

ことを特徴とする請求項 2 2 又は 2 3 に記載の信号処理装置。

**【請求項 2 6】**

30

複数の列をなすように配列され、光電変換により入射光に応じた画素信号を出力する複数の画素と、

前記複数の列の各々に対応して設けられ、各々が前記画素信号と時間に応じて変化する参照信号との比較における大小関係を判定し、前記大小関係が反転したことに応じて制御信号を出力する、複数の比較器と、

前記参照信号の変化が開始してからの経過時間を示すカウント値を出力するカウンタと、

信号処理回路と、を有し、

前記複数の比較器の各々は、1 つの前記画素信号に対して、第 1 の比較及び第 2 の比較を含む複数回の前記比較を行うよう構成されており、

40

前記信号処理回路は、前記第 1 の比較により得られた第 1 のカウント値と、前記第 2 の比較により得られた第 2 のカウント値とを加算及び / 又は平均するよう構成されており、

前記信号処理回路は、前記第 1 のカウント値の最下位ビットから第 N + 1 ビットまでと、前記第 2 のカウント値の最下位ビットから第 M ビットまでとを用いるよう構成されており、N は自然数であり、M は N + 1 よりも大きい自然数であり、前記第 1 のカウント値の少なくとも第 M ビットは前記加算及び前記平均のいずれにも用いられない、

ことを特徴とする撮像装置。

**【請求項 2 7】**

前記カウント値は、複数のビットを含むグレイコードであることを特徴とする請求項 2 6 に記載の撮像装置。

50

**【請求項 28】**

前記カウンタは、前記複数の比較器に対して共通の前記カウント値を出力することを特徴とする請求項 26 又は 27 に記載の撮像装置。

**【請求項 29】**

前記比較器は、前記複数の列の各々に対応して 1 個ずつ設けられることを特徴とする請求項 26 乃至 28 のいずれか 1 項に記載の撮像装置。

**【請求項 30】**

前記比較器は、前記複数の列の各々に対応して複数個ずつ設けられることを特徴とする請求項 26 乃至 28 のいずれか 1 項に記載の撮像装置。

**【請求項 31】**

前記複数の列のうちの同一の列に対応する複数の前記比較器は、互いに異なる入力オフセット電圧を有することを特徴とする請求項 30 に記載の撮像装置。

10

**【請求項 32】**

前記第 1 の比較の際に前記カウンタが出力する前記カウント値は、N + 1 ビットのグレイコードであり、

前記第 2 の比較の際に前記カウンタが出力する前記カウント値は、M ビットのグレイコードである

ことを特徴とする請求項 26 乃至 31 のいずれか 1 項に記載の撮像装置。

**【請求項 33】**

前記複数の列の各々に対応して設けられ、各々が前記制御信号が出力された時点における前記カウント値を保持する複数の第 1 メモリと、前記複数の列の各々に対応して設けられ、各々が前記制御信号が出力された時点における前記カウント値を保持する複数の第 2 メモリと、を更に有し、

20

前記複数の第 2 メモリの各々は、

N + 1 ビットのビット幅を有し、前記第 2 の比較によって得られた前記カウント値のうちの最下位ビットから第 N + 1 ビットまでを保持するメモリと、

M - ( N + 1 ) ビットのビット幅を有し、前記第 2 の比較によって得られた前記カウント値と前記第 1 の比較によって得られた前記カウント値との差分に相当するカウント値のうちの第 N + 2 ビットから第 M ビットまでを保持するリップルカウンタと

を有することを特徴とする請求項 26 乃至 32 のいずれか 1 項に記載の撮像装置。

30

**【請求項 34】**

前記複数の比較器の各々は、前記第 1 の比較及び前記第 2 の比較の際に、同一の前記参照信号を用いて前記比較を行い、

前記第 1 の比較及び前記第 2 の比較は、互いに異なる期間に行われる

ことを特徴とする請求項 26 乃至 33 のいずれか 1 項に記載の撮像装置。

**【請求項 35】**

前記複数の比較器の各々は、

前記第 1 の比較の際に、前記画素信号と、第 1 の参照信号との大小関係を判定し、

前記第 2 の比較の際に、前記画素信号と、前記第 1 の参照信号とは異なる第 2 の参照信号との大小関係を判定する

40

ことを特徴とする請求項 26 乃至 34 のいずれか 1 項に記載の撮像装置。

**【請求項 36】**

前記信号処理回路は、

前記第 1 のカウント値から、前記第 2 のカウント値のうちの最下位ビットから第 N + 1 ビットまでの値を減算した差分値を取得し、

前記第 2 のカウント値の 2 倍と、前記差分値とを加算して得られた値を出力する

ことを特徴とする請求項 26 乃至 35 のいずれか 1 項に記載の撮像装置。

**【請求項 37】**

前記信号処理回路は、

前記第 1 のカウント値から、前記第 2 のカウント値のうちの最下位ビットから第 N + 1

50

ビットまでの値を減算した差分値を取得し、

前記差分値が、 $- (2^N - 1) [LSB]$ 以上であり、かつ $2^N - 1 [LSB]$ 以下の場合は、前記第2のカウント値の2倍と、前記差分値とを加算して得られた値を出力し、

前記差分値が、 $2^N - 1 [LSB]$ より大きい場合は、前記第2のカウント値の2倍と、前記差分値とを加算し、前記加算の結果から $2^{N+1}$ を減算して得られた値を出力し、

前記差分値が、 $- (2^N - 1) [LSB]$ より小さい場合は、前記第2のカウント値の2倍と、前記差分値とを加算し、前記加算の結果に $2^{N+1}$ を加算して得られた値を出力する

ことを特徴とする請求項26乃至35のいずれか1項に記載の撮像装置。

#### 【請求項38】

各々が光電変換により入射光に応じて生成されたアナログ信号と時間に応じて変化する参照信号との比較における大小関係を判定し、前記大小関係が反転したことに応じて制御信号を出力する、複数の比較器と、

前記参照信号の変化が開始してからの経過時間を示すカウント値を出力するカウンタと、

信号処理回路と、を有し、

前記複数の比較器の各々は、1つの前記アナログ信号に対して、第1の比較及び第2の比較を含む複数回の前記比較を行い、

前記信号処理回路は、前記第1の比較により得られた第1のカウント値と、前記第2の比較により得られた第2のカウント値とを加算及び／又は平均するよう構成されており、

前記信号処理回路は、前記第1のカウント値の最下位ビットから第 $N+1$ ビットまでと、前記第2のカウント値の最下位ビットから第Mビットまでとを用いるよう構成されており、Nは自然数であり、Mは $N+1$ よりも大きい自然数であり、前記第1のカウント値の少なくとも第Mビットは前記加算及び前記平均のいずれにも用いられない、

ことを特徴とする信号処理装置。

#### 【請求項39】

前記信号処理回路は、

前記第1のカウント値から前記第2のカウント値のうちの最下位ビットから第 $N+1$ ビットまでの値を減算した差分値を取得し、

前記第2のカウント値の2倍と、前記差分値とを加算して得られた値を出力する

ことを特徴とする請求項38に記載の信号処理装置。

#### 【請求項40】

前記信号処理回路は、

前記第1のカウント値から、前記第2のカウント値のうちの最下位ビットから第 $N+1$ ビットまでの値を減算した差分値を取得し、

前記差分値が、 $- (2^N - 1) [LSB]$ 以上であり、かつ $2^N - 1 [LSB]$ 以下の場合は、前記第2のカウント値の2倍と、前記差分値とを加算して得られた値を出力し、

前記差分値が、 $2^N - 1 [LSB]$ より大きい場合は、前記第2のカウント値の2倍と、前記差分値とを加算し、前記加算の結果から $2^{N+1}$ を減算して得られた値を出力し、

前記差分値が、 $- (2^N - 1) [LSB]$ より小さい場合は、前記第2のカウント値の2倍と、前記差分値とを加算し、前記加算の結果に $2^{N+1}$ を加算して得られた値を出力する

ことを特徴とする請求項38に記載の信号処理装置。

#### 【請求項41】

光電変換により入射光に応じて生成されたアナログ信号と時間に応じて変化する参照信号との比較における大小関係を判定するステップであって、1つの前記アナログ信号に対する第1の比較及び第2の比較を含む、ステップと、

前記大小関係が反転したことに応じて制御信号を出力するステップと、

前記参照信号の変化が開始してからの経過時間を示すカウント値を出力するステップと、

前記第1の比較により得られた第1のカウント値と、前記第2の比較により得られた第2のカウント値とを加算及び／又は平均するステップと、を有し、

前記加算及び／又は前記平均するステップにおいて、前記第1のカウント値の最下位ビットから第N+1ビットまでと、前記第2のカウント値の最下位ビットから第Mビットまでとが用いられ、Nは自然数であり、MはN+1よりも大きい自然数であり、前記第1のカウント値の少なくとも第Mビットは前記加算及び前記平均のいずれにも用いられない、ことを特徴とする信号処理方法。

**【請求項42】**

請求項1乃至21及び請求項26乃至37のいずれか1項に記載の撮像装置と、

前記撮像装置から出力された信号を処理する信号処理部と

を有することを特徴とする撮像システム。 10

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、撮像装置及び撮像システムに関する。

**【背景技術】**

**【0002】**

C M O Sイメージセンサの回路構成の一種として、複数の画素の各列に対応して設けられたアナログデジタル（A D）変換回路を有するものがある。このようなC M O Sイメージセンサに関連して、特許文献1には、画素からの信号を複数回にわたってA D変換し、A D変換により得られたデジタル値を加算することで、撮像装置が動作する際に発生する熱雑音を低減することができる旨が記載されている。 20

**【0003】**

また、特許文献2には、カウンタが各列の記憶手段に対してバッファを介してカウント値を出力する撮像装置が開示されている。この撮像装置の各列の記憶手段は、画素信号の電位とランプ信号の電位との大小関係が逆転するタイミングにおいて、カウント値を保持する。

**【先行技術文献】**

**【特許文献】**

**【0004】**

【特許文献1】特開2010-103913号公報 30

【特許文献2】特開2013-93837号公報

**【発明の概要】**

**【発明が解決しようとする課題】**

**【0005】**

しかしながら、特許文献2の構成において、入力された画素信号に対し複数回のA D変換を行う場合、各回のA D変換結果をそれぞれ保持するための記憶手段を追加する必要が生じるため、素子数が多くなり得る。

**【0006】**

本発明は上述の課題に鑑みてなされたものであり、複数の画素の各列にA D変換回路を有し、入力された画素信号に対して複数回のA D変換を行う撮像装置において、素子数を低減することを目的とする。 40

**【課題を解決するための手段】**

**【0007】**

本発明の一観点に係る撮像装置は、複数の列をなすように配列され、光電変換により入射光に応じた画素信号を出力する複数の画素を備え、前記画素信号を前記列ごとにA D変換してデジタル値を得る撮像装置であって、前記複数の列の各々に対応して設けられ、同一の前記画素信号に対して、第1のA D変換を行って得られた前記デジタル値を保持する第1メモリ群及び第2のA D変換を行って得られた前記デジタル値を保持する第2メモリ群を有し、前記第1メモリ群は、N+1ビット（Nは自然数）のビット幅を有し、前記第 50

1 の A D 変換によって得られた前記デジタル値のうちの最下位ビットから第  $N + 1$  ビットまでを保持し、前記第 2 メモリ群は、 $N + 1$  ビットより大きい  $M$  ビット ( $M$  は自然数) のビット幅を有し、前記第 2 の A D 変換によって得られた前記デジタル値のうちの最下位ビットから第  $M$  ビットまでを保持することを特徴とする。

#### 【0008】

本発明の他の一観点に係る撮像装置は、複数の列をなすように配列され、光電変換により入射光に応じた画素信号を出力する複数の画素と、前記複数の列の各々に対応して設けられ、前記画素信号と、時間に応じて変化する参照信号との大小関係の比較を行い、前記大小関係が反転したことに応じて制御信号を出力する比較器と、前記参照信号の変化が開始してからの経過時間を示すカウント値を出力するカウンタと、前記複数の列の各々に対応して設けられ、前記制御信号が出力された時点における前記カウント値を保持する第 1 メモリ群及び第 2 メモリ群と、を有し、前記比較器は、同一の前記画素信号に対して、第 1 の比較及び第 2 の比較を含む複数回の前記比較を行い、前記第 1 メモリ群及び前記第 2 メモリ群は、前記第 1 の比較により得られた前記カウント値及び前記第 2 の比較により得られた前記カウント値をそれぞれ保持し、前記第 1 メモリ群は、 $N + 1$  ビット ( $N$  は自然数) のビット幅を有し、前記第 1 の比較によって得られた前記カウント値のうちの最下位ビットから第  $N + 1$  ビットまでを保持し、前記第 2 メモリ群は、 $N + 1$  ビットより大きい  $M$  ビット ( $M$  は自然数) のビット幅を有し、前記第 2 の比較によって得られた前記カウント値のうちの最下位ビットから第  $M$  ビットまでを保持することを特徴とする。

#### 【発明の効果】

#### 【0009】

複数の画素の各列に A D 変換回路を有し、入力された画素信号に対して複数回の A D 変換を行う撮像装置において、素子数を低減することができる。

#### 【図面の簡単な説明】

#### 【0010】

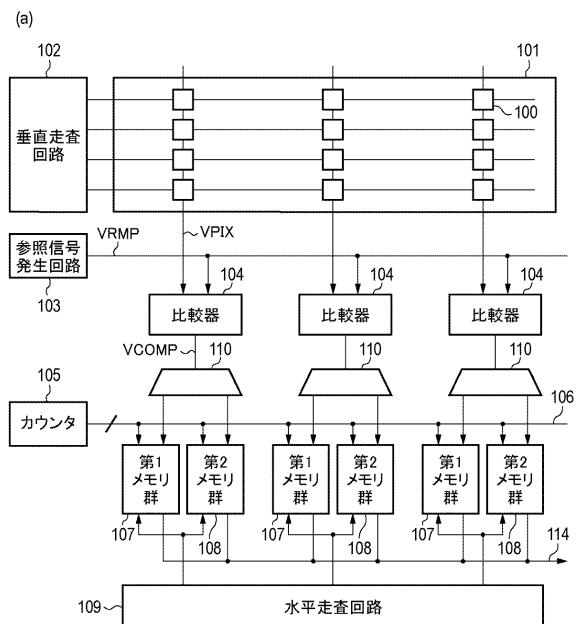

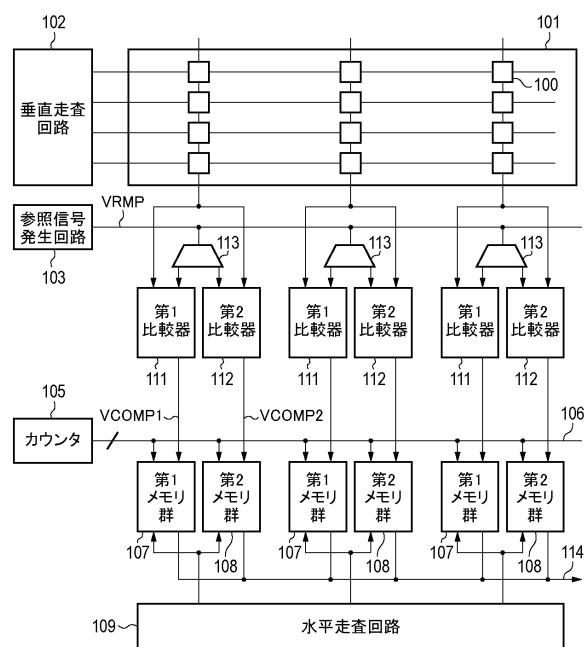

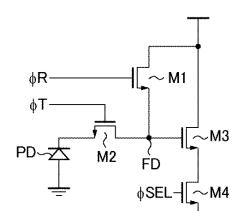

【図 1】(a) は、第 1 の実施形態に係る撮像装置の構成を示すブロック図である。(b) は、画素の構成を示す回路図である。

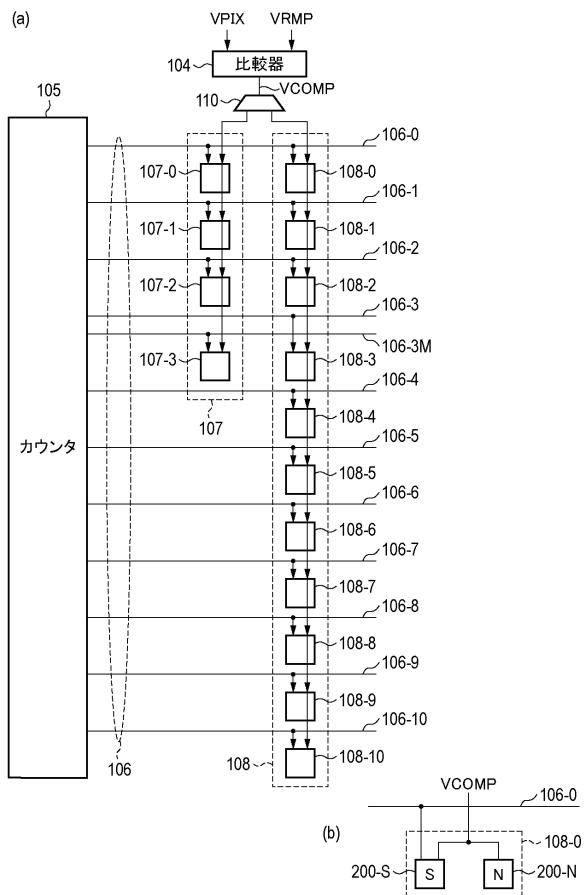

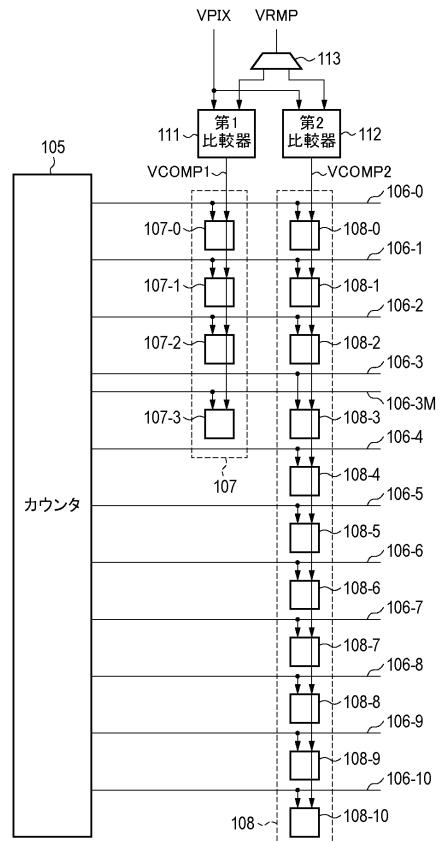

【図 2】(a) は、第 1 の実施形態に係る第 1 メモリ群及び第 2 メモリ群の構成をより詳細に示すブロック図である。(b) は、メモリの構成をより詳細に示すブロック図である。

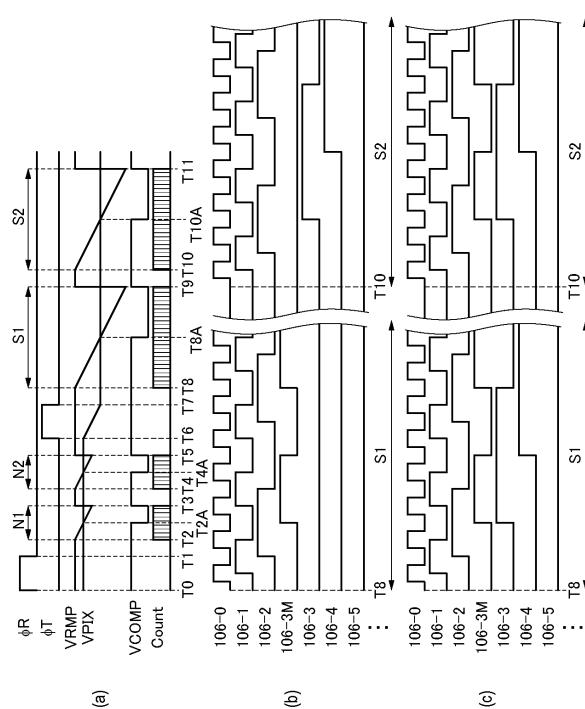

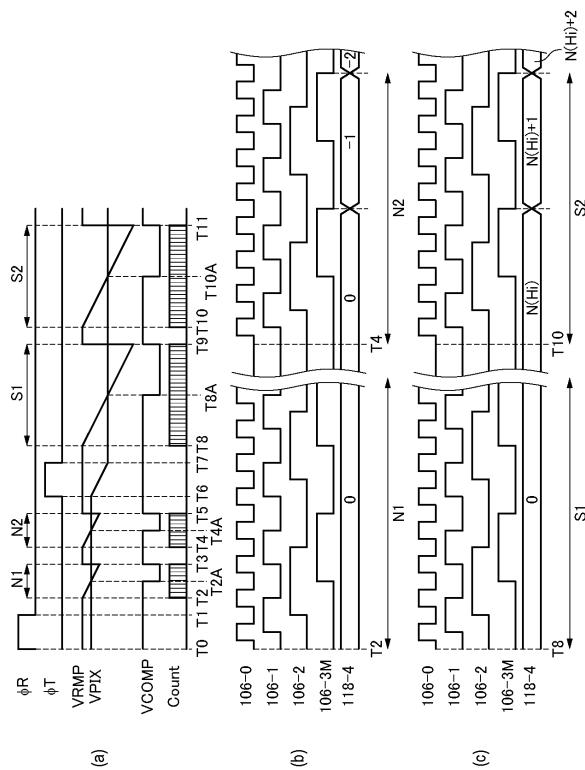

【図 3】(a) は、第 1 の実施形態に係る撮像装置の動作を示すタイミング図である。(b) は、カウント信号を示すタイミング図である。(c) は、カウント信号の変形例を示すタイミング図である。

【図 4】第 1 の実施形態に係るデジタル値の処理方法を説明する図である。

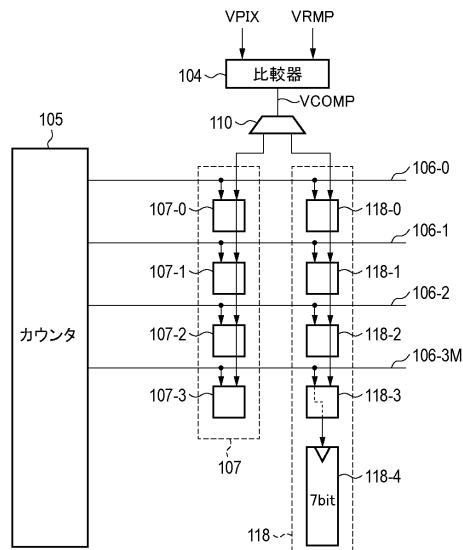

【図 5】第 2 の実施形態に係る第 1 メモリ群及び第 2 メモリ群の構成をより詳細に示すブロック図である。

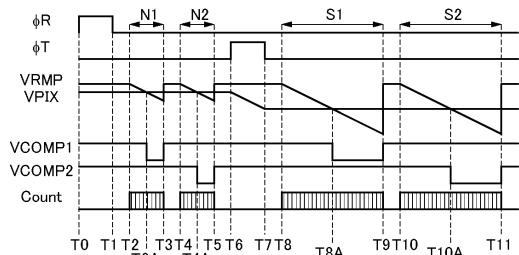

【図 6】(a) は、第 2 の実施形態に係る撮像装置全体の動作を示すタイミング図である。(b) は、期間  $N_1$ 、 $N_2$  におけるカウント信号を示すタイミング図である。(c) は、期間  $S_1$ 、 $S_2$  におけるカウント信号を示すタイミング図である。

【図 7】第 3 の実施形態に係る撮像装置の構成を示すブロック図である。

【図 8】第 3 の実施形態に係る第 1 メモリ群及び第 2 メモリ群の構成をより詳細に示すブロック図である。

【図 9】第 3 の実施形態に係る撮像装置の動作を示すタイミング図である。

【図 10】(a) は、第 4 の実施形態に係る撮像装置の動作を示すタイミング図である。(b) は、カウント信号を示すタイミング図である。

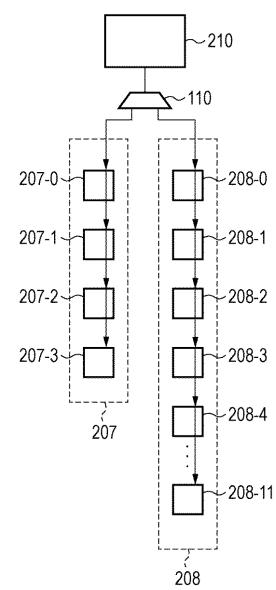

【図 11】第 6 の実施形態に係る撮像システムの構成を示すブロック図である。

【図 12】(a) は、第 5 の実施形態に係る撮像装置の構成を示すブロック図である。(b) は、画素の構成を示す回路図である。

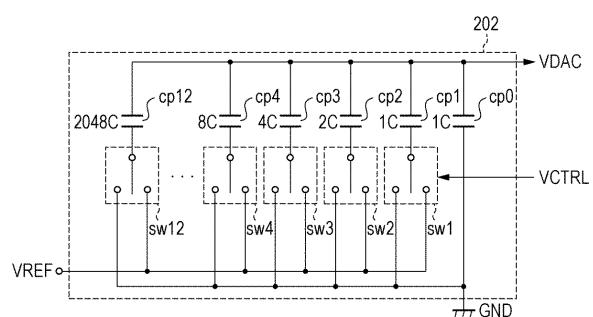

【図 13】第 5 の実施形態に係る電圧生成回路の構成を示す回路図である。

【図 14】第 5 の実施形態に係る第 1 メモリ群及び第 2 メモリ群の構成をより詳細に示す

10

20

30

40

50

ブロック図である。

【発明を実施するための形態】

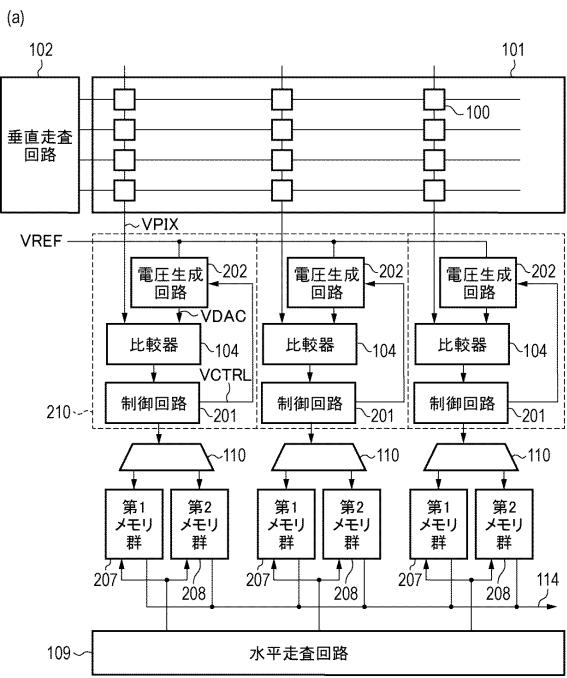

【0011】

[第1の実施形態]

図1(a)及び図1(b)に第1の実施形態の撮像装置を示す。図1(a)は、撮像装置の構成を示すブロック図であり、図1(b)は、画素の構成を示す回路図である。

【0012】

撮像装置は、画素アレイ101、垂直走査回路102、参照信号発生回路103、複数の比較器104、カウンタ105、複数の第1メモリ群107、複数の第2メモリ群108、水平走査回路109及び複数の選択回路110を有する。画素アレイ101は、複数の行及び複数の列を含む行列状に配置された複数の画素100を有する。比較器104、第1メモリ群107、第2メモリ群108及び選択回路110は画素アレイ101の各列に対応して設けられる。

10

【0013】

画素100は、光電変換部PD、リセットトランジスタM1、転送トランジスタM2、増幅トランジスタM3、選択トランジスタM4を有する。光電変換部PDは、光電変換により入射光に応じた電荷を生成する。光電変換部PDは、例えばフォトダイオードにより構成される。リセットトランジスタM1、転送トランジスタM2及び選択トランジスタM4は、それぞれ、垂直走査回路102から供給される制御信号R、T、SELによって制御される。光電変換部PDは、転送トランジスタM2のソースと接続され、転送トランジスタM2のドレインは増幅トランジスタM3のゲートノードであるフローティングディフュージョンFDと接続される。転送トランジスタM2をオンにすることにより、光電変換部PDで生成された電荷がフローティングディフュージョンFDに転送される。

20

【0014】

リセットトランジスタM1のソースはフローティングディフュージョンFDと接続され、リセットトランジスタM1のドレインは電源電圧を有する電源線に接続される。リセットトランジスタM1をオンにすることにより、フローティングディフュージョンFDの電圧がリセットされる。このような構成により、画素100は、フローティングディフュージョンFDの電圧がリセットされた状態に対応するリセットレベルの信号と、リセット後に電荷がフローティングディフュージョンFDに転送された後の状態に対応する光信号とを出力可能である。

30

【0015】

増幅トランジスタM3のドレインは電源線に接続され、増幅トランジスタM3のソースは選択トランジスタM4のドレインと接続される。選択トランジスタM4のソースは画素100の出力線に接続される。増幅トランジスタM3は、選択トランジスタM4をオンにして不図示の電流負荷を接続することにより、ソースフォロワとして動作可能である。このとき、増幅トランジスタM3は、フローティングディフュージョンFDに転送された電荷に応じた画素信号VPIXを画素100の出力線に出力する。この出力線は、画素アレイ101の列ごとに共通に設けられており、比較器104に接続される。

40

【0016】

垂直走査回路102は、上述の制御信号R、T、SELを画素アレイ101の各行の画素100に出力し、画素アレイ101のうちの所定の行を選択して読み出す動作の制御を行う。比較器104には、画素100から読み出される画素信号VPIXと、参照信号発生回路103が発生する参照信号VRMPとが入力され、両者の大小関係を比較する。比較器104は比較結果を示す制御信号VCOMPを選択回路110に出力する。画素信号VPIXと参照信号VRMPの大小関係が反転すると、そのタイミングで制御信号VCOMPの極性が反転する。参照信号VRMPは電圧が時間に応じて変化する信号である。本実施形態では、参照信号VRMPは時間に対して電圧が線形に変化するランプ信号とするが、これに限定されない。例えば参照信号VRMPは、時間に対し階段状に電圧が変化する信号であってもよい。選択回路110は、制御信号VCOMPの出力先として、

50

第1メモリ群107と第2メモリ群108のいずれかを選択する。

#### 【0017】

カウンタ105は、複数の信号線を介して、例えば11ビットのグレイコード信号を含むカウント信号群106を出力する。カウンタ105からカウント信号群106が输出される複数の信号線は、各列の第1メモリ群107及び第2メモリ群108に共通に接続される。カウント信号群106が示す値（カウント値）は、参照信号VRMPの変化が開始してからの経過時間に対応する。第1メモリ群107及び第2メモリ群108は、制御信号VCOMPの極性が反転する時点において、カウント値をAD変換結果であるデジタル値として保持する。第1メモリ群107及び第2メモリ群108に保持されたデジタル値は、水平走査回路109から走査のための制御信号が入力されたタイミングで出力線114を介して順次撮像装置の後段の回路に出力される。本実施形態では、AD変換結果を保持するメモリ群として、第1メモリ群107及び第2メモリ群108の2つが撮像装置に設けられている。したがって、撮像装置は、AD変換を2回行い、2回分のAD変換結果を保持することができる。具体的な処理は後述するが、本実施形態では、これらの2回のAD変換結果を加算して、出力信号のノイズを低減することができる。10

#### 【0018】

図2(a)及び図2(b)は、第1の実施形態の第1メモリ群107及び第2メモリ群108の構成をより詳細に説明するための、画素アレイ101の1列分に対応する列回路の構成を示す図である。(a)は、第1の実施形態に係る第1メモリ群及び第2メモリ群の構成をより詳細に示すブロック図であり、(b)は、第1メモリ群及び第2メモリ群に含まれるメモリの構成をより詳細に示すブロック図である。20

#### 【0019】

カウンタ105は、合計12本の信号線を介して、12個のカウント信号を含むカウント信号群106を出力する。各信号線を伝送する各カウント信号を、カウント信号106-0～106-10、106-3Mとする。カウント信号106-0～106-10は、カウント信号106-0を最下位ビットとし、カウント信号106-10を最上位ビットとする、11ビットのグレイコード信号を構成する。また、カウント信号106-0、106-1、106-2、106-3Mは、106-0を最下位ビットとし、106-3Mを最上位ビットとする、4ビットのグレイコード信号を構成する。30

#### 【0020】

第1メモリ群107は4ビットのメモリ107-0～107-3を含む。メモリ107-0～107-3には、カウント信号106-0、106-1、106-2、106-3Mがそれぞれ入力される。第2メモリ群108は11ビットのメモリ108-0～108-10を含む。メモリ108-0～108-10には、カウント信号106-0～106-10がそれぞれ入力される。40

#### 【0021】

図2(b)には、メモリ107-0～107-3、108-0～108-10の構成例が示されている。これらのメモリを代表して、メモリ108-0の構成のみを説明するが他のメモリも同様の構成とすることができる。本実施形態のメモリ108-0は、撮像装置の内部又は撮像装置の後段の映像信号処理部でデジタルCDS(Correlated Double Sampling)処理を行うために、2つのデータを保持可能な構成となっている。メモリ108-0は、リセットレベルの信号のAD変換結果を保持するNラッチ200-Nと、光信号のAD変換結果を保持するSラッチ200-Sとを有する。ここで第1メモリ群107に含まれるメモリの個数、すなわち第1メモリ群107のビット幅は、同一信号に対して複数回のAD変換を行った際の、各回のAD変換結果の差分値の最大値より大きい値に規定する。なお、この差分値は、主に画素信号VPIX及び参照信号VRMPに重畠されるランダムノイズ成分並びに比較器104が発生するランダムノイズ成分に起因する。これにより、2回のAD変換結果の間で値が変動しうるビットの値を複数個保持できる構成となる。50

#### 【0022】

例えば、1回目と2回目のA/D変換結果の差分値の絶対値が $2^N - 1$  [ LSB ]以下の場合、第1メモリ群107に必要なビット幅は $N + 1$ ビットとなる。本実施形態では、 $N = 3$ 、すなわち差分値の絶対値は7 [ LSB ]以下とし、これにより第1メモリ群107のビット幅は4ビットに設定されていることを前提とする。これは、各回のA/D変換結果の上位7ビット (= 11ビット - 4ビット) は1回目のA/D変換と2回目のA/D変換において同じ値となるので、第1メモリ群107のビット幅は少なくとも4ビットあればよいためである。

#### 【0023】

次に、図3(a)、図3(b)及び図3(c)のタイミング図を用いて本実施形態の撮像装置の動作を説明する。図3(a)は、第1の実施形態に係る撮像装置全体の動作を示すタイミング図である。図3(b)は、カウント信号を示すタイミング図である。図3(c)は、カウント信号の変形例を示すタイミング図である。

10

#### 【0024】

まず、時刻T0から時刻T1までの期間において、制御信号Rがハイレベルになり、リセットトランジスタM1がオンになる。これにより、フローティングディフュージョンFDの電圧が所定の電圧レベルにリセットされる。その後、時刻T2から時刻T3までの期間N1及び時刻T4から時刻T5までの期間N2において、リセットレベルの画素信号VPIXに対する2回のA/D変換が行われる。

#### 【0025】

まず、期間N1における第1のA/D変換について説明する。期間N1において、選択回路110は、制御信号VCOMPの出力先として、第1メモリ群107を選択する。時刻T2において、参照信号発生回路103から出力される参照信号VRMPの電圧が減少し始める。同時にカウンタ105から出力されるカウント信号群106が示すカウント値が時間とともに増加し始める。この時点では、参照信号VRMPの電圧がリセットレベルの画素信号VPIXの電圧よりも大きいので、比較器104の出力である制御信号VCOMPはハイレベルである。

20

#### 【0026】

その後、参照信号VRMPの電圧が、リセットレベルの画素信号VPIXの電圧よりも小さくなる時刻T2Aにおいて、参照信号VRMPの電圧と、リセットレベルの画素信号VPIXの電圧の大小関係が反転し、制御信号VCOMPはローレベルになる。第1メモリ群107は、時刻T2Aの時点におけるカウント信号群106が示すカウント値を、A/D変換後のリセットレベルのデジタル値として保持する。第1メモリ群107は4個のメモリ107-0~107-3を含む。言い換えると、第1メモリ群107はビット幅が4ビットであるため、期間N1において第1メモリ群107に保持されるデジタル値は、カウント信号群106が示すカウント値のうちの最下位ビットから第4ビット目までの下位4ビットのみである。

30

#### 【0027】

その後、期間N2における第2のA/D変換が行われる。期間N2において、選択回路110は、制御信号VCOMPの出力先として、第2メモリ群108を選択する。上述と同様のA/D変換が行われ、時刻T4Aにおいて、第2メモリ群108は時刻T4Aの時点におけるカウント信号群106が示すカウント値を、A/D変換後のリセットレベルのデジタル値として保持する。第2メモリ群108は11個のメモリ108-0~108-10を含む。言い換えると、第2メモリ群108はビット幅が11ビットであるため、期間N2において第2メモリ群108に保持されるデジタル値は、カウント信号群106が示すカウント値の最下位ビットから第11ビット目までとなる。なお、期間N1及び期間N2においてA/D変換により得られるデジタル値は、各メモリのNラッチ200-Nに保持される。また、期間N2における第2のA/D変換に用いられる参照信号VRMPの波形は、期間N1における第1のA/D変換に用いられる参照信号VRMPの波形と同一とする。

40

#### 【0028】

その後、時刻T6から時刻T7の期間において制御信号Tがハイレベルになり、転送

50

トランジスタM2がオンになる。これにより、入射光により光電変換部PDで発生した電荷がフローティングディフュージョンFDに転送される。この電荷の転送とともに、画素信号VPIXの電圧が低下する。時刻T7において、画素信号VPIXの電圧は、電荷転送により光信号に応じた値になる。その後、時刻T8から時刻T9までの期間S1及び時刻T10から時刻T11までの期間S2において、光信号のレベルの画素信号VPIXに対する2回のAD変換が行われる。

#### 【0029】

期間S1、S2におけるAD変換動作は、デジタル値が各メモリのSラッチ200-Sに保持される点を除いて、期間N1、N2におけるAD変換動作と同様であるため、説明を省略する。

10

#### 【0030】

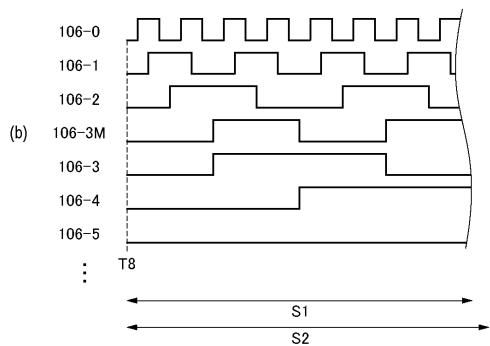

次に図3(b)を参照しながら、カウント信号群106の動作タイミングを説明する。図3(b)は、期間S1と期間S2における、カウント信号群106のうちの下位6ビットの各カウント信号106-0~106-5と、カウント信号106-3Mの波形を示している。

#### 【0031】

期間S1の開始時刻である時刻T8において、カウント信号106-0~106-2と106-3Mはグレイコードの値で「0000」(10進数で「0」)を示している。時刻T8以降、時間経過に応じて値が増加し、グレイコードの値で「1000」(10進数で「15」)になると、その次は、再び「0000」に戻る。また、カウント信号106-3~106-10は常にローレベル(0)である。このように、期間S1においては、カウント信号106-0~106-2と106-3Mで構成された4ビットのグレイコード信号が、0~15までのカウントを繰り返している。よって、制御信号VCOMPのレベルが反転する時刻T8Aにおいて、第1メモリ群107のSラッチ200-Sには、0~15までのカウント値のいずれかがグレイコードで保持される。

20

#### 【0032】

期間S2の開始時刻である時刻T10において、カウント信号106-0~106-10はグレイコードの値で「0...0000」(10進数で「0」)を示している。時刻T10以降、時間の経過に応じてカウント信号106-0~106-10が示す値が増加する。このように、期間S2においては、カウント信号106-0~106-10で構成された11ビットのグレイコードでのカウントが行われる。よって、制御信号VCOMPのレベルが反転する時刻T10Aにおいて、第2メモリ群108のSラッチ200-Sには、カウント値が11ビットのグレイコードで保持される。

30

#### 【0033】

このように、本実施形態では、期間S1、S2の2つの期間に2回のAD変換が行われる。期間S2に保持されるカウント値は11ビット、すなわちカウント信号群106のすべてのビットであり、期間S1に保持されるカウント値はカウント信号群106のうちの下位4ビットである。このようにして期間S1、S2に得られたデジタル値を用いて、AD変換を2回行った結果を加算、あるいは平均化することで、AD変換結果に含まれるノイズを低減できる。

40

#### 【0034】

なお、図3(b)のカウント信号では、期間S1に出力されるカウント信号と期間S2に出力されるカウント信号とが異なっている。特に、期間S1において、AD変換の動作に関係しないカウント信号106-3~106-10を常にローレベルとしている。これにより、期間S1にもカウント信号106-3~106-10のレベルを変化させる場合と比べ、消費電力が低減される。しかしながら、図3(c)に示されたカウント信号の変形例のように、期間S1、S2におけるカウント信号は同一の動作タイミングであってもよい。すなわち、第1のAD変換の際にカウンタ105が出力するカウント値と、第2のAD変換の際にカウンタ105が出力するカウント値とを同一にしてもよい。この場合、カウンタ105の動作が簡略化される。

50

## 【0035】

次に、第1メモリ群107及び第2メモリ群108に保持されたデジタル値を用いて2回のA/D変換結果を加算した結果に相当する信号を得るための処理方法について、図4を参照しつつ説明する。上述したように、各メモリ群に保持されるデジタル値は、期間S1に保持される下位4ビットのデジタル値と期間S2に保持される全11ビットのデジタル値である。したがって、これらを単純加算しても所望の値とはならないので、以下に述べる演算処理が必要となる。なお、これらのデジタル値に対する演算処理は、グレイコードからバイナリコードに変換された後に行われる。

## 【0036】

ここで、期間S1において保持される下位4ビットをS1(Lo)とする。また、期間S2において保持される全ビットをS2(ALL)、下位4ビットをS2(Lo)、上位7ビットをS2(Hi)とする。さらに、本実施形態では期間S1において保持されるデジタル値には上位7ビットが保持されないが、仮にこのデジタル値に全11ビットが存在した場合の値をS1(ALL)、上位7ビットをS1(Hi)とする。ただし、上述したように複数回行われるA/D変換後のデジタル値の上位ビットは、同じ値であることが前提であるため、下式が成立する。

$$S1(Hi) = S2(Hi)$$

## 【0037】

本処理は、第1メモリ群107及び第2メモリ群108に保持されたデジタル値を用いて、2回のA/D変換結果の和であるS1(ALL) + S2(ALL)を求めることが目的である。また、各メモリ群に保持された既知の値は、S1(Lo)とS2(ALL)である。この観点でS1(ALL) + S2(ALL)を以下のように式変形する。

$$\begin{aligned} & S1(ALL) + S2(ALL) \\ &= S1(Hi) + S1(Lo) + S2(Hi) + S2(Lo) \\ &= 2 \times S2(Hi) + S2(Lo) + S1(Lo) \\ &= 2 \times \{ S2(Hi) + S2(Lo) \} + S1(Lo) - S2(Lo) \\ &= 2 \times S2(ALL) + diff \end{aligned}$$

ここで、diff = S1(Lo) - S2(Lo)である。

## 【0038】

すなわち、第2メモリ群108に保持された値であるS2(ALL)の2倍と、差分値diff(4ビット値)とを加算することで、2回のA/D変換結果の和であるS1(ALL) + S2(ALL)と同じ値が算出可能である。

## 【0039】

ただし、S1(Lo)及びS2(Lo)の取り得る値は0~15であるため、上式の差分値diffをそのまま適用すると下位ビットから上位ビットへの繰り上げ又は繰り下げに起因する誤差が生じ得る。そのため、差分値diffに対して、S1(Lo)及びS2(Lo)の組み合わせによっては繰り上げ、あるいは、繰り下げの桁処理が必要となる場合がある。桁処理の内容は以下のようにS1(Lo) - S2(Lo)の値によって決定される。

(Case 1) -8 < S1(Lo) - S2(Lo) < 8 の場合

桁処理なし (diff = S1(Lo) - S2(Lo)とする)

(Case 2) S1(Lo) - S2(Lo) - 8 の場合

桁処理あり (diff = S1(Lo) - S2(Lo) + 2^4とする)

(Case 3) 8 S1(Lo) - S2(Lo) の場合

桁処理あり (diff = S1(Lo) - S2(Lo) - 2^4とする)

## 【0040】

以下、図4を参照し、具体例を挙げつつ桁処理の内容について説明する。

(Case 1) -8 < S1(Lo) - S2(Lo) < 8 の場合

Bin[0] ~ Bin[3]は、S1又はS2をバイナリ変換した後のビットごとの波形のうちの下位4ビットを示している。S2(ALL)行は、Bin[0] ~ Bin[3]

10

20

30

40

50

] の取り得る値の一例を示している。

#### 【0041】

以降、本ケースでは、 $S_2(ALL)$ が「55」(バイナリ値で「110111」)である場合について説明する。 $S_2(Lo)$ 行は、 $S_2(ALL)$ が「55」の時の下位4ビットの値「7」(バイナリ値で「0111」)を示している。 $S_2(ALL)$ が「55」のとき、 $S_1(ALL)$ の取り得る範囲は「55」±7[LSB]である。 $S_1(Lo)$ 行は、 $S_1(ALL)$ の下位4ビットである「0」~「14」(バイナリ値で「0000」~「1110」)を示している。

#### 【0042】

$S_1(Lo) - S_2(Lo)$ 行は、 $S_1(Lo)$ から $S_2(Lo)$ を引いた値であり、

diff行は桁処理を行った後の結果を示している。なお、本ケースでは桁処理は発生しないため、 $S_1(Lo) - S_2(Lo)$ 行と同じ値となる。

#### 【0043】

$S_1 + S_2$ (期待値)行は、 $S_2(ALL)$ が「55」の時に、 $S_1(ALL)$ が取り得る範囲(「55」±7[LSB])におけるAD変換結果の加算値 $S_1(ALL) + S_2(ALL)$ の期待値を示している。

#### 【0044】

$S_1 + S_2$ (Simple)行は、仮に上述の桁処理を施さなかった場合に得られる計算値である下式を示している。

$$2 \times S_2(ALL) + S_1(Lo) - S_2(Lo)$$

20

#### 【0045】

$S_1 + S_2$ 行は、桁処理を施した後の計算値である下式を示している。

$$2 \times S_2(ALL) + diff$$

#### 【0046】

この値が $S_1 + S_2$ (期待値)と等しくなるように桁処理が行われる必要がある。本ケースでは $-8 < S_1(Lo) - S_2(Lo) < 8$ であるため、図示された $S_1$ の取り得る範囲において、 $S_1 + S_2$ (Simple)と $S_1 + S_2$ (期待値)に差は生じない。したがって、本ケースでは桁処理が不要である。

#### 【0047】

$$(Case 2) S_1(Lo) - S_2(Lo) = -8$$

30

本ケースでは、 $S_2(ALL)$ が「63」(バイナリ値で「111111」)であり、 $S_2(Lo)$ が「15」(バイナリ値で「1111」)となる場合を示している。

#### 【0048】

ここで、例えば、 $S_1(ALL)$ が $S_2(ALL)$ より「1」大きい「64」(バイナリ値で「1000000」)の場合を考える。この時、実際に第1メモリ群107に保持される値 $S_1(Lo)$ は「0」(バイナリ値で「0000」)となり、桁処理を行わない場合、下式のようになる。

$$S_1(Lo) - S_2(Lo) = 0 - 15 = -15$$

#### 【0049】

したがって、桁処理を行わない場合の2回のAD変換結果の和に相当する $S_1 + S_2$ (Simple)行の値は下式のようになる。

$$2 \times S_2(ALL) + S_1(Lo) - S_2(Lo) = 63 \times 2 - 15 = 111$$

40

#### 【0050】

この結果は、 $S_1 + S_2$ (期待値)である「127」と異なる。この理由は以下の通りである。 $S_2(ALL)$ の値「63」の下位4ビット $S_2(Lo)$ は、「15」(バイナリ値で「1111」)である。ここで、 $S_2(ALL)$ の「63」より「1」だけ大きい $S_1(ALL)$ の下位ビットの値である $S_1(Lo)$ は「15」の次の値の「16」ではなく「0」となる。これは、下位ビットのビット幅が4ビットしかないためである。よって、桁処理を行わない場合の、 $S_1 + S_2$ (Simple)は、 $S_1 + S_2$ (期待値)と「16」だけずれた値となる。

50

**【0051】**

そのため、この値のずれの「16」を補正するために繰り上げの桁処理として $dif\ f\ f$ を下式で定義する必要がある。

$$dif\ f\ f = S1(Lo) - S2(Lo) + 2^4$$

**【0052】**

この $dif\ f\ f$ を用いて $S1(ALL) + S2(ALL)$ を計算すると、繰り上げ処理後の $S1(ALL) + S2(ALL)$ の値は、下式のようになる。

$$2 \times S2(ALL) + dif\ f\ f = 2 \times 63 - 15 + 16 = 127$$

**【0053】**

これにより、 $S1 + S2$ （期待値）と一致する結果が得られる。上述の例は、 $S1(Lo)$ が「0」の場合であるが、「1」～「6」の場合も同様の処理が必要となる。また、 $S1(Lo)$ が「8」～「15」の場合は上述の桁処理は行わない。

10

**【0054】**

(Case 3) 8  $S1(Lo) - S2(Lo)$  の場合

本ケースでは、 $S2(ALL)$ が「64」（バイナリ値で「10000000」）であり、 $S2(Lo)$ が「0」（バイナリ値で「0000」）となる場合を示している。

**【0055】**

ここで、例えば、 $S1(ALL)$ が $S2(ALL)$ より「1」小さい「63」（バイナリ値で「111111」）の場合を考える。この時、実際に第1メモリ群107に保持される値 $S1(Lo)$ は「15」（バイナリ値で「1111」）となり、桁処理を行わない場合、

20

$$S1(Lo) - S2(Lo) = 15 - 0 = 15$$

**【0056】**

したがって、桁処理を行わない場合の2回のAD変換結果の和に相当する $S1 + S2$ （Simple）行の値は下式のようになる。

$$2 \times S2(ALL) + S1(Lo) - S2(Lo) = 64 \times 2 + 15 = 143$$

**【0057】**

この結果は、 $S1 + S2$ （期待値）である「127」と異なる。本ケースではCase 2とは逆に繰り下げる桁処理として $dif\ f\ f$ を下式で定義する必要がある。

$$dif\ f\ f = S1(Lo) - S2(Lo) - 2^4$$

30

**【0058】**

この $dif\ f\ f$ を用いて $S1(ALL) + S2(ALL)$ を計算すると、繰り下げる桁処理後の $S1(ALL) + S2(ALL)$ の値は、下式のようになる。

$$2 \times S2(ALL) + dif\ f\ f = 2 \times 64 + 15 - 16 = 127$$

**【0059】**

これにより、 $S1 + S2$ （期待値）と一致する結果が得られる。上述の例は、 $S1(Lo)$ が「15」の場合であるが、「9」～「14」の場合も同様の処理を行う必要がある。また、 $S1(Lo)$ が「0」～「7」の場合は上述の桁処理を行わない。

**【0060】**

上述の桁処理の説明は光信号のAD変換結果についてのものであるが、画素リセットレベルのAD変換結果に対しても同様の処理を行うことができる。桁処理の終了後、デジタルCDS処理を行うことでリセットレベルに含まれるノイズが除去された画像データを得ることができる。なお、上述の桁処理方法は、各メモリ群の後段であれば撮像装置の内部で行われてもよく、撮像装置の後段の映像信号処理部等で行われてもよい。

40

**【0061】**

以上説明したように、本実施形態によれば、同一画素から出力された画素信号に対し、複数回のAD変換を行い、これにより得られたAD変換結果を加算することで、ノイズを小さくすることができる。この加算において、第1メモリ群107のビット幅を想定されるノイズに応じて信号の全ビット数よりも少なくしている。これにより、第1メモリ群107内のメモリの個数を信号の全ビット数と同じに設定した場合と比べて少なくすること

50

ができる。例えば、上述の例では 11 個から 4 個に低減されている。したがって、撮像装置の素子数を低減することができる。

#### 【0062】

なお、上述の説明においてカウンタ 105 から出力されるカウント信号はグレイコードとしているが、グレイコード以外の形式であってもよい。例えば、通常の 2 進数を用いたバイナリコードであってもよい。しかしながら、グレイコードは、カウント値の増加時に反転するビットが 1 つのみであることから、カウント値の増加と比較器出力の変化のタイミングずれの影響が小さくなるため、カウント信号にはグレイコードを適用することがより好ましい。

#### 【0063】

なお、上述の説明では、第 1 メモリ群 107 のビット幅は 4 ビットであり、第 2 メモリ群 108 のビット幅は 11 ビットであり、カウント信号群 106 が示すカウント値も 11 ビットとしているがこれに限定されない。すなわち、これらのビット数は本発明の要旨を逸脱しない範囲で任意の値とすることができます。より詳細には、以下のように一般化される。1 回目と 2 回目の A/D 変換結果の差分値の絶対値が  $2^N - 1$  [LSB] (N は自然数) 以下の場合、第 1 メモリ群 107 のビット幅は N + 1 ビットとする。このとき、第 2 メモリ群 108 のビット幅及びカウント信号群 106 が示すカウント値のビット数は N + 1 より大きい M ビット (M は自然数) とする。この場合、第 1 メモリ群 107 は、カウント信号群 106 のうちの最下位ビットから第 N + 1 ビットまでを保持する。第 2 メモリ群 108 は、カウント信号群 106 のうちの最下位ビットから第 M ビットまでを保持する。

10

#### 【0064】

この場合、上述の桁処理は以下のように N を用いて一般化することができます。

(Case 1) - ( $2^N - 1$ ) < S1 (Lo) - S2 (Lo) < ( $2^N - 1$ ) の場合

桁処理なし

(Case 2) S1 (Lo) - S2 (Lo) - ( $2^N - 1$ ) の場合

桁処理あり (diff = S1 (Lo) - S2 (Lo) +  $2^{N+1}$  とする)

(Case 3) ( $2^N - 1$ ) - S1 (Lo) - S2 (Lo) の場合

桁処理あり (diff = S1 (Lo) - S2 (Lo) -  $2^{N+1}$  とする)

#### 【0065】

上述の説明では、撮像装置は、2 回の A/D 変換を行い、A/D 変換結果を 2 つのメモリ群に保持する構成となっているが、A/D 変換の回数及びメモリ群の個数は 2 つに限られない。例えば、3 回以上の複数回 A/D 変換を行い、A/D 変換結果を 3 つ以上の複数個のメモリ群に保持する構成としてもよい。

30

#### 【0066】

上述の説明では、複数回の A/D 変換で得られたデジタル値を単純加算しているが、この加算は単純加算でなくてもよい。例えば、上述の加算処理を、加算後の値を加算が行われた信号の個数で除算することにより、平均化処理に置き換えてよい。

#### 【0067】

##### [第 2 の実施形態]

図 5 は、第 2 の実施形態の第 1 メモリ群 107 及び第 2 メモリ群 118 の構成を説明するための図である。なお、本実施形態において、撮像装置の構成は図 1 に示す第 1 の実施形態の構成と同様のため、説明を省略する。

40

#### 【0068】

第 1 メモリ群 107 の構成は、第 1 の実施形態と同様である。第 2 メモリ群 118 の構成は、メモリ 108-4 ~ 108-10 が 7 ビット幅のリップルカウンタ 118-4 に置き換えられている点で第 1 の実施形態の第 2 メモリ群 108 の構成と異なる。すなわち、第 2 メモリ群 118 は、下位 4 ビットのメモリ 118-0 ~ 118-3 とリップルカウンタ 118-4 を含む。メモリ 118-0 ~ 118-3 には、第 1 メモリ群 107 と同じカウント信号 106-0、106-1、106-2、106-3 M が、カウンタ 105 から入力される。さらに、カウント信号 106-3 M は、メモリ 118-3 を介して、リッ

50

プルカウンタ 118 - 4 に入力される。リップルカウンタ 118 - 4 は、カウント信号 106 - 3 M の立下りエッジをカウントする。すなわち、カウント信号 106 - 3 M がハイレベルからローレベルになる際にリップルカウンタ 118 - 4 に保持される値が増加又は減少する。ここで、第 1 メモリ群 107 のビット幅の設定方法は、第 1 実施形態で述べたものと同様であるため説明を省略する。

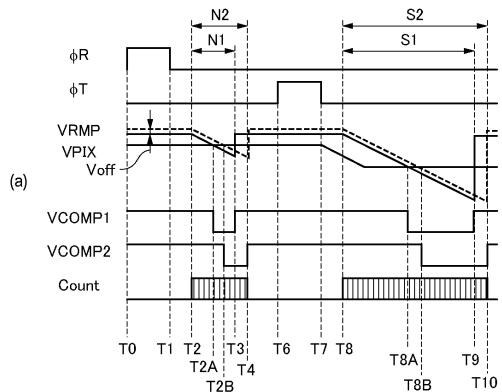

#### 【0069】

次に、図 6 (a)、図 6 (b) 及び図 6 (c) のタイミング図を用いて本実施形態の撮像装置の動作を説明する。図 6 (a) は、第 2 の実施形態に係る撮像装置全体の動作を示すタイミング図である。図 6 (b) は、期間 N1、N2 におけるカウント信号を示すタイミング図である。図 3 (c) は、期間 S1、S2 におけるカウント信号を示すタイミング図である。図 6 (a) に示されている、制御信号 R、T、参照信号 V R M P、画素信号 V P I X、制御信号 V C O M P の動作タイミングは第 1 の実施形態と同様であり、期間 N1、N2、S1、S2 に A/D 変換が行われる点も第 1 の実施形態と同様である。よって、これらについての詳細な説明を省略する。10

#### 【0070】

以下、本実施形態における第 1 の実施形態との差異点である、期間 N2、S2 におけるリップルカウンタ 118 - 4 の動作について説明する。図 6 (b) に示されているように、期間 N2 において、リップルカウンタ 118 - 4 は、カウント信号 106 - 3 M の立下りエッジに応じてカウントダウンを行う。言い換えると、下位ビットのカウント値が 15 から 0 に戻るときにリップルカウンタ 118 - 4 に保持されるカウント値が 1 だけ小さくなる。その後、時刻 T4A において制御信号 V C O M P の極性が反転する。このとき、その時点のカウント信号 106 - 0 ~ 106 - 2、106 - 3 M の値が、第 2 メモリ群 118 のメモリ 118 - 0 ~ 118 - 3 内の各 N ラッチ 200 - N に保持される。さらにこのとき、リップルカウンタ 118 - 4 に供給されるカウント信号 106 - 3 M の変化が停止するように制御され、リップルカウンタ 118 - 4 もこれ以降、期間 S2 の A/D 変換が開始するまでは時刻 T4A 時点のカウント値 N (H i) を保持する。20

#### 【0071】

図 6 (c) に示されているように、上述の動作に後続する期間 S2 において、リップルカウンタ 118 - 4 は、カウント信号 106 - 3 M の立下りエッジに応じて、カウントアップを行う。この動作において、リップルカウンタ 118 - 4 のカウント値の初期値は時刻 T4A 時点のカウント値 N (H i) である。その後、時刻 T10A において制御信号 V C O M P の極性が反転する。このとき、その時点のカウント信号 106 - 0 ~ 106 - 2、106 - 3 M の値が、第 2 メモリ群 118 のメモリ 118 - 0 ~ 118 - 3 内の各 S ラッチ 200 - S に保持される。さらにこのとき、リップルカウンタ 118 - 4 に供給されるカウント信号 106 - 3 M の変化が停止するように制御される。30

#### 【0072】

ここで、期間 S2 におけるカウントは、時刻 T4A 時点のカウント値 N (H i) を初期値として行われるため、リップルカウンタ 118 - 4 に保持される上位ビット値は、デジタル CDS 処理が行われた後の値である。言い換えると、リップルカウンタ 118 - 4 には、(S2 (H i) - N2 (H i)) に相当する CDS 処理後の上位ビット値が保持される。40

#### 【0073】

次に、各メモリ群に保持されたデジタル値の処理方法について説明する。上述のように、デジタル CDS 処理された上位ビットが既に得られている。よって、下位ビットのみの処理が必要となる。リセットレベルに対する 2 回の A/D 変換で得られた下位ビットの値同士の差分値を d\_i f\_f\_N とし、光信号に対する 2 回の A/D 変換で得られた下位ビットの値同士の差分値を d\_i f\_f\_S とする。差分値 d\_i f\_f\_N、d\_i f\_f\_S に対して、第 1 の実施形態で述べた桁処理を施し、それぞれ桁処理後の差分値を得る。得られた差分値と、リップルカウンタに保持された値を用いて以下の値を算出することにより、デジタル CDS 後の信号を得ることができる。50

$2 \times (S_2(H_i) - N_2(H_i)) + (diff\_S) - (diff\_N)$

#### 【0074】

本実施形態においても、第1の実施形態と同様の効果を得ることができる。

なお、上述の説明では、第1メモリ群107のビット幅は4ビットであり、第2メモリ群118のメモリ118-0~118-3に対応するビット幅も4ビットである。また、リップルカウンタ118-4のビット幅は7ビットである。しかしながら、第1の実施形態と同様にこのビット数には限定されない。すなわち、これらのビット数は本発明の要旨を逸脱しない範囲で任意の値とすることができる。より詳細には、以下のように一般化される。1回目と2回目のAD変換結果の差分値の絶対値が $2^N - 1$  [ LSB ] (Nは自然数)以下の場合、第1メモリ群107のビット幅はN+1ビットとする。このとき、第2メモリ群118内の複数のメモリのビット幅もN+1ビットとする。また、第2メモリ群118内のリップルカウンタ118-4のビット幅はM-(N+1)ビット(Mは自然数)とする。この場合、第1メモリ群107と、第2メモリ群118内の複数のメモリとは、カウント信号群106のうちの最下位ビットから第N+1ビットまでを保持する。第2メモリ群118は、カウント信号群106のうちの第N+2ビットから第Mビットまでを保持する。10

#### 【0075】

##### [第3の実施形態]

図7は、第3の実施形態に係る撮像装置の構成を示す図である。図1に示す第1の実施形態の撮像装置と異なり、本実施形態の撮像装置は、比較器104に代えて第1比較器111及び第2比較器112を有する。また、本実施形態の撮像装置は、選択回路110に代えて第1比較器111及び第2比較器112の前段に選択回路113を有する。参照信号VRMPは選択回路113を介して第1比較器111及び第2比較器112に入力される。第1比較器111から比較結果として出力される制御信号VCOMP1は、第1メモリ群107に入力される。第2比較器112から比較結果として出力される制御信号VCOMP2は、第2メモリ群108に入力される。20

#### 【0076】

図8は、第3の実施形態に係る第1メモリ群107及び第2メモリ群108の構成をより詳細に示すブロック図である。第1比較器111から出力される制御信号VCOMP1は、第1メモリ群107内の各メモリ107-0~107-3に入力される。第2比較器112から出力される制御信号VCOMP2は、第2メモリ群108内の各メモリ108-0~108-10に接続される。その他の構成は第1の実施形態と同様であるため説明を省略する。30

#### 【0077】

次に、図9のタイミング図を参照して、本実施形態の動作を、特に、第1の実施形態と異なる点について説明する。なお、カウント信号群106の動作については、図3(b)、又は図3(c)と同様であるため、図示及び説明を省略する。

#### 【0078】

選択回路113は、期間N1と期間S1のAD変換時においては、参照信号VRMPを第1比較器111に入力させる。これにより、第1比較器111においてAD変換が行われ、第1メモリ群107にデジタル値が保持される。また、選択回路113は、期間N2と期間S2のAD変換時においては、参照信号VRMPを第2比較器112に入力させる。これにより、第2比較器112においてAD変換が行われ、第2メモリ群108にデジタル値が保持される。その他の処理は第1実施形態と同様のため説明を省略する。40

#### 【0079】

本実施形態においても、第1の実施形態と同様の効果を得ることができる。

なお、本実施形態では、画素100の各列に対応する比較器及びメモリ群は2個ずつ設けられているが、この個数は複数個であれば任意に変更可能であり、例えば3個以上であってもよい。

#### 【0080】

**[ 第 4 の実施形態 ]**

次に、第4の実施形態を説明する。図10(a)は、第4の実施形態に係る撮像装置の動作を示すタイミング図である。図10(b)は、カウント信号を示すタイミング図である。本実施形態の撮像装置の構成は図7及び図8に示すものと同様である。本実施形態では、第2比較器112の入力端子に対して所定の入力オフセット電圧V<sub>off</sub>を加えてA/D変換を実施することで、期間N1のA/D変換期間と期間N2のA/D変換期間とを重ねることができる点が第3の実施形態と異なる。また、同様に、期間S1のA/D変換期間と期間S2のA/D変換期間とを重ねることもできる。この入力オフセット電圧V<sub>off</sub>の付加は、一例として、第2比較器112に入力される参照信号VRMPの電圧を変化させることで実現できる。図10(a)において、第2比較器112に入力される参照信号VRMPに対して入力オフセット電圧V<sub>off</sub>を加えた波形が破線で示されている。10

**【 0 0 8 1 】**

T2までの期間の動作は図9と同様であるため説明を省略する。時刻T2から時刻T3までの期間N1において、第1比較器111におけるリセットレベルのA/D変換が行われる。時刻T2から時刻T4までの期間N2において、第2比較器112におけるリセットレベルのA/D変換が行われる。第2比較器112に入力される参照信号VRMPには入力オフセット電圧V<sub>off</sub>が付加されているので、期間N1のA/D変換レンジと期間N2のA/D変換レンジを一致させるため、期間N2は期間N1よりも長くなる。

**【 0 0 8 2 】**

時刻T6から時刻T7の期間において制御信号Tがハイレベルになり、転送トランジスタM2がオンになる。これにより、入射光により光電変換部PDで発生した電荷がフローティングディフュージョンFDに転送される。20

**【 0 0 8 3 】**

時刻T8から時刻T9までの期間S1において、第1比較器111における光信号のA/D変換が行われる。時刻T8から時刻T10までの期間S2において、第2比較器112における光信号のA/D変換が行われる。上述の期間N1と期間N2の関係と同様に、期間S2は期間S1よりも長くなる。

**【 0 0 8 4 】**

図10(b)に示す期間S1、S2におけるカウント信号群106のタイミング図と併せて、A/D変換動作の一例を説明する。図10(b)に示されるように、期間S1、S2の間、カウント信号106-0～106-10及び106-3Mは、いずれも変動し、A/D変換時のカウントに供される。30

**【 0 0 8 5 】**

画素信号VPIXと参照信号VRMP(実線)の大小関係が反転するタイミングT8Aにおいて、第1比較器111から出力される制御信号VCOMP1の極性が反転する。これにより、カウント信号106-0～106-2、106-3Mで構成される4ビット幅のデジタル値が第1メモリ群107の各Sラッチ200-Sに保持される。同様に、画素信号VPIXと参照信号VRMP(破線)の大小関係が反転するタイミングT8Bにおいて、第2比較器112から出力される制御信号VCOMP2の極性が反転する。カウント信号106-0～106-10で構成される11ビット幅のデジタル値が第2メモリ群108の各Sラッチ200-Sに保持される。40

**【 0 0 8 6 】**

以降の取得されたデジタル値に対する処理は、期間S2に保持された変換結果に対して、所定の入力オフセット電圧V<sub>off</sub>に相当する値の減算を要することを除き、上述の処理と同様のため説明を省略する。

**【 0 0 8 7 】**

第1の実施形態では、期間N2における第2のA/D変換に用いられる参照信号VRMPの波形は、期間N1における第1のA/D変換に用いられる参照信号VRMPの波形と同一としており、また、期間N1と期間N2とは互いに異なる期間とされている。これに対し本実施形態では、撮像装置は、複数の比較器を有し、かつ第2比較器112の入力端子に50

対して所定の入力オフセット電圧  $V_{off}$  を加えて A/D 変換を行う。よって、本実施形態によれば、第 1 の実施形態の効果が得られることに加え、期間 N1 と期間 N2 の少なくとも一部を重ねることができ、期間 S1 と期間 S2 の少なくとも一部を重ねることもできる。

#### 【0088】

なお、本実施形態では参照信号 VRMP に入力オフセット電圧  $V_{off}$  に相当する電圧を加算したものとして説明したが、画素信号 VPIX に入力オフセット電圧  $V_{off}$  を加算してもよい。

#### 【0089】

上述の第 3 又は第 4 の実施形態の変形例として、参照信号発生回路 103 が 2 つの参照信号 VRMP を出力可能に構成し、2 つの参照信号 VRMP を選択回路 113 を介さずに第 1 比較器 111 及び第 2 比較器 112 にそれぞれ入力させてよい。この場合、各 A/D 変換時において、参照信号発生回路 103 が 2 つの参照信号 VRMP の波形を個別に制御し得るようにする。これにより、期間 N1 の A/D 変換期間と期間 N2 の A/D 変換期間とを重ねることができ、期間 S1 の A/D 変換期間と期間 S2 の A/D 変換期間とを重ねることもできる。また、第 3 又は第 4 の実施形態の各メモリ群を図 5 に示す第 2 の実施形態の構成と同様の構成としてもよく、同様の動作が可能である。10

#### 【0090】

#### [第 5 の実施形態]

次に、第 5 の実施形態を説明する。図 12(a) は、第 5 の実施形態に係る撮像装置の構成を示すブロック図であり、図 12(b) は、画素 100 の構成を示す回路図である。図 1 及び図 7 に示す撮像装置と異なり、図 12(a) に示す本実施形態の撮像装置は、比較器 104、制御回路 201、及び電圧生成回路 202 を含む逐次比較型 A/D 変換回路 210 と、第 1 メモリ群 207 と第 2 メモリ群 208 とを列ごとに有する。また、本実施形態の撮像装置には、参照信号発生回路 103 及びカウンタ 105 が設けられていない。図 12(b) に示す画素 100 の構成は図 1(b) と同様であるため、その説明を省略する。20

#### 【0091】

画素 100 から出力される画素信号 VPIX は、比較器 104 の一方の入力端子に入力される。電圧生成回路 202 は、制御回路 201 から出力される制御信号 VCTR に基づき、二分探索を逐次行う逐次比較動作のための電圧信号 VDAC を、比較器 104 の他方の入力端子に出力する。また、電圧生成回路 202 には、不図示の電圧源から基準電圧 VREF が入力される。比較器 104 は、画素信号 VPIX と、電圧信号 VDAC とを逐次比較して比較結果を示す信号を制御回路 201 に出力する。制御回路 201 は、比較器 104 からの信号を受けて、制御信号 VCTR を電圧生成回路 202 に出力する。また、制御回路 201 は、逐次比較により得られた比較結果を選択回路 110 に出力する。選択回路 110 は、比較結果であるデジタル値の出力先として、第 1 メモリ群 207 と第 2 メモリ群 208 のいずれかを選択する。30

#### 【0092】

図 13 は、電圧生成回路 202 の構成を示す回路図である。電圧生成回路 202 は、バイナリウェイトの容量値を有する複数のキャパシタ  $C_{p0} \sim C_{p12}$  と、複数のキャパシタ  $C_{p1} \sim C_{p12}$  にそれぞれ直列接続された複数のスイッチ  $S_{w1} \sim S_{w12}$  とを有する。バイナリウェイトとは、公比 2 の等比数列をなす重み（容量値）の集合のことである。図 13 の例では、キャパシタ  $C_{p0} \sim C_{p12}$  は順に 1C、1C、2C、4C … 2048C の容量値を有する。40

#### 【0093】

電圧生成回路 202 は、制御信号 VCTR に基づいて複数のスイッチ  $S_{w1} \sim S_{w12}$  の各々が切り替えられることにより、入力された基準電圧 VREF を分圧し、電圧信号 VDAC として出力する回路である。キャパシタ  $C_{p0} \sim C_{p12}$  の一端は電圧生成回路 202 の出力端子に接続される。キャパシタ  $C_{p0}$  の他端は接地電位 GND に接続される50

。複数のキャパシタ c p 1 ~ c p 1 2 の他端は、対応する複数のスイッチ s w 1 ~ s w 1 2 の一端にそれぞれ接続される。複数のスイッチ s w 1 ~ s w 1 2 の他端は、制御信号 V C T R L に基づき、基準電圧 V R E F 又は接地電位 G N D のいずれかに接続されるように切り替え可能な端子となっている。すなわち、複数のスイッチ s w 1 ~ s w 1 2 は、キャパシタ c p 1 ~ c p 1 2 のうちの 1 つ以上を選択するか、あるいはいずれも選択しないという動作を行うスイッチ回路を構成する。

#### 【 0 0 9 4 】

基準電圧 V R E F は、逐次比較型 A D 変換回路 2 1 0 の外部から供給される定電圧であり、接地電位 G N D よりも高い電圧値を有する。複数のスイッチ s w 1 ~ s w 1 2 の接続状態が切り替わることにより、複数のキャパシタ c p 1 ~ c p 1 2 の各々には基準電圧 V R E F 又は接地電位 G N D が供給される。これにより、基準電圧 V R E F が入力される端子と、電圧信号 V D A C が出力される端子との間に接続される合成容量値が変化し、電圧信号 V D A C の電圧が変化する。言い換えると、電圧生成回路 2 0 2 は、スイッチ s w 1 ~ s w 1 2 を制御する制御信号 V C T R L に基づいて電圧信号 V D A C の電圧を変化させるデジタルアナログ変換回路である。図 1 3 の構成では、スイッチ s w 1 ~ s w 1 2 の個数が 1 2 個であるため 1 2 ビットの逐次比較動作を実現できる。

#### 【 0 0 9 5 】

図 1 4 は、第 5 の実施形態の第 1 メモリ群 2 0 7 と第 2 メモリ群 2 0 8 の、画素アレイ 1 0 1 の 1 列分に対応する列回路の構成を示す図である。第 1 メモリ群 2 0 7 は、最下位から 4 ビット分の比較結果を保持する複数のメモリ 2 0 7 - 0 ~ 2 0 7 - 3 を有し、第 2 メモリ群 2 0 8 は最下位から最上位までの 1 2 ビット分の比較結果を保持する複数のメモリ 2 0 8 - 0 ~ 2 0 8 - 1 1 を有する。各メモリは、図 2 ( b ) と同様に 2 つのデータを保持可能な構成となっている。第 1 メモリ群 2 0 7 のビット幅は、上述の第 1 の実施形態等と同様に、同一信号に対して複数回の A D 変換を行った際の、各回の A D 変換結果の差分値の最大値より大きい値に規定する。本実施形態における差分値は、主に画素信号 V P I X 及び電圧生成回路 2 0 2 の出力である電圧信号 V D A C に重畠されるランダムノイズ成分並びに比較器 1 0 4 が発生するランダムノイズ成分に起因する。これにより、2 回の A D 変換結果の間で値が変動しうるビットの値を複数個保持できる構成となる。

#### 【 0 0 9 6 】

次に A D 変換の動作について説明する。本実施形態においても、これまでに述べた他の実施形態と同様に画素のリセットレベル及び光信号レベルのそれぞれに対して、2 回ずつ A D 変換が行われる。各 A D 変換動作は、逐次比較型 A D 変換回路 2 1 0 により逐次比較動作によって実施される。リセットレベル及び光信号レベルの 1 回目の A D 変換結果は、第 1 メモリ群 2 0 7 に最下位から 4 ビットがそれぞれ保持され、同 2 回目の A D 変換結果は、第 2 メモリ群 2 0 8 に最下位から 1 2 ビットまでのすべてのビットが保持される。

#### 【 0 0 9 7 】

その後、保持された A D 変換結果がバイナリコードでない場合はバイナリコードに変換後、バイナリコードである場合はそのまま、2 回の A D 変換結果を加算した結果に相当する信号を得るために処理が行われる。当該処理の内容は、第 1 の実施形態にて説明した内容のうち、バイナリコードへの変換後の処理と同様であるため詳細な説明を省略する。

#### 【 0 0 9 8 】

以上説明したように、本実施形態によれば、逐次比較型 A D 変換回路を有する撮像装置においても、同一画素から出力された画素信号に対し、複数回の A D 変換を行い、これにより得られた A D 変換結果を加算することで、ノイズを小さくすることができる。

#### 【 0 0 9 9 】

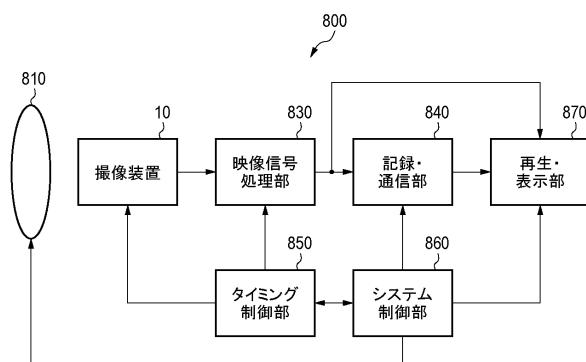

#### [ 第 6 の実施形態 ]

図 1 1 には、第 6 の実施形態に係る撮像システム 8 0 0 の構成が示されている。撮像システム 8 0 0 は、例えば、デジタルスチルカメラ、デジタルカムコーダ、監視カメラ等を含み得る。撮像システム 8 0 0 は、光学部 8 1 0 、撮像装置 1 0 、映像信号処理部 8 3 0 、記録・通信部 8 4 0 、タイミング制御部 8 5 0 、システム制御部 8 6 0 及び再生・表示

10

20

30

40

50

部 870 を含む。撮像装置 10 には、上述の第 1 乃至第 5 の実施形態の撮像装置が用いられる。

#### 【 0100 】

レンズ等の光学系である光学部 810 は、被写体からの光を撮像装置 10 の、複数の画素 100 が 2 次元状に配列された画素アレイ 101 に結像させ、被写体の像を形成する。撮像装置 10 は、タイミング制御部 850 からの信号に基づくタイミングで、画素アレイ 101 に結像された光に応じた信号を出力する。撮像装置 10 から出力された信号は、映像信号処理部である映像信号処理部 830 に入力され、映像信号処理部 830 が、プログラム等によって定められた方法にしたがって信号処理を行う。なお、映像信号処理部 830 で行われる信号処理は、第 1 の実施形態等で述べたデジタル CDS、桁処理等を含んでもよい。映像信号処理部 830 での処理によって得られた信号は画像データとして記録・通信部 840 に送られる。記録・通信部 840 は、画像を形成するための信号を再生・表示部 870 に送り、再生・表示部 870 に動画又は静止画像を再生・表示させる。あるいは、映像信号処理部 830 からの出力信号が直接再生・表示部 870 に送られ、動画又は静止画像の再生・表示が行われる構成を有してもよい。記録・通信部 840 は、また、映像信号処理部 830 からの信号を受けて、システム制御部 860 と通信を行うほか、不図示の記録媒体に、画像を形成するための信号を記録する動作も行う。10

#### 【 0101 】

システム制御部 860 は、撮像システムの動作を統括的に制御するものであり、光学部 810、タイミング制御部 850、記録・通信部 840、及び再生・表示部 870 の駆動を制御する。また、システム制御部 860 は、例えば記録媒体である不図示の記憶装置を備える。この記憶装置に撮像システムの動作を制御するのに必要なプログラム等が記録される。また、システム制御部 860 は、例えばユーザの操作に応じて駆動モードを切り替える信号を撮像システム内に供給する。具体的な例としては、読み出す行の変更、リセットする行の変更、電子ズームに伴う画角の変更、電子防振に伴う画角のずらし等である。タイミング制御部 850 は、システム制御部 860 による制御に基づいて撮像装置 10 及び映像信号処理部 830 の駆動タイミングを制御する。20

#### 【 0102 】

以上のように、本実施形態の撮像システム 800 は、上述の第 1 乃至第 5 の実施形態のいずれかの撮像装置 10 を適用して撮像動作を行うことが可能である。30

#### 【 0103 】

本発明を適用し得る実施形態は、上述の実施形態のみに限定されない。例えば、いずれかの実施形態の一部の構成を、他の実施形態に追加した実施形態、あるいは他の実施形態の一部の構成と置換した実施形態も本発明を適用し得る実施形態であると理解されるべきである。

#### 【 0104 】

また、第 6 の実施形態に示した撮像システムは、本発明の撮像装置を適用しうる撮像システムの一例を示したものであり、本発明の撮像装置を適用可能な撮像システムは図 11 に示した構成に限定されるものではない。

#### 【 符号の説明 】

##### 【 0105 】

100 画素

104 比較器

105 カウンタ

107 第 1 メモリ群

108 第 2 メモリ群

40

【図1】

【図2】

【図3】

【図4】

| Case1         |                                                             | S1の取り得る範囲 |  |

|---------------|-------------------------------------------------------------|-----------|--|

| BIn[0]        |                                                             | S2        |  |

| BIn[1]        |                                                             |           |  |

| BIn[2]        |                                                             |           |  |

| BIn[3]        |                                                             |           |  |

| S2(AL)        | 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62                |           |  |

| S2(Lo)        | 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14                          |           |  |

| S1(Lo)        | -7 -6 -5 -4 -3 -2 -1 0 1 2 3 4 5 6 7                        |           |  |

| diff          | -7 -6 -5 -4 -3 -2 -1 0 1 2 3 4 5 6 7                        |           |  |

| S1+S2(期待値)    | 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 |           |  |

| S1+S2(Simple) | 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 |           |  |

| S1+S2         | 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 |           |  |

| Case2         |                                                             | S1の取り得る範囲 |  |

| BIn[0]        |                                                             | S2        |  |

| BIn[1]        |                                                             |           |  |

| BIn[2]        |                                                             |           |  |

| BIn[3]        |                                                             |           |  |

| S2(AL)        | 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70                |           |  |

| S2(Lo)        | 8 9 10 11 12 13 14 15 0 1 2 3 4 5 6                         |           |  |

| S1(Lo)        | -7 -6 -5 -4 -3 -2 -1 0 1 2 3 4 5 6 7                        |           |  |

| diff          | -7 -6 -5 -4 -3 -2 -1 0 1 2 3 4 5 6 7                        |           |  |

| S1+S2(期待値)    | 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 |           |  |

| S1+S2(Simple) | 119 120 121 122 123 124 125 126 111 112 113 114 115 116 117 |           |  |

| S1+S2         | 119 120 121 122 123 124 125 126 127 128 129 130 131 132 133 |           |  |

| Case3         |                                                             | S1の取り得る範囲 |  |

| BIn[0]        |                                                             | S2        |  |

| BIn[1]        |                                                             |           |  |

| BIn[2]        |                                                             |           |  |

| BIn[3]        |                                                             |           |  |

| S2(AL)        | 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71                |           |  |

| S2(Lo)        | 9 10 11 12 13 14 15 0 1 2 3 4 5 6 7                         |           |  |

| S1(Lo)        | -7 -6 -5 -4 -3 -2 -1 0 1 2 3 4 5 6 7                        |           |  |

| diff          | -7 -6 -5 -4 -3 -2 -1 0 1 2 3 4 5 6 7                        |           |  |

| S1+S2(期待値)    | 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 |           |  |

| S1+S2(Simple) | 137 138 139 140 141 142 143 128 129 130 131 132 133 134 135 |           |  |

| S1+S2         | 121 122 123 124 125 126 127 128 129 130 131 132 133 134 135 |           |  |

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

(b)

【図13】

【図14】

---

フロントページの続き

(72)発明者 吉田 大介

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 鈴木 明

(56)参考文献 特開2015-023391(JP,A)

特開2009-296423(JP,A)

国際公開第2015/019837(WO,A1)

特開2013-110457(JP,A)

特開2013-106225(JP,A)

特開2012-191359(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H03M 1/56