US 20110167526A1

### (19) United States

# (12) Patent Application Publication Chow et al.

(10) **Pub. No.: US 2011/0167526 A1**(43) **Pub. Date:** Jul. 7, 2011

## (54) MICROSPRINGS HAVING NANOWIRE TIP STRUCTURES

(75) Inventors: **Eugene Chow**, Fremont, CA (US);

Pengfei Qi, Palo Alto, CA (US)

(73) Assignee: PALO ALTO RESEARCH CENTER INCORPORATED,

Palo Alto, CA (US)

(21) Appl. No.: 13/045,042

(22) Filed: Mar. 10, 2011

### Related U.S. Application Data

(62) Division of application No. 11/963,507, filed on Dec. 21, 2007, now Pat. No. 7,927,905.

#### **Publication Classification**

(51) **Int. Cl. G01Q 70/08** (2010.01) **B82Y 30/00** (2011.01)

(52) **U.S. Cl.** ...... **850/56**; 977/762; 977/773

(57) ABSTRACT

A stress-engineered microspring is formed generally in the plane of a substrate. A nanowire (or equivalently, a nanotube) is formed at the tip thereof, also in the plane of the substrate. Once formed, the length of the nanowire may be defined, for example photolithographically. A sacrificial layer underlying the microspring may then be removed, allowing the engineered stresses in the microspring to cause the structure to bend out of plane, elevating the nanowire off the substrate and out of plane. Use of the nanowire as a contact is thereby provided. The nanowire may be clamped at the tip of the microspring for added robustness. The nanowire may be coated during the formation process to provide additional functionality of the final device.

FIG. 3 PRIORART

FIG. 4

FIG. 6B

FIG. 6C

FIG. 7A

FIG. 7B

FIG. 8A

FIG. 8B

FIG. 9A

FIG. 9B

FIG. 10A

FIG. 10B

FIG. 11A

FIG. 11B

FIG. 12A

FIG. 12B

FIG. 13A

FIG. 13B

FIG. 14A

FIG. 14B

FIG. 15A

80

FIG. 16

### MICROSPRINGS HAVING NANOWIRE TIP STRUCTURES

### CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] The present application is a divisional application of copending U.S. Application for Letters Patent titled "Method of Producing Microsprings Having Nanowire Tips", Ser. No. 11/963,507, filed on Dec. 21, 2007, which, in its entirety, is hereby incorporated herein by reference and to which priority is claimed.

#### BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

[0003] The present invention relates generally to photolithographically patterned spring contacts, and more particularly to a plurality of such photolithographically patterned spring contacts having nanowire tips, released at one end from a substrate such that the tips are oriented out of the plane of the substrate.

[0004] 2. Description of the Prior Art

[0005] Photolithographically patterned spring devices (referred to herein as "microsprings") have been developed, for example, to produce low cost probe cards, and to provide electrical connections between integrated circuits. Such microsprings are disclosed and described, for example, in U.S. Pat. No. 5,914,218, which is incorporated by reference herein. A microspring is generally a micrometer-scale elongated metal structure having a free (cantilevered) portion which bends upward from an anchor portion which is affixed directly or indirectly to a substrate. The microspring is formed from a stress-engineered metal film (i.e., a metal film fabricated to have a stress differential such that its lower portions have a higher internal compressive stress than its upper portions) that is at least partially formed on a release material layer. The microspring is attached to the substrate (or intermediate layer) at a proximal, anchor portion thereof. The microspring further includes a distal, tip portion which bends away from the substrate when the release material located under the tip portion is removed (e.g., by etching).

[0006] The stress differential is produced in the spring material by one of several techniques. According to one technique, different materials are deposited in layers, each having a desired stress characteristic, for example a tensile layer formed over a compressive layer. According to another technique a single layer is provide with an intrinsic stress differential by altering the fabrication parameters as the layer is deposited. The spring material is typically a metal or metal alloy (e.g., Mo, MoCr, W, Ni, NiZr, Cu), and is typically chosen for its ability to retain large amounts of internal stress. Microsprings are typically produced using known photolithography techniques to permit integration of the microsprings with other devices and interconnections formed on a common substrate. Indeed, such devices may be constructed on a substrate upon which electronic circuitry and/or elements have previously been formed.

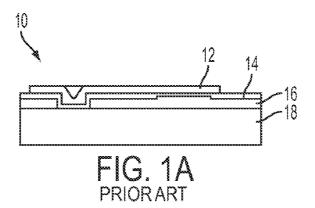

[0007] FIGS. 1A-1C illustrate the basic, prior art process of fabricating stress-engineered cantilevered microsprings 10. With reference first to FIG. 1A, stress-engineered cantilevers 10 are fabricated by depositing and patterning one or more films to form a stress-engineered cantilever 12 with a designed strain-gradient over a sacrificial layer 14, which itself is formed over a dielectric layer 16 pattered over a

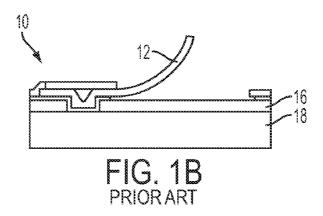

substrate 18. Deposition conditions and other parameters may be controlled, as known in the art, to tailor the stresses along the elevation (e.g., in various layers) of the stressengineered cantilever 12. Stress-engineered cantilever 12 can be of a single film type, such as MoCr alloy, where different layers of the film have different stresses. As stress-engineered cantilever 12 is initially formed in a plane which is parallel to the primary plane of substrate 18, we refer to the fabrication of stress-engineered cantilever 12 as being "in-plane." Stressengineered cantilever 12 may also be composed of different film types with different stresses. Stress-engineered cantilever 12 is patterned and then released, as illustrated in FIG. 1B, by etching away a portion of sacrificial layer 14 underneath the stress-engineered cantilever 12. To lift the spring up and away from the substrate the stress gradient should be such that more compressive layers are disposed closer to the substrate, and the more tensile layers disposed thereover.

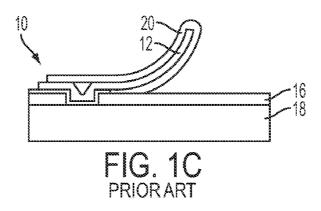

[0008] After stress-engineered cantilever 12 is released, additional layers 20 can optionally be plated on the surface of stress-engineered cantilever 12, as shown in FIG. 1C, to improve strength and conductivity. In additional, multiple stress-engineered cantilevers 12 may be formed in an overlying relationship such that, for example, a lower stress-engineered cantilever 12 provides structural support for an upper stress-engineered cantilever 12, as disclosed in the aforementioned U.S. patent application Ser. No. 11/292,474.

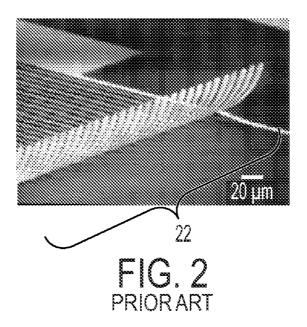

[0009] Stress-engineered cantilevers formed by this process are unique because the process facilitates the formation of arrays 22 of devices with contact points out of the plane in which the devices are manufactured, as shown in FIG. 2. Linear and 2-d arrays can thereby be produced. Typically, array 22 is formed, with a tip-to-tip spacing selected according to the application of the array. For example, for probe testing, the tip-to-tip spacing would match the spacing of contact pads, leads or the like on the device under test.

[0010] Another unique aspect of the process used to fabricate array 22 is that the stress-engineered cantilevers 12 are formed from thin films (e.g., 5 um or less) in-plane, that is, in the same plane as the original substrate. This is in contrast to processes used to produce, for example, conventional silicon atomic force microscopy (AFM) tips, where a tip is fabricated from a relatively thick film (10-20 microns), requiring expensive and complex 3D etching techniques, and where the etch sidewall profile strongly effects the shape tip of the tip of the AFM tip.

[0011] Such microsprings may be used in probe cards, for electrically bonding integrated circuits, circuit boards, and electrode arrays, and for producing other devices such as inductors, variable capacitors, scanning probes, and actuated mirrors. For example, when utilized in a probe card application, the tip of the free portion of a microspring is brought into contact with a contact pad formed on an integrated circuit, and signals are passed between the integrated circuit and test equipment via the probe card (i.e., using the microspring as an electrical contact).

[0012] Microsprings typically terminate at a tip, whose shape may be controlled photolithographically as the microspring is pattered in-plane. In certain applications, the microspring has a tip profile (e.g., an apical point) capable of physically penetrating an oxide layer that may form on the surface to which electrical contact is to be made. In order to provide a reliable contact with a surface to be contacted, the microspring must provide a relatively high contact force (the force which the spring applies in resisting a force oppositely

applied from the surface to be contacted). This is particularly true in applications in which the apical point must penetrate an oxide layer. For example, some probing and packaging applications require a contact force on the order of 50-100 mg between the tip and the structure being contacted.

[0013] In certain applications, such as probe-based data storage, lithography, imaging, metrology, and printing and biology addition, there is a desire or requirement for extremely sharp microspring tips (<100 nm). In these applications lower forces are often used (<1 micronewton). Current lithographic process have not proven sufficient to provide the desired sharpness. There have been various attempts to provide very fine tip structures in the prior art.

[0014] One approach to providing a very fine tip structure for a microspring has been to manually bond a pre-formed nanowire onto the tip of a released microspring. There are several known methods of producing nanowires.

[0015] Silicon nanowires—Chemical vapor deposition (CVD) has been widely used to synthesize and grow large quantities of high quality silicon nanowires. The growth involves a vapor-liquid-solid process: vapor phase precursor (e.g., SiH4) decomposes on the surface of catalysts (e.g., Au) when heated up, and forms a liquid alloy. The continuous feeding of Si into the alloy will supersaturate the alloy and Si nanowires will begin to grow elongate.

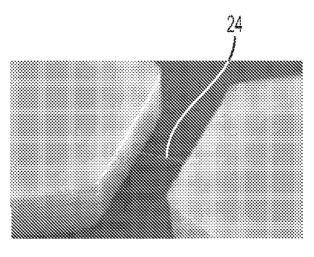

[0016] Silicon nanowires grow preferentially along the <111> direction through epitaxial growth. If the vertical {111} planes are exposed, Si nanowires 24 can grow horizontally, and bridge two opposite {111} planes, as illustrated in FIG. 3 (from R. He, D. Gao, R. Fan, A. I. Hochbaum, C. Carraro, R. Maboudian, and P. Yang, "Si Nanowire Bridges in Microtrenches: Integration of Growth into Device Fabrication," Advanced Materials, vol. 17, pp. 2098-2102, 2005). The density, diameter, and length of the bridging Si nanowire 24 can be well-tuned by controlling the density of catalyst, size of the catalyst, and the distance between the two opposite planes. Growth temperatures are in the range of 400° C. and diameters are typically 10-20 nanometers (nm).

[0017] Germanium nanowires—The chemical vapor deposition (CVD) growth strategy for germanium nanowires is very similar to silicon nanowires, which also follows a vaporliquid-solid process, except that a gas phase precursor will be a germanium-containing gas, such as GeH4 instead of SiH4, and in general the growth temperature will be lower than Si nanowire growth (approximately 300° C.). Typical diameters are 10-40 nanometers (nm).

[0018] Carbon nanotubes—Growth of nanometer-scale structures in carbon produce a unique, hollow or tube-like structure. Accordingly, such structures formed of Carbon are commonly referred to as nanotubes. For carbon nanotube growth, CVD growth is also one of the best synthesis methods. The gas phase precursors are carbon containing gases, such as CH4, C2H4, C2H5OH vapor etc; metal catalysts are usually Fe, Co, Ni etc instead of Au for Si and Ge nanowires. Typical growth temperatures are approximately 650° C. and of diameter less than 3 nm.

[0019] Nanotubes spread out on a substrate can be placed onto a silicone AFM tip by using micromanipulators. Nanotubes manually attached to probe tips are available as "CNTek carbon nanotube-tipped AFM probes" from Nanoscience Instruments, Inc. (www.nanoscience.com). For many applications, such probes are prohibitively expensive. Furthermore, production of arrays are not practical with this method because the assembly process is insufficiently repeatable in

terms of nanotube position and length. In general, given the very small size of these structures, accurately positioning and bonding the nanowire onto the tip of a probe has proven challenging.

[0020] Another effort at providing integrated nanowires and microsprings involves growth of nanowires on conventional cantilever tips. Growth of carbon nanotubes on a probe structure has been attempted with using chemical vapor deposition where the catalyst is patterned on the side of an existing silicon etched probe tip. It is asserted that this process produces nanotubes protruding on 90% of an array of probe tips on a wafer, extending 1-10 micrometers beyond the silicon tip. However, this non-uniformity has prohibited use of these structures, as grown, for probing applications. To shorten the nanotubes to sub-1 micrometer extension, an oxidation discharge process has been employed, which necessitates handling each single cantilever in a tapping mode electrical AFM mode setup. Similar to the gluing, the process is essentially serial, and prohibitive in terms of cost, time, and ultimately uniformity.

[0021] Field enhanced growth has also been used for nanometer-scale tip production, such as growing tungsten nanowires seeded from metal pads in a tungsten vapor ambient. The process is serial (one tip at a time), cumbersome, and requires precise alignment of a sharp tip counter electrode close to the silicon tip. Nonetheless, nanowires on the ends of silicon tips have been fabricated and used in probing experiments.

[0022] Focused ion beam etching and electron beam induced deposition have also been used to produce devices having micromachined nanometer-scale tips, referred to herein as nanotips. Each of these techniques attempts to place a nanowire or nanotube perpendicularly at the micromachined tip of an in-plane probe structure. However, such processes suffer from low uniformity, control, yields, and throughputs due to the difficulty of vertically aligning the nanowires (both in length and in angle relative to the plane of the probe).

[0023] What is needed is a way to make nanowires or equivalently, nanotubes, on cantilevers in a parallel process such that two dimensional arrays of uniform nanotips can be readily formed.

### SUMMARY OF THE INVENTION

[0024] Accordingly, the present invention is directed to a method of manufacturing a of stress-engineered, cantilevered microspring having a nanowire tip, and to a microspring and an array of microsprings so formed. Nanowires (as used herein including both solid structures and hollow or nanotube structures) are grown generally in-plane with the substrate at the tips of the microsprings prior to release of the microsprings from the substrate. Controlled geometry of the nanowires may therefore be provided by standard growth and patterning processes. The microsprings with nanowire tips may then be released from the substrate, causing the microspring tips and hence the nanowire tips to point up, out of the plane of the substrate, due to a relaxing stress gradient. The nanowires may be in electrical communication with the microsprings facilitating the use of the nanowires as contacts, probe tips, and the like. This approach significantly simplifies the integration of uniform nanowires into probe based applications.

[0025] According to one aspect of the invention, the basic steps of providing a microspring having a nanowire tip comprise:

[0026] Defining a stress-engineered cantilever and appropriate growth boundaries in-plane

[0027] Defining the nanowire catalyst/seed layers

[0028] Growth of the nanowires with good control and uniformity

[0029] Release the stress-engineered cantilever and the nanowire, forming a nanotip array

[0030] According to another aspect of the present invention, uniform nanowire length can be provided by photolithographically defining a mask which protects a selected length of the grown nanowire from etching. That is, portions of the nanowire not protected by the mask may be removed for example by etching. Length of the nanowire may then be controlled up to the resolution of the lithographic masking process.

[0031] According to another aspect of the present invention, a nanowire grown at the tip of a microspring may be clamped at the point of attachment of the nanowire to the microspring to provide improved robustness. This clamping may be accomplished by deposition and patterning of a thin-film layer, taking advantage of the processes and orientation used to form the microspring and nanowire.

[0032] According to still another aspect of the present invention, a field enhancement process may be employed to facilitate nanowire growth. Electrodes may be formed of the material ultimately forming the microspring. A potential between these electrodes assists with directionality, thickness, and other attributes of the grown nanowire.

[0033] According to yet another aspect of the present invention, catalyst sites for nanowire growth may be deterministically provided on the surface of the microspring. While this results in some out-of-plane growth of a nanowire, the nanowire may be coaxed in-plane, if necessary, and held in place by a clamping structure, again for example photolithographically defined.

[0034] According to a still further aspect of the present invention, the microspring and the nanowire may be separately and independently fabricated, then joined together such that the nanowire extends out of plane upon release of the microspring. The nanowire is preferably attached to the microspring prior to spring release, but may alternatively be attached after release. A clamping structure may optionally be employed to improve the robustness of the mechanical connection between the nanowire and the microspring. The nanowire may be attached to the microspring either on the face of the microspring or on a sidewall of the microspring.

[0035] Finally, according to still another aspect of the present invention, the nanowire at the tip of the microspring may be coated with a material to obtain a desired functionality. For example, electrical junctions may be formed on the surface of the nanowire. Or, the nanowire may be coated in a biological material, as may be appropriate for nanometer-scale sensing, drug delivery, etc.

[0036] The above is a summary of a number of the unique aspects, features, and advantages of the present invention. However, this summary is not exhaustive. Thus, these and other aspects, features, and advantages of the present invention will become more apparent from the following detailed

description and the appended drawings, when considered in light of the claims provided herein.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0037] In the drawings appended hereto like reference numerals denote like elements between the various drawings. While illustrative, the drawings are not drawn to scale. In the drawings:

[0038] FIGS. 1A through 1C are illustrations of a prior art process for fabrication of a microspring.

[0039] FIG. 2 is a micrograph of an array of microsprings released from a substrate according to the prior art.

[0040] FIG. 3 is a nanowire grown between exposed faces of a seed structure according to the prior art.

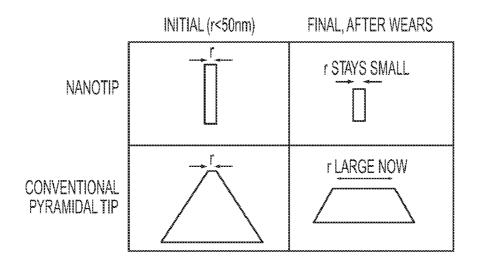

[0041] FIG. 4 is a table illustrating the wear characteristics of two different profiles of nanotips for probe applications.

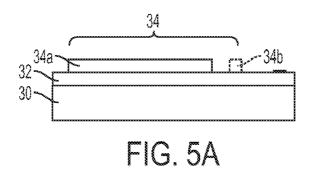

[0042] FIGS. 5A and 5B are an elevation view and a plan view, respectively, of a first step in the process of producing a microspring having a nanowire grown in situ at the tip thereof according to an embodiment of the present invention.

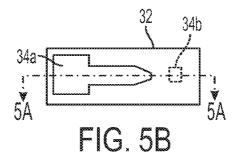

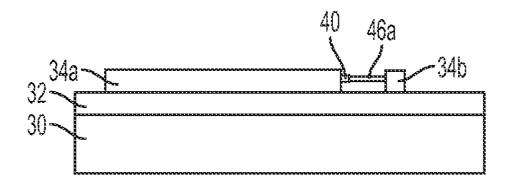

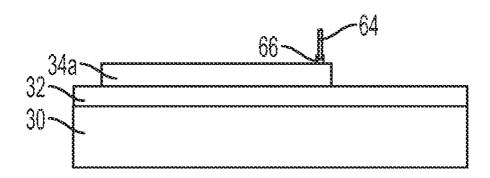

[0043] FIGS. 6A and 6B are an elevation view and a plan view, respectively, of the step of providing catalyst sites for the growth of nanowires in the process of producing a microspring having a nanowire grown in situ at the tip thereof according to an embodiment of the present invention.

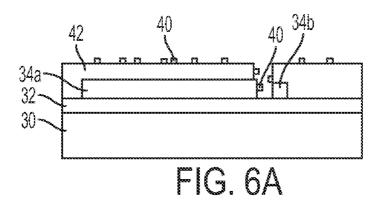

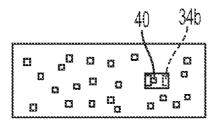

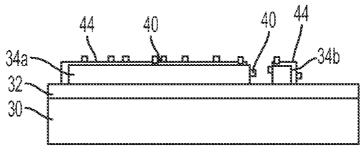

[0044] FIG. 6C is an elevation view of the step of providing catalyst sites from the growth of nanowires, including the limiting of growth of nanowires on selected surfaces by the application of a fouling layer in the process of producing a microspring having a nanowire grown in situ at the tip thereof according to an embodiment of the present invention.

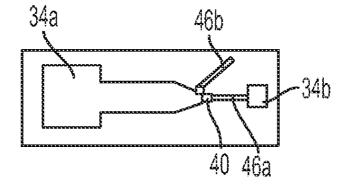

[0045] FIGS. 7A and 7B are an elevation view and a plan view, respectively, of the step of growing a nanowire in the process of producing a microspring having a nanowire grown in situ at the tip thereof according to an embodiment of the present invention.

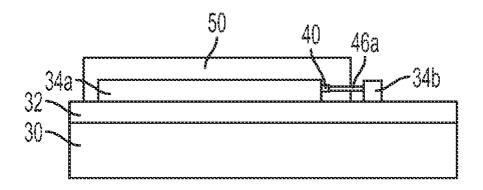

[0046] FIGS. 8A and 8B are an elevation view and a plan view, respectively, of the step of masking and defining the nanowire length (and elimination of extraneous secondary nanowires) in the process of producing a microspring having a nanowire grown in situ at the tip thereof according to an embodiment of the present invention.

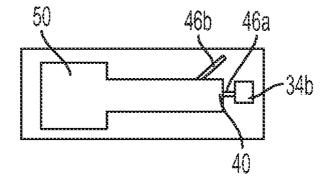

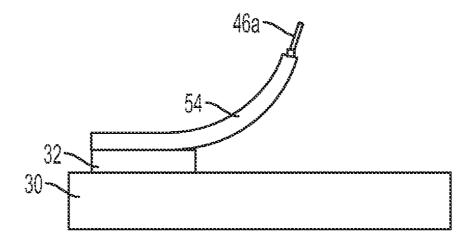

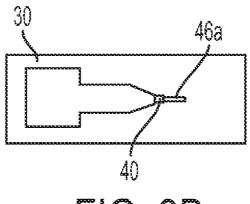

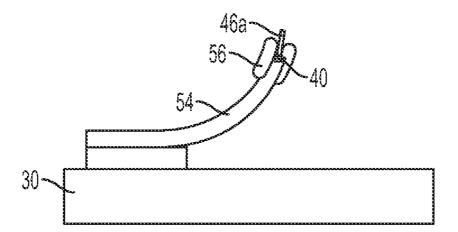

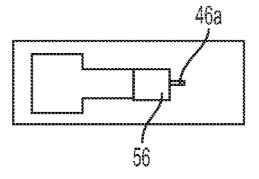

[0047] FIGS. 9A and 9B are an elevation view and a plan view, respectively, of the release step in the process of producing a microspring having a nanowire grown in situ at the tip thereof according to an embodiment of the present invention

[0048] FIGS. 10A and 10B are an elevation view and a plan view, respectively, of the step of forming a clamping structure at the junction of a microspring tip and nanowire in the process of producing a microspring having a nanowire grown in situ at the tip thereof according to another embodiment of the present invention.

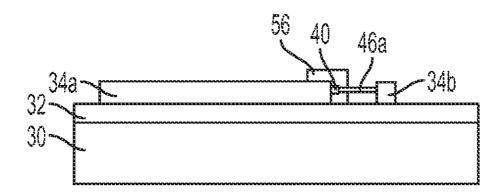

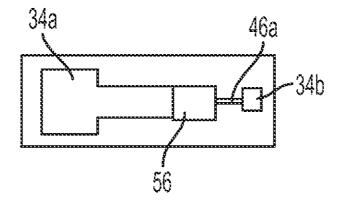

[0049] FIGS. 11A and 11B are an elevation view and a plan view, respectively, of the release step in the process of producing a microspring having a nanowire grown in situ at the tip thereof according to the process shown in FIGS. 10A and 10B.

[0050] FIGS. 12A and 12B are an elevation view and a plan view, respectively, of the step of field enhanced growth of a nanowire at the tip of a microspring in the process of producing a microspring having a nanowire grown in situ at the tip thereof according to yet another embodiment of the present invention.

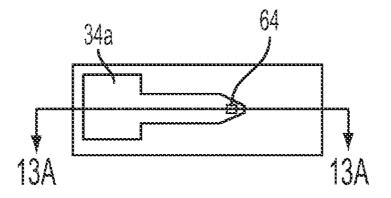

[0051] FIGS. 13A and 13B are an elevation view and a plan view, respectively, of the step of controlled catalyst site growth of a nanowire out of plane at the tip of a microspring in the process of producing a microspring having a nanowire grown in situ at the tip thereof according to still another embodiment of the present invention.

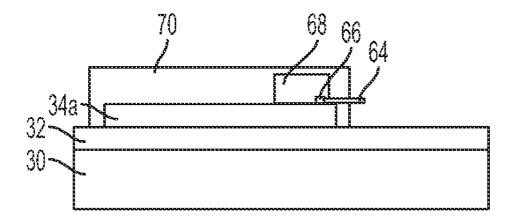

[0052] FIGS. 14A and 14B are an elevation view and a plan view, respectively, of the step of clamping in-plane a nanowire grown out of plane at the tip of a microspring in the process of producing a microspring having a nanowire grown in situ at the tip thereof according to the embodiment shown in FIGS. 13A and 13B.

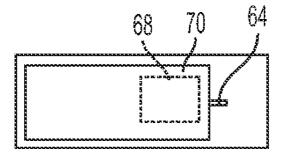

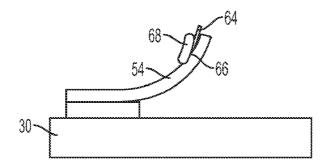

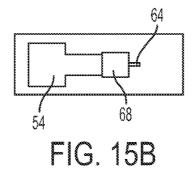

[0053] FIGS. 15A and 15B are an elevation view and a plan view, respectively, of the release step in the process of producing a microspring having a nanowire grown in situ at the tip thereof according to the process shown in FIGS. 14A and 14B.

[0054] FIG. 16 is a perspective view of a portion of a nanowire showing a selected coating applied to a portion thereof according to yet another embodiment of the present invention

### DETAILED DESCRIPTION OF THE INVENTION

[0055] We next present a description of several embodiments of the present invention. The specific requirements for these embodiments vary by application, but probe array requirements for data storage applications are fairly representative of other applications.

[0056] Requirement for probe based data storage include:

[0057] fine tip resolution (<100 nm, with <30 nm pre-

[0058] robust tips (don't wear, tip stays sharp, consistent position)

[0059] uniform tip heights to facilitate alignment to the substrate (height deviation within several microns)

[0060] high yield fabrication process (for 100s to thousands of probes)

[0061] adequate conductivity of nanotips

[0062] Sharp tips enable small data bits to be written and read—18 nanometer pitches and 2 terabits/in<sup>2</sup> have been demonstrated. Equally important though, is the sharpness as a function of time. Inevitably the tips wear—especially for the approaches which uses a hard media substrate. High aspect ratio tips are advantaged because the radius tends to stay small as the tip wears (FIG. 4). Nanotips can be higher aspect ratio than traditional bulk silicon etched based tips. Because the media is not patterned, the tips do not have to be perfectly straight and perfectly vertical from the substrate. However they do need to be sufficiently uniform to be able to repeatedly contact the same spot so that they can read a bit after writing it (media is initially unpatterned, and the writing and reading tips are usually the same). In addition the bit size should be sufficiently uniform, which could depend on multiple factors such as tip radius and force. The force uniformity requirements, for a given cantilever, can translate into a height uniformity requirement. Ideal requirements are force variation of less than 10 nano-Newtons (nN) and tip radius of less than 20 nanometers (nm), with small tip height variation (on the order of several micrometers or less, depending on cantilever probe stiffness).

[0063] The tip fabrication process should be readily integrated with the cantilever process. The yield needs to be extremely high, but slight deviations from 100% can be cor-

rected in software and planned for with redundancy. Finally the electrical conductivity of the tip should be appropriate for the writing/reading mechanism. Normally the bulk silicon based tips are not doped for lower conductivity, but if needed the nanotips wires could be doped.

[0064] According to the present invention, nanowires or nanotubes are fabricated parallel to the substrate at the tips of in-plane fabricated stress-engineered cantilevers. The stress-engineered cantilevers pull the nanotip out of the plane when released. The nanowire can then be grown parallel to the surface of a substrate, so that multiple processing techniques can be used to control growth uniformity.

[0065] The basic steps of a first embodiment of the present invention include:

[0066] Define the stress-engineered cantilever

[0067] Define the nanowire catalyst/seed layers

[0068] Grow the nanowires with good control and uniformity

[0069] Release the stress-engineered cantilever and the nanowire, forming a nanotip array

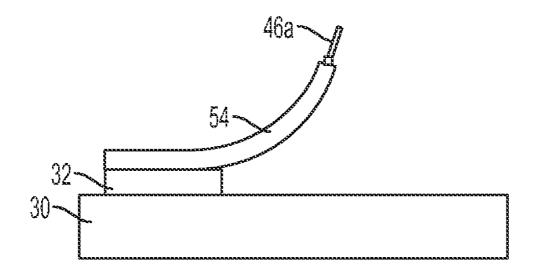

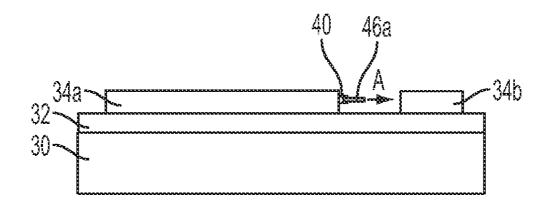

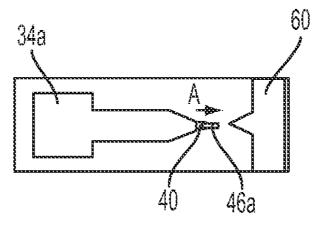

[0070] With reference initially to FIGS. 5A and 5B, there is shown therein and described below a basic process for integrating silicon nanowires onto a stress engineered cantilever. The process begins with the deposition of a sacrificial layer 32 over a silicon, glass, quartz or a polymer such as polyimide substrate 30. Release layer 32 is formed of materials known and used in stressed metal applications, such as Ti, Ni, SiO2, SiN, SiOxNy or Si. Optionally, substrate 30 may have previously formed thereon electronic components and/or circuitry (not shown), or alternatively substrate 30 may be a printed circuit board or printed wiring board. An optional insulating underlayer (not shown) may be deposited and patterned in applications in which electrical insulation is desired between the microspring and other elements of the final plural microspring structure.

[0071] A stress-engineered material system 34 is next deposited over the structure, then photolithographically patterned. Ultimately, material system 34 becomes a microspring when released. According to one embodiment, material system 34 comprises prior to release two spaced apart regions 34a, 34b, which are photolithographically formed and which will be used for the growth of a nanowire or nanotube therebetween. Accordingly, material system 34 may be any of a variety of metals or alloys suitable for the creation of microsprings, such as Mo, MoCr, W, Ni, NiZr, Cu (or a non metal). Material system 34 can also be composed of a low stress single crystal silicon layer and a high stress layer, tensile or compressive. The (111) plane of single crystal silicon has been shown to provide a high yield for growing in-plane nanowires (normal to the sidewalls). This system is illustrate in FIG. 3. A stress-engineered layer such as silicon nitride can be used to pull the silicon layer up during the

[0072] Material system 34 is deposited in such a way as to develop within the layer a stress differential in a vertical direction across the layer's cross-section. That is, the stress in the system varies from bottom to top. According to one embodiment, material system 34 comprises a single layer of material, and the gas pressure or power is varied during the deposition process to create a stress-engineered single layer (i.e., a layer comprised of a single material) having a desired cross-sectional stress differential. According to another embodiment (not shown), material system 34 is itself comprised of a number of sub-layers, each sub-layer having a

desired intrinsic stress. When properly selected, the assembly of sub-layers mechanically and electrically functions as a single system, but the bulk stress differential across the system of layers is a composition of the individual stresses of the sub-layers. These techniques are further described in U.S. Pat. No. 5,613,861, and U.S. Pat. No. 5,914,218 which are incorporated by reference herein. While formed in a plane, the result of the stress in system 34 is that when the layer is patterned into a microspring structure, two regions are formed. A first, proximal, anchor region attaches the microspring to the substrate (or an intermediate layer over the substrate), and a second, distal, tip region is released from the substrate by removal of a portion of release layer 32. When released, the tip region of the microspring bends out of plane, resulting in a non-planar microspring profile having a desired spring constant. The released structure is discussed further below.

[0073] Various combinations of stress engineered layers and nanotips are possible, but the compatibility of the process temperatures needs to be considered. For example, silicon or germanium nanowires can be grown above metal stress-engineered layers as long as the temperatures do not anneal out the stress, meaning an effective limit of approximately 400 C or less. Carbon nanotube manufacturing is typically at much higher temperatures, on the order of 700 C, so the stress engineered layer may be further deposited (or alternatively, deposited in whole) after the nanotube growth. Alternatively, material from which stress-engineered material system 34 is formed should be a high temperature film like a tensile nitride

[0074] According to one embodiment, the single crystal silicon can be purchased as the top layer of an SOI (siliconon-insulator) wafer, which has thin silicon and thin oxide on a thick substrate. The in-plane cantilever structure can be patterned with standard photolithography and etching techniques.

[0075] With reference next to FIGS. 6A and 6B, the next step is to deposit nanometer scale metal dots 40 to serve as growth seed (catalyst) sites and to define the diameter of the nanowire to be formed. One method is to flow a solution containing nanodots 40 over a prepatterned liftoff mask 42. Commercially available nanodot solutions include gold particles 10s of nm diameter. (See www.Aldrich-Sigma.com; www.tedpella.com.) The concentration of particles should be high enough so that one or more particles attaches to the sidewall of the cantilever tip. The liftoff layer (such as photoresist) is then removed to remove unwanted and unneeded seed dots from the structure.

[0076] According to a variation of this embodiment, the catalyst sites at the locations of nanodots 40 may be "poisoned" to selectively suppress nanowire growth. As illustrated in FIG. 6C, a fouling layer 44 may be formed on surfaces of the stress-engineered material system to poison the catalyst thereover. Molybdenum, for example, is known to prevent nanowire growth from gold seed dots. A thin layer of patterned Mo may be defined such that only areas of portions 34a and 34b between which nanowire growth is desired are exposed. Accordingly, layer 44 may be comprised of Mo or an Mo alloy. Nanowire growth in all but the regions on layer 44 is thereby limited. If the fouling layer 44 is on the top surface of 34A and 34B but not on the sidewalls, then growth of nanowires should preferentially occur on the sidewalls over the top surface of 34A and 34B. In FIG. 6C the nanodot 40' on

the sidewall of 34B is not under a fouling layer 44 and is thus the most likely place for nanowire growth to occur.

[0077] With reference to FIGS. 7A and 7B, nanowires 46a, 46b are next grown. While growth of nanowires is well known in the art, in one embodiment of the present invention silicon wires may be grown, driven by a vapor phase precursor (using a chemical vapor deposition process), initiating from the gold dots 40 on the (111) sidewalls of the microspring tip. Ideally one wire, primary nanowire 46a, grows from each microspring sidewall, and the growth stops when it hits the opposing boundary region. However, it may be common that extraneous secondary nanowires, such as such as nanowires 46b, will grow from dots of various exposed sidewall portions of the microspring. Many aspects of the final nanowire may be controlled at this stage, such as the diameter of the wire, tensile properties of the nanowire, etc. It is noted that the growth of nanowires 46 are such that they are in electrical communication with stress-engineered material system 34 so that when stress-engineered material system 34 is released to form a microspring the nanowire may form an electrically conductive tip of the microspring.

[0078] With reference next to FIGS. 8A and 8B, a mask layer 50 may then be applied over the structure, and patterned in order to protect the microspring and a portion of nanowire 46a (and portions of wires 46b). Etching may then be performed to remove any exposed material, such as exposed portions of nanowires 46a, 46b, as well as the exposed portion 34b of stress-engineered material system 34. It will be noted that this etching step also effectively removes any extraneous secondary nanowires 46b. Note also that this step lithographically defines the length (and hence aspect ratio) of primary nanowire 46a, permitting very controlled and uniform nanowire length for an array of such nanowires, overcoming the uniform length problem present in many prior art efforts to provide nano-scale probe tips.

[0079] With reference to FIGS. 9A and 9B, mask layer 50 is removed for example by a solvent process. Sacrificial release layer 32 is next etched and portion 34a of stress-engineered material system 34 is undercut, releasing a portion 34a and thereby forming a microspring 54. The internal stress gradient lifts the microspring 54 out of the plane, taking with it the nanowire 46a.

[0080] In this embodiment, the vertical (i.e., out of plane) nanotip properties are controlled though multiple mechanisms which are applied while the microsprings are being fabricated in-plane. Such control has heretofore not been possible, particularly as a complete set of attributes controllable as part of a single manufacturing process. Specifically, the following attributes may be process-controlled:

[0081] Nanowire axis direction—this attribute may be controlled by selection of the crystal plane to be exposed as the microspring sidewall, electric field guided, fluidics to steer assembly.

[0082] Nanowire length (axial)—this attribute may be controlled by the size of the gap photolithographically formed between sections 34a and 34b of the stress engineered material system 34 and by the masking and etching steps following growth of the nanowire.

[0083] Number of nanowires in an array—this attribute may be controlled by the patterning of stochastically deposited nanodots (catalyst sites), or in an alternate embodiment, by deterministic patterning of seed layers (described further below), and by the masking and etching steps following growth of the nanowire.

[0084] Size of the nanowires—this attribute may be controlled by the size of the deposited nanodots which act as catalyst sites for nanowire growth, or in an alternate embodiment, by high resolution patterning of the catalyst layer.

[0085] Robustness of the nanowires—this attribute is provided by the robustness of the connection at the growth site of the nanowire (attachment at a growth site tends to be more robust than attachment at a point of adhesion of a separately formed nanowire), the control over the nanowire aspect ratio as part of the growth process, and the control of nanowire length by the masking and etching steps following growth of the nanowire.

[0086] Functionality of the nanowires—this attribute may be controlled by the pattern-wise dope, coat with polymers, or bio-coated particles.

[0087] There are many alternative embodiments which have important advantages and applications. According to a first such alternative embodiment, shown in FIGS. 10A, 10B, 11A and 11B, a clamping structure 56 is formed at the junction of the microspring tip and the nanowire for strength. With reference to FIGS. 10A and 10B, which show elevation and plan views, respectively, of a structure in the process of being produced, clamping structure 56 may be comprised of a material such as platinum or gold and is deposited with standard techniques like sputtering or plating, and readily patterned with etching or liftoff techniques such that it encases the junction between portion 34a of stress-engineered material system and nanowire 46a. This deposition and patterning takes place advantageously prior to release of portion 34a of stress-engineered material system from sacrificial layer 14. Improved adherence of nanowire 46a to the microspring formed on release of portion 34a is obtained. FIGS. 11A and 11B show the final structure including microspring 54, nanowire tip 46a, and clamping structure 56 in elevation and plan views, respectively.

[0088] It should be noted that in the foregoing, regions 34a and 34b were comprised of the same material. It will be appreciated however, that regions 34a and 34b may alternatively be comprised of different materials and/or formed at different times. For example, an oxide layer could serve as a boundary stop region 34b and have the advantage that it would etch away with the release layer, reducing the number of steps. Such an oxide material may in fact be the same material as sacrificial release layer 32. Indeed, it is possible to grow nanowires from the tip region of portion 34a without a corresponding region 34b (hence, region 34b is shown in dashed outline), with masking and etching as previously described to control the direction, size, and number of nanowires

[0089] Furthermore, it should be noted that in the prior description nanowire 46 was grown such that it extends between the sidewalls of regions 34a and 34b. However, the nanowire may, in fact, grow from the upper surface of region 34a (as opposed to the sidewall), to either the sidewall or upper surface of region 34b, or from the sidewall of region 34a to the upper surface of region 34b. It is therefore apparent that the long axis of the nanowire may vary a certain degree from being perfectly parallel with the plane of the substrate. Furthermore, the nanowire itself may not be linear at all. In these cases, the nanowire is said to generally extend in the direction of the plane of the substrate, with the important aspect being that upon release of the microspring, the nanowire presents its tip for desired contact rather than the tip of the

microspring. Typically this means that the tip of the nanowire extends farther above the surface of the substrate than the tip of the microspring.

[0090] According to another embodiment of the present invention, an in-plane field enhanced structure is used to guide nanowire growth. Such an embodiment in the process of production, is shown in elevation view in FIG. 12A and in plan view in FIG. 12B. Planar processing and etching techniques are be used to form portion 34b of stress-engineered material system 34 as a sharp counter electrode 60 to guide growth of the nanowire 46a. Such a lithographically aligned counter electrode 60 can be connected so that a single electrode controls growth over the entire wafer. For example, portion 34a may be electrically grounded, while a potential applied to electrode 60, resulting in guided growth of the nanowire 46a in the direction of arrow A. As with the priordescribed embodiments, counter electrode 60 can be removed after nanowire growth (by masking and etching) to allow for the release of the cantilever and lifting of the nanotip. In some applications the counter electrode 60 does not have to be removed, and can remain a permanent part of the final device. [0091] According to still another variation of the present invention, the catalyst sites (locations of nanodots 40) can be patterned directly by assembling nanodots in a solution with liftoff, or with masking of nanostructured substrates (such as iron nanoparticles in mesoporous silica). However, as this is still a stochastic process which will ultimately limit yield. Direct patterning of a catalyst is also applicable for integration with stress engineered devices. Electron beam lithography represents one method which may be used to pattern a nanometer scale dot (20-50 nm in diameter). Microcontact printing and dip pen lithography are alternate methods for patterning. Optimized growth conditions can lead to single wire/tube growth for each catalyst site. With reference to FIG. 13A, which is an elevation view, and FIG. 13B, which is a plan view, according to one aspect of this embodiment, the catalyst sites are patterned on the top surface of portion 34a of the stress-engineered material system. Nanowire 64 is then grown vertically from a catalyst site, such as patterned nanodot 66. Loosely adhered nanowires, such as nanowire 64, are controllably tipped over with fluidic force, such as by an directed gas stream, and then clamped by a clamping structure 68 onto stress-engineered material system portion 34a, as illustrated in FIGS. 14A and 14B. A masking layer 70 may be deposited and patterned over the structure to define the final length of nanowire 64 as previously described. The final released structure is illustrated in FIGS. 15A and 15B, which are unique in that nanowire 64 is rooted on microspring 54 not at a sidewall of the later, but rather on a planar surface thereof. [0092] According to another embodiment described herein, functionalized nanotips, as illustrated in FIG. 16, may be provided at the tips of the microsprings. Following growth of nanowire 80, a coating may me selectively applied to a portion thereof, such as distal portion 82, leaving the remainder 84 of nanowire 80 uncoated. The coating may be applied by way of a standard thin film or other appropriate process. A horizontally grown nanowire or nanotube can thereby be readily functionalized for a sensing or biochemical application. For example, part of the tip can be doped to form an electronic heterojunction for measuring a specific chemical concentration such as proton concentration (pH) or the like.

Furthermore, biological coatings may be applied to the

nanowire, or nanoparticles can be attached to well defined portions of the nanowires, for sensing or drug delivery on a nanometer scale.

[0093] According to a final embodiment of the present invention, prefabricated nanowires may be attached to prefabricated microsprings in-plane, prior to release of the microsprings from the substrate. According to this embodiment, the microsprings are formed as previously described. In one variation, first region 34A and possibly second region 34b are formed (e.g., FIG. 5A). Individual single or multiwall carbon nanotubes or nanowires in solution may then be assembled between portions 34a and 34b using Langmuir-Blodgett film monolayer protocols. A Langmuir-Blodgett film can be made by floating nanowires or carbon nanotubes on water surface inside a teflon trough with pressing bars. When the bars are pressed, the floating nanowires or carbon nanotube will be assembled and aligned. The nanowire or carbon nanotube assembly direction can be aligned with the microspring long axis direction so that nanowires or carbon nanotube can be attached to the microspring tips with the desired orientation. (See, D. Whang, S. Jin, Y. Wu and C. M. Lieber, "Large-Scale Hierarchical Organization of Nanowire Arrays for Integrated Nanosystems," Nano Lett. 3, 1255-1259 (2003)).

[0094] According to another variation of this embodiment, surface energy techniques can be used to assemble pre-fabricated nanowires. A patterned hydrophilic film on a cantilever tip region (such as 34A) would attract nanowires in solution to that region. Self assembled monolayers can be used to control the surface energy. See for example see S. Liu, J. B-H. Tok, J. Locklin Z. Bao, "Assembly and Alignment of Metallic Nanorods on Surfaces with Patterned Wettability", Small, Vol. 2, No. 12, p. 1448-1453, 2006; B. R. Martin, S. K. St. Angelo, T. E. Mallouk, "Interactions Between Suspended Nanowires and Patterned Surfaces", Advanced Functional Materials, Vol 12, No. 11-12, pp. 759-765, 2002.

[0095] According to still another variation of the present embodiment, dielectrophoretic or electrophoretic forces are used to assemble single tubes and grow them between regions 34a, 34b. An electric field between two patterned conductive regions (such as 34A, 34B) can be used to assemble prefabricated nanowires in a controlled manner. For example, an alternating electric field across a gap can assemble carbon nanotubes using diaeletrophoretic forces; see "L. A. Nagahara, I. Amlani, J. Lewenstein, R. Tsui, "Directed placement of suspended carbon nanotubes for nanometer-scale assembly", Vol. 80, No. 20, pp. 3826-3828, 2002). Similarly, electrophoretic forces can be used to assemble a nanowire which has its own electric charge. A constant electric field between two conductors, such as 34A and 34B could be used direct such a nanowire onto the tip region of the cantilever. The nanowires follow the electric field lines, so they could be directed to assemble in a designed direction with respect to the cantilever tip region 34A. If the nanowire had a positive charge on one side and a negative charge on the other, the positive end would go to the negative voltage electrode (could be 34A) and the negatively charged end of the nanowire would move towards the positive voltage electrode (could be 34B).

[0096] In still another variation, microfluidic channels are used for assembling bundles of nanotubes or nanowires. This microfluidic method has been demonstrated to align nanowires with good control. Silicone mode form channels are used to allow a solution containing nanowires to pass there-

through. Some nanowires will be aligned when passing through the channels, and attach to the substrate. The flow direction may be aligned with the long axis of the microsprings, and the aligned nanowires thereby attached with the desired orientation. (See, Y. Huang, X. Duan, Q. Wei, and C. M. Lieber, "Directed Assembly of One-Dimensional Nanostructures into Functional Networks," Science 291, 630-633 (2001)).

[0097] Regardless of the technique used to manipulate the nanowires on the microsprings, once the nanowires are satisfactorily placed, a clamping layer may be applied in order to secure the nanowires in place, and the structure may be masked and etched to remove undesirable nanowires, to control the length of the nanowires, to release the microspring, to remove the region 34b, etc., as previously described. A microspring curving upward out of the plane of the substrate having one or more nanowires of desired length and orientation is obtained. An array of such devices may just as easily be obtained

[0098] While a plurality of preferred exemplary embodiments have been presented in the foregoing detailed description, it should be understood that a vast number of variations exist, and these preferred exemplary embodiments are merely representative examples, and are not intended to limit the scope, applicability or configuration of the invention in any way. For example, the majority of the embodiments described above have focused on the production of a single nanowire at the tip of a microspring. However, it is entirely within the scope of the present invention to produce a structure having a plurality of such nanowires at the tip of the microspring, depending solely on the intended application of the structure so obtained. Furthermore, the description herein illustrates the production of a single microspring with nanowire formed thereon. However, any of the embodiments described herein may produce an array of such devices. The array may be a linear array (tips aligned in a single row), a two-dimensional array (tips varying in two dimensions in a plane above the substrate), or other suitable arrangement as a function of the intended application of the array. Therefore, the foregoing detailed description provides those of ordinary skill in the art with a convenient guide for implementation of the invention, by way of examples, and contemplates that various changes in the functions and arrangements of the described embodiments may be made without departing from the spirit and scope of the invention defined by the claims thereto.

What is claimed is:

- 1. A spring contact, comprising:

- a substrate;

- a stress-engineered member having an anchor portion and a free portion, the anchor portion fixed to the substrate and substantially extending in a first plane, the free portion not fixed to the substrate and extending out of and not parallel with the first plane;

- a nanowire formed on the free portion and extending out of and not parallel with the first plane;

- wherein the stress-engineered member as-formed is provided with an inherent stress gradient in a direction substantially perpendicular to the first plane, said nanowire initially formed on and in electrical communication with the free portion, and the free portion released from the substrate such that the inherent stress gradient in the stress-engineered member biases the free portion away from the substrate carrying with it the nanowire.

- 2. The spring contact of claim 1 wherein said stress-engineered member is formed to have a sidewall extending substantially perpendicular to said first plane, and said nanowire is formed on said sidewall.

- 3. The spring contact of claim 2, wherein said stress-engineered member comprises a stress engineered layer over a single-crystal silicon layer such that said sidewall presents the <111> plane of said single crystal silicon in the region in which said nanowire is formed on said sidewall.

- **4.** The spring contact of claim **1**, wherein said nanowire has a tip which, following release of the free portion of said stress-engineered member, extends above said substrate by a distance greater than the greatest distance said free portion extends above said substrate.

- 5. The spring contact of claim 1, wherein each of the stress-engineered member and the nanowire have a primary long axis, and further wherein each said primary long axis is generally parallel to the other.

- 6. The spring contact of claim 1, further comprising a clamping structure formed over and around at least the point of connection between the stress-engineered member and the nanowire.

- 7. The spring contact of claim 6, wherein said nanowire originally extends out of and not parallel with said first plane, and further wherein said nanowire is bent and clamped by said clamping structure into said first plane prior to release of said free portion.

- **8**. The spring contact of claim **1**, wherein at least a tip portion of said nanowire has a coating applied thereto.

- **9**. The spring contact of claim **1**, wherein at least a tip portion of said nanowire is doped.

- 10. The spring contact of claim 1, further comprising a plurality of nanodots applied as a coating over said microspring body, and wherein said nanodots form catalyst sites from which said nanowire forms.

- 11. The spring contact of claim 10, wherein said nanowire originally extends out of and not parallel with said first plane, and further wherein said nanowire is bent and clamped by a clamping structure into said first plane prior to release of said free portion.

\* \* \* \* \*