#### RÉPUBLIQUE FRANÇAISE

## INSTITUT NATIONAL DE LA PROPRIÉTÉ MOUSTRIELLE

(A n'utiliser que pour les commandes de reproduction).

2 520 544

**PARIS**

A1

# DEMANDE DE BREVET D'INVENTION

<sub>10</sub> N° 83 01157

- Procédé pour composer les adresses d'une mémoire.

- (51) Classification internationale (Int. Cl. 3). G 11 C 8/00; G 06 F 7/38; H 04 N 9/535.

- (33) (32) (31) Priorité revendiquée : JP, 27 janvier 1982, nº 57-11180.

- Date de la mise à la disposition du public de la demande............ B.O.P.I. « Listes » n° 30 du 29-7-1983.

- Déposant : DAINIPPON SCREEN SEIZO KABUSHIKI KAISHA, société de droit japonais. JP.

- (72) Invention de : Mitsuhiko Yomada, Tsukasa Nishida et Toshifumi Inoue.

- 73 Titulaire : Idem 71

- (74) Mandataire : Cabinet Pierre Loyer,18, rue de Mogador, 75009 Paris.

### PROCEDE POUR COMPOSER LES ADRESSES D'UNE MEMOIRE

La présente invention a trait à un procédé pour composer les adresses d'une mémoire dans laquelle plusieurs données correspondant à plusieurs adresses sont accessibles simultanément.

Habituellement, lorsqu'une donnée est introduite ou extraite sur une adresse d'une mémoire, il n'est pas possible d'accéder aux autres adresses pour une opération d'écriture ou de lecture. S'il devient possible d'accéder simultanément à plusieurs adresses, on peut en attendre de nombreux avantages, tels qu'un accroissement de la vitesse de traitement résultant de la réduction du temps d'accès, et ainsi de suite.

On a déjà proposé une telle méthode d'accès simultané à plusieurs adresses.

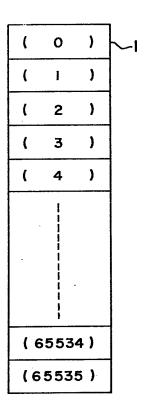

Dans ce cas, lorsque des adresses (x) signifiant 0, 1, 2, 3, ..., sont à une dimension, une mémoire 1 ayant des adresses composées de manière continue, comme représenté Fig. 1, est divisée en plusieurs blocs, et les adresses ne sont plus mémorisées séquentiellement dans les divers blocs (ici, au nombre de deux) numérotés 2 et 3 dans la Fig. 2a, mais sont mémorisées selon une opération entrelacée dans les blocs 4 et 5 par un procédé dit d'entrelacement de mémoire, comme le représente la Fig. 2b. Dans cette forme de mise en oeuvre du procédé d'entrelacement de mémoire, les adresses adjacentes telles que (2) et (3), ou (15) et (16) dans un espace logique d'adresse d'une mémoire sont accessibles simultanément.

Toutefois, dans une mémoire classique telle qu'une mémoire-table ayant des adresses à deux dimensions (x,y), où x signifie 0, 1, 2, 3, ... et y signifie 0,

La présente invention a notamment pour but de définir un procédé pour composer les adresses d'une mémoire ayant des adresses à n dimensions dans un espace logique d'adresses constitué de plusieurs sections unitaires ayant chacune des intersections avec les adresses à n dimensions, ce procédé étant exempt des inconvénients évoqués ci-dessus, et capable de réaliser un traitement rapide.

35 Le procédé selon l'invention est caractérisé par le fait de diviser une mémoire, ayant des adresses à n dimensions dans un espace logique d'adresses constitué de plusieurs sections unitaires ayant chacune des intersections avec

les adresses à n dimensions, en un nombre 2<sup>n</sup> de blocs de mémoire ayant chacun des lignes indépendantes de données et d'adresses dans lesquelles l'adresse de chaque intersection de la section unitaire correspond à une adresse de chaque bloc de mémoire, de manière à accéder simultanément aux adresses des intersections de la section unitaire.

Une forme de mise en œuvre du procédé selon l'invention est caractérisée en ce que les blocs de mémoire sont repérés consécutivement par des numéros tels que 0, 1, 2, 3 ... et  $2^n-1$ , et en ce que chacune des adresses à n dimensions telles que  $A^1$ ,  $A^2$ , ...  $A^{n-1}$  et  $A^n$  correspond à un bloc de mémoire dont le numéro d'ordre est égal à un reste obtenu en divisant par  $2^n$  le terme  $\sum_{k=1}^{n} 2^{k-1} A_k$

Une autre forme de mise en œuvre du procédé selon l'invention est caractérisée en œ que l'adresse de chaque bloc de mémoire est déterminée en divisant par 2 les adresses de la mémoire et en omettant leurs fractions.

Une autre forme de mise en oeuvre du procédé selon l'invention s'applique à la réalisation d'une table d'index multidimensionnelle utilisable pour la conversion de signaux d'analyse d'une image en couleurs.

Selon l'invention, cette forme de mise en oeuvre est caractérisée par le fait de stocker dans une mémoire-table des ensembles de signaux secondaires des couleurs R, G et B pour le rouge, le vert et le bleu, ces signaux correspondant 20 à des ensembles de signaux primaires des couleurs C, M, Y et K pour des encres de couleurs cyan, magenta, jaune et noir, les signaux secondaires des couleurs R, G et B étant lus dans la mémoire-table par adressage sur une adresse (C, M, Y, K), cette mémoire-table étant divisée en 2 blocs de mémoire ayant chacun des lignes indépendantes de données et d'adresses repérées consécutivement par des numéros d'ondre O, 1, 2, 3 ... et 15, tandis que chaque adresse (C, M, Y, K) correspond au bloc de mémoire dont le numéro d'ordre est déterminé par une division (C+2M+4Y+8K)/24.

Des formes préférées de mise en oeuvre de la présente invention seront décrites ci-après de manière plus détaillée, en se référant aux dessins annexés, 30 dans lesquels :

la Fig. 1 représente des adresses d'une mémoire, composées d'une manière classique;

- la Fig. 2 représente des adresses stockées dans deux blocs composant une mémoire d'un type classique, la Fig. 2(b) représentant des adresses stockées selon une méthode classique d'entrelacement de mémoire;

- la Fig. 3 représente quatre blocs de mémoire dans lesquels des adresses à deux

dimensions sont composées conformément à la présente invention; la Fig. 4 représente une mémoire d'index qui exprime les numéros des blocs de

mémoire et des adresses à deux dimensions composées selon l'invention;

la Fig. 5 représente une mémoire d'index qui exprime les numéros des blocs de mémoire et des adresses tridimensionnelles composées selon l'invention;

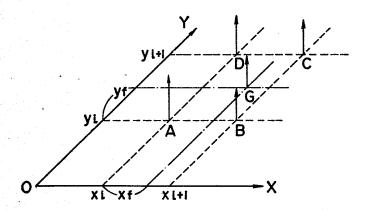

la Fig. 6 est un schéma expliquant une interpolation selon l'invention, et

-5

30

la Fig. 7 est un schéma de principe d'un circuit arithmétique pour exécuter l'interpolation selon l'invention.

En se référant aux Fig. 3-7, on voit un espace logique d'adressage d'une mémoire ayant des adresses à n dimensions. Cet espace est composé de plusieurs sections unitaires qui ont chacune des intersections avec les adresses à n dimensions. Dans un système à deux dimensions, les adresses des intersections d'une section unitaire ayant une forme quadratique sont exprimées sous la forme d'un ensemble de (1,1), (2,1), (1,2) et (2,2), et ainsi de suite, et dans un système à trois dimensions, les adresses des intersections d'une section unitaire ayant une forme cubique sont exprimées sous la forme d'un ensemble de (1,1,1), (2,1,1), (1,2,1), (1,1,2), (2,2,1), (2,1,2), (1,2,2) et (2,2,2), et ainsi de suite.

Tout d'abord, pour faciliter la compréhension de l'invention, celle-ci sera expliquée en termes d'adresses à deux dimensions (x,y), où x signifie 0, 1, 2, 3, ..., et y signifie 0, 1, 2, 3, ....

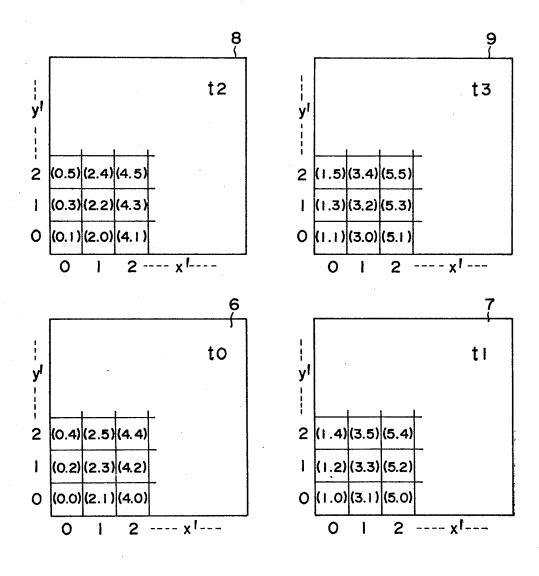

Dans cette forme de mise en oeuvre, telle qu'elle est représentée à la Fig.3, la mémoire est divisée en 2<sup>2</sup> = 4 blocs 6, 7, 8 et 9, ci-après référencés tO, tl, t2 et t3, respectivement, chaque bloc ayant des lignes d'adresses et des lignes de données indépendantes, et chaque donnée d'adresse des quatre intersections de la section unitaire est stockée dans chaque bloc tO, tl, t2 ou t3.

C'est à dire que lorsque y est égal à zéro, les données d'adresse (x,y) sont stockées dans les blocs de mémoire, par exemple :

(0,0) dans le bloc t0, (1,0) dans le bloc tl

(2,0) dans le bloc t2, (3,0) dans le bloc t3

(4,0) dans le bloc tO, (5,0) dans le bloc tl et ainsi de suite. En général, la donnée d'adresse (x,y) est stockée dans un bloc de mémoire  $tp_2$  où  $p_2$  signifie un reste qui est obtenu par une division  $(x+2y)/2^2$ .

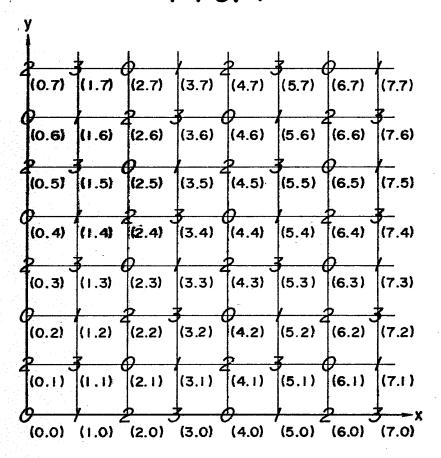

Cette relation est représentée visuellement dans la Fig. 4 qui montre les numéros des blocs de mémoire et les adresses à deux dimensions. C'est à dire 35 que les intersections des deux lignes qui s'étendent dans les direction x et y signifient les adresses bidémensionnelles (0,0), (0,1), ..., et que les numéros "O", "1", "2" et "3" apparaissant sur les intersections signifient les numéros

d'ordre affectés aux blocs de mémoire, c'est à dire que "0", "1", "2" et "3" signifient respectivement les blocs de mémoire t0, t1, t2 et t3.

Par suite, le numéro d'ordre  $p_2$  du bloc-mémoire  $tp_2$  dans lequel il y a lieu de stocker une adresse (x,y) s'obtient au moyen de la formule (I) ci-après, dans 5 laquelle MODE, () signifie un reste obtenu en divisant par  $2^2$  un nombre de ().

$$p_2 = MODE_2(x+2y) \qquad (I)$$

En outre, ainsi que cela a été décrit ci-dessus, les adresses des intersections de la section unitaire sont stockées séparément dans les différents blocs de mémoire, et par conséquent les adresses stockées dans chacun des blocs sont dispersées. Toutefois, pour répartir convenablement les adresses dans les différents blocs, la relation entre l'adresse (x,y) de la mémoire et l'adresse (x',y') du bloc est déterminée par la formule (II) ci-après, dans laquelle les nombres  $\frac{x}{2}$  et  $\frac{y}{2}$  dans () sont des nombres entiers obtenus en omettant leurs fractions.

15

$$x' = (\frac{x}{2})$$

$$y' = (\frac{y}{2})$$

(II)

Autrement dit, les adresses des intersections de chaque section unitaire sont réparties dans les différents blocs de mémoire ayant des lignes d'adresses 20 indépendantes et des lignes de données indépendantes.

L'invention va maintenant être exposée en se référant à un système tridimensionnel dans lequel une section unitaire de forme cubique possède huit intersections ayant des adresses tridemensionnelles (x,y,z) dans lesquelles x signifie  $0, 1, 2, 3, \ldots$  y signifie  $0, 1, 2, 3, \ldots$  et z signifie  $0, 1, 2, 3, \ldots$

Dans cette forme de mise en oeuvre, la mémoire est divisée en 2<sup>3</sup>= 8 blocs t0, t1, t2, t3, t4, t5, t6 et t7, ayant chacun des lignes d'adresses et des lignes de données indépendantes, et les adresses des intersections de chaque section unitaire sont composées de manière à être stockées dans les différents blocs de mémoire.

Par exemple, lorsque y est égal à zéro et que z est égal à zéro, les données d'adresses (x,y,z) sont stockées dans les blocs de mémoire, de la manière suivante :

(8,0,0) dans le bloc to et ainsi de suite.

D'une manière générale, une donnée d'adresse (x,y,z) est stockée dans un bloc de mémoire tp<sub>3</sub>, où un numéro d'ordre p<sub>3</sub> signifie un reste obtenu par une division (x+2y+4z)/2<sup>3</sup>. Cette relation est représentée dans la Fig. 5 qui montre les numéros des blocs de mémoire et les adresses tridimensionnelles.

Ie numéro d'ordre  $p_3$  du bloc  $tp_3$  dans lequel il y a lieu de stocker l'adresse (x,y,z) est obtenu au moyen de la formule (III) ci-après dans laquelle MODE $_3$  ( ) signifie un reste obtenu en divisant par  $2^3$  un nombre contenu dans ( ).

$$P_3 = MODE_3(x+2y+4z) \qquad (III)$$

En outre, la relation entre l'adresse (x,y,z) de la mémoire et l'adresse (x',y',z') de chaque bloc de mémoire est déterminée au moyen de la formule (IV) ci-après, dans laquelle les nombres  $\frac{x}{2}$ ,  $\frac{y}{2}$  et  $\frac{z}{2}$  dans ( ) sont des nombres entiers obtenus en omettant leurs fractions.

15

$$x' = \left(\frac{x}{2}\right)$$

$$y' = \left(\frac{y}{2}\right)$$

$$z' = \left(\frac{z}{2}\right)$$

(IV)

Comme décrit ci-dessus, les adresses des intersections de chaque section unitaire sont réparties dans les divers blocs ayant chacun des lignes d'adresses et des lignes de données indépendantes.

L'invention sera maintenant expliquée en se référant à un système à n dimensions, dans lequel une section unitaire possède n intersections avec des adresses à n dimensions  $(A_1, A_2, A_3, \dots \text{ et } A_n)$   $(n = 1, 2, 3, \dots)$ .

Dans cette forme de mise en oeuvre, la mémoire est divisée en  $2^n$  blocs de mémoire t0, t1, t2, t3, .... et  $t(2^n-1)$ , ayant chacun des lignes d'adresses et des lignes de données indépendantes. D'une manière générale, une donnée d'adresse  $(A_1, A_2, A_3, \ldots, A_n)$  est stockée dans un bloc  $tp_n$ , où un numéro d'ordre  $p_n$  est obtenu au moyen de la formule (V) ci-après qui est établié à partir des formules (I) et (III) précitées, et dans laquelle  $MODE_n$  () signifie un reste obtenu en divisant par  $2^n$  un nombre contenu dans ().

30

$$p_{n} = MODE_{n} (A_{1} + 2A_{2} + 4A_{3} + 8A_{4} + \dots + 2^{n-1}A_{n})$$

$$= MODE_{n} (\sum_{k=1}^{n} 2^{k-1}A_{k}) \dots (V)$$

En outre, la relation entre l'adresse  $(A_1, A_2, A_3, A_4, \ldots, A_n)$  de la mémoire et l'adresse  $(A_1', A_2', A_3', A_4', \ldots, A_n')$  de chaque bloc est déterminée au moyen de la formule (VI) ci-après de la même manière que pour les formules (I) et (III) des formes de mise en œuvre décrites précédemment.

$$\mathbf{A}_{\underline{1}}^{\dagger} = \left(\frac{\mathbf{A}_{\underline{1}}}{2}\right)$$

$$\mathbf{A}_{\underline{2}}^{\dagger} = \left(\frac{\mathbf{A}_{\underline{2}}}{2}\right)$$

$$\vdots$$

$$\vdots$$

$$\mathbf{A}_{\underline{n}}^{\dagger} = \left(\frac{\mathbf{A}_{\underline{n}}}{2}\right)$$

$$\mathbf{A}_{\underline{n}}^{\dagger} = \left(\frac{\mathbf{A}_{\underline{n}}}{2}\right)$$

Par conséquent, selon la présente invention, les adresses à n dimensions des intersections de chaque section unitaire sont réparties dans les différents blocs de mémoire ayant chacun des lignes d'adresses et des lignes de données indépendantes dans le système à n dimensions.

On comprendra aisément d'après la description ci-dessus que les adresses des intersections de chaque section unitaire sont accessibles simultanément, à la différence des procédés classiques avec lesquels on ne peut accéder aux adresses que séquentiellement, même quand ces adresses sont multi-dimensionnelles et quand 11 existe un grand nombre d'adresses d'intersections de chaque section unitaire. Par conséquent, le temps d'accès pourra être largement diminué grâce au procédé selon la présente invention.

Dans les formes de mise en oeuvre de l'invention qui viennent d'être décrites, l'accès simultané vers plusieurs blocs de mémoire ne peut pas toujours être exécuté sur les mêmes adresses, en commun, et l'accès aux blocs de mémoire devrait se faire sur leurs adresses respectives.

Un exemple de la présente invention sera décrit ci-après, à titre non limitatif.

Iorsque des signaux primaires sont convertis, très fréquemment, en signaux secondaires par un calcul approprié, il faut beaucoup de temps si le calcul est exécuté chaque fois sur un seul signal. Il est donc préférable d'obtenir les signaux secondaires à l'avance, en traitant les signaux primaires par un calcul de simulation, puis de les stocker dans une mémoire d'index sous la forme de données pouvant être lues à n'importe quel moment dans cette mémoire d'index en utilisant les signaux primaires comme signaux d'adressage, ce qui permet de réaliser la conversion des signaux à une grande vitesse.

lorsque des signaux primaires (x,y) à deux dimensions sont convertis en signaux secondaires F(x,y) à deux dimensions, et que ces derniers sont ensuite stockés dans une mémoire d'index comme représenté Fig. 6, les signaux secondaires  $F(x_i^{+}x_f^{-}, y_i^{+}y_f^{-})$ , où  $x_i^{-}$  et  $y_i^{-}$  signifient des parties entières et  $x_f^{-}$  et  $y_f^{-}$  des parties décimales correspondant aux signaux primaires  $(x_i^{+}x_f^{-}, y_i^{+}y_f^{-})$  en un point G, sont obtenus à partir des valeurs  $F(x_i^{-}, y_i^{-})$ ,  $F(x_i^{+}x_i^{-}, y_i^{-})$ ,  $F(x_i^{-}x_i^{-}, y_i^{-})$  et  $F(x_i^{-}x_i^{-}, y_i^{-}x_i^{-})$ , ces valeurs étant désignées ci-après comme données d'interpolation des signaux secondaires des intersections d'une surface d'interpolation ABCD, selon la formule (VII) ci-après pour une méthode d'interpolation linéaire :

10

$$F(x_{i}^{+}x_{f}, y_{i}^{+}y_{f}) = F(x_{i}^{-}, y_{i}^{-}) (1-x_{f}^{-}) (1-y_{f}^{-}) + F(x_{i}^{+}1, y_{f}^{-})x_{f}^{-} (1-y_{f}^{-}) + F(x_{i}^{-}, y_{i}^{+}1) (1-x_{f}^{-})y_{f}^{-} + F(x_{i}^{+}1, y_{i}^{+}1)x_{f}^{-}y_{f}^{-} \dots (VII)$$

Pour exécuter une telle interpolation selon une méthode classique, les données d'interpolation sont stockées dans une mémoire d'index ayant une composition d'adresses classique, et il faut alors chaque fois lire ces données une à une sur la table d'index.

Par contre, il devient possible, grâce au procédé selon l'invention, dans lequel un ensemble de données d'interpolation correspondant aux adresses des intersections de la section unitaire sont stockées dans les différents blocs de mémoire, de lire simultanément et d'une manière commode l'ensemble des données d'interpolation dans une mémoire dont les adresses sont composées de la manière décrite ci-dessus conformément à la présente invention.

Ceci signifie qu'il devient possible, selon l'invention, de lire tout un ensemble de données d'interpolation pendant le temps qu'il faudrait autrement pour lire une seule donnée d'interpolation selon une méthode classique. Par conséquent, dans un système à deux dimensions selon la présente invention, le temps de lecture pourra être réduit à un quart de celui qu'exige la méthode classique.

De plus, le procédé selon l'invention pourra être appliqué d'une manière beaucoup plus performante à une mémoire d'index multi-dimensionnelle pour utiliser cette mémoire lors de la conversion de signaux d'images en couleurs, de la manière décrite en détail ci-après.

Iorsque des signaux primaires numériques de séparation de couleurs C, M, Y et K appartenant au premier système de signaux, et correspondant aux couleurs

cyan, magenta, jaune et noir des encres d'impression, sont convertis en signaux secondaires numériques de séparation de couleurs R, G et B appartenant au deuxième système de signaux, pour les couleurs rouge, verte et bleue, en vue de la reproduction d'une image en couleurs, en même temps qu'on simule, au moyen de 1'écran cathodique de contrôle d'un dispositif à balayage pour l'analyse des couleurs, l'aspect final de l'impression d'après les signaux primaires de l'image, ceci pouvant se faire aussi au moyen d'un dispositif électronique de vérification des tirages en couleur, les valeurs  $U(C_1, M_1, Y_1, K_1)$  des signaux secondaires d'image R, G et B obtenues à l'avance en exécutant un calcul arithmétique de simulation et une conversion de signal des quatre bits supérieurs  $C_1, M_1, Y_1$  et  $K_1$  correspondant aux parties entières des signaux d'image primaires C, M, Y et K exprimés en 256 gradations (8 bits), sont stockées à l'avance dans une mémoire d'index dont les adresses sont composées conformément au procédé selon l'invention, comme décrit ci-dessus. Par conséquent, l'interpolation pourra ensuite être exécutée à grande vitesse de la manière décrite ci-après :

Selon cette forme de mise en oeuvre, étant donné que les adresses (C, M, Y, K) de la mémoire d'index sont à quatre dimensions, la mémoire est divisée en 2 = 16 blocs de mémoire tO, tl, t2, t3 .... et tl5. Un numéro d'ordre p<sub>4</sub> du bloc de mémoire tp<sub>4</sub> s'obtient au moyen de la formule (IIX) ci-après qui est elle-même obtenue par substitution de n=4, A<sub>1</sub>=C<sub>1</sub>, A<sub>2</sub>=M<sub>1</sub>, A<sub>3</sub>=Y<sub>1</sub> et A<sub>4</sub>=K<sub>1</sub> dans la formule (V) décrite ci-dessus, et la relation entre l'adresse (C<sub>1</sub>, M<sub>1</sub>, Y<sub>1</sub>, K<sub>1</sub>) de la mémoire et l'adresse (C<sub>1</sub>', M<sub>1</sub>', Y<sub>1</sub>', K<sub>1</sub>') du bloc de mémoire est déterminée par la formule suivante (IX) basée sur la formule (VI) :

$$p_{4} = MODE_{4}(C_{1} + 2M_{1} + 4Y_{1} + 8K_{1})$$

$$C_{1}' = (\frac{C_{1}}{2}), M_{1}' = (\frac{M_{1}}{2})$$

$$Y_{1}' = (\frac{Y_{1}}{2}), K_{1}' = (\frac{K_{1}}{2})$$

IX)

25

Donc, dans cette forme de mise en oeuvre où les adresses sont composées selon le procédé de l'invention, lorsque les signaux primaires d'image C = C<sub>i</sub>+C<sub>f</sub>, M = M<sub>i</sub>+M<sub>f</sub>, Y = Y<sub>i</sub>+Y<sub>f</sub> et K = K<sub>i</sub>+K<sub>f</sub>, où C<sub>f</sub>, M<sub>f</sub>, Y<sub>f</sub> et K<sub>f</sub>correspondent aux quatre bits inférieurs, 0 \le C<sub>f</sub>, M<sub>f</sub>, Y<sub>f</sub>, K<sub>f</sub> < 1, sont obtenus sous la forme de la division unitaire de un par l'interpolation, un ensemble de 16 valeurs

35 U(C<sub>i</sub>, M<sub>i</sub>, Y<sub>i</sub>, K<sub>i</sub>), U(C<sub>i</sub>+1, M<sub>i</sub>, Y<sub>i</sub>, K<sub>i</sub>), .... et U(C<sub>i</sub>+1, M<sub>i</sub>+1, Y<sub>i</sub>+1, K<sub>i</sub>+1) c'est à dire 16 données d'interpolation correspondant à 16 adresses (C<sub>i</sub>, M<sub>i</sub>, Y<sub>i</sub>, K<sub>i</sub>), (C<sub>i</sub>+1, M<sub>i</sub>, Y<sub>i</sub>, K<sub>i</sub>) .... et (C<sub>i</sub>+1, M<sub>i</sub>+1, Y<sub>i</sub>+1, K<sub>i</sub>+1) des

intersections de la section unitaire incluant un point devant être interpolé, pourra être lu simultanément dans les différents blocs de mémoire. Ainsi, le temps d'accès pourra être considérablement réduit grâce à l'invention.

En utilisant les données d'interpolation lues dans la mémoire, on peut obtenir les signaux d'image secondaires correspondants R, G et B par la méthode d'interpolation linéaire exprimée par la formule (%) ci-après ou par une autre méthode simple d'interpolation décrite dans la demande de brevet japonais N° 52-57198 (demande ouverte à l'inspection sous le N° 53-123201).

10

$$U(C_{i}+C_{f}, M_{i}+M_{f}, Y_{i}+Y_{f}, K_{i}+K_{f})$$

$$= U(C_{i}, M_{i}, Y_{i}, K_{i}) (1-C_{f}) (1-M_{f}) (1-Y_{f}) (1-K_{f})$$

$$+ U(C_{i}+1, M_{i}, Y_{i}, K_{i}) C_{f} (1-M_{f}) (1-Y_{f}) (1-K_{f})$$

$$+ U(C_{i}, M_{i}+1, Y_{i}, K_{i}) (1-C_{f}) M_{f} (1-Y_{f}) (1-K_{f})$$

$$+ U(C_{i}, M_{i}, Y_{i}+1, K_{i}) (1-C_{f}) (1-M_{f}) Y_{f} (1-K_{f})$$

$$+ U(C_{i}, M_{i}, Y_{i}, K_{i}+1) (1-C_{f}) (1-M_{f}) Y_{f} (1-K_{f})$$

$$+ U(C_{i}+1, M_{i}+1, Y_{i}, K_{i}) C_{f} M_{f} (1-Y_{f}) (1-K_{f})$$

$$+ U(C_{i}+1, M_{i}, Y_{i}+1, K_{i}) C_{f} (1-M_{f}) Y_{f} (1-K_{f})$$

$$+ U(C_{i}+1, M_{i}, Y_{i}+1, K_{i}+1) C_{f} (1-M_{f}) (1-Y_{f}) K_{f}$$

$$+ U(C_{i}, M_{i}+1, Y_{i}+1, K_{f}) (1-C_{f}) M_{f} Y_{f} (1-K_{f})$$

$$+ U(C_{i}, M_{i}+1, Y_{i}+1, K_{i}+1) (1-C_{f}) M_{f} (1-Y_{f}) K_{f}$$

$$+ U(C_{i}, M_{i}+1, Y_{i}+1, K_{i}+1) (1-C_{f}) M_{f} Y_{f} K_{f}$$

$$+ U(C_{i}, M_{i}+1, Y_{i}+1, K_{i}+1) (1-C_{f}) M_{f} Y_{f} K_{f}$$

$$+ U(C_{i}, M_{i}+1, Y_{i}+1, K_{i}+1) (1-C_{f}) M_{f} Y_{f} K_{f}$$

$$+ U(C_{i}+1, M_{i}+1, Y_{i}+1, K_{i}+1) C_{f} (1-M_{f}) Y_{f} K_{f}$$

$$+ U(C_{i}+1, M_{i}+1, Y_{i}+1, K_{i}+1) C_{f} M_{f} (1-Y_{f}) K_{f}$$

$$+ U(C_{i}+1, M_{i}+1, Y_{i}+1, K_{i}+1) C_{f} M_{f} (1-Y_{f}) K_{f}$$

$$+ U(C_{i}+1, M_{i}+1, Y_{i}+1, K_{i}+1) C_{f} M_{f} (1-Y_{f}) K_{f}$$

$$+ U(C_{i}+1, M_{i}+1, Y_{i}+1, K_{i}+1) C_{f} M_{f} (1-Y_{f}) K_{f}$$

$$+ U(C_{i}+1, M_{i}+1, Y_{i}+1, K_{i}+1) C_{f} M_{f} (1-Y_{f}) K_{f}$$

$$+ U(C_{i}+1, M_{i}+1, Y_{i}+1, K_{i}+1) C_{f} M_{f} (1-Y_{f}) K_{f}$$

35

• .../..

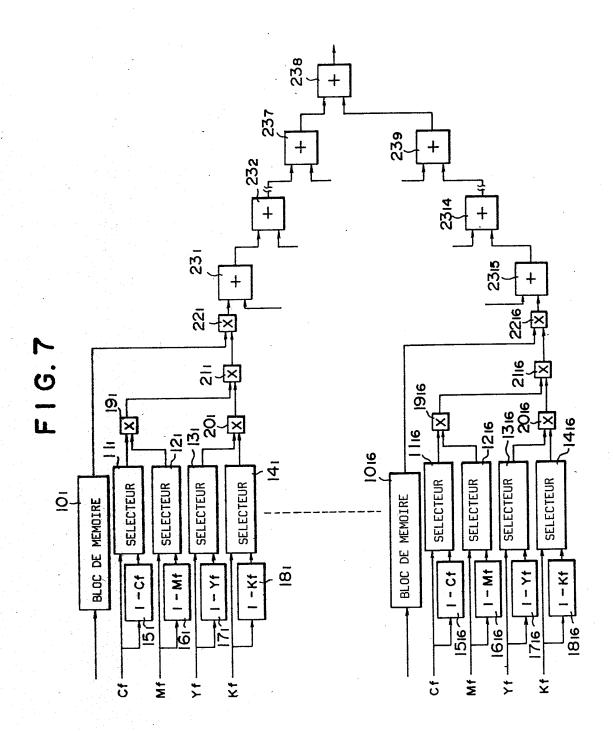

La Fig. 7 représente un circuit arithmétique pour éxécuter l'interpolation expaninée par la formule (X), ce circuit comprenant 16 blocs de mémoire  $10_1$  -  $10_{16}$  qui fournissent les données d'interpolation, des sélécteurs  $11_1$  -  $11_{16}$ ,  $12_1$  -  $12_{16}$ ,  $13_1$  -  $13_{16}$  et  $14_1$  -  $14_{16}$  qui choisissent  $C_f$  ou 1- $C_f$ ,  $M_f$  ou 1- $M_f$ ,  $Y_f$  ou 1- $Y_f$ , et  $X_f$  ou 1- $X_f$ , des soustracteurs  $15_1$  -  $15_{16}$ ,  $16_1$  -  $16_{16}$ ,  $17_1$  -  $17_{16}$  et  $18_1$  -  $18_{16}$  qui calculent respectivement 1- $C_f$ , 1- $M_f$ , 1- $Y_f$  et 1- $X_f$  des multiplicateurs  $19_1$  -  $19_{16}$ ,  $20_1$  -  $20_{16}$ ,  $21_1$  -  $21_{16}$  et  $22_1$  -  $22_{16}$  pour multiplier les valeurs de sortie des sélecteurs 11 - 14 et des blocs de mémoire 10, et enfin des additioneurs  $23_1$  -  $23_{15}$  qui totalisent les produits des multiplications, obtenant ainsi la valeur interpolée  $U(C_1$ - $C_f$ ,  $M_1$ - $M_f$ ,  $Y_1$ - $Y_f$ ,  $X_1$ - $X_f$ ,  $X_1$ -X

Dans cette forme de mise en œuvre, les données d'interpolation peuvent être lues simultanément dans les blocs de mémoire, et le calcul de l'interpolation peut être exécuté en même temps. Par suite, le temps de traitement de l'interpolation pourra être considérablement diminué par rapport à la 15 méthode classique.

Tandis que l'invention a été décrite et représentée avec suffisamment de détails pour qu'elle puisse être clairement comprise, il reste bien entendu que différentes modifications peuvent être apportées à la forme, aux détails et à la disposition des divers éléments sans sortir du cadre de la présente invention.

### REVENDICATIONS

Procédé pour composer les adresses d'une mémoire ayant des adresses à n dimensions dans un espace logique d'adresses constitué de plusieurs sections unitaires ayant chacune des intersections avec les adresses à n dimensions,

5

10

- caractérisé par le fait de diviser cette mémoire en un nombre 2<sup>n</sup> de blocs de mémoire ayant chacum des lignes indépendantes de données et d'adresses, dans lesquelles l'adresse de chaque intersection de la section unitaire correspond à une adresse de chaque bloc de mémoire de manière à accéder simultanément aux adresses des intersections de la section unitaire.

- 2. Procédé selon la revendication 1, caractérisé en ce que les blocs de mémoire sont repérés consécutivement par des numéros d'ordre tels que 0, 1, 2, 3, ... et  $2^n$ -1, et en ce que chacune des adresses à n dimensions telles que  $A^1$ ,  $A^2$ , ...,  $A^{n-1}$  et  $A^n$  correspond à un bloc de mémoire dont le numéro d'ordre est égal à un reste obtenu en divisant par  $2^n$  le terme  $\sum_{k=1}^n 2^{k-1}.A_k$

- 3. Procédé selon la revendication 1, caractérisé en ce que l'adresse de chaque bloc de mémoire est déterminée en divisant par deux les adresses de la mémoire et en omettant leurs fractions.

- 4. Procédé selon la revendication 1, caractérisé par le fait de stocker dans une mémoire-table des ensembles de signaux secondaires des couleurs R, G et B pour le rouge, le vert et le bleu, ces signaux correspondant à des ensembles de signaux primaires des couleurs C, M, Y et K pour des encres de couleurs cyan, magenta, jaune et noir, les signaux secondaires des couleurs R, G et B étant lus dans la table par adressage sur une adresse (C, M, Y, K), cette table étant divisée en 2<sup>4</sup> blocs de mémoire ayant chacun des lignes indépendantes de données et d'adresses repérées consécutivement par des numéros d'ordre 0, 1, 2, 3 ... et 15, tandis que chaque adresse (C, M, Y, K) correspond au bloc de mémoire dont le numéro d'ordre est déterminé par une division (C+2M+4Y+8K)/2<sup>4</sup>.

FIG.I

F I G. 2

F I G. 3

F1G.4

F J G. 6

(9.0.1) (9.0.0) (90.2)(9.0.3)5 (8.0.0) (8.0.1) (8.0.3) (8.0.2)£. <u>.</u> (9.2.3) 4  $\mathcal{O}$ (2.0.0) (7.0.3)(7.0.1) (7.0.2)(8.1.3)  $\frac{3}{(9.3.3)}$ Ø (8.2.3) (9.4.3) M 5 (0.0.9) (6.0.1) (6.0.2)(8.3.3) (6.0.3)(7.1.3).5.3) 5 <u>o</u> (7.2.3)(8.4.3)  $\boldsymbol{\varphi}$ V Ø (5.0.0) (2.0.1) (5.0.2)(5.0.3)(8.5.3) (7.3.3)(6.1.3)(7.4.3) *6* (6.2.3) 5 S (4.0.1) (4.0.0) (4.0.3)(4.0.2)(6.3.3) (5.1.3)(7.5.3)(6.4.3) 5 (5.2.3) 4 (3.0.1) (30.0) (3.0.3)(3.0.2)(4.1.3) (6.5.3)(5.3.3)(5.4.3) (4.2.3) B M (2.0.3)(2.0.2)(2.0.1) (5.0.0)  $\frac{6}{(4.3.3)}$ (3.1.3)3 (5.5.3) (3.2.3) (4.4.3) Q O 0 (1.0.1) (1.0.2)(0.0.1) (1.0.3) (2.1.3) (4.5.3) 33 B. (3.4.3) (2.2.3) 5 (0.0.0) (0.0.3) (0.0.1) (0.0.2)(1.1.3) (2.3.3) 5.3) Ю. (2.4.3) .2.3) (1.3.3) (2.5.3) 10,101 U/01 61.17 0,3 (0) 3 5.4.3) 4201 0231 (0.2.2) (0,2.1) .5.3) (0,5,0) 63.2) 03.1 (V3.3) 10.40 00.0 (O.A.) 0.4.2 (0A.3) 105.11 (0,50) (0.8.5)