## (12) 发明专利

(10) 授权公告号 CN 108120972 B

(45) 授权公告日 2023.01.31

(21) 申请号 201711210651.3

G01S 7/02 (2006.01)

(22) 申请日 2017.11.27

(56) 对比文件

(65) 同一申请的已公布的文献号

US 2007152873 A1, 2007.07.05

申请公布号 CN 108120972 A

JP S6254188 A, 1987.03.09

(43) 申请公布日 2018.06.05

US 2013057428 A1, 2013.03.07

(30) 优先权数据

EP 2818887 A1, 2014.12.31

16200945.0 2016.11.28 EP

US 2012280856 A1, 2012.11.08

(73) 专利权人 恩智浦有限公司

CN 102439476 A, 2012.05.02

地址 荷兰埃因霍温高科技园区60邮编:

5656 AG

CN 103576155 A, 2014.02.12

(72) 发明人 埃尔温·杨森

CN 101427475 A, 2009.05.06

西塞罗·西尔韦拉·沃谢

US 3936824 A, 1976.02.03

(74) 专利代理机构 中科专利商标代理有限责任

公司 11021

US 5596327 A, 1997.01.21

专利代理人 杨静

CN 103728616 A, 2014.04.16

(51) Int.Cl.

CN 103631746 A, 2014.03.12

G01S 13/02 (2006.01)

杨涛.MIMO雷达波形设计与实时处理系统研究.《中国博士学位论文全文数据库信息科技辑》.2014, (第10期), I136-145.

审查员 曹义军

权利要求书2页 说明书7页 附图7页

(54) 发明名称

字的位模式。

雷达

(57) 摘要

B

108120972 B

CN 该发明描述一种用于雷达系统的模拟前端和操作方法。发射器电路发射雷达信号，而接收器电路接收并处理经反射雷达信号且输出接收到的雷达信号。定时电路控制所述发射器电路和所述接收器电路的操作，且输出指示所述接收器电路是否将会接收所述经反射雷达信号的有效数据信号。转换器转换所述接收到的雷达信号且输出数字数据。串行化电路接收所述数字数据且将包含所述数字数据的串行数据流供应给数据处理装置。所述有效数据信号还传达到所述转换器以致使所述转换器在所述有效数据信号指示所述接收器电路将不会接收所述经反射雷达信号时输出对应于码字的位模式，且在所述有效数据信号指示所述接收器电路将会接收所述经反射雷达信号时输出对应于包含雷达数据的数据

1. 一种用于雷达系统(100)的模拟前端(200、300、400、450),其特征在于,包括:

发射器电路(124),其被配置成发射雷达信号;

接收器电路(128),其被配置成接收并处理经反射雷达信号且输出接收到的雷达信号;

定时电路(160),其被布置成控制所述发射器电路和所述接收器电路的操作且输出指示所述接收器电路是否将会接收所述经反射雷达信号的有效数据信号;

转换器(210、194),其被配置成转换所述接收到的雷达信号且输出数字数据;以及

串行化电路(212),其被布置成从所述转换器接收所述数字数据且将包含来自所述转换器的所述数字数据的串行数据流供应给数据处理装置(110),其中所述有效数据信号还被传达到所述转换器以致使所述转换器在所述有效数据信号指示所述接收器电路将不会接收所述经反射雷达信号时输出对应于码字的位模式,且在所述有效数据信号指示所述接收器电路将会接收所述经反射雷达信号时输出对应于包含雷达数据的数据字的位模式。

2. 根据权利要求1所述的模拟前端(200、300、400、450),其中对应于所述码字的所述位模式与对应于数据字的所述位模式具有相同的位频率和/或字频率。

3. 根据权利要求1或2所述的模拟前端(400),其中所述接收器电路是第一接收器电路(130)并且其中所述模拟前端进一步包括:

第二接收器电路(130'),其被配置成接收并处理所述经反射雷达信号且输出另一个接收到的雷达信号;以及

多路复用器(402),其被布置成将来自所述第一接收器电路和所述第二接收器电路的数字雷达数据供应到所述串行化电路(212),其中所述串行化电路被配置成供应包含来自所述第一接收器电路和所述第二接收器电路的雷达数据的单个串行数据流。

4. 根据权利要求3所述的模拟前端(400),进一步包括用于连接到所述数据处理装置(110)的仅单个导线对(142),并且其中所述串行化电路被配置成在所述单个导线对上输出所述单个串行数据流。

5. 根据权利要求1或2所述的模拟前端(200、300、400),其中所述转换器(210)是编码器,所述编码器被布置成对所述接收到的雷达信号进行编码且以经编码形式输出数字数据。

6. 根据权利要求5所述的模拟前端(200、300、400),其中所述编码器被配置成在所述有效数据信号指示所述接收器电路将不会接收所述经反射雷达信号时输出对应于码字的位模式。

7. 根据权利要求1或2所述的模拟前端(450),其中所述转换器(194)是模/数转换器并且其中所述模/数转换器被配置成输出对应于所述模/数转换器的预选值的位模式序列。

8. 根据权利要求1或2所述的模拟前端(300、400),且进一步包括:

模/数转换器,其被布置成使所述接收到的雷达信号数字化且输出数字雷达数据;以及

抽取电路(302),其被布置成减小由所述模/数转换器输出的所述数字雷达数据的取样频率。

9. 一种汽车雷达系统(100),其特征在于,包括根据权利要求1到8中任一项所述的模拟前端(200、300、400、450)以及连接到所述模拟前端以接收所述串行数据流的所述数据处理装置(110)。

10. 一种操作雷达系统的模拟前端的方法(500),其特征在于,包括:

当定时信号指示接收器电路将不会接收雷达信号时,将来自所述接收器电路的接收到的雷达信号转换成具有对应于码字的位模式的接收到的数字雷达信号(504);

当定时信号指示所述接收器电路将会接收雷达信号时,将来自所述接收器电路的接收到的雷达信号转换成具有对应于包含雷达数据的数据字的位模式的接收到的数字雷达信号(508);以及

将码字和数据字作为同一串行数字数据流的一部分输出到数字数据处理装置。

## 雷达

### 技术领域

[0001] 本说明书涉及雷达系统,且具体地说涉及数字雷达系统和操作方法。

### 背景技术

[0002] 雷达系统大体上是已知的且具有广泛范围的应用。一些雷达系统使用模拟和数字电子装置的混合装置。具体地说,一些雷达系统具有模拟前端(AFE),所述模拟前端大体上负责产生无线电信号并经由一根或多根天线发射所述无线电信号,以及处理由一根或多根天线接收的经反射信号以提取有用信息。雷达系统的剩余部分(大体上被称为后端)接着可处理经提取信息,基于所述信息采取任何另外的动作,且大体上控制雷达系统的整体操作另外还有雷达系统与任何其它系统之间的交互。

[0003] 数字雷达系统的后端大体上包括用于处理经由模拟前端接收的雷达信息的一个或多个数字微处理器,例如具有其自身的机载或独立数字信号处理器的微控制器。因此,大体上在模拟前端与微处理器(有时被称为基带处理器,因为所述微处理器大体上处理基带信号的数据)的数字域之间存在某一形式的接口。

[0004] 在接收经反射无线电的模拟前端与分析雷达反射的数字基带之间有一定间隔的雷达系统可能引起多个考量。这种间隔的后果是,敏感模拟雷达信号需要在电子装置之间(例如,在集成电路(IC)之间)传送,从而可能导致信号衰减。

[0005] 在使用其它系统分区和传送的雷达系统中,敏感模拟雷达信号的数字化版本可从模拟前端发送到数字基带。此方法可帮助减少信号衰减,但可能具有例如以下缺点:承载数位另外还有指示数位何时含有对应于实际雷达反射的数据所需的实体导线的数目。举例来说,一些模拟前端以脉冲模式(例如使用扫频序列)操作,且因此从接收器电路输出的数据中只有一小部分对应于由于信号反射而产生的有效雷达数据。

[0006] 确保此边带信息(“数据有效”)准确地供应到基带处理器可能是至关重要的,这是因为所述基带可能会成块地分析传入的数字数据,且需要边带信息,从而使得基带处理器了解何时将会接收需要处理的有效雷达数据且何时将不会接收所述有效雷达数据。此边带定时信息理想地应是非常准确的,且可使用高速且耗电的信号从前端提供到微处理器。

[0007] 另外,当数字化数据从前端发射到基带处理器时,各种同步信号也可能需要从前端供应到基带处理器,所述同步信号例如位时钟信号(用来识别数据字内的单独位)和帧时钟信号(用来识别数字数据流内的单独数据字)。因此,除用来发送一个或多个实际数字数据流的导线之外,其它实体导线也可用来将此同步信息供应到基带处理器。

[0008] 因此,能够在保持系统稳健性的同时以简单和/或低功率方式使模拟前端与后端处理器介接将是有益的。

### 发明内容

[0009] 根据本公开的第一方面,设置有一种用于雷达系统的模拟前端,包括:发射器电路,其被配置成发射雷达信号;接收器电路,其被配置成接收并处理经反射雷达信号且输出

接收到的雷达信号;定时电路,其被布置成控制发射器电路和接收器电路的操作且输出指示接收器电路是否将会接收经反射雷达信号的有效数据信号;转换器,其被配置成转换接收到的雷达信号且输出数字数据;以及串行化电路,其被布置成从转换器接收数字数据且将包含来自转换器的数字数据的串行数据流供应给数据处理装置,其中所述有效数据信号还传达到转换器以致使所述转换器在有效数据信号指示接收器电路将不会接收经反射雷达信号时输出对应于码字的位模式,而在有效数据信号指示接收器电路将会接收经反射雷达信号时输出对应于包含雷达数据的数据字的位模式。

[0010] 通过在单个数据流中同时提供码字和数据字,雷达数据的存在可传信到数据处理装置和/或同步信息可提供到数据处理装置。

[0011] 在一个或多个实施例中,对应于码字的位模式可以与对应于数据字的位模式具有相同的位频率和/或字频率。

[0012] 在一个或多个实施例中,接收器电路可以是第一接收器电路且模拟前端还可包括:第二接收器电路,其被配置成接收并处理经反射雷达信号且输出另一接收到的雷达信号;以及多路复用器,其被布置成将来自第一接收器电路和第二接收器电路的数字雷达数据供应到串行化电路,其中所述串行化电路可被配置成供应包含来自第一接收器电路和第二接收器电路的雷达数据的单个串行数据流。

[0013] 在一个或多个实施例中,模拟前端还可包括用于连接到数据处理装置的仅单个导线对,并且其中串行化电路可被配置成在单个导线对上输出单个串行数据流。

[0014] 在一个或多个实施例中,转换器可以是编码器,所述编码器被布置成对接收到的雷达信号进行编码且以经编码形式输出数字数据。

[0015] 在一个或多个实施例中,编码器可被配置成在有效数据信号指示接收器电路将不会接收经反射雷达信号时输出对应于码字的位模式。

[0016] 在一个或多个实施例中,经编码形式平均而言可具有恒定DC值。

[0017] 在一个或多个实施例中,编码器可以是8b/10b编码器和/或码字可以是k码。

[0018] 在一个或多个实施例中,转换器可以是模/数转换器,并且其中所述模/数转换器可被配置成输出对应于模/数转换器的预选值的位模式序列。

[0019] 在一个或多个实施例中,预选值可以是模/数转换器的最大输出值和最小输出值。

[0020] 在一个或多个实施例中,模拟前端还可包括:模/数转换器,其被布置成使接收到的雷达信号数字化且输出数字雷达数据;以及抽取电路,其被布置成降低由模/数转换器输出的数字雷达数据的取样频率。

[0021] 在一个或多个实施例中,模拟前端还可包括:延迟元件,其被布置成将延迟引入到有效数据信号中,所述延迟对应于由抽取电路导致的任何延迟。

[0022] 在一个或多个实施例中,抽取电路可以是可编程抽取链路和/或延迟元件可以是可编程延迟线。

[0023] 根据本公开的第二方面,设置有一种雷达系统,包括:根据第一方面的模拟前端及其任何优选特征,以及连接到模拟前端以接收串行数据流的数据处理装置。

[0024] 雷达系统可以是汽车雷达系统或工业感测系统,或者姿势识别系统或存在检测系统,例如入侵报警系统。

[0025] 根据本公开的第三方面,设置有一种用于雷达系统的模拟前端的操作方法,包括:

在定时信号指示接收器电路将不会接收雷达信号时将来自接收器电路的接收到的雷达信号转换成具有对应于码字的位模式的接收到的数字雷达信号；在定时信号指示接收器电路将会接收雷达信号时将来自接收器电路的接收到的雷达信号转换成具有对应于包含雷达数据的数据字的位模式的接收到的数字雷达信号；以及将码字和数据字作为同一串行数字数据流的一部分输出到数字数据处理装置。

[0026] 第一方面的特征还可以是用于第三方面的对应特征。

## 附图说明

- [0027] 现将仅借助于例子且参考附图详细描述本发明的实施例，在附图中：

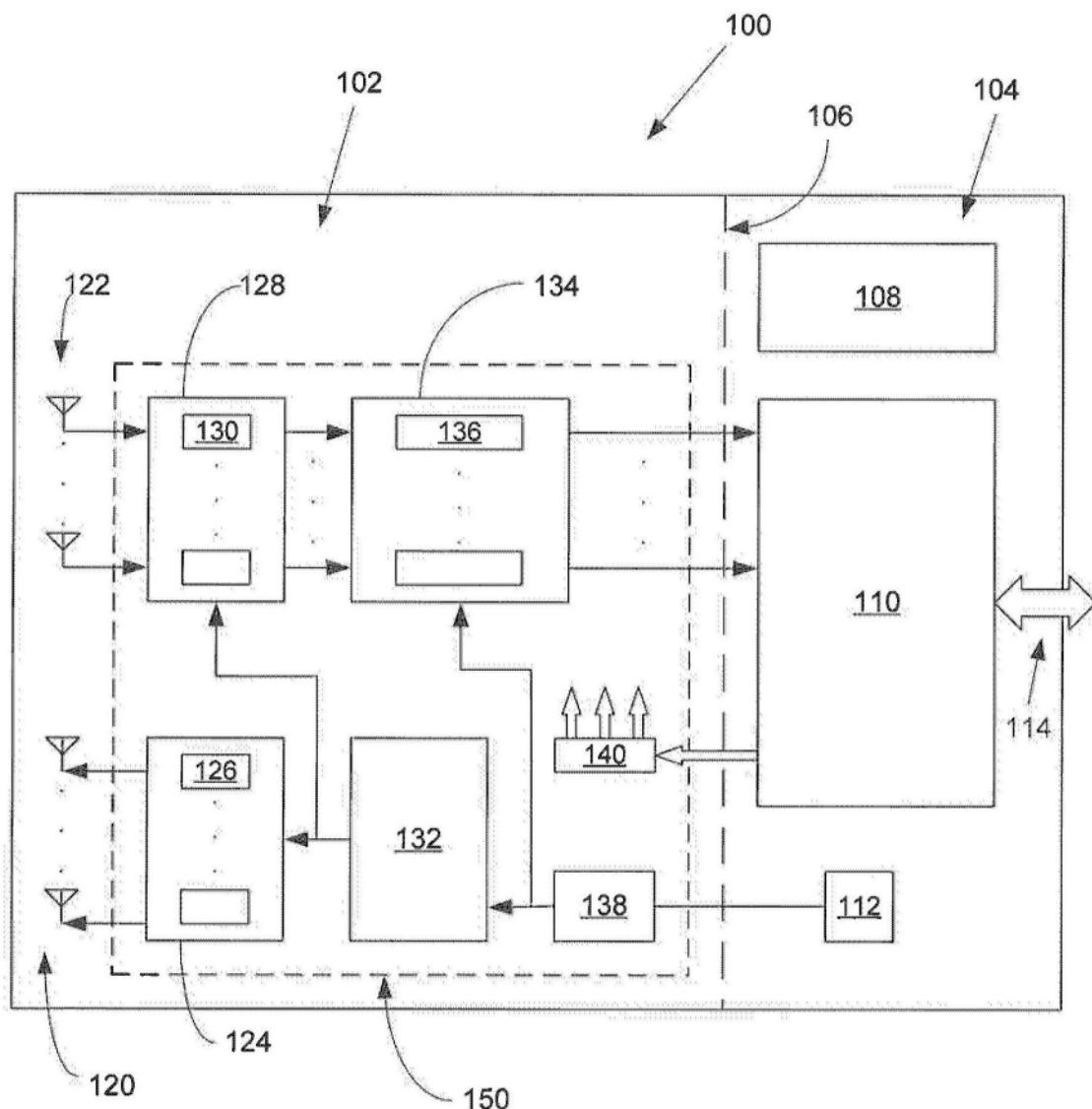

- [0028] 图1示出例子雷达系统的示意框图；

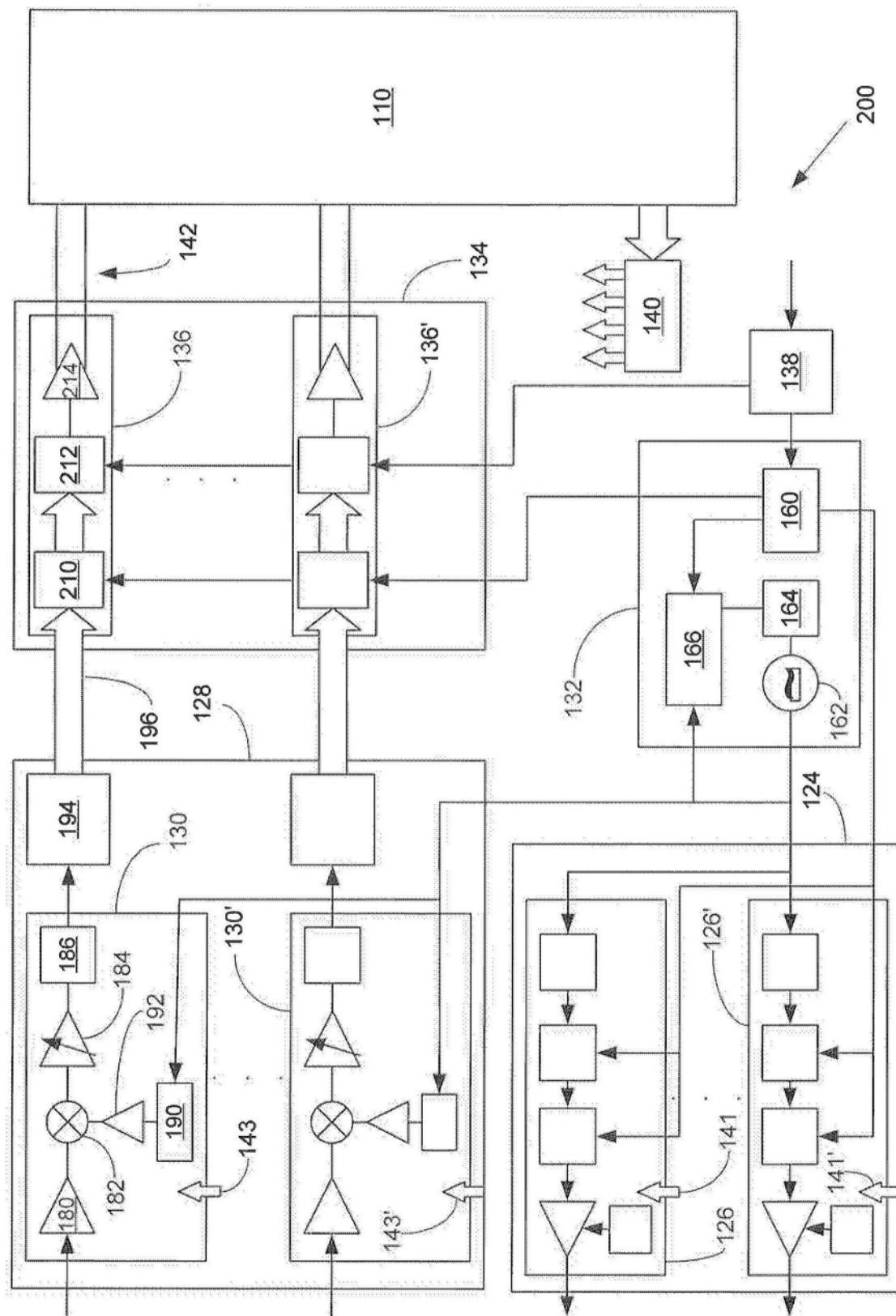

- [0029] 图2示出图1的雷达系统的模拟和数字部分的第一例子的示意框图；

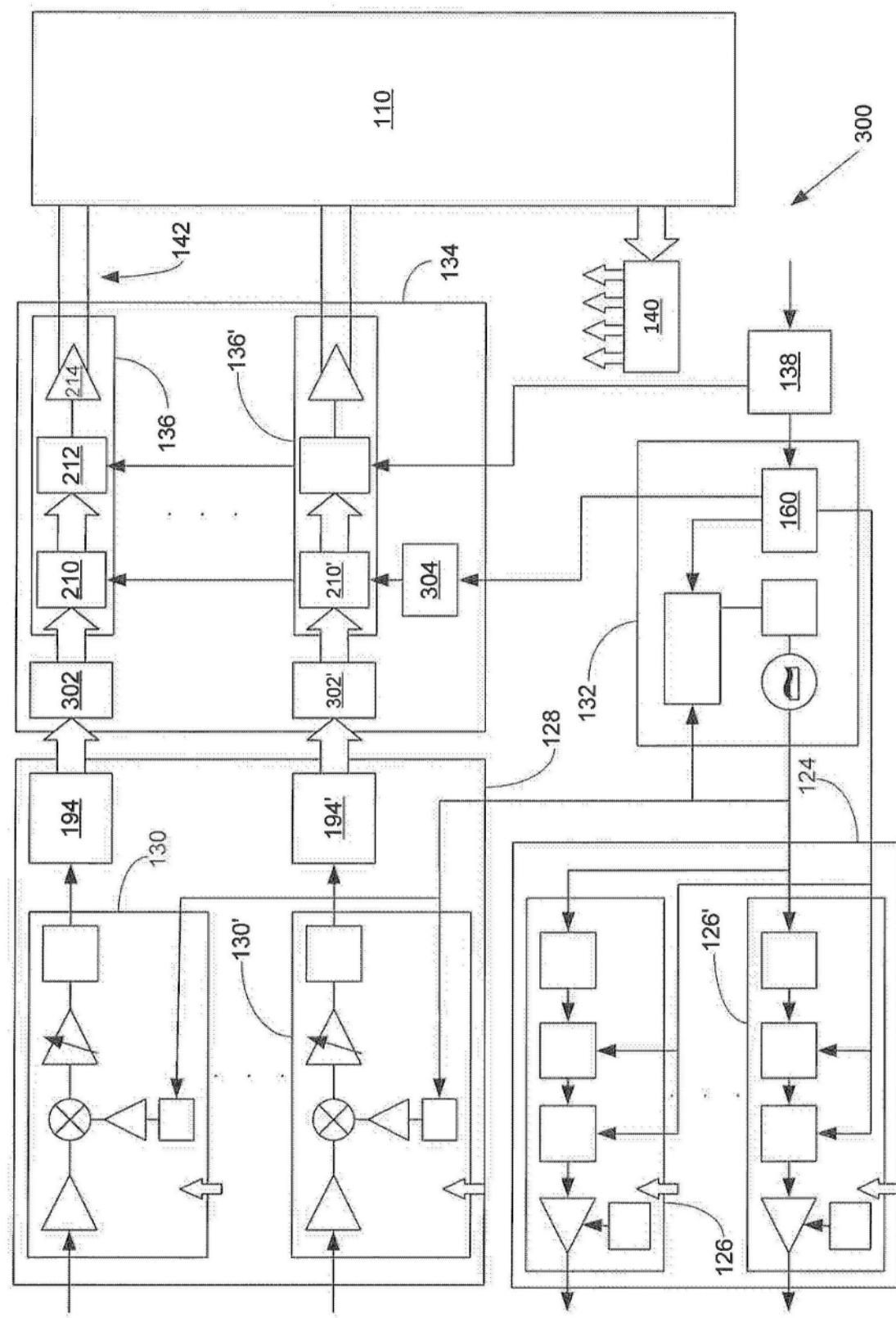

- [0030] 图3示出图1的雷达系统的模拟和数字部分的第二例子的示意框图；

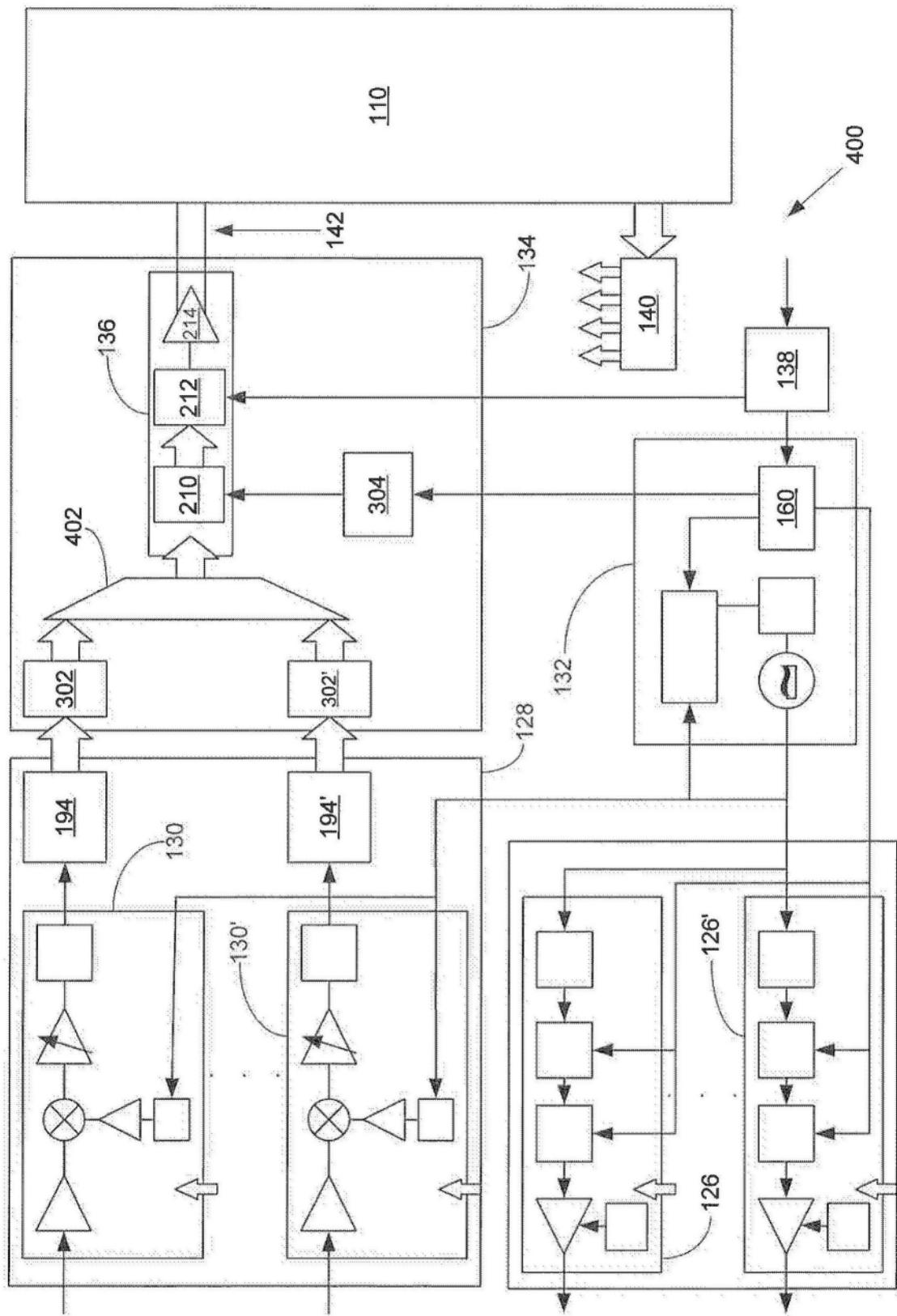

- [0031] 图4示出图1的雷达系统的模拟和数字部分的第三例子的示意框图；

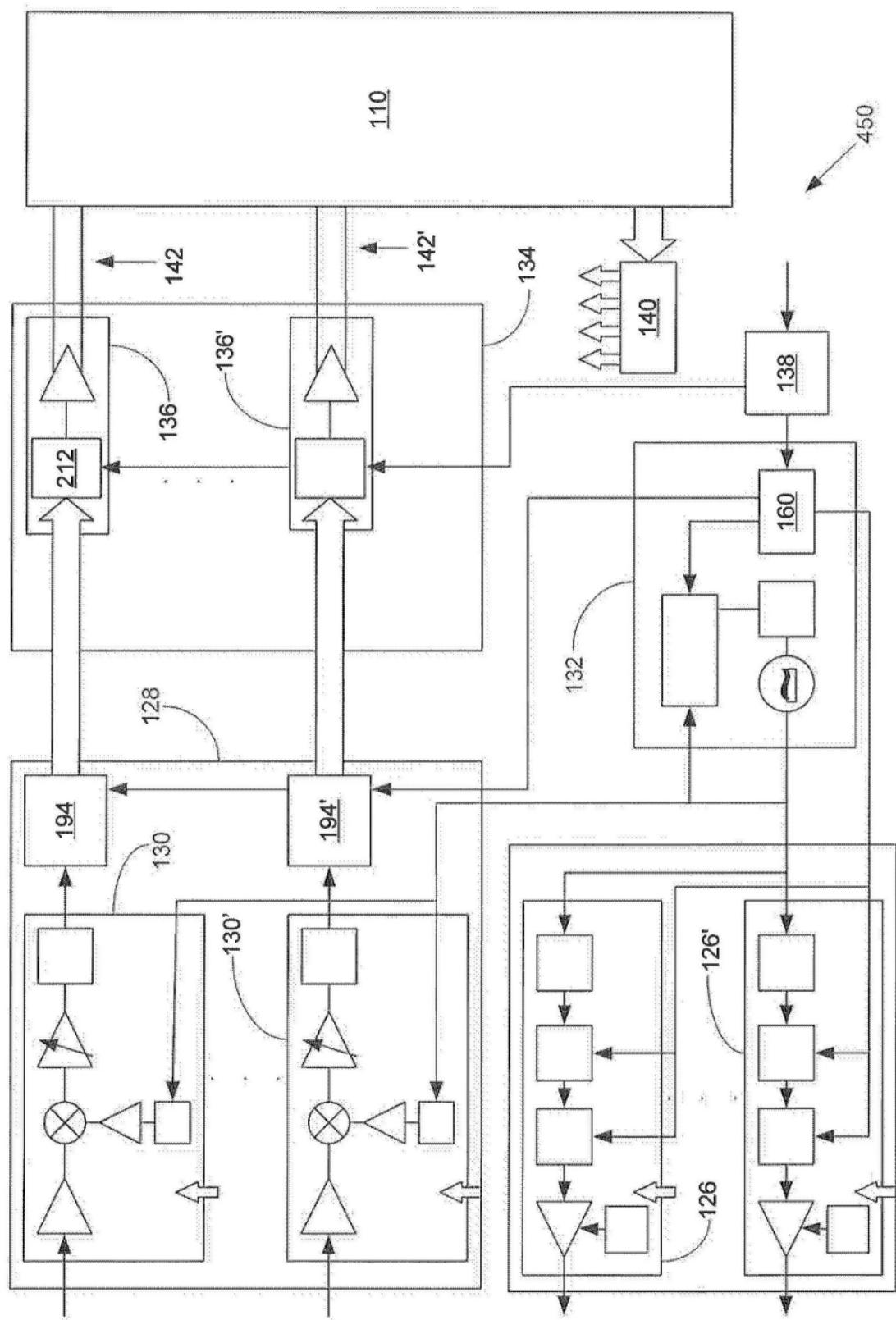

- [0032] 图5示出图1的雷达系统的模拟和数字部分的第四例子的示意框图；

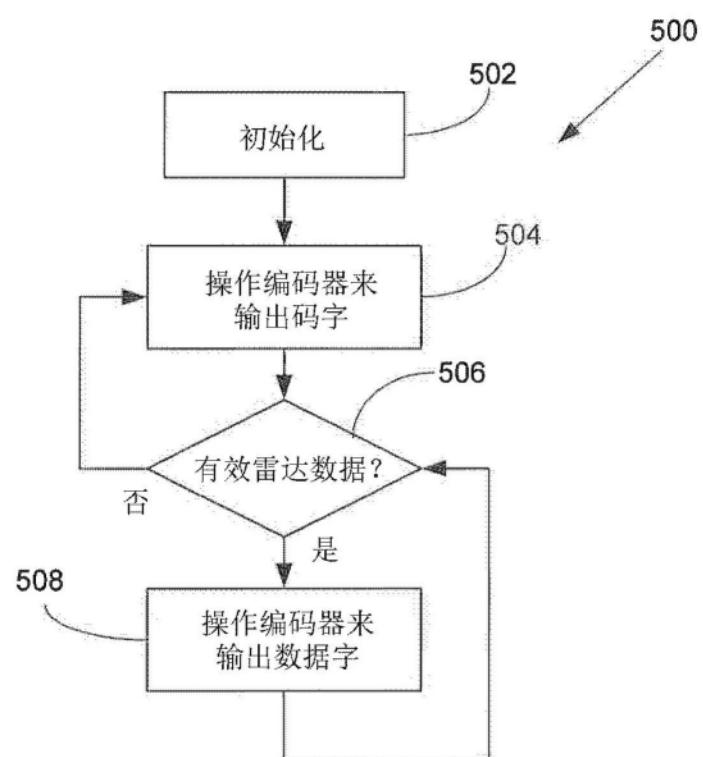

- [0033] 图6示出过程流程图，所述过程流程图说明模拟和数字部分的操作方法；并且

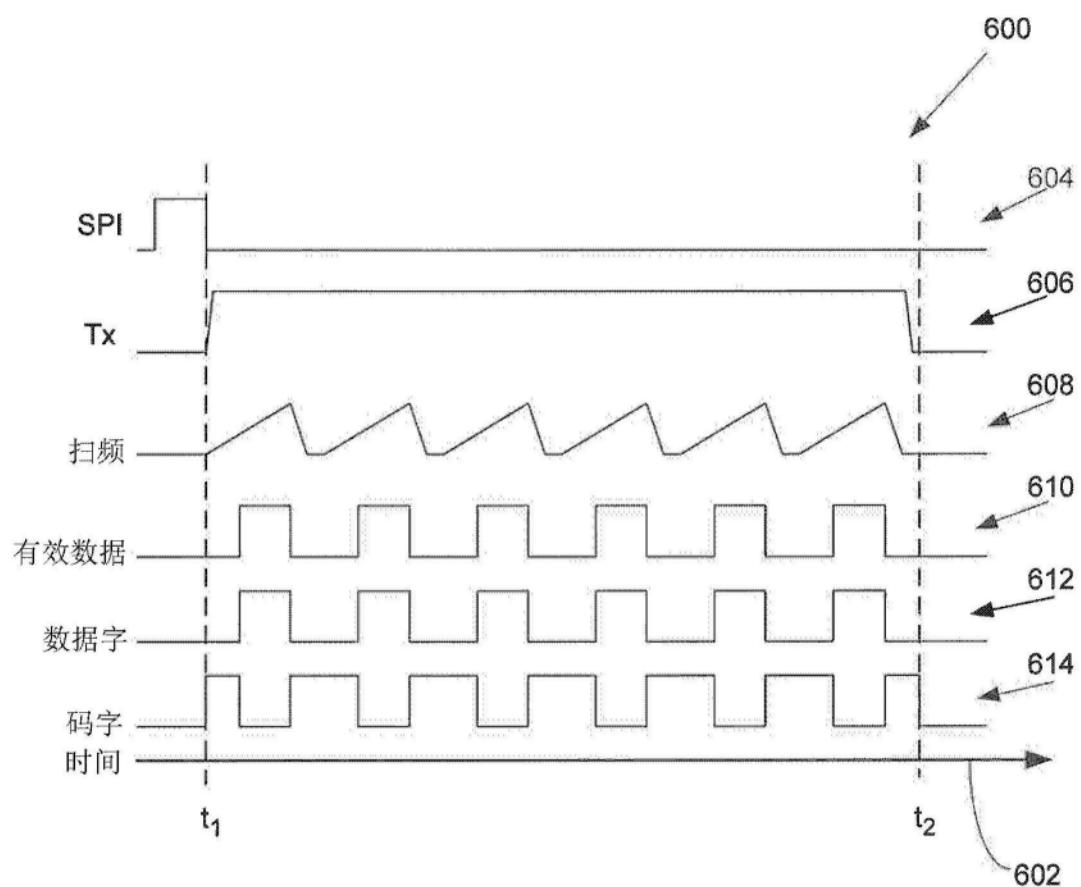

- [0034] 图7示出定时图，所述定时图说明操作期间各个信号的状态。

- [0035] 除非另外指示，否则不同图式中的类似项目共享相同参考标记。

## 具体实施方式

[0036] 参考图1，示出例子雷达系统100的示意框图。为了解释清楚起见，省略雷达系统100的各种常规部分。然而，所属领域的一般技术人员将会明白省略的常规部分。雷达系统100尤其适合于汽车应用，然而，所述雷达系统100还可用于其它应用，例如用于姿势识别的感测系统。雷达系统100大体上包括大体通过虚线106分界的前端102和后端104。后端104包括电源管理系统108、数据处理器110（其可以是微处理器、微控制器、数字信号处理器、片上系统或类似装置或者它们的任何组合）、晶体振荡器112以及总线或其它通信接口114，处理器110可经由所述总线或其它通信接口114与后端的其它部分（未示出）通信和/或与例如车辆的其它系统或子系统通信。举例来说，接口114可提供以太网、控制器区域网络（CAN）或FlexRay通信协议。

[0037] 前端102是大体上模拟前端且包括一根或多根雷达发射器天线120以及一根或多根雷达接收器天线122。前端102还包括发射器电路124，所述发射器电路124包括用于每根发射器天线的相应发射器路径电路（例如，126）。还设置有接收器电路128，包括用于每根相应接收器天线122的接收器路径电路130。还设置有波形生成器电路132，其将主本地振荡器（L0）信号供应到发射器和接收器电路中的每一个。还设置有串行器电路134，且其包括用于每个接收器电路的相应串行器电路136。还设置有主时钟生成电路138，且所述主时钟生成电路138从晶体振荡器112接收信号并将主时钟信号输出到波形生成器132另外还输出到串行器电路134。还设置有与数据处理器110通信的主串行外围接口（140），且微处理器110可经由所述主串行外围接口140与模拟前端的各个部分通信。应了解，在其它实施例中，可代替使用其它类型的控制总线。串行器电路134包括线路驱动器电路，数字化数据经由所述线路驱动器电路在一对线路（例如，142）上以低电压差分信令（LVDS）串行格式发射到数据处

理器110。应了解,在其它实施例中,可代替使用其它类型的串行数据发射。因此,这在模拟前端与作为数字基带的处理器110之间提供一般的模/数转换和接口。

[0038] 发射器电路124、接收器电路128、串行化电路134、波形生成器132和主时钟生成器138中的每一个可设置为集成电路。这些部件在下文更详细地描述。

[0039] 图2示出大体上对应于图1中的虚线150内的元件以及微控制器110的第一例子模拟前端200的示意框图。

[0040] 主时钟生成器138将主时钟信号供应到波形生成器132。波形生成器132包括定时引擎160,所述定时引擎160将各种定时控制信号提供到电路的各个部分。波形生成器132包括锁相回路,所述锁相回路包括电压可控制振荡器162、低通滤波器164和 $\Delta \Sigma$ 调制和任选分频器电路166,所述 $\Delta \Sigma$ 调制和任选分频器电路166被配置成产生可变频率本地振荡器信号。可变频率本地振荡器信号应用到发射器电路124和接收器电路128以使得能够发射和接收扫频雷达信号。

[0041] 发射路径电路126包括x3乘法块、可控制开关、二进制移相器、功率放大器和电平检测器。每条发射路径126、126'是类似的。每条发射路径126、126'附接到SPI总线且从定时引擎160接收可用频率本地振荡器信号另外还有控制信号以开始和停止扫频发射序列。

[0042] 每条接收器路径(例如,130)包括低噪声放大器180、混频器182、可变增益放大器184、带通滤波器186、x3乘法块190和连接到混频器182的第二输入端的另一个放大器192。每个接收器路径电路130以类似方式与SPI(例如,143)通信,另外还从波形生成器电路132接收可变频率本地振荡器信号作为输入。如本领域中大体上已知的,任何经反射雷达信号与本地振荡器信号混合且所得中频信号由电路产生且在接收器路径130上输出。

[0043] 输出中频信号输出到模/数转换器194,所述模/数转换器194可以例如是12位SAR(逐次近似寄存器)模/数转换器。ADC 194在并行数据信道196上以480Mb每秒的数据速率将12位并行数据字输出到串行器电路136。串行器136包括8b/10b编码器210,所述编码器并行于串行器212以每秒600Mb的速率供应并行格式的10位数据字。两个相邻12位数据字(总共对应于24位)作为三个8位字提供到8b/10b编码器210,所述8b/10b编码器210接着将三个10位字输出到串行器212。串行器212使10位编码的并行输入数据串行化且将单独位的序列作为数据信号输出到LVDS驱动器214。LVDS驱动器214接着使用差分信令在一对导线142上将串行数据位的序列(有效地为1位字)发射到微控制器110,如本领域中大体上已知的。每个串行器电路的每个8b/10b编码器从定时引擎160接收信号。定时引擎160输出指示接收器电路何时可预计接收有效雷达信号的信号且因此对应于雷达活动的窗口。此定时信号在本文中也被称为“有效数据”信号,这是因为在信号为高时其指示传入数据可被认为是有效数据,而在信号为低时其指示预计无有效数据。并行于每个串行器电路136的串行转换器212还从主时钟138接收主时钟信号以对并-串转换进行定时。

[0044] 如下文更详细地描述,当来自定时引擎160的窗口活动或有效数据信号为低时,那么8b/10b编码器210输出8b/10b控制码(也被称为k码),所述k码指示对应于编码或控制信号而不是有效数据信号的10位数据字。当来自定时引擎160的窗口活动或有效数据信号为高时,那么8位/10位编码器执行其普通编码过程且输出10位数据字而不是控制字。

[0045] 单个数据链路142可用来执行前端与处理器110之间的同步,另外还指示有效数据的起点。8b/10b控制字用来执行前端与基带处理器之间的同步,从而使得基带处理器了解

数字化信号的哪个位是首先发射的位。否则,不可能根据随机位序列确定数据字的起点。并且,8b/10b控制字可用来指示数据不受基带处理器关注。然而,当由处理器接收的数据不是8b/10b控制字时,那么处理器可识别出这是待处理的有用数据。因此,通过在控制字与数据字之间切换,由于控制字与真实数据字以同一速率发射,所有必要定时信息可供用于处理器,因此,能够以最高可能分辨率获得必要定时信息而没有任何额外开销。

[0046] 图3示出类似于图2中所示的系统200的第二雷达前端系统300的示意框图。然而,在图3中,可编程抽取链路302设置在ADC 194、194'与串行器电路136之间。并且,可编程延迟线304设置在定时引擎160与8b/10b编码器210、210'之间以便将时间延迟引入到供应到8b/10b编码器210、210'的有效数据信号中。可编程抽取链路(PDC)302、302'通过降低有效取样频率而有效地改变取样带宽。通过使用更高抽取因数减少在串行接口142上发射到微处理器的数据量,由此减小微处理器110中存储数据所需的存储器容量。

[0047] 然而,可编程抽取链路将增加数据流的等待时间,因为所述数据流通常包括数据的某一形式的有限脉冲响应操作(例如,过滤)。因此,当引入PDC元件302、302'时,从定时引擎160输出的定时信号将会不一致。因此,可编程延迟线(PDL)304在定时引擎与到8b/10b编码器210、210'的定时信号输入端之间引入。在没有延迟元件的情况下,定时引擎信号将导致过早地(即,在第一数据字将实际包含有效雷达数据之前)切换到“有效数据”模式。可编程延迟线304的延迟时长经编程以匹配由可编程抽取链路导致的延迟。因此,通过使来自定时引擎160的窗口活动信号延迟,8b/10b编码器在输入之后匹配于有效雷达数据到达的时间从输出控制码切换到数据码。

[0048] 参考图4,再次示出类似于图2和3中所示的前端200、300的第三例子前端400的示意框图。类似于前端300,串行器电路134包括用于每个接收器路径电路130、130'的可编程抽取链路302、302'。然而,仅设置有单个串行电路136。多路复用器402设置来组合PDC 302、302'的输出且将单个并行数据流提供到串行化电路136的8b/10b编码器210。再次,可编程延迟线304设置在定时引擎160与8b/10b编码器的输入端之间以将延迟引入到有效信号,所述延迟类似于由PDC元件302、302'导致的延迟。因此,在图4中所示的前端400中,单个导线对将单个数据流提供到微处理器110,所述单个数据流包括用于多个雷达接收器的所有雷达数据以及单个流中的所有需要的有效数据和定时同步信息。

[0049] 尽管以上三个例子系统描述作为有效数据机制的同步和开始而使用8b/10b编码控制字,但将了解可使用其它类型的保留位序列应用同一方法。举例来说,代替使用8b/10b k码字,其它控制符号可用来使前端与基带处理器同步。

[0050] 图5示出大体上类似于第一到第三例子的第四例子系统450。然而,在此系统中,省略了8b/10b编码器,且改为来自定时引擎160的“数据有效”控制信号供应到接收器链路中的ADC 194、194'中的每一个且对其进行控制。因此,如果省略8b/10b编码器,那么其它控制符号或控制字可替代地用来使前端与基带处理器同步另外还用来指示有效数据的起点。由普通数据字构成的专用模式从串行器电路136发射到微处理器110。数据字模式被选择成使得数据字的特定序列不会在雷达系统的正常操作期间发生。在大多数一般情况下,可能不会满足此条件。然而,在雷达应用的具体情况下可能会满足。

[0051] 定时引擎“窗口活动”信号供应到ADC 194、194',所述ADC 194、194'附接到接收器路径电路130、130'中的每一个。当窗口活动信号为低时(指示未接收到有效雷达数据),那

么每个ADC 194、194'替代地输出对应于其最大值的数据字,且接着输出对应于其最小值的数据字。因此,当此最大值和最小值数据字的模式由微处理器接收时,这些数据字可类似于如上文所描述的k码而识别。因此,当最大值和最小值数据字序列的固定模式由微处理器接收时,基带处理器110可假设不在发射雷达数据。这种极端输出值模式将不会见于真实雷达数据中。这将对应于ADC194、194'对每个样品进行剪辑,这在实践中是极其不太可能的且将导致信号中无信息。因此,使用此数据字组合和序列,有可能通知处理器何时有效数据在发射或不在发射以及在到处理器的相同导线142上使前端与基带处理器同步。

[0052] 参考图6,示出过程流程图500,所述过程流程图500更详细地说明操作方法。图7示出定时图600,所述定时图600示出随着时间602而变的系统中的各种信号。轨迹604表示在SPI总线上发送的控制信号。轨迹606表示发射器电路124的活动。轨迹608表示雷达扫频信号。轨迹610表示由定时引擎160输出的有效数据信号。轨迹612表示作为从串行器电路136到微处理器110的数据字的雷达信号的输出位模式。轨迹614表示对应于从串行器电路136、136'到微处理器110的码字或控制字的位模式的输出。

[0053] 如图6中所示,在502处初始化系统。信号由处理器110在SPI总线上发送,所述信号指示新的扫频序列将在时间T1时开始于SPI信号604的下降边缘。因此,发射电路124变为活动且在定时引擎160的控制下,波形生成器电路132将对应于扫频信号608的频率递增的本地振荡器信号输出到发射路径126、126',从而致使发射天线120输出扫频雷达信号。在时间t1时,恰好在扫频信号608开始增长之前,定时引擎160将有效数据信号610的值设定为低,从而指示预计在接收器电路128上无有效雷达信号。因此,首先,有效数据信号610为低,且因此8b/10b编码器210、210'在504处输出控制字序列且如轨迹614所示为高。

[0054] 处理进行到506,在506处确定是否还预计有效雷达数据或不再预计有效雷达数据。在有效数据信号610为低时,预计无有效雷达数据且因此8b/10b编码器继续在504处输出控制字数据序列。

[0055] 最终,可预计有效经反射雷达信号且因此定时引擎160将有效数据信号610设定为高。因此,在508处,8b/10b编码器停止输出控制字数据序列,而是改为输出对应于接收到的雷达数据的8b/10b经编码数据字,如数据字信号612为高及码字信号614为低所示。当有效数据信号随后变低时610(对应于由定时引擎160输出的窗口活动信号变低),不再预计有效雷达数据且因此处理进行到504,在504处8b/10b编码器停止输出经编码数据字,且改为开始在504处输出控制字,如数据字信号612变低及码字信号614变高所示。

[0056] 处理以此方式针对当前序列内的每个扫频信号而持续,直到当前扫频信号序列在时间t2时结束为止。微控制器110接着可通过在SPI上发布扫频序列信号的下一个起点而起始下一扫频序列。

[0057] 因此,上述方法避免了发送单独的“数据有效”边带信号的需要,从而导致比利用一个或多个额外同步信号的传统方案相比更加稳健、更加便宜且功率更低的方案。此外,数据的同步信号可与数据本身一起发送,而不是需要单独的位时钟和帧时钟信号。

[0058] 因此,通过将侧信道定时信息和雷达数据组合在单个流中,可在不需要额外导线或电力的情况下将准确的定时信息提供到微处理器。因此,此方法提高了定时准确度,另外与其它方法相比还减少了硬件和电力需求。

[0059] 此外,与其它方法相比,可使用连接在雷达前端与微处理器之间的更少的LVDS差

分线路。因此,可使用功率更低且更小的印刷电路板。

[0060] 无需发送单独的位时钟和帧时钟信号,这是因为所有时钟信息和帧信息自动构建到发送到微处理器的串行化流中。因此,不存在时间和对准的问题。

[0061] 在使用8b/10b数据编码的系统中,这使谱内容偏移远离由前端雷达系统使用的中频波段。因此,LVDS信号对中频流的干扰风险降低。

[0062] 因此,在控制字数据模式与实际数据字数据模式之间切换的方法允许微处理器区分有效和无效数据,另外还提供在控制字以与真实数据字相同的速率发射时需要的所有同步定时。

[0063] 上述方法与在实际数据之前发射信息标头的方法相比也是优选的。插入标头数据将增加系统的等待时间。此外,仍将需要发射用于串行数据流的同步信息。

[0064] 图4中所示的系统特别有利于处理器110可能定位于与雷达前端不同的物理位置中的应用。图4中所示的系统允许单个简易双绞线连接以将所有所需数据从前端传送到微处理器。

[0065] 在本说明书中,已依据选定细节集合呈现例子实施例。然而,本领域的普通技术人员将理解,可实践包括这些细节的不同选定集合的许多其它例子实施例。希望所附权利要求书涵盖所有可能的例子实施例。

[0066] 除非明确陈述具体次序,否则可按任何次序执行任何指令和/或流程图步骤。另外,本领域的技术人员将认识到,尽管已论述一个例子指令集/方法,但是本说明书中的材料可通过多种方式组合,从而还产生其它例子,并且应在此详细描述提供的上下文内来理解。

[0067] 虽然本公开容许各种修改和替代形式,但是已借助于例子在图式中示出且详细描述了其特殊性。然而,应理解,超出所描述的特定实施例的其它实施例也是可能的。也涵盖落在所附权利要求书的范围内的所有修改、等效物和替代实施例。

图1

图2

图3

图4

图5

图7