(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4305097号

(P4305097)

(45) 発行日 平成21年7月29日(2009.7.29)

(24) 登録日 平成21年5月15日(2009.5.15)

(51) Int.Cl.

H04N 5/335 (2006.01)

H01L 27/146 (2006.01)

F 1

H04N 5/335

H04N 5/335

H01L 27/14Z

R

A

請求項の数 8 (全 20 頁)

|           |                              |

|-----------|------------------------------|

| (21) 出願番号 | 特願2003-308389 (P2003-308389) |

| (22) 出願日  | 平成15年9月1日 (2003.9.1)         |

| (65) 公開番号 | 特開2005-79942 (P2005-79942A)  |

| (43) 公開日  | 平成17年3月24日 (2005.3.24)       |

| 審査請求日     | 平成18年5月22日 (2006.5.22)       |

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 000002185<br>ソニー株式会社<br>東京都港区港南1丁目7番1号               |

| (74) 代理人  | 100092152<br>弁理士 服部 毅麿                               |

| (72) 発明者  | 小関 賢<br>神奈川県横浜市保土ヶ谷区神戸町134番地<br>ソニー・エルエスアイ・デザイン株式会社内 |

審査官 小田 浩

最終頁に続く

(54) 【発明の名称】 固体撮像装置および固体撮像装置の駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

光を電気信号に変換する複数の単位セルから画素信号を取り出す固体撮像装置において、

一方の端子から入力される前記画素信号を保持する第1の容量素子と、

基準電圧が入力される一方の入力端子に前記第1の容量素子の他方の端子が接続される

オペアンプと、

前記第1の容量素子の前記一方の端子と前記オペアンプの他方の入力端子との間に接続

され、前記画素信号の読み出し要求に応じてオン／オフされるスイッチ素子と、

を有することを特徴とする固体撮像装置。

10

## 【請求項 2】

前記単位セルと前記第1の容量素子との間に配設されると共に、スイッチング手段を介して前記第1の容量素子に接続され、前記単位セルから出力される第1の画素信号を保持する第2の容量素子と、

前記基準電圧を前記第1の容量素子と前記第2の容量素子とを接続する接続ノードへ選択的に供給する基準電圧供給手段と、をさらに有したことを特徴とする請求項1記載の固体撮像装置。

## 【請求項 3】

光を電気信号に変換する複数の単位セルから画素信号を取り出す固体撮像装置において、

20

一方の端子から入力される前記画素信号を保持する第1の容量素子と、

スイッチング手段を介して一方の端子が前記第1の容量素子の他方の端子と接続された

第2の容量素子と、

一方の端子が前記第1の容量素子と前記第2の容量素子とを接続する接続ノードに接続

された第3の容量素子を含むと共に、第1の基準電圧を生成する第1の基準電圧生成手段

と、

一方の端子が前記接続ノードに接続された第4の容量素子を含むと共に、第2の基準電

圧を生成する第2の基準電圧生成手段と、

前記接続ノードへ、前記第1の基準電圧又は前記第2の基準電圧を選択的に供給する基

準電圧切り替え手段と、

を有することを特徴とする固体撮像装置。

#### 【請求項4】

光を電気信号に変換する複数の単位セルから画素信号を取り出す固体撮像装置において

、一方の端子から入力される前記画素信号を保持する第1の容量素子と、

スイッチング手段を介して一方の端子が前記第1の容量素子の他方の端子と接続された

第2の容量素子と、

第1の基準電圧が入力される一方の入力端子に前記第2の容量素子の他方の端子が接続

されたオペアンプと、

一方の端子が前記第1の容量素子と前記第2の容量素子とを接続する接続ノードに接続

された第3の容量素子を含むと共に、前記第1の基準電圧を生成する第1の基準電圧生成

手段と、

一方の端子が前記接続ノードに接続された第4の容量素子を含むと共に、第2の基準電

圧を生成する第2の基準電圧生成手段と、

前記接続ノードへ、前記第1の基準電圧又は前記第2の基準電圧を選択的に供給する基

準電圧切り替え手段と、

を有することを特徴とする固体撮像装置。

#### 【請求項5】

前記第3及び第4の容量素子の前記一方の端子はさらに、それぞれ前記第2の容量素子

の他方の端子に接続され、

前記基準電圧切り替え手段は、前記接続ノード及び前記第2の容量素子の他方の端子へ

、前記第1の基準電圧又は前記第2の基準電圧を選択的に供給する、

ことを特徴とする請求項4記載の固体撮像装置。

#### 【請求項6】

一方の端子から入力される画素信号を保持する第1の容量素子と、

基準電圧が入力される一方の入力端子に前記第1の容量素子の他方の端子が接続される

オペアンプと、

前記第1の容量素子の前記一方の端子と前記オペアンプの他方の入力端子との間に接続

され、前記画素信号の読み出し要求に応じてオン／オフされるスイッチ素子と、

を備えた固体撮像装置の駆動方法において、

前記画像信号を前記第1の容量素子に保持して前記スイッチ素子をオンする、

ことを特徴とする固体撮像装置の駆動方法。

#### 【請求項7】

一方の端子から入力される画素信号を保持する第1の容量素子と、

スイッチング手段を介して一方の端子が前記第1の容量素子の他方の端子と接続された

第2の容量素子と、

一方の端子が前記第1の容量素子と前記第2の容量素子とを接続する接続ノードに接続

された第3の容量素子を含むと共に、第1の基準電圧を生成する第1の基準電圧生成手段

と、

一方の端子が前記接続ノードに接続された第4の容量素子を含むと共に、第2の基準電

10

20

30

40

50

圧を生成する第 2 の基準電圧生成手段と、

前記接続ノードへ、前記第 1 の基準電圧又は前記第 2 の基準電圧を選択的に供給する基準電圧切り替え手段と、

を備えた固体撮像装置の駆動方法において、

前記基準電圧切り替え手段によって、前記接続ノードに前記第 2 の基準電圧を供給して前記第 1 の基準電圧を供給する、

ことを特徴とする固体撮像装置の駆動方法。

#### 【請求項 8】

一方の端子から入力される画素信号を保持する第 1 の容量素子と、

スイッチング手段を介して一方の端子が前記第 1 の容量素子の他方の端子と接続された第 2 の容量素子と、

第 1 の基準電圧が入力される一方の入力端子に前記第 2 の容量素子の他方の端子が接続されたオペアンプと、

一方の端子が前記第 1 の容量素子と前記第 2 の容量素子とを接続する接続ノードに接続された第 3 の容量素子を含むと共に、前記第 1 の基準電圧を生成する第 1 の基準電圧生成手段と、

一方の端子が前記接続ノードに接続された第 4 の容量素子を含むと共に、第 2 の基準電圧を生成する第 2 の基準電圧生成手段と、

前記接続ノードへ、前記第 1 の基準電圧又は前記第 2 の基準電圧を選択的に供給する基準電圧切り替え手段と、

を備えた固体撮像素子の駆動方法において、

前記基準電圧切り替え手段によって、前記接続ノードに前記第 2 の基準電圧を供給して前記第 1 の基準電圧を供給する、

ことを特徴とする固体撮像装置の駆動方法。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は固体撮像装置および固体撮像装置の駆動方法に関し、特に光を電気信号に変換する複数の単位セルから画素信号を取り出す固体撮像装置および固体撮像装置の駆動方法に関する。

##### 【背景技術】

##### 【0002】

近年、CCDにかわるイメージセンサとして、CMOSイメージセンサが注目を集めている。これはCCDのシステムが複雑であるのに対し、CMOSイメージセンサは簡略で、多くのメリットを持ち合わせているからである。例えば、CCDは、製造に専用プロセスを必要とし、また動作に複数の電源電圧を必要とし、さらに複数の周辺ICを組み合わせて動作させる必要がある。これに対しCMOSイメージセンサは、一般的なCMOS集積回路と同様の製造プロセスを用いることが可能であり、また単一電源での駆動が可能であり、さらにCMOSプロセスを用いたアナログ回路や論理回路を同一チップ内に混在させることができる。

##### 【0003】

CCDの出力回路は、FD(Floating Diffusion)アンプを用いた1ch出力が主流であるのに対し、CMOSイメージセンサは、画素毎にFDアンプを有し、画素アレイの中のある一行を選択し、それらを同時に列方向へと読み出すような列並列出力型が主流である(例えば特許文献1参照)。これは、画素内に配置されたFDアンプでは、十分な駆動能力を得ることは難しく、データレートを下げる必要で、並列処理が有利とされているからである。

##### 【0004】

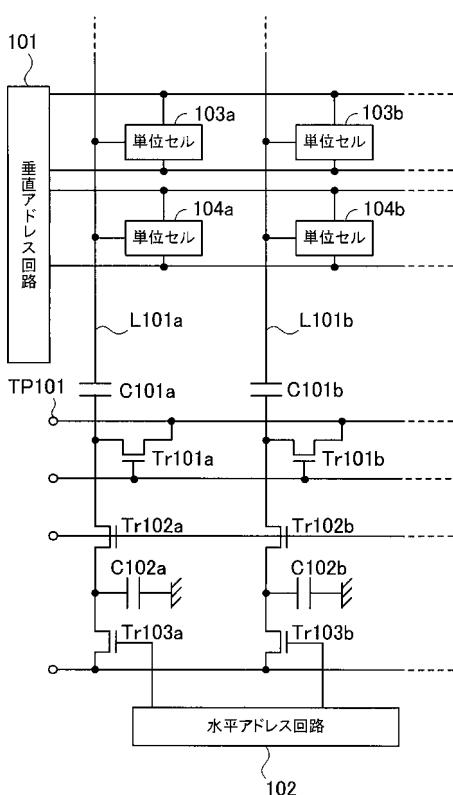

図12は、並列出力型CMOSイメージセンサの信号出力回路の回路図である。この例ではまず、信号レベル+雑音レベル(以降、D相と呼ぶ)を読み出したあと、雑音レベル

10

20

30

40

50

(以降、P相と呼ぶ)を読み出し、引き算を行うことで信号レベルだけを取り出している。この例ではD相を先に読み出しているが、P相から先に読み出すようなタイプもある。

#### 【0005】

垂直信号線L101a, L101b, …にD相レベルを読み出すのに、まず、トランジスタTr101a, Tr101b, …と、トランジスタTr102a, Tr102b, …をオンし、コンデンサC101a, C101b, …とコンデンサC102a, C102b, …との間の接続ノードを、端子TP101に供給されるクランプ電圧に固定する。そして、垂直アドレス回路101により単位セル(画素)103a, 103b, …、単位セル104a, 104b, …を選択し、D相レベルをコンデンサC101a, C101b, …に記憶する。

10

#### 【0006】

次にトランジスタTr101a, Tr101b, …をオフにして、単位セル103a, 103b, …、単位セル104a, 104b, …からP相レベルを読み出す。先のタイミングで、コンデンサC101a, C101b, …にはD相レベルが記憶されているので、コンデンサC102a, C102b, …にはD相レベルからの変化量だけが入力される事になる。コンデンサC102a, C102b, …に取り出される電圧は、コンデンサC101a, C101b, …とコンデンサC102a, C102b, …の分圧比に依存する。ここで、コンデンサC102aの電圧をVsigとすると、Vsigは次の式(1)で示される。

$$V_{sig} = (C101a / C101a + C102a) \times (V_d - V_p) + V_{cp} \dots (1)$$

20

ただし、C101aはコンデンサC101aの容量、C102aはコンデンサC102aの容量、VdはD相の電圧、VpはP相の電圧、Vcpは端子TP101から供給されるクランプ電圧である。Vd - Vpは信号レベル(画素信号)を示し、式(1)は雑音レベルが除去されることを示している。なお、コンデンサC102b, …の電圧も式(1)と同様にして求めることができる。

#### 【0007】

トランジスタTr102a, Tr102b, …をオフすることにより、信号レベルはコンデンサC102a, C102b, …に保持される。そして、信号レベルは、水平アドレス回路102によって、トランジスタTr103a, Tr103b, …を順次オンすることにより、電荷積分回路(例えば特許文献2参照)へ出力され、後段の回路へと出力される。

30

#### 【0008】

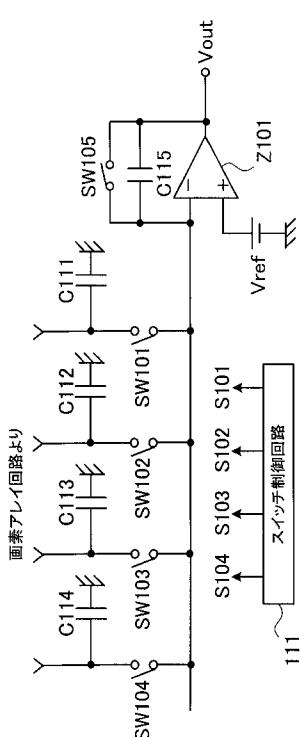

図13は、電荷積分回路の回路図である。図13のスイッチSW101～SW104は、図12のトランジスタTr103a, Tr103b, …に対応し、コンデンサC111～C114は、図12のコンデンサC102a, C102b, …に対応する。また、スイッチ制御回路111は、図12の水平アドレス回路102に対応する。スイッチ信号S101～S104は、スイッチSW101～SW104をオン／オフする信号である。

#### 【0009】

始めにスイッチSW105をオンにしてコンデンサ(積分容量)C115をリセットする。次にスイッチSW105をオフにして、スイッチSW101をオンし、コンデンサC111に保持されていた信号レベルをコンデンサC115に読み出す。信号レベルは、オペアンプZ101の出力端子から信号電圧Voutとして出力される。ここで、信号電圧Voutは、コンデンサC111に保持される電圧が式(1)のように表されることを用いて次の(2)のように示される。

$$\begin{aligned} V_{out} &= (C111 / C115) \times [V_{ref} - \{K(V_d - V_p) + V_{cp}\}] + V_{ref} \\ &= K(C111 / C115) \times (V_p - V_d) + (C111 / C115) \times (V_{ref} - V_{cp}) + V_{ref} \dots (2) \end{aligned}$$

ただし、K = C101a / (C101a + C111)で、C101aは図12のコンデ

40

50

ンサ C 101a の容量を示す。また、C 111 はコンデンサ C 111 の容量、C 115 はコンデンサ C 115 の容量、Vref はオペアンプ Z 101 の正相端子に入力される基準電圧である。

#### 【0010】

式(2)の( $C_{111}/C_{115}) \times (V_{ref} - V_{cp})$ )の項は単なるオフセットであるが、容量の比が乗算されるので増幅されて出力される。そのため、オフセットを最小にするには、 $V_{ref} = V_{cp}$  とすればよい。すなわち、オペアンプ Z 101 に入力される基準電圧  $V_{ref}$  と、図 12 で示した端子 TP 101 に供給されるクランプ電圧  $V_{cp}$  を、同一電源から同一電圧として出力するようにすればよい。なお、コンデンサ C 112, ... における信号電圧も式(2)と同様にして求めることができる。

10

#### 【0011】

基準電圧  $V_{ref}$  (クランプ電圧  $V_{cp}$ ) は、チップ外部から供給される場合もあるが、チップ内部で生成することも可能で、特に CMOS イメージセンサの場合はシステムがコンパクトであるためにチップ内部で生成される場合が多い。

#### 【0012】

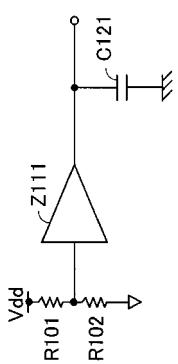

図 14 は、クランプ電圧発生回路の一例を示す。図に示すクランプ電圧発生回路は、電源  $V_{dd}$  の電圧を抵抗 R 101, R 102 によって分圧し、アンプ Z 111 でインピーダンス変換して電圧を出力している。アンプ Z 111 の出力には、コンデンサ C 121 が接続されている。コンデンサ C 121 は、出力される電圧の安定性を得るために非常に大きな容量 (通常  $\mu F$  オーダー) が求められ、チップ内部では作成困難であるために外付けされる。アンプ Z 111 は、電圧を出力するときコンデンサ C 121 の充電から始まるため動作速度が遅くなり、瞬間的な動作 (瞬時に目的の電圧値を出力するなど) に対応することができない。次に、このクランプ電圧発生回路を電荷積分回路に適用した場合について説明する。

20

#### 【0013】

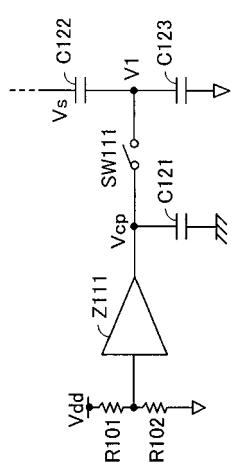

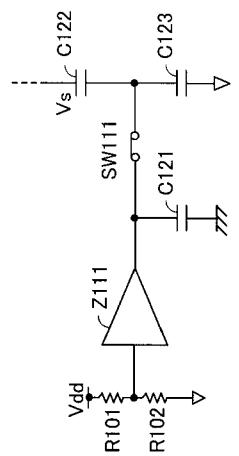

図 15 は、クランプ電圧を出力していないときのクランプ電圧発生回路を示した回路図で、図 16 は、クランプ電圧を出力しているときのクランプ電圧発生回路を示した回路図である。図 15, 16 のコンデンサ C 122 は図 12 のコンデンサ C 101a に対応し、コンデンサ C 123 は図 12 のコンデンサ C 102a に対応している。コンデンサ C 122 には、単位セルから電圧  $V_s$  が印加されているとする。

30

#### 【0014】

図 15においては、スイッチ SW 111 はオフしており、コンデンサ C 121 にはクランプ電圧  $V_{cp}$  が充電されている。この状態におけるコンデンサ C 122 とコンデンサ C 123 の接続ノードの電圧を  $V_1$  とする。

#### 【0015】

図 16 に示すようにスイッチ SW 111 がオンした場合、コンデンサ C 122 とコンデンサ C 123 の接続ノードの電圧は、電圧  $V_1$  から瞬時にクランプ電圧  $V_{cp}$  になるのが理想であるが、アンプ Z 111 の駆動が遅いために、要求されるクランプ電圧  $V_{cp}$  と誤差が生じる。この誤差電圧はコンデンサ C 121 ~ C 123 の容量分圧で決まり、次の式(3)で示される。

40

$$V_{er} = V_{cp} - \{ C_{121} \times V_{cp} + (C_{123} + C_{122}) \times V_1 \} / (C_{121} + C_{123} + C_{122}) \dots (3)$$

この誤差電圧  $V_{er}$  はアンプ Z 111 によってクランプ電圧  $V_{cp}$  とされる前にコンデンサ C 123 にサンプリングされた場合、 $V_{ref} = V_{cp}$  が成立しなくなり、オフセットとして出力される。よって、アンプ Z 111 は、通常、次の信号レベルの読み出し動作までには、再びクランプ電圧  $V_{cp}$  を出力する駆動能力を有するよう設計される。

【特許文献 1】国際公開第 WO / 9707628 号パンフレット (第 18 頁、第 21 図)

【特許文献 2】特開平 11 - 69231 号公報 (第 4 頁、第 1 図)

#### 【発明の開示】

#### 【発明が解決しようとする課題】

50

**【0016】**

しかし、従来では図13に示すように、信号レベルを蓄えるコンデンサC111～C114の基準電位(グランド)と、オペアンプZ101の基準電位(基準電圧Vref)とが異なっているため、グランドに対して基準電圧Vrefが振動し、またはノイズが乗ってしまうと、増幅されて信号電圧Voutに現れるという問題点があった。

**【0017】**

また、単位セルの数が多くなってくると、画素信号を保持するコンデンサの数も多くなり、クランプ電圧をより安定して出力する必要が生じる。そのため、クランプ電圧を出力するアンプの駆動能力を高くし、またはアンプの出力に接続されるコンデンサの容量を大きくする必要があり、消費電力が大きくなり、または実装面積が大きくなるといった問題点があった。10

**【0018】**

本発明はこのような点に鑑みてなされたものであり、基準電圧が振れても、または基準電圧にノイズが乗っても、それらを抑制して出力することができる固定撮像装置およびその駆動方法を提供することを目的とする。

**【0019】**

また本発明では、消費電力および実装面積を抑え、安定したクランプ電圧を出力することができる固体撮像装置およびその駆動方法を提供することを目的とする。

**【課題を解決するための手段】****【0020】**

本発明では上記問題を解決するために、光を電気信号に変換する複数の単位セルから画素信号を取り出す固体撮像装置において、一方の端子から入力される前記画素信号を保持する第1の容量素子と、基準電圧が入力される一方の入力端子に前記第1の容量素子の他方の端子が接続されるオペアンプと、前記第1の容量素子の前記一方の端子と前記オペアンプの他方の入力端子との間に接続され、前記画素信号の読み出し要求に応じてオン／オフされるスイッチ素子と、を有することを特徴とする固体撮像装置が提供される。20

**【0021】**

このような固体撮像装置によれば、オペアンプの入力端子間は画素信号を保持する第1の容量素子が接続された状態となるので、一方の入力端子に入力される基準電圧の振れ、または基準電圧に乗るノイズは、第1の容量素子を介し他方の入力端子にも入力される。30

**【0022】**

また本発明では、光を電気信号に変換する複数の単位セルから画素信号を取り出す固体撮像装置において、一方の端子から入力される前記画素信号を保持する第1の容量素子と、スイッチング手段を介して一方の端子が前記第1の容量素子の他方の端子と接続された第2の容量素子と、一方の端子が前記第1の容量素子と前記第2の容量素子とを接続する接続ノードに接続された第3の容量素子を含むと共に、第1の基準電圧を生成する第1の基準電圧生成手段と、一方の端子が前記接続ノードに接続された第4の容量素子を含むと共に、第2の基準電圧を生成する第2の基準電圧生成手段と、前記接続ノードへ、前記第1の基準電圧又は前記第2の基準電圧を選択的に供給する基準電圧切り替え手段と、を有することを特徴とする固体撮像装置が提供される。40

**【0023】**

このような固体撮像装置によれば、第1の容量素子と第2の容量素子とを接続する接続ノードへの電圧を、第1の基準電圧生成手段より生成される第1の基準電圧と第2の基準電圧生成手段より生成される第2の基準電圧とを切替えて供給し、すばやく目的とする電圧にする。

**【発明の効果】****【0024】**

本発明の固体撮像装置では、オペアンプの入力端子間は画素信号を保持する第1の容量素子が接続された状態になるので、一方の入力端子に入力される基準電圧の振れ、または50

基準電圧に乗るノイズは第1の容量素子を介し他方の入力端子にも入力され、オペアンプの出力のノイズは抑制される。

#### 【0025】

また、本発明の固体撮像装置では、第1の基準電圧と第2の基準電圧とを切替えて第1の容量素子と第2の容量素子とを接続する接続ノードに電圧を供給するので、消費電力および実装面積を抑え、安定した電圧をすばやく接続ノードに出力することができる。

#### 【発明を実施するための最良の形態】

##### 【0026】

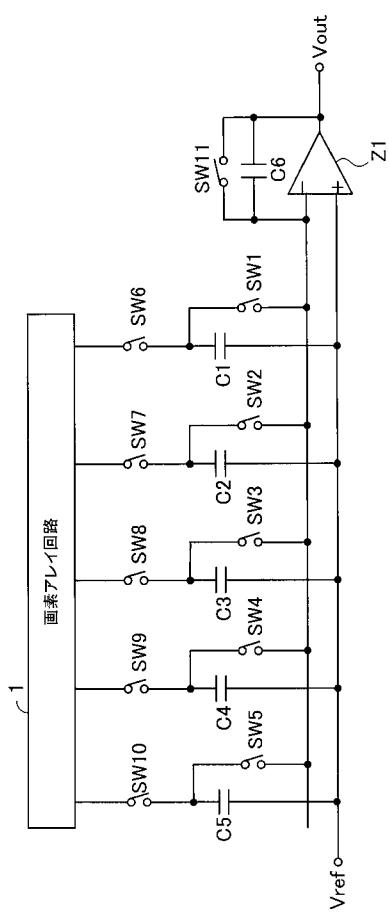

以下、本発明の実施の形態を図面を参照して詳細に説明する。図1は、第1の実施の形態に係る固体撮像装置の回路図である。図に示す固体撮像装置は、例えば、1つの半導体チップに形成され、デジタルビデオカメラ、携帯電話のデジタルカメラに適用される。固体撮像装置は、オペアンプZ1、コンデンサC1～C6、スイッチSW1～SW11、および画素アレイ回路1を有している。なお図1では、説明を簡単にするためにコンデンサC1～C5、スイッチSW1～SW5、スイッチSW6～SW10と5つしか示していないが、実際には、画素アレイ回路1が有する2次元的に配列された画素（単位セル）の水平方向の画素数分だけ並ぶことになる。例えば、SXGAフォーマットであれば約1300列存在する。

##### 【0027】

オペアンプZ1の正相端子には基準電圧Vrefが入力されている。また、正相端子には、コンデンサC1～C5の一端が接続されている。逆相端子には、スイッチSW1～SW5の一端が接続されている。スイッチSW1～SW5の他端は、コンデンサC1～C5の他端に接続されている。また、コンデンサC1～C5の他端は、スイッチSW6～SW10を介して画素アレイ回路1と接続されている。オペアンプZ1の逆相端子と出力の間には、コンデンサC6とスイッチSW11が並列に接続されている。なお、基準電圧Vrefは、チップ内部で発生するようにしてもよいし、外部から供給するようにしてもよい。

##### 【0028】

画素アレイ回路1から出力される画素信号をオペアンプZ1から出力するには、まずスイッチSW11をオンし、コンデンサC6に充電されている電荷をリセットする。次いで画素アレイ回路1から画素信号が出力されるときにスイッチSW6～SW10をオンし、その後オフする。これによってコンデンサC1～C5には、画素信号が保持される。そして、スイッチSW1～SW5をオンすることによって、コンデンサC1～C5に保持されていた画素信号が信号電圧VoutとしてオペアンプZ1から出力される。

##### 【0029】

ここで、図13で示した回路では、コンデンサC111～C114の基準（画素信号が入力されない方の端子の電位）はグランドにとられている。そのため、基準電圧Vrefの振れ、または基準電圧Vrefから入ったノイズは、コンデンサC111～C114、コンデンサC115、および寄生容量Cp（逆相端子とグランド間の容量）の比で決まるゲインがかかって出力される。基準電圧Vrefに混入するノイズをノイズ電圧Vn（AC成分のみとする）とし、また、グランドは完全に固定されているとすると、オペアンプZ101の信号電圧Voutは次の式(4)で示される。

$$V_{out} = \{ (Cx + C115 + Cp) / C115 \} \times Vn \dots (4)$$

ただし、CxはコンデンサC111～C114の容量、C115はコンデンサC115の容量、Cpは寄生容量Cpの容量を示す。式(4)に示すようにCpが大きい場合などは、大きなゲインとなってノイズ電圧Vnは増幅されて出力される。

##### 【0030】

図1の回路では、コンデンサC1～C5の基準はオペアンプZ1の正相端子に入力される基準電圧Vrefとなっている。よって、オペアンプZ1の信号電圧Voutは次の式(5)となる。

$$V_{out} = Vn \dots (5)$$

10

20

30

40

50

図1の回路では、式(5)に示すようにノイズ電圧 $V_n$ はゲインがかかることなくオペアンプZ1から出力される(ただし厳密には、ノイズの周波数、スイッチSW11をオン/オフによって変わってくる)。これは、基準電圧 $V_{ref}$ から混入するノイズは、オペアンプZ1の正相端子に入力されるとともに、コンデンサC1~C5を介して逆相端子にも入力されるからである。よって、基準電圧 $V_{ref}$ の振れ、基準電圧 $V_{ref}$ に混入するノイズを低減することができる。

#### 【0031】

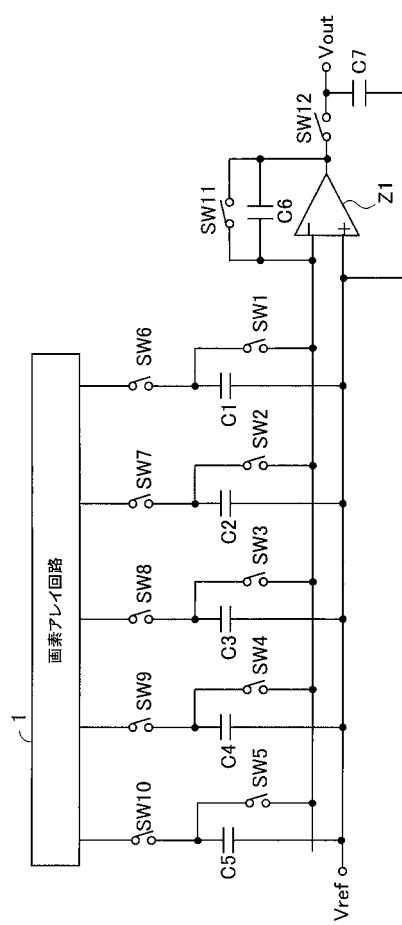

次に第2の実施の形態について説明する。図2は、第2の実施の形態に係る固体撮像装置の回路図である。図2の固体撮像装置では、図1の固体撮像装置にサンプルホールド回路が接続されているところが異なる。図2において、図1と同じものには同じ符号を付し、その説明を省略する。図2の固体撮像装置では、オペアンプZ1の出力にスイッチSW12が接続されている。また、スイッチSW12とオペアンプZ1の正相端子の間にコンデンサC7が接続されている。10

#### 【0032】

コンデンサC7の基準は、オペアンプZ1の正相端子に入力される基準電圧 $V_{ref}$ と同じになっている。図に示す回路は基準電圧 $V_{ref}$ から混入されるノイズ電圧 $V_n$ に対しては式(5)と同じ振る舞いを示し、さらにコンデンサC7に保持される電荷量はノイズ電圧 $V_n$ の変化に対して常に一定に保たれる。よって、後段の回路でコンデンサC7に保持される一定の電荷(電圧)を取り出せば、基準電圧 $V_{ref}$ の振れ、基準電圧 $V_{ref}$ に混入されるノイズを除去することができる。20

#### 【0033】

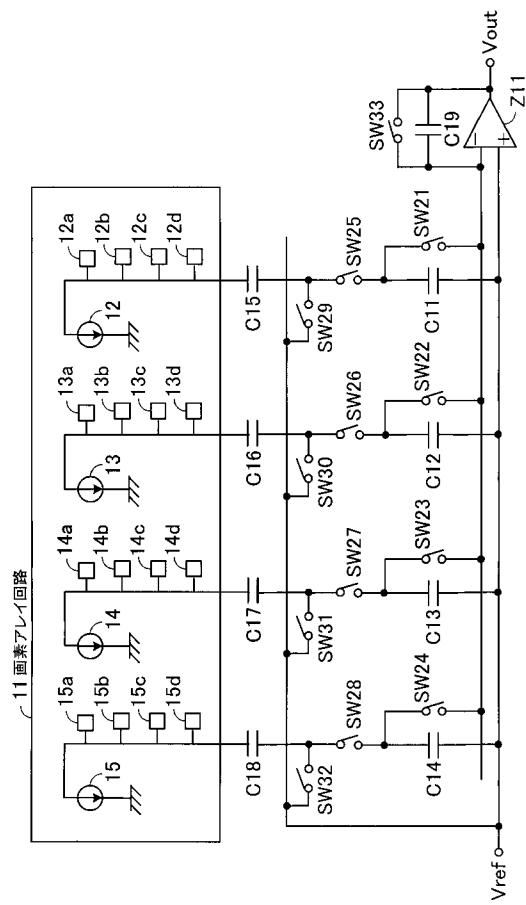

次に第3の実施の形態について説明する。図3は、第3の実施の形態に係る固体撮像装置の回路図である。図3に示す固体撮像装置は、オペアンプZ11、コンデンサC11~C19、スイッチSW21~SW33、および画素アレイ回路11を有している。

#### 【0034】

画素アレイ回路11は、電流源12~15、単位セル12a~12d、13a~13d、14a~14d、15a~15dを有している。単位セル12a~12d、13a~13d、14a~14d、15a~15dは、光を電気信号に変換する。そして、図示していないが、例えばトランジスタなどのスイッチで選択され、画素信号としてコンデンサC15~C18に出力する。なお図では、説明を簡単にするため単位セルを4×4しか示していないが、実際は多数の画素が並ぶ。30

#### 【0035】

オペアンプZ11の正相端子には基準電圧 $V_{ref}$ が入力される。また、正相端子には、コンデンサC11~C14の一端が接続されている。逆相端子には、スイッチSW21~SW24の一端が接続されている。スイッチSW21~SW24の他端は、コンデンサC11~C14の他端と接続されている。コンデンサC11~C14の他端は、スイッチSW25~SW28を介してコンデンサC15~C18の一端と接続されている。コンデンサC15~C18の他端は画素アレイ回路11と接続されている。スイッチSW29~SW32の一端は、コンデンサC15~C18とスイッチSW25~SW28との間に接続され、他端は基準電圧 $V_{ref}$ が入力されるオペアンプZ11の正相端子と接続されている。オペアンプZ11の逆相端子と出力の間には、コンデンサC19とスイッチSW33が並列に接続されている。なお、基準電圧 $V_{ref}$ は、チップ内部で発生するようにしてもよいし、外部から供給するようにしてもよい。40

#### 【0036】

画素アレイ回路11から出力される画素信号をオペアンプZ11から出力するには、まずスイッチSW25~SW32をオンにする。これによって直列接続されたコンデンサC11,C15、コンデンサC12,C16、コンデンサC13,C17、およびコンデンサC14,C18の間の電圧(クランプ電圧)は、基準電圧 $V_{ref}$ で固定される。次いで、コンデンサC15~C18に基準電圧 $V_{ref}$ を基準として画素アレイ回路11のD相レベルの信号を保持する。次いで、スイッチSW29~SW32をオフして、画素アレ50

イ回路 11 の P 相レベルの信号を読み込む。これによって、コンデンサ C11 ~ C14 には、P 相レベルと D 相レベルの差の信号、すなわち画素信号が保持される。次いで、スイッチ SW21 ~ SW24 をオンすることによって、画素信号の電圧がオペアンプ Z11 から信号電圧 Vout として出力される。

#### 【0037】

ここで、図 12 で示した回路では、コンデンサ C102a, C102b, … の基準（画像の信号が入力されない方の端子の電位）はグランドにとられている。従って、第 1 の実施の形態で説明したように、基準電圧 Vref にノイズ電圧 Vn が乗ると、オペアンプ Z11 の正相端子のみにノイズ電圧 Vn が入力されるため増幅されて出力されることになる。しかし、図 3 の回路では、コンデンサ C11 ~ C14 の基準はオペアンプ Z11 の正相端子に入力される基準電圧 Vref にとってあるため、基準電圧 Vref にノイズ電圧 Vn が乗っても、コンデンサ C11 ~ C14 を介して反転端子にも入力されるため、増幅されることなくノイズを抑制することができる。10

#### 【0038】

また、基準電圧 Vref がクランプ電圧としてコンデンサ C15 ~ C18 に充電されるので、クランプ電圧と基準電圧 Vref が等しくなり、上記で説明した式(2)の第 2 項は 0 となる。よって、オフセットの出力を抑えることができ、画像の黒レベルの誤差を低減することができる。

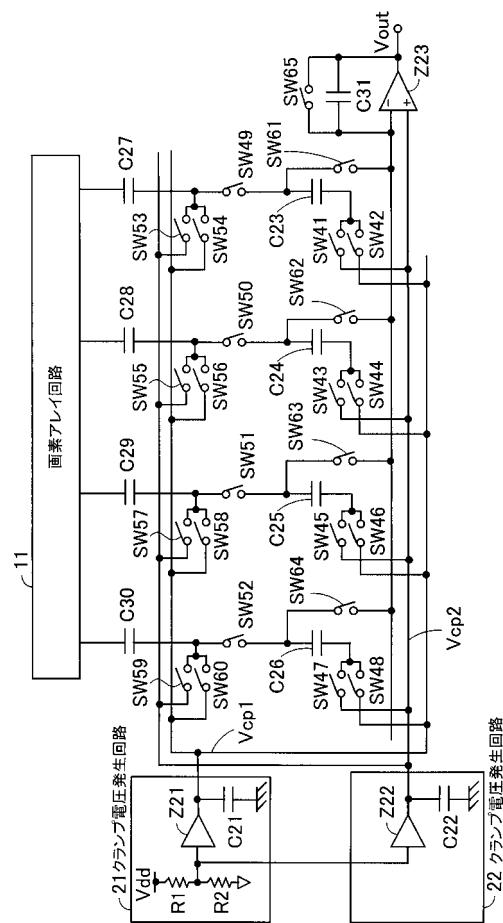

#### 【0039】

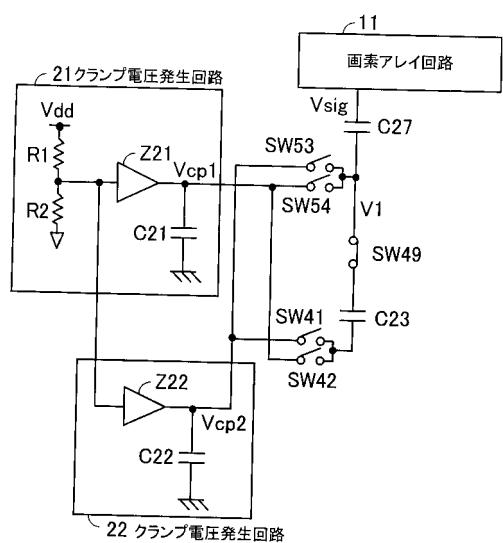

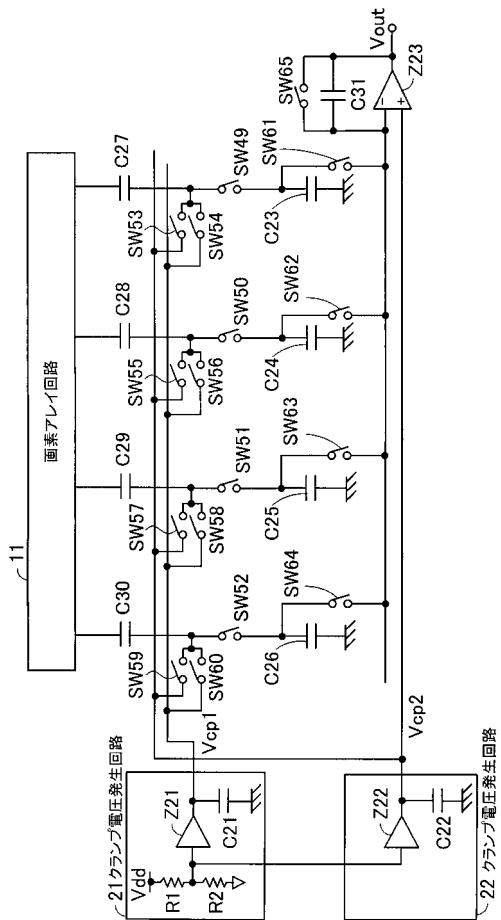

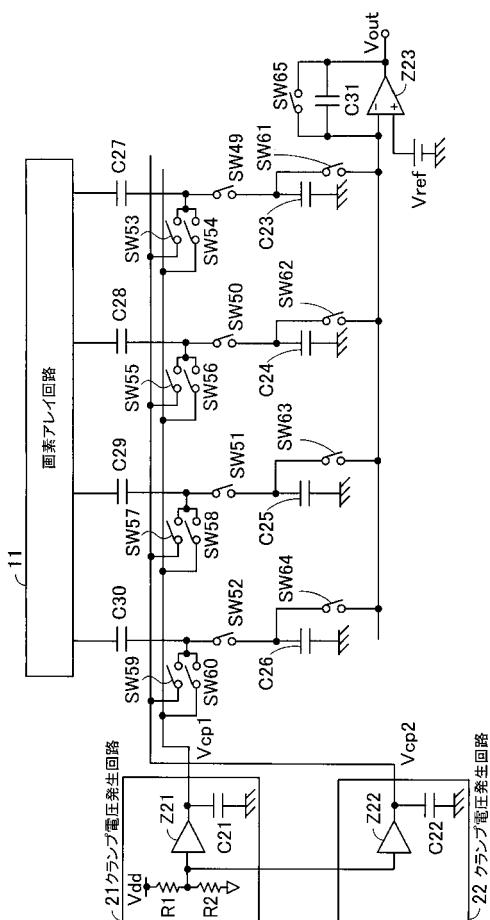

次に第 4 の実施の形態について説明する。図 4 は、第 4 の実施の形態に係る固体撮像装置の回路図である。図に示す固体撮像装置は、オペアンプ Z23、コンデンサ C23 ~ C31、スイッチ SW41 ~ SW65、画素アレイ回路 11、およびクランプ電圧発生回路 21, 22 を有している。なお、画素アレイ回路 11 は、図 3 で説明した画素アレイ回路と同じであり、その詳細な説明は省略する。20

#### 【0040】

クランプ電圧発生回路 21 は、抵抗 R1, R2、アンプ Z21、コンデンサ C21 を有している。抵抗 R1, R2 は直列に接続され、抵抗 R1 の一端は、電源 Vdd に接続されている。抵抗 R1, R2 の接続点はアンプ Z21 の入力と接続されている。すなわち、アンプ Z21 は、抵抗 R1, R2 によって分圧された電源 Vdd の電圧をインピーダンス変換し、クランプ電圧 Vcp1 を出力している。アンプ Z21 の出力には、コンデンサ C21 が接続されている。30

#### 【0041】

クランプ電圧発生回路 22 は、アンプ Z22 およびコンデンサ C22 を有している。アンプ Z22 には、クランプ電圧発生回路 21 の抵抗 R1, R2 によって分圧された電源 Vdd の電圧が入力される。アンプ Z22 は、入力される電圧をインピーダンス変換し、クランプ電圧 Vcp2 を出力している。アンプ Z22 の出力には、コンデンサ C22 が接続されている。

#### 【0042】

クランプ電圧発生回路 21 のアンプ Z21 とクランプ電圧発生回路 22 のアンプ Z22 は同じ回路構成からなり、同じ特性を有する。また、コンデンサ C21 とコンデンサ C22 は同じ容量を有し、同じ特性を有する。アンプ Z21, Z22 のオフセット電圧を同じとすれば、アンプ Z21, Z22 は、抵抗 R1, R2 によって分圧された同じ電圧が入力されるので、定常状態においては同じ電圧のクランプ電圧 Vcp1, Vcp2 が出力される。なお、アンプ Z21, Z22 の出力に接続されるコンデンサ C21, C22 は、外付けまたはチップに内蔵される。40

#### 【0043】

オペアンプ Z23 の正相端子は、クランプ電圧発生回路 22 のアンプ Z22 の出力と接続されている。また、オペアンプ Z23 の正相端子は、スイッチ SW41, SW43, SW45, SW47 を介してコンデンサ C23 ~ C26 の一端と接続されている。逆相端子には、スイッチ SW61 ~ SW64 を介してコンデンサ C23 ~ C26 の他端と接続され50

ている。コンデンサ C 23～C 26の一端はスイッチ SW42, SW44, SW46, SW48を介して、クランプ電圧発生回路 21のアンプ Z21の出力と接続されている。オペアンプ Z23の逆相端子と出力の間には、コンデンサ C27とスイッチ SW65が並列に接続されている。

#### 【0044】

コンデンサ C 23～C 26の一端は、スイッチ SW49～SW52を介してコンデンサ C 27～C 30の一端と接続されている。また、コンデンサ C 27～C 30の一端は、スイッチ SW53, SW55, SW57, SW59を介してクランプ電圧発生回路 22のアンプ Z22の出力と接続されている。また、コンデンサ C 27～C 30の一端は、スイッチ SW54, SW56, SW58, SW60を介してクランプ電圧発生回路 21のアンプ Z21の出力と接続されている。コンデンサ C 27～C 30の他端は、画素アレイ回路 11と接続されている。10

#### 【0045】

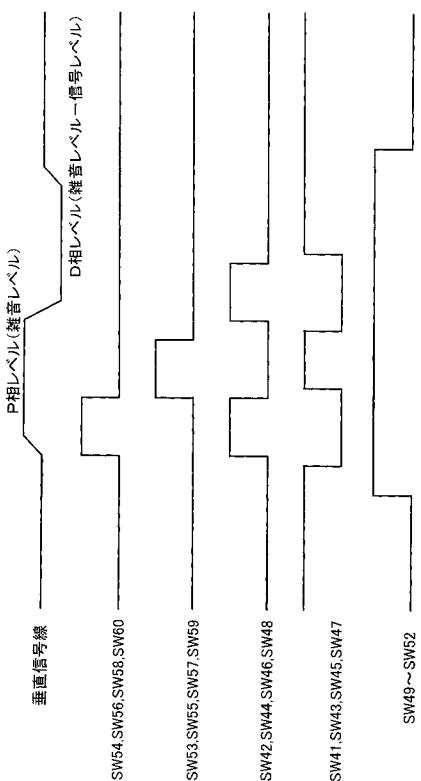

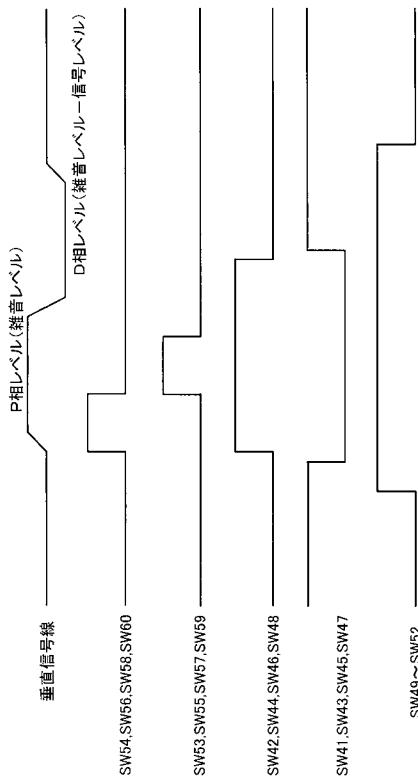

以下、タイミングチャートを用いて図 4 の回路の動作を説明する。図 5 は、図 4 の回路のタイミングチャートである。図 5 に示す垂直信号線は、画素アレイ回路 11 の垂直信号線（具体例を示すと、図 12 の垂直信号線 L101a, L101b, …に対応）に生じる電圧を示している。また、図に示す SW41～SW60 は、図 4 のスイッチ SW41～SW60 に対応している。H 状態のとき、スイッチ SW41～SW60 はオンし、L 状態のとき、スイッチ SW41～SW60 はオフする。

#### 【0046】

図に示すように、垂直信号線に P 相レベルが出力される前に、スイッチ SW49～SW52 をオンする。これにより、コンデンサ C 23～C 26 とコンデンサ C 27～C 30 は直列接続となる。また、スイッチ SW41, SW43, SW45, SW47 をオフする。20

#### 【0047】

垂直信号線に P 相レベル出力が出力されたとき、スイッチ SW54, SW56, SW58, SW60、スイッチ SW42, SW44, SW46, SW48 をオンする。これにより、コンデンサ C 23～C 26 とコンデンサ C 27～C 30 の接続ノードは、クランプ電圧発生回路 21 から出力されるクランプ電圧 Vcp1 にクランプされる。

#### 【0048】

次いで、スイッチ SW54, SW56, SW58, SW60、スイッチ SW42, SW44, SW46, SW48 をオフし、スイッチ SW53, SW55, SW57, SW59 をオンする。そして、スイッチ SW41, SW43, SW45, SW47 をオンする。これによって、コンデンサ C 27～C 30 を充電していたクランプ電圧 Vcp1 は、クランプ電圧発生回路 22 から出力されるクランプ電圧 Vcp2 に切替わる。30

#### 【0049】

クランプ電圧発生回路 21 でクランプ電圧 Vcp1 を出力しているとき、アンプ Z21 の動作はコンデンサ C 21 によって遅いために、目的とするクランプ電圧 Vcp1 と実際にコンデンサ C 27～C 30 に生じている電圧には誤差が生じている。ここで、クランプ電圧発生回路 22 のクランプ電圧 Vcp2 に切替えると、クランプ電圧発生回路 22 では、コンデンサ C 27～C 30 にすでに一部電荷が充電されているので、残りの電荷を充電すればよく、負荷が軽くなっている。よって、コンデンサ C 27～C 30 をすばやくクランプ電圧 Vcp2 に充電することができ、誤差電圧を抑えることができる。40

#### 【0050】

垂直信号線の電圧が D 相レベル出力の電圧となるとき、スイッチ SW41, SW43, SW45, SW47 をオフし、スイッチ SW42, SW44, SW46, SW48 をオンし、コンデンサ C 23～C 26 の基準をクランプ電圧 Vcp1 に切替える。次いで、D 相レベルの出力が終了する前に、スイッチ SW42, SW44, SW46, SW48 と、スイッチ SW41, SW43, SW45, SW47 のオン / オフを切替える。これは、D 相レベルが読み出されるとき垂直信号線の電位が変化してクランプ電圧発生回路 21 のコンデンサ C 21 に電荷が流入出し、目的とするクランプ電圧との間に誤差電圧が発生するた50

めである。すなわち、クランプ電圧  $V_{cpl}$  からクランプ電圧  $V_{cp2}$  に切替えることによって、コンデンサ  $C_{21}$  の電荷の充放電を一部で済ませ、また、クランプ電圧発生回路  $2_2$  のコンデンサ  $C_{22}$  もその一部を補えばよく、クランプ電圧の誤差電圧を抑制する。

#### 【0051】

次いで、スイッチ  $SW_{49} \sim SW_{52}$  をオフすることによって、コンデンサ  $C_{23} \sim C_{26}$  には、P相レベルとD相レベルの差分の信号、すなわち、画素信号が保持される。なお、図4に示すスイッチ  $SW_{61} \sim SW_{64}$  をオンすれば、コンデンサ  $C_{23} \sim C_{26}$  に保持されていた画素信号は、オペアンプ  $Z_{23}$  から信号電圧  $V_{out}$  として出力される。

#### 【0052】

このように、2つのクランプ電圧発生回路により、クランプ電圧を切替えて供給し、すばやく充電させることによってクランプ信号の誤差電圧を抑えることができる。10

また、オペアンプ  $Z_{23}$  の正相端子にクランプ電圧を入力するので、クランプ電圧にノイズが混入しても、コンデンサ  $C_{23} \sim C_{26}$  を介し逆相端子にも入力され相殺されるので、ノイズの出力を低減することができる。

#### 【0053】

また、P相レベル、D相レベルで発生する誤差電圧を誤差電圧  $V_{erp}$ ,  $V_{erd}$  とすると、誤差電圧  $V_{erp}$ ,  $V_{erd}$  は、コンデンサ  $C_{21}$  に蓄積されるため、次の画素信号の読み出し動作までに(1H内)クランプ電圧  $V_{cpl}$  を出力するための電荷が充電されている必要がある。図4で示す回路では、途中でクランプ電圧発生回路  $2_2$  にクランプ電圧の出力が切替わるため、コンデンサ  $C_{21}$  に生じる誤差電圧  $V_{erp}$ ,  $V_{erd}$  は小さく済み、誤差電圧  $V_{erp}$ ,  $V_{erd}$  をなくすための充電も少量で済む。よって、コンデンサ  $C_{21}$  は、大きな容量を必要とせず小さなスペースでチップに内蔵することが可能となる。また、1H内で動作させるための時定数を持たせるためにアンプ  $Z_{21}$  に供給する電力を上げる必要もなく、消費電力を抑えることができる。クランプ電圧発生回路  $2_2$  のコンデンサ  $C_{22}$  も、クランプ電圧発生回路  $2_1$  が目的とするクランプ電圧  $V_{cpl}$  を出力できなかった分を補うだけの電荷を出力できればよく、大きな容量を必要とせず、小さなスペースでチップに内蔵することが可能となる。また、アンプ  $Z_{22}$  に供給する電力を上げる必要もなく、消費電力を抑えることができる。20

#### 【0054】

次に、誤差電圧について詳細に説明する。まず、図15, 16で説明した回路での誤差電圧について説明する。この場合、前述したように誤差電圧  $V_{er}$  は式(3)で示される。式(3)において、SXGAフォーマットの列を約1300列とし、 $V_{cpl} = 1V$ 、 $C_{121} = 1\mu F$ 、 $C_{123} = 2pF \times 1300 = 2600pF$ 、 $C_{122} = 2pF \times 1300 = 2600pF$ 、 $V_1 = 2V$ を式(3)に代入すると、 $V_{er} = -5.2mV$ となる。 $V_1 = 2V$ で、 $V_{cpl} = 1V$ としたので、1V差のクランプ電圧を印加しており、誤差電圧  $V_{er}$  が約5mVを出力するということは、約1/200の圧縮率ということになる。これは、 $C_{121}$ と( $C_{122} + C_{123}$ )でほとんど決まる値である。30

#### 【0055】

図4で示した回路についての誤差電圧について説明する。図6は、誤差電圧を説明するための回路図その1、図7は、誤差電圧を説明するための回路図その2、図8は、誤差電圧を説明するための回路図その3である。図6に示す回路は、図4の回路を一部抜き出したものであり、同じものには同じ符号を付しその説明を省略する。図7の回路は、図6に示す回路のスイッチ  $SW_{42}$ ,  $SW_{54}$  をオンした状態を示している。図8の回路は、図6に示す回路のスイッチ  $SW_{41}$ ,  $SW_{53}$  をオンした状態を示している。40

#### 【0056】

図6の状態において、画素アレイ回路  $1_1$  から出力されている画素信号の電圧を  $V_{sig}$  とする。また、コンデンサ  $C_{23}$ ,  $C_{27}$  の接続ノードの電圧を  $V_1$  とする。また、クランプ電圧発生回路  $2_1$  が出力するクランプ電圧を  $V_{cpl1}$ 、クランプ電圧発生回路  $2_2$  が出力するクランプ電圧を  $V_{cpl2}$  とする。

#### 【0057】

この状態から図7に示すように、スイッチSW42, SW54がオンすると、コンデンサC27にはクランプ電圧発生回路21からのクランプ電圧Vcp1が印加される。コンデンサC27に印加されるクランプ電圧は、アンプZ21の駆動が追いつかないために、図6のコンデンサC23, C27の接続間の電圧V1と、コンデンサC23, C27による分圧によって決まる。図7の状態でのクランプ電圧Vcp1に対する誤差電圧Ver1は、電荷保存の法則より次の式(6)で示される。

$$\begin{aligned} Ver1 = Vcp1 - [V1 \times C27 + (V1 - Vcp2)C23 \\ + Vcp1 \times C21] / (C27 + C21) \dots (6) \end{aligned}$$

ここで、C27はコンデンサC27の容量、C23はコンデンサC23の容量、C21はコンデンサC21の容量である。SXGAフォーマットの列を約1300列とし、Vcp1 = 1V、Vcp2 = 1V、C21 = 1μF、C23 = 2pF × 1300 = 2600pF、C27 = 2pF × 1300 = 2600pF、V1 = 2Vとすると(アンプZ21, Z22のオフセットについては無視する)、Ver1 = -5.2mVとなる。この時点では、上記で説明した図15, 16の回路の誤差電圧と同じである。

#### 【0058】

この状態から図8に示すように、スイッチSW42, SW54をオフし、スイッチSW41, SW53をオンすると、クランプ電圧Vcp2がコンデンサC27に印加される。図8では、コンデンサC23, C27の接続ノードの電圧と、コンデンサC23の接続ノードと反対側の端子の初期電圧はV1 + Vcp1となっているだけで、図8における誤差電圧Ver2は、式(6)のV1とVcp2をVcp1 + Ver1に置き換えればよく、次の式(7)で示される。

$$Ver2 = Vcp2 - [(Vcp1 \times Ver1) \times C27 + Vcp2 \times C22] / (C27 + C22) \dots (7)$$

式(7)に式(6)に代入したのと同じ条件を入力すると、Ver2 = -13.5μVとなってVer1の約1/400の値となる。

#### 【0059】

このように、2つのクランプ電圧発生回路を連続的に切替えてクランプ電圧を出力することで、誤差電圧を抑制することが可能となる。その抑圧能力は図15, 16に示す1つだけの場合に比べて指数関数的に抑制するため、単純に2倍の大きさの外付け容量を用意する場合に比べても極めて有効であり、また、小さな容量で済むためそれを充電するアンプの時定数を1H以内に抑えようとした場合も消費電力の増大を招かずに済む。なお、クランプ電圧発生回路は、2以上であってもよい。クランプ電圧発生回路を設けた数に対応して、コンデンサに供給するクランプ電圧を指数関数的にはやく目的とするクランプ電圧にすることができる。

#### 【0060】

上記で説明したようにD相レベルのときに垂直信号線の電圧が変化すると、クランプ電圧に誤差電圧が発生してしまう。ここで、図15において、D相レベルが読み出しされるとき、コンデンサC122とコンデンサC123は直列接続となり、D相レベルの電圧の変化はコンデンサC121によって受け止められる形となる。この誤差電圧をVer3とすると次の式(8)で示される。

$$\begin{aligned} Ver3 = (Vsigp - Vsigd) \times [ (C122 // C123) \\ / \{ (C122 // C123) + C121 \}] \dots (8) \end{aligned}$$

ここで、(C122 // C123)はコンデンサC122, C123の直列合成容量、VsigpはP相レベル時の垂直信号線の電圧、VsigdはD相レベル時の垂直信号線の電圧である。なお、(Vsigp - Vsigd)はP相レベルからD相レベルへ変化するときの電圧の変化である。

#### 【0061】

ここで、(Vsigp - Vsigd) = 1V、(C122 // C123) = (2.6nF // 2.6nF) = 1.3nF、C121 = 1μFとすると、Ver3 = 1.3mVとなる。これは、(C122 // C123)とC121の容量比で決まる。

10

20

30

40

50

**【0062】**

図4の回路では、このV<sub>err</sub>3を抑制するために、スイッチSW41, SW43, SW45, SW47をオンからオフ、スイッチSW42, SW44, SW46, SW48をオフからオンに切替え、クランプ電圧V<sub>cpl</sub>1によって式(8)に示した誤差電圧V<sub>err</sub>3を発生させる。そして、再びスイッチSW41, SW43, SW45, SW47をオフからオン、スイッチSW42, SW44, SW46, SW48をオンからオフに切替えることで、発生した誤差電圧V<sub>err</sub>3をさらに(C27//C23)とC22の容量で抑制するようにしている。すなわち、クランプ電圧の切替えによって、式(8)の(V<sub>sigp</sub>-V<sub>sigd</sub>)をさらに式(8)に作用させることとなる。上記と同じ条件の数値を代入すると誤差電圧は、1.7μVとなる。

10

**【0063】**

このようにD相レベル読み出しのときも2つのクランプ電圧発生回路を連続的に切替えることによって、誤差電圧を抑圧することができる。また、指数関数的に誤差電圧を抑制するので、例えば、クランプ電圧発生回路を2つ具備する場合、2倍の容量のコンデンサを用意する必要はない。

**【0064】**

次に、タイミングチャートを用いて図4の回路の、他の例の動作を説明する。図9は、図4の回路の他の例のタイミングチャートである。図9に示す垂直信号線は、画素アレイ回路11の垂直信号線に生じている電圧を示している。また、図に示すSW41～SW60は、図4のスイッチSW41～SW60に対応している。H状態のとき、スイッチSW41～SW60はオンし、L状態のとき、スイッチSW41～SW60はオフする。

20

**【0065】**

図に示すように、垂直信号線にP相レベルの電圧が outputされる前に、スイッチSW49～SW52をオンする。これにより、コンデンサC27～C30とコンデンサC23～C26は直列接続となる。また、スイッチSW41, SW43, SW45, SW47をオフする。

**【0066】**

次いで、スイッチSW54, SW56, SW58, SW60をオン、スイッチSW41, SW43, SW45, SW47をオフし、スイッチSW42, SW44, SW46, SW48をオンする。これによって、コンデンサC27～C30には、クランプ電圧V<sub>cpl</sub>1が充電される。

30

**【0067】**

次いで、スイッチSW54, SW56, SW58, SW60をオフし、スイッチSW53, SW55, SW57, SW59をオンする。すなわち、クランプ電圧発生回路22によって、コンデンサC27～C30にクランプ電圧V<sub>cpl</sub>2を充電する。コンデンサC27～C30には、クランプ電圧発生回路21のクランプ電圧V<sub>cpl</sub>1によりすでに電荷が一部充電されているので、クランプ電圧発生回路22は残りの電荷を充電すればよく、負荷が軽くなっている。よって、コンデンサC27～C30はすばやくクランプ電圧V<sub>cpl</sub>2に充電され誤差電圧を抑制することができる。

**【0068】**

40

垂直信号線の電圧がD相レベル出力の電圧になると、スイッチSW42, SW44, SW46, SW48をオフし、スイッチSW41, SW43, SW45, SW47をオンする。コンデンサC23～C26のコンデンサC27～C30と接続されていない側の端子に供給されるクランプ電圧は、クランプ電圧発生回路21からのクランプ電圧V<sub>cpl</sub>1から、クランプ電圧発生回路22からのクランプ電圧V<sub>cpl</sub>2に切替わる。よって、D相レベルが読み出されるとき垂直信号線の電位が変化し、誤差電圧が発生しても、クランプ電圧発生回路22は、すでにクランプ電圧V<sub>cpl</sub>1によって充放電された電荷のみを補えばよく、誤差電圧が抑制される。

**【0069】**

次いで、スイッチSW49～SW52をオフすることによって、コンデンサC23～C

50

26には、P相レベルとD相レベルの差分の信号、すなわち、画素信号が保持される。スイッチSW61～SW64をオンすれば、コンデンサC23～C26に保持されていた画素信号は、オペアンプZ23から信号電圧Voutとして出力される。

#### 【0070】

このように、P相レベル出力時にスイッチSW42, SW44, SW46, SW48と、スイッチSW41, SW43, SW45, SW47を一度切替えると、そのままD相レベル出力期間になるまでその状態を保ち、D相レベル期間が終わる前に再びスイッチSW42, SW44, SW46, SW48と、スイッチSW41, SW43, SW45, SW47を切替えるようにしても、図5で示したタイミングチャートの動作のときと同様の効果を得ることができる。

10

#### 【0071】

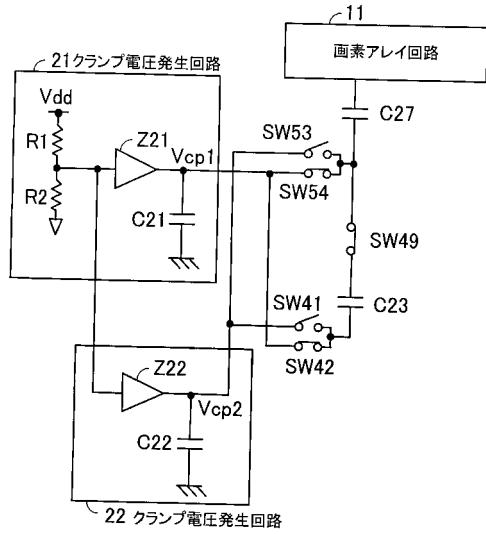

次に第5の実施の形態について説明する。図10は、第5の実施の形態に係る固体撮像装置の回路図である。図10において、図4と同じものには同じ符号を付し、その説明を省略する。

#### 【0072】

図10に示す固体撮像装置は、図4に示した固体撮像装置のコンデンサC23～C26のコンデンサC27～C30と接続されていない側の端子がグランドに接続されている。コンデンサC23～C26の基準をグランドとしても、コンデンサC27～C30に充電するクランプ電圧Vcp1, Vcp2を切替えることによって、P相レベルのタイミングで発生するクランプ電圧の誤差電圧を抑制することができる。なお、この場合、図5に示したタイミングチャートは、スイッチSW41～SW48を削除したものとなる。

20

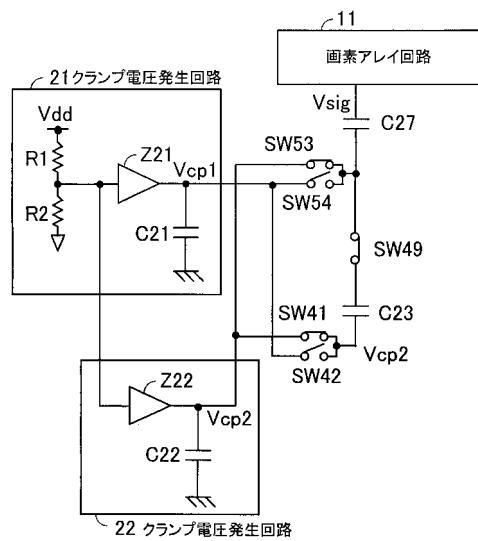

#### 【0073】

次に第6の実施の形態について説明する。図11は、第6の実施の形態に係る固体撮像装置の回路図である。図11において、図10と同じものには同じ符号を付し、その説明を省略する。

#### 【0074】

図11に示す固体撮像装置は、図10に示した固体撮像装置のオペアンプZ23の正相端子に電源による固定の基準電圧Vrefが入力されている。オペアンプZ23の正相端子に固定の基準電圧Vrefが入力されても、コンデンサC27～C30に充電するクランプ電圧Vcp1, Vcp2を切替えることによって、P相レベルのタイミングで発生するクランプ電圧の誤差電圧を抑制することができる。なお、この場合、図5に示したタイミングチャートは、スイッチSW41～SW48を削除したものとなる。

30

#### 【図面の簡単な説明】

#### 【0075】

【図1】第1の実施の形態に係る固体撮像装置の回路図である。

【図2】第2の実施の形態に係る固体撮像装置の回路図である。

【図3】第3の実施の形態に係る固体撮像装置の回路図である。

【図4】第4の実施の形態に係る固体撮像装置の回路図である。

【図5】図4の回路のタイミングチャートである。

【図6】誤差電圧を説明するための回路図その1である。

40

【図7】誤差電圧を説明するための回路図その2である。

【図8】誤差電圧を説明するための回路図その3である。

【図9】図4の回路の他の例のタイミングチャートである。

【図10】第5の実施の形態に係る固体撮像装置の回路図である。

【図11】第6の実施の形態に係る固体撮像装置の回路図である。

【図12】並列出力型CMOSイメージセンサの信号出力回路の回路図である。

【図13】電荷積分回路の回路図である。

【図14】クランプ電圧発生回路の一例を示す。

【図15】クランプ電圧を出力していないときのクランプ電圧発生回路を示した回路図である。

50

【図16】クランプ電圧を出力しているときのクランプ電圧発生回路を示した回路図である。

【符号の説明】

【0076】

1, 11 .....画素アレイ回路、21, 22 .....クランプ電圧発生回路、C1 ~ C7, C11 ~ C19, C21 ~ C31 .....コンデンサ、SW1 ~ SW12, SW21 ~ SW33, SW41 ~ SW65 .....スイッチ、Z1, Z11, Z23 .....オペアンプ、Z21, Z22 .....アンプ、R1, R2 .....抵抗。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

---

フロントページの続き

(56)参考文献 特開2002-252794(JP,A)

特開2001-045325(JP,A)

特開2000-077961(JP,A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/335

H01L 27/146