(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6029020号

(P6029020)

(45) 発行日 平成28年11月24日(2016.11.24)

(24) 登録日 平成28年10月28日(2016.10.28)

(51) Int.Cl.

F 1

|        |         |           |

|--------|---------|-----------|

| HO 1 L | 21/8246 | (2006.01) |

| HO 1 L | 27/105  | (2006.01) |

| HO 1 L | 43/08   | (2006.01) |

| HO 1 L | 43/10   | (2006.01) |

| HO 1 L | 29/82   | (2006.01) |

|        |       |       |

|--------|-------|-------|

| HO 1 L | 27/10 | 4 4 7 |

| HO 1 L | 43/08 | M     |

| HO 1 L | 29/82 |       |

請求項の数 8 (全 20 頁)

(21) 出願番号 特願2013-516265 (P2013-516265)

(86) (22) 出願日 平成24年4月19日 (2012.4.19)

(86) 国際出願番号 PCT/JP2012/061165

(87) 国際公開番号 WO2012/160937

(87) 国際公開日 平成24年11月29日 (2012.11.29)

審査請求日 平成27年3月4日 (2015.3.4)

(31) 優先権主張番号 特願2011-113697 (P2011-113697)

(32) 優先日 平成23年5月20日 (2011.5.20)

(33) 優先権主張国 日本国 (JP)

前置審査

(73) 特許権者 504157024

国立大学法人東北大学

宮城県仙台市青葉区片平二丁目1番1号

(74) 代理人 100095407

弁理士 木村 满

(74) 代理人 100109449

弁理士 毛受 隆典

(74) 代理人 100132883

弁理士 森川 泰司

(74) 代理人 100177149

弁理士 佐藤 浩義

(72) 発明者 深見 俊輔

東京都港区芝五丁目7番1号 日本電気株式会社内

最終頁に続く

(54) 【発明の名称】磁気メモリ素子および磁気メモリ

## (57) 【特許請求の範囲】

## 【請求項 1】

垂直磁気異方性を有する強磁性体から構成される磁化自由層と、

前記磁化自由層と対向して設けられ、垂直磁気異方性を有する強磁性体から構成される

応答層と、

前記応答層に対向して前記磁化自由層とは反対側に設けられ、非磁性体から構成される

非磁性層と、

前記非磁性層に対向して前記応答層とは反対側に設けられ、垂直磁気異方性を有する強

磁性体から構成されるリファレンス層とを具備し、

前記磁化自由層は磁化が互いに反平行方向に固定された第1磁化固定領域と第2磁化固

定領域と、磁化方向が可変な磁化自由領域を具備し、

前記応答層は0.9 nmから1.3 nmの厚さを有し、

前記応答層、前記非磁性層、前記リファレンス層は、前記磁化自由層と電気的に分離さ

れ、

前記磁化自由領域の中心から前記応答層の中心までの距離が5 nm以上15 nm以下で

ある、

ことを特徴とする磁気メモリ素子。

## 【請求項 2】

垂直磁気異方性を有する強磁性体から構成される磁化自由層と、

前記磁化自由層と対向して設けられ、垂直磁気異方性を有する強磁性体から構成される

10

20

応答層と、

前記応答層に対向して前記磁化自由層とは反対側に設けられ、非磁性体から構成される非磁性層と、

前記非磁性層に対向して前記応答層とは反対側に設けられ、垂直磁気異方性を有する強磁性体から構成されるリファレンス層とを具備し、

前記磁化自由層は磁化が互いに反平行方向に固定された第1磁化固定領域と第2磁化固定領域と、磁化方向が可変な磁化自由領域を具備し、

前記応答層は0.9nmから1.3nmの厚さを有し、

前記応答層、前記非磁性層、前記リファレンス層は、前記磁化自由層と電気的に分離され、

前記応答層の幅が前記磁化自由層の幅より大きい、

ことを特徴とする磁気メモリ素子。

## 【請求項3】

前記第1磁化固定領域、及び／又は前記第2磁化固定領域と磁気的に結合するように設けられ、前記第1磁化固定領域、及び／又は前記第2磁化固定領域の磁化を固定する磁化固定層を有することを特徴とする請求項1または2に記載の磁気メモリ素子。

## 【請求項4】

前記応答層は前記磁化自由領域の表裏面のいずれかに設けられることを特徴とする請求項1～3のいずれか一項に記載の磁気メモリ素子。

## 【請求項5】

前記応答層は、CoFeBを含有することを特徴とする請求項1～4のいずれか一項に記載の磁気メモリ素子。

## 【請求項6】

前記応答層がCoFeBとFeの積層構成を有することを特徴とする請求項1～4のいずれか一項に記載の磁気メモリ素子。

## 【請求項7】

前記非磁性層は、MgOを含有することを特徴とする請求項1～6のいずれか一項に記載の磁気メモリ素子。

## 【請求項8】

請求項1～7のいずれか一項に記載の磁気メモリ素子を有することを特徴とする磁気メモリ。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、磁気メモリ素子および磁気メモリに関する。特に本発明は磁壁移動を利用し、垂直磁気異方性を有する材料により構成された磁気メモリ素子および当該磁気メモリ素子を用いた磁気メモリに関する。

## 【背景技術】

## 【0002】

磁気メモリ、又は磁気ランダムアクセスメモリ(Magnetic Random Access Memory; MRAM)は高速動作、および無限回の書き換えが可能な不揮発性メモリであり、既に一部で実用化が始まり、またより汎用性を高めるための開発が行われている。MRAMでは記憶素子として磁性体を用い、磁性体の磁化の向きに対応させて情報を記憶する。この磁性体の磁化をスイッチングさせる方法としていくつかの方式が提案されているが、いずれも電流を使う点では共通している。MRAMを実用化する上では、この書き込み電流をどれだけ小さくできるかが非常に重要であり、非特許文献1によれば書き込み電流の0.5mA以下への低減、さらに好ましくは0.2mA以下への低減が求められている(非特許文献1)。これは書き込み電流が0.2mA程度まで低減されると、非特許文献1で提案されている2T-1MTJ(two transistor

10

20

30

40

50

s - one magnetic tunnel junction)回路構成において最小レイアウトが可能となり、DRAM、SRAMなどの既存の揮発性メモリと同等以上のコストパフォーマンスを実現できるためである。

MRAMへの情報の書き込み方法のうちで最も一般的なのは、磁性記憶素子の周辺に書き込みのための配線を配置し、この配線に電流を流すことで発生する磁場によって磁性記憶素子の磁化の方向をスイッチングさせる方法である。この方法は磁場による磁化反転となるため、原理的には1ナノ秒以下の書き込みが可能であり、高速MRAMを実現する上では好適である。しかしながら熱安定性、外乱磁場耐性が確保された磁性体の磁化をスイッチングするための磁場は一般的には数100e(エールステッド、 $100\text{e} = 795 \cdot 77 \text{ A/m}$ )程度となり、このような磁場を発生させるためには数mA程度の電流が必要となる。この場合、チップ面積が大きくならざるを得ず、また書き込みに要する消費電力も増大するため、他のランダムアクセスメモリと比べて競争力で劣ることになる。これに加えて、素子が微細化されると、書き込み電流はさらに増大してしまい、スケーリングの点でも好ましくない。10

近年このような問題を解決する手段として、以下の2つの方法が提案されている。1つ目はスピン注入磁化反転である。これは反転可能な磁化を有する第1の磁性層(磁化自由層)と、それに電気的に接続され、磁化が固定された第2の磁性層(リファレンス層)から構成された積層膜において、第2の磁性層(リファレンス層)と第1の磁性層(磁化自由層)の間で電流を流したときのスピン偏極した伝導電子と第1の磁性層(磁化自由層)中の局在電子との間の相互作用を利用して第1の磁性層(磁化自由層)の磁化を反転する方法である。読み出しの際には第1の磁性層(磁化自由層)と第2の磁性層(リファレンス層)の間で発現される磁気抵抗効果を利用する。従ってスピン注入磁化反転方式を用いたMRAMは2端子の素子となる。スピン注入磁化反転はある電流密度以上のときに起こることから、素子のサイズが小さくなれば、書き込みに要する電流は低減される。すなわちスピン注入磁化反転方式はスケーリング性に優れていると言うことができる。しかしながら、一般的に第1の磁性層(磁化自由層)と第2の磁性層(リファレンス層)の間には非磁性層が設けられ、書き込みの際には比較的大きな電流をこの非磁性層に流さなければならず、書き換え耐性や信頼性が課題となる。また、書き込みの電流経路と読み出しの電流経路が同じになることから、読み出しの際の誤書き込みも懸念される。このようにスピン注入磁化反転はスケーリング性には優れるものの、実用化にはいくつかの障壁がある。20

一方で2つ目の方である電流誘起磁壁移動現象を利用した磁化反転方法は、スピン注入磁化反転の抱える上述のような問題を解決することができる。電流誘起磁壁移動現象を利用したMRAMは例えば特許文献1で開示されている(特許文献1)。電流誘起磁壁移動現象を利用したMRAMは、一般的には反転可能な磁化を有する第1の磁性層(磁化自由層)において、その両端部の磁化が互いに反平行となるように固定されている。このような磁化配置のとき、第1の磁性層内には磁壁が導入される。ここで、非特許文献2で報告されているように、磁壁を貫通する方向に電流を流したとき、磁壁は伝導電子の方向に移動することから、第1の磁性層(磁化自由層)内に電流を流すことにより書き込みが可能となる(非特許文献2)。情報を読み出す際には、磁壁が移動する領域に設けられる磁気トンネル接合(Magnetic Tunnel Junction; MTJ)を用い、磁気抵抗効果により読み出しを行う。従って、電流誘起磁壁移動方式を利用したMRAMは3端子の素子となり、上述の非特許文献1で提案されている2T-1MTJ構成とも整合する。電流誘起磁壁移動も、ある電流密度以上のときに起こることから、スピン注入磁化反転と同様にスケーリング性があると言える。これに加えて、電流誘起磁壁移動を利用したMRAM素子では、書き込み電流が磁気トンネル接合中の非磁性層を流れることはなく、また書き込み電流経路と読み出し電流経路は別となるため、スピン注入磁化反転で挙げられるような上述の問題は解決されることになる。30

また非特許文献2では電流誘起磁壁移動に必要な電流密度として $1 \times 10^{-8} [\text{A}/\text{cm}^2]$ 程度を要している。この場合、例えば磁壁移動の起こる層(磁化自由層)の幅を100nm、膜厚を10nmとした場合の書き込み電流は1mAとなる。これは前述の書き40

込み電流に関する条件を満たすことができない。一方で、非特許文献3で述べられているように、電流誘起磁壁移動が起こる強磁性層（磁化自由層）として垂直磁気異方性を有する材料を用いることによって、書き込み電流を十分小さく低減できることが報告されている（非特許文献3）。このようなことから、電流誘起磁壁移動を利用してMRAMを製造する場合、磁壁移動が起こる層（磁化自由層）としては垂直磁気異方性を有する強磁性体を用いることが好ましいと言える。

磁化自由層に垂直磁気異方性を有する強磁性体を用いたMRAMの構成は、特許文献2、特許文献3に開示されている（特許文献2、3）。

#### 【先行技術文献】

##### 【特許文献】

10

##### 【0003】

【特許文献1】特開2005-191032号公報

【特許文献2】国際公開第2009/001706号

【特許文献3】国際公開第2009/060749号

##### 【非特許文献】

##### 【0004】

【非特許文献1】Sakimura et al., "MRAM Cell Technology for Over 500-MHz SoC", IEEE Journal of Solid-State Circuits, 2007, vol. 42, p. 830.

20

【非特許文献2】Yamaguchi et al., "Real-Space Observation of Current-Driven Domain Wall Motion in Submicron Magnetic Wires", Physical Review Letters, 2004, vol. 92, p 077205.

【非特許文献3】Fukami et al., "Micromagnetic analysis of current driven domain wall motion in nanostrips with perpendicular magnetic anisotropy", Journal of Applied Physics, 2008, vol. 103, p. 07E718.

#### 【発明の概要】

30

#### 【発明が解決しようとする課題】

##### 【0005】

特許文献2に開示されているMRAMにおいては、電流誘起磁壁移動による書き込みを行う磁化自由層に対して、読み出しを行うための非磁性層、リファレンス層が隣接している。書き込み電流低減等の書き込み特性の向上のためには、磁化自由層の材料、構成を適切に設計する必要がある。一方、読み出し信号量増大等の読み出し特性の向上のためには、磁化自由層、非磁性層、リファレンス層の構造、構成を適切に設計する必要がある。すなわち、磁化自由層は書き込み特性、読み出し特性の両方の要請を満たすように設計する必要があるということが言える。これは書き込み特性、読み出し特性の片方の要請を満たすように設計する場合と比べて、設計の自由度が低くなり、特性の向上が困難となる。

40

一方、特許文献3に開示されているMRAMにおいては、書き込みは磁化自由層内で行われ、磁化自由層の磁化方向をセンシングするための面内磁気異方性を有するソフトな応答層が設けられ、それに隣接して非磁性層、リファレンス層が設けられている。さらに、応答層は磁化自由層からの漏洩磁界をセンシングするために基板平行面内において磁化自由層からずれるようにして設けられている。特許文献3で開示されている構造では、書き込み特性は磁化自由層の設計により向上可能である。一方読み出し特性は応答層、非磁性層、リファレンス層からなるMTJの設計により向上可能である。すなわち、書き込み特性と読み出し特性の独立な設計が可能である。その一方で、この構造を形成するために必要なプロセス数は特許文献2に開示されている構造を形成するために必要なプロセス数と比べて多くなる。また応答層の磁化自由層に対する基板平行面内のズレ量も適切に調整

50

する必要があり、これはプロセスマージンの低下、微細化の困難化を招く。さらにセル面積も増大し、コストの増大を招く。

すなわち、特許文献2に開示されているMRAM素子は良好な書き込み特性と読み出し特性の両立が難しく、一方特許文献3に開示されているMRAM素子はプロセスマージン、低コスト化の点でデメリットがある。

本発明の目的は、特許文献2に開示されたMRAM素子の有する書き込み特性と読み出し特性の独立な設計が困難であるという問題点を解決し、また特許文献3に開示されたMRAM素子が有するプロセス数の増大、プロセスマージンの低下、セル面積の増大などの問題も解決することのできる磁気メモリ素子を提供することにある。

より端的に言えば、本発明の目的は、書き込み特性と読み出し特性の独立した設計が可能で、かつプロセス数の増大、プロセスマージンの低下、セル面積の増大が生じない磁気メモリ素子を提供することにある。10

#### 【課題を解決するための手段】

##### 【0006】

前述した目的を達成するために、本発明の第1の態様は、垂直磁気異方性を有する強磁性体から構成される磁化自由層と、前記磁化自由層と対向して設けられ、垂直磁気異方性を有する強磁性体から構成される応答層と、前記応答層に対向して前記磁化自由層とは反対側に設けられ、非磁性体から構成される非磁性層と、前記非磁性層に対向して前記応答層とは反対側に設けられ、垂直磁気異方性を有する強磁性体から構成されるリファレンス層とを具備し、前記磁化自由層は磁化が互いに反平行方向に固定された第1磁化固定領域と第2磁化固定領域と、磁化方向が可変な磁化自由領域を具備し、前記応答層は0.9nmから1.3nmの厚さを有し、前記応答層、前記非磁性層、前記リファレンス層は、前記磁化自由層と電気的に分離され、前記磁化自由領域の中心から前記応答層の中心までの距離が5nm以上15nm以下である、ことを特徴とする磁気メモリ素子である。20

本発明の第2の態様は、垂直磁気異方性を有する強磁性体から構成される磁化自由層と、前記磁化自由層と対向して設けられ、垂直磁気異方性を有する強磁性体から構成される応答層と、前記応答層に対向して前記磁化自由層とは反対側に設けられ、非磁性体から構成される非磁性層と、前記非磁性層に対向して前記応答層とは反対側に設けられ、垂直磁気異方性を有する強磁性体から構成されるリファレンス層とを具備し、前記磁化自由層は磁化が互いに反平行方向に固定された第1磁化固定領域と第2磁化固定領域と、磁化方向が可変な磁化自由領域を具備し、前記応答層は0.9nmから1.3nmの厚さを有し、前記応答層、前記非磁性層、前記リファレンス層は、前記磁化自由層と電気的に分離され、前記応答層の幅が前記磁化自由層の幅より大きい、ことを特徴とする磁気メモリ素子である。30

本発明の第3の態様は、第1又は第2の態様に記載の磁気メモリ素子を有することを特徴とする磁気メモリである。

#### 【発明の効果】

##### 【0007】

本発明によれば、書き込み特性と読み出し特性の独立した設計が可能で、かつプロセス数の増大、プロセスマージンの低下、セル面積の増大が生じない磁気メモリ素子を提供することができる。40

#### 【図面の簡単な説明】

##### 【0008】

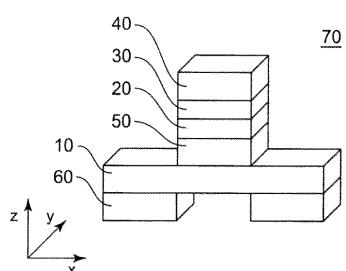

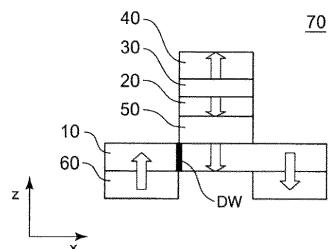

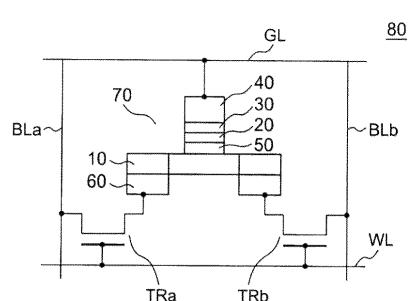

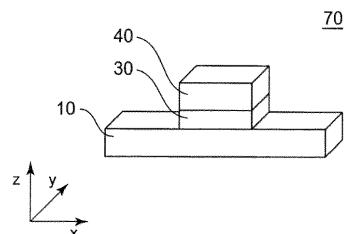

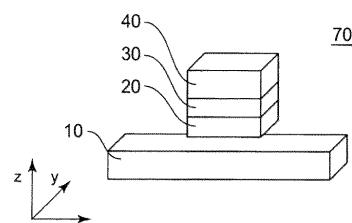

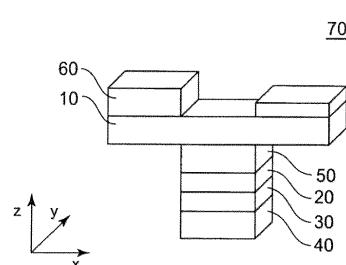

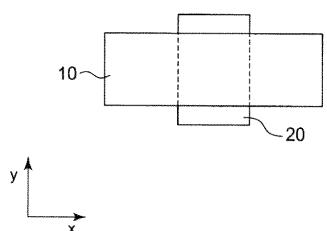

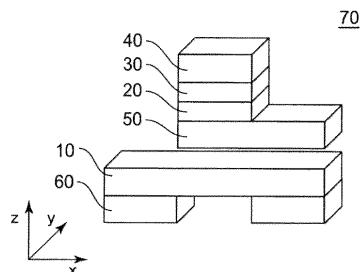

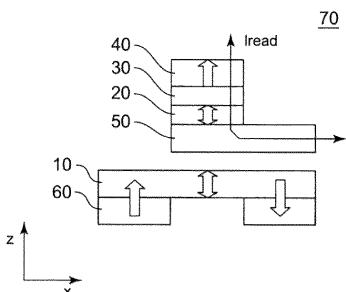

図1Aは磁気メモリ素子70の構造を示す斜視図である。

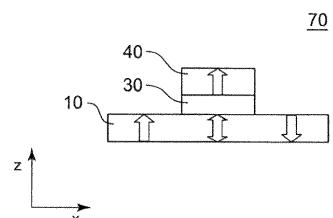

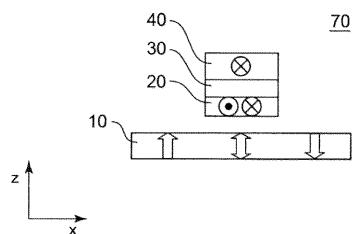

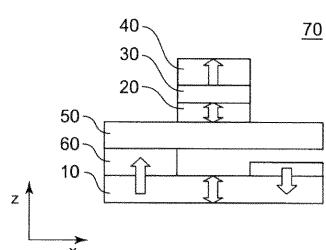

図1Bは図1Aのx-z断面図であって、矢印は磁化の向きを示している。

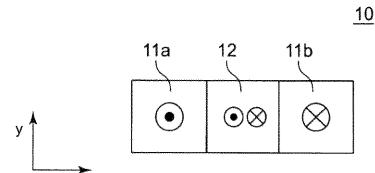

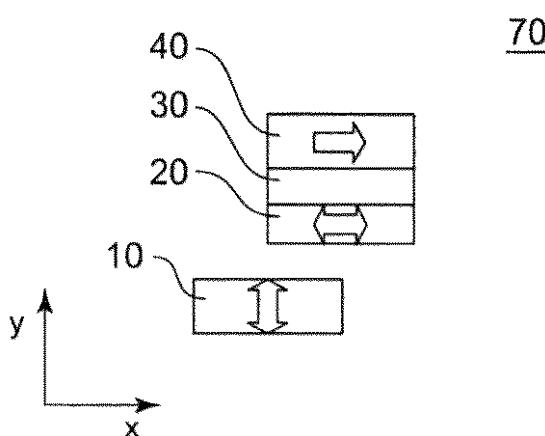

図1Cは図1Aの磁化自由層10のx-y平面図である。

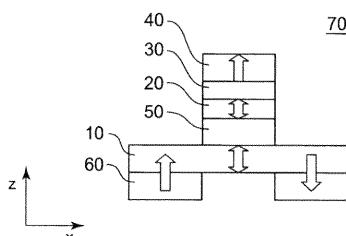

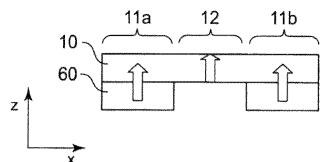

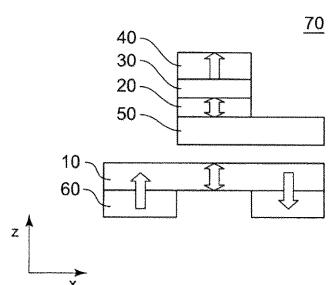

図2Aは磁気メモリ素子70が“0”状態における磁化の状態を示す図である。

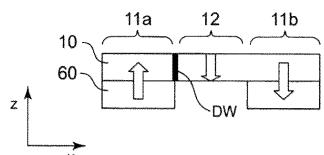

図2Bは磁気メモリ素子70が“1”状態における磁化の状態を示す図である。

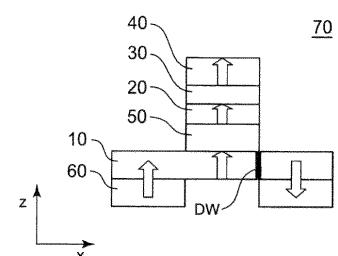

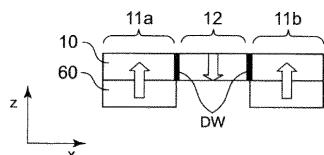

図3Aは磁気メモリ素子70のメモリ状態の初期化方法の一例を模式的に示す図である。

図 3 B は磁気メモリ素子 7 0 のメモリ状態の初期化方法の一例を模式的に示す図である。

図 3 C は磁気メモリ素子 7 0 のメモリ状態の初期化方法の一例を模式的に示す図である。

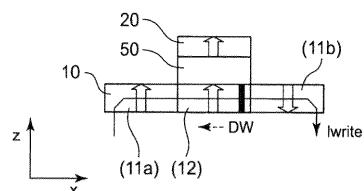

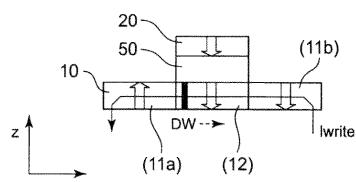

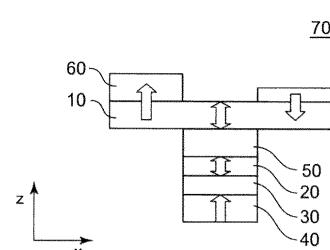

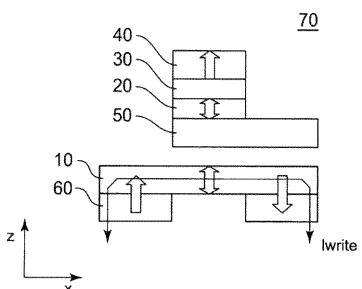

図 4 A は磁気メモリ素子 7 0 への情報の書き込み方法を示す図である。

図 4 B は磁気メモリ素子 7 0 への情報の書き込み方法を示す図である。

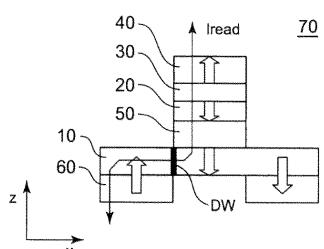

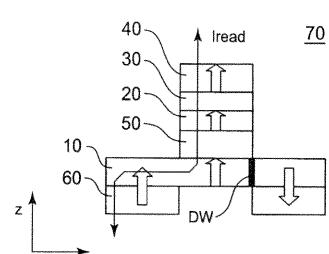

図 5 A は磁気メモリ素子 7 0 からの情報の読み出し方法を模式的に示す図である。

図 5 B は磁気メモリ素子 7 0 からの情報の読み出し方法を模式的に示す図である。

図 6 は磁気メモリ素子 7 0 からの情報の読み出し方法を模式的に示す図である。

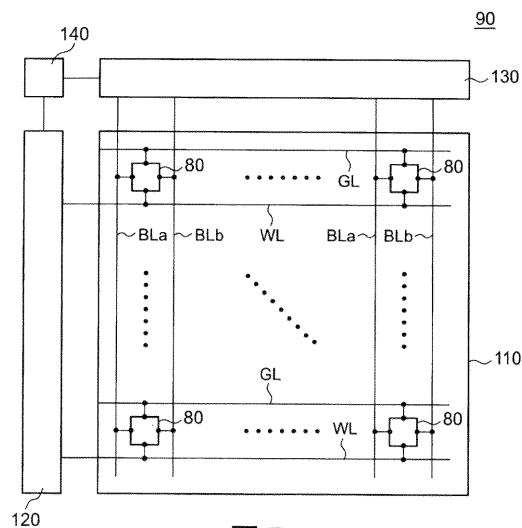

図 7 は磁気メモリ 9 0 の構成の一例を示すブロック図である。

10

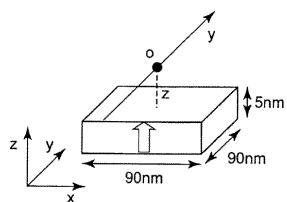

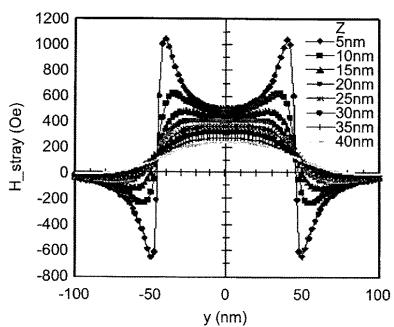

図 8 A は磁化自由領域 1 2 からの漏洩磁界の計算結果を示す図である。

図 8 B は磁化自由領域 1 2 からの漏洩磁界の計算結果を示す図である。

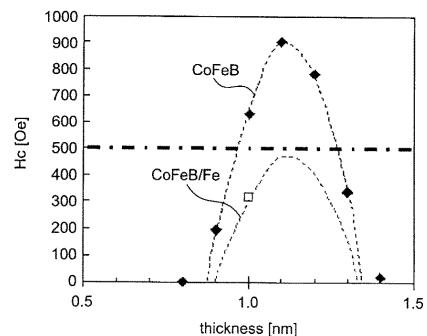

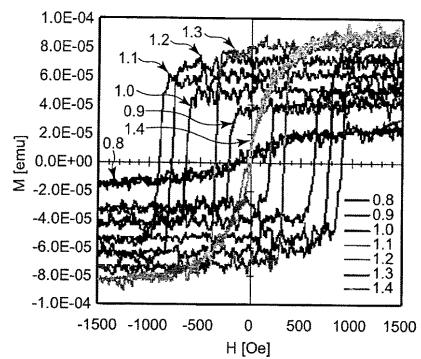

図 9 A は基板 / T a / C o F e B / M g O / T a 積層膜をドット状に加工したサンプルの磁化曲線を示す図であって、図中の数字 0 . 8 ~ 1 . 4 は C o F e B の膜厚 ( n m ) を意味している。

図 9 B は基板 / T a / C o F e B / M g O / T a 積層膜保磁力の C o F e B 膜厚依存性の測定結果を示す図であって、C o F e B の代わりに C o F e B と F e の積層膜を用いたものの測定点もプロットされている。

図 10 A は特許文献 2 に公開されている磁気メモリ素子の構造を模式的に示す斜視図であって、図中の符号は本発明に対応させてある。

20

図 10 B は特許文献 2 に公開されている磁気メモリ素子の構造を模式的に示す断面図であって、図中の符号は本発明に対応させてある。

図 11 A は特許文献 3 に公開されている磁気メモリ素子の構造を模式的に示す斜視図であって、図中の符号は本発明に対応させてある。

図 11 B は特許文献 3 に公開されている磁気メモリ素子の構造を模式的に示す断面図であって、図中の符号は本発明に対応させてある。

図 11 C は特許文献 3 に公開されている磁気メモリ素子の構造を模式的に示す断面図であって、図中の符号は本発明に対応させてある。

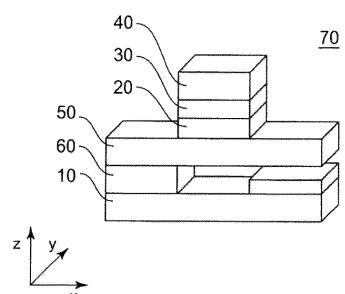

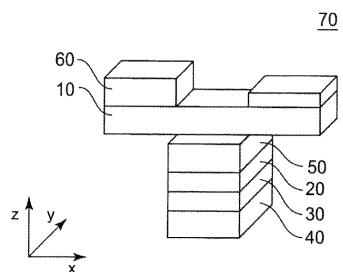

図 12 A は磁気メモリ素子 7 0 の第 1 の変形例の構造を模式的に示す斜視図である。

図 12 B は磁気メモリ素子 7 0 の第 1 の変形例の構造を模式的に示す断面図である。

30

図 13 A は磁気メモリ素子 7 0 の第 2 の変形例の構造を模式的に示す斜視図である。

図 13 B は磁気メモリ素子 7 0 の第 2 の変形例の構造を模式的に示す断面図である。

図 14 A は磁気メモリ素子 7 0 の第 2 の変形例の構造を模式的に示す斜視図である。

図 14 B は磁気メモリ素子 7 0 の第 2 の変形例の構造を模式的に示す平面図である。

図 15 A は磁気メモリ素子 7 0 の第 3 の変形例の構造を模式的に示す斜視図である。

図 15 B は磁気メモリ素子 7 0 の第 3 の変形例の構造を模式的に示す断面図である。

図 16 A は図 15 A および図 15 B に示された構造を有する磁気メモリ素子 7 0 における、書き込み電流の経路を示す図である。

図 16 B は図 15 A および図 15 B に示された構造を有する磁気メモリ素子 7 0 における、読み出し電流の経路を示す図である。

40

#### 【発明を実施するための形態】

##### 【0 0 0 9】

以下、図面に基づいて本発明に好適な実施形態を詳細に説明する。

##### (構造)

図 1 A ~ C は本発明に係る磁気メモリ素子 7 0 の主要な部分の代表的な構造を模式的に示している。図 1 A はその斜視図を、図 1 B は x - z 断面図を、図 1 C は磁化自由層 1 0 の x - y 平面図を示している。なお、図に示されている x - y - z 座標系において、z 軸は基板垂直方向を示し、x - y 軸は基板平面に平行であるものとする。

本発明に係る磁気メモリ素子 7 0 は少なくとも磁化自由層 1 0 、磁化自由層 1 0 と隣接して(対向して)設けられる応答層 2 0 、応答層 2 0 に隣接して(対向して)磁化自由層

50

10とは反対側に設けられる非磁性層30、非磁性層30に隣接して(対向して)応答層20とは反対側に設けられるリファレンス層40を具備する。また必須ではないが、応答層20と磁化自由層10の間に、応答層10に隣接して(対向して)設けられる導電層50、磁化自由層10に隣接して(対向して)設けられる磁化固定層60を具備することが好ましい。磁化自由層10、応答層20、リファレンス層40、磁化固定層60は強磁性体から構成される。図1B、図1Cにおいては、磁化の向きの例が矢印で示されている。

図1Cは磁化自由層10の構造を模式的に示した平面図である。磁化自由層10は垂直磁気異方性を有する強磁性体から構成される。また、磁化自由層10は第1磁化固定領域11a、第2磁化固定領域11b、及び磁化自由領域12の3つの領域から構成される。

第1磁化固定領域11a、第2磁化固定領域11bは実質的に一方向に固定された磁化を有する。また第1磁化固定領域11a、第2磁化固定領域11bの磁化は互いに反平行な向きに固定されている。図1Cでは第1磁化固定領域11a、第2磁化固定領域11bはそれぞれ+ z方向、- z方向に固定されているものとして描かれている。磁化自由領域12の磁化は反転可能である。この場合+ z、- zのいずれかの方向を向くことができる。

磁化自由層10内の3つの領域が上述のような磁化構造であるとき、磁化自由領域12の磁化方向に応じて、第1磁化固定領域11aと磁化自由領域12の境界、および第2磁化固定領域11bと磁化自由領域12の境界のいずれか一方に磁壁が形成される。図1Cの場合、磁化自由領域12の磁化が+ z方向のとき、第2磁化固定領域11bと磁化自由領域12の境界に磁壁が形成され、磁化自由領域12の磁化が- z方向のとき、第1磁化固定領域11aと磁化自由領域12の境界に磁壁が形成される。

また、図1A～図1Cに示される実施の形態においては、第1磁化固定領域11aは磁化自由領域12の一方の端部に隣接し、第2磁化固定領域11bは磁化自由領域12の別の端部に隣接する。具体的には、図1Cの例では、第1磁化固定領域11aは磁化自由領域12の- x方向側の端部に隣接し、第2磁化固定領域11bは磁化自由領域12の+ x方向側の端部に隣接している。しかし一般的には、第1磁化固定領域11a、第2磁化固定領域11bは磁化自由領域12に接続されればよく、それらの間での位置関係には任意性がある。例えば、第1磁化固定領域11aが磁化自由領域12の一方の端部に接続され、また第2磁化固定領域11bも磁化自由領域12の前記一方の端部に接続されてもよい。この場合には磁化自由層10は三叉路を有する構造となる。

また図1A～図1Cに示される実施の形態においては、応答層20、非磁性層30、リファレンス層40はこの順に積層して設けられる。応答層20、リファレンス層40は強磁性体から構成される。また非磁性層30は非磁性体から構成され、好適には絶縁体から構成される。このとき、応答層20、非磁性層30、リファレンス層40の3つの層の積層体によって磁気トンネル接合(Magnetic Tunnel Junction; MTJ)が構成される。

応答層20は垂直磁気異方性を有する強磁性体から構成される。またその磁化は反転可能であり、+ z方向、または- z方向のいずれかの方向を向く。また応答層20は前記磁化自由領域12と強磁性的に結合しており、磁化自由領域12の磁化方向に応じて、応答層20の磁化方向が決定される。応答層20は磁化自由領域12の上部または下部に設けられ、x-y面内において、オーバーラップするように形成される。

リファレンス層40は垂直磁気異方性を有する強磁性体から構成され、かつ実質的に一方向に固定された磁化を有する。図1Bの例ではリファレンス層40の磁化は+ z方向に固定されている。また図示されていないが、リファレンス層40は以下のような積層構造を有していてもよい。例えばリファレンス層40は強磁性体、非磁性体、強磁性体の3層がこの順に積層された構造を有していてもよい。ここで2つの強磁性体に挟まれた非磁性体は上下の強磁性体を反平行方向に磁気結合させる(積層フェリ結合させる)機能を有していることが好ましい。このような機能を有する非磁性体としてはRuが知られている。リファレンス層40を積層フェリ結合を有する積層構造にすることによって、外部への漏洩磁界を低減し、磁化自由層10などのその他の層への磁気的な影響を低減することができる。

10

20

30

40

50

きる。これに加えて、リファレンス層には反強磁性体が隣接していてもよい。これは、反強磁性体を隣接させ、磁場中で熱処理を行うことによって界面の磁化方向を一方向に固定することができるためである。代表的な反強磁性体としては Pt - Mn、Ir - Mnなどが例示される。

磁化固定層 60 は少なくとも 1 つ設けられる。図 1 A ~ 図 1 C に示される実施の形態においては、磁化固定層 60 は 2 つ設けられており、それぞれ第 1 磁化固定領域 11a、第 2 磁化固定領域 11b に隣接して設けられている。磁化固定層 60 は第 1 磁化固定領域 11a、第 2 磁化固定領域 11b の磁化の方向を上述のように互いに反平行となる向きに向けた上でその向きに固定する役割を有する。その意味で、磁化固定層 60 は磁化自由層 10 と磁気的に結合していればよく、必ずしも隣接して設けられる必要はない。また磁化自由層 10 の第 1 磁化固定領域 11a と第 2 磁化固定領域 11b の磁化が互いに反平行で固定されさえすれば、磁化固定層 60 は必ずしも設けられる必要はない。

10

導電層 50 は磁化自由層 10 と応答層 20 の間に設けられている。導電層 50 は導電性の材料から構成され、磁化自由層 10 と応答層 20 を電気的に接続する。

また図 1 A ~ 図 1 C には示されていないが、第 1 磁化固定領域 11a、第 2 磁化固定領域 11b はそれぞれ異なる外部の配線に接続され、またリファレンス層 40 は別の外部の配線へと接続される。すなわち、当該磁気メモリ素子 70 は 3 端子の素子となる。なお、第 1 磁化固定領域 11a、第 2 磁化固定領域 11b と外部の配線の経路、及びリファレンス層 40 と外部の配線の経路には別の層が挿入されても構わない。例えば、これらの層と外部の配線との間に導電性のコンタクト層が設けられることが好ましい。また例えば第 1 磁化固定領域 11a と第 2 磁化固定領域 11b は磁化固定層 60 を介して外部の配線に接続されても構わない。

20

#### (メモリ状態)

次に本発明に係る磁気メモリ素子 70 のメモリ状態について説明する。

図 2 A および図 2 B はそれぞれ、本発明に係る磁気メモリ素子 70 の “0”、“1” それぞれのメモリ状態における磁化の状態の例を模式的に示している。図 2 A は “0” 状態における磁化の状態を、図 2 B は “1” 状態における磁化の状態を示している。なおここでは第 1 磁化固定領域 11a の磁化は +z 方向に固定され、第 2 磁化固定領域 11b の磁化は -z 方向に固定されているものとしている。

いま、図 2 A に示されるような “0” 状態においては、磁化自由領域 12、及び応答層 20 の磁化は +z 方向成分を有している。このとき第 2 磁化固定領域 11b との境界に磁壁 DW が形成される。一方、図 2 B に示されるような “1” 状態においては、磁化自由領域 12、及び応答層 20 の磁化は -z 方向成分を有している。このとき第 1 磁化固定領域 11a との境界に磁壁 DW が形成される。

30

図 2 A および図 2 B ではリファレンス層 40 の磁化は +z 方向に固定されているものとして描かれている。このとき図 2 A に示される “0” 状態、及び図 2 B に示される “1” 状態において、応答層 20、非磁性層 30、及びリファレンス層 40 から形成される MTJ の磁化配置は、それぞれ平行、反平行となる。従って、当該 MTJ に電流を通じたときにはそれぞれ相対的に低抵抗、高抵抗が実現される。

なお、図 2 A、図 2 B で定義された磁化状態とメモリ状態 (“0”、“1”) の間の対応には任意性があり、この限りではないことは明らかである。

40

#### (動作方法)

##### 1. 初期化方法

次に本発明に係る磁気メモリ素子 70 のメモリ状態の初期化方法について説明する。なお、ここで言う初期化とは、第 1 磁化固定領域 11a と第 2 磁化固定領域 11b の磁化を互いに反平行方向になるように向け、磁化自由層 10 に单一の磁壁を導入するプロセスのことを意味する。

図 3 A ~ 図 3 C は本発明に係る磁気メモリ素子 70 のメモリ状態の初期化方法の一例を模式的に示している。なお、図 3 A ~ 図 3 C では簡単のために磁化自由層 10 と磁化固定層 60 以外の層は省略されている。図 3 A ~ 図 3 C においては、第 1 磁化固定領域 11a

50

側は第2磁化固定領域11b側に比べてハードであるものとしている。

図3A～図3Cに示された初期化方法の例においては、以下の手順で外部磁界を印加することによりメモリ状態の初期化を行う。はじめに+z方向に十分大きな外部磁界を印加する。このとき、図3Aに示されるように、全領域の磁化は+z方向を向く。次に比較的小さな外部磁界を-z方向に印加する。このとき図3Bに示されるように磁化自由領域12の磁化がはじめに反転し、-z方向を向く。続いて-z方向の外部磁界をやや強くする。このとき図3Cに示されるように第2磁化固定領域11b側の磁化が反転し、-z方向を向く。図3Cに示された状態は第1磁化固定領域11aと磁化自由領域12の境界に磁壁DWがトラップされた状態であり、これは図2Bの“1”状態に一致する。このように外部磁界を印加することによって当該磁気メモリ素子70のメモリ状態を初期化することが可能となる。10

## 2. 書き込み方法

次に本発明に係る磁気メモリ素子70への情報の書き込み方法について説明する。

図4Aおよび図4Bは本発明に係る磁気メモリ素子70への情報の書き込み方法を模式的に示している。なお、図4Aおよび図4Bでは簡単のために磁化自由層10、導電層50、応答層20以外の層は省略されている。いま、図2Aで定義された“0”状態において図4Aに示すように、矢印I<sub>w r i t e</sub>で示された方向に電流を導入する。このとき伝導電子は磁化自由層10において第2磁化固定領域11bから磁化自由領域12を経由して第1磁化固定領域11aへと流れる。このとき第2磁化固定領域11bと磁化自由領域12の境界に形成された磁壁DWにはスピントランスファートルク(Spin Transfer Torque; STT)が働き、x軸の負方向に移動する。すなわち電流誘起磁壁移動が起こる。ここで、第1磁化固定領域11aの磁化は固定されているため、磁壁DWは第1磁化固定領域11aと磁化自由領域12の境界で停止する。またこのとき磁化自由領域12の磁化の反転に伴い、応答層20の磁化も-x方向に反転する。この状態は図2Bで定義された“1”状態に相当する。このようにして“1”書き込みを行うことができる。20

また図2Bで定義された“1”状態において図4Bに示すように、矢印I<sub>w r i t e</sub>で示された方向に電流を導入する。このとき伝導電子は磁化自由層10において第1磁化固定領域11aから磁化自由領域12を経由して第1磁化固定領域11aへと流れる。このとき第2磁化固定領域11bと磁化自由領域12の境界に形成された磁壁DWにはスピントランスファートルク(Spin Transfer Torque; STT)が働き、x軸の正方向に移動する。すなわち電流誘起磁壁移動が起こる。ここで、第2磁化固定領域11bの磁化は固定されているため、磁壁DWは第2磁化固定領域11bと磁化自由領域12の境界で停止する。またこのとき磁化自由領域12の磁化の反転に伴い、応答層20の磁化も+x方向に反転する。この状態は図2Aで定義された“0”状態に相当する。このようにして“0”書き込みを行うことができる。30

なお、“0”状態における“0”書き込み、及び“1”状態における“1”書き込みを行った場合には状態の変化は起こらない。すなわちオーバーライトが可能である。

## 3. 読み出し方法

次に本発明に係る磁気メモリ素子70からの情報の読み出し方法について説明する40

図5Aおよび図5Bは図1A～図1Cに示された構成を有する磁気メモリ素子70からの情報の読み出し方法を模式的に示している。本発明においては主にトンネル磁気抵抗効果(Tunneling Magneto resistive effect; TMR effect)を利用して情報の読み出しを行う。そのために応答層20、非磁性層30、リファレンス層40から構成される磁気トンネル接合(MTJ)を貫通する方向に電流I<sub>r e a d</sub>を導入する。なおこのI<sub>r e a d</sub>の方向には任意性がある。

いま、図5Aに示されるように図2Aで定義された“0”状態においてI<sub>r e a d</sub>を導入したとき、当該MTJにおいて磁化は平行状態となっているので、相対的に低抵抗が実現される。また図5Bに示されるように図2Bで定義された“1”状態においてI<sub>r e a d</sub>を導入したとき、当該MTJにおいて磁化は反平行状態となっているので、相対的に高50

抵抗が実現される。このようにして、当該磁気メモリ素子 70 に格納された情報は抵抗値の差として検出することができる。

#### (回路構成)

次に、本発明に係る磁気メモリ素子 70 を有する磁気メモリセル 80 に書き込み電流及び読み出し電流を導入するための回路構成について説明する。

図 6 は、磁気メモリセル 80 の 1 ビット分の回路の構成例を示している。図 6 に示される例では、磁気メモリ素子 70 は 3 端子の素子であり、ワード線 WL、グラウンド線 GL、及びビット線対 BLa、BLb に接続されている。例えば、リファレンス層 40 につながる端子は、読み出しのためのグラウンド線 GL に接続されている。第 1 磁化固定領域 11a につながる端子は、トランジスタ TRa のソース / ドレインの一方に接続され、ソース / ドレインの他方は、ビット線 BLa に接続されている。第 2 磁化固定領域 11b につながる端子は、トランジスタ TRb のソース / ドレインの一方に接続され、ソース / ドレインの他方は、ビット線 BLb に接続されている。トランジスタ TRa、TRb のゲートは、共通のワード線 WL に接続されている。

10

データ書き込み時、ワード線 WL は High レベルに設定され、トランジスタ TRa、TRb が ON される。また、ビット線対 BLa、BLb のいずれか一方が High レベルに設定され、他方が Low レベル（グラウンドレベル）に設定される。その結果、トランジスタ TRa、TRb、磁化自由層 10 を経由して、ビット線 BLa とビット線 BLb との間で書き込み電流が流れれる。

データ読み出し時、ワード線 WL は High レベルに設定され、トランジスタ TRa、TRb が ON される。また、ビット線 BLa はオープン状態に設定され、ビット線 BLb は High レベルに設定される。その結果、読み出し電流が、ビット線 BLb からトランジスタ TRb 及び磁気メモリ素子 70 の MTJ を貫通してグラウンド線 GL へ流れれる。これによって磁気抵抗効果を利用した読み出しが可能となる。

20

図 7 は、本発明の実施例に係る磁気メモリ 90 の構成の一例を示すブロック図である。磁気メモリ 90 は、メモリセルアレイ 110、X ドライバ 120、Y ドライバ 130、コントローラ 140 を備えている。メモリセルアレイ 110 は、アレイ状に配置された複数の磁気メモリセル 80 を有している。磁気メモリセル 80 の各々は、上述の磁気メモリ素子 70 を有している。既出の図 6 で示されたように、各磁気メモリセル 80 は、ワード線 WL、グラウンド線 GL、及びビット線対 BLa、BLb に接続されている。X ドライバ 120 は、複数のワード線 WL に接続されており、それら複数のワード線 WL のうちアクセス対象の磁気メモリセル 80 につながる選択ワード線を駆動する。Y ドライバ 130 は、複数のビット線対 BLa、BLb に接続されており、各ビット線をデータ書き込みあるいはデータ読み出しに応じた状態に設定する。コントローラ 140 は、データ書き込みあるいはデータ読み出しに応じて、X ドライバ 120 と Y ドライバ 130 のそれぞれを制御する。

30

#### (原理)

次に、本発明で用いる原理について説明する。

本発明に係る磁気メモリ素子 70 においては、メモリ情報は磁化自由領域 12、及び応答層 20 の磁化の方向として格納され、磁化自由層 10 内での電流誘起磁壁移動によってメモリ状態の書き換えが行われる。そしてメモリ状態が書き換えられたとき、応答層 20 の磁化方向が変化し、それによって応答層 20、非磁性層 30、リファレンス層 40 からなる MTJ の抵抗状態が変化する。ここでは応答層 20 の磁化が磁化自由領域 12 の磁化方向の変化に応答して変化する仕組みについて説明する。

40

磁化自由領域 12 は +z 方向、または -z 方向のいずれかの方向に磁化している。従つて応答層 20 が磁化自由領域の上方 (+z 方向) に設けられているとき、応答層 20 の位置においては、磁化自由領域 12 が +z 方向に磁化しているときには +z 方向の漏洩磁界が形成され、一方 -z 方向に磁化しているときには -z 方向の漏洩磁界が形成される。応答層 20 はこの漏洩磁界によって磁化反転を起こし、磁化自由領域 12 の磁化に応答する。

50

図 8 A および図 8 B は磁化自由領域 1 2 からの漏洩磁界の計算結果である。ここでは磁化自由領域 1 2 のサイズは図 8 A に示すように  $90 \text{ nm} \times 90 \text{ nm} \times 5 \text{ nm}$  を想定しており、この磁化自由領域 1 2 の中心から  $z = \text{nm}$  上方における漏洩磁界の  $y$  座標依存性が示されている。図 8 B からわかるように磁化自由領域 1 2 からの距離 ( $z$ ) が小さいほど漏洩磁界は大きく、 $z = 10 \text{ nm}$  では約 500 [Oe] (約  $4 \times 10^4 \text{ A/m}$ ) 程度の漏洩磁界が発生することがわかる。すなわち、 $z = 10 \text{ nm}$  の場合、応答層 2 0 の保磁力が 500 [Oe] ( $4 \times 10^4 \text{ A/m}$ ) 以下になるように設計することで本発明を実施可能である。また  $z = 5 \text{ nm}$  では周辺部において約 1000 [Oe] (約  $8 \times 10^4 \text{ A/m}$ ) 程度の漏洩磁界が発生することがわかる。従って、 $z = 5 \text{ nm}$  の場合、応答層 2 0 の保磁力が 1000 [Oe] ( $8 \times 10^4 \text{ A/m}$ ) 以下になるように設計することで本発明を実施可能である。

#### (材料)

##### 1. 応答層、非磁性層の材料

前述のような原理から、応答層 2 0 は保磁力が 1000 [Oe] ( $8 \times 10^4 \text{ A/m}$ ) 以下となるような垂直磁気異方性材料を用いる必要がある。加えて、応答層 2 0、非磁性層 3 0、リファレンス層 4 0 からなる MTJ の MR 比を高めることで大きな読み出し信号が得られる。ところで、最近 MgO に隣接する CoFeB は、CoFeB の膜厚がある範囲内にあるとき、垂直磁化が発現されることが報告されている (Ikeda et al., "A perpendicular-anisotropy CoFeB-MgO magnetic tunnel junction", Nature Materials, 2010, vol. 9, p 721. 参照)。加えて上記文献においては、この CoFeB / MgO 膜を用いて MTJ を作製したとき、100% 以上の MR 比が得られることが報告されている。

図 9 A は基板 / Ta / CoFeB / MgO / Ta なる積層膜をドット状に加工したサンプルの磁化曲線であって、図 9 B は当該積層膜の保磁力の CoFeB 膜厚依存性の測定結果を示している。0.9 nm から 1.3 nm の膜厚範囲において垂直磁気異方性が実現され、いずれの場合も保磁力は 1000 [Oe] ( $8 \times 10^4 \text{ A/m}$ ) 以下となっていることがわかる。また図 9 B では、CoFeB の代わりに CoFeB と Fe の積層膜を用いたものの測定点もプロットされている。CoFeB / Fe とした場合、さらに小さな保磁力が実現されている。

このようなことから、応答層 2 0、非磁性層 3 0 の材料としては特に CoFeB、MgO が好ましいと言うことができる。

また、図 9 A および図 9 B からわかるように、磁化自由領域 1 2 からの漏洩磁界が 500 [Oe] ( $4 \times 10^4 \text{ A/m}$ ) 以上であれば、応答層 2 0 に対して広い設計マージンが確保できる。ここで図 8 からわかるように、磁化自由領域 1 2 と応答層 2 0 の膜厚方向の中心の距離が 15 nm 以下であれば、漏洩磁界は 500 [Oe] ( $4 \times 10^4 \text{ A/m}$ ) 以上となっている。このことから、磁化自由領域 1 2 と応答層 2 0 の膜厚方向の中心の距離は 15 nm 以下であることが好ましいと言える。

##### 2. その他の層の材料

応答層 2 0、非磁性層 3 0 に用いることの好ましい材料に関しては上述の通りであるが、一般的に磁化自由層 1 0、応答層 2 0、非磁性層 3 0、リファレンス層 4 0、及び磁化固定層 6 0 に用いることのできる材料については以下のようないくつかの材料が挙げられる。

磁化自由層 1 0 は前述の通り垂直磁気異方性を有する強磁性体により構成されることが好ましい。具体的には Fe - Pt 合金、Fe - Pd 合金、Co - Pt 合金、Co - Pd 合金、Tb - Fe - Co 合金、Gd - Fe - Co 合金、Tb - Fe 合金、Tb - Co 合金、Gd - Fe 合金、Gd - Co 合金、Co - Cr - Pt 合金、Co - Re - Pt 合金、Co - Ru - Pt 合金、Co - W 合金などの合金系材料のほか、Co / Pt 積層膜、Co / Pd 積層膜、Co / Ni 積層膜、Co / Cu 積層膜、Co / Ag 積層膜、Co / Au 積層膜、Fe / Pt 積層膜、Fe / Pd 積層膜、Fe / Au 積層膜などの交互積層膜が例示される。特にこの中で発明者らは Co / Ni 積層膜を用いて制御性の高い電流誘起磁壁移動が

10

20

30

40

50

実現できることを実験的に確認しており(Applied Physics' Express, vol. 1, p. 101303(2008))、この点でCo/Ni積層膜が磁化自由層10の好適な材料として挙げられる。

リファレンス層40は例えば垂直磁気異方性を有する強磁性体から構成される。このときリファレンス層40に用いることのできる材料は磁化自由層10に用いることのできる材料として例示したものと重複するので省略する。ただし、リファレンス層40は磁化が安定して固定されていることが求められるので、なるべくハードな磁性体であることが好ましい。この点でFe-Pt合金、Fe-Pd合金、Co-Pt合金、Co/Pt積層膜、Co/Pd積層膜などが好適である。またその磁化方向は一方向に固定されている必要があり、さらに外部への漏洩磁界が小さいことが好ましい。このために前述のように、積層フェリ結合を有する積層構造とすることが好ましい。すなわち、リファレンス層40は、例えば強磁性体/Ru/強磁性体というような積層構成を有することが好適である。またリファレンス層40は面内磁気異方性を有する強磁性体から構成されてもよい。この場合にはあらゆる磁性体を用いることができる。代表的にはCo-Feなどが挙げられる。なお、リファレンス層40に面内磁気異方性を有する材料を用いた場合の実施の形態の例は、後に第4の変形例として説明される。

また磁化固定層60には、垂直磁気異方性を有する強磁性体から構成される。この場合に用いることのできる材料は磁化自由層10に用いることのできる材料として例示したものと重複するので省略する。

導電層50は導電性の材料であればどのような材料を用いても構わない。ただし、応答層20にCoFeBを用い、非磁性層30にMgOを用いる場合、導電層50はCoFeBに垂直磁気異方性を発現させるために、Ti、V、Cr、Zr、Nb、Mo、Hf、Ta、Wを含有することが好ましい。

また本発明に係る磁気メモリ素子70においては、前述のように書き込みに電流誘起磁壁移動を用いる。このときの電流は磁化自由層10に導入するが、磁化自由層10に対して導電層50が隣接する場合、導電層50にも書き込み電流は流れる。この電流が大きければ、トータルの書き込み電流も増加してしまい好ましくない。この点で導電層50の抵抗は比較的高いことが好ましい。上記のTi、V、Cr、Zr、Nb、Mo、Hf、Ta、Wは上述のCo/Ni系の材料に比べて比較的抵抗が高く、この点でも好ましい。また上記のような材料は窒化、または酸化することによって、導電層50の抵抗をさらに増大させることもできる。代表的にはTa-N、Ti-N、Zr-Nなどが例示される。

非磁性層30は一般的には絶縁性材料により構成されることが好ましい。具体的にはMg-Oの他、Al-O、Al-N、Ti-Oなどを用いることができる。

応答層20には上述のCoFeB以外の保磁力の小さな垂直磁気異方性を有する強磁性体を用いてもよい。この場合に用いることのできる材料は磁化自由層10に用いることのできる材料として例示したものと重複するので省略する。

#### (効果)

次に本発明で得られる効果について説明する。

前述のように、垂直磁気異方性を有する強磁性体における電流誘起磁壁移動を書き込み方法に用いた磁気メモリ素子は特許文献2、特許文献3などに公開されている。図10Aおよび図10Bは特許文献2に公開されている磁気メモリ素子の構造を、図11A～図11Cは特許文献3に公開されている磁気メモリ素子の構造を、それぞれ模式的に示している。図10A、図11Aは斜視図を示しており、図10B、図11B、図11Cは断面図を示している。なお、図中の符号は本発明に対応させてある。また以下の説明においては、各レイヤーの名称は本発明と対応するように記述される。

図10Aおよび図10Bに示されるように、特許文献2に示される磁気メモリ素子70においては、電流誘起磁壁移動による書き込みを行う磁化自由層10に対して、読み出しを行うための非磁性層30、リファレンス層40が隣接している。図10Aおよび図10Bに示される構造では、書き込みは磁化自由層10内で行われる。従って書き込み電流低減等の書き込み特性の調整のためには、磁化自由層10の材料、構成を適切に設計する必

10

20

30

40

50

要がある。一方、読み出し信号量増大等の読み出し特性の調整のためには、磁化自由層 10、非磁性層 30、リファレンス層 40 の構造、構成を適切に設計する必要がある。すなわち、磁化自由層 10 は書き込み特性、読み出し特性の両方の要請を満たすように設計する必要があるということが言える。これは書き込み特性、読み出し特性の片方の要請を満たすように設計する場合と比べて、設計の自由度が低くなり、特性の向上が困難となる。

一方、図 11A～図 11C に示されるように、特許文献 3 に示される磁気メモリ素子 70においては、書き込みは磁化自由層 10 内で行われ、磁化自由層 10 の磁化方向をセンシングするための面内磁気異方性を有するソフトな応答層 20 が設けられ、それに隣接して非磁性層 30、リファレンス層 40 が設けられている。また、応答層 20 は磁化自由層 10 からの漏洩磁界をセンシングするために x - y 面内において磁化自由層 10 からずれるようにして設けられている。図 11A～図 11C に示される構造では、図 10A および図 10B と同様に書き込み特性は磁化自由層 10 の設計により調整可能である。一方読み出し特性は応答層 20、非磁性層 30、リファレンス層 40 からなる MTJ の設計により調整可能である。すなわち、書き込み特性と読み出し特性の独立な設計が可能である。その一方で、図 11A～図 11C に示された構造を形成するために必要なプロセス数は図 10A および図 10B に示された構造を形成するために必要なプロセス数と比べて多くなる。また応答層 20 の磁化自由層 10 に対する x - y 面内でのズレ量も適切に調整する必要があり、これはプロセスマージンの低下、微細化の困難化を招く。さらにセル面積も増大し、コストの増大を招く。

即ち、図 10A および図 10B に示される特許文献 2 に公開されている磁気メモリ素子は良好な書き込み特性と読み出し特性の両立が難しく、一方図 11A～図 11C に示される特許文献 3 に公開されている磁気メモリ素子はプロセスマージン、低コスト化の点でデメリットがある。本発明に係る磁気メモリ素子 70 はこれらの問題を解決する。

具体的には、本発明に係る磁気メモリ素子 70 は、書き込み特性は磁化自由層 10 によって決まり、読み出し特性は応答層 20、非磁性層 30、リファレンス層 40 によって決まる。従って書き込み特性と読み出し特性の独立な設計が可能となり、特許文献 2 に係る磁気メモリ素子の課題が解決される。また、本発明に係る磁気メモリ素子 70 は、構造は図 10A および図 10B に示されている特許文献 2 に係る磁気メモリ素子と同様である。従って特許文献 3 に係る磁気メモリ素子のもつデメリットとも無縁である。

即ち、本発明は、良好な書き込み特性と読み出し特性の両立が可能であり、プロセスマージンの大きい磁気メモリ素子を低コストで提供することができる。

#### [変形例]

以上で説明された磁気メモリ素子 70 は以下に説明される変形例を用いても実施することができる。

#### (第 1 の変形例)

図 12A および図 12B は本発明に係る磁気メモリ素子 70 の第 1 の変形例の構造を模式的に示している。第 1 の変形例は磁化固定層 60 の位置に関する。本発明に係る磁気メモリ素子 70 は磁化自由層 10 を具備し、磁化自由層 10 内の第 1 磁化固定領域 11a、第 2 磁化固定領域 11b は互いに反平行方向に固定される。また、図 1A～図 1C ではこの第 1 磁化固定領域 11a、第 2 磁化固定領域 11b の磁化的反平行方向への固定のために磁化固定層 60 が設けられる例が示されている。図 1A～図 1C ではこの磁化固定層 60 は磁化自由層 10 に対して基板側 (-z 方向) に配置されているが、この磁化固定層 60 の位置には任意性がある。

図 12A および図 12B では磁化固定層 60 が磁化自由層 10 に対して上方に設けられる例が示されている。図 12A および図 12B に示されるように磁化固定層 60 が磁化自由層 10 の上方に設けられる場合、磁化自由層 10 と磁化固定層 60 は連続的に堆積させることができ、その磁気結合が容易となる。

プロセス数の観点では、図 12A および図 12B に示される構造は図 1A～図 1C に示される構造と比べて増加し、図 11A～図 11C に示される特許文献 3 の磁気メモリ素子と同程度になる。しかし図 12A および図 12B に示される構造は、図 11A～図 11C

10

20

30

40

50

に示された構造と比べて、応答層 20 を x - y 面内ですらす必要はなく、プロセスマージンは広くなり、また素子面積も増大しない。

また図 12 A および図 12 B に示された例以外でも、第 1 磁化固定領域 11 a、第 2 磁化固定領域 11 b の磁化を反平行方向に向けた上で固定することができれば、磁化固定層 60 はどこに設けられてもよく、またいくつ設けられてもよい。

#### ( 第 2 の変形例 )

図 13 A、図 13 B、図 14 A、および図 14 B は本発明に係る磁気メモリ素子 70 の第 2 の変形例の構造を模式的に示している。第 2 の変形例は応答層 20、非磁性層 30、リファレンス層 40 の位置、形状に関する。本発明に係る磁気メモリ素子 70 は応答層 20、及びそれに隣接して非磁性層 30、リファレンス層 40 を具備するが、これらの設けられる位置、及び形状についてはある条件を満たした範囲内で任意性がある。

10

図 13 A および図 13 B では応答層 20、非磁性層 30、リファレンス層 40 が磁化自由層 10 に対して基板側 ( - z 方向 ) に設けられる例が示されている。磁化自由層 10 の下面に導電層 50 が接続され、それに隣接して応答層 20、非磁性層 30、リファレンス層 40 がこの順に設けられている。

前述のように応答層 20 は磁化自由層 10 内の磁化自由領域 12 からの漏洩磁界に対して磁化方向が可変である。すなわち、磁化自由領域 12 からの漏洩磁界によって磁化方向が応答できる位置であればどのような位置に設けられてもよく、磁化自由層 10 の上側であってもよいし、下側であってもよい。

また図 14 A および図 14 B では応答層 20 が磁化自由層 10 の y 方向の幅よりも大きく形成されている。図 8 の漏洩磁界の分布のグラフからわかるように、磁化自由領域 12 からの漏洩磁界は、エッジ部分において増加する。図 14 A および図 14 B に示されたように、応答層 20 を大きめに形成した場合、このエッジ部分の大きな漏洩磁界を検出することが可能であり、検出感度の点で有利となる。

20

また図示されていないが、応答層 20 は x - y 面内で磁化自由領域 12 からずれるようにして形成されても構わない。またその形状も長方形状でも構わないし、円形でも構わない。

#### ( 第 3 の変形例 )

図 15 A および図 15 B は本発明に係る磁気メモリ素子 70 の第 3 の変形例の構造を模式的に示している。第 3 の変形例は磁気メモリ素子 70 の端子数に関する。図 1 A ~ 図 1 C を用いて説明されたように、本発明に係る磁気メモリ素子 70 は典型的には 3 端子の素子となるが、3 以外の端子であっても本発明に係る磁気メモリ素子 70 を実施することは可能である。

30

図 15 A および図 15 B では 4 端子の素子として本発明を実施する場合の磁気メモリ素子の構造が示されている。図 1 A ~ 図 1 C に示される例においては、磁化自由層 10 と応答層 20、非磁性層 30、リファレンス層 40 は導電層 50 を介して電気的に接続されていたが、図 15 A および図 15 B に示される例では、これらは電気的に分離されている。

図 16 A および図 16 B は図 15 A および図 15 B に示された構造を有する磁気メモリ素子 70 における、書き込み電流の経路 ( 図 16 A ) 、及び読み出し電流の経路 ( 図 16 B ) を示している。書き込みの際は、磁化自由層 10 内に電流を導入する。一方読み出しの際は、応答層 20、非磁性層 30、リファレンス層 40 を貫通するように電流を導入し、その電流経路は導電層 50 から磁化自由層 10 を経由せずに外部の回路へと接続される。

40

#### 【産業上の利用可能性】

#### 【 0 0 1 0 】

本発明の利用例として、携帯電話、モバイルパソコンや P D A ( Personal Digital Assistant ) に使用される不揮発性の半導体メモリ装置や、自動車などに使用される不揮発性メモリ内蔵のマイコンが挙げられる。またレーストラックメモリのような大規模のストレージデバイスなどへの利用も可能である。加えて、ロジック回路に不揮発性の抵抗変化素子を適用することで実現が可能である不揮発ロジック回路に

50

も本発明を用いることができる。

なお、本出願は、2011年5月20日に出願された、日本国特許出願第2011-113697号からの優先権を基礎として、その利益を主張するものであり、その開示はここに全体として参考文献として取り込む。

【符号の説明】

【0011】

|      |          |    |

|------|----------|----|

| 10   | 磁化自由層    | 10 |

| 11 a | 第1磁化固定領域 |    |

| 11 b | 第2磁化固定領域 |    |

| 12   | 磁化自由領域   |    |

| 20   | 応答層      |    |

| 30   | 非磁性層     |    |

| 40   | リファレンス層  |    |

| 50   | 導電層      |    |

| 60   | 磁化固定層    |    |

| 70   | 磁気メモリ素子  |    |

| 80   | 磁気メモリセル  |    |

| 90   | 磁気メモリ    |    |

| 110  | メモリセルアレイ | 20 |

| 120  | Xドライバ    |    |

| 130  | Yドライバ    |    |

| 140  | コントローラ   |    |

【図1A】

図1A

【図1B】

図1B

【図1C】

図1C

【図2A】

図2A

【図2B】

図2B

【図3A】

図3A

【図3B】

図3B

【図3C】

図3C

【図4A】

図4A

【図4B】

図4B

【図5B】

図5B

【図5A】

図5A

【図6】

図6

【図7】

図7

【図8A】

図8A

【図9B】

図9B

【図10A】

図10A

【図8B】

図8B

【図9A】

図9A

【図10B】

図10B

【図11A】

図11A

【図 1 1 B】

図 11B

【図 1 1 C】

図 11C

【図 1 2 A】

図 12A

【図 1 3 A】

図 13A

【図 1 2 B】

図 12B

【図 1 3 B】

図 13B

【図 1 4 A】

図 14A

【図 1 4 B】

図 14B

【図 1 5 A】

図 15A

【図 1 5 B】

図 15B

【図 1 6 A】

図 16A

【図 1 6 B】

図 16B

---

フロントページの続き

(72)発明者 石綿 延行

東京都港区芝五丁目7番1号 日本電気株式会社内

(72)発明者 杉林 直彦

東京都港区芝五丁目7番1号 日本電気株式会社内

(72)発明者 大野 英男

宮城県仙台市青葉区片平二丁目1番1号 国立大学法人東北大学内

(72)発明者 池田 正二

宮城県仙台市青葉区片平二丁目1番1号 国立大学法人東北大学内

(72)発明者 山ノ内 路彦

宮城県仙台市青葉区片平二丁目1番1号 国立大学法人東北大学内

審査官 上田 智志

(56)参考文献 國際公開第2010/095589 (WO, A1)

特開2009-081315 (JP, A)

國際公開第2010/041719 (WO, A1)

國際公開第2009/093387 (WO, A1)

特開2010-219104 (JP, A)

國際公開第2010/007893 (WO, A1)

國際公開第2008/068967 (WO, A1)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8246

H01L 27/105

H01L 29/82

H01L 43/08