(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5023163号

(P5023163)

(45) 発行日 平成24年9月12日(2012.9.12)

(24) 登録日 平成24年6月22日(2012.6.22)

(51) Int.Cl.

F 1

|              |           |            |      |

|--------------|-----------|------------|------|

| HO1L 29/78   | (2006.01) | HO1L 29/78 | 301G |

| HO1L 21/336  | (2006.01) | HO1L 27/08 | 321D |

| HO1L 27/092  | (2006.01) | HO1L 21/28 | 301R |

| HO1L 21/8238 | (2006.01) | HO1L 29/58 | G    |

| HO1L 21/28   | (2006.01) |            |      |

請求項の数 3 (全 10 頁) 最終頁に続く

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2010-8465 (P2010-8465)      |

| (22) 出願日     | 平成22年1月18日 (2010.1.18)        |

| (65) 公開番号    | 特開2010-263183 (P2010-263183A) |

| (43) 公開日     | 平成22年11月18日 (2010.11.18)      |

| 審査請求日        | 平成24年3月5日 (2012.3.5)          |

| (31) 優先権主張番号 | 12/434,070                    |

| (32) 優先日     | 平成21年5月1日 (2009.5.1)          |

| (33) 優先権主張国  | 米国(US)                        |

早期審査対象出願

|           |                |

|-----------|----------------|

| (73) 特許権者 | 000003078      |

|           | 株式会社東芝         |

|           | 東京都港区芝浦一丁目1番1号 |

| (74) 代理人  | 100108855      |

|           | 弁理士 蔵田 昌俊      |

| (74) 代理人  | 100091351      |

|           | 弁理士 河野 哲       |

| (74) 代理人  | 100088683      |

|           | 弁理士 中村 誠       |

| (74) 代理人  | 100109830      |

|           | 弁理士 福原 淑弘      |

| (74) 代理人  | 100075672      |

|           | 弁理士 峰 隆司       |

| (74) 代理人  | 100095441      |

|           | 弁理士 白根 俊郎      |

最終頁に続く

(54) 【発明の名称】半導体装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項1】

半導体基板上に形成された第1の高誘電体材料層と、

前記第1の高誘電体材料層上に形成された酸素を含む第1の合金層と、

前記酸素を含む第1の合金層上に形成されたRe層と、

前記第1の高誘電体材料層と前記酸素を含む第1の合金層との間に位置するRe酸化物層

を含むp型電界効果トランジスタと、

前記半導体基板上に形成された第2の高誘電体材料層と、

前記第2の高誘電体材料層上に形成された酸素を含む第2の合金層と、

前記酸素を含む第2の合金層上に形成されたSiを含む金属層と、

前記第2の高誘電体材料層と前記酸素を含む第2の合金層との間に位置するAl層と、

前記Siを含む金属層と前記酸素を含む第2の合金層との間に位置するAl層を含むn型電

界効果トランジスタと

を具備する半導体装置。

## 【請求項2】

半導体基板上に高誘電体材料の層を堆積し、

酸素原子を含む合金層を形成し、

Re及びRe酸化物からなるグループから選択される1以上からなる第1の層を前記合金層

の一部領域上に堆積し、

熱処理を加え、前記高誘電体材料の層と前記合金層との間に、Re酸化物層を形成する

10

20

ことを具備するp型電界効果トランジスタを形成し、

前記第1の層を前記合金層の一部領域上に堆積した後に、全面にSiを含む金属層を堆積し、

前記Siを含む金属層、前記第1の層、前記合金層、及び前記高誘電体材料の層からなる積層構造をパターニングして、前記p型電界効果トランジスタの形成領域及びn型電界効果トランジスタの形成領域に積層構造を残し、

前記Siを含む金属層に対してAl原子を注入した後、熱処理を行って、前記n型電界効果トランジスタの形成領域において前記合金層と前記高誘電体材料の層との間に第1のAl層を形成することを特徴とする半導体装置の製造方法。

【請求項3】

10

前記熱処理を行って、前記n型電界効果トランジスタの形成領域において前記合金層と前記高誘電体材料の層との間に前記第1のAl層を形成する際に、前記p型電界効果トランジスタの形成領域においてSiを含む前記金属層と前記合金層との間にAlとReの合金層を形成し、かつ前記n型電界効果トランジスタの形成領域において前記合金層と前記高誘電体材料の層との間に第2のAl層を形成する請求項2記載の半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

20

【0002】

金属-酸化物-半導体電界効果トランジスタ(FET)は集積回路の共通部品であり、典型的には、コンダクタンスを制御するゲート電極を形成するために半導体材料のいくつかの層の堆積が後続する、Siベース又はGeベースの半導体基板に対するドーピングによって形成される。FETは、p型原子がドープされた領域からなるソース及びドレインを有するp型FET(pFET)、もしくはn型原子がドープされた領域からなるソース及びドレインを有するn型FET(nFET)として形成される。しばしば、pFET構造は、類似したnFET構造と組み合わされてロジックゲートや他の半導体装置が形成される。ソース及びドレイン領域に加えて、FET構造は、ドーピングによって形成されたソース、ドレイン及びチャネル領域を含む半導体基板上に、ゲート高誘電体(high k)材料の層及び導電材料(金属及び/又は高度にドープされた多結晶シリコン)の層を堆積して形成される。pFET構造では、ゲート電極に対する負のゲート・ソース間電圧の印加により生成される電界により、高誘電体材料とチャネルの境界付近にホールの集中が生じる。十分な電圧(閾値電圧)が供給されると導電チャネルが形成され、ソースからドレインに電流が流れる。ゲート材料の性質はトランジスタの閾値電圧に大きな影響を与える。ゲート誘電体層及びその境界における電荷と同様に、ゲート電極材料とチャネル材料との間の仕事関数の変更により、トランジスタの閾値電圧を調節することができる。

30

【0003】

なお、特許文献1には、PチャネルMOSFETのゲート電極が、第1の濃度の酸素を含有する第1の導電性膜と、第1の濃度より高い第2の濃度の酸素を含有する第2の導電性膜と、第2の濃度より低い第3の濃度の酸素を含有する第3の導電性膜とを含む積層構造を有することが開示されている。また、非特許文献1には、Reを用いたゲートの閾値の不安定性が開示されている。さらに、非特許文献2には、Reを用いたゲートの閾値の不安定性の物理モデルが開示されている。

40

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2008-84970号公報

【非特許文献】

【0005】

50

【非特許文献 1】 "Role of Oxygen Vacancies in VFB/Vt stability of pFET metals on HfO<sub>2</sub>" , E. Cartier et al. , 2005 Symposium on VLSI Technology Digest of Technical Papers, pp230

【非特許文献 2】 "Flatband voltage shift of ruthenium gated stacks and its link with the formation of a thin ruthenium oxide layer at the ruthenium/dielectric interface" , Z. Li et al. , JOURNAL OF APPLIED PHYSICS 101, 034503 (2007)

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の目的は、高い仕事関数及び高温安定性を備えたメタルゲートを有する半導体装置及びその製造方法を提供することである。 10

【課題を解決するための手段】

【0007】

本発明の一視点によれば、半導体基板上に形成された第1の高誘電体材料層と、前記第1の高誘電体材料層上に形成された酸素を含む第1の合金層と、前記酸素を含む第1の合金層上に形成されたRe層と、前記第1の高誘電体材料層と前記酸素を含む第1の合金層との間に位置するRe酸化物層を含むp型電界効果トランジスタと、前記半導体基板上に形成された第2の高誘電体材料層と、前記第2の高誘電体材料層上に形成された酸素を含む第2の合金層と、前記酸素を含む第2の合金層上に形成されたSiを含む金属層と、前記第2の高誘電体材料層と前記酸素を含む第2の合金層との間に位置するAl層と、前記Siを含む金属層と前記酸素を含む第2の合金層との間に位置するAl層を含むn型電界効果トランジスタとを具備する半導体装置が提供される。 20

【0008】

本発明の他の視点によれば、半導体基板上に高誘電体材料の層を堆積し、酸素原子を含む合金層を形成し、Re及びRe酸化物からなるグループから選択される1以上からなる第1の層を前記合金層の一部領域上に堆積し、熱処理を加え、前記高誘電体材料の層と前記合金層との間に、Re酸化物層を形成することを具備するp型電界効果トランジスタを形成し、前記第1の層を前記合金層の一部領域上に堆積した後に、全面にSiを含む金属層を堆積し、前記Siを含む金属層、前記第1の層、前記合金層、及び前記高誘電体材料の層からなる積層構造をパターニングして、前記p型電界効果トランジスタの形成領域及びn型電界効果トランジスタの形成領域に積層構造を残し、前記Siを含む金属層に対してAl原子を注入した後、熱処理を行って、前記n型電界効果トランジスタの形成領域において前記合金層と前記高誘電体材料の層との間に第1のAl層を形成することを特徴とする半導体装置の製造方法が提供される。 30

【発明の効果】

【0009】

本発明によれば、高い仕事関数及び高温安定性を備えたメタルゲートを有する半導体装置及びその製造方法を提供することができる。

【図面の簡単な説明】

【0010】

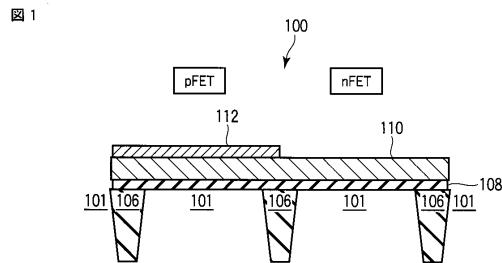

【図1】本発明の一実施形態に係る半導体装置の製造方法の最初の工程を示す断面図。 40

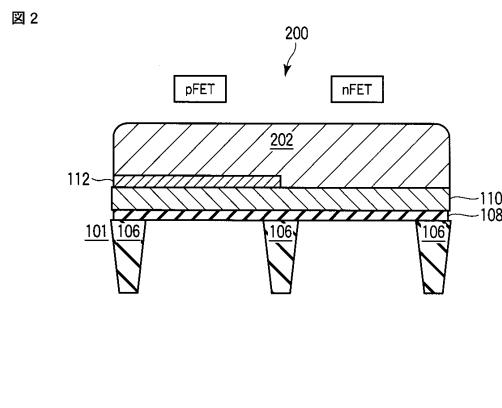

【図2】図1の次の工程を示す断面図。

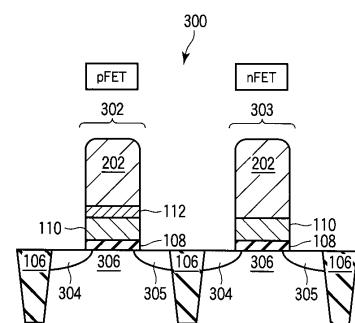

【図3】図2の次の工程を示す断面図。

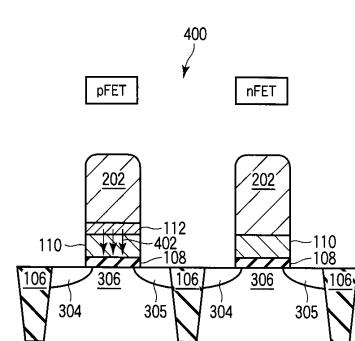

【図4】図3の次の工程を示す断面図。

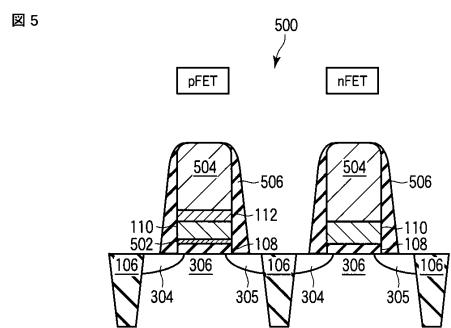

【図5】図4の次の工程を示す断面図。

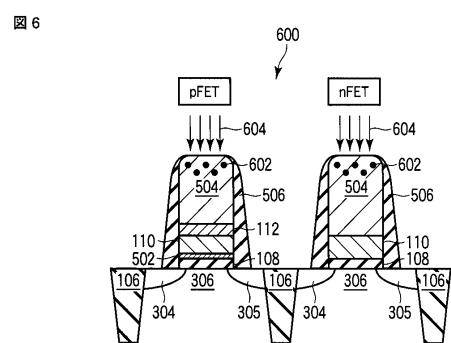

【図6】図5の次の工程を示す断面図。

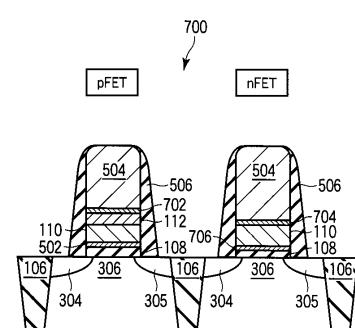

【図7】図6の次の工程を示す断面図。

【発明を実施するための形態】

【0011】

本発明の実施形態の詳細な説明の前に、その概要について説明する。本発明の実施形態 50

では、約4.6 eVを越える実効仕事関数を持つpFET構造用の高誘電率材料及びメタルゲート及び半導体装置の製造中に要求される高温における安定性について記述する。高仕事関数の性質は、高誘電率 (high k) ゲート材料とゲート電極構造との間の境界にRe (レニウム) 酸化物の薄膜を形成することによって得られる。ゲート電極は、半導体基板に近い側に設けられるRe酸化物の薄膜、high kゲート材料、高濃度に酸素を含む合金層、Re層、Re酸化物の薄膜上に形成されたSiを含む合金層、がこの順番で積層された積層構造を有し、ゲート電極の積層構造はバランスが保たれている。

#### 【 0 0 1 2 】

以下に説明する実施形態はpFET構造を有する半導体装置に適用が可能である。特に、以下に説明する実施形態は、約-500mVから0 mVまでの低い閾値電圧を有するpFET構造及び/又は約4.6 eV以上の実効仕事関数を備えたゲート電極を有するpFET構造に適用が可能である。説明する実施形態に係る半導体装置は、ゲート誘電体 (high k材料) とゲート電極の残りの部分との間の薄いRe酸化物層の形成により達成される。

10

#### 【 0 0 1 3 】

低い閾値電圧は、高い仕事関数を持つゲート電極の形成によって達成できる。実効仕事関数は、ゲート電極とチャネル領域と間のフェルミエネルギーの差である。実効仕事関数は、MOSキャパシタのC-V特性の測定、及び測定されたフラットバンド電圧及びチャネル領域のドーパント濃度により評価することができる。本実施形態に係る半導体装置では、ゲート誘電体の表面上に1原子層以上の厚さのRe酸化物の層を形成し、Re酸化物の薄層上にゲート電極の残りの部分を形成することにより、高い仕事関数が生成される。Re酸化物の薄層は熱促進拡散プロセスによって形成される。始めに、酸素を含む合金層及びReの層がゲート誘電体材料上に連続的に形成される。次に、ラピッドサーマルアニールが行われ、Re層から酸素を含む合金層にReが拡散される。このラピッドサーマルアニールにより、high kゲート誘電体材料と酸素を含む合金層との間に1原子層以上の厚さのRe酸化物層が形成され、合金層の粒界に存在するRe原子が生じる。

20

#### 【 0 0 1 4 】

以下に図面を参照して説明する実施の形態において、対応する箇所には同じ参照符号を付して説明を行なう。さらに、その説明に際し、N型原子及びドーパントは、半導体材料内で負電荷の流れをサポートするために使用される負の電荷の追加の同等物を導入するあらゆる原子、イオン、又は組成を含む。N型原子及びドーパントは、周期表のグループ15内の元素を含み、リン及びヒ素を含んでいる。P型原子及びドーパントは、半導体材料内で正電荷の流れをサポートするために使用される正の電荷 (又はホール) の追加の同等物を導入するあらゆる原子、イオン、又は組成を含む。P型原子及びドーパントは、周期表のグループ13内の元素を含み、ボロン、アルミニウム、ガリウム及びインジウムを含んでいる。

30

#### 【 0 0 1 5 】

図1～図7は、本発明の一実施形態に係るpFETを含む半導体装置の製造方法の典型的な工程を示している。この製造方法では、ロジックゲート、CMOS (相補金属-酸化物-半導体) デバイス及びpFET及びnFETを含む他の半導体装置の製造に共通であるように、pFET構造とnFET構造とが同時に形成される。当業者であれば容易に理解できるように、この方法によりpFET構造のみを備えた半導体装置及び/又は他の形式の半導体構造と組み合わせたpFET構造を含む半導体装置を製造することもできる。1原子層程度の厚さのRe酸化物層を備えた構造は、例示する方法以外の他の方法によっても形成することができ、発明の範囲に含まれている。

40

#### 【 0 0 1 6 】

図1は、本実施形態による方法に従って半導体装置を形成するための始めの構造を示している。半導体基板101上に素子分離領域106が形成され、各トランジスタ領域が素子分離領域106によって分離される。各トランジスタ領域は、工程の後段ステージで良く知られているイオン注入技術により形成されるソース、ドレイン及びチャネル領域を有する。

50

## 【0017】

半導体基板101上にゲート誘電体層108が形成される。ゲート誘電体として高誘電率の材料が使用でき、ハフニウムオキサイド又は金属シリコン材料等がある。金属シリコンオキサイド材料は、以下の化学式で表わされる組成を含む。すなわち、 $MSiO$ 、 $MSiON$ 、 $M_1M_2SiO$ 、 $M_xSi_{1-x}O_2$ 及び $M_xSi_{1-x}ON$ であり、 $M$ と $M_1$ は、独立してグループIVAの元素あるいはランタン系列の元素であり、 $M_2$ は、窒素、グループIVAの元素あるいはランタン系列の元素であり、さらに $x$ は0より大きく1未満である。具体例として $Hf_xSi_{1-x}O_2$ 、 $Hf_xSi_{1-x}ON$ 、 $Zr_xSi_{1-x}O_2$ 、 $Zr_xSi_{1-x}ON$ 、 $La_xSi_{1-x}O_2$ 、 $La_xSi_{1-x}ON$ 、 $Gd_xSi_{1-x}O_2$ 、 $Gd_xSi_{1-x}ON$ 、 $HfZrSiO$ 、 $HfZrSiON$ 、 $HfLaSiO$ 及び $HfGdSiO$ を含み、 $x$ は0と1の間である。一例では、ゲート誘電体層108の厚さは約0.1nmから約25nmまでである。他の例では、ゲート誘電体層108の厚さは約0.2nmから約20nmまでである。さらに他の例では、ゲート誘電体層108の厚さは約0.3nmから約10nmまでである。10

## 【0018】

合金層110がゲート誘電体層108上に形成される。合金層110は、 $TiN$ 、 $TiAlN$ 、 $TiC$ 、 $TaC$ 、 $TaN$ 、 $TaAlC$ 及び $TaAlN$ の1つ以上からなる。合金層110は酸素を十分に含み、合金層110を堆積する際の $O_2$ 圧力の調整により酸素含有量が調節可能である。一例では、合金層110を堆積する際の $O_2$ の分圧は約1kPaから約50kPaまでである。他の例では、合金層110を堆積する際の $O_2$ の分圧は約5kPaから約30kPaまでである。さらに他の例では、合金層110を堆積する際の $O_2$ の分圧は約5kPaから約15kPaまでである。一例では、合金層110内の酸素濃度は約0.5重量%から約30重量%までである。他の例では、合金層110内の酸素濃度は約1重量%から約20重量%までである。さらに他の例では、合金層110内の酸素濃度は約1重量%から約10重量%までである。一例では、合金層110の厚さは約1nmよりも大きい。他の例では、合金層110の厚さは約2nmから約50nmまでである。さらに他の例では、合金層110の厚さは約2nmから約30nmまでである。20

## 【0019】

続いて、Re層112が合金層110上に形成される。このRe層112は、Re金属原子及び/又はRe酸化物を含んでいてもよい。Reはその酸化物として $ReO_2$ 、 $ReO_3$ 、 $Re_2O_3$ 、及び $Re_2O_7$ の組成を取り得る。特に $ReO_3$ は、通常の金属酸化物では見られないような非常に小さい電気抵抗を示すことから、低抵抗であることが望まれるゲート電極してより好ましい。以下の説明では、Re酸化物として $ReO_3$ を使用する。しかしながら、本実施形態による閾値制御技術では、Re酸化物として $ReO_3$ に限られず、その組成は $Re/O = 1/3$ でもよい。また、金属酸化物中には酸素空孔が形成されるため、その組成がRe酸化物のそれから±10%の範囲でずれる場合があり、その場合にも本実施形態による効果は発現するし有効である。Re層112は、半導体装置100のpFET構造が形成される領域上にのみ堆積される。Re層112を堆積する領域を選択的にターゲットとするために、よく知られたマスキング技術が使用される。一例では、Re層112の厚さは約1nmから約25nmまでである。他の例では、Re層112の厚さは約1nmから約20nmまでである。さらに他の例では、Re層112の厚さは約2nmから約10nmまでである。30

## 【0020】

図2では、図1に示される半導体装置100上にドープトシリコン(ポリシリコン)又はポリシリコン-ゲルマニウム(ポリSiGe)の層202が堆積された半導体装置200を示している。層202は、シリサイドを形成するのに適した、ポリシリコン及びポリSiGe以外の他の物質を含んでいてもよい。一例では、ポリシリコン又はポリSiGe層202の厚さは約5nmから約100nmまでである。他の例では、ポリシリコン又はポリSiGe層202の厚さは約10nmから約75nmまでである。さらに他の例では、ポリシリコン又はポリSiGe層202の厚さは約15nmから約60nmまでである。40

## 【0021】

図3では、層108、110、112及び202内に縦型分離部を形成して、半導体装置300に物理的に分離されたゲート電極302(pFET構造)及びゲート電極303(nF50

ET構造)を形成するために、よく知られているエッチング技術が使用される。エッチング技術として、ドライエッチング及び/又はウェットエッチング技術が使用される。

【0022】

pFET構造では、よく知られている技術を使用したp型イオンの注入により、ソース304及びドレイン305が形成される。さらにpFET構造では、ソース304及びドレイン305間にn型の性質を持つチャネル306が形成されるように、n型原子を備えた半導体の領域内にソース304及びドレイン305が形成される。nFET構造では、よく知られている技術を使用したn型イオンの注入により、ソース304及びドレイン305が形成される。さらにnFET構造では、ソース304及びドレイン305間にp型の性質を持つチャネル306が形成されるように、p型原子を備えた半導体の領域内にソース304及びドレイン305が形成される。 10

【0023】

図4では、半導体装置400が熱活性化工程を経て、ゲート誘電体層108の表面上に薄いReO<sub>3</sub>層(図5中の符号502)が形成される。半導体装置400は、約1000以上の温度で約60秒未満の期間加熱される。あるいは、半導体装置400は、約10から約500msecの期間、レーザアニーリングが行われてもよい。この熱活性化工程により、層112から層110と層108との間の境界にRe原子が拡散される。Re原子は酸素を含む合金層110を通じて拡散されるので、Reが酸化され、ReO<sub>3</sub>が形成される。Re原子が拡散される方向が図4中に矢印402で示されている。熱活性化工程後に形成される薄いReO<sub>3</sub>層が図5中に符号502で示されている。一例では、薄いReO<sub>3</sub>層502はほぼ原子の厚さである。他の例では、薄いReO<sub>3</sub>層502は約0.2nmから約2nmまでの厚さである。さらに他の例では、薄いReO<sub>3</sub>層502は約0.1nmから約1nmまでの厚さである。 20

【0024】

図5では、半導体装置500は、熱活性化により薄いReO<sub>3</sub>層502が形成され、かつポリシリコン又はポリSiGe層202がSiを含む金属層504に変換される。Siを含む金属層504は、ラピッドサーマルアニーリング(RTA)技術を含むシリサイドを形成するなど、よく知られている技術によって形成できる。Ni、Pt、Co、Pd及びTiの1以上に限定されない金属膜がポリシリコン又はポリSiGe層202上に堆積され、加熱されてSiを含む金属層504が形成される。約300から約800までのアニーリングより、Siを含む金属層504が形成される。Siを含む金属層504は、ポリシリコン、ポリSiGe、Niシリサイド、NiPtシリサイド、NiPdシリサイド、Tiシリサイド及びCoシリサイドから選択される1以上を含んでいてもよい。この時点で、積層ゲート電極構造の各側面の誘電体材料の外側にサイドオウルスペーサ506が形成されていてもよい。 30

【0025】

図6では、Alイオン注入ビーム604の使用により、半導体装置600のSiを含む金属層504に対してAl原子604が注入される。この際、標準的なイオン注入技術が使用できる。一例では、注入エネルギーは約20keV未満である。他の例では、注入エネルギーは約10keV未満である。イオン注入は、Siを含む金属層504の表面における注入されたAl原子602の濃度が約5x10<sup>15</sup>原子/cm<sup>2</sup>以上になるまで行われる。 40

【0026】

図7では、加熱工程により、注入されたAl原子の拡散が行われる。加熱は少なくとも約1分間行われる。一例では、加熱は約300から約700までの温度で行われる。他の例では、加熱は約350から約600までの温度で行われる。さらに他の例では、加熱は約400から約550までの温度で行われる。pFET構造を形成する領域とnFET構造を形成する領域との間では、Al原子の拡散パターンの間には差がある。半導体装置700内のpFET構造では、Al拡散がRe層112で停止し、Siを含む金属層504と合金層110との間にAl-Re合金702が形成される。半導体装置700内のnFET構造では、Siを含む金属層504と合金層110との間に第1のAl層704が形成され、かつ合金層110とゲート誘電体層108との間に第2のAl層706が形成される。Alの拡散が終了した後、pFET構造は約4.6eVより大きい実効仕事関数を持ち、約4.4eV未満の実効仕事関数を持つnFET構造 50

が必要に応じて形成される。

【0027】

一例では、pFET構造用のゲート電極の実効仕事関数は約4.6 から約5.6 eVまでである。他の例では、pFET構造用のゲート電極の実効仕事関数は約4.6 から約5 eVまでである。さらに他の例では、pFET構造用のゲート電極の実効仕事関数は約4.6 から約4.9 eVまでである。

【0028】

一例では、本実施形態の半導体装置は、製造工程時又は製造後に、少なくとも600 の温度に耐えうることができ、かつFET デバイスとしての機能を保持できる。他の例では、本実施形態の半導体装置は、製造工程時又は製造後に、約200 から約600 までの温度に耐えうることができ、かつFET デバイスとしての機能を保持できる。さらに他の例では、本実施形態の半導体装置は、製造工程時又は製造後に、約300 から約500 までの温度に耐えうことができ、かつFET デバイスとしての機能を保持できる。

10

【0029】

なお、本発明は上記した実施形態に限定されるものではなく、種々の変形が可能であることはいうまでもない。本発明は、論理ゲート半導体装置で頻繁に使用される、nFET構造を伴ったpFET構造の形成を実証するのに特に有用である。Reの拡散は、Reを含む層及び酸素を含む合金を含む層を有する任意の半導体装置において実施することができる。さらに、上記実施形態で説明した処理温度、処理圧力、処理時間等のパラメータ条件は適宜、変更が可能であることはいうまでもない。

20

【符号の説明】

【0030】

100、200、300、400、500、600、700...半導体装置、101...半導体基板、106...素子分離領域、108...ゲート誘電体層、110...合金層、112...Re層、202...ポリシリコン又はポリSiGe層、302、303...ゲート電極、304...ソース、305...ドレイン、306...チャネル、502...薄いRe酸化物層、504...Siを含む金属層、506...サイドオウールスペーサ、602...注入されたAl原子、604...Al原子、702...Al-Re 合金、704...第1のAl層、706...第2のAl層。

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

## フロントページの続き

(51)Int.Cl. F I

H 0 1 L 29/423 (2006.01)

H 0 1 L 29/49 (2006.01)

(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100103034

弁理士 野河 信久

(74)代理人 100119976

弁理士 幸長 保次郎

(74)代理人 100153051

弁理士 河野 直樹

(74)代理人 100140176

弁理士 砂川 克

(74)代理人 100101812

弁理士 勝村 紘

(74)代理人 100124394

弁理士 佐藤 立志

(74)代理人 100112807

弁理士 岡田 貴志

(74)代理人 100111073

弁理士 堀内 美保子

(74)代理人 100134290

弁理士 竹内 将訓

(74)代理人 100127144

弁理士 市原 卓三

(74)代理人 100141933

弁理士 山下 元

(72)発明者 土屋 義規

アメリカ合衆国、 カリフォルニア州 92612、 アーバイン、 マッカーサー・ブルバード 19900、 スイート400 東芝アメリカ電子部品社内

審査官 正山 旭

(56)参考文献 特開2008-84970 (JP, A)

特開2009-141161 (JP, A)

特表2011-509523 (JP, A)

特開平3-36734 (JP, A)

米国特許出願公開第2010/0013021 (US, A1)

特開平7-99290 (JP, A)

米国特許第5510651 (US, A)

E. Cartier et al., Role of Oxygen Vacancies in VFB/Vt stability of pFET metals on HfO<sub>2</sub>, 2005 Symposium on VLSI Technology Digest of Technical Papers, 米国, IEEE, 2005年6月14日, pp.230-231

Z. Li et al., Flatband voltage shift of ruthenium gated stacks and its link with the formation of a thin ruthenium oxide layer at the ruthenium/dielectric interface, Journal of Applied Physics, 米国, American Institute of Physics, 2007年2月6日, Vol. 101, pp.034503-1-9

(58)調査した分野(Int.Cl., DB名)

H 01 L 29 / 78

H 01 L 21 / 28

H 01 L 21 / 8238

H 01 L 27 / 092

H 01 L 29 / 423

H 01 L 29 / 49