(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5183875号

(P5183875)

(45) 発行日 平成25年4月17日(2013.4.17)

(24) 登録日 平成25年1月25日(2013.1.25)

(51) Int.Cl.

H01L 27/146 (2006.01)

H04N 5/374 (2011.01)

F 1

H01L 27/14

H04N 5/335 740

請求項の数 12 (全 10 頁)

(21) 出願番号 特願2006-17038 (P2006-17038)

(22) 出願日 平成18年1月26日 (2006.1.26)

(65) 公開番号 特開2006-352070 (P2006-352070A)

(43) 公開日 平成18年12月28日 (2006.12.28)

審査請求日 平成20年12月22日 (2008.12.22)

(31) 優先権主張番号 10-2005-0051555

(32) 優先日 平成17年6月15日 (2005.6.15)

(33) 優先権主張国 韓国 (KR)

(73) 特許権者 511234806

インテレクチュアル・ヴェンチャーズ・リミテッド・ライアビリティ・カンパニー

アメリカ合衆国ワシントン州98005、

ベルビュー、ワンハンドレッドアンドセーティーナインス・アヴェニュー・サウスイースト、3150、ビルディング 4

(74) 代理人 100099623

弁理士 奥山 尚一

(74) 代理人 100098769

弁理士 有原 幸一

(74) 代理人 100107319

弁理士 松島 鉄男

最終頁に続く

(54) 【発明の名称】コンパクトなピクセルレイアウトを有するCMOSイメージセンサ

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のピクセルがロー及びカラムに配列されたピクセルアレイを有するイメージセンサにおいて、

隣接するローにそれぞれ割り当てられる2個のフォトダイオード、及び該2個のフォトダイオードに共有される共通フローティング拡散領域を有する第1アクティブ領域と、

前記第1アクティブ領域と空間的に分離されて形成され、前記共通フローティング拡散領域の電荷に応答してピクセル信号を出力する駆動トランジスタを有する第2アクティブ領域と、

前記駆動トランジスタのゲートから連続するように形成されたポリシリコンバスと、

前記第2アクティブ領域の一部である前記駆動トランジスタのドレイン領域と、前記ポリシリコンバスとがオーバーラップされて形成されたキャパシタと、を備えることを特徴とするイメージセンサ。

## 【請求項 2】

前記第1及び第2アクティブ領域と空間的に分離されて形成され、前記ピクセルをリセットするリセットトランジスタを有する第3アクティブ領域をさらに備えることを特徴とする請求項1に記載のイメージセンサ。

## 【請求項 3】

前記第2アクティブ領域に形成されるローアドレス指定用のアドレス選択トランジスタをさらに備えることを特徴とする請求項2に記載のイメージセンサ。

10

20

**【請求項 4】**

前記ピクセルアレイから選択されたローを構成する前記ピクセルの前記駆動トランジスタのソース領域にパルスを印加することにより、ロードレス指定が行われることを特徴とする請求項2に記載のイメージセンサ。

**【請求項 5】**

前記第2アクティブ領域の別の一部である前記駆動トランジスタのドレイン領域は、ピクセル出力信号ラインに接続されることを特徴とする請求項2に記載のイメージセンサ。

**【請求項 6】**

前記駆動トランジスタのソース領域と、前記アドレス選択トランジスタのドレイン領域とは、前記第2アクティブ領域内の共通領域に形成されることを特徴とする請求項3に記載のイメージセンサ。10

**【請求項 7】**

前記第2アクティブ領域の一部である前記アドレス選択トランジスタのソース領域は、ピクセル出力信号ラインに接続されることを特徴とする請求項3に記載のイメージセンサ。10

**【請求項 8】**

前記ポリシリコンバスは、前記共通フローティング拡散領域及び前記第3アクティブ領域の一部である前記リセットトランジスタのソース領域と、電気的に接続することを特徴とする請求項5または請求項7に記載のイメージセンサ。

**【請求項 9】**

前記ポリシリコンバスと前記共通フローティング拡散領域とは、金属の第1接続線を介して接続され、20

前記ポリシリコンバスと前記リセットトランジスタのソース領域とは、金属の第2接続線を介して接続されることを特徴とする請求項8に記載のイメージセンサ。

**【請求項 10】**

前記駆動トランジスタのドレイン領域と前記第3アクティブ領域の別の一部である前記リセットトランジスタのドレイン領域とは、それぞれVDD電源線に接続されることを特徴とする請求項8に記載のイメージセンサ。

**【請求項 11】**

前記フォトダイオードは、ピンフォトダイオードであることを特徴とする請求項1～請求項3のいずれか一項に記載のイメージセンサ。30

**【請求項 12】**

前記駆動トランジスタは、NチャネルMOSトランジスタまたは空乏型PチャネルMOSトランジスタであることを特徴とする請求項1～請求項3のいずれか一項に記載のイメージセンサ。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、固体イメージセンサに関し、特に、4個または3個のトランジスタから構成されるコンパクトなレイアウトのピクセル、高感度、及び低い暗電流を有するCMOSイメージセンサに関する。40

**【背景技術】****【0002】**

通常のイメージセンサは、センサピクセルで収集された入射してきた光子を電子に変換することによって、光を感知する。収集サイクルの完了後に、電荷は電圧に変換されて、センサの出力端子に供給される。CMOSイメージセンサにおいて、電荷-電圧変換は、ピクセル自体内で直接行われ、アナログピクセル電圧は多様なピクセルアドレス指定及びスキーリング方式に基づいて出力端子に伝達される。このアナログ信号はまた、チップ出力に到達する前に、チップ上でデジタル信号に変換され得る。ピクセルは、通常はソースフォロアであるバッファ増幅器を備えている。このバッファ増幅器は、適切なアドレス指50

定トランジスタによってピクセルに接続されるセンスラインを駆動する。

#### 【0003】

電荷 - 電圧変換が完了し、その結果として生成された信号がピクセルから出力された後、ピクセルは新しい電荷を収集する準備のためにリセットされる。電荷検出ノードとしてフローティング拡散(Floating Diffusion)領域(以下、「FDノード」と記す)を使用するピクセルにおいて、このリセットは、FDノードを基準電圧に瞬間に導電接続するリセットトランジスタをターンオンすることにより行われる。このステップでは、収集された電荷を除去するが、周知のkTC - リセットノイズを生成する。kTCノイズは、所望の低ノイズ性能を達成する必要がある場合に、相關二重サンプリング(Correlated Double Sampling:以下、「CDS」と記す)信号処理により、信号から除去されなければならない。CDSの概念を利用する通常のCMOSセンサは、ピクセル内に4個のトランジスタ(以下、「4T」とも記す)を備える必要がある。

10

#### 【0004】

4Tのピクセル回路の例は、Guidashに付与された米国特許の明細書(特許文献1、特許文献2、特許文献3を参照)などに開示されている。また、VDDバイアスラインにスイッチングパルスを印加することによって、ピクセルからアドレス選択トランジスタを回路的に切り離し、3個のトランジスタ(以下、「3T」とも記す)のみを有するピクセルを用いてCDS動作を達成することもできる。これはMasahiro Kasanoの論文(非特許文献1を参照)に開示されている。

20

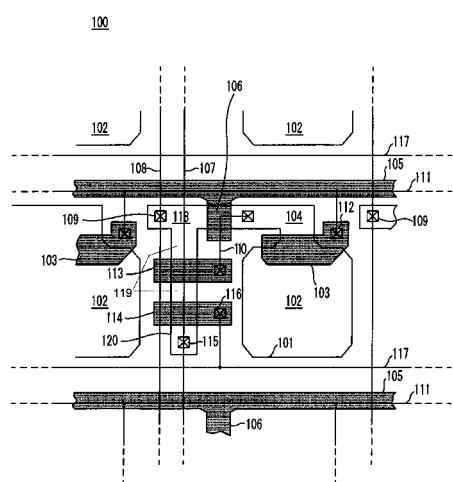

#### 【0005】

図1は、ピンフォトダイオード及び全てのトランジスタが共通のアクティブ領域を有する、従来の標準的な4Tイメージセンサを示す簡素化されたレイアウト図である。

#### 【0006】

図1において、参考番号100は、典型的なCMOSイメージセンサに使用される従来の4Tを含むピクセルアレイを表す。複数のこのようなピクセルは、実際のイメージセンサにおいてロー(rows)及びカラム(columns)に配列されてアレイを形成するが、図面の簡素化のため、ここでは、1つのピクセルのみが詳細に示されている。アクティブ領域101は、ピクセルの全ての能動素子、すなわち、ピンフォトダイオード102、トランスファトランジスタ(103はそのゲート)、FDノード104、リセットトランジスタ(106はそのゲート)、ドレインバイアスノード118、ソースフォロア(SF)の機能を果たす駆動トランジスタ(113はそのゲート、119はそのソース・ドレン領域)、及びアドレス選択トランジスタ(114はそのゲート、120はそのソース)を備えている。

30

#### 【0007】

取り囲まれたアクティブ領域101の外側の領域は、この技術分野で周知のような、厚い素子分離酸化膜で充填されたSTI(Shallow Trench Isolation)領域である。また、図1において、ピクセル内に存在する多層の金属インターポネクトは、図面の明瞭さのために省略され、代わりに接続ラインによって概略的に示されている。ライン117は、アドレス選択トランジスタのゲート114のコンタクト116に接続されるロー・アドレスラインであり、ライン111は、トランスファトランジスタのゲート103のコンタクト112に接続されるロー・トランスファラインであり、ポリシリコンバス105は、ピクセルのリセットトランジスタのゲート106にローリセット信号を供給する。カラムライン108は、コンタクト109を介してドレインバイアスノード118にVDDバイアスを提供し、カラムライン107は、コンタクト115を介してアドレス選択トランジスタのソース120からの出力信号をアレイ周辺に位置するカラム信号処理回路に伝達する。FDノード104は、インターポネクト110を介して駆動トランジスタのゲート113に接続される。また、アドレス指定信号と、リセット信号とがそれぞれライン117及びコンタクト116と、ポリシリコンバス105とを介してアレイの周辺領域からピクセルに供給される。

40

50

**【0008】**

図1のピクセルは、正しく機能するものの、2つの主な短所がある。すなわち、あまりにも多くのトランジスタが大きなピクセル領域を占めてしまい、また、フォトダイオードを構成するアクティブ領域とその他のトランジスタを構成するアクティブ領域とが空間的に接続しているため、トランジスタの位置及びその相互接続配線を効率的に配列できない。よって、低費用と高解像度のイメージセンサを設計するためにピクセルサイズを低減する必要がある時、各ピクセル内の多数のトランジスタの存在は問題となり得る。

**【0009】**

この問題を解決するために、上述の米国特許では、異なるローに配置される隣接するピクセルのフォトダイオードを4Tの読み出し回路が共有する技術を開示している。

10

**【0010】**

しかしながら、このような従来の4Tイメージセンサピクセルでは、コンパクトなレイアウトが依然として困難であり、また、ピクセル信号の読み出しのためのトランジスタ(特に、リセットトランジスタ)を構成するアクティブ領域とフォトダイオードを構成するアクティブ領域とが空間的に接続しているため、関連のピクセル要素の位置及びその相互内部接続配線が効率的に配列できないという問題がある。

**【非特許文献1】** "A 2.0  $\mu$ m Pixel Pitch MOS Image Sensor with an Amorphous Si Film Color Filter." (Digest of Technical Papers ISCC、vol.48、Feb.2005、pp.348-349)

20

**【特許文献1】** 米国特許第6,107,655号明細書

**【特許文献2】** 米国特許第6,352,869号明細書

**【特許文献3】** 米国特許第6,657,665号明細書

**【発明の開示】****【発明が解決しようとする課題】****【0011】**

本発明は、上記したような従来の技術の問題点を解決するためになされたものであり、その目的は、高解像度、高性能、及びコンパクトサイズの実用的なCMOSイメージセンサを提供することにある。

**【課題を解決するための手段】**

30

**【0012】**

本発明の目的は、イメージセンサにおいて、リセットトランジスタを、フローティング拡散領域(電荷検出ノード)から空間的に分離された独立のアクティブ領域に配置することによって達成される。

**【0013】**

また、本発明に係るイメージセンサのピクセルは、電荷検出ノードであるフローティング拡散領域とソースフォロアの機能を果たす駆動トランジスタのドレインとの間に電気的に接続されるキャパシタを備えている。このキャパシタは、駆動トランジスタのゲートに延びるポリシリコンバスと駆動トランジスタのドレイン領域とをオーバーラップさせることにより形成される。そして、そのオーバーラップ量を調整して、キャパシタのキャパシタンスを変化させることができる。このような特徴は、変換利得、そしてセンサの感度を調整するのに重要である。適切な値のキャパシタンスは、またセンサのダイナミックレンジ(Dynamic Range:以下、「DR」と記す)及び信号対雑音比(SNR)を決定する。

40

**【0014】**

また、本発明に係るイメージセンサのピクセルは、受光素子がピンフォトダイオードを用いて構成されるため、フォトダイオード領域内のシリコン-シリコン酸化膜界面の近くに配置される浅いP型注入領域(すなわち、pinning layer)を使用して、界面準位を消滅することによって、低い暗電流を維持する。

**【0015】**

50

また、本発明に係るイメージセンサにおいて、駆動トランジスタは、NチャネルMOSトランジスタ又はPチャネルMOSトランジスタで具現でき、特に、空乏型PチャネルMOSトランジスタで具現する場合、ノイズの特性を改善することができる。

#### 【0016】

具体的に、本発明の一側面によるイメージセンサは、複数のピクセルがロー及びカラムに配列されたピクセルアレイを有するイメージセンサにおいて、隣接するローにそれぞれ割り当てられる2個のフォトダイオード及び該2個のフォトダイオードに共有される共通フローティング拡散領域を有する第1アクティブ領域と、前記第1アクティブ領域と空間的に分離されて形成され、前記ピクセルをリセットさせるリセットトランジスタを有する第2アクティブ領域と、前記第1及び第2アクティブ領域と空間的に分離されて形成され、前記共通フローティング拡散領域の電荷に応答してピクセル信号を出力する駆動トランジスタを有する第3アクティブ領域とを備える。

10

#### 【0017】

本発明の他の一側面によるイメージセンサは、複数のピクセルがロー及びカラムに配列されたピクセルアレイを有するイメージセンサにおいて、隣接するローにそれぞれ割り当てられる2個のフォトダイオード及び該2個のフォトダイオードに共有される共通フローティング拡散領域を有する第1アクティブ領域と、前記第1アクティブ領域と空間的に分離されて形成され、前記共通フローティング拡散領域の電荷に応答してピクセル信号を出力する駆動トランジスタを有する第2アクティブ領域と、前記駆動トランジスタのゲートから連続するように形成されたポリシリコンバスと、前記第2アクティブ領域の一部である前記駆動トランジスタのドレイン領域及び前記ポリシリコンバスがオーバーラップされて形成されたキャパシタとを備える。

20

#### 【0018】

本発明の上記2つの側面において、前記フォトダイオードは、ピンフォトダイオードから構成され得るし、前記駆動トランジスタは、NチャネルMOSトランジスタまたは空乏型PチャネルMOSトランジスタで具現され得る。

#### 【発明の効果】

#### 【0019】

本発明によれば、高性能、簡単な構造及び小型サイズの3T及び4Tのピクセルを有する実用的なCMOSイメージセンサを提供することができる。

30

#### 【発明を実施するための最良の形態】

#### 【0020】

以下、本発明の最も好ましい実施の形態を図面を参照しながら説明する。

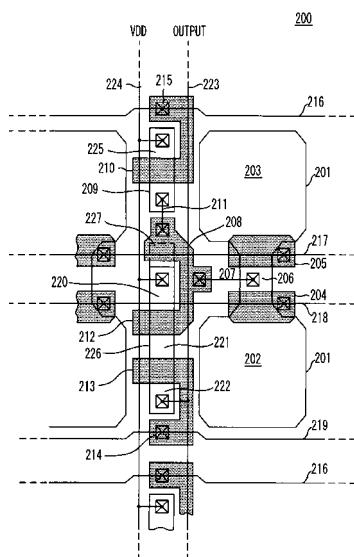

#### 【0021】

図2は、トランスファゲート、リセットトランジスタ、アドレス選択トランジスタ、駆動トランジスタ(ソースフォロア)、及びピンフォトダイオードを有し、空間的に分離された複数のアクティブ領域を有する、本発明の一実施の形態に係るCMOSイメージセンサの平面図であって、ローを共有するピクセルの簡素化されたレイアウトを示す。

#### 【0022】

図2に示されているように、ピクセルアレイ200は、共通回路を共有する1対のピンフォトダイオード202、203を有する2つのピクセルローを備えている。ここでも、金属層は、図面簡素化のために省略され、概略的な相互接続線によって示されている。もちろん、本実施の形態におけるピクセルもまた複数のロー及びカラムに配列されてアレイを形成する。

40

#### 【0023】

本発明のロー共有ピクセルの特徴は、ピクセル内のアクティブ領域を3つの異なるブロックに分離する点である。特に、第1アクティブ領域201は、一对のピンフォトダイオード202、203を備え、第2アクティブ領域209は、リセットトランジスタのためのものであり、第3アクティブ領域226は、駆動トランジスタ及びアドレス選択トランジスタのためのものである。第1アクティブ領域201は、またトランスファゲート20

50

4、205及び電荷検出用の共通フロー・テイキング拡散領域（以下「共通FDノード」と記す）206を備える。金属の第1相互接続線207は、共通FDノード206を、駆動トランジスタのゲート212と接続するポリシリコンバス208に接続させる。金属の第2相互接続線211は、またポリシリコンバス208をリセットトランジスタのソースに接続させる。

#### 【0024】

リセット信号がコンタクト215を介して第1ローバスライン216からリセットトランジスタのゲート210に供給される。リセットトランジスタのドレイン225がドレインカラムバスライン（以下、第1カラムバスラインと記す）224に接続される。同様に、駆動トランジスタのドレイン220と同じ第1カラムバスライン224に接続される。

第1カラムバスライン224は、VDD電源ラインである。駆動トランジスタのソース221は、ゲート213がコンタクト214を介して第2ローバスライン219からロードレス指定信号を受信するアドレス選択トランジスタのドレインとは共通である。

10

#### 【0025】

アドレス選択トランジスタのソース222で出力信号が感知され、このソース222はもう1つのカラムバスライン（以下、第2カラムバスラインと記す）223に接続される。ここでは、第2カラムバスライン223は、ピクセル出力信号ラインである。

#### 【0026】

トランスファゲートバスライン217、218は、アレイ200の周辺に位置する回路で生成される適切な電荷伝達信号をトランスファゲート205、204に供給する。第1及び第2カラムバスライン224、223もまた、アレイ200の周辺に位置する回路に接続され、この周辺回路は、必要なバイアスを供給し、アドレス指定されたピクセルからの出力信号を処理する。これらは、図示されていないが、この技術分野における通常の知識を有する者にとっては、周知のものである。

20

#### 【0027】

図2から分かるように、本実施の形態では、従来の4Tを有するピクセルのアクティブ領域を3つの異なるブロックに分割し、2つのローにそれぞれ属する2つのフォトダイオードが同じピクセル信号感知回路を共有することによって、ピクセルの効率的なレイアウトが可能となる。本実施の形態のレイアウトは、より高い開口率を有するため、より高性能のセンサの実現を可能にする。

30

#### 【0028】

一方、ポリシリコンバス208下の第3アクティブ領域226を破線227で示すように延ばすことによって、共通FDノード206と駆動トランジスタのドレイン220との間に電気的に接続されるキャパシタを形成できる。ポリシリコンバス208と第3アクティブ領域226との間のオーバーラップ量を調整して、キャパシタのキャパシタンスを変化させることができる。この特徴は変換利得、そしてセンサの感度を調整するのに重要である。適切な値のキャパシタンスは、またセンサのダイナミックレンジ(DR)及び信号対雑音比(SNR)を決定する。

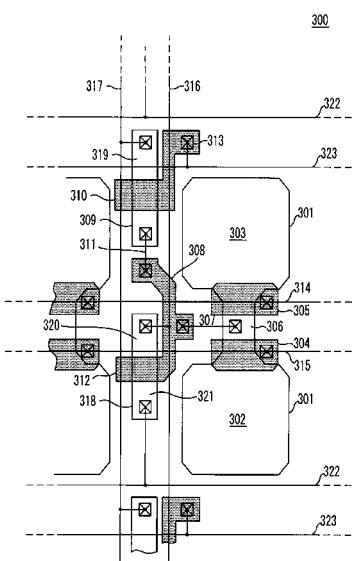

#### 【0029】

図3は、本発明の別の実施の形態に係るCMOSイメージセンサの平面図であって、ロードレス指定のためのアドレス選択トランジスタが省略される場合におけるロー共有ピクセルの簡素化されたレイアウトを示す。

40

#### 【0030】

図3に示されている本実施の形態に係るピクセルアレイ300は、図2に示されたものと類似したレイアウトを有し、アクティブ領域は同様に3つの個別領域に分離されている。第1アクティブ領域301は、ピンフォトダイオード302、303、トランスファゲート304、305及び共通FDノード306を備える。ほかの2つの異なるアクティブ領域、即ち第2アクティブ領域309及び第3アクティブ領域318はそれぞれ、ゲート310及びドレイン319を有するリセットトランジスタ、並びにゲート312、ソース321及びドレイン320を有する駆動トランジスタを備える。この構成において、アド

50

レス選択トランジスタは省略され、Kasanoにより開示されたもののように、電源線322をパルスする外部回路によって代替される。

#### 【0031】

第1相互接続線307は、共通F Dノード306をポリシリコンバス308に接続させる。第2相互接続線311は、ポリシリコンバス308をリセットトランジスタのソースに接続させる。リセットトランジスタのゲート310は、そのリセットパルスをリセットライン323からコントラクト313を介して受信する。ピクセルは、電源線322によってアドレス指定されるが、電源線322は、駆動トランジスタのソース321に接続されて、駆動トランジスタをターンオンさせる。出力信号は、駆動トランジスタのドレイン320から検出され、このドレイン320は、カラムバスライン316に接続される。別のカラムバスライン317は、リセットトランジスタのドレイン319にバイアスを供給する。10

#### 【0032】

また、上記の実施の形態と同様に、ポリシリコンバス308とオーバーラップしてキャパシタを形成するように、第3アクティブ領域318を拡張することができる。この拡張されたキャパシタは図面を明瞭にし簡素化するために、図示されていない。トランスマッゲートバスライン314、315は、トランスマッゲート304、305に伝達パルスを供給する。パルスは、図示されていない周辺回路で生成される。また、この技術分野における通常の知識を有する者にとって周知であるように、出力信号も周辺回路で処理される。20

#### 【0033】

本実施の形態の長所は、1ピクセル当たり2つのトランジスタのみを有するので、適度な設計ルールを使用しても、非常に小さなピクセルサイズの高性能イメージセンサを設計することができるという点である。

#### 【0034】

また、上記の2つの実施の形態は、フォトダイオード領域202、203、302、303内のシリコン-シリコンダイオキサイド界面に注入されるp<sup>+</sup>ホウ素不純物を有するピンフォトダイオードを用いる。この不純物注入は、周知のように、界面準位をクエンチングして、低い暗電流の生成を可能にする。

#### 【0035】

上記した新しいレイアウトの長所はまた、ピクセルのトランジスタがより小さな領域を占めることによって実現される、高い開口率である。

#### 【0036】

また、本発明において、駆動トランジスタは、NチャネルMOSトランジスタまたはPチャネルMOSトランジスタで具現できる。特に、空乏型PチャネルMOSトランジスタで具現するならば、ノイズ特性を改善することができる。

#### 【0037】

以上では、3T及び4Tを有するピクセルをコンパクトにレイアウトした本発明の好ましい実施の形態に関して説明したが、本発明は、上記説明した実施の形態に限定されるものではなく、特許請求の範囲によって定められる技術的思想及び分野から逸脱しない範囲内で上記説明した実施の形態に対して様々な変更が可能であり、それらも本発明の技術的範囲に属することは明らかである。40

#### 【図面の簡単な説明】

#### 【0038】

【図1】ピンフォトダイオード及び全てのトランジスタが共通アクティブ領域を有する、従来の4Tを有するイメージセンサの簡素化されたレイアウトを示す図である。

【図2】トランスマッゲート、リセットトランジスタ、アドレス選択トランジスタ、駆動トランジスタ(ソースフォロア)、及びピンフォトダイオードを収容し、空間的に分割された複数のアクティブ領域を有する、本発明の実施の形態に係るローを共有するピクセルの簡素化されたイメージセンサのレイアウト図である。50

【図3】本発明の別の実施の形態に係るアドレス選択トランジスタが省略された場合における、ローを共有するピクセルの簡素化されたイメージセンサのレイアウト図である。

【符号の説明】

【0039】

|                                      |                               |    |

|--------------------------------------|-------------------------------|----|

| 100、200、300                          | ピクセルアレイ                       |    |

| 101                                  | アクティブ領域                       |    |

| 102、202、203、302、303                  | ピンフォトダイオード                    |    |

| 103、204、205、304、305<br>トランジスタのゲート)   | トランスマルチゲート(トランスマルチ<br>トランジスタ) |    |

| 104、206、306<br>FDノード)                | 共通フローティング拡散領域(共通<br>ドレインノード)  | 10 |

| 105、208、308                          | ポリシリコンバス                      |    |

| 106、210、310                          | リセットトランジスタのゲート                |    |

| 107、108                              | カラムライン                        |    |

| 109、112、115、116、214、215、313<br>コンタクト | コンタクト                         |    |

| 110                                  | インターフェース                      |    |

| 111                                  | ロートランスマルチゲート                  |    |

| 113、212、312                          | 駆動トランジスタのゲート                  |    |

| 114、213                              | アドレス選択トランジスタのゲート              |    |

| 118                                  | ドレインバイアスノード                   | 20 |

| 117                                  | ロードレスライン                      |    |

| 119<br>ン領域                           | 駆動トランジスタのソース・ドレイ<br>ン         |    |

| 120、222                              | アドレス選択トランジスタのソース              |    |

| 201、301                              | 第1アクティブ領域                     |    |

| 207、307                              | 第1相互接続線                       |    |

| 209、309                              | 第2アクティブ領域                     |    |

| 211、311                              | 第2相互接続線                       |    |

| 216                                  | 第1ローバスライン                     |    |

| 217、218、314、315                      | トランスマルチゲートバスライン               | 30 |

| 219                                  | 第2ローバスライン                     |    |

| 220、320                              | 駆動トランジスタのドレイン                 |    |

| 221、321                              | 駆動トランジスタのソース                  |    |

| 223                                  | 第2カラムバスライン                    |    |

| 224                                  | 第1カラムバスライン                    |    |

| 225、319                              | リセットトランジスタのドレイン               |    |

| 226、318                              | 第3アクティブ領域                     |    |

| 316、317                              | カラムバスライン                      |    |

| 322                                  | 電源線                           |    |

| 323                                  | リセットライン                       | 40 |

【図1】

【図2】

【図3】

---

フロントページの続き

(74)代理人 100114591

弁理士 河村 英文

(74)代理人 100125380

弁理士 中村 綾子

(74)代理人 100142996

弁理士 森本 聰二

(74)代理人 100154298

弁理士 角田 恭子

(74)代理人 100166268

弁理士 田中 祐

(74)代理人 100170379

弁理士 德本 浩一

(74)代理人 100161001

弁理士 渡辺 篤司

(74)代理人 100118407

弁理士 吉田 尚美

(74)代理人 100125036

弁理士 深川 英里

(72)発明者 ヤロスラフ ハイネセク

アメリカ合衆国 75013 テキサス アレン パムパ ドライブ 905

審査官 柴山 将隆

(56)参考文献 特開平10-256520(JP,A)

特開2006-196884(JP,A)

特開2001-298177(JP,A)

特開2000-232216(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 27/146

H04N 5/374