(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-294295

(P2005-294295A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>H01L 21/822

H01L 21/331

H01L 27/04

H01L 29/732

F 1

H01L 27/04

H01L 29/72H

P

テーマコード(参考)

5FO03

5FO38

審査請求 未請求 請求項の数 1 O L (全 6 頁)

(21) 出願番号

特願2004-102505 (P2004-102505)

(22) 出願日

平成16年3月31日 (2004.3.31)

(71) 出願人 000191238

新日本無線株式会社

東京都中央区日本橋横山町3番10号

(72) 発明者 林 智則

埼玉県上福岡市福岡二丁目1番1号 新日本無線株式会社川越製作所内

F ターム(参考) 5F003 AP01 AP08 BA97 BB06 BB08

BC08 BE08 BJ90 BP04 BP31

5F038 BH06 BH13 BH16 EZ12 EZ20

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】 大電流が発生しても破壊することのない静電破壊保護素子を備えた半導体装置を提供する。

【解決手段】 バイポーラトランジスタで静電破壊保護素子を形成し、ベース領域表面に、エミッタ領域を取り囲むように形成された、ベース領域より不純物濃度が高い一導電型の高濃度領域を備え、静電破壊保護素子の高濃度領域と前記エピタキシャル層とで構成するP N接合に電流を流す。また、静電破壊保護素子のエミッタ領域とベース領域とで構成するP N接合に電流を流す。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

一導電型のエピタキシャル層が形成された半導体基板上に、該半導体基板と前記エピタキシャル層との間の一導電型の埋込層と前記エピタキシャル層表面から前記埋込層に達する一導電型の拡散層で構成されるコレクタ領域と、前記エピタキシャル層表面に形成された逆導電型の拡散領域からなるベース領域と、該ベース領域表面に形成された一導電型の拡散領域からなるエミッタ領域と、該エミッタ領域と前記ベース領域とを接続する第1の電極と、前記コレクタ領域に接続する第2の電極とからなる静电破壊保護素子を備え、内部回路を静电破壊から保護する半導体装置において、

前記ベース領域に接し、前記エミッタ領域を取り囲むように配置した、前記ベース領域より不純物濃度が高い一導電型の高濃度領域を備え、 10

前記第1の電極及び前記第2の電極間の印加電圧が上昇したとき、前記静电破壊保護素子の前記高濃度領域と前記エピタキシャル層とで構成するPN接合に電流を流し、

前記第1の電極及び前記第2の電極間の印加電位がさらに上昇し、前記ベース領域に印加する電位が上昇したとき、前記静电破壊保護素子の前記エミッタ領域と前記ベース領域とで構成するPN接合に電流を流すことを特徴とする半導体装置。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は静电破壊保護素子を備えた半導体装置に関し、特に大電流が流れた場合でも破損しない静电破壊保護素子を備えた半導体装置に関する。 20

## 【背景技術】

## 【0002】

一般に半導体装置は、静电気による破壊を受けやすい。そのため、入出力電極と内部回路との間には、静电破壊保護素子を備えるのが一般的である（特許文献1参照）。

## 【0003】

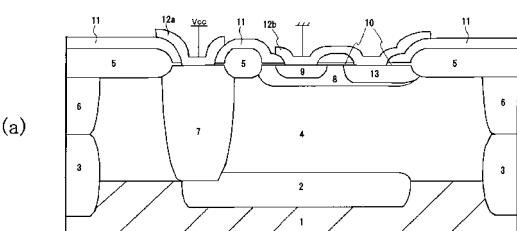

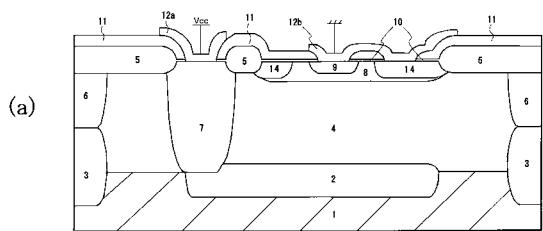

この種の静电破壊保護素子の一例を図2(a)に示す。図2(a)において、1はP型半導体基板、2はコレクタ領域の一部を構成するN<sup>+</sup>型埋込層、3は分離領域の一部を構成するP<sup>+</sup>型埋込層、4はN型エピタキシャル層、5はLOCOS酸化膜、6はP<sup>+</sup>型埋込層3と共に分離領域を構成するP型拡散層、7はN<sup>+</sup>型埋込層2と共にコレクタ領域の一部を構成するN型コレクタ領域、8はP型ベース領域、9はN型エミッタ領域、10は酸化膜、11は層間絶縁膜、12a、12bはアルミニウム配線、13はP<sup>+</sup>型拡散層を示している。 30

## 【0004】

図2(a)に示す静电破壊保護素子は、内部回路を構成するNPNバイポーラトランジスタと同時形成される。まず、P型半導体基板1上にコレクタ領域の一部を構成するN<sup>+</sup>型埋込層2と分離領域の一部を構成するP<sup>+</sup>型埋込層3を形成するため、イオン注入し、拡散を行う。その後、N型エピタキシャル層4を成長させ、N<sup>+</sup>型埋込層2とP<sup>+</sup>型埋込層3を形成する。N型エピタキシャル層4表面から不純物イオンを注入し、先に形成したP<sup>+</sup>型埋込層3に達するP型拡散層6を形成することで、分離領域を形成する。LOCOS酸化膜5を形成した後、コレクタ領域形成予定領域に不純物イオンを注入し、先に形成したN<sup>+</sup>型埋込層2に達するN型コレクタ領域7を形成し、コレクタ領域を形成する。次に表面に酸化膜10を形成する。ベース領域形成予定領域に不純物イオンを注入し、P型ベース領域8を形成する。同様に、エミッタ領域形成予定領域に、酸化膜10を通して不純物イオンを注入し、N型エミッタ領域9を形成する。P型ベース領域8に接続するベース取り出し領域を形成するため、不純物イオンを注入し、P<sup>+</sup>型拡散層13を形成する。層間絶縁膜11を形成した後、N型コレクタ領域7、N型エミッタ領域9、P<sup>+</sup>型拡散層13上の酸化膜10を除去し、N型コレクタ領域7に接続するアルミニウム配線12a、P型ベース領域8及びN型エミッタ領域9に接続するアルミニウム配線12bを形成する。アルミニウム配線12aは電源電圧電位(Vcc)に、アルミニウム配線12bは接地電 40

位に接続し、静電保護素子を完成する。

【0005】

このような構造の静電破壊保護素子では、N型コレクタ領域7を接続したアルミニウム配線12aに強い負電圧が印加した場合、N型エピタキシャル層4とP<sup>+</sup>型拡散層13とのPN接合の順方向に電流が流れ、電荷はP<sup>+</sup>型拡散層13とN型エミッタ領域9を短絡させて接地したアルミニウム配線12b側に排出される。この場合、PN接合は順方向特性となり、静電保護素子の破壊電流は十分大きく、PN接合に大電流が流れても、静電保護素子が破壊されることはない。

【0006】

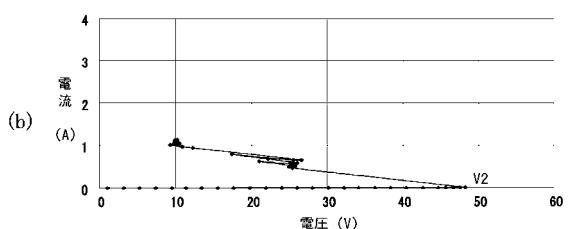

一方、N型コレクタ領域を接続したアルミニウム配線12aに強い正電圧が印加した場合の電流電圧特性を図2(b)に示す。上述の負電圧が印加したときと異なり、印加電圧が上昇するに従い、PN接合の逆方向電流が徐々に増加し、N<sup>+</sup>型埋込層2に逆方向電流が流れ込み、電圧降下によって、P型ベース領域8の電位は上昇する。この電位が図2(b)のアバランシュ・ブレイクダウン現象を発生させる電圧V2に達すると、その瞬間、NPN型バイポーラトランジスタがオンし、P<sup>+</sup>型拡散層13とN型エピタキシャル層4間を大電流が通過し、接地に電荷を排出する構成となっている。

【特許文献1】特開2001-144191号

【発明の開示】

【発明が解決しようとする課題】

【0007】

図2(a)に示す構造の静電破壊保護素子において、N型エミッタ領域9周囲の抵抗値が高く、電流が流れにくい。そのため、アバランシュ・ブレイクダウン現象が発生し大電流が通過するとき、N型エミッタ領域9周囲の電流通路で高熱が発生し、静電破壊保護素子が破壊してしまうという問題があった。静電破壊保護素子の破壊を防ぐため、エミッタ面積を大きくしても、N型エミッタ領域9周囲の抵抗値が高く、電流が流れにくく、静電破壊保護素子の破壊を防ぐことができなかつた。そこで本発明は、大電流が発生しても破壊することのない静電破壊保護素子を備えた半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記目的を解決するため本発明は、一導電型のエピタキシャル層が形成された半導体基板上に、該半導体基板と前記エピタキシャル層との間の一導電型の埋込層と前記エピタキシャル層表面から前記埋込層に達する一導電型の拡散層で構成されるコレクタ領域と、前記エピタキシャル層表面に形成された逆導電型の拡散領域からなるベース領域と、該ベース領域表面に形成された一導電型の拡散領域からなるエミッタ領域と、該エミッタ領域と前記ベース領域とを接続する第1の電極と、前記コレクタ領域に接続する第2の電極とからなる静電破壊保護素子を備え、内部回路を静電破壊から保護する半導体装置において、前記ベース領域に接し、前記エミッタ領域を取り囲むように配置した、前記ベース領域より不純物濃度が高い一導電型の高濃度領域を備え、前記第1の電極及び前記第2の電極間の印加電圧が上昇したとき、前記静電破壊保護素子の前記高濃度領域と前記エピタキシャル層とで構成するPN接合に電流を流し、前記第1の電極及び前記第2の電極間の印加電位がさらに上昇し、前記ベース領域に印加する電位が上昇したとき、前記静電破壊保護素子の前記エミッタ領域と前記ベース領域とで構成するPN接合に電流を流すことを特徴とするものである。

【発明の効果】

【0009】

本発明の半導体装置は、コレクタ領域に大きな正の電圧が印加したとき、アバランシュ・ブレイクダウンが起こるまで電圧が上昇し、ベース領域とエミッタ領域で構成するPN接合に電流を流すことにより、高熱が発生しない構造とした。その結果、熱起因による静電破壊保護素子の破壊を防止することができる。また高熱が発生しないため、PN接合間に流れる電流値を大きくすることができる。

10

20

30

40

50

## 【発明を実施するための最良の形態】

## 【0010】

本願発明の静電破壊保護素子は、上述のように静電気などの急激な電位変化に対し、高濃度領域とエミッタ領域との間に大電流を流すことができるよう、エミッタ領域の近傍に、ベース領域より不純物濃度の高い高濃度領域を、エミッタ領域を取り囲むように配置している。以下本願発明に関して詳細に説明する。

## 【実施例1】

## 【0011】

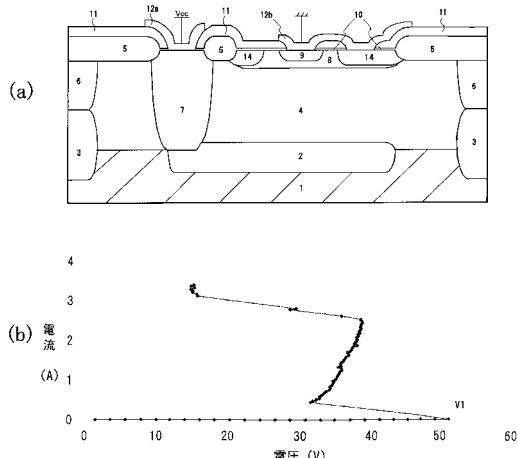

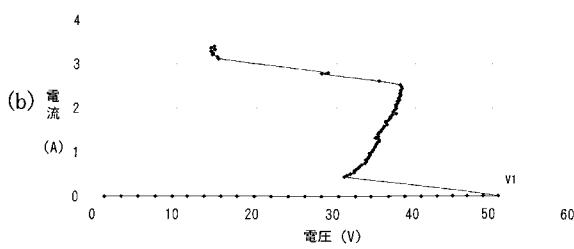

図1に、本願発明に係る静電破壊保護素子をNPN型バイポーラトランジスタで構成した断面図を示す。本発明に係る静電破壊保護素子は、次のように形成することができる。まずP型半導体基板1上に、コレクタ領域の一部を構成するN<sup>+</sup>型埋込層2、分離領域の一部を構成するP<sup>+</sup>型埋込層3を形成するため、不純物イオンを注入する。その後、N型エピタキシャル層4を厚さ5μm程度成長させる。先に形成したP<sup>+</sup>型埋込層3に接続するP型拡散層6を形成し、素子分離層を形成する。さらにN型エピタキシャル層4の表面にLOCOS酸化膜5を形成する。その後、N<sup>+</sup>型埋込層2に達するN型コレクタ領域7を形成する。次に、P型ベース領域8を形成する。

## 【0012】

露出する表面に酸化膜10を形成した後、N型エミッタ領域9を形成する。次にP<sup>+</sup>型の高濃度不純物層14を形成する。高濃度不純物層14は、N型エミッタ領域9の端部から1μm程度離れた周辺にその端部を配置し、N型エミッタ領域9の周囲を取り囲むように形成する。また高濃度不純物層14の一部は、N型コレクタ領域7側のN型エピタキシャル層4と接するように配置するのが好ましい。

## 【0013】

その後、層間絶縁膜11を全面に形成し、N型コレクタ領域7、高濃度不純物層14及びN型エミッタ領域9表面を露出し、それぞれに接続するアルミニウム配線12a、12bを形成する。アルミニウム配線12aは電源電圧電位(Vcc)に、アルミニウム配線12bは接地電位にそれぞれ接続し、静電破壊保護素子を完成する。

## 【0014】

以上のような静電破壊保護素子を備えた半導体装置は、アルミニウム配線12aに過剰な負電圧が印加した場合、N型エピタキシャル層4と高濃度不純物層14とのPN接合の順方向特性により、電荷を接地に排出する。

## 【0015】

またアルミニウム配線12aに過剰な正電圧が印加した場合には、図1(b)に示す電気的特性を示すことになる。すなわち、N型エピタキシャル層4と高濃度不純物層14とのPN接合は逆方向であるため空乏層が広がり、電流は流れない。しかし、アバランシェ・ブレイクダウン現象によって電圧V1に達すると、PN接合を逆方向電流が流れる。流れる電流が徐々に増加すると、N型埋込層2に逆方向電流が流れ込み、電圧降下によってP型ベース領域8の電位が上昇する。この電位の上昇により、NPNトランジスタがオンし、N型エピタキシャル層4、高濃度不純物層14、P型ベース領域8、N型エミッタ領域9からなるNPN接合に逆方向電流が流れ、アルミニウム配線12aからアルミニウム配線12bへ大電流を流すことができ、電荷を接地に排出する。

## 【0016】

特に本発明では、高濃度不純物層14によって、N型エミッタ領域9の周囲の抵抗を低くすることができるため、P型ベース領域8周辺に高抵抗の部分が発生する事がないので、N型エミッタ領域9周辺のP型ベース領域8が高温とならない。しかも、N型エミッタ領域9を取り囲むように高濃度不純物層14を配置しているため、電流が集中する事がない。その結果、熱起因による素子破壊を防止することができる。

## 【0017】

なお本実施例中ではN型エミッタ領域9と高濃度不純物層14との間の寸法を1μmとしたが、N型エミッタ領域9と高濃度不純物層14が接触せず、抵抗が高くならない範囲

10

20

30

40

50

で適宜設定可能である。また、静電破壊保護素子の電圧V1、N型エピタキシャル層4と高濃度不純物層14とのPN接合、P型ベース領域8とN型エミッタ領域9とのPN接合に流れる電流値は、それぞれの半導体領域の不純物濃度、寸法等を適宜設定することで、所望の値に設定することができる。

#### 【0018】

たとえば、図1(b)に示す特性を示す静電破壊保護素子は、N型エピタキシャル層4の比抵抗が5×cm、厚さが5μm、エミッタサイズが6μm×50μm、高濃度不純物層14の幅が4μmの場合を示しているが、エミッタ幅のみを広くすることで、静電破壊保護素子に流すことができる電流値を大きくすることができる。

#### 【0019】

また、高濃度不純物層14幅を2μmとした場合、4μmの場合と比較して静電破壊保護素子の破壊電流(破壊に至る電流値)が減少し、ばらつくことが確認された。具体的には、高濃度不純物層14幅が4μmの場合、平均破壊電流2.5A、バラツキ1.12%であったものが、幅2μmの場合は、平均破壊電流1.98A、バラツキ9.62%となることを確認している。従って、上記電圧V1が大きい場合、高濃度不純物層14幅をひろげ、バラツキ等が小さくなる幅に設定する必要がある。

#### 【0020】

なお本発明では、電流をより分散して流すことができるよう、N型エミッタ領域9の周囲全部を取り囲むように高濃度不純物層14を配置する必要がある。それは、エミッタサイズ、高濃度不純物層の幅等の形成条件は同一で、高濃度不純物層をエミッタ領域の周辺を取り囲むように配置した場合と、コレクタ領域側のみに配置した場合とを比較したとき、前者の平均破壊電流が2.5A、バラツキが1.12%であったものが、後者の平均破壊電流は1.68Aに低下し、バラツキは12.5%に増大することを確認しているからである。

#### 【図面の簡単な説明】

#### 【0021】

【図1】本願発明の半導体装置の一実施例を説明する図である。

【図2】従来のこの種の半導体装置を説明する図である。

#### 【符号の説明】

#### 【0022】

1:P型半導体基板、2:N<sup>+</sup>型埋込層、3:P<sup>+</sup>型埋込層、4:N型エピタキシャル層、5:LOCOS層、6:P型拡散層、7:N型コレクタ領域、8:P型ベース領域、9:N型エミッタ領域、10:酸化膜、11:絶縁酸化膜、12a、12b:アルミニウム配線、13:P<sup>+</sup>型拡散層、14:高濃度不純物層

【図1】

【 図 2 】