(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6157811号

(P6157811)

(45) 発行日 平成29年7月5日(2017.7.5)

(24) 登録日 平成29年6月16日(2017.6.16)

(51) Int.Cl.

G06F 9/445 (2006.01)

F 1

G06F 9/06

610K

請求項の数 6 外国語出願 (全 14 頁)

(21) 出願番号 特願2012-166673 (P2012-166673)

(22) 出願日 平成24年7月27日 (2012.7.27)

(65) 公開番号 特開2013-178733 (P2013-178733A)

(43) 公開日 平成25年9月9日 (2013.9.9)

審査請求日 平成27年6月18日 (2015.6.18)

(31) 優先権主張番号 13/193,718

(32) 優先日 平成23年7月29日 (2011.7.29)

(33) 優先権主張国 米国(US)

前置審査

(73) 特許権者 500520743

ザ・ボーイング・カンパニー

The Boeing Company

アメリカ合衆国、60606-2016

イリノイ州、シカゴ、ノース・リバーサイド・プラザ、100

(74) 代理人 110002077

園田・小林特許業務法人

(72) 発明者 リーキ、ルイジ・ピー。

アメリカ合衆国 カリフォルニア 92653, ラグーナ ヒルズ, ラルゴ ドライヴ 24982

最終頁に続く

(54) 【発明の名称】ブート前データ検証のための方法及びシステム

## (57) 【特許請求の範囲】

## 【請求項 1】

航空機アビオニクスデバイス用のオペレーションナルライトプログラム(OFP)の実行用のデータの読み込みに先立って、前記OFPを定義するデータを検証する方法であつて、

a) 前記OFPを定義する、航空機内の1次データ記憶領域内のデータに対する第1の検証番号を計算するステップと、

b) 前記第1の検証番号と、航空機アビオニクスデバイスのブートROMに保存されている番号とを比較するステップと、

c) 前記第1の検証番号が前記保存されている番号と一致しないことを確認するステップと、

d) 前記第1の検証番号が前記保存されている番号と一致しないことの前記確認に基づき、前記1次データ記憶領域内のものと同一のOFPを定義している、前記航空機内の2次データ記憶領域内のデータに対する第2の検証番号を計算するステップと、

e) 前記第2の検証番号と、前記航空機アビオニクスデバイスの前記ブートROMに保存されている前記番号とを比較するステップと、

f) 前記第2の検証番号と前記保存されている番号とが一致することを確認するステップと、

g) 前記第2の検証番号と前記保存された番号が一致することの確認に基づき、前記1次データ記憶領域内のデータを前記2次データ記憶領域内のデータで上書きするステップ

10

20

と、

h ) 前記 OFP を実行させるステップと、を含む方法。

【請求項 2】

前記第1の検証番号を計算するステップ及び前記第2の検証番号を計算するステップの各々が、前記 OFP のチェックサムを計算するステップを含む、請求項1に記載の方法。

【請求項 3】

前記第1の検証番号を計算するステップ及び前記第2の検証番号を計算するステップの各々が、前記 OFP を定義するデータのチェックサムを計算するため、前記ブートROMデバイス内の命令を実行するステップを含む、請求項1に記載の方法。

【請求項 4】

航空機アビオニクスデバイスであって、

プロセシング装置と、

前記プロセシング装置によって基本入出力システムが実行されるブートROMと、

前記航空機アビオニクスデバイスに関連するオペレーションナルフライトプログラム(OFP)のイメージを保存するように構成されている1次データ記憶領域と、

前記航空機アビオニクスデバイスに関連する前記 OFP の追加イメージを保存するように構成された少なくとも一つの2次データ記憶領域と、を含み、

前記プロセッシング装置が、

前記1次データ記憶領域内に保存されている前記イメージに対する第1の検証番号を計算し、

前記1次データ記憶領域内に保存されている前記イメージに対して計算された前記第1の検証番号と、前記ブートROMに保存されている番号とを比較し、

前記1次データ記憶領域内に保存されている前記イメージに対する前記第1の検証番号が前記保存されている番号と一致しないことを確認し、

前記1次データ記憶領域内に保存されている前記イメージに対する前記第1の検証番号が前記保存されている番号と一致しないことの前記確認に基づき、前記少なくとも一つの2次データ記憶領域内の前記追加イメージに対する第2の検証番号であって、前記少なくとも一つの2次データ記憶領域内の前記追加イメージに対応するデータが前記1次データ記憶領域内のものと同一の OFP を定義している、第2の検証番号を計算し、

前記少なくとも一つの2次データ記憶領域内に保存されている前記追加イメージに対して計算された前記第2の検証番号と、前記ブートROMに保存されている前記番号とを比較し、

前記第2の検証番号と前記保存されている番号とが一致することを確認し、

前記1次データ記憶領域の前記イメージを前記航空機アビオニクスデバイスに関連する前記 OFP の前記追加イメージで上書きし、

前記2次データ記憶領域の前記追加イメージによって定義される前記 OFP を実行する、ようにプログラムされている、航空機アビオニクスデバイス。

【請求項 5】

前記第1及び第2の検証番号の各々が前記 OFP に対するチェックサムを含む、請求項4に記載の航空機アビオニクスデバイス。

【請求項 6】

前記少なくとも一つの2次データ記憶領域が、シリコンメモリデバイス、コンピュータハードドライブ、CD-ROM、フラッシュドライブ、及びサムドライブのうちの少なくとも一つを含む、請求項4に記載の航空機アビオニクスデバイス。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の分野は概して、一又は複数のプログラムの実行を開始するBIOS(基本入出力システム)を組み込むコンピュータベースシステムの起動に関し、より詳しくはこのようなプログラムのためのブート前データ検証を組み込む方法及びシステムに関する。

10

20

30

40

50

**【背景技術】****【0002】**

該して、コンピュータシステムに最初の電源が投入されると、起動プログラムが動作し、不揮発性メモリに保存される。このような起動プログラムはブートファームウェアと呼ばれることがあり、口語的にはBIOSプログラムと呼ばれる。BIOSプログラムは、標準的なパーソナルコンピュータから航空機内の航空電子工学機器（例えば、航空電子工学ユニットすなわち「ブラックボックス」）として配備される組み込みシステムにいたるまで、多数のコンピュータシステムで実行される。

**【0003】**

BIOSプログラムの実行は、BIOSが実行される処理装置と通信可能に結合されているシステムコンポーネントの検出及び識別に有用である。例えば、コンピュータハードドライブ、表示装置、及び外部メモリデバイスは、BIOSの実行によって識別及び処理されるが、このようなデバイス用のソフトウェアドライバは、BIOSが操作をオペレーティングシステムに戻したときに読み込まれる。幾つかのアプリケーションでは、BIOSは実行すべき組込み試験（BIT）を始動するソフトウェアを含むことができ、それによって、ハードドライブ、表示装置などが少なくとも部分的に動作していることを判断する。すなわち、プロセッサはデバイスと通信することができる。オペレーティングシステムを起動するBIOSの一部、又は航空機システムの場合には、動作を開始するデバイスに関連する飛行管制プログラム（OFP）によって、最終的にBIOSの実行が完了する。

10

20

**【0004】**

このようなシステムでは、BIOSが動作してオペレーティングシステム又はOFPの実行を開始する。しかしながら、BIOSにはオペレーティングシステム又はOFPの内容の検証を行える命令は含まれていない。そのため、オペレーティングシステム、OFP、又は他のアプリケーションが破損している場合には、特定のシステムの動作には障害が発生するか、まったく動作しない。

**【0005】**

航空機搭載の航空電子工学機器では、BIOS又はブートROMからOFPを実行している場合には、誤った取り外し並びに交換作業が問題の原因となる。例えば、デバイスがOFPを正しく実行していない場合には、航空電子工学デバイスは取り外し及び交換が行われ、取り外されたデバイスは整備倉庫に送られる。上述のように取り外されたデバイスに関する問題点は再現することができず、OFPが誤っていたと判断されることがしばしばある。そのため、修復作業はOFPの再読み込み、再試験、及び運用への復帰で構成されることになる。

30

**【発明の概要】****【0006】**

本発明の態様によれば、プログラム実行のためのデータの読み込みに先立って、実行可能なプログラムを定義するデータの検証方法が提示されている。この方法は、1次データ記憶領域内のデータ、実行可能なプログラムを定義するデータに対する検証番号を計算するステップ、計算された検証番号と保存されている番号とを比較するステップ、検証番号が保存されている番号と一致した場合に1次データ記憶領域内のプログラムを実行するステップ、1次データ記憶領域内で実行可能な同一のプログラムを2次データ記憶領域内で定義するデータに対して検証番号を計算するステップを含む。検証番号と保存されている番号とが一致しない場合には、2次データ記憶領域内のデータに対して計算した検証番号と保存されている番号とを比較し、2次データ記憶領域内のデータに対する検証番号と保存されている番号とが一致する場合には、該当するプログラムを実行し、2次データ記憶領域内のデータに対する検証番号と保存されている番号とが一致しない場合には、失敗したことを示す。好ましくは、この方法は、同一の実行可能なプログラムを定義するデータを含む各データ記憶領域に対して反復される手順d)、e)及びf)をさらに含む。好ましくは、この方法は、2次データ記憶領域に対して計算した検証番号と保存されている番

40

50

号とが一致しない場合に、2次データ記憶領域内のデータを1次記憶領域にコピーするステップをさらに含む。有利には、この方法は、航空機搭載電子工学機器に対して、飛行管制プログラムのチェックサムを計算するステップを含んでいてもよい。有利には、この方法は、実行可能なプログラムを定義するデータのチェックサムを計算するため、ポートROMデバイス内の命令を実行するステップを含んでいてもよい。有利には、この方法は、計算した検証番号と基本入出力システムに関連するメモリに保存されている番号とを比較するステップを含む。

【0007】

本発明のさらなる態様によれば、処理装置、当該処理装置によって基本入出力が実行されるポートROM、デバイスに関連する実行可能なアプリケーションのイメージを保存するように構成された1次データ記憶領域、及びデバイスに関連する実行可能なアプリケーションの少なくとも1つの追加イメージを保存するように構成された少なくとも1つの2次データ記憶領域を含むデバイスが提供される。デバイスは、1次データ記憶領域内に保存されたイメージ及び少なくとも1つの2次データ記憶領域内に保存された各イメージに対して個別に検証番号を計算し；各イメージに対して計算された個別の検証番号とポートROMに保存されている番号とを比較し；イメージに対して計算された検証番号が任意の1次又は2次データ記憶領域に保存された番号と一致し、イメージに対して計算した個別の検証番号が保存された番号と一致しなかった場合には、1次又は2次のデータ記憶領域の1つからイメージをコピーし；さらに1次及び2次データ記憶領域の1つの保存されたイメージによって定義されるプログラムを実行する、ようにプログラムされている。有利には、このデバイスは、航空機搭載の航空電子工学ユニットを含むことができる。有利には、このデバイスは、飛行管制プログラムを含むことができ、独立に計算された検証番号は飛行管制プログラム用のチェックサムを含むことができる。有利には、このデバイスは、前記1次及び2次データ記憶領域内の各イメージに対して個別に計算された検証番号が、イメージによって定義されたプログラムの実行前に保存されている番号と一致することを検証するように、プログラムすることができる。有利には、個別の検証番号を計算する場合に、実行可能なアプリケーションのイメージのチェックサムを計算する前記ポートROM内の命令を実行するように、デバイスをプログラムすることができる。有利には、前記デバイスがランダムアクセスメモリを含む場合に、デバイスは前記データ記憶領域の一つからイメージをコピーするようにプログラムすることができ、個別に計算された検証番号は、実行のため前記ランダムアクセスメモリに保存された番号に一致する。有利には、デバイスは、シリコンメモリデバイス、コンピュータハードドライブ、CD-ROM、フラッシュドライブ、及びサムドライブのいずれか一つを含んでいてもよい。

【0008】

本発明のさらなる態様では、コンピュータ上で具現化されコンピュータで実行可能な命令を有する一又は複数のコンピュータで読み取り可能な記憶媒体が提供される。記憶媒体の少なくとも一部分は、実行可能なアプリケーションに関連するチェックサムを表わすデータを含む。少なくとも一つのプロセッサで実行した場合、コンピュータで実行可能な命令によって少なくとも一つのプロセッサは複数のデータ記憶領域内のデータ、同一の実行可能なプログラムを定義する各データ記憶領域内のデータに対して個別の検証番号を計算し、複数のデータ記憶領域内の各々に対して個別に計算された番号を保存されている番号と比較し、計算された検証番号が保存されている番号と一致しなかった場合、個別に計算された検証番号が複数のデータ記憶領域の中の任意の一つに保存された番号と一致する場合には複数のデータ記憶領域の一つのデータをコピーし、さらに、複数のデータ記憶領域の中の一つに保存されたデータによって定義されたプログラムを実行する。有利には、実行可能なアプリケーションは飛行管制プログラムを含んでいてもよい。有利には、コンピュータで実行可能な命令によって、少なくとも一つのプロセッサは、各データ記憶領域に対して計算された検証番号が、保存されているデータによって定義されたプログラムの実行に先立って、保存された番号と一致することを検証することができる。

【0009】

10

20

30

40

50

しかも本発明のさらなる態様により、メモリソースからプログラムを実行する方法が提供されている。この方法は、複数のデータ記憶領域内のデータ、同一の実行可能なプログラムを定義する各データ記憶領域内のデータに対して個別の検証番号を計算するステップ、データ記憶領域内の各々に対して個別に計算された番号と保存されている番号とを比較するステップ、個別に計算された検証番号が保存されている番号と一致しなかった場合、個別に計算された検証番号が複数のデータ記憶領域の中の任意の一つに保存された番号と一致する場合には複数のデータ記憶領域の一つのデータを複製するステップ、さらに、複数のデータ記憶領域の中の一つに保存されたデータによって定義されたプログラムを実行するステップを含む。好ましくは、この方法は、各データ記憶領域に対して個別に計算された検証番号が、保存されているデータによって定義されたプログラムの実行に先立って、保存された番号と一致することを検証するステップをさらに含むことができる。有利には、個別の検証番号を計算する場合には、この方法は、航空機搭載の航空電子工学機器に対する飛行管制プログラムのチェックサムを計算するステップ、及び同一の実行可能なプログラムを定義するデータのチェックサムを計算するためのブートROMデバイス内の命令を実行するステップのうちの少なくとも一つを含むことができる。

## 【0010】

既に説明した特徴、機能及び利点は、様々な実施形態で独立に実現することが可能であるか、以下の説明及び図面を参照してさらなる詳細が理解されうる、さらに別の実施形態で組み合わせることが可能である。

## 【図面の簡単な説明】

## 【0011】

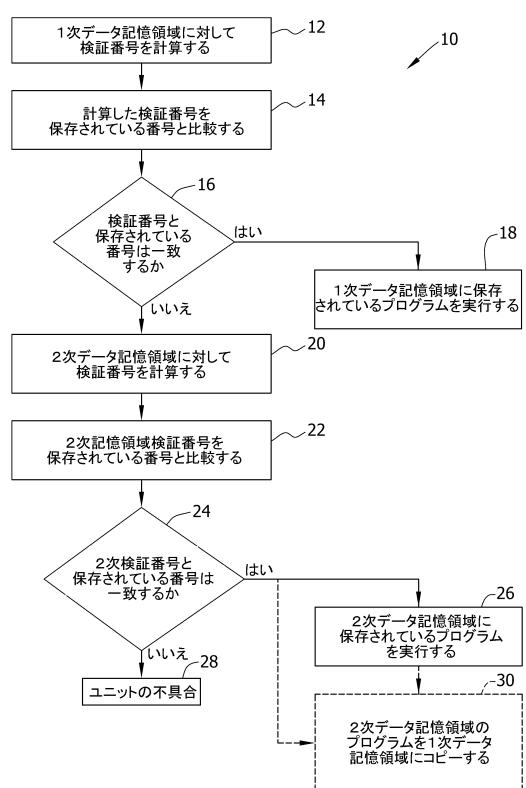

【図1】図1は検証プロセスのフロー図である。

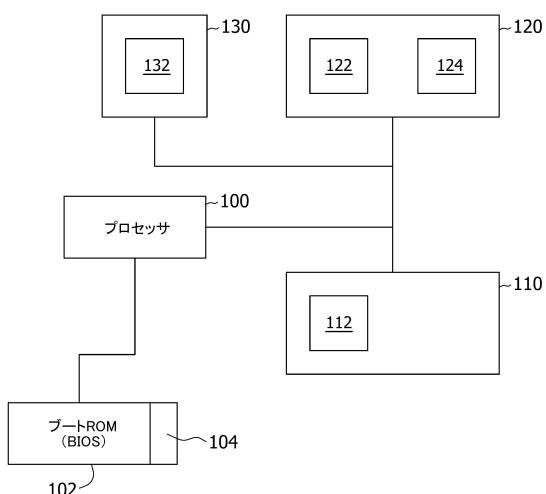

【図2】図2は種々の記憶領域内のアプリケーションの複数のイメージを示す処理システムの図である。

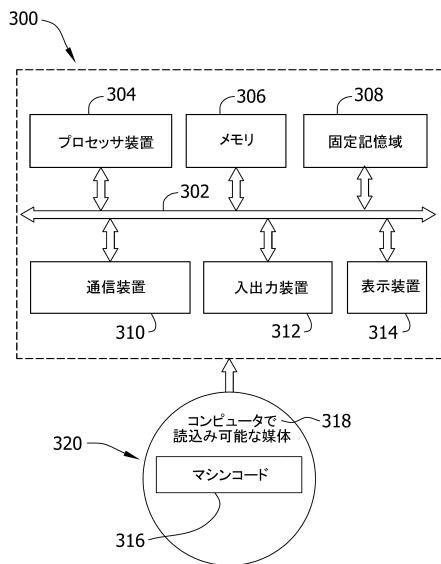

【図3】図3はデータ処理システムの図である。

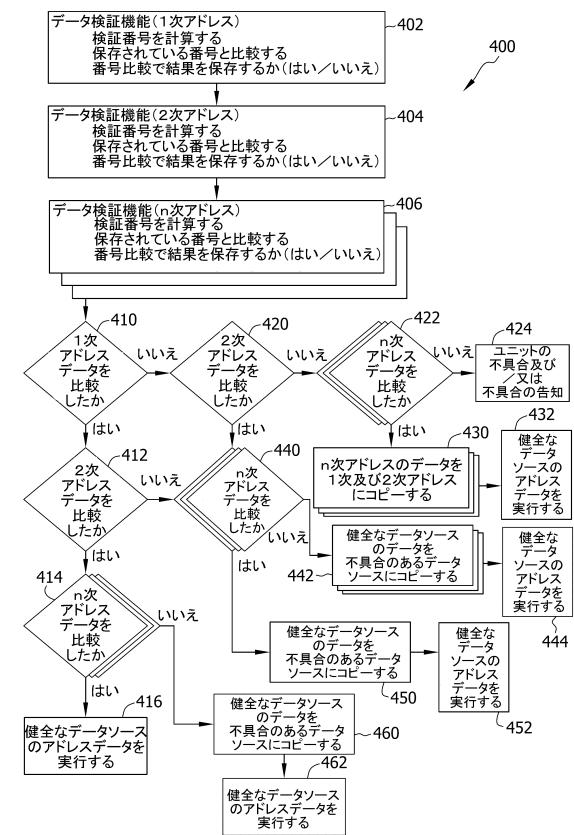

【図4】図4は検証プロセスのフロー図である。

## 【発明を実施するための形態】

## 【0012】

説明されている実施形態は、例えば、実行前にデータが読み込まれる不揮発性メモリに保存されるデータ（例えば、オペレーティングシステムファイル、アプリケーション、及び例えば重要なシステムファイル、カーネルファイル、コンフィギュレーションファイルなどを含むコンピュータシステムの初期化に必要となるその他の情報）の検証を対象としている。例示的な実施形態では、検証試験が失敗した場合には（例えば、チェックサム試験が失敗する場合）、同一データの2次ソースを利用することができる。データの2次ソースが検証試験に合格した場合には、データは2次ソースに関連するメモリから読み込まれ、実行される。幾つかの実施形態では、検証済みの2次ソース内のデータのコピーは、1次メモリの中で検証できなかったデータを上書きすることができる。メモリデバイスの容量が増大し且つ物理的なサイズが小さくなるにつれて、3倍、4倍、5倍、さらにはn倍までのデータソースを想定することができるため、不具合の発生を示す前に実行用のアプリケーションの読み込み時に複数回の実行を試みることができる。このような実施形態はまた、他のソースからの有効なファイルで破損したファイルを上書きすることを可能にし、結果的に「自己修復」機能を提供する。

## 【0013】

本明細書に記載されているように、基本入出力システム（BIOS）に追加命令が付加されている。この命令により、例えば、オペレーティングシステムの内容、アプリケーション及びシステムを初期化するための他の保存情報から構成されるデータの検証を実行することができる。単純な例では、BIOSで実行される命令により、不揮発性メモリに保存された航空電子工学ユニットの飛行管制プログラム（OFP）に対する計算を行い、航空電子工学ユニットすなわち「ブラックボックス」によって実行されるように意図することができる。BIOSはさらに、計算されたチェックサムがOFP用に保存されたチエ

10

20

30

40

50

ツクサムに等しく、チェックサムは例えば BIOS に関連するメモリに保存されていることを検証する。

【0014】

図 1 に関してさらに説明されているように、チェックサムが等しい場合には、 BIOS によって ODP の作動が許可される、及び / 又は ODP が実行される。チェックサムが等しくない場合には、 BIOS は ODP の別のインスタンスが保存されている別のメモリロケーションに移動し、チェックサムの計算及び保存されているチェックサムに対する検証を可能にする。このプロセスは、検証可能なチェックサムを有するイメージが検出されるまで、 ODP の複数のミラーイメージに対して反復することが可能で、検出された時点で当該イメージは実行可能となるか、実行可能となるメモリ内へ転送可能となる。さらに、チェックサム検証試験に合格する ODP のイメージは、チェックサムが検証できないメモリロケーションにコピーすることが可能で、将来のシステムのブートアップで実行することができる ODP の検証可能なコピーを生成することができる。この実施形態では、 BIOS が実行されるブート ROM は、データの 2 次 (3 次など) ソースの (メモリ) ロケーションで構成されている。

10

【0015】

上述の考え方は図 1 のフローチャート 10 を用いて容易に視覚化することができる。実際の手順は様々な方法で実行可能であるが、一又は複数のデータソースがデータの 1 次ソースの読み込み、実行、及び交換のための機能を処理することによってアクセス可能であるという点において、すべてが一貫している。フローチャート 10 を参照すると、1 次データ記憶領域に対する検証番号は計算 (12) され、計算された検証番号はチェックサムなどの保存された値と比較 (14) される。検証番号と保存されている番号が一致する場合 (16) には、1 次データ記憶領域に保存されているプログラムは読み込まれ、実行 (18) される。

20

【0016】

検証番号と保存されている番号が一致しない場合 (16) には、1 次データ記憶領域にあるべきデータの正確なコピーを含んでいなければならない 2 次データ記憶領域に対する検証番号が計算 (20) される。2 次データ記憶領域に対して計算 (20) された検証番号は、保存されている番号と比較 (22) される。検証番号と 2 次データ記憶領域に関連して保存されている番号とが一致する場合 (24) には、2 次データ記憶領域に保存されているプログラムは実行 (26) される。

30

【0017】

検証番号と 2 次データ記憶領域に関連して保存されている番号とが一致しない場合 (24) には、ユニットは故障 (28) しているものとみなすことができる。2 次データ記憶領域のプログラムの実行は、さまざまな方法で実現することができる。プログラムは 2 次データ記憶領域から直接実行すること (26) が可能で、又は、1 次データ記憶領域から実行できるように、2 次データ記憶領域のデータは 1 次データ記憶領域にコピー (30) することが可能である。代替的に、プログラムを 2 次記憶領域から実行し、次に一旦プログラムが読み込まれると自己修復機能として、1 次記憶領域にコピー (30) してもよい。別の実施形態では、2 次データ記憶領域に保存されているプログラムは、当該プログラムが実行できるメモリから読み込まれる。

40

【0018】

図 1 に関連する最も単純な実施例では、データ検証機能 (計算された番号と保存されている番号との比較) が 1 次メモリロケーションに関して合格した場合には、このようなメモリロケーションでプログラムが実行される (18)。しかしながら、当業者であれば、図 1 によって図解されたプロセスは必ずしも 2 個のデータ記憶領域に限定されないことを理解するであろう。ある種のアプリケーションでは、データ検証機能が n 個のデータ記憶領域に関して実行されるものと想定されている。

【0019】

特に、検証番号の計算は、チェックサムなどの値の計算を含むことがある。図 2 は、

50

1次データ記憶領域、2次データ記憶領域、3次記憶領域及びn次記憶領域などが複数の方法で具現化されることを示している。図2で、プロセッサ100はBIOSが保存されるブートROMデバイス102に結合している。ブートROMデバイス102の一部は、プロセッサ100によって実行されるアプリケーションに対するチェックサム104(又は複数のアプリケーションに対する複数のチェックサム)を保存する。メモリ110は実行されるアプリケーションの1次イメージ112を含む。本明細書に記載されているように、プロセッサ100、ブートROM102、及びメモリ110を組み込んでいるデバイスは、複数のメモリデバイス、例えば、メモリデバイス120及び130を含むように構成されうる。図2の例に示したように、メモリデバイス120は実行されるアプリケーションの2つのイメージ(122及び124)で構成されており、メモリデバイス130は実行されるアプリケーションの単一イメージ132で構成されている。10

#### 【0020】

メモリデバイス120の実施例では、データ記憶領域は単一メモリデバイス内で分離されたパーティションであってもよい。他の実施例では、データ記憶領域は物理的に分離されたメモリデバイス(例えば、ハードドライブ、シリコンメモリデバイス、CD-ROM、フラッシュドライブ、サムドライブなど)として具現化されうる。さらに別の実施例では、データ記憶領域は同一形式の物理的に分離されたメモリデバイス(例えば、分離された回路基板上のメモリデバイス)として具現化されうる。また、本明細書で記載されている機能を実現するためには、多数の物理メモリデバイスの実施形態及び構成の組み合わせが利用可能である。20

#### 【0021】

さらに、実施形態は飛行管制プログラムに限定されない。検証されるデータは、オペレーティングシステム、アプリケーション、及び/又はメモリに保存されるシステムの初期化に必要な他の情報を含みうる。この実施形態では、メモリに保存されるデータは、実行用に読み込まれる前に、又はBIOSがオペレーティングシステムにシステムの制御を引き渡す前に有効となる(検証される)。有効化が失敗した場合には、このようなデータの2次ソースが利用され、検証試験に合格するものとみなされる。

#### 【0022】

さらに、2次データソースの一つのデータをメモリから読み込んで1次データメモリにコピーすることができる。例えば、再度図2を参照すると、イメージ112が1次イメージであって、イメージ112に対して計算された検証がブートROM102に保存されているチェックサム104とが一致せず、イメージ132がブートROM102に保存されているチェックサムと一致しない場合には、ブートROM102はイメージ132をメモリ110にコピーする命令を含むように構成することができ、各実施形態を説明するためにイメージ112は破損したものとみなし、上書きすることができる。30

#### 【0023】

ある種のアプリケーションでは、例えば、上述の航空機搭載の航空電子工学システムでは、様々な場所での運用に必要となるソフトウェア及びデータを多数コピーすることにより、システムの冗長性が高まり、ブートアップ及び最終的にはシステムの運用を阻害する問題の自動訂正が可能になる。オペレータがいる場合でも、機能が自動化され、時間が節約される。40

#### 【0024】

一つの実施形態では、本明細書に記載されているメソッド、システム、及びコンピュータで読み込み可能な媒体の技術的な効果は、(a)デバイスのデータ記憶領域内に実行可能なプログラムを構成するデータが、例えば、これらのデータが保存されているチェックサムに等しいことによって、予想通りであることを検証すること、(b)検証試験に合格した場合、データ記憶デバイスに関連するプログラムを実行すること、(c)デバイスの種々のデータ記憶領域内の実行可能なプログラムを構成するデータが、例えば、これらのデータが保存されているチェックサムに等しいことによって、予想通りであることを検証することを試みること、(d)検証試験に合格した場合、種々のデータ記憶デバイスの50

プログラムを実行すること、(e) デバイスが後に元のデータ記憶領域からプログラムを実行できるように、種々のデータ記憶領域から元のデータ記憶領域にプログラムを潜在的にコピーすること、のうちの少なくとも一つを含む。

【0025】

次に図3に注目すると、データ処理システムのより詳細な図が、例示的な実施形態に従って図解されている。この例示的な実施例では、データ処理システム300は、通信ファブリック302を含み、これによりプロセッサ装置304、メモリ306、固定記憶域308、通信装置310、入出力(I/O)装置312、及び表示装置314の間の通信を可能にする。種々の実施形態では、システム300は汎用パーソナルコンピュータ又は航空機搭載の航空電子工学ユニットを表わしている。

10

【0026】

プロセッサ装置304は、メモリ306に読み込まれうるソフトウェアに対する命令を実行するように働く。プロセッサ装置304は、特定の実装に応じて、一又は複数のプロセッサの組であってもよく、あるいはマルチプロセッサコアであってもよい。さらに、プロセッサ装置304は、単一チップ上に様々な種類のプロセッサが共存する異種プロセッサシステムを一又は複数個使用して実装してもよい。別の例示的な実施例では、プロセッサ装置304は同一形式の複数のプロセッサを含む対称型マルチプロセッサシステムであってもよい。

【0027】

メモリ306及び固定記憶域308は、OFPなどのアプリケーションのイメージ(又はイメージ群)が保存される様々な記憶デバイスの例である。本明細書で使用しているように、記憶デバイスは、一時的又は永続的に情報を保存するが可能な任意の数のハードウェアである。これらの例では、メモリ306は、例えば、限定しないが、ランダムアクセスメモリ(RAM)又は他の好適な揮発性又は不揮発性の記憶デバイスであってもよい。メモリ306の一部は、先行するパラグラフで説明したように、ブートROMデバイスとして構成してもよい。固定記憶域308は特定の実装に応じて様々な形態をとりうる。例えば、限定しないが、固定記憶域308は一又は複数のコンポーネント又はデバイスを含みうる。例えば、固定記憶域308は、ハードドライブ、フラッシュメモリ、書換型光ディスク、書換型磁気テープ、又はこれらの組み合わせであってもよい。固定記憶域308によって使用される媒体は着脱式であってもよい。例えば、限定しないが、着脱式ハードドライブは固定記憶域308に使用しうる。

20

【0028】

通信装置310はこれらの例では、他のデータ処理システム又はデバイスとの通信を提供する。これらの例では、通信装置310はネットワークインターフェースカード(NIC)である。通信装置310は、物理的及び無線の通信リンクのいずれか一方又は両方を使用することによって、通信を提供することができる。

30

【0029】

入出力装置312により、データ処理システム300に接続可能な他のデバイスによるデータの入力及び出力が可能になる。例えば、限定しないが、入出力装置312はキーボード及びマウスによるユーザー入力のための接続を提供しうる。さらに、入出力装置312は出力をプリンタに送ってもよい。表示装置314はユーザーに情報を表示する機構を提供する。

40

【0030】

オペレーティングシステム及びアプリケーション又はプログラムに対する命令は、固定記憶域308上に配置される。これらの命令は、プロセッサ装置304によって実行するため、メモリ306に読み込まれうる。異なる実施形態のプロセスは、メモリ306などのメモリに配置されうる命令を実装したコンピュータを使用して、プロセッサ装置304によって実行されうる。これらの命令はマシンコードと呼ばれ、プロセッサ装置304のプロセッサによって読み込まれ実行される。種々の実施形態のマシンコードは、メモリ306又は固定記憶域308など、種々の物理的な又は有形のコンピュータで読み込可能な

50

媒体上に具現化しうる。

【0031】

追加的に、又は代替的に、マシンコード316は、選択的に着脱可能でコンピュータで読み込める媒体318上に機能的な形態で配置され、プロセッサ装置304での実行用のデータ処理システム300に読み込み又は転送することができる。マシンコード316及びコンピュータで読み込める媒体318は、これらの実施例ではコンピュータプログラム製品320を形成する。1つの実施例では、コンピュータで読み込める媒体318は、例えば、固定記憶域308の一部であるハードドライブなどの記憶デバイスに転送するための固定記憶域308の一部であるドライブまたは他のデバイスに挿入又は配置される光ディスク又は磁気ディスクなど、有形の形態をとりうる。有形の形態では、コンピュータで読み込める媒体318はまた、データ処理システム300に接続されているハードドライブ、サムドライブ、又はフラッシュメモリなどの固定記憶域の形態をとりうる。コンピュータで読み込める媒体318の有形の形態はまた、コンピュータで記録可能な記憶媒体とも呼ばれる。幾つかの例では、コンピュータで読み込める媒体318は着脱式ではないことがある。

【0032】

代替的に、マシンコード316は、通信装置310との通信リンク及び/又は入出力装置312との接続によって、コンピュータで読み取可能な媒体318からデータ処理システム300に転送することができる。通信リンク及び/又は接続は、例示的な実施例で物理的なもの又は無線によるものであります。コンピュータで読み込める媒体はまた、マシンコードを含む通信リンク又は無線転送など、無形の形態をとりうる。

【0033】

幾つかの例示的な実施形態では、マシンコード316は、データ処理システム300内で使用するため、他のデバイス又はデータ処理システムから、ネットワークを介して固定記憶域308へダウンロードすることができる。例えば、データ処理サーバーのコンピュータで読み取可能な記憶媒体に保存されたマシンコードは、ネットワークを介してサーバーからデータ処理システム300にダウンロードすることができる。マシンコード316を提供するデータ処理システムは、ホストコンピュータ、クライアントコンピュータ、又はマシンコード316を保存及び転送することができる他のデバイスであってもよい。

【0034】

データ処理システム300に対して例示されている種々のコンポーネントは、異なる実施形態が実装しうる方法に対して構造上の制限を設けることを意図していない。異なる例示的実施形態は、データ処理システム300に対して図解されているコンポーネントに対して追加的又は代替的なコンポーネントを含むデータ処理システム内に実装しうる。図3に示した他のコンポーネントは、実施例とは異なることがある。

【0035】

1つの実施例では、データ処理システム300の記憶装置は、データを保存しうる任意のハードウェア装置である。メモリ306、固定記憶域308及びコンピュータで読み込める媒体318は有形の記憶デバイスの例である。

【0036】

他の実施例では、バスシステムは通信ファブリック302を実装するために使用可能で、システムバス又は入出力バスなどの一又は複数のバスを含みうる。言うまでもなく、このバスシステムは、当該バスシステムに結合された様々なコンポーネント又はデバイス間でのデータ転送を可能にする、任意の好適な形式のアーキテクチャを用いて実装することができる。また、通信装置は、モジュール又はネットワークアダプタなど、データの送受信に使用される一又は複数のデバイスを含むことができる。さらに、メモリは例えば、限定しないが、通信ファブリック302によってアクセス可能な外部メモリ又はメモリ制御装置を介してみられるような、メモリ306又はキャッシュであってもよい。

【0037】

図4は検証プロセスの代替的な実装を示すフロー図400である。上述の実施形態は、

10

20

30

40

50

当該記憶領域からプログラムが実行されるとすぐに、適切なチェックサムを有するプログラム記憶領域が見つかるまで、プログラム記憶領域のチェックサムを計算するプロセスについて説明した。フローチャート400は、第1のプログラム記憶領域がチェックサム試験に合格した場合でも、すべてのプログラム記憶領域が検証されるプロセスを図解している。すべてのプログラム記憶領域の内容を検証することにより、プログラム記憶領域2～nが破損しているが、プログラム記憶領域1は常に検証試験に合格しているため、このような破損は検出されない、というシナリオは回避される。もしプログラム記憶領域2～nの破損が検出されないままであると、プログラム記憶領域1が検証試験に合格しないことがあれば、プログラム記憶領域1～nを取り込んでいるユニットは不必要に動作不能となるだろう。

10

#### 【0038】

次にフローチャート400を参照すると、1次アドレス（プログラム記憶領域1）用のデータ検証機能が実施される（402）。具体的には、先行する段落で説明した内容と同様に、検証番号が計算され、保存されている番号と比較され、比較の結果が保存される。データ検証機能は2次アドレス（プログラム記憶領域2）に対して実施（404）され、結果が保存される。同様に、n次アドレス（プログラム記憶領域n）の残りの部分に対しても実施され、結果が保存される。

#### 【0039】

一つのシナリオでは、すべてのプログラム記憶領域が検証試験に合格する。具体的には、プログラムが1次アドレスから実行されるポイントで、1次アドレスでの比較410が合格したこと、2次アドレスでの比較412が合格したこと、及びn次アドレスでの比較414が合格したことが検証されている。

20

#### 【0040】

別のシナリオでは、プログラム記憶領域の多く又はすべてが検証試験に合格しない。具体的には、1次アドレスでの比較410が合格しなかったこと、2次アドレスでの比較420が合格しなかったこと、及びn次アドレスのうちの一又は複数で比較422が合格しなかったことを検証した場合には、何であれ最終的に検証試験に合格したn次アドレスのうちの一つで最終的にプログラムが実行（430）される。n次アドレスのうちの一つも合格しない場合には、ユニットの不具合（424）が発生し、通知（例えば、報告）されることがある。しかしながら、n次アドレスのうちの一つで比較422が合格した場合には、そのプログラム記憶領域のデータが、1次プログラム領域、2次プログラム記憶領域、及び比較が合格しなかったn次プログラム記憶領域の任意の領域にコピー（430）される。次に、1次プログラム記憶領域、2次プログラム記憶領域又は比較が合格したn次プログラム記憶領域のうちの一つのいずれかからプログラムが実行（432）される。

30

#### 【0041】

1次アドレスでの比較410が合格せず、2次アドレスでの比較420が合格したが、n次アドレスのうちの一又は複数で比較440のうちの一つが合格しなかったシナリオでは、2次プログラム記憶領域のデータが、1次プログラム記憶領域及び比較が合格しなかったn次プログラム記憶領域のいずれかにピー（442）され、プログラムは最終的に1次プログラム記憶領域、2次プログラム記憶領域又はn次プログラム記憶領域のうちの一つのいずれかから実行される。

40

#### 【0042】

同様に、1次アドレスでの比較410が合格せず、2次アドレスでの比較420が合格し、且つn次アドレスでの比較440のすべてが合格したシナリオでは、2次プログラム記憶領域又はn次プログラム記憶領域のうちの一つのデータが、1次プログラム記憶領域に複写（450）され、プログラムは最終的に1次プログラム記憶領域、2次プログラム記憶領域又はn次プログラム記憶領域のうちの一つのいずれかから実行（452）される。

#### 【0043】

最終的に、1次アドレスでの比較410が合格し、2次アドレスでの比較412が合格

50

し、且つ  $n$  次アドレスでの比較 4 1 4 のうちの少なくとも一つが合格しなかったシナリオでは、1 次プログラム記憶領域又は 2 次プログラム記憶領域のうちの一つのデータが、比較 4 1 4 が合格しなかった  $n$  次プログラム記憶領域に複写 (4 6 0) され、プログラムは最終的に 1 次プログラム記憶領域、2 次プログラム記憶領域又は  $n$  次プログラム記憶領域のうちの一つのいずれかから実行 (4 6 2) される。

【0044】

上述の方法及びシステム構成は、当該プログラムに対する 1 次記憶ローケーションが破損している場合であっても、プログラムを確実に実行するため、実行可能である。これまで、又特に、航空機搭載の航空電子工学システムに関連してスペース及び重量が厳しく制約されている場合には、「追加の」プログラムイメージを保存するための単純な追加メモリのための物理的なスペースが確保できなかった。しかしながら、メモリデバイスの物理的な大きさが小さくなる一方で、記憶容量は増大し続けたため、本明細書に記載した構成が実現可能になってきた。種々の実施形態により、保存されているプログラムのイメージが破損している可能性がある場合でも、「健全」であることが確認されているアプリケーションイメージをコピーすることにより、ユニットは少なくとも一定のレベルでの自己修復を行うため、修理を目的とした航空機からのユニット取り外しを減らすことが可能になっている。

【0045】

本明細書で使用しているように、「一つの」という語から始まって单数形で記載されている要素又はステップは、複数の要素又はステップを除外することが明示的に記載されていない限り、複数の要素又はステップを除外しないと理解すべきである。さらに、本発明の「一つの実施形態」又は「例示的実施形態」への言及は、記載されている機能をも取り込む付加的な実施形態の存在を除外するように解釈されることを意図していない。

【0046】

種々の有利な実施形態の説明は、例示及び説明を目的として提示されているものであり、網羅的な説明であること、又は開示された形態に実施形態を限定することを意図していない。当業者には、多数の修正例及び変形例が明らかであろう。さらに、種々の有利な実施形態は、他の有利な実施形態に照らして別の利点を提供することができる。選択された一又は複数の実施形態は、実施形態の原理、実際の用途を最もよく説明するため、及び他の当業者に対し、種々な実施形態の開示と、考慮される特定の用途に適した種々な修正との理解を促すために選択及び記述されている。

【0047】

本明細書では、最良のモードを含め、種々な実施形態を開示する実施例を使用しているため、当業者は任意の機器やシステムの作成ならびに使用、及び組込まれた任意の方法の実施を含む実施形態を実行することができる。特許可能な範囲は特許請求の範囲によって定義されており、当業者であれば想起される他の実施例も含みうる。このような他の実施例は、それらが特許請求の範囲の文字言語から逸脱しない構造要素を有する場合、あるいは、それらが特許請求の範囲の文字言語とごくわずかな相違を有する等価な構造要素を含んでいる場合は、特許請求の範囲の範囲内にあることを意図している。

【符号の説明】

【0048】

- 100 プロセッサ

- 102 ブートROM (BIOS)

- 104 チェックサム

- 112 アプリケーションの 1 次イメージ

- 120、130 メモリデバイス

- 122、124 アプリケーションのイメージ

- 132 アプリケーションの单一イメージ

- 300 データ処理システム

- 302 通信ファブリック

10

20

30

40

50

- 3 0 4 プロセッサ装置

3 0 6 メモリ

3 0 8 固定記憶域

3 1 0 通信装置

3 1 2 入出力装置

3 1 4 表示装置

3 1 6 マシンコード

3 1 8 コンピュータで読み込み可能な媒体

3 2 0 コンピュータプログラム製品

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(72)発明者 ウィックム, ティモシー エス.

アメリカ合衆国 カリフォルニア 92647, ハンティントン ビーチ, コッド サークル

16901-ビー

(72)発明者 タルボット, マーク エー.

アメリカ合衆国 カリフォルニア 92646, ハンティントン ビーチ, ダンブレック ド

ライヴ 9631

(72)発明者 ウェルブルック, グレゴリー エム.

アメリカ合衆国 カリフォルニア 90815, ロング ビーチ, ラドガ アヴェニュー 2

646

(72)発明者 ワン, チャーリー シー.

アメリカ合衆国 カリフォルニア 92647, ハンティントン ビーチ, ウッドストリーム

サークル 16911 80番

(72)発明者 ミレレス, オスカー

アメリカ合衆国 カリフォルニア 90638, ラ ミラダ, マーレット ドライヴ 130

47

(72)発明者 ルービン,マイケル ディー.

アメリカ合衆国 テキサス 78641, リアンダー, サドル ブランケット ブレイス 2

719

審査官 石川 亮

(56)参考文献 特開2008-084291(JP, A)

特開2006-229956(JP, A)

特開2011-008552(JP, A)

特開2009-155092(JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 9 / 445

G 06 F 11 / 00