(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2007-184566

(P2007-184566A)

(43) 公開日 平成19年7月19日(2007.7.19)

| (51) Int.CI.                  | F 1                         | テマコード (参考) |

|-------------------------------|-----------------------------|------------|

| <b>HO1L 29/06 (2006.01)</b>   | HO1L 29/06                  | 601N 4M118 |

| <b>HO1L 33/00 (2006.01)</b>   | HO1L 33/00                  | C 5FO41    |

| <b>HO1L 31/10 (2006.01)</b>   | HO1L 31/10                  | A 5FO48    |

| <b>HO1L 29/80 (2006.01)</b>   | HO1L 29/80                  | A 5FO49    |

| <b>HO1L 21/8234 (2006.01)</b> | HO1L 27/06                  | 102A 5F1O2 |

|                               | 審査請求 有 請求項の数 6 O L (全 18 頁) | 最終頁に続く     |

|              |                              |          |                                            |

|--------------|------------------------------|----------|--------------------------------------------|

| (21) 出願番号    | 特願2006-329405 (P2006-329405) | (71) 出願人 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日     | 平成18年12月6日 (2006.12.6)       | (74) 代理人 | 100065385<br>弁理士 山下 権平                     |

| (31) 優先権主張番号 | 特願2005-352571 (P2005-352571) | (74) 代理人 | 100122921<br>弁理士 志村 博                      |

| (32) 優先日     | 平成17年12月6日 (2005.12.6)       | (74) 代理人 | 100130029<br>弁理士 永井 道雄                     |

| (33) 優先権主張国  | 日本国 (JP)                     | (72) 発明者 | 塙谷 俊介<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

|              |                              | (72) 発明者 | 池田 外充<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

|              |                              |          | 最終頁に続く                                     |

(54) 【発明の名称】半導体ナノワイヤを用いた半導体素子、それを用いた表示装置及び撮像装置

## (57) 【要約】

【課題】ナノワイヤを用いて、発光または受光機能とスイッチング機能を兼ね備えた半導体素子を提供する。

【解決手段】P N接合またはP I N接合を備える第1の領域7と、電界効果型トランジスタ構造を備える第2の領域8とを有する半導体ナノワイヤ1と、半導体ナノワイヤ1の両端に接続される一対の電極(2, 3)と、第2の領域の少なくとも一部に絶縁層5を介して設けられているゲート電極4とを備えている。更に、半導体ナノワイヤ1は、P型半導体部とN型半導体部とを有し、且つP型半導体部またはN型半導体部の一方は、第1及び第2の領域の構成要素となっている。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

P N 接合または P I N 接合を備える第 1 の領域と、電界効果型トランジスタのチャネル領域、ゲート絶縁膜及びゲート電極を含む第 2 の領域とを有し、

少なくとも、前記 P N 接合または P I N 接合と前記チャネル領域とは半導体ナノワイヤに含まれ、

前記半導体ナノワイヤの両端に接続される一対の電極を備えた半導体素子であって、

前記半導体ナノワイヤは、P 型半導体部とN 型半導体部とを有し、且つ

前記 P 型半導体部または前記 N 型半導体部の一方は、前記第 1 及び第 2 の領域の構成要素であることを特徴とする半導体素子。

10

**【請求項 2】**

前記一対の電極には、複数本の前記半導体ナノワイヤが並列に接続されていることを特徴とする請求項 1 に記載の半導体素子。

**【請求項 3】**

前記第 1 の領域は、発光領域であることを特徴とする請求項 1 に記載の半導体素子。

**【請求項 4】**

前記第 1 の領域は、受光領域であることを特徴とする請求項 1 に記載の半導体素子。

**【請求項 5】**

請求項 3 に記載の半導体素子が、一次元又は二次元状に配列していることを特徴とする表示装置。

20

**【請求項 6】**

請求項 4 に記載の半導体素子が、一次元又は二次元状に複数配列していることを特徴とする撮像装置。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、半導体ナノワイヤを用いた半導体素子に関する。また、本発明は、半導体ナノワイヤを用いて、P N 又は P I N 接合素子、及び電界効果トランジスタと併せ持つ半導体素子に関するものである。更に、本発明は、前記半導体素子を用いた表示装置及び撮像装置に関する。

30

**【背景技術】****【0 0 0 2】**

半導体ナノワイヤとは、半導体特性を示す直径数百 nm 程度以下の直径を有する構造のものを指す。そして、上記半導体ワイヤは、例えば VLS (Vapor-Liquid-Solid) 法を用いて作製される。

**【0 0 0 3】**

VLS 法とは基板上の金属微粒子と基板もしくは所望とする元素とが溶融化化合物合金を形成し、これがさらに原料ガスを分解することによりナノワイヤが成長する方法である。この VLS 法は、ナノワイヤを始め、各種カーボンナノチューブ、酸化物ウイスカーの合成法として知られている。上記手法で作製された半導体ナノワイヤは移動度が数百 cm<sup>2</sup>/Vs ~ 数千 cm<sup>2</sup>/Vs と非常に高い移動度を示す。その為、上記半導体ナノワイヤをチャネル部位として用いた電界効果型トランジスタ (FET) に用いることが可能であり、実用化に向けて種々研究が行われている（例えば特許文献 1）。

40

**【0 0 0 4】**

特許文献 1 では、上記半導体ナノワイヤを溶媒に分散させ、それを流力などにより基板上に配向させることによりナノワイヤ電界効果型トランジスタを作製している。特許文献 1 に示す作製手法では、塗布プロセスでトランジスタの形成を行うことが可能であるため、高移動度で大面積の T F T を作製することが可能となる。

**【0 0 0 5】**

従来のシリコンや化合物半導体トランジスタでは高移動度を有するが、大面積基板の用

50

意が困難であったり、真空装置を必要としたりする為に大面積化が困難である。一方、有機トランジスタの場合、基板の制約が少ないうえ塗布プロセスを用いることができるため大面積のトランジスタを作製することは可能であるが、移動度が、 $\sim 0.1\text{cm}^2/\text{Vs}$ と低くその用途は限られている。

#### 【0006】

上記半導体ナノワイヤトランジスタは上記2つのトランジスタの課題を同時に解決することが可能となるため、無機系のトランジスタの性能を維持したまま、TFTの大面積化、低コスト化、フレキシブル化などが可能となる。そのため、有機ELディスプレイ用TFTや、シートコンピューターなどへの応用を考えることができ、新しいエレクトロニクスデバイスの創出への強力なツールとなる可能性を秘めている。10

#### 【0007】

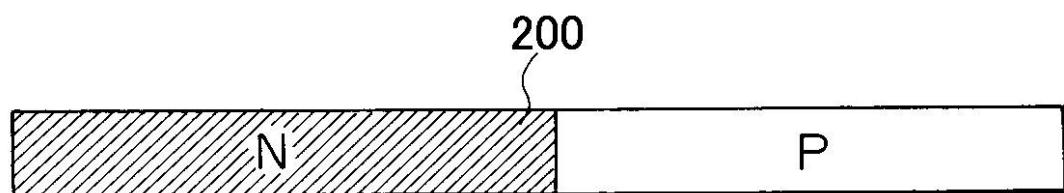

一方、上記半導体ナノワイヤにおいて、図10に示すようにナノワイヤ中にP-N接合を有する半導体ナノワイヤ200が報告されている（例えば特許文献2）。特許文献2では、半導体ナノワイヤ中に存在するP-N接合を利用して、LEDや太陽電池、熱電素子への応用を提案している。

#### 【0008】

無機LEDは、有機ELと比較して効率が $10\text{~}1\text{m/W} \sim 100\text{~}1\text{m/W}$ と非常に高効率であり、寿命も数万時間以上と非常に長いため、各種照明等で既に実用化が始まっている。

#### 【0009】

また、太陽電池の分野では、有機太陽電池や色素増感太陽電池などの研究が進められているが、シリコン系や化合物半導体などの無機系太陽電池の効率には及ばず、実用化されているのは無機系太陽電池のみである。20

#### 【0010】

しかしながら、上記無機LEDや無機系太陽電池では効率や寿命の点では実用化のレベルに達しているが、基板の制約や真空プロセスが必要なため、素子の大面積化・低コスト化が困難である。そのため、大面積化やコスト面では有機ELや有機太陽電池、色素増感太陽電池と比較して短所となってしまう。

#### 【0011】

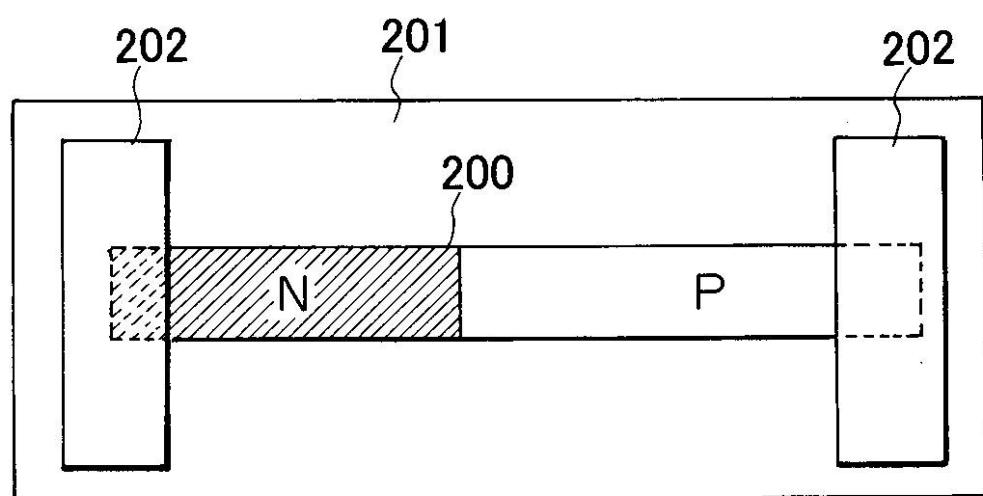

そこで、特許文献2では、半導体ナノワイヤ200を、図11に示すように基板201上に配列させて、一対の電極202で挟むことにより素子化することが考えられている。このような構成の素子を作製すれば、無機の性能を維持したまま大面積化が容易な半導体素子を低コストで作製することができ、例えば大面積の照明や太陽電池を低コストで供給することができる可能性を秘めていると言える。30

#### 【特許文献1】米国特許第6872645号明細書

#### 【特許文献2】米国特許第6882051号明細書

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0012】

しかしながら、従来の技術では、上記ナノワイヤを用いて表示装置や撮像装置などを形成する必要がある場合、別途スイッチング部（例えば、電界効果型トランジスタ）を設ける必要があり装置構成が複雑になってしまい問題を有している。

本発明者らは、このような問題を踏まえ、受光領域あるいは発光領域として機能する部分と、スイッチング動作を行うための部分とを、同じナノワイヤを用いて構成しようという画期的なアイデアに到達したのである。40

#### 【課題を解決するための手段】

#### 【0013】

本発明に係る半導体素子は、P N接合またはP I N接合を備える第1の領域と、電界効果型トランジスタのチャネル領域、ゲート絶縁膜及びゲート電極を含む第2の領域とを有し、

少なくとも、前記P N接合またはP I N接合と前記チャネル領域とは半導体ナノワイヤ50

に含まれ、

前記半導体ナノワイヤの両端に接続される一対の電極を備えた半導体素子であって、

前記半導体ナノワイヤは、P型半導体部とN型半導体部とを有し、且つ

前記P型半導体部または前記N型半導体部の一方は、前記第1及び第2の領域の構成要素であることを特徴とする。

#### 【0014】

また、別の本発明は、少なくとも1つのPN接合部を構成するP型半導体部とN型半導体部、又は少なくとも1つのPIN接合部を構成するP型半導体部と真性半導体部とN型半導体部とを有する第1の領域(PN接合部又はPIN接合部を有する。)と、前記第1の領域の前記PN又はPIN接合部を構成する前記P型半導体部又は前記N型半導体部が延長された第2の領域(FET構造を有する。)とを有する半導体ナノワイヤと、

前記半導体ナノワイヤの前記第2の部分の少なくとも一部に絶縁層を介して配置されたゲート電極と、

前記半導体ナノワイヤの両端に接続される一対の電極と、を備え、

前記第2の領域は電界効果トランジスタを構成していることを特徴とする。

#### 【0015】

また、別の本発明は、

少なくとも1つの接合部を構成する第1半導体部と第2半導体部とを有する第1の領域と、前記第1の部分の前記接合部を構成する前記第1半導体部又は前記第2半導体部が延長された第2の領域とを有する半導体ナノワイヤと、

前記半導体ナノワイヤの前記第2の領域の少なくとも一部に絶縁層を介して配置されたゲート電極と、

前記半導体ナノワイヤの両端に接続される一対の電極と、を備え、

前記第2の領域は電界効果トランジスタを構成する半導体素子であることを特徴とする。

#### 【0016】

本発明において、接合構造は、PN接合構造やPIN接合構造にかぎらず、ダブルヘテロ構造や、量子井戸構造、PIPIN構造などの構造も含まれるものである。

#### 【発明の効果】

#### 【0017】

本発明によれば、PN接合、PIN接合等の半導体接合による機能とFET機能を同時に発現させることができる。また、PN接合やPIN接合等の接合領域とFET領域間の接続抵抗を小さくすることが可能である。そのため、PN接合領域等の半導体接合領域で発光素子や受光素子を構成した場合、素子全体の発光効率や光電変換効率を高くすることができる。

#### 【発明を実施するための最良の形態】

#### 【0018】

以下、図面を参照しながら、本発明の実施の形態を詳細に説明するが、これによって本発明は限定されない。

#### 【0019】

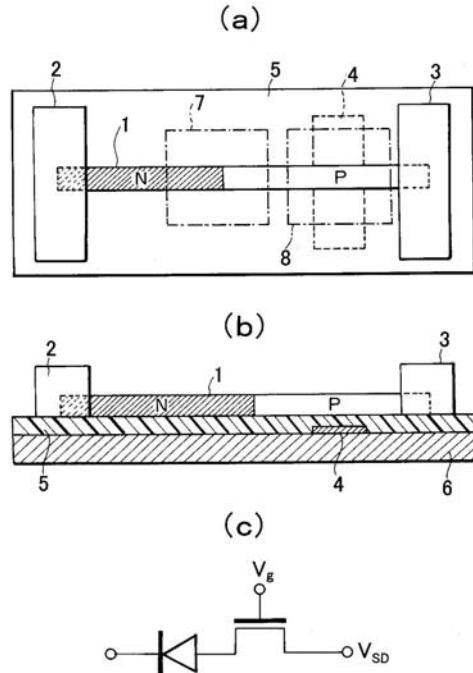

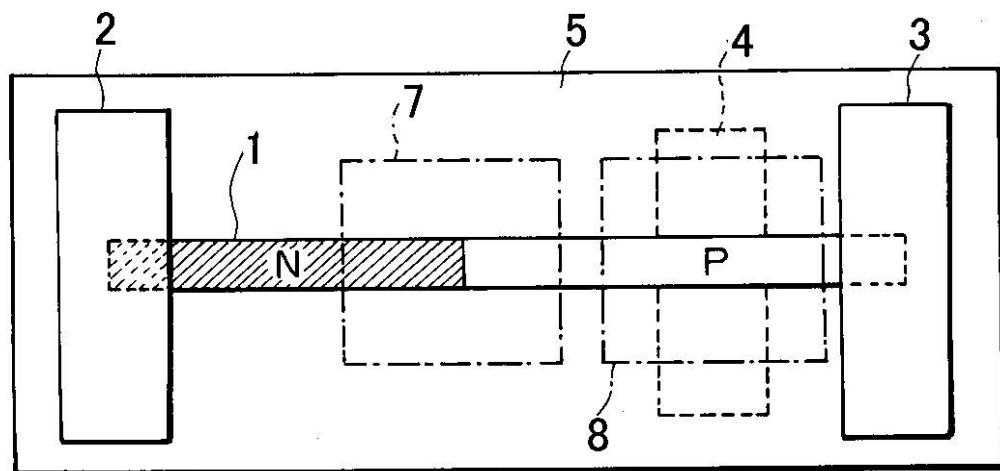

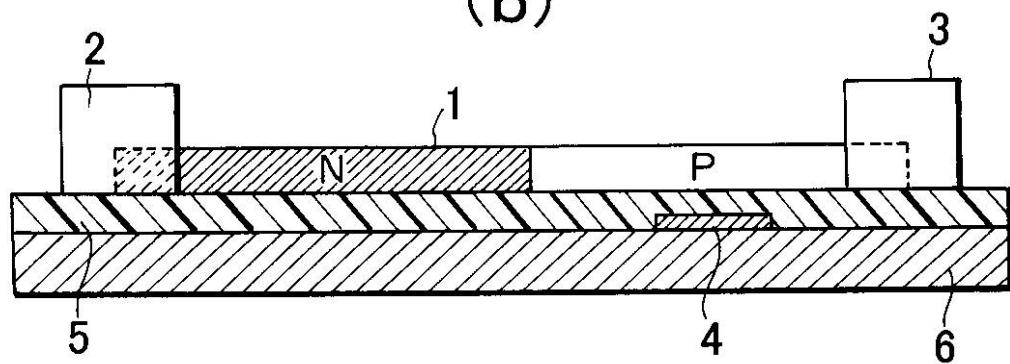

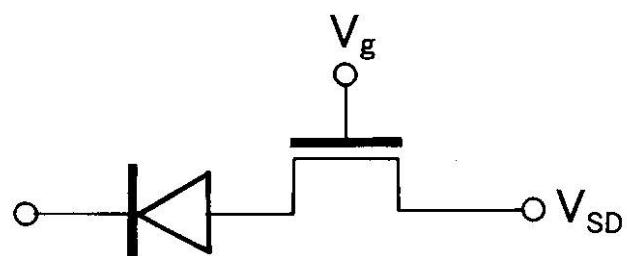

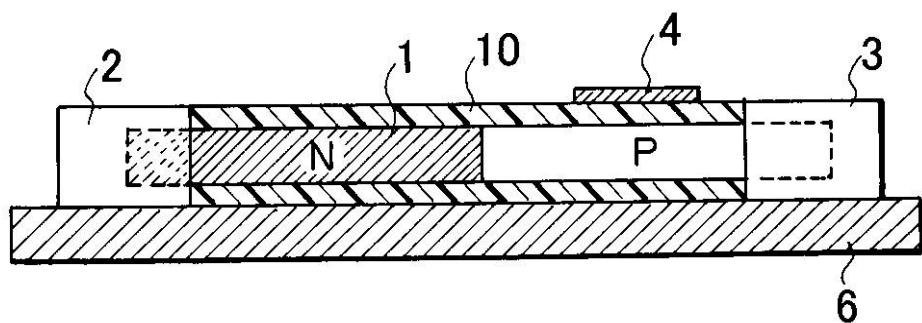

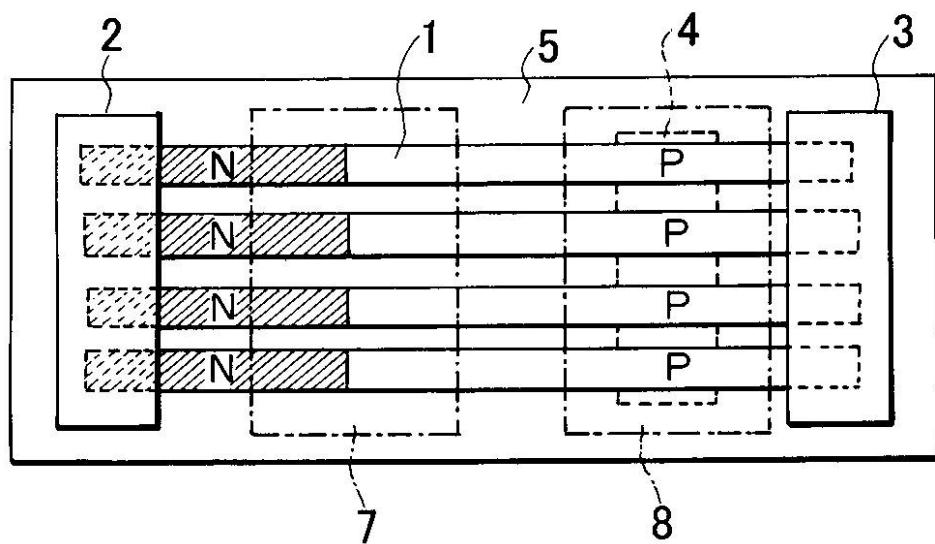

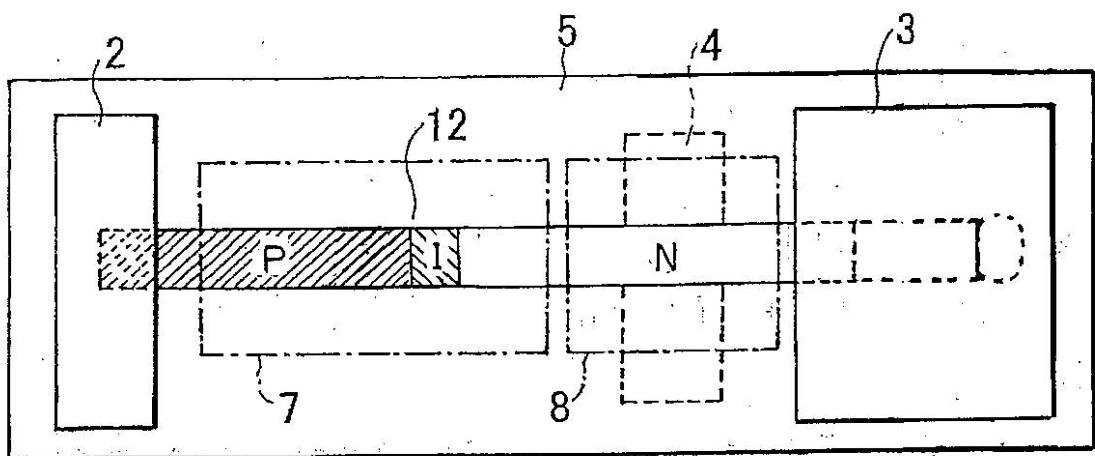

図1に本発明の実施形態の一例を示す。図1(a)は本発明の一実施形態の半導体素子を示す平面図、(b)はその断面図、(c)は等価回路図である。

#### 【0020】

図1に示す半導体素子は、基板6上に設けられた、PN接合を有する半導体ナノワイヤ1と、半導体ナノワイヤ1の両端部に接続された一対の電極2、電極3(電極3はソース又はドレイン電極となる)を有する。また、ゲート電極4、ゲート絶縁層5を有する。半導体ナノワイヤ1は第1の領域となるP-N接合部7と、第2の領域となるFET8とから成り、FET8はP型伝導部(P型半導体部)もしくはN型伝導部(N型半導体部)のいずれか一方から成る。ここでは、P型伝導部からなる。

#### 【0021】

10

20

30

40

50

図1に示すような構成にすれば、FET領域でゲート電圧を操作することによりナノワイヤに流れる電流を制御することが可能となる。

#### 【0022】

半導体ナノワイヤ1は、P型伝導部とN型伝導部を有しており、直径数ナノメートル～数百ナノメートルである。また、その長さは、特に制限されるものではないが、例えば、数十ナノメートル以上である。勿論、数マイクロメートル以上の長さであっても本発明における半導体ナノワイヤである。例えば、直径が、2nmから300nm、長さが、例えば、1μmから5μm程度の半導体ナノワイヤが挙げられる。

#### 【0023】

材料については、II-VI族化合物半導体、II-II-V族化合物半導体、I-V族化合物半導体、I-VI族化合物半導体、I-VII族化合物半導体、II-II-VI族化合物半導体など、VII族半導体などが挙げることができる。さらに具体的な一例として、Si、Ge、SiGe、AlGaAs、ZnO、ZnS、ZnSe、ZnTe、CdS、CdSe、CdTe、GaAs、GaN、GaAs、GaP、InP、InN、InAs、カーボンナノチューブなどが例示される。10

#### 【0024】

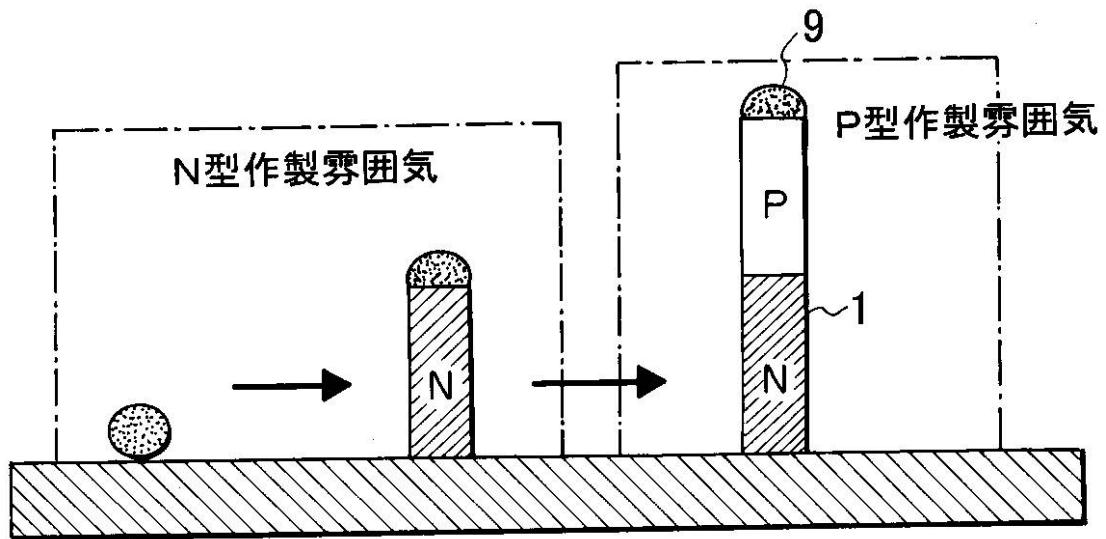

上記半導体ナノワイヤの作製方法は特に制限されないが、VLS法で作製することが好ましい。VLS(Vapor-Liquid-Solid)法とは基板上の金属微粒子(金、ニッケル、コバルト等)と基板もしくは所望とする元素とが溶融化合物合金を形成し、これがさらに原料ガスを分解することによりナノワイヤが成長する方法である。この方法を用いて図2に示すように反応ガスの雰囲気を制御してドーピングを行うことにより、P型伝導部とN型伝導部の両方の部位を有するナノワイヤを提供することができる。VLS法ではワイヤの成長が選択的に触媒粒子9部分で起こるため、上記P-N構造やP-I-N構造を容易に作製することができる。20

#### 【0025】

電極2、電極3、ゲート電極4は、導電性材料であれば特に限定されず、白金、金、銀、ニッケル、クロム、銅、鉄、錫、アンチモン鉛、タンタル、インジウム、アルミニウム、亜鉛、マグネシウム、およびこれらの合金を用いることができる。また、インジウム・錫酸化物等の導電性金属酸化物、あるいはドーピング等で導電率を向上させた無機および有機半導体を用いることができる。無機および有機半導体としては、例えばシリコン単結晶、ポリシリコン、アモルファスシリコン、ゲルマニウム、グラファイト、ポリアセチレン、ポリパラフェニレン、ポリチオフェン、ポリピロール、ポリアニリン、ポリチエニレンビニレン、ポリパラフェニレンビニレン等が挙げられる。電極の作製方法としてはスパッタ法、蒸着法、溶液やペーストからの印刷法、インクジェット法などが例示される。30

#### 【0026】

ゲート絶縁層5は、絶縁性を有していれば何でもよいが、誘電率が高く、導電率が低いものが好ましい。例としては、酸化シリコン、窒化シリコン、酸化アルミニウム、酸化チタン、酸化タンタルなどの無機酸化物や窒化物、ポリアクリレート、ポリメタクリレート、ポリエチレンテレフタレート、ポリイミド、ポリエーテル、シロキサン含有ポリマー等の有機高分子が挙げられる。また、上記絶縁材料の中でも、表面の平滑性の高いものが好ましい。更に、図3に示す様にゲート絶縁層として絶縁体10を被覆することにより、ゲート絶縁層を設けなくともトランジスタを形成することができ、このような構成にすることにより素子構成をより簡単にすることができます。この際の絶縁体については絶縁性を有するものであれば特に限定されることはない。例えば半導体ナノワイヤ表面を酸化・窒化させることで絶縁層を形成したり、PZTやY<sub>2</sub>O<sub>3</sub>、ZrO<sub>2</sub>、HfO<sub>2</sub>など半導体ナノワイヤと異なる材料で被覆したりすることができる。最初にナノワイヤ上に絶縁層を形成する場合には、絶縁層が形成されたナノワイヤの端部絶縁層を除去してからソース・ドレイン電極を形成する。40

#### 【0027】

50

基板 6 はガラス、セラミック、半導体、金属、プラスチックなど特に制限されることはな

いが、低コスト化が容易なガラス基板やプラスチック基板を用いることが好ましい。また

プラスチック基板を用いる場合にはフレキシブルなトランジスタを提供することができ

るため、フレキシブルな表示装置を始めとする種々のフレキシブルデバイスを提供するこ

とが可能となる。

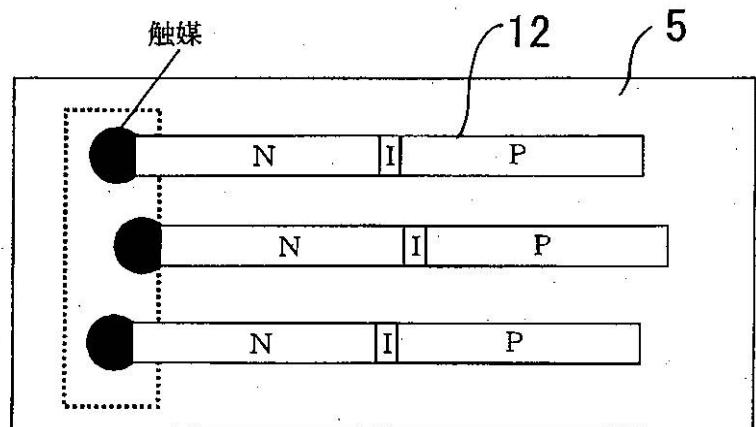

#### 【 0 0 2 8 】

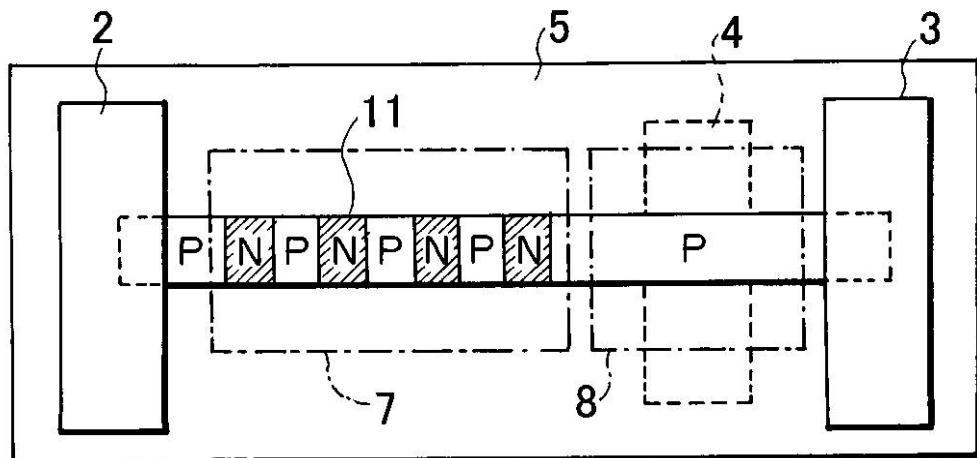

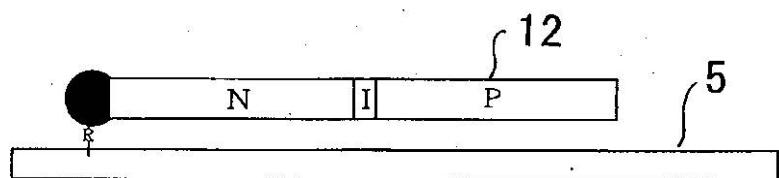

図 1 では、半導体ナノワイヤの PN 接合部 7 は一つの P N 接合の場合を示しているが、図

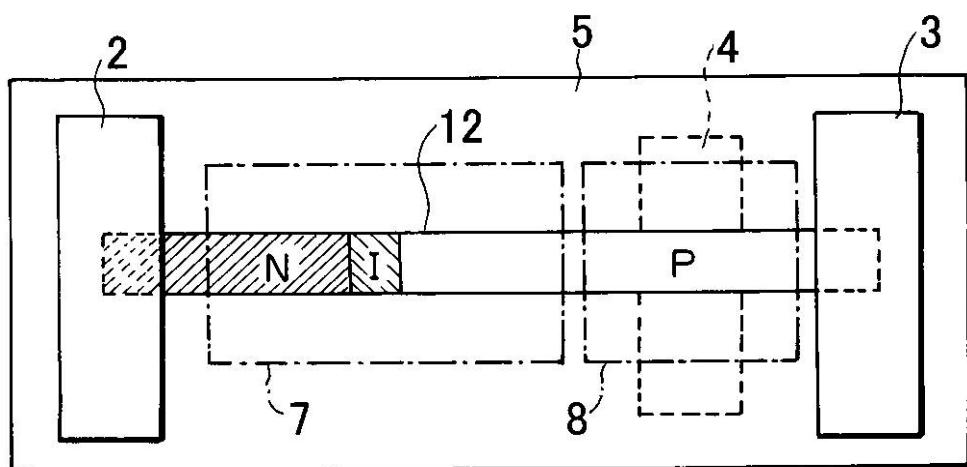

4 に示すように P N 接合を複数有する半導体ナノワイヤ 11 を用いてもよい。また、図 5

に示すように P-I-N ( I は真性半導体部 ) 構造を有する半導体ナノワイヤ 12 を用いても

よい。尚、上記接合構造には、ダブルヘテロ構造や、量子井戸構造、PIPIN構造などの構

造も含まれ、その用途に応じて適宜その種類を選択すれば良い。

10

#### 【 0 0 2 9 】

半導体ナノワイヤ 1 の配列方法については特に制限されることはないが、ナノワイヤを

溶媒に分散させ、それを流力や電界などの外部力を用いて配向させることが好ましい。尚

、この際のナノワイヤを分散させる溶媒については、ナノワイヤの親水性・疎水性やゼー

タ電位に応じて分散しやすい溶媒を適宜選択すれば良い。

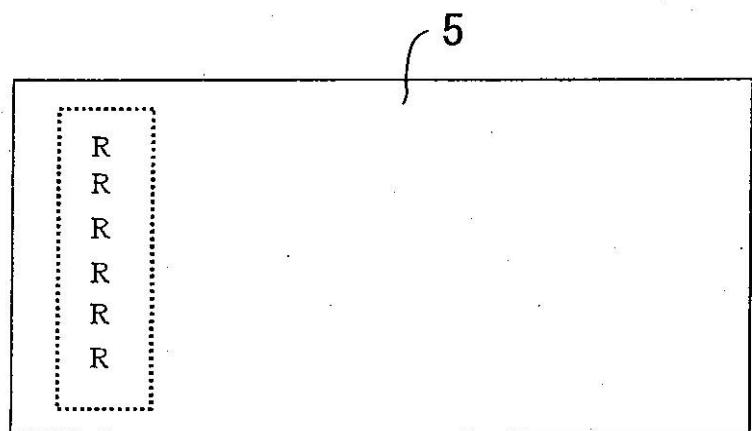

また、本実施形態では、図 12 示すように、触媒となる金属微粒子と選択的に結合又は配

位する官能基を基板上にパターンニングすることで（パターンニングされた官能基を R で

示す）、触媒微粒子を介してナノワイヤを基板上に固定することができる。このような手

法を用いれば、図 13 に示すようにナノワイヤの P 型や N 型を所望の方向に配列させること

ができる。

20

#### 【 0 0 3 0 】

尚、図 1 では電極 2 , 3 間に 1 本の半導体ナノワイヤのみ存在する場合を示したが、図

6 に示す様に複数の半導体ナノワイヤ 1 が電極 2 , 3 間に存在する場合も本発明の実施形

態に含まれる。また、図 1 では基板上に半導体ナノワイヤ 1 が配列している構成であるが

、基板 6 が存在しない場合も本発明の実施形態に含まれる。

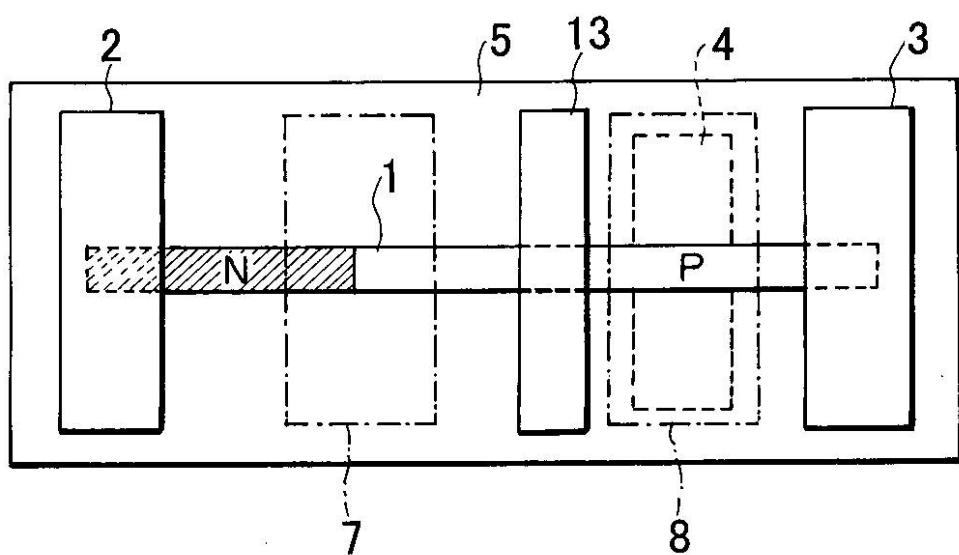

#### 【 0 0 3 1 】

また、本発明の実施形態の半導体素子は、図 7 に示す様に P-N 接合部と FET の間に電極 1

3 を設けることにより、上記 P-N 接合部と上記 FET に印加する電圧を独立で変化させること

ができる。

30

#### 【 0 0 3 2 】

この様な構成にすることにより、P-N 接合部と FET のそれぞれの部分でナノワイヤに印加

される最適な電圧を選ぶことができ、より高性能な半導体素子を提供することが可能とな

る。

#### 【 0 0 3 3 】

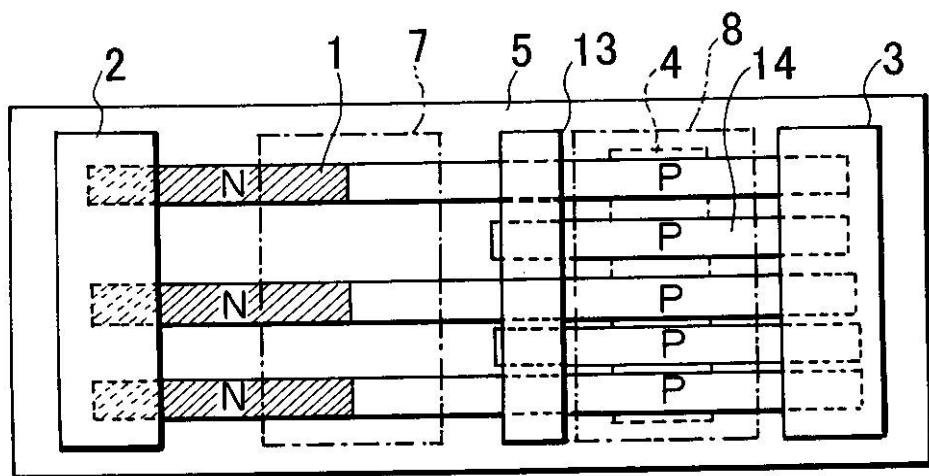

また、図 8 に示す様に FET 部にのみ新たに半導体ナノワイヤ 14 を配列する構成にす

れば、P-N 接合部に流れる電流値を増加させることができる。本実施形態の P N 接合領域 7

を発光素子に用いる場合、輝度を上げる為には LED に流れる電流を増加させることが求め

られる。その為、特に図 8 の構成は P N 接合部 7 を発光素子に用いる場合に特に好適であ

る。尚、図示はしないが P-N 接合部のナノワイヤの本数を多くすることも当然可能である

。

40

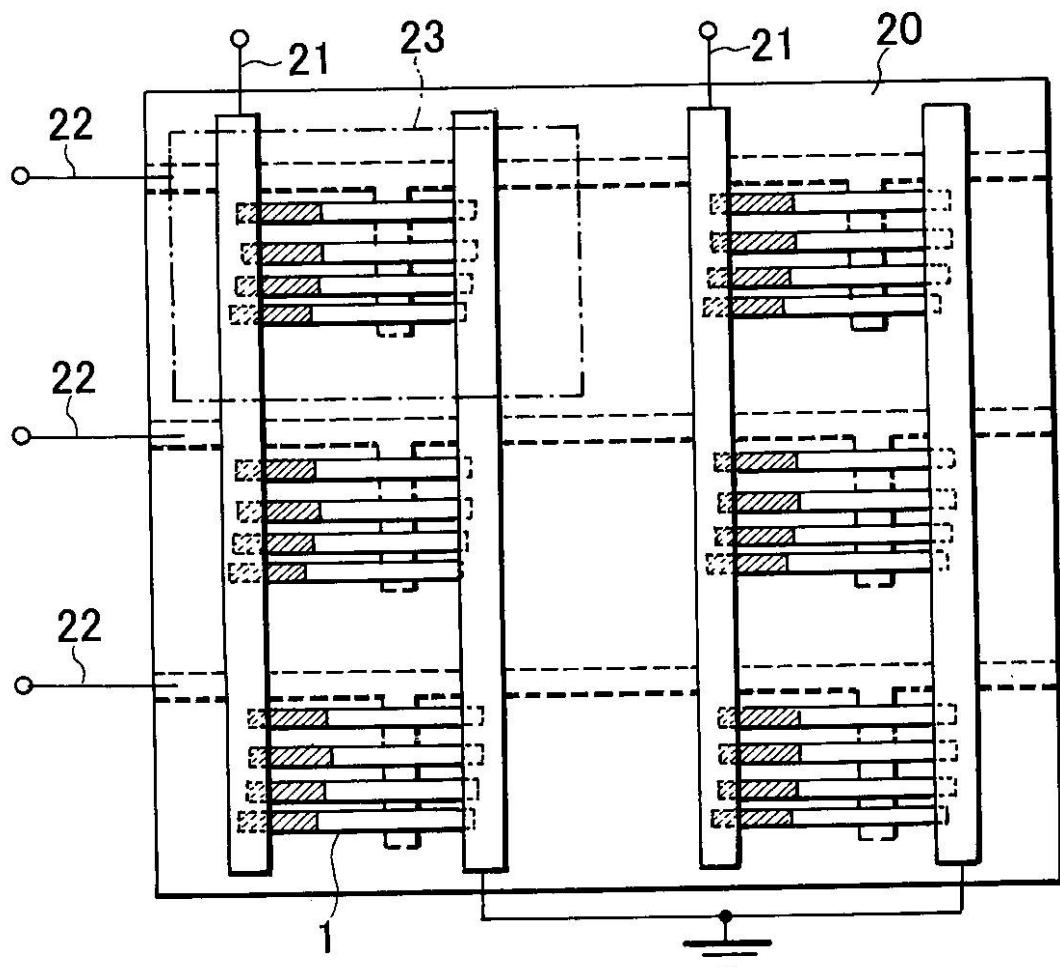

#### 【 0 0 3 4 】

次に上記半導体素子を複数配列させ、一つ一つの素子のアドレスを行う場合について説

明する。図 9 が複数の半導体素子が同一基板 20 上に複数存在する場合の一例を示す図で

ある。ソースライン 21 に印加する電圧  $V_{SD}$  を走査するのと同時にゲートライン 22 に

電圧  $V_g$  を印加することにより各素子の ON · OFF 制御を行う。例えば、図 9 中の半

導体素子 23 のみを ON にする場合、ソースライン 21 に電圧  $V_{SD}$  が印加された時に、ゲ

ートライン 22 に電圧  $V_g$  を印加する。

#### 【 0 0 3 5 】

本実施形態では各素子に FET 機能を有しているため、P - N 接合部に LED の構成を作り込

むことにより表示装置を提供することができる。特に、LEDに赤、緑、青の発光を示す材料をそれぞれ利用することにより、フルカラーの表示装置を提供することができる。

#### 【0036】

また、P-N接合部分にフォトダイオードの構成を作りこめば、撮像装置として用いることが可能となる。この際、上記撮像装置にカラーフィルターを具備することでカラー化が可能となる。

#### 【0037】

本実施形態の半導体素子はP-N接合部とFET部を有しているため、簡単な素子構成で表示装置及び撮像装置を作製することができる。尚、本発明の素子構成は図9に限られたものではなく、例えばキャパシタを別途有している構造であったり、複数のトランジスタを有している構造であったりしても良い。

#### 【0038】

また、FET領域8のP型伝導部に周囲からN型不純物を導入し、P型伝導部の周囲にPN接合部を形成するN型伝導部を形成し、そのN型伝導部上にゲート電極を形成することで、接合型FETを作成することもできる。

#### 【0039】

なお、半導体ナノワイヤは、塗布プロセスを用いて素子作製できるため、上述したように受光領域あるいは発光領域とスイッチング領域とを一つの塗布プロセスを用いて作製できる。

#### 【0040】

この様な構成にすることにより、該半導体ナノワイヤ中にPN接合又はPIN接合由來の機能を発現させるP-N接合部又はPIN接合部とトランジスタ機能を発現するFETの両方を設けることができる。

#### 【0041】

上記半導体素子の構成では、素子にスイッチング機能を発現させることが可能となる。そのため、該半導体素子を多数同一基板上に設ける場合においてTFTを別途設ける必要がなくとも各素子のアドレスを行うことが可能となり、素子の低コスト化に繋がる。また、PN接合領域、PIN接合領域を適宜選択することにより、発光や光電変換などPN接合、PIN接合に由来する所望の機能をより高効率で発現させることができる。

#### 【0042】

また、上記半導体ナノワイヤは触媒粒子を用いるVLS (Vapor-Liquid-Solid)法で作製することができる。VLS法では選択的に触媒粒子部分でナノワイヤの成長が起こるため、コアシェル構造になることなく上記P-N構造やP-I-N構造を容易に作製することができる。

#### 【0043】

また、上記半導体素子は上記第1の領域(PN接合又はPIN接合)と上記第2の領域(FET)の間に電極を設けることができる。

#### 【0044】

該電極を設けることにより、上記PN接合部又はPIN接合部と上記FETに印加する電圧を独立に変化させることができる。

#### 【0045】

そのため、上記PN接合部又はPIN接合部と上記FETのそれぞれの機能が発現する最適な電圧を印加することが可能となり、素子の高性能化が可能となる。また、上記PN接合部又はPIN接合部と上記FETのナノワイヤの本数を変化させることができ、それらの領域に流れる電流値を容易に制御することができる。

#### 【0046】

また、上記半導体素子は一対の電極に複数本の半導体ナノワイヤが並列接続するように構成することができる。上記構成にすることにより、PN接合部又はPIN接合部での機能発現領域の面積が増加するため、1本のみ半導体ナノワイヤが存在する場合と比較して、より高性能な半導体素子を提供することができる。

10

20

30

40

50

## 【0047】

また、上記第1の領域は発光素子とすることができます。P N接合又はP I N接合に発光機能を設けることにより、F E T機能と発光機能の両方を有する半導体素子を提供することが可能となる。そして、同一の半導体ナノワイヤ上にF E T機能と発光機能を具備することができるため、非常に簡単な構成でスイッチング機能を有する半導体素子を提供することができる。

## 【0048】

また、上記第1の領域は受光素子とすることができます。P N接合部又はP I N接合部に10

フォトダイオード機能を設けることにより、F E T機能とフォトダイオード機能の両方を有する半導体素子を提供することが可能となる。そして同一の半導体ナノワイヤ上にF E T機能とフォトダイオード機能を具備することができるため、非常に簡単な構成でスイッチング機能を有する半導体素子を提供することができる。

## 【0049】

また、上記第1の部分が発光素子である半導体素子を一次元又は二次元状に配列して表示装置を提供することができる。上記半導体素子はF E T機能も有しているため、上記半導体素子を一次元又は二次元状に配列させることにより、T F T機能を有する表示装置を提供することができる。この表示装置は、T F Tを別途設けることが不要であるため、従来の表示装置と比較して非常に簡単な構成で表示装置を提供することができる。

## 【0050】

また、上記第1の部分が受光素子である半導体素子を一次元又は二次元状に配列して撮像装置を提供することができる。上記半導体素子はF E T機能も有しているため、上記半導体素子を一次元又は二次元状に配列させることにより、T F T機能を有する表示装置を提供することができる。この撮像装置は、T F Tを別途設けることが不要であるため、従来の撮像装置と比較して非常に簡単な構成で撮像装置を提供することができる。

## 【0051】

以下、実施例により具体的に説明するが本発明は以下に示すものに限られたものではない。

## 【0052】

## &lt;実施例1&gt;

本実施例は、本発明を表示装置として用いた場合である。半導体ナノワイヤはGaN系のものを用いる。ナノワイヤの作製はVLS法を用いて行い作製する。

## 【0053】

作製方法は、まず、サファイア基板上に粒径が50nmのA u微粒子を形成する。その後、トリメチルガリウム(TMGa)およびアンモニア雰囲気中において基板を900℃に加熱しバッファ層となるGaNナノワイヤを作製する。

## 【0054】

その後、その上にN型GaNを作製するためにトリメチルガリウム(TMGa)、シランガス及びアンモニアの雰囲気中においてナノワイヤを成長させ、n-GaN:Si層を作製する。そして、その上に活性層としてトリメチルガリウム(TMGa)、トリメチルインジウム(TMIn)及びアンモニアの雰囲気中で活性層のInGaN層を作製する。最後にP型GaNを作製するために、シクロペンタジエニルマグネシウム(Cp<sub>2</sub>Mg)ガス、トリメチルガリウム(TMGa)、アンモニアの雰囲気中で基板を900℃に加熱することによってGaN:Mg層を形成する。最後に窒素雰囲気中において600℃でアニーリングを行うことによりLED構造を有する半導体ナノワイヤを得る。このようにして得られたナノワイヤのそれぞれの厚さはGaN:約5μm、n-GaN:Si:約10μm、InGaN:10nm、p-GaN:Mg:10μmである。そして上記手法により得られたナノワイヤをエタノール溶液中に分散する。基板からのナノワイヤの切り離しは超音波を用いて行うことができる。

一方、基板側についてはガラス基板上にゲート電極をパターンニングし、その上にゲート絶縁層としてシリカ膜を形成する。

## 【0055】

10

20

30

40

50

その後、図14における電極3の下部部分になるゲート絶縁層5に、図12に示すようにマイクロコンタクトプリントティング法により3-メルカプト-1-プロパノール(OHC<sub>3</sub>H<sub>6</sub>SH)を選択的にパターンニングし、SH基をパターンニングする。図12において、RはパターンニングされたSH基を示す。

#### 【0056】

そして、上記手法で得られた基板上に上記ナノワイヤ分散溶液を流すことにより、図13のようにAu微粒子触媒が選択的にSH基と結合することで、図14に示すように、N型の部分が電極3に揃うようになる。その後、ソース・ドレイン電極であるTi/Au電極を蒸着により形成する。

#### 【0057】

以上のような手法によって、青色発光をする表示素子と電界効果型トランジスタが形成される。本実施例により作製される表示装置は、電界効果型トランジスタとLEDを一括で形成できるので簡単な構成の表示装置を提供することができる。

#### 【0058】

##### <実施例2>

本実施例は、本発明を2次元光センサー(撮像装置)として用いた場合である。半導体ナノワイヤはシリコンを用いる。ナノワイヤの作製はVLS法を用いて行い作製する。作製方法は、まずシリコン基板上に粒径が50nmのAu微粒子を形成する。その後、SiH<sub>4</sub>およびPH<sub>3</sub>ガス雰囲気中で450℃で加熱することにより、PドープのN型Siナノワイヤを形成する。その後、SiH<sub>4</sub>およびB<sub>2</sub>H<sub>6</sub>ガス雰囲気中で450℃で加熱することにより、N型Siナノワイヤ上にP型Siナノワイヤを形成する。最後に窒素雰囲気中において500℃でアニーリングを行うことによりP-N接合を有するフォトダイオードナノワイヤを得る。このようにして得られたナノワイヤのそれぞれの厚さはN型10μm、P型：約30μmである。

#### 【0059】

そして上記手法により得られたナノワイヤをエタノール溶液中に分散する。

#### 【0060】

一方、基板側についてはガラス基板上にゲート電極をパターンニングし、その上にゲート絶縁層としてシリカ膜を形成する。

#### 【0061】

その後、図1における電極2の下部部分になるゲート絶縁層5に、図12に示すようにマイクロコンタクトプリントティング法により3-メルカプト-1-プロパノール(OHC<sub>3</sub>H<sub>6</sub>SH)を選択的にパターンニングし、SH基をパターンニングする。

#### 【0062】

そして、上記手法で得られた基板上に上記ナノワイヤ分散溶液を流すことにより、Au微粒子触媒が選択的にSH基と結合することで、図1に示すように、N型の部分が電極2に揃うようになる。ナノワイヤを配列し、その後、ソース・ドレイン電極であるTi/Au電極を蒸着により形成する。

#### 【0063】

以上のような手法によって、P-N接合を有するフォトダイオードと電界効果型トランジスタが形成される。本実施例により作製される2次元光センサー(撮像装置)は、トランジスタとフォトダイオードを一括で形成できるので簡単な構成の2次元光センサー(撮像装置)を提供することができる。

#### 【図面の簡単な説明】

#### 【0064】

【図1】(a)は本発明の一実施形態の半導体素子の一例を示す平面図、(b)はその断面図、(c)は等価回路図である。

【図2】VLS法による半導体ナノワイヤの合成方法を表す図である。

【図3】本発明の他の実施形態の半導体素子の一例を示す図である。

【図4】本発明の他の実施形態の半導体素子の一例を示す図である。

【図5】本発明の他の実施形態の半導体素子の一例を示す図である。

【図6】本発明の他の実施形態の半導体素子の一例を示す図である。

【図7】本発明の他の実施形態の半導体素子の一例を示す図である。

【図8】本発明の他の実施形態の半導体素子の一例を示す図である。

【図9】本発明の他の実施形態の半導体素子を複数配列させたときの一例を示す図である。

【図10】P-N接合を有する半導体ナノワイヤを示す図である。

【図11】P-N接合を有する半導体ナノワイヤに電極を備え付けた半導体素子の図である。

【図12】半導体ナノワイヤ1の配列方法を示す図である。

【図13】半導体ナノワイヤ1の配列方法を示す図である。

【図14】本発明の第1実施例の半導体素子の一例を示す図である。

【符号の説明】

【0065】

- 1 半導体ナノワイヤ

- 2 ソース電極

- 3 ドレイン電極

- 4 ゲート電極

- 5 ゲート絶縁層

- 6 基板

- 7 P-N接合領域

- 8 FET領域

- 9 触媒粒子

- 10 絶縁体

- 11 半導体ナノワイヤ

- 12 半導体ナノワイヤ

- 13 電極

- 14 半導体ナノワイヤ

- 20 基板

- 21 ソースライン

- 22 ゲートライン

- 23 半導体素子

- 200 半導体ナノワイヤ

- 201 基板

- 202 電極

10

20

30

【図1】

(a)

(b)

(c)

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

## フロントページの続き

| (51)Int.Cl.                    | F I          | テーマコード(参考) |

|--------------------------------|--------------|------------|

| <b>H 01 L 27/06 (2006.01)</b>  | H 01 L 29/78 | 6 1 8 B    |

| <b>H 01 L 29/786 (2006.01)</b> | H 01 L 29/78 | 6 2 2      |

| <b>H 01 L 27/146 (2006.01)</b> | H 01 L 27/14 | C          |

| <b>B 8 2 B 1/00 (2006.01)</b>  | B 8 2 B 1/00 |            |

| <b>H 01 L 27/15 (2006.01)</b>  | H 01 L 27/15 | B          |

F ターム(参考) 4M118 AA01 AB01 BA05 CA03 CA05 CB01 CB02 CB03 FB03 FB08

FB09 FB13 FB14

5F041 CA40 CB33

5F048 AA01 AC10 BA15 BA16

5F049 MA02 MB02 NB05 QA20 SS03

5F102 GA14 GB01 GC02 GD10 GJ10 GL04 GM04 HC01

5F110 AA30 BB01 BB10 CC01 DD01 DD02 EE02 EE03 EE04 EE06

EE42 EE43 EE44 FF01 FF02 FF03 FF22 FF26 GG01 GG02

GG03 GG04 GG24 GG30 GG42 HK02 HK03 HK04 HK06 HK32

NN71