(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2010-141066

(P2010-141066A)

(43) 公開日 平成22年6月24日(2010.6.24)

(51) Int.Cl.

H01L 23/12 (2006.01)

F 1

H01L 23/12

テーマコード (参考)

501T

審査請求 未請求 請求項の数 13 O L (全 14 頁)

(21) 出願番号

特願2008-315181 (P2008-315181)

(22) 出願日

平成20年12月11日 (2008.12.11)

(71) 出願人 000116024

ローム株式会社

京都府京都市右京区西院溝崎町21番地

(72) 発明者 安永 尚司

京都府京都市右京区西院溝崎町21番地ロ

ーム株式会社内

(54) 【発明の名称】半導体装置

(57) 【要約】 (修正有)

【課題】リードフレームを有さず小型薄型で放熱性が増した半導体装置を簡便な設備と低成本で提供する。

【解決手段】半導体チップ5と、前記半導体チップに接する第一端部9および他方側の第二端部10を有するワイヤ4と、前記半導体チップと前記ワイヤとを封止する封止樹脂層6と、を有する半導体装置において、前記ワイヤの第二端部の表面が前記封止樹脂層から露出していることから、フレームを有しない半導体装置が得られる。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

半導体チップと、

前記半導体チップに接するワイヤと、

前記ワイヤの一部を残して、前記ワイヤと前記半導体チップとを封止する封止樹脂層とかなることを特徴とする半導体装置。

**【請求項 2】**

前記ワイヤの一部は、キャビラリによって形成される端子部であることを特徴とする請求項 1 に記載の半導体装置。

**【請求項 3】**

半導体チップと、

第一端部と、前記半導体チップに接する第二端部を有するワイヤと、

前記第一端部に接し、前記ワイヤと同じ材質からなる端子部と、

前記ワイヤと前記半導体チップとを封止する封止樹脂層とかなることを特徴とする半導体装置。

**【請求項 4】**

前記端子部はひとつまたは連続した複数からなることを特徴とする請求項 2 から 3 に記載の半導体装置。

**【請求項 5】**

前記端子部はウエッジツールによって形成されることからなるステッチボンドであることを特徴とする請求項 2 から 4 に記載の半導体装置。

**【請求項 6】**

前記端子部に導体からなる電極が形成されていることを特徴とする請求項 2 から 5 に記載の半導体装置。

**【請求項 7】**

前記半導体チップが前記封止樹脂層から露出していることを特徴とする請求項 1 から 6 に記載の半導体装置。

**【請求項 8】**

半導体チップを支持材に実装する工程と、

前記半導体チップにワイヤを接続する工程と、

前記ワイヤの一部を端子部として形成する工程と、

さらに前記ワイヤと前記半導体チップとを封止する工程とを有することを特徴とする半導体装置の製造方法。

**【請求項 9】**

半導体チップを支持材に実装する工程と、

第一端部と、前記半導体チップにワイヤと同じ材質で第二端部を形成する工程と、

前記ワイヤと前記半導体チップとを封止する封止樹脂層を前記支持材上に形成する工程と、

前記支持材を除去することにより前記ワイヤの第一端部の面を前記封止樹脂層から露出させる工程とを有することを特徴とする半導体装置の製造方法。

**【請求項 10】**

前記第一端部に接し、前記ワイヤと同じ材質からなる端子部を前記支持材上に形成する工程を有することを特徴とする請求項 9 に半導体装置の製造方法。

**【請求項 11】**

前記端子部は前記支持材にひとつまたは連続して形成する工程を含むことを特徴とする請求項 8 から 10 に記載の半導体装置の製造方法。

**【請求項 12】**

前記端子部はウエッジツールによってステッチボンドを形成される工程を含むことを特徴とする請求項 8 から 11 に記載の半導体装置の製造方法。

**【請求項 13】**

10

20

30

40

50

前記端子部に導体からなる電極を形成する工程を有することを特徴とする請求項 8 から 12 に記載の半導体装置の製造方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子を搭載し、樹脂封止して形成される半導体装置の構造およびその製造方法に関する。 10

【0002】

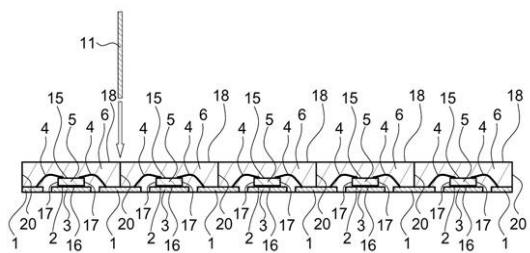

従来から MAP という半導体装置の製造方法がある。MAP とは、 Mold Array Package と呼ばれる一括樹脂封止技術であり、図 13 に示すようにダイボン材 2 を介して搭載したアイランド 3 と、フレーム 1 と、ワイヤ 4 とを封止樹脂層 6 で全面を一括で覆い、硬化させることにより全体を一括で樹脂封止し、さらにダイシングライン（半導体装置側面 20）に沿ってダイシングブレード 11 やレーザ（図示しない）などを用いて切断することにより、個片化された半導体装置 7 を製造する方法である。

なお、図 13 において、チップ表面 15 とチップ裏面 16 とチップ側面 17 と半導体装置表面 18 と半導体装置裏面 19 と半導体装置側面 20 はそれぞれの場所の名前を表す。 20

【0003】

この種の個片化された半導体装置の一例として、図 12 に示す構造がある。図 12 に示すようにチップ 5 をフレーム 1 上にダイボン材 2 を用いて設置され、ワイヤボンディング 4 を用いてチップ 5 とフレーム 1 を接続し、封止樹脂層 6 で封止される。 20

【特許文献 1】特開平 09 - 082741 号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

しかしながら、このような半導体装置は、以下のような課題を有する。

【0005】

電気製品の小型化が進む昨今において、半導体装置も同様にさらなる小型化や薄型化が要求され、同時に半導体装置のコストダウンも要求されている。しかし、従来の MAP 技術においては、フレーム 1 のような板があることで、小型化や薄型化、さらにはコストダウンの妨げとなっている。 30

【0006】

本発明は、このような従来技術の課題を解決するものであり、その目的とすることは、小型で薄型の半導体装置を提供するところにある。

【課題を解決するための手段】

【0007】

本発明はこのような目的を達成するためになされたもので、請求項 1 に記載の発明は、半導体チップと、前記半導体チップに接するワイヤと、前記ワイヤの一部を残して、前記ワイヤと前記半導体チップとを封止する封止樹脂層とからなることを特徴とする。

これによると、半導体装置がフレームを有しないため、従来の半導体装置よりもコストが下がるとともに、大きく薄型化にも貢献する。ワイヤの一部が樹脂層から露出していればよいため、樹脂層の裏面側だけでなく、樹脂層の側面からワイヤの一部が露出してもよい。このとき、半導体装置を実装基板に実装する時の半田の濡れ性が向上するため、電気的接続の信頼性も向上する。 40

【0008】

請求項 2 に記載の発明は、請求項 1 に記載の発明において、前記ワイヤの一部は、キャピラリによって形成される端子部であることを特徴とする。

これによると、ワイヤの一部である前記端子部はキャピラリによって作られる。従来、半導体装置の端子部は別途リードフレームなどを必要としていたが、上記のように前記端子部がキャピラリによって形成できるため、コストが下がるとともに、薄型化にも大きく貢献する。 50

**【 0 0 0 9 】**

請求項 3 に記載の発明は、半導体チップと、第一端部と、前記半導体チップに接する第二端部を有するワイヤと、前記第一端部に接し、前記ワイヤと同じ材質からなる端子部と、前記ワイヤと前記半導体チップとを封止する封止樹脂層とからなることを特徴とする半導体装置である。

これによると、半導体装置がフレームを有さず、また前記端子部がワイヤと同じ材質からなるため、別途リードフレームなどを必要としていたが、上記のように前記端子部がキャピラリによって形成できるため、コストが下がるとともに、大きく薄型化にも貢献する。

**【 0 0 1 0 】**

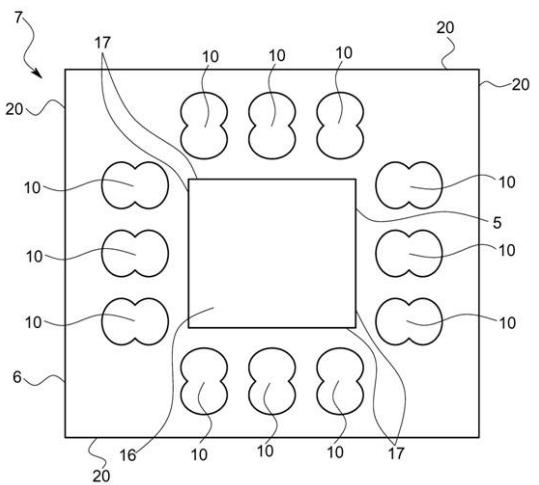

請求項 4 に記載の発明は、請求項 2 から 3 に記載の発明において、前記端子部はひとつまたは連続した複数からなることを特徴とする記載の半導体装置である。 10

これによると、端子部を複数個直線状に連続させることにより、前記端子部のサイズを大きくできる。または、前記端子部を複数個任意に連続させることにより、半導体装置を実装基板などへ実装する際に、前記端子部のサイズや形状を任意に形成することが可能となり、設計の自由度が増す。

**【 0 0 1 1 】**

請求項 5 に記載の発明は、請求項 2 から 4 に記載の発明において、前記端子部はウエッジツールによって形成されることからなるステッチボンドであることを特徴とする半導体装置である。

これによると、前記端子部をウエッジツールによって形成されるステッチボンドの形状にすると、実装基板などへ実装する際に、前記端子部の形状を略矩形に形成することができるため、従来の QFN パッケージとほぼ同じ端子形状と見なすことができることから、従来と同じ設備で実装基板に半導体装置を実装するため、不要なコストがかからない。 20

**【 0 0 1 2 】**

請求項 6 に記載の発明は、請求項 2 から 5 に記載の発明において、前記端子部に導体からなる電極が形成されていることを特徴とする半導体装置である。

これによると、従来と同じ例えは半田ボール付きのパッケージと見なすことができるため、従来と同じ設備で実装基板に半導体装置を実装できるため、不要なコストがかからない。 30

**【 0 0 1 3 】**

請求項 7 に記載の発明は、請求項 1 から 6 に記載の発明において、前記半導体チップが前記封止樹脂層から露出していることを特徴とする半導体装置である。

これによると、前記半導体チップは前記樹脂層から露出していればよいため、前記樹脂層のどの面から露出していてもよい。すると、前記半導体チップが前記樹脂層から露出しているため、放熱性が高く、熱対策が容易となる。

**【 0 0 1 4 】**

請求項 8 に記載の発明は、半導体チップを支持材に実装する工程と、前記半導体チップにワイヤを接続する工程と、前記ワイヤの一部を端子部として形成する工程と、さらに前記ワイヤと前記半導体チップとを封止する工程とを有することを特徴とする半導体装置の製造方法である。 40

これによると、半導体装置がフレームを有しないため、従来の半導体装置よりもコストが下がるとともに、薄型化にも大きく貢献する半導体装置の製造方法が得られる。また、ワイヤの一部が樹脂層から露出していればよいため、樹脂層の裏面側だけでなく、樹脂層の側面からワイヤの一部が露出してもよい。このとき、半導体装置を実装基板に実装する時の半田の濡れ性が向上するため、電気的接続の信頼性も向上する半導体装置の製造方法が得られる。

**【 0 0 1 5 】**

請求項 9 に記載の発明は、半導体チップを支持材に実装する工程と、第一端部と、前記半導体チップにワイヤと材質で第二端部を形成する工程と、前記ワイヤと前記半導体チップとを封止する封止樹脂層を前記支持材上に形成する工程と、前記支持材を除去することに 50

より前記ワイヤの第一端部の面を前記封止樹脂層から露出させる工程とを有することを特徴とする半導体装置の製造方法である。

これによると、半導体装置がフレームを有さず、また前記端子部がワイヤと同じ材質からなるため、別途リードフレームなどを必要としていたが、上記のように前記端子部がキャピラリによって形成できるため、コストが下がるとともに、薄型化にも大きく貢献する半導体装置の製造方法が得られる。

#### 【0016】

請求項10に記載の発明は、請求項9に記載の発明において、前記第一端部に接し、前記ワイヤと同じ材質からなる端子部を前記支持材上に形成する工程を有することを特徴とする半導体装置の製造方法である。10

これによると、前記第一端部と同じ材質の端子部を前記支持材上に形成するため、前記支持材を除去したときに前記ワイヤと同じ材質の端子で形成できるので、別の材質を用意する必要が無く、不要なコストがかからない製造方法が得られる。

#### 【0017】

請求項11に記載の発明は、請求項8から10に記載の発明において、前記端子部は前記支持材にひとつまたは連続して形成する工程を含むことを特徴とする半導体装置の製造方法である。

これによると、端子部を複数個直線状に連続させることにより、前記端子部のサイズを大きくできる。または、前記端子部を複数個任意に連続させることにより、半導体装置を実装基板などへ実装する際に、前記端子部のサイズや形状を任意に形成することが可能となり、設計の自由度が高い半導体装置の製造方法が得られる。20

#### 【0018】

請求項12に記載の発明は、請求項8から11に記載の発明において、前記端子部はウエッジツールによってステッチボンドを形成される工程を含むことを特徴とする半導体装置の製造方法である。

これによると、前記端子部をウエッジツールによって形成されることからなるステッチボンドの形状にすると、実装基板などへ実装する際に、前記端子部の形状を略矩形に形成することができるため、従来のQFNパッケージとほぼ同じ端子形状と見なすことができることから、従来と同じ設備で実装基板に半導体装置を実装するため、不要なコストがかからない半導体装置の製造方法が得られる。30

#### 【0019】

請求項13に記載の発明は、請求項8から12に記載の発明において、前記端子部に導体からなる電極を形成する工程を有することを特徴とする半導体装置の製造方法である。

これによると、従来と同じ例えば半田ボール付きのパッケージと見なすことができるために、従来と同じ設備で実装基板に半導体装置を実装できるため、不要なコストがかからない半導体装置の製造方法が得られる。

#### 【発明の効果】

#### 【0020】

以上、本発明によると、従来のような半導体チップを載せるためのフレームを有しないため、半導体装置のコストが下がるとともに、薄型化にも貢献する。また、ワイヤの第一端部が樹脂層から露出しているため、放熱性が増す。さらに、半導体装置を実装基板に実装する時の半田の濡れ性が向上するため、電気的接続の信頼性も向上する。40

#### 【0021】

さらに、ワイヤの第一端部が一回または複数回ボンディングすることからなるボンディング部の形状を有すると、実装基板などへ実装する際に、ワイヤの第一端部のサイズや形状を任意に設定できるため、設計の自由度が増す。

#### 【0022】

また、ワイヤの第一端部がウエッジツールを用いることからなるボンディング部の形状であると、実装基板などへ実装する際に、封止樹脂層から露出するワイヤの第一端部の形状を略矩形に形成することができるため、従来のQFNパッケージと見なすことができるこ50

とから、従来と同じ設備で実装基板に半導体装置を実装できるため、不要なコストがかからない。

#### 【0023】

さらに、ワイヤの第一端部に半田ボールのような導体からなる電極が形成されていると、従来と同じパッケージと見なすことができるところから、従来と同じ設備で実装基板に半導体装置を実装できるため、不要なコストがかからない。

#### 【0024】

また、半導体チップが封止樹脂から露出しているため、放熱性が高く、熱対策が容易となる。

#### 【0025】

さらに、半導体装置は半導体チップを支持材に実装する工程と、前記半導体チップの所定の場所に導体からなるワイヤで第二端部を形成し、さらに前記支持材に前記ワイヤの第一端部を形成することにより、前記ワイヤの第二端部と前記ワイヤの第一端部とを前記ワイヤで接続する工程と、前記半導体チップと前記ワイヤと前記ワイヤの第二端部と前記ワイヤの第一端部とを封止する封止樹脂層を前記支持材上に形成する工程と、前記支持材を除去することにより前記ワイヤの第一端部の表面を前記封止樹脂層から露出させる工程と、からなるため、フレームを有しない半導体装置が完成する。よって、従来のような半導体チップを載せるためのフレームを有しないため、半導体装置のコストが下がるとともに、薄型化にも貢献する半導体装置の製造方法がえられる。また、ワイヤの第一端部が樹脂層から露出しているため、放熱性が増す。さらに、半導体装置を実装基板に実装する時の半田の濡れ性が向上するため、電気的接続の信頼性も向上する。

10

20

30

#### 【0026】

さらに、上記工程において、前記ワイヤの第一端部は支持材に一回または複数回ボンディングすることにより形成される工程からなると、ワイヤボンディングの第一端部を支持材の同一地点に複数回ボンディングすることによりワイヤの第一端部を形成すると、ワイヤの第一端部のサイズを大きくできる。また、上記ワイヤの第一端部を複数回ボンディングする場所を支持材の同一地点でない場所にすると、実装基板などへ実装する際に、封止樹脂層から露出するワイヤの第一端部のサイズを、任意のサイズや形状に形成することが可能となり、さらに設計の自由度が増す半導体装置の製造方法がえられる。

#### 【0027】

また、ワイヤの第一端部を上記支持材へのボンディングにおいて、ウェッジツールを用いることにより形成される工程からなると、ワイヤボンディングの第一端部が略矩形に形成されることから、実装基板などへ実装する際に、封止樹脂層から露出するワイヤの第一端部の形状を略矩形に形成することができるため、従来のQFNパッケージと見なすことができる。よって、従来と同じ設備で実装基板に半導体装置を実装できるため、さらに不要なコストがかからない半導体装置の製造方法がえられる。

40

#### 【実施例】

#### 【0028】

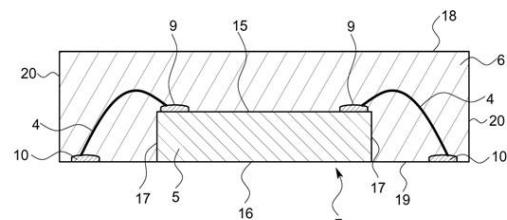

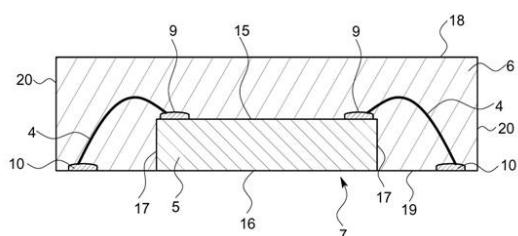

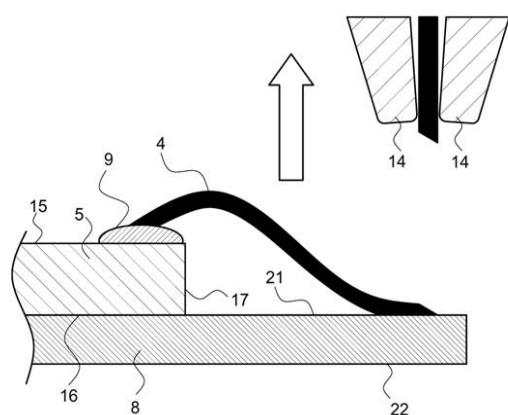

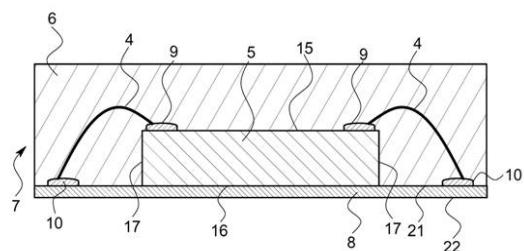

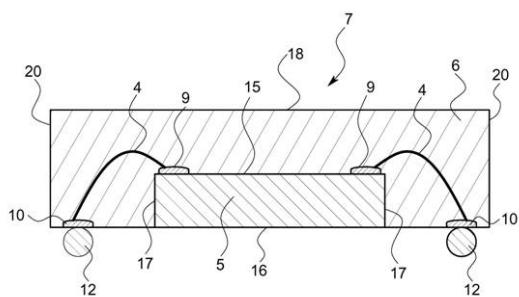

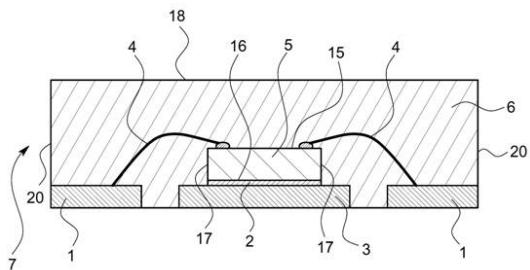

(実施例1) 図1は本発明の半導体装置の構造の一例の断面図であり、図1の半導体装置の製造方法を図2、図3、図4で説明する。

#### 【0029】

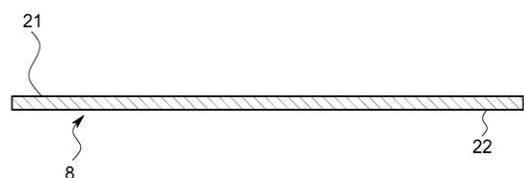

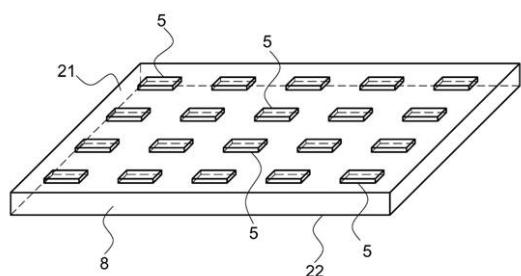

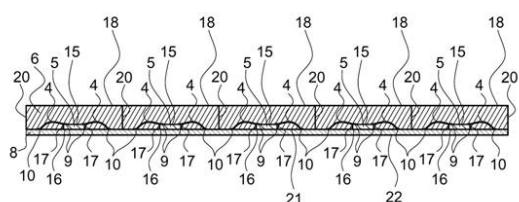

図2(a)は本発明による複数の半導体装置7を製造する過程を説明するために示した支持材8の断面図である。まず、支持材8を用意し、チップ5を実装する面を上向きにして設置する。ここで、支持材8はワイヤボンディングが可能な材料であればよく、セラミックやアルミや銅などの板や、シートや粘着テープなどの粘着材やシートが挙げられる。

#### 【0030】

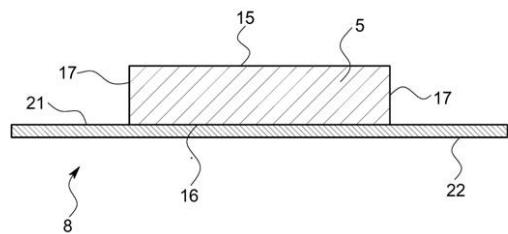

次に図2(b)のように支持材裏面22とは反対側の支持材表面21にチップ5を実装させる。例えば支持材8が金属板である場合、銀ペーストを含むダイボン材2などを介してチップ5を支持材表面21に実装させる。または粘着シートや粘着テープなどの場合、ダ

50

イポン材は介さずチップ5を支持材表面21の所望の位置に実装させる。図2(c)は、図2(b)のチップのうち、一つに着目した断面図である。

#### 【0031】

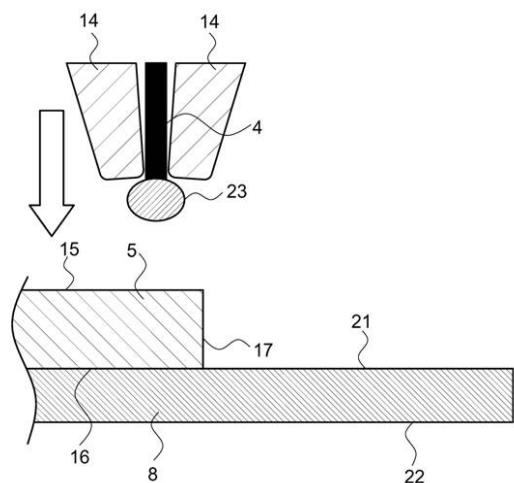

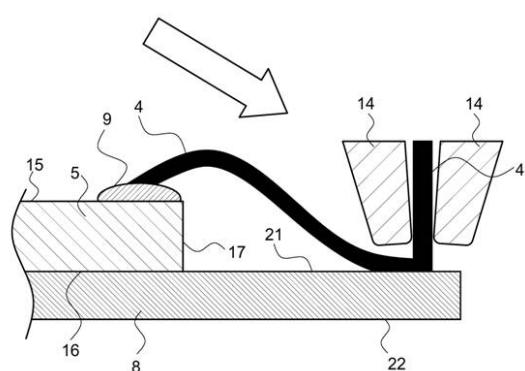

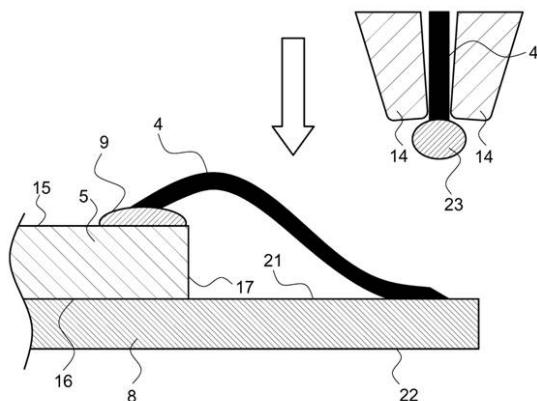

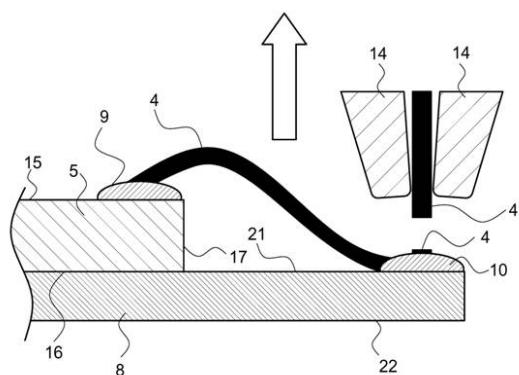

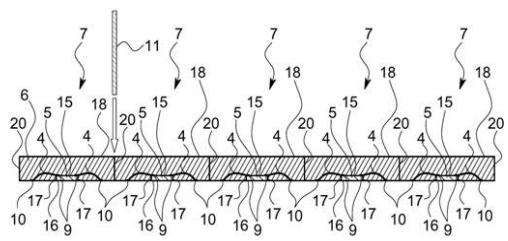

次にキャピラリ14でワイヤボンディングする図を、図3(a)～図3(e)に工程順に示す。チップ5のワイヤの第二端部9などの所定の場所から支持材8の所望の位置のワイヤの第一端部10までワイヤ4を形成するために、キャピラリ14でワイヤボンディングをする。ここで、ワイヤの第一端部10は最終的にはこの半導体装置7の表面から露出し、半導体装置7の外部電極になることから、ワイヤの第一端部10のサイズを大きくするために、チップ5のワイヤの第一端部10などの所定の場所に、ワイヤボール23を形成したあとに、ワイヤの第一端部を形成することで、ワイヤの第一端部10を大きくできる。さらに、他端側の第一端部までワイヤ4を形成し、ワイヤの第一端部10を形成する。さらにワイヤの第一端部10を大きくするには上記の工程を同一地点で繰り返してボンディングすることによって形成できる。または、ワイヤ4を形成する前にワイヤの第一端部10を形成し、その後ワイヤ4を形成することも可能である。また、チップ5から支持材8にワイヤ4を形成する例をあげたが、これとは逆に、支持材表面21からチップ5に向かってワイヤ4を形成してもよい。

10

#### 【0032】

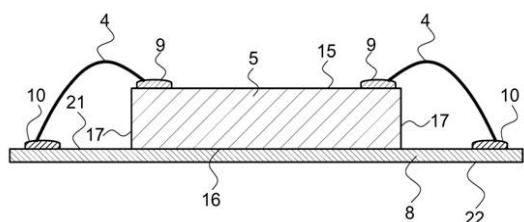

上記工程により、図4(a)のような断面図になり、さらに図4(b)のように、ワイヤ4を形成した半導体装置7を、エポキシなどの封止樹脂層6で封止し、個片化させる。詳しくは、図4(c)に示すように、支持材8に実装させたチップ5とワイヤ4とワイヤの第一端部9とワイヤの第一端部10とを覆うように封止樹脂層6で一括封止し、レーザやダイシングブレード11で個片化することにより、図4(b)のような構造となる。なお、個片化は支持材8を除去する前後のどちらでも良いが、今回は支持材8を除去した後に個片化する工程を記す。

20

#### 【0033】

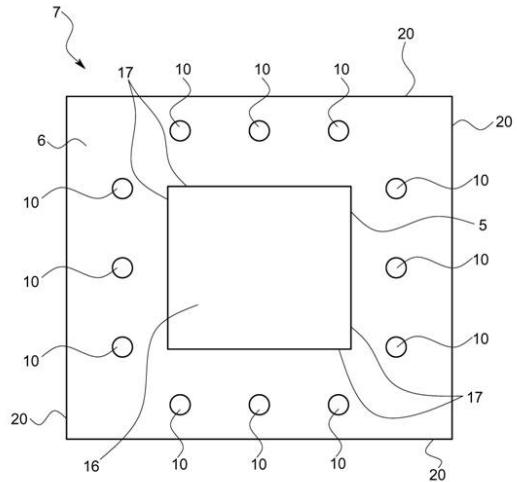

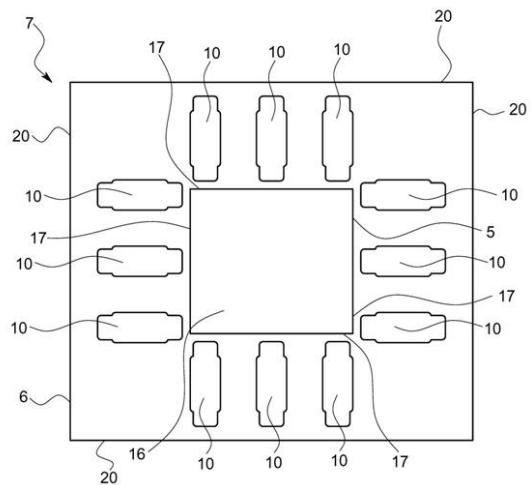

次に図4(c)のように支持材8を除去する。詳しくは、例えば支持材8が金属板である場合、裏面からウエットエッティングやCMP(化学機械研磨)や研削などにより、支持材8を除去する。また、ワイヤの第一端部10も同様に研削してもよい。次に図4(d)で示すように、個片化させたいラインに沿ったダイシングラインに沿って切斷することにより、半導体装置7が得られる。半導体装置7を裏面から見ると、図5のようにワイヤの第一端部10は円状の外部端子になる。ワイヤの第一端部10の直径は例えば $10\text{ }\mu\text{m} \sim 200\text{ }\mu\text{m}$ 程度である。

30

#### 【0034】

最後に図6に示すように、半導体装置7を裏面から見ると、ワイヤの第一端部10の表面が半導体装置7から露出しており、このワイヤの第一端部10に半田ボール12を形成すると、公知のパッケージと同じ端子形状となり、従来の工程や手法、設備などを利用できるため、余分なコストも必要ない。

40

#### 【0035】

##### (実施例2)

実施例1と同様に、まず支持材8を用意し、チップ5を実装する面を上向きにして設置する。ここで、支持材8はワイヤボンディングが可能な材料であればよく、セラミックやアルミや銅などの板状部材や、シートや粘着テープなどのシート状部材が挙げられる。

#### 【0036】

そして、支持材8の上にチップ5を実装させる。例えば支持材8が金属板である場合、ダイポン材を介してチップ5を支持材8に実装させる。または粘着シートや粘着テープなどの場合、ダイポン材は介さずチップ5を支持材8の所望の位置に実装させる。

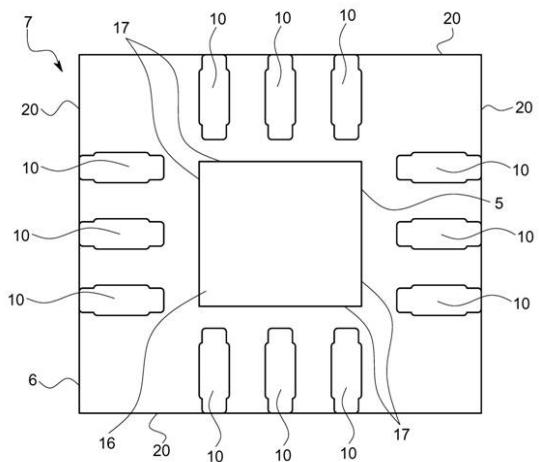

#### 【0037】

次に、チップ5のワイヤの第二端部9などの所定の場所から支持材8の所望の位置のワイヤの第一端部10までワイヤ4を形成する。ここで、ワイヤの第一端部10は最終的にはこの半導体装置7の表面から露出し、半導体装置7の外部電極になることから、図7のよ

50

うに、公知のウェッジツールを用いることによってワイヤの第二端部10を形成すると、ワイヤの第一端部10は略矩形に形成することができる。ウェッジツールを用いることによるワイヤの第一端部10の短辺は例えば $50\text{ }\mu\text{m} \sim 500\text{ }\mu\text{m}$ で、長辺は例えば $50\text{ }\mu\text{m} \sim 2\text{ mm}$ 程度である。ここで、ワイヤの第一端部10は半導体装置7の表面から露出していればよいので、図8に示すように半導体装置7の側面から露出していてもよい。この時、半導体装置7を実装基板に実装する時、半田が実装面のワイヤの第一端部10だけではなく露出面13にも付着することができる。

#### 【0038】

そして、ワイヤボンディングを形成した半導体装置7を、エポキシなどの封止樹脂層6で封止する。詳しくは、支持材8に実装させたチップ5とワイヤ4とワイヤの第二端部9とワイヤの第一端部10とを覆うように封止樹脂層6で封止する。10

#### 【0039】

次に、支持材8を除去する。詳しくは、例えば支持材8が金属板である場合、裏面からウエットエッチングやCMPや研削などにより、支持材8を除去する。また、ワイヤの第一端部10も同様に研削してもよい。そして、ダイシングラインに沿って切断することにより、半導体装置7が得られる。

#### 【0040】

以上、ボンディング部をウェッジツールを用いることにより形成すると、実装基板などへ実装する際に、封止樹脂層から露出するワイヤの第一端部の形状を略矩形に形成することができるため、従来のQFNパッケージと見なすことができるところから、従来と同じ設備で実装基板に半導体装置を実装できるため、不要なコストがかからない。20

#### 【図面の簡単な説明】

#### 【0041】

【図1】本発明の一実施例を示す断面図。

【図2a】本発明の一製造方法を示す断面図。

【図2b】本発明の一製造方法を示す断面図。

【図2c】本発明の一製造方法を示す断面図。

【図3a】本発明の一製造方法を示す断面図。

【図3b】本発明の一製造方法を示す断面図。

【図3c】本発明の一製造方法を示す断面図。

【図3d】本発明の一製造方法を示す断面図。

【図3e】本発明の一製造方法を示す断面図。

【図4a】本発明の一製造方法を示す断面図。

【図4b】本発明の一製造方法を示す断面図。

【図4c】本発明の一製造方法を示す断面図。

【図4d】本発明の一製造方法を示す断面図。

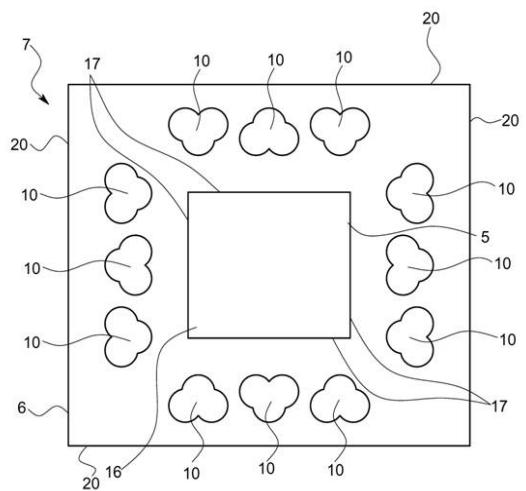

【図5】本発明の実施例1を示す裏面図。

【図6】本発明の実施例1を示す断面図。

【図7】本発明の実施例2を示す裏面図。

【図8】本発明の実施例2を示す裏面図。

【図9】本発明の実施例2を示す裏面図。

【図10】本発明の実施例2を示す裏面図。

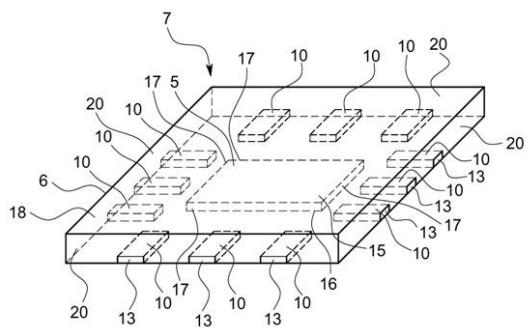

【図11】本発明の実施例2を示す斜視図。

【図12】従来例を示す断面図。

【図13】従来例の一製造方法を示す断面図。

#### 【符号の説明】

#### 【0042】

1 フレーム

2 ダイポン材

3 アイランド

10

20

30

40

50

|    |               |    |

|----|---------------|----|

| 4  | ワイヤ           |    |

| 5  | チップ           |    |

| 6  | 封止樹脂          |    |

| 7  | 半導体装置         |    |

| 8  | 支持材           |    |

| 9  | ワイヤの第二端部      |    |

| 10 | ワイヤの第一端部(端子部) |    |

| 11 | ダイシングブレード     |    |

| 12 | 半田ボール         |    |

| 13 | 露出面           | 10 |

| 14 | キャピラリ         |    |

| 15 | チップ表面         |    |

| 16 | チップ裏面         |    |

| 17 | チップ側面         |    |

| 18 | 半導体装置表面       |    |

| 19 | 半導体装置裏面       |    |

| 20 | 半導体装置側面       |    |

| 21 | 支持材表面         |    |

| 22 | 支持材裏面         |    |

| 23 | ワイヤボール        | 20 |

【図1】

【図2 a】

【図2 b】

【図 2 c】

【図 3 a】

【図 3 b】

【図 3 c】

【図 3 d】

【図 3 e】

【図 4 a】

【図 4 b】

【図 4 c】

【図4d】

【 図 5 】

【図6】

【 図 7 】

【図8】

【図9】

【図10】

【 図 1 1 】

【図12】

【 図 1 3 】