(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5632694号

(P5632694)

(45) 発行日 平成26年11月26日(2014.11.26)

(24) 登録日 平成26年10月17日(2014.10.17)

(51) Int.Cl.

F 1

|                   |                  |            |   |

|-------------------|------------------|------------|---|

| <b>H01L 43/08</b> | <b>(2006.01)</b> | H01L 43/08 | S |

| <b>H01L 43/12</b> | <b>(2006.01)</b> | H01L 43/08 | Z |

| <b>G11B 5/39</b>  | <b>(2006.01)</b> | H01L 43/12 |   |

|                   |                  | G11B 5/39  |   |

請求項の数 16 (全 29 頁)

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2010-223722 (P2010-223722) |

| (22) 出願日     | 平成22年10月1日 (2010.10.1)       |

| (65) 公開番号    | 特開2011-97046 (P2011-97046A)  |

| (43) 公開日     | 平成23年5月12日 (2011.5.12)       |

| 審査請求日        | 平成25年5月22日 (2013.5.22)       |

| (31) 優先権主張番号 | 09174576.0                   |

| (32) 優先日     | 平成21年10月30日 (2009.10.30)     |

| (33) 優先権主張国  | 欧州特許庁 (EP)                   |

|           |                                                              |

|-----------|--------------------------------------------------------------|

| (73) 特許権者 | 000005108<br>株式会社日立製作所<br>東京都千代田区丸の内一丁目6番6号                  |

| (74) 代理人  | 110000855<br>特許業務法人浅村特許事務所                                   |

| (72) 発明者  | 小川 晋<br>イギリス国 C B 3 O F Z ケンブリッジ・ケンブリッジ、チャールズ・バベッジ・ロード 6、B 3 |

| (72) 発明者  | デイビッド ウィリアムズ<br>イギリス国 C B 1 2 E B ケンブリッジ・ケンブリッジ、グレシャム・プレース 3 |

最終頁に続く

(54) 【発明の名称】磁気抵抗デバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

表面を有する基板と、

細長半導体チャネルと、

該チャネルへの接点の組を提供する少なくとも2つの導電性リードを含む磁気抵抗デバイスであって、

前記チャネルは前記表面上に形成されて第一方向に伸びており、

前記2つの導電性リードは前記チャネルと前記接点の組で接し、かつ前記第一方向に対して垂直方向に配置されており、

前記チャネルと前記少なくとも2つの導電性リードとは、前記第一方向と前記表面とに垂直な第二方向に前記基板に対して積重ねられ、

前記磁気抵抗デバイスは、前記チャネルに沿って前記第一方向と前記第二方向に平行な側面を有し、該側面に対し略垂直な方向の磁場に対して反応することを特徴とする磁気抵抗デバイス。

## 【請求項 2】

請求項1記載の磁気抵抗デバイスにおいて、さらに、前記チャネルと接触した半導体シャントを含み、該シャント、前記チャネル及び前記接点の組は、前記第二方向に基板に対して積重ねられていることを特徴とする磁気抵抗デバイス。

## 【請求項 3】

請求項2記載の磁気抵抗デバイスにおいて、前記チャネルは、不純物添加がなされてい

10

20

ないか、あるいは、前記チャネルは、前記シャントより軽く不純物添加がなされていて、前記シャントとは反対の導電型を有することを特徴とする磁気抵抗デバイス。

【請求項 4】

請求項 2 又は 3 記載の磁気抵抗デバイスにおいて、前記シャントは単結晶であることを特徴とする磁気抵抗デバイス。

【請求項 5】

請求項 2 乃至 4 記載のいずれかの磁気抵抗デバイスにおいて、前記シャントはケイ素を含むことを特徴とする磁気抵抗デバイス。

【請求項 6】

請求項 2 乃至 5 記載のいずれかの磁気抵抗デバイスにおいて、さらに、前記シャントに接した導電性層を含み、前記シャントは、前記導電性層と前記チャネルとの間に置かれていることを特徴とする磁気抵抗デバイス。 10

【請求項 7】

請求項 6 記載の磁気抵抗デバイスにおいて、前記導電性層はケイ素を含むことを特徴とする磁気抵抗デバイス。

【請求項 8】

請求項 6 又は 7 記載の磁気抵抗デバイスにおいて、前記導電性層は基板の最上位層を含むことを特徴とする磁気抵抗デバイス。

【請求項 9】

請求項 6 又は 7 記載の磁気抵抗デバイスにおいて、前記導電性層はケイ化金属 (metal silicide) を含むことを特徴とする磁気抵抗デバイス。 20

【請求項 10】

請求項 1 乃至 9 記載のいずれかの磁気抵抗デバイスにおいて、前記チャネルは、第二半導体層と、第三半導体層の一部とを含み、前記第二半導体層は、前記シャントと前記第三半導体層との間に置かれることを特徴とする磁気抵抗デバイス。

【請求項 11】

請求項 10 記載の磁気抵抗デバイスにおいて、前記第二半導体層と前記第三半導体層の部分とは単結晶であり、及び / 又は、前記第三半導体層の他の部分は非結晶性であることを特徴とする磁気抵抗デバイス。

【請求項 12】

請求項 1 乃至 11 記載のいずれかの磁気抵抗デバイスにおいて、前記チャネルは、ケイ素又はケイ素ゲルマニウム (silicon-germanium) を含むことを特徴とする磁気抵抗デバイス。 30

【請求項 13】

請求項 1 乃至 12 記載のいずれかの磁気抵抗デバイスにおいて、さらに、誘電体層を含み、該誘電体層はトレンチ (溝) を含み、前記シャント及び少なくとも前記チャネルの一部は、前記トレンチ (溝) の中に形成されていることを特徴とする磁気抵抗デバイス。

【請求項 14】

請求項 1 乃至 13 記載のいずれかの磁気抵抗デバイスにおいて、前記少なくとも 2 つのリードは、ケイ素及び / 又はケイ化金属を含むことを特徴とする磁気抵抗デバイス。 40

【請求項 15】

請求項 1 乃至 14 記載のいずれかの磁気抵抗デバイスにおいて、さらに、追加のリードを含み、該リードは、前記チャネルへのさらに別の接点を与え、前記チャネルは、前記さらに別の接点と、接点の組との間に置かれていることを特徴とする磁気抵抗デバイス。

【請求項 16】

請求項 1 乃至 15 記載のいずれかの磁気抵抗デバイスにおいて、さらに、第一及び第二磁気遮蔽層を含み、前記シャント、前記チャネル及び前記接点の組は、前記第一及び第二磁気遮蔽層の間に置かれていることを特徴とする磁気抵抗デバイス。

【発明の詳細な説明】

【技術分野】

**【0001】**

本発明は磁気抵抗デバイスに関するものであり、次のものに限定するものではないが、特にハードディスクドライブの読み出しヘッドとして用いられるものに関する。

**【背景技術】****【0002】**

ハードディスクドライブ(HDD)(又は、“磁気ディスクドライブ”)は、高密度情報記憶のために広く用いられている。HDDは、この種類の記憶を伝統的に備えたサーバやデスクトップコンピュータなどの計算機システムでは、普通に採用されているものである。しかし、例えば1インチドライブなどの、小型ハードディスク機構のHDDは、音楽プレーヤやデジタルカメラなどの携帯型電子装置にも採用されている。

10

**【先行技術文献】****【特許文献】****【0003】**

【特許文献1】EP 1 868 254 A

【特許文献2】EP 08 157 887.4

【特許文献3】US 2006/0022672 A1

【特許文献4】EP 08 157 888.2

**【非特許文献】****【0004】**

【非特許文献1】エス・エー・ソリン(S. A. Solin)、ティー・ティオ(T. Thio)、ディー・アール・ハインズ(D. R. Hines)、ジェイ・ジェイ・ヘレマン(J. J. Heremans)著、“非均質ナロー・ギャップ半導体における拡張された室温幾何学的磁気抵抗”(Enhanced Room-Temperature Geometric Magnetoresistance in Inhomogeneous Narrow-Gap Semiconductors)、サイエンス誌、第289巻、1530ページ、2000年発行

20

【非特許文献2】エス・エー・ソリン(S. A. Solin)、ディー・アール・ハインズ(D. R. Hines)、エー・シー・エイチ・ロー(A. C. H. Rowe)、ジェイ・エス・ツアイ(J. S. Tsai)、ユー・エー・パシュキン(Yu A. Pashkin)著、“異常磁気抵抗を用いたナノレベルの磁場センサ”(Nanoscopic magnetic field sensor based on extraordinary magnetoresistance)、真空科学及び技術誌(Journal of Vacuum Science and Technology)、B21巻、3002ページ、2003年発行

30

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

HDDの高密度情報記憶は、記憶密度を向上させることにより実現することができる。現在、記憶密度は、およそ毎年倍増しており、磁気記憶媒体に縦方向に配置したビットセルへのデータ記録や、いわゆる“スピン値”読み出しヘッドを用いたデータ読みしなどの、既存の技術を用いて達成できる最大の記憶密度は、概ね $100\text{Gb/in}^2$ である。

**【0006】**

しかし、HDDの記憶密度は増加を続けているため、記憶媒体と読み出しヘッドは、超常磁性効果の問題を抱えている。

40

**【0007】**

超常磁性効果は、強磁性体結晶粒が十分に小さいため、結晶粒の磁化方向を変化させるために必要なエネルギーが熱エネルギーと同等となる場合に生じる。従って、結晶粒の磁化は、変動の影響を受けるため、データ破壊に至ることもある。

**【0008】**

記憶媒体については、この問題に対して解決策が示されている。その解決策は、記録媒体の表面に対して(長手方向ではなく)垂直方向にビットセルを配置することにより、各ビットセルを十分大きくして、超常磁性効果を回避できるというものである。

**【0009】**

読み出しヘッド側で、この問題を解決するために、強磁性材料を用いることを避け、いわ

50

ゆる、異常磁気抵抗（EMR）効果の利点を生かす提案がなされている。

#### 【0010】

EMR効果を有するデバイスは、エス・エー・ソリン（S. A. Solin）、ティー・ティオ（T. Thio）、ディー・アール・ハインズ（D. R. Hines）、ジェイ・ジェイ・ヘレマン（J. J. Heremans）著、“非均質ナローギャップ半導体における拡張された室温幾何学的磁気抵抗”サイエンス誌、第289巻、1530ページ、2000年発行に記載されている。このデバイスはファンデルポー構成（van der Pauw configuration）で配置され、非磁性アンチモン化インジウム（InSb）のディスクに同心状に埋め込まれた金不均質体（gold inhomogeneity）を含んでいる。磁場がゼロ（H = 0）の場合、電流は金不均質体を流れる。しかし、磁場がゼロでない（H ≠ 0）場合には、金不均質体の周囲の円環を貫通する磁場の境界線分布に対して、電流は垂直に屈曲する。これにより、コンダクタンスが下がる。10

#### 【0011】

現在、アンチモン化インジウム（300 °Kで、 $\mu_n = 7 \times 10^4 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ ）、砒化インジウム（300 °Kで、 $\mu_n = 3 \times 10^4 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ ）、砒化ガリウム（300 °Kで、 $\mu_n = 8.5 \times 10^3 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ ）などの、低キャリア密度を有する高移動性狭ギャップ半導体は、EMRを用いた読み込みヘッドの材料として最良の候補とされている。

#### 【0012】

エス・エー・ソリン（S. A. Solin）、ディー・アール・ハインズ（D. R. Hines）、エー・シー・エイチ・ロー（A. C. H. Rowe）、ジェイ・エス・ツァイ（J. S. Tsai）、ユー・エー・パシュキン（Yu A. Pashkin）著、“異常磁気抵抗を用いたナノレベルの磁場センサ”、真空科学及び技術誌（Journal of Vacuum Science and Technology）、B 21巻、3002ページ、2003年発行には、砒化インジウム／アンチモン化インジウムアルミニウム（InSb/In<sub>1-x</sub>Al<sub>x</sub>Sb）の量子井戸ヘテロ構成を含むホールバー型構成（Hall bar-type arrangement）を有するデバイスが記載されている。20

#### 【0013】

このデバイスの欠点は、活性層を保護し閉じこめるために、厚い（すなわち、概ね75 nm）パッシベーション層と、窒化ケイ素の層の形状を有する絶縁膜とを必要とする点にある。これにより、チャネルと磁気媒体との間の分離が向上するため、磁場の強度を弱めることとなり、結果として出力信号の強度が下がる。30

#### 【0014】

ケイ素は、保護を必要とせず、ケイ素に由来した磁気抵抗特性を有する磁場センサが知られている。

#### 【0015】

例えば、EP 1 868 254 A1は、ケイ素で形成したチャネルを有し、EMR効果を有するデバイスを記載している。ケイ化チタン又は高濃度で不純物添加されたケイ素で形成された導体は、シャントとして作用し、これが、チャネルの片側面に沿ってチャネルに接続している。複数のリードは、チャネルの反対側に、チャネルに沿って間隔を置いて接続している。これにより、チャネル、シャント及びリードは、デバイスを構成する層に垂直な方向の磁場に対して反応する側面EMRデバイス又は“平面状”EMRデバイスを形成するものとなる。40

#### 【0016】

2008年6月9日出願の欧州特許出願番号EP 08 157 887.4（EPC 54条（3））には、ケイ素で形成されたチャネルを有し、細長いチャネルを含む平面状EMRデバイスが記載されている。シャントが、チャネルの片側面に沿ってチャネルに接続しており、複数のリードの組が、チャネルの反対側面に沿って接続している。このデバイスは、チャネルに反転層を形成するための上面ゲート構造も含んでいる。

#### 【0017】

US 2006/0022672 A1には、III-Vヘテロ構造で形成された、他の平面状EMRデバイスが記載されている。50

## 【0018】

2008年6月9日出願欧州特許出願番号EP 08 157 888.2 (EPC54条(3))には、ケイ素で形成されたチャネルを有する(非EMR)磁気抵抗デバイスが記載されている。複数のリードの組が、チャネルの片側面に沿ってチャネルに接続している。シャントは、オプションとして、チャネルの下に設けられていてもよい。このデバイスは、チャネルに反転層を形成するための上面ゲート構造も含んでいる。

## 【0019】

平面状EMRデバイス及び、類似の種類の平面状EMRデバイスは、例えば、電流経路を屈曲するためにローレンツ力を用いており、及び/又はホール効果を用いているが、HDDの磁気ヘッドスライダを製造する際に用いられる既存の製造プロセス、特に、空気ペアリング面を形成する際に用いられるラッピング処理とは、一般的には両立が難しいものとなっている。10

## 【課題を解決するための手段】

## 【0020】

本発明は、この問題を解決しようとするものである。

## 【0021】

本発明の第一の様態によれば、基板と、第一方向に伸びた細長半導体チャネルと、チャネルへの接点の組を提供する少なくとも2つの導電性リードとを含む磁気抵抗デバイスが設けられ、チャネルと接点の組は、第一方向と基板面とに垂直な第二方向で基板に対して積重ねられ(stacked)、該デバイスは、チャネルに沿って側面を有し、側面に対し一般的に垂直な方向の磁場に対して反応(responsive)する。20

## 【0022】

従って、デバイスは、既存の平面型MRデバイスと対比して、既存のスライダ形成技術を適用できる垂直型MRデバイス又は積層MRデバイスを提供することができる。特に、側面は、空気ペアリング面(air bearing surface)の一部を形成することができる。

## 【0023】

さらに、デバイスは、チャネルと接触した半導体シャント(semiconductor shunt)を含んでいる。

## 【0024】

チャネルは、不純物添加がなされていない(即ち、ドープされていない)か、あるいは、シャントほどには不純物添加がなされていない(即ち、シャントより軽くドープされている)ものであってよく、リード及び/又はシャントに対して反対の導電型を有していてもよい。例えば、チャネルはP<sup>-</sup>型であってもよい。シャントは、単結晶であってもよい。シャントは、ケイ素(silicon:シリコン)を含んでいてもよい。シャントは、n<sup>+</sup>型であってもよい。30

## 【0025】

不純物添加のないケイ素を元にした材料をチャネルに用い、多量に不純物添加されたケイ素を元にした材料をシャントとリードに用いることにより、十分に高い抵抗値と、十分に大きな出力信号と、十分に低いジョンソン雑音とを有する磁気抵抗デバイスを実現することができる。40

## 【0026】

デバイスは、オプションのシャントに接触した導電性層を含んでいてもよく、このオプションのシャントは、チャネルと導電性層との間に置かれている。導電性層は、ケイ素を含んでいてもよい。導電性層は、基板の最上位層を含んでいてもよい。導電性層は、ケイ化金属(metal silicide)を含んでいてもよい。

## 【0027】

チャネルは、第二半導体層と、第三半導体層の一部とを含むものであってよく、この第二半導体層は、オプションのシャントと、第三半導体層との間に置かれる。第二半導体層及び第三半導体層は、単結晶であってよい。第三半導体層の他の部分は、非結晶性であってよい。第二半導体層は、ケイ素またはケイ素ゲルマニウム(silicon-germanium)を含50

んでいてもよい。

【0028】

デバイスは、さらに、誘電体層を含んでいてもよく、この誘電体層はトレンチ（溝）を有しており、トレンチ（溝）内には、オプションのシャントと、チャネルの少なくとも一部とが形成されている。

【0029】

少なくとも2つのリードは、半導体材料を含み、 $n^+$ 型であってもよい。少なくとも2つのリードは、ケイ素及び／又はケイ化金属を含むものであってよい。

【0030】

デバイスは、追加のリードを含むものであってよく、このリードは、チャネルへのさらに別の接点を提供し、チャネルは、さらに別の接点と、複数の接点の組との間に置かれている。

10

【0031】

デバイスは、さらに、第一及び第二磁場遮蔽層（magnetic field shielding layers）を含むものであってよく、オプションのシャント、チャネル及び複数の接点の組は、第一磁場遮蔽層と第二磁場遮蔽層との間に置かれている。

【0032】

基板は、オプションとして、AlTiC基板の形態の、磁気ヘッドスライダ基板を含んでよい。

20

【0033】

本発明の第二の様態によれば、磁気ディスクドライブのための磁気ヘッドスライダが提供され、スライダはデバイスを含んでいる。

【0034】

本発明の第三の様態によれば、ハウジングを含む磁気ディスクドライブが提供され、ハウジング内には磁気媒体が搭載され、磁気ヘッドスライダは、磁気媒体と隣接して動作するために、ハウジング内に設けられている。

30

【0035】

本発明の第四の様態によれば、磁気抵抗デバイスを製造する方法が提供され、この方法は、表面を有する基板を提供するステップと、細長半導体チャネルを形成するステップであって、チャネルが第一方向に伸びていることを特徴とするステップと、チャネルに対して複数の接点の組を提供する少なくとも2つのリードを、第一方向と基板の表面とに対して垂直な第二方向に、チャネルと複数の接点の組とを積重ねるように形成するように形成するステップとを含み、さらに、チャネルに沿った面を形成するステップを含み、本デバイスは、面に対して一般的に垂直な磁場に反応する。

【0036】

本方法は、さらに、基板の表面上に半導体シャントを形成するステップを含んでいてよい。

【0037】

本方法は、さらに、基板の表面上に誘電体層を形成するステップを含んでいてもよく、この誘電体層は、基板の表面を露出させて、基板上にシャント又はチャネルを選択的に形成するトレンチ（溝）を有している。

40

【0038】

本基板は、最上位の半導体層を含んでもよく、本方法は、さらに、最上位の半導体層に第一半導体層を選択的に形成するステップを含んでいてもよい。第一半導体層を選択的に形成するステップは、最上位の半導体層に第一半導体層をエピタキシャル成長させるステップを含んでいてよい。

【0039】

本方法は、さらに、第一半導体層又は基板上に第二半導体層を選択的に形成するステップを含んでいてよい。第二半導体層を選択的に形成するステップは、第二半導体層チャネルをエピタキシャル成長させるステップを含んでいてよい。

50

**【0040】**

本方法は、第二又は第三半導体層と誘電体層との上に第三半導体層を形成するステップを含んでいてもよく、第三半導体層の一部は、第二又は第三半導体層の上に形成される。第二半導体層と、第三半導体層の一部とは、単結晶であってもよい。第三半導体層の他の部分は、非結晶性であってもよい。

**【0041】**

本方法は、さらに、第三半導体層上に、第二誘電体層を形成するステップであって、第二誘電体層が、第三半導体層の表面を露出させる複数のトレンチ（溝）の組を有することを特徴とするステップと、第三半導体層上にリードを選択的に形成するステップとを含んでいてもよい。

10

**【0042】**

リードを形成するステップは、第四半導体層をデポジットするステップを含んでいてもよい。リードを形成するステップは、第四半導体層をケイ化する (siliciding) ステップを含んでいてもよい。

**【0043】**

本方法は、基板の少なくとも一部を犠牲にするステップを含んでいてもよい。本デバイスは、基板上に形成された積層構造を含んでいてもよく、本方法は、さらに、他の基板を積層構造に接合するステップを含んでいてもよい。

**【0044】**

面 (face) を形成するステップは、デバイスの縁をラッピング (lapping) するステップを含んでいてもよい。

20

**【0045】**

本発明の第五の様態によれば、磁気抵抗デバイスを製造し、磁気ヘッドスライダを製造する方法が提供される。

**【0046】**

本発明のいくつかの実施例を、添付の図面を例示として引用し、以下説明する。

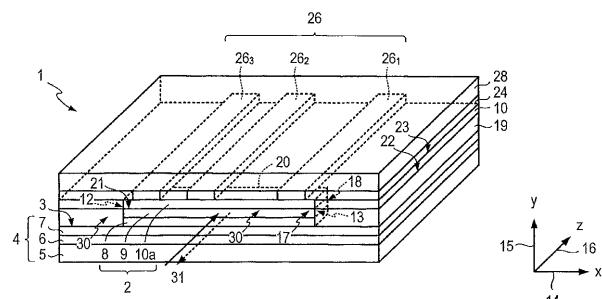

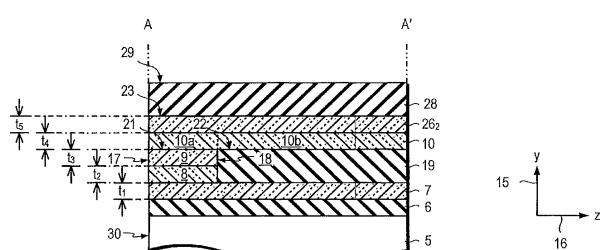

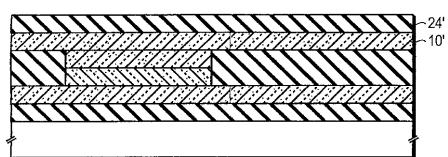

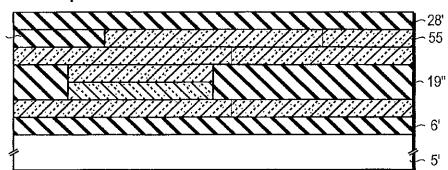

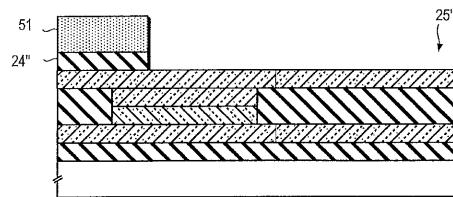

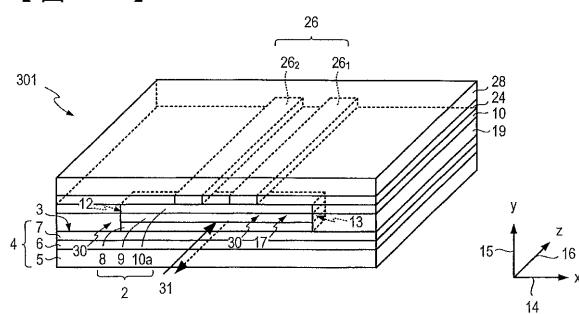

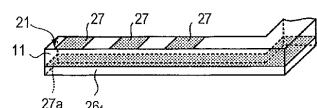

**【図面の簡単な説明】****【0047】****【図1】第一磁気抵抗デバイスの概略透視図**

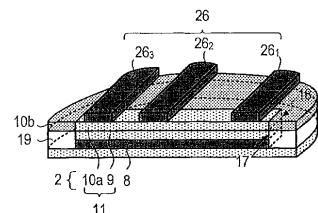

【図1a】図1に示した第一磁気抵抗デバイスのシャント、チャネル層及びリードの、より詳細な概略透視図。

30

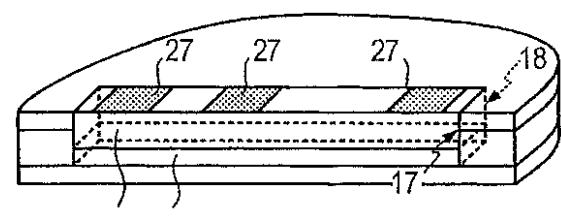

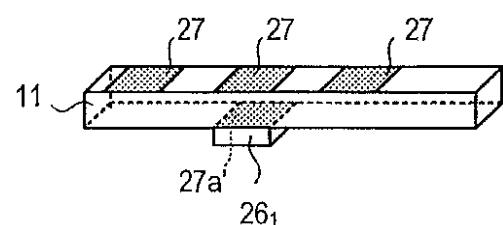

【図1b】図1に示した第一磁気抵抗デバイスのシャント、チャネル及び接触領域の、より詳細な概略透視図。

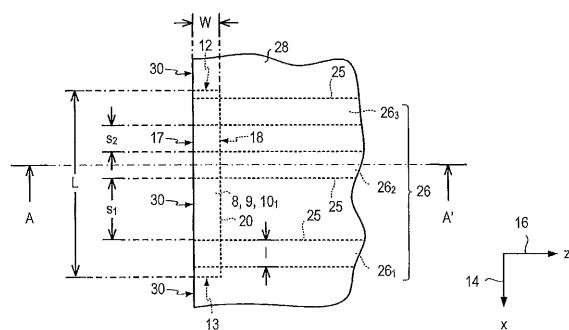

**【図2】図1に示した第一磁気抵抗デバイスの平面図。**

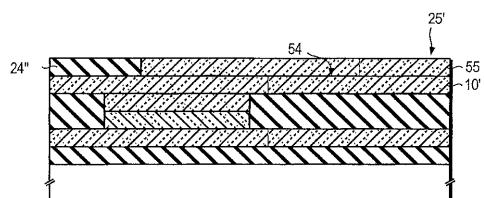

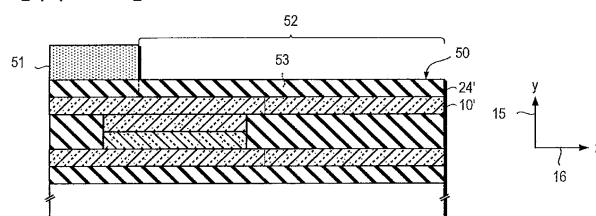

【図3】図2に示した第一磁気抵抗デバイスの、線 A - A' での断面図。

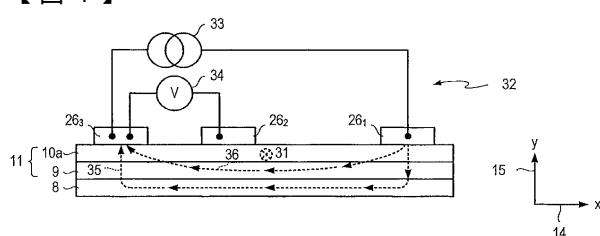

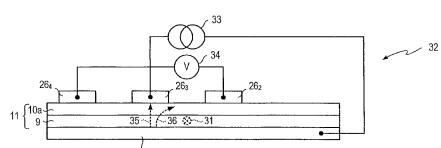

【図4】図1に示した第一磁気抵抗デバイスを動作させるための回路構成の概略図。

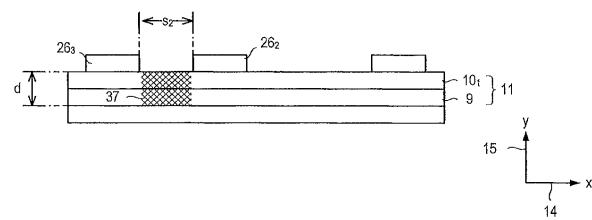

【図5】図1に示した第一磁気抵抗デバイスの検知領域 (sensitive region) を示す図。

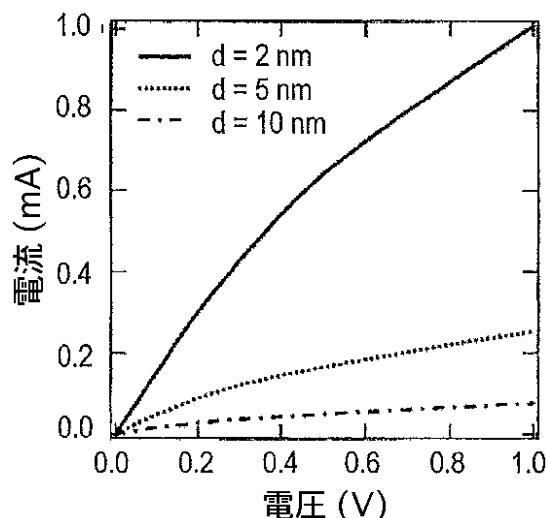

【図6】図1に示した第一磁気抵抗デバイスの電流電圧特性について、異なる3つの層厚みについてシミュレーションした結果を示す図。

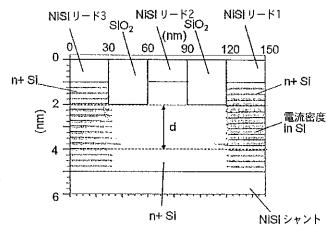

【図7】図1に示した第一磁気抵抗デバイスの電流密度特性についてシミュレーションした結果を示す図。

40

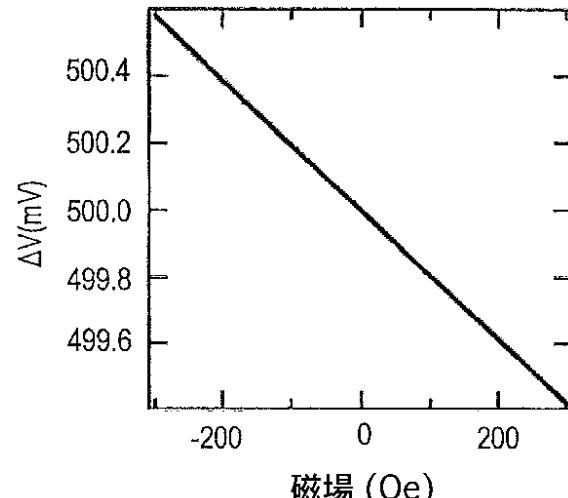

【図8】図1に示した第一磁気抵抗デバイスの磁気抵抗特性についてシミュレーションした結果を示す図。

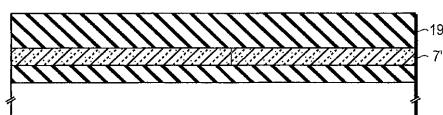

【図9a】第一磁気抵抗デバイスの多段階による製造を示す図。

【図9b】第一磁気抵抗デバイスの多段階による製造を示す図。

【図9c】第一磁気抵抗デバイスの多段階による製造を示す図。

【図9d】第一磁気抵抗デバイスの多段階による製造を示す図。

【図9e】第一磁気抵抗デバイスの多段階による製造を示す図。

【図9f】第一磁気抵抗デバイスの多段階による製造を示す図。

【図9g】第一磁気抵抗デバイスの多段階による製造を示す図。

50

- 【図 9 h】第一磁気抵抗デバイスの多段階による製造を示す図。

【図 9 i】第一磁気抵抗デバイスの多段階による製造を示す図。

【図 9 j】第一磁気抵抗デバイスの多段階による製造を示す図。

【図 9 k】第一磁気抵抗デバイスの多段階による製造を示す図。

【図 9 l】第一磁気抵抗デバイスの多段階による製造を示す図。

【図 9 m】第一磁気抵抗デバイスの多段階による製造を示す図。

【図 9 n】第一磁気抵抗デバイスの多段階による製造を示す図。

【図 9 o】第一磁気抵抗デバイスの多段階による製造を示す図。

【図 9 p】第一磁気抵抗デバイスの多段階による製造を示す図。

【図 9 q】第一磁気抵抗デバイスの多段階による製造を示す図。

【図 9 r】第一磁気抵抗デバイスの多段階による製造を示す図。

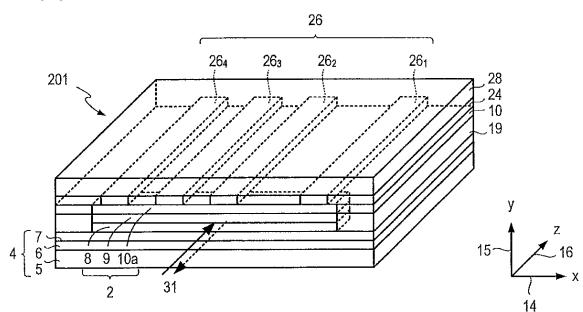

【図 10】第二磁気抵抗デバイスの概略透視図。 10

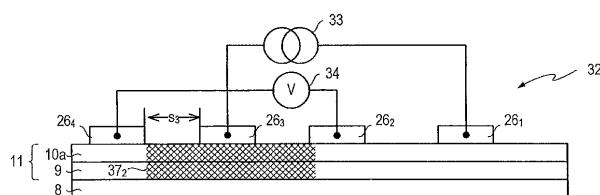

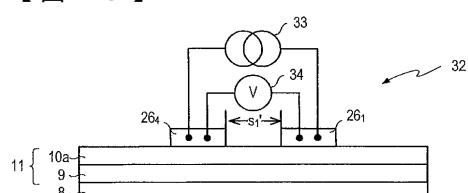

【図 11】図 10 に示した第二磁気抵抗デバイスを動作させるための回路構成の概略図。

【図 12】第三磁気抵抗デバイスの概略透視図。

【図 13】図 12 に示した第三磁気抵抗デバイスを動作させるための回路構成の概略図。

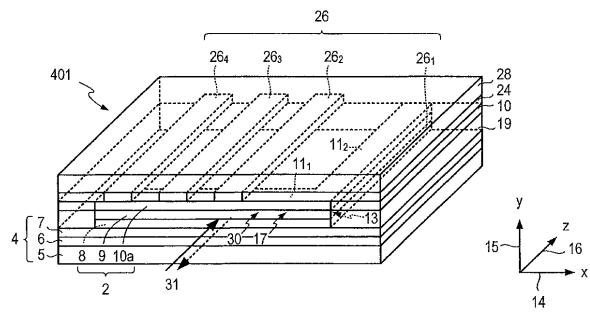

【図 14】第四磁気抵抗デバイスの概略透視図。

【図 14 a】図 14 に示した第四磁気抵抗デバイスのチャネル及び接触領域の、より詳細な概略透視図。

【図 14 b】代替となる磁気抵抗デバイスのチャネル及び接触領域の、より詳細な概略透視図。 20

【図 15】図 14 に示した第四磁気抵抗デバイスを動作させるための回路構成の概略図。

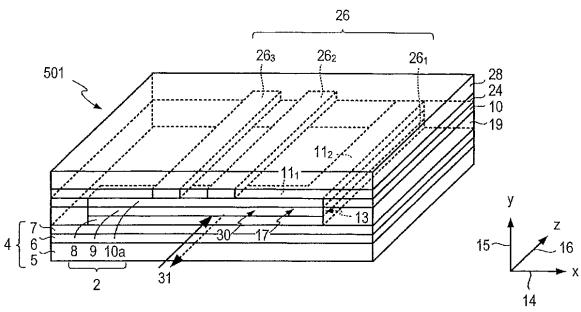

【図 16】第五磁気抵抗デバイスの概略透視図。

【図 17】図 16 に示した第五磁気抵抗デバイスを動作させるための回路構成の概略図。

【図 18】第六磁気抵抗デバイスの概略透視図。

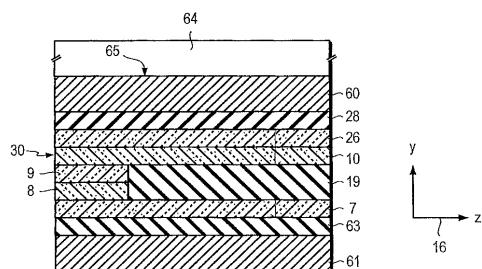

【図 19】図 18 に示した第六磁気抵抗デバイスの断面図。

【図 20 a】図 18 に示した第六磁気抵抗デバイスの複数段階の製造を示す図。

【図 20 b】図 18 に示した第六磁気抵抗デバイスの複数段階の製造を示す図。

【図 20 c】図 18 に示した第六磁気抵抗デバイスの複数段階の製造を示す図。

【図 20 d】図 18 に示した第六磁気抵抗デバイスの複数段階の製造を示す図。

【図 20 e】図 18 に示した第六磁気抵抗デバイスの複数段階の製造を示す図。

【図 20 f】図 18 に示した第六磁気抵抗デバイスの複数段階の製造を示す図。 30

【図 21】第七磁気抵抗デバイスの概略透視図。

【図 22】第八磁気抵抗デバイスの概略透視図。

【図 23】第九磁気抵抗デバイスの概略透視図。

【図 24】第十磁気抵抗デバイスの概略透視図。

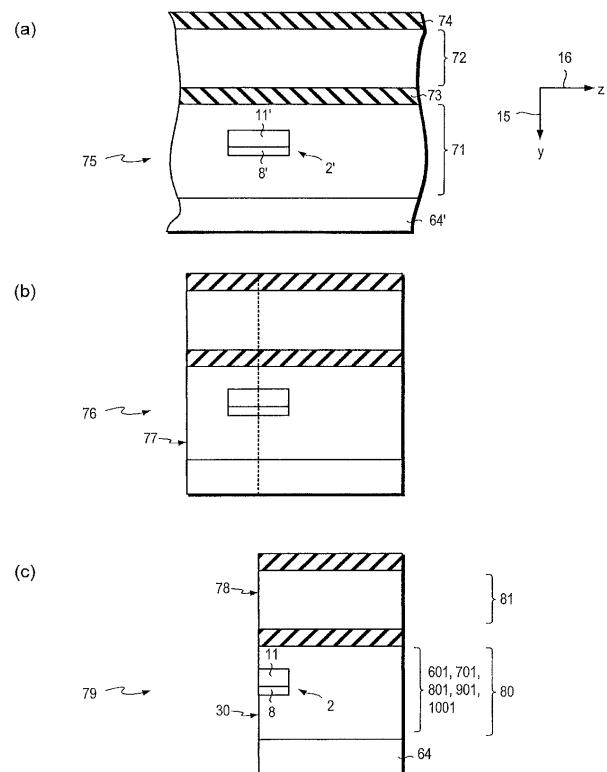

【図 25】図 25 a 乃至図 25 c は、ハードディスクドライブ内のスライダの、磁気抵抗デバイスを含むヘッド素子部の製造を示す図。

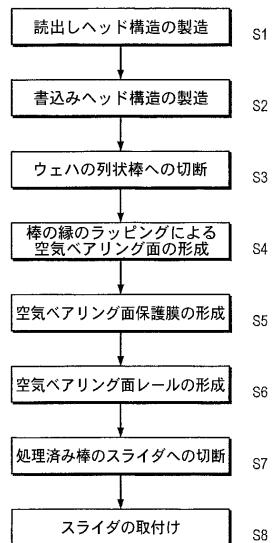

【図 26】スライダの製造方法の処理フローチャート。

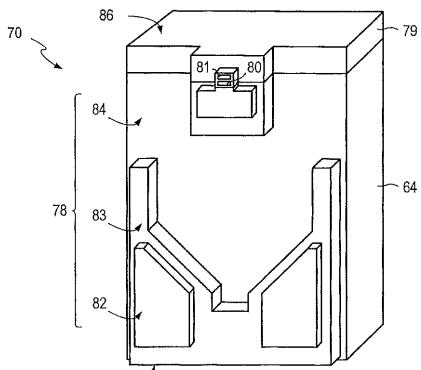

【図 27】スライダの概略透視図。

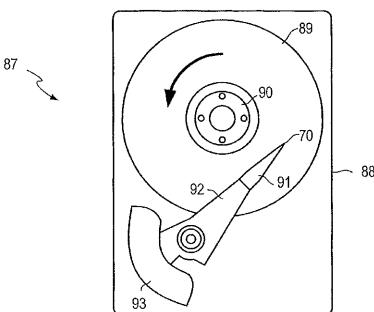

【図 28】磁気ディスクドライブの概略平面図。 40

【発明を実施するための形態】

【0048】

第一磁気抵抗デバイス 1

デバイス構造

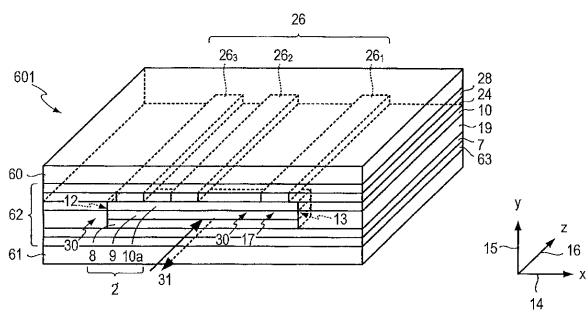

図 1、図 1 a、図 1 b、図 2 及び図 3 に、第一磁気抵抗デバイス 1 を示す。

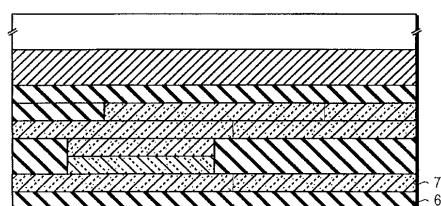

- 【0049】

デバイス 1 は、略平面基板 4 の表面 3 上に配置された層構造 2 を含んでいる。基板 4 は、半導体基部 5（以下、“ハンドル層”（handle layer）と称する）と、埋込絶縁層（buried insulator layer）6 と、厚さ  $t_1$  を有する半導体最上位層 7 とを含む、半導体オンインシュレータ型（semiconductor-on-insulator）基板の形状となっている。以下で詳説 50

するように、半導体表面層 7 は、後続の層 8、9、10a のエピタキシャル成長のためのシード層として用いられる。半導体基部 5 及び埋込絶縁層 6 は、犠牲層となりうる。他の基板 64 (図 19) は、デバイスの残りの反対側上の面 65 (図 19) 上に接合される。

#### 【0050】

本例においては、シリコンオンインシュレータ型 (silicon-on-insulator) 基板 4 を用いる。従って、半導体基部 5 はケイ素 (Si) を含み、埋込絶縁層 6 は二酸化ケイ素 ( $\text{SiO}_2$ ) を含み、シード層 7 は単結晶ケイ素 (Si) を含んでいる。本例においては、シード層 7 は、概ね 1 nm の厚み  $t_1$  を有する。

#### 【0051】

層構造 2 は、シード層 7 上に成長させた厚さ  $t_2$  を有する半導体材料の第一層 8 と、第一半導体層 8 上に成長させた厚さ  $t_3$  を有する半導体材料の第二層 9 と、第二半導体層 9 上に成長させた厚さ  $t_4$  を有する半導体材料の第三層 10 の一部 10a とを含んでいる。

第一及び第二半導体層 8、9 と、第三半導体層 10 の一部 10a とは、エピタキシャル層であり、単結晶である。以下で詳説するように、第三半導体層 10 は、非晶性の別の部分 10b を含んでいる。

#### 【0052】

第一半導体層 8 は、 $n^+$  型 (すなわち、n 型であり、 $10^{20} \text{ cm}^{-3}$  又は  $10^{21} \text{ cm}^{-3}$  のオーダまで不純物添加したもの) である。第二及び第三半導体層 9、10 は、不純物添加がないもの (すなわち、真性 (intrinsic)) であるか、 $p^-$  型 (すなわち、p 型であり、 $10^{15} \text{ cm}^{-3}$  と  $10^{18} \text{ cm}^{-3}$  の間のオーダの濃度で不純物添加したもの) とすることができます。いくつかの実施様態においては、第二及び第三半導体層 9、10 は、 $n^-$  型 (すなわち、n 型であり、 $10^{15} \text{ cm}^{-3}$  と  $10^{18} \text{ cm}^{-3}$  の間のオーダの濃度で不純物添加したもの) とすることができます。

#### 【0053】

第二半導体層 9 と、第三半導体層 10 の一部 10a とは、アクティブ・センサ・チャネル 11 を形成している。従って、第二半導体層 9 と、第三半導体層 10 の一部 10a とは、ここでは、各々、第一及び第二チャネル層 9、10 と称する。より高い濃度で不純物添加した第一半導体層 8 は、チャネル 11 からの電流をシャント (Shunt) させることができ、低抵抗の導電性領域を提供する。従って、ここでは、第一半導体層 8 を“シャント層”又は単に“シャント”と称する。例えば、シャント 8 には、濃度  $10^{20} \text{ cm}^{-3}$  又は  $10^{21} \text{ cm}^{-3}$  のオーダまでヒ素を不純物添加してもよい。いくつかの実施様態においては、第一半導体層 8 (すなわち、シャント) を省いてもよい。

#### 【0054】

本例においては、シャント層及びチャネル層 8、9、10a は、全て、ケイ素 (Si : シリコン) で形成されている。しかし、シャント層 8 及び / 又はチャネル層 9、10a は、例えば、10% のゲルマニウム成分 (すなわち、 $x = 0.1$ ) を有する、ケイ素ゲルマニウム (silicon-germanium) ( $\text{Si}_{1-x}\text{Ge}_x$ ) で形成することができる。

#### 【0055】

シャント 8 は、概ね 1 nm の厚み  $t_2$  を有し、第一チャネル層 9 は、概ね 1 nm の厚み  $t_3$  を有している。

#### 【0056】

シャント層及びチャネル層 8、9、10a は、各々、概ね 1 nm と 10 nm の間の厚みを有するものであってよい。しかし、層 8、9、10a は、デバイスの抵抗値を抑えるように、できるだけ薄く形成することが好ましい。

#### 【0057】

チャネル 11 は、第一長手方向 14 (ここでは、x 軸と記す) の第一及び第二端点 12、13 の間の、一般的に長さ L を有する細長の部分である。本例においては、長さ L は、概ね 150 nm である。第一、第二及び第三方向 14、15、16 は互いに直交している。第二方向 15 は、層が積重なっている方向 (ここでは、y 軸と記す) である。第二方向 15 は、基板 4 の表面 3 に対して法線方向である。ここでは、第二方向 15 は、“垂直方

10

20

30

40

50

向”又は“積層方向”とも称される。チャネル11は、第一及び第二縁(又は“側面”)17、18間の、第三方向16(ここでは、z軸と記す)の幅Wを有する。本例においては、幅Wは、概ね10nmである。シャント及びチャネル層8、9、10aは、一般的に(平面図において)ともに広い範囲に及んでおり、そのため、シャント8は、チャネル11と実質的に同一の側面(すなわち、x方向及びz方向)の寸法を有する。

#### 【0058】

また、基板4は、第一方向14に向けられた細長の凹んだ段部(elongate recessed step)20(又は、開放端を有する“スロット”あるいは“トレンチ(溝)”(open-sided “slot” or “trench”))を含む、誘電体材料をデポジットした第一パタン層19(ここでは、単に、“第一誘電体層”と称する)を支持している。シャント8及び第一チャネル層9は、トレンチ(溝)20に形成されている。シャント8と第一チャネル層9とを合わせた厚さは、第一誘電体層19の厚さと同一である。従って、第一チャネル層9の表面21と、第一誘電体層19の表面22は、同一の高さとなる。本例においては、誘電体材料は、二酸化ケイ素( $\text{SiO}_2$ )を含んでいる。

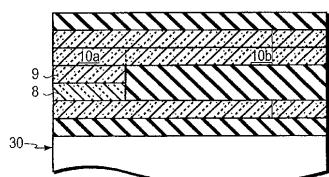

#### 【0059】

第三半導体層10は、第一チャネル層9及び第一誘電体層19の表面21、22の上に形成され、上面23を有している。第三半導体層10は、ケイ素を含んでいるが、ケイ素ゲルマニウムを用いることもできる。本例においては、第三半導体層10は、概ね1nmの厚さ $t_4$ を有している。

#### 【0060】

前述したように、第三半導体層10は、下地材料(underlying material)に依存して、結晶性と非結晶性の領域10a、10bを含んでいる。従って、第一チャネル層9を覆う第三半導体層10の部分10aは単結晶であるが、第一誘電体層19上の他の部分10bは、非結晶性である。

#### 【0061】

第三半導体層10は、細長チャネル11に対して垂直に置かれた、すなわち第三方向16に向けられた3つの細長トレンチ(溝)25を含む誘電体材料がデポジットした第二パタン層24(以下では、単に“第二誘電体層”と称する)を支持する。第二パタン層24は、二酸化ケイ素( $\text{SiO}_2$ )を含んでいる。本例においては、第二誘電体層24は、概ね1nmの厚さを有している。

#### 【0062】

また、図1a(明確に説明するために、第二誘電体層24は不図示)において、第三半導体層10は、複数の導電性リード26の組、すなわち、第一、第二及び第三導電性リード $26_1$ 、 $26_2$ 、 $26_3$ を支持している。リード26は第二誘電体層24の各トレンチ(溝)25内に形成されている。リード26は、チャネル11に沿って(x軸14に沿って)離れた間隔で、チャネルに対し垂直な向きで(z軸16の方向に)置かれている。第一及び第二リード $26_1$ 、 $26_2$ は、概ね30nmの長さ $s_1$ の間隔で離れている。第二及び第三リード $26_2$ 、 $26_3$ は、概ね30nmの長さ $s_2$ の間隔で離れている。しかし、図1に示すように、第一及び第二リード $26_1$ 、 $26_2$ は、第二及び第三リード $26_2$ 、 $26_3$ の間隔よりも広い間隔で離れている、すなわち、 $s_1 > s_2$ である。リード26は、概ね30nmの長さ1(すなわち、第一方向14に沿う長さ)を有している。

#### 【0063】

各リード26は、より高い濃度で不純物添加した半導体の層を含んでいる。本例においては、この半導体はケイ素(silicon)である。リード26は、シャント8と同一の導電型を有することが好ましい。本例においては、リード26は、n型である。例えば、リード26には、概ね $1 \times 10^{20} \text{ cm}^{-3}$ の濃度までヒ素(As)を不純物添加してもよい。本例においては、リード26は、概ね20nmの厚さ $t_5$ を有するが、概ね1nm程まで薄くすることもできる。

#### 【0064】

リード26は、導電性を向上させるように、金属・半導体合金を含んでいてもよい。例

10

20

30

40

50

えば、ケイ素の場合、ニッケル、チタンあるいはタングステンの薄膜をデポジットし、概ね 500 nm でアニーリングし、不反応金属を湿式エッチングにより除去して (wet-etching unreacted metal)、リード 26 をケイ化 (silicide) してもよい。

#### 【0065】

また、図 1 bにおいて、リード 26 は、チャネル 11 の第一縁 17 から始まり、チャネル 11 を越えて、さらに、第三方向 16 に向かってチャネル 11 の第二縁 18 を越えている。リード 26 は、チャネル 11 の第一及び第二縁 17、18 の間に、チャネル 11 へのインターフェース又は接点 27 を提供する。

#### 【0066】

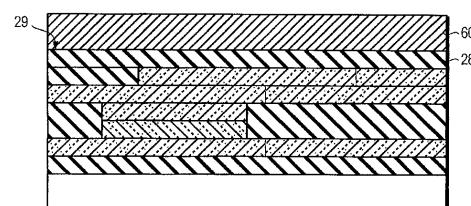

また、図 1、図 2 及び図 3において、第二誘電体層 24 及びリード 26 は、露出した表面 29 を有しデポジットした誘電体材料の第三層 28 (“第三誘電体層 28”) により覆われている。第三誘電体層 28 は、二酸化ケイ素 (SiO<sub>2</sub>) を含んでいる。

10

#### 【0067】

以下で詳説するように、さらに他の誘電体層、磁気遮蔽層及び / 又は新規の基板 (substrate) を含む、さらに他の層を、誘電体層 28 の表面 29 に (または誘電体層 28 上の他の表面の層上に) デポジット又は接合 (bond) させることもできる。

#### 【0068】

デバイス 1 は、実質的に平坦であり、第一及び第二方向 14、15 に平行、すなわち、チャネル 8 と、層が積重ねられる方向とに平行な平面上に置かれた面 30 を有している。従って、チャネル 11 の第一縁 17 は、面 30 に沿って伸びている。ここで、この面は、“側面”と称する。側面 30 は、誘電体材料の保護層 (protective layer) (不図示) により覆われていてもよい。この保護層は、自然に形成された二酸化ケイ素 (SiO<sub>2</sub>) の層を含むことができる。

20

#### 【0069】

動作に際しては、デバイス 1 は、異常磁気抵抗効果 (extraordinary magnetoresistance) (EMR) を及ぼし、側面 30 に対して垂直、あるいは概ね垂直に (すなわち、垂直から数度角度を以て (a few degree off perpendicular))、すなわち、z 軸 16 に対して平行 (又は、逆平行)、あるいは概ね平行 (又は、概ね逆平行) に通る磁場 31 を検出する磁場センサとして用いることができる。図 14において、磁場 31 は、ページ紙面に入り込んで通るように示してある。しかし、磁場は、図面ページから出て行くように通ることもできる。

30

#### 【0070】

以下で詳説するように、デバイス 1 は、磁気ディスクドライブ 87 (図 28) の読み出しヘッド 80 (図 27) として用いることができる。シャント 8 (が、もし存在している場合)、チャネル 11 及びリード 26 の構成により、デバイス 1 は、ラッピング (lapping) などの現在のスライダ製造技術を用いて、磁気ヘッドスライダ 70 (図 27) に統合することができる。ラッピングは、表面を定義するために用いられ、この表面は、空気ベアリング面 (ABS) と称され、磁気媒体 89 (図 28) に対向している。従って、デバイス 1 は、スライダに組み込むことができ、これにより、デバイス 1 の側面 30 をラッピングにより形成され、空気ベアリング面の一部分を形成する。デバイス 1 は、側面 30 を垂直に通る磁場 31 に対して反応するため、デバイス 1 は、磁気媒体 89 (図 28) から発生する磁場を検出するために、その向きは正確に設定されている。

40

#### デバイス動作

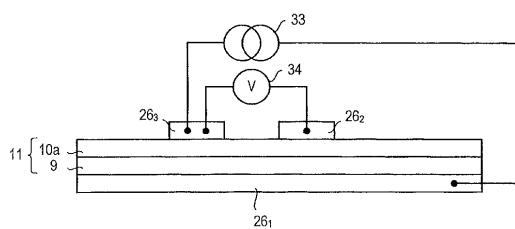

#### 【0071】

特に、磁気抵抗デバイス 1 を動作させる回路 32 を示す図 4 を参照する。回路 32 は、シャント 8 と第一及び第三リード 26<sub>1</sub>、26<sub>3</sub> 間のチャネル 11 とを流れる電流 I を駆動するように構成した電流源 33 と、第二及び第三リード 26<sub>2</sub>、26<sub>3</sub> 間に発生した電圧 V を測定するように構成した電圧計 34 を含んでいる。代替的な構成として、電流源 33 は、第一及び第二リード 26<sub>1</sub>、26<sub>2</sub> 間の電流を駆動するように構成することもできる。

50

## 【0072】

印可される磁場 $3_1$ がない場合には、第一及び第三リード $2_6_1$ 、 $2_6_3$ 間を流れる電流は、チャネル $1_1$ に流れ込み、シャント $8$ により経路 $3_5$ を迂回する。磁場 $3_1$ が、 $z$ 軸 $1_6$ (図1)に沿って印可された場合には、電流は、シャント $8$ から逸れて(deflected)、経路 $3_6$ に沿ってチャネル $1_1$ を流れる。印可された磁場 $3_1$ による電気抵抗の変化は、電圧リード $2_6_2$ 、 $2_6_3$ 間で検出される。

## 【0073】

図5において、印可された磁場 $3_1$ を検出可能な領域 $3_7$ は、不純物添加されていない、あるいは少量の不純物添加がなされた、第二及び第三リード $2_6_2$ 、 $2_6_3$ 間のチャネル $1_1$ に設けられる。従って、概ね $30\text{ nm}$ のリード間隔 $s_2$ と、2つの層を合わせた厚さ $d = t_3 + t_4$ を用いて、 $10\text{ Tb/in}^2$ 程度の記憶密度に対応した容量を有する磁気媒体 $8_9$ (図28)中のビットを検出することができる。10

## 【0074】

図6は、3つの異なるチャネル厚さ $d$ 、すなわち、 $d = 2\text{ nm}$ 、 $d = 5\text{ nm}$ 及び $d = 10\text{ nm}$ を有するデバイスに関する、電流電圧特性曲線のATLASシミュレーションを示すものである。本モデルにおいては、リード幅 $l_1$ 、 $l_2$ 及び $l_3$ は、いずれも同一、すなわち $l_1 = l_2 = l_3 = 30\text{ nm}$ であり、リード間隔 $s_1$ 及び $s_2$ も、いずれも同一、すなわち、 $s_1 = s_2 = 30\text{ nm}$ である。シャント $8$ の幅 $W$ は、 $10\text{ nm}$ である。

## 【0075】

図7は、上記と同一のデバイスに関し、 $d = 2\text{ nm}$ の場合の電流密度のATLASシミュレーションを示すものである。図7に示すように、電流は、主に、リード $2_6$ とシャント $8$ との間を流れる。第一及び第二リード $2_6_1$ 、 $2_6_2$ 間の抵抗は、概ね $1\text{ k}\Omega$ である。20

## 【0076】

図8は、印可された磁場の関数として、出力信号のATLASシミュレーションを示すものである。ここで、第一リード $2_6_1$ には、 $0\text{ V}$ のバイアスを印可し、第三リード $2_6_3$ には、 $1\text{ V}$ のバイアスを印可して、 $z$ 軸 $1_6$ (図1)に沿って印可された磁場の範囲で、第二及び第三リード $2_6_2$ 、 $2_6_3$ 間の電圧差を測定した。シミュレーション結果と、より大きなデバイス(不図示)に関する測定を線形外挿した結果によると、デバイスからの出力信号は、 $2\mu\text{V/Oe}$ 程度になることが分かる。30

デバイスの製造

## 【0077】

図9a乃至図9rを引用し、デバイス1を製造する方法を説明する。

## 【0078】

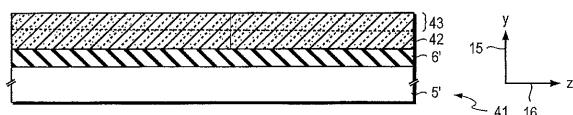

図9aにおいて、プロセスは、半導体オンインシュレータ型ウェハ41から始まる。ウェハ41は、半導体ハンドル層 $5'$ と、埋込絶縁層 $6'$ と、単結晶半導体の最上位層 $4_2$ とを有する。最上位半導体層 $4_2$ は、通常、数 $10\text{ nm}$ の厚さを有する。このような厚さの層 $4_2$ にする必要はないため、層 $4_2$ は、より薄くすることができる。

## 【0079】

本例においては、シリコン・オン・インシュレータ型ウェハ41を用いる。最上位ケイ素層 $4_2$ は、通常、概ね $20\text{ nm}$ と $100\text{ nm}$ の間の範囲の厚さを有する。最上位ケイ素層 $4_2$ の厚みを薄くするため、熱酸化(thermal oxidation)し、その後に湿式エッティングする処理を用いることができる。ウェハ41を熱的に酸化させ、最上位ケイ素層(top silicon layer) $4_2$ の表面領域 $4_3$ を、二酸化ケイ素(silicon dioxide)に変換する。図9bに示すように、この処理により、二酸化ケイ素層 $4_4$ を、単結晶ケイ素の薄膜 $7'$ 上に残すことができ、以下、この薄膜層はシード層 $7'$ と称する。二酸化ケイ素層 $4_4$ は、混合比 $2:5:3$ の $\text{NH}_2\text{F:C}_2\text{H}_4\text{O}_2:\text{H}_2\text{O}$ (又は、“SILOXエッティング液”として知られている)混合液を用いて除去することができる。40

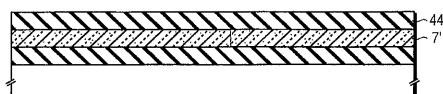

## 【0080】

図9cに示すように、層デポジションの準備が整ったウェハ3'は、埋込絶縁層 $6'$ 、上

50

にあるシード層 7' を含んでいて、他方、埋込絶縁層 6' はハンドル層 5' 上に置かれる。

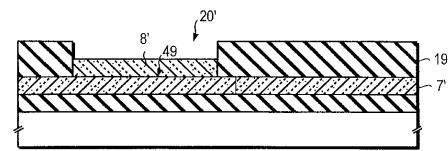

#### 【0081】

図 9 d に示すように、シード層 7' の上に誘電体材料の第一層 19' をデポジットする。本例においては、誘電体材料は二酸化ケイ素であり、化学蒸着 (CVD) を用いてデポジットする。

#### 【0082】

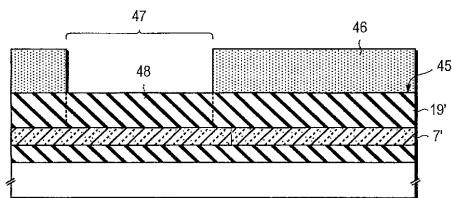

図 9 e に示すように、電子ビームレジストからなる層（不図示）を、第一誘電体層 19' の上面 45 に適用（例えばスピン塗布）し、焼成により硬化（cure）させる。電子ビームレジスト層（不図示）には、走査電子ビーム（不図示）を用いてパターン形成し、適切な現像液を用いて現像し、（x 方向 14 に沿った）細長ウインドウ 47 を含むようにパターン形成されたレジスト層 46 を残す。ウインドウ 47 は、意図したシャント及び第一チャネル層 8'、9' と、概ね同じ（x 方向 14 に沿った）長さとなるが、（z 方向に沿っては）より広い幅となる。

#### 【0083】

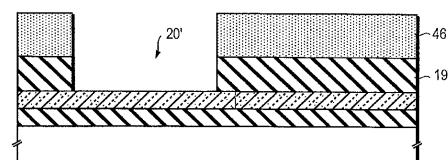

下のシード層 7' にまで伸びた第一誘電体層 19' の領域 48 を、湿式エッティングにより、例えば、SILOX エッティング液を用いて除去する。図 9 f に、結果として得られる構造を示すが、この構造は、パターン形成された第一誘電体層 19" 中に幅広のトレンチ（溝）20' を含むものとなっている。

#### 【0084】

パターン形成されたレジスト層 46 を除去する。図 9 g に、結果として得られる構造を示すが、この構造は、トレンチ（溝）20' の底に、シード層 7' が露出した領域 49 を含むものとなっている。

#### 【0085】

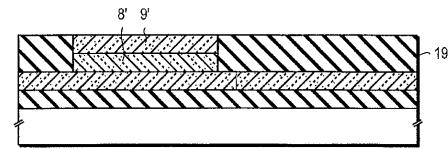

図 9 h に示すように、トレンチ（溝）20' のシード層 7' が露出した領域 49 上に、半導体材料の第一層 8' を選択的に成長させる。第一半導体層 8' は、高濃度で不純物添加され、第一導電型を有する。本例においては、第一半導体層 8' は n 型であり、成長の過程でその場で不純物添加がなされる。

#### 【0086】

第一半導体層 8' は、シード層 7' 上でエピタキシャル成長し、それにより単結晶層を形成する。第一半導体層 8' は、パターン形成された第一誘電体層 19" 上には成長しない。本例においては、半導体はケイ素であり、従って、概ね 700°C で CVD を用いて、選択的なエピタキシャル成長を行うことができる。

#### 【0087】

図 9 i に示すように、第一半導体層 8' 上に、半導体材料の第二層 9' を選択的に成長させる。第二半導体層 9' は、第二導電型を有するように、不純物添加しないか、あるいは、僅かに不純物添加する。本例においては、半導体層 8' は真性（intrinsic）である。

#### 【0088】

第二半導体層 9' は、第一半導体層 8' 上でエピタキシャル成長し、単結晶層を形成する。第二半導体層 9' は、パターン形成された第一誘電体層 19" 上では成長しない。本例においては、半導体はケイ素であるが、ケイ素ゲルマニウムを用いることもできる。ここでも、ケイ素を用いた場合、概ね 700°C で CVD を用いて、選択的な成長を行うことができる。

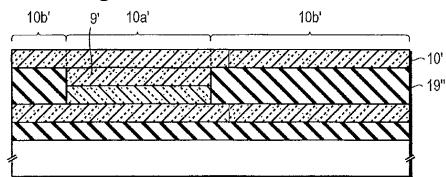

#### 【0089】

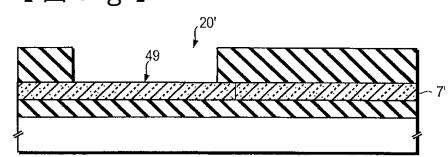

図 9 j に示すように、第二半導体層 9' 及びパターン形成された第一誘電体層 19" の上に、半導体材料の第三層 10' を成長させる。第三半導体層 10' は、第二導電型を有するように、不純物添加しないか、あるいは、僅かに不純物添加する。本例においては、第三半導体層 10' は、真性（intrinsic）である。

#### 【0090】

10

20

30

40

50

第三半導体層 10' は、第二半導体層 9' 上でエピタキシャル成長し、単結晶層 10a' を形成する。しかし、第三半導体層 10' が成長すると、パタン形成された第一誘電体層 19" 上には、非結晶性層 10b' を形成する。本例においては、半導体はケイ素であるが、ケイ素ゲルマニウムを用いることもできる。概ね 600 で CVD を用いて、非選択的な成長を行うことができる。

#### 【0091】

図 9k に示すように、第三半導体層 10' 上に、誘電体材料の第二層 24' を成長させる。本例においては、誘電体材料は二酸化ケイ素であるが、窒化ケイ素などの他の誘電体材料を用いることもできる。

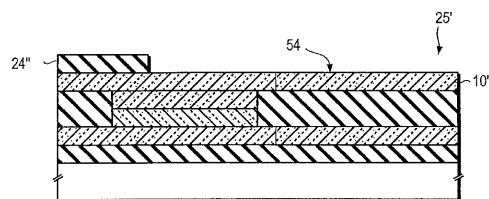

#### 【0092】

図 9l に示すように、電子ビームレジスト層（不図示）を、第二誘電体層 24' の上面 50 に塗布（スピンドル塗布）し、焼成により硬化させる。電子ビームレジスト層（不図示）は、走査電子ビーム（不図示）を用いてパタン形成し、適切な現像液を用いて現像し、（z 方向 16 に沿った）細長ウインドウ 47 を含むようにパタン形成されたレジスト層 51 を残す。

#### 【0093】

下の第三半導体層 10' にまで伸びた第二誘電体層 24' の領域 53 を、湿式エッティングにより、例えば、SILOX エッティング液を用いて除去する。図 9m に、結果として得られる構造を示すが、この構造は、パタン形成された第二誘電体層 24" 中にトレンチ（溝） 25' を含むものとなっている。

#### 【0094】

パタン形成されたレジスト層 51 を除去する。図 9n に、結果として得られる構造を示すが、この構造は、トレンチ（溝） 25' の底に、第三半導体層 10' の露出した領域 54 を含むものとなっている。

#### 【0095】

図 9o に示すように、トレンチ（溝） 25' の第三半導体層 10' が露出した領域 54 に、半導体材料の第四層 55 を選択的に成長させる。第四半導体層 55 は、高濃度で不純物添加され、第一導電型を有する。本例においては、第四半導体層 55 は n 型であり、成長の過程でその場で不純物添加がなされる。

#### 【0096】

第四半導体層 55 は、第三半導体層 10' 上でエピタキシャル成長し、従って、単結晶層を形成する。第四半導体層 55 は、パタン形成された第二誘電体層 24" 上には成長しない。本例においては、半導体はケイ素である。前述したように、概ね 700 で CVD を用いて、ケイ素に対して選択的なエピタキシャル成長を行うことができる。

#### 【0097】

第四半導体層 55 は、リード 26（図 1）を形成するように、残しておくこともできる。しかし、リードの抵抗が下がるように、リードをケイ化することもできる。この場合の処理には、第四半導体層 55 及び第二誘電体層 24" の上に、ニッケル（Ni）、チタン（Ti）又はタンクステン（W）などの適した金属をデポジットさせるステップと、ケイ化物（silicide）を形成するようにアニーリングするステップとが含まれる。ニッケルとケイ素の場合は、概ね 500 でアニーリングを行うことができる。湿式エッティングを用いて、（例えば、第二誘電体層 24" 上の）不反応金属を除去することができる。

#### 【0098】

図 9p に示すように、第四半導体層 55 と第二誘電体層 24" の上に、誘電体材料 29' の第三層をデポジットさせる。本例においては、誘電体材料は二酸化ケイ素（silicon dioxide）であるが、窒化ケイ素（silicon nitride）などの他の誘電体材料を用いることもできる。

#### 【0099】

後述するように、追加の処理段階、例えば、アルミニウムチタン（aluminum titanium carbide）で形成された、担体ウェハ（carrier wafer） 64'（図 20b）を、例えば、第

10

20

30

40

50

三誘電体層 29' の上、あるいは、第三誘電体層 29' 上に置かれた層 60' (図 20 b) の上に接合し、ハンドル層 5' 及び絶縁層 6' を除去し、シード層 7 にパタン形成し、それをケイ化し、さらに、シャント層と、第一誘電体層 19" の残りの部分の下に保護誘電体層を形成する処理を実行することもできる。

#### 【0100】

図 9 q に示すように、(幅広の) シャント層 8' とチャネル 11' を通る線 58 に沿って、隣接部分 57 からウェハの側部又は縁部 56 を除去するように、ウェハを切断する。この切断には、粗切断のためにウェハ・ノコギリ (wafer saw: ウェハソー) を用い、密切断のためにラッピングを行う。しかし、これ以外の切断方法、例えば、イオンビームミリングなどの方法を用いることもできる。図 9 r に、結果として得られる構造を示すが、デバイス 1 が、側面 30、シャント 8 及びチャネル層 9、10 a を含む構造となっている。

10

#### 【0101】

二酸化ケイ素又は他の材料からなる薄い(例えば、厚さ 2 nm 以下の)保護層をデポジットさせ、側面 30 を覆うように成長させる、あるいは成長を可能とすることができる。

#### 【0102】

後述するように、切断の処理は、側面 30 を形成するために、棒形成 (formation of bars) と、棒の縁部 (the edge of the bar) のラッピングとを含んでいる。

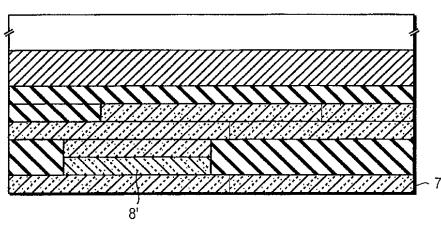

### 第二磁気抵抗デバイス 201

#### 【0103】

図 10 に、第二磁気抵抗デバイス 201 を示す。

20

#### 【0104】

第二磁気抵抗デバイス 201 は、前述の第一磁気抵抗デバイス 1 (図 1) と同様である。従って、同一の引用番号は、同一の特徴を指すために用いることとする。

#### 【0105】

第二デバイス 201 が第一デバイス 1 (図 1) と異なる点は、リードが 4 本になること、すなわち、第一、第二、第三及び第四リード 26<sub>1</sub>、26<sub>2</sub>、26<sub>3</sub>、26<sub>4</sub> となることである(さらに、この結果、チャネル 11 への接点が 4 本になる)。第三及び第四リード間の間隔 s<sub>2</sub> は、第二及び第三リード間の間隔 s<sub>2</sub> と同一とすることができる。チャネル及びシャント 8、11 は、これらの数のリード 26 を収容するために、さらに細長としてもよい。

30

#### 【0106】

図 11 に、磁気抵抗デバイス 201 を動作させる回路 32 を示す。

#### 【0107】

電流源 33 は、シャント 8 と、第一及び第三リード 26<sub>1</sub>、26<sub>3</sub> 間のチャネル 9 とを流れる電流 I を駆動するように構成されている。電圧計 34 は、第三及び第四リード 26<sub>3</sub>、26<sub>4</sub> 間に発生した電圧 V を測定するように構成されている。

#### 【0108】

第二デバイス 201 の出力は、第一デバイス 1 (図 1) の出力の 2 倍の大きさとすることができます。しかし、検知領域 37<sub>2</sub> (sensitive area) は、第二及び第四リード 26<sub>2</sub>、26<sub>4</sub> との間に広く設けられている。

40

#### 【0109】

第二デバイス 201 は、第一デバイス 1 (図 1) と実質的に同一の方法で製造される。しかし、パタン形成したレジスト層 51 (図 91) は、異なるパタンを有するため、3 本のリードではなく、4 本のリードを形成することになる。

### 第三磁気抵抗デバイス 301

#### 【0110】

図 12 に、第三磁気抵抗デバイス 301 を示す。

#### 【0111】

第三磁気抵抗デバイス 301 は、前述の第一磁気抵抗デバイス 1 (図 1) と同様である。従って、同一の引用番号は、同一の特徴を指すために用いることとする。

50

**【0112】**

第三デバイス301が第一デバイス1(図1)と異なる点は、リード26が2本のみになること、すなわち、第一及び第二リード $26_1$ 、 $26_2$ となることである。第一及び第二リード間の間隔 $s_1'$ は、第一及び第二デバイスの第二及び第三リード間の間隔 $s_2$ と同一とすることができます。シャント8とチャネル11は、より短くしてもよい。

**【0113】**

図13に、磁気抵抗デバイス301を動作させる回路32を示す。

**【0114】**

電流源33は、シャント8と、第一及び第二リード $26_1$ 、 $26_2$ 間のチャネル11とを流れる電流Iを駆動するように構成されている。電圧計34は、第一及び第二リード $26_1$ 、 $26_2$ 間に発生した電圧Vを測定するように構成されている。10

**【0115】**

第三デバイス301の出力信号は、第一デバイス1(図1)の出力と同一である。

**【0116】**

第三デバイス301は、第一デバイス1(図1)と実質的に同一の方法で製造される。しかし、パタン形成したレジスト層51(図91)が、異なるパタンを有するため、3本のリードではなく、2本のリードを形成することになる。

**第四磁気抵抗デバイス401****【0117】**

図14及び図14aに、第四磁気抵抗デバイス401を示す。20

**【0118】**

第四磁気抵抗デバイス401は、前述の第二磁気抵抗デバイス201(図10)と同様である。従って、同一の引用番号は、同一の特徴を指すために用いることとする。

**【0119】**

第四デバイス401が第二デバイス201(図10)と異なる点は、第一リード $26_1$ が、シャント8に接続されており、シャント8が効果的に第一リード $26_1$ の一部となることがある。従って、第一リード $26_1$ は、平面図ではL字型となる。その結果、チャネル11も、平面図ではL字型となり、各々、x軸及びz軸に沿って置かれる第一及び第二部分 $11_1$ 、 $11_2$ を有する。

**【0120】**

第二、第三及び第四リード $26_2$ 、 $26_3$ 、 $26_4$ は、チャネル11の表面21への接点27を提供し、第一リード $26_1$ は、チャネル11の反対面への接点27aを提供する。図14及び図14aでは、表面21は、チャネル11の上面であり、反対面は、チャネルの底面又は下面である。デバイス401は、逆さにしてスライダに取り付けることにより、表面21がデバイスの下面となり、反対面が下地の基板に対して上側とができる。

**【0121】**

いくつかの実施様態においては、第一半導体層8を省いて、パタン形成したケイ化したシード層7により、リード $26_1$ を提供することができる。これを用いることにより、チャネル11により提供される(y軸に沿った)短い接合領域(junction region)を有するデバイスを形成することができる。接点から、例えば、接合層の底部から電荷を注入し、例えば、接合層の上面の接点で、電荷を収集することができ、これにより、“Y型”デバイスの形状を形成することができる。異なる接点により収集される電荷の比率は、印可される磁場に影響されて決まる。40

**【0122】**

リード $26_1$ は、図14aに示すような比較的長い接点27aではなく、図14bに示すように、比較的短い接点27a'を提供するようにパタン形成してもよい。

**【0123】**

チャネル層11の第二部分 $11_2$ は、側面30に対して垂直に伸びており、そのため、側面30に対して垂直に印可された磁場31に対しては平行となるので、デバイス40150

の磁気抵抗作用には寄与しない。

**【0124】**

図15に、磁気抵抗デバイス401を動作させる回路32を示す。図15に示すように、第二デバイス201(図10)を動作させるのに用いたものと同じ構成、すなわち、図11に示す4本リード構成を用いることができる。

**【0125】**

磁場31を印可すると、第二及び第四リード26<sub>2</sub>、26<sub>4</sub>間に電圧が発生する。チャネル11の長さにより、発生した電圧には、ホール電圧成分(Hall voltage component)と、磁場31中の電流経路35の屈曲で生じる電圧差成分とが含まれる。

**【0126】**

第四デバイス401は、第一デバイス1(図1乃至図4)と実質的に同様の方法で製造される。しかし、製造は2つの点で異なる。

**【0127】**

一つ目の違いは、パタン形成されたレジスト層46(図9e)が、異なるパタンを有する、すなわち、細長の棒状ではなく、L字型のパタンを用いる点である。

**【0128】**

二つ目の違いは、パタン形成されたレジスト層51(図9l)が異なるパタンを有する点である。このパタンも、3本のリードを定義するものであるが、これらのリードは、異なる場所に配置されている。

第五磁気抵抗デバイス501

**【0129】**

図16に、第五磁気抵抗デバイス501を示す。

**【0130】**

第五磁気抵抗デバイス501は、前述の第四磁気抵抗デバイス401(図14)と同様である。従って、同一の引用番号は、同一の特徴を指すために用いることとする。

**【0131】**

第四デバイス401と同様に、第一のリード26<sub>1</sub>が、シャント8に接続されており、シャント8が効果的に第一リード26<sub>1</sub>の一部となる。しかし、第五デバイス501は、3本のリード26のみ、すなわち、第二及び第三リード26<sub>2</sub>、26<sub>3</sub>のみを有する。

**【0132】**

第四磁気抵抗デバイス401と同様に、図14aに示すものと同様の比較的長い接点27aを提供するのではなく、図14bに示すものと同様の比較的短い接点27a'を提供するように、リード26<sub>1</sub>をパタン形成してもよい。

**【0133】**

図17に、磁気抵抗デバイス501を動作させる回路32を示す。図17に示すように、第一デバイス1(図1)を動作させるのに用いたものと同一の構成、すなわち、図4に示すような3本リード構成を用いることができる。

**【0134】**

第五デバイス501は、第一デバイス1(図1)と実質的に同様の方法で製造される。しかし、製造は2つの点で異なる。

**【0135】**

一つ目の違いは、パタン形成されたレジスト層46(図9e)が、異なるパタンを有する、すなわち、細長の棒状ではなく、L字型のパタンを用いる点である。

**【0136】**

二つ目の違いは、パタン形成されたレジスト層51(図9l)が異なるパタンを有する点である。このパタンも、3本のリードを定義するものであるが、これらのリードは、異なる場所に配置されている。

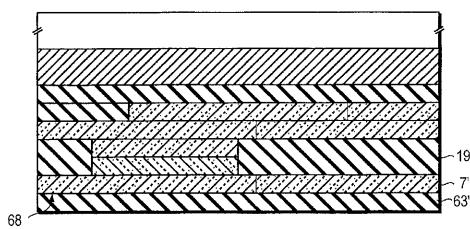

第六磁気抵抗デバイス601

**【0137】**

図18及び図19に、第六磁気抵抗デバイス601を示す。

10

20

30

40

50

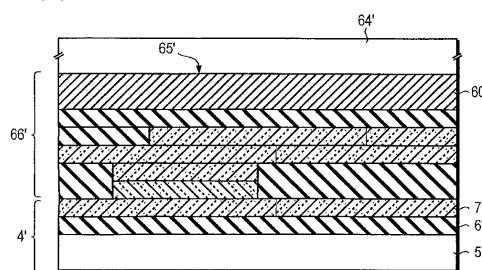

**【 0 1 3 8 】**

第六磁気抵抗デバイス 6 0 1 は、前述の第一磁気抵抗デバイス 1 ( 図 1 ) と同様である。従って、同一の引用番号は、同一の特徴を指すために用いることとする。

**【 0 1 3 9 】**

第六デバイス 6 0 1 は、以下の点で異なる。すなわち、第一及び第二磁気遮蔽層 6 0 、 6 1 は、シャント 8 と、チャネル 1 1 と、パタン形成された第一誘電体層 1 9 と、パタン形成された第二誘電体層 2 4 と、リード 2 6 と、第三誘電体層 2 9 とを含む垂直構造 6 2 を挟む形となっている点である。さらに、第六デバイス 6 0 1 は、以下の点で異なる。すなわち、ハンドル層 5 ( 図 1 ) が犠牲となり、埋込絶縁層 6 ( 図 1 ) も犠牲となり、別のもっと厚い誘電体層 6 3 で置き換えられている点である。デバイス 6 0 1 は、表面 6 5 上のアルミ炭化チタン ( aluminum titanium carbide ) ウェハ 6 4 ( 明確化のため、図 1 8 では不図示 ) に接合されている。10

**【 0 1 4 0 】**

第六デバイス 6 0 1 を動作させるために、第一デバイス 1 ( 図 1 ) を動作させるために用いたものと同一の構造を用いることができる。

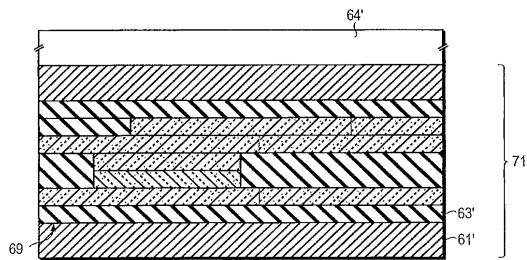

**【 0 1 4 1 】**

図 2 0 a 乃至図 2 0 f を用いて、第六デバイス 6 0 1 を製造するための追加の処理段階を説明する。

**【 0 1 4 2 】**

特に、図 2 0 a に示すように、第三誘電体層 2 9 ' の上面 2 9 上に、第一磁気遮蔽層 6 0 ' をデポジットさせる。本例においては、磁気遮蔽層 6 0 ' は、パーマロイ ( すなわち、ニッケルと鉄の合金 ) を含んでおり、スパッタリングによりデポジットさせる。20

**【 0 1 4 3 】**

図 2 0 b に示すように、構造 6 6 は、ウェハ 6 4 ' に接合されている。本例においては、ウェハ 6 4 ' は、アルミ炭化チタン ( " AlTiC " ) ウェハ 6 4 ' の形状となっている。特に、ウェハ 6 4 ' は、第一磁気遮蔽層 6 0 ' の上面 6 5 ' に接合されている。

**【 0 1 4 4 】**

ハンドル層 5 ' は、埋込絶縁層 6 ' に到るまでエッティングする。その結果得られる構造を図 2 0 c に示す。

**【 0 1 4 5 】**

埋込絶縁層 6 ' は、シード層 7 ' に到るまでエッティングする。そ結果得られる構造を図 2 0 d に示す。30

**【 0 1 4 6 】**

シード層 7 ' は、( 幅広の ) チャネル 1 1 ' 又は ( 幅広の ) シャント層 8 ' と同一又は同様の延長を有するように、電子ビーム・リソグラフィと湿式エッティングを用いてパタン形成することができ、さらに、例えば、ニッケル ( Ni ) を用いてケイ化することができる。シード層 7 は、パタン形成により、チャネル 1 1 ' 又はシャント層 8 ' に対する短尺の接点 2 7 a ' ( 図 1 4 b ) を提供することができる。

**【 0 1 4 7 】**

図 2 0 e に示すように、シード層 7 ' の下側 6 8 、あるいは、パタン形成されケイ化されたシード層 ( 不図示 ) 及び第一誘電体層 1 9 ' の下側 ( 不図示 ) に、誘電体材料の新しい層 6 3 ' をデポジットさせる。本例においては、誘電体材料は二酸化ケイ素であり、化学蒸着 ( C V D ) を用いてデポジットする。40

**【 0 1 4 8 】**

図 2 0 f に示すように、第三誘電体層 6 3 ' の下面 6 9 上に、第二磁気遮蔽層 6 1 ' をデポジットさせる。本例においては、磁気遮蔽層 6 1 ' は、パーマロイを含んでおり、スパッタリングによりデポジットさせる。

**【 0 1 4 9 】**

図 2 0 f は、結果として得られる、ウェハ 6 4 ' 上のデバイス構造 7 1 を示すものである。50

**【0150】**

この段階で、ウェハを棒状（不図示）に裁断し、棒の縁をラッピングすることにより、側面30（図18）を形成することができる。

**【0151】**

しかし、デバイス601（図18）で、磁気ヘッドスライダ70（図27）の一部を形成しようとする場合には、裁断及びラッピング段階の前に、書込みヘッド72（図25a）を製造するのが普通である。これについては、後に詳述する。

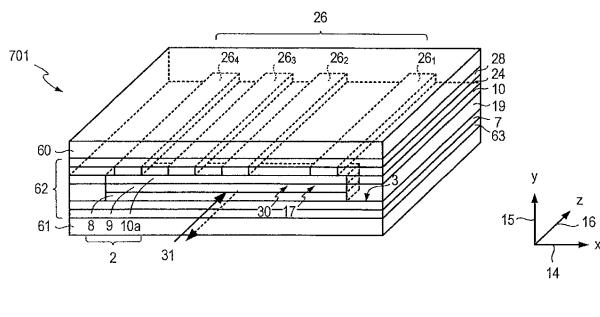

**第七磁気抵抗デバイス701****【0152】**

図21に、第七磁気抵抗デバイス701を示す。

10

**【0153】**

第七磁気抵抗デバイス701は、前述の第二磁気抵抗デバイス201（図10）及び第六磁気抵抗デバイス601（図18）と同様である。従って、同一の引用番号は、同一の特徴を指すために用いることとする。

**【0154】**

第七磁気抵抗デバイス701は、4本のリード26、すなわち、第一、第二、第三及び第四リード<sub>26</sub><sub>1</sub>、<sub>26</sub><sub>2</sub>、<sub>26</sub><sub>3</sub>、<sub>26</sub><sub>4</sub>を有するという点で、第六磁気抵抗デバイス601（図18）と異なる。第三及び第四リード間の間隔<sub>s</sub><sub>2</sub>は、第二及び第三リード間の間隔<sub>s</sub><sub>2</sub>と同一とすることができる。これらの数のリード26を収容するために、層構造2はより長くしてもよい。

20

**【0155】**

第七デバイス701は、第二デバイス201と同様の方法で動作させることができる。

**【0156】**

第七デバイス701は、第六デバイス601（図18）と実質的に同一の方法で製造される。しかし、第二磁気抵抗デバイス201（図10）と同様に、3本ではなく、4本のリード26を形成するために、パタン形成したレジスト層51（図91）は異なるパタンを有する。

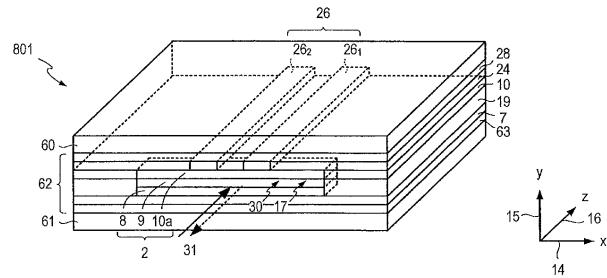

**第八磁気抵抗デバイス801****【0157】**

図22に、第八磁気抵抗デバイス801を示す。

30

**【0158】**

第八磁気抵抗デバイス801は、前述の第三磁気抵抗デバイス301（図12）及び第六磁気抵抗デバイス601（図18）と同様である。従って、同一の引用番号は、同一の特徴を指すために用いることとする。

**【0159】**

第八磁気抵抗デバイス801は、前述の第三磁気抵抗デバイス301（図12）と同様であるが、第六磁気抵抗デバイス601（図18）とは、2本のリード、すなわち第一及び第二リード<sub>26</sub><sub>1</sub>、<sub>26</sub><sub>2</sub>を有するという点で異なる。

**【0160】**

第八磁気抵抗デバイス801は、第三デバイス301（図12）と同様の方法で動作させることができる。

40

**【0161】**

第八デバイス801は、第六デバイス601（図18）と実質的に同一の方法で製造される。しかし、第三磁気抵抗デバイス301（図12）と同様に、3本ではなく、2本のリード26を形成するために、パタン形成したレジスト層51（図91）は異なるパタンを有する。

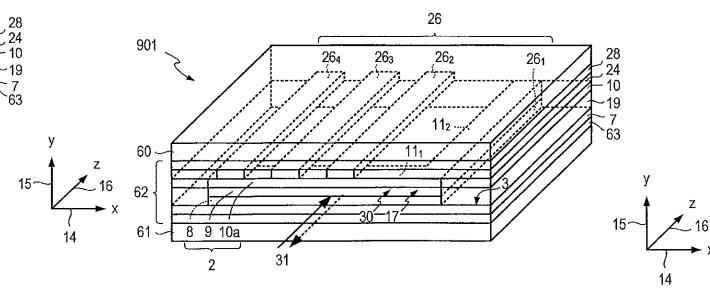

**第九磁気抵抗デバイス901****【0162】**

図23に、第九磁気抵抗デバイス901を示す。

**【0163】**

50

第九磁気抵抗デバイス901は、前述の第四磁気抵抗デバイス401(図14)及び第六磁気抵抗デバイス601(図18)と同様である。従って、同一の引用番号は、同一の特徴を指すために用いることとする。

#### 【0164】

第九磁気抵抗デバイス901は、前述の第四磁気抵抗デバイス401(図14)と同様であるが、第六磁気抵抗デバイス601(図18)とは、第一リード26<sub>1</sub>がシャント8に接続し、シャント8が効果的に第一リード26<sub>1</sub>の一部になるという点で異なる。

#### 【0165】

第九磁気抵抗デバイス901は、第四デバイス401(図14)と同様の方法で動作させることができる。

10

#### 【0166】

第九デバイス901は、第六デバイス601(図18)と実質的に同一の方法で製造される。しかし、第四磁気抵抗デバイス401(図14)と同様に、パタン形成したレジスト層46(図9e)は、直線状の棒とは異なるパタン、すなわちL字型パタンを有し、パタン形成したレジスト層51(図91)は異なるパタンを有する。このパタンも、3本のリードを定義するものであるが、これらのリードは異なる場所に配置されている。

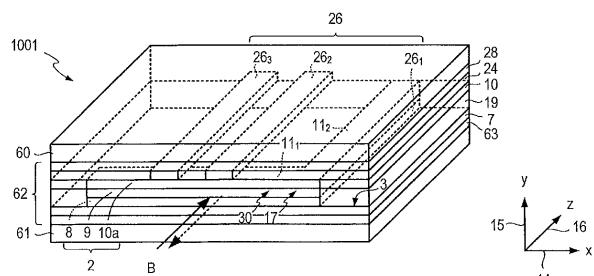

### 第十磁気抵抗デバイス1001

#### 【0167】

図24に、第十磁気抵抗デバイスを示す。

#### 【0168】

第十磁気抵抗デバイス1001は、前述の第五磁気抵抗デバイス501(図16)及び第六磁気抵抗デバイス601(図18)と同様である。従って、同一の引用番号は、同一の特徴を指すために用いることとする。

20

#### 【0169】

第十磁気抵抗デバイス1001は、前述の第五磁気抵抗デバイス501(図16)と同様であるが、第六磁気抵抗デバイス601(図18)とは、第一リード26<sub>1</sub>がシャント8に接続しているという点で異なる。

#### 【0170】

第十磁気抵抗デバイス1001は、第五デバイス501(図16)と同様の方法で動作させることができる。

30

#### 【0171】

第十磁気抵抗デバイス1001は、第六デバイス601(図18)と実質的に同一の方法で製造される。しかし、第五磁気抵抗デバイス501(図16)と同様に、パタン形成したレジスト層46(図9e)は、直線状の棒とは異なるパタン、すなわちL字型パタンを有し、パタン形成したレジスト層51(図91)は異なるパタンを有する。このパタンは、2本のリードを定義する。

### 磁気ヘッドスライダ

#### 【0172】

図25及び図26に、磁気ヘッドスライダ70を製造する方法を示す。

#### 【0173】

読み出しヘッド構造71は、前述したように製造する(ステップS1)。図25aに示すように、読み出しヘッド構造71は、ラッピングされていないチャネル11'及びオプションのシャント8'を含むラッピングされていない垂直層構造2'を含んでいる。

40

#### 【0174】

書き込みヘッド構造72を製造する(ステップS2)。

#### 【0175】

図25aに示すように、読み出しヘッド構造71及び書き込みヘッド構造72は、例えば、スパッタリングされたアルミナ(A1<sub>2</sub>O<sub>3</sub>)を含む厚い誘電体層73により、互いに隔離することができる。書き込みヘッド構造72も、他の厚い誘電体層74により保護することができる。

50

## 【0176】

前述してきたデバイスの多くは、チャネル11の上面に接点27を備え、チャネル11の下にシャント8を備えるように図示してある。しかし、これらのデバイスは逆さにして、シャント8がチャネルの上面に置かれ、接点27がチャネル11の下に置かれるようにして、デバイスをスライダ70の中に統合することができる。このように、図25aに示すように、読出しヘッド構造71は、図20fに示した読出しヘッド構造71とは逆の位置関係となる。

## 【0177】

処理したウェハ75を、 $x$ 軸に沿って伸び、縁76を有する棒76にスライスする(sliced: 裁断又は切断) (ステップS3)。通常、一本の棒76からは、おおむね50本の読出しヘッド及び書込みヘッドを作ることができる。

10

## 【0178】

縁77をラッピングし、側面30を有する空気ベアリング面78を形成する(ステップS4)。適切なラッピング処理は、米国特許番号2002/0126421A1に記載されており、参照により本明細書に援用する。

## 【0179】

図25cは、接合基板64上に設けられ、結果として得られる構造79を示すものであり、ここでは“ヘッド要素部”と称する。ヘッド要素部79は、第六、第七、第八、第九又は第十磁気抵抗デバイス601、701、801、901、1001などの読出しヘッド80と、書込みヘッド81とを含んでいる。

20

## 【0180】

例えは数ナノメートルの厚さを有する保護フィルム(不図示)を、空気ベアリング面78に形成することができる(ステップS5)。乾式エッチングにより、空気ベアリング面レールを形成する(ステップS6)。処理された列状の棒を、分離した磁気ヘッドスライダ70に切断する(切り出す)(ステップS7)。最後に、懸架装置(suspension: サスペンション)に取り付ける前に、磁気ヘッドスライダ70を試験する(ステップS8)。

## 【0181】

図27に、磁気ヘッドスライダ70を詳細に示す。

## 【0182】

前述したように、ヘッド要素部79は、基板64上に形成され、読出しヘッド80及び書込みヘッド81とを含んでいる。

30

## 【0183】

空気ベアリング面78は、階段状の面82、83、84の組を含んでおり、それらは、レール面82、浅いグループ(溝)面83、深いグループ(溝)面84となっている。スライダ70は、先端面(leading face: 先行面)85と終端(trailing end: 後端)86とを含んでいる。

## 【0184】

図28に、磁気ディスクドライブ87を示す。

## 【0185】

磁気ディスクドライブ87は、スピンドルモータ(不図示)により駆動する中心ハブ90に、磁気ディスク又は“媒体”89を積重ねたもの(明確化のため1つのみを示す)を搭載したハウジング88を含んでいる。

40

## 【0186】

各磁気ディスク89には、2つのスライダ70が備えられており、ディスク89の各側に一つづつスライダ70が備えられている。各スライダ70は、各懸架装置91の先端に取り付けられ、さらに懸架装置は、アクチュエータ93により駆動される各アームにより支持されている。

## 【0187】

このように、磁気ディスクドライブ87には、前述したような垂直型の磁気抵抗デバイスを有するスライダ70を設けることができる。

50

**【0188】**

前述した実施様態に対して、多くの修正を加えることが可能である。

**【0189】**

例えば、チャネル11は、僅かに不純物添加したp型とすることができる。さらに、ケイ素に代えて、例えば、 $\times$ が概ね0.1の $\text{Si}_{1-x}\text{Ge}_x$ を用いることもできる。

**【0190】**

ひずみ半導体(strained semiconductor)、例えば、ひずみケイ素(strained silicon)を用いてもよい。

**【0191】**

I II - V材料などの、他の半導体材料系を用いることもできる。

10

**【0192】**

チャネルは、不純物添加を全くしない、あるいは、概ね $1 \times 10^{15} \text{ cm}^{-3}$ の濃度まで、又は、概ね $1 \times 10^{16} \text{ cm}^{-3}$ の濃度まで、又は、概ね $1 \times 10^{17} \text{ cm}^{-3}$ の濃度まで、又は、概ね $1 \times 10^{18} \text{ cm}^{-3}$ の濃度まで不純物(n型又はp型)添加したものとしてもよい。

**【0193】**

シャント及び/又はリードは、少なくとも $1 \times 10^{19} \text{ cm}^{-3}$ の濃度まで、又は、少なくとも $1 \times 10^{20} \text{ cm}^{-3}$ の濃度まで、又は、少なくとも $1 \times 10^{21} \text{ cm}^{-3}$ の濃度まで、例えば、概ね $1 \times 10^{21} \text{ cm}^{-3}$ の濃度で不純物(n型又はp型)添加したものとしてもよく、及び/又は、シャント及び/リードは、不純物添加(-doped layers)した一つあるいはそれ以上の数の層を含むものであってよい。

20

**【0194】**

チャネル及び/シャントは、概ね1nmと5nmの間の厚み、又は、概ね5nmと10nmの間の厚み、又は、概ね10nmと20nmの間の厚みを有するものであってよい。リードは、概ね1nmと5nmの間の厚み、又は、概ね5nmと10nmの間の厚み、又は、概ね10nmと20nmの間の厚み、又は、概ね20nmと概ね50nmの厚みを有するものであってよい。チャネル、シャント及びリードは、異なる厚みを有していてよい。

**【0195】**

シャントは、例えば、第一チャネル層を成長させる前にシャントの一部を覆うことにより、又は、成長の後で第一チャネル層をエッティングすることにより、チャネルの一部に沿って伸びてもよく、その逆でもよい。シャントは、必ずしも矩形である必要はない。

30

**【0196】**

チャネルは、概ね1nmと5nmの間の幅(すなわち、W)、又は、概ね5nmと10nmの間の幅、又は、概ね10nmと20nmの幅を有するものであってよい。チャネルは、概ね20nmと50nmの間の長さ(すなわち、L)、又は、概ね50nmと100nmの間の長さ、又は、概ね100nmと200nmの長さ、又は、概ね200nmと500nmの長さを有するものであってよい。

**【0197】**

チャネルの検出領域が、多結晶ケイ素(polycrystalline silicon)の粒径(grain size)に比べて小さい場合には、多結晶シード層(polycrystalline seed layer)を用いてもよい。

40

**【0198】**

終端リードは、垂直方向ではなく、チャネルの終端からチャネルに到るように配置してもよい。デバイスは、用いられないリードを含むものであってよい。例えば、デバイスは、4本又はそれ以上の数のリードを含んでいるが、チャネルを介して信号を出力し、信号を検出するために、実際の数より少ないリードを用いるものであってよい。

**【0199】**

適切なCVDの形態及び、半導体材料の選択的又は非選択的なデポジットを提供するために適したデポジット条件は、ルーチン的な実験により求めることができる。エッティング

50

及び現像に際して、他の濃度及び混合比を用いてもよい。他のエッティング（例えば、乾式エッティング）、他のレジスト材料、及び他の現像材料を用いてもよい。エッティング、照射及び現像の時間は、変更することができ、その値は、実験により求めることができる。アニーリング温度も、実験により求めることができる。

### 【0200】

デバイスは、必ずしも、EMR効果を有する必要はなく、例えば、電流経路を屈曲させるためにローレンツ力を用いる、及び／又はホール効果を用いた、MR効果を有することもできる。

### 【符号の説明】

#### 【0201】

1 第一磁気抵抗デバイス

2 層構造

3 表面

4 平面基板

5 半導体基部

6 埋込絶縁層

7 半導体最上位層

8 第一半導体層

9 第二半導体層

10 第三半導体層

10

20

【図1】

【図1a】

【図1b】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図8】

【図9 a】

【図9 b】

【図9 c】

【図9 d】

【図9 e】

【図9 f】

【図9 g】

【図9 h】

【図9 i】

【図9j】

【図9n】

【図9k】

【図9o】

【図9l】

【図9p】

【図9m】

【図11】

【図12】

【図9r】

【図10】

【図13】

【図14】

【図16】

【図14a】

【図14b】

【図15】

【図19】

【図20a】

【図20b】

【図17】

【図18】

【図20c】

【図20d】

【図20e】

【図 20 f】

【図 22】

【図 21】

【図 23】

【図 24】

【図 25】

【図26】

【図27】

【図28】

---

フロントページの続き

(72)発明者 福田 宏

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所 中央研究所内

(72)発明者 鶯尾 勝由

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所 中央研究所内

審査官 小山 満

(56)参考文献 特開2007-335839(JP,A)

特開2006-019728(JP,A)

特開2001-223411(JP,A)

特開2011-040750(JP,A)

米国特許出願公開第2009/0073615(US,A1)

米国特許出願公開第2009/0218563(US,A1)

特開2009-295987(JP,A)

特開2002-163808(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 43/08

G11B 5/39

H01L 43/12