**【特許請求の範囲】****【請求項 1】**

プロセッサと I / F とメモリ制御回路とを備えるメモリアクセス装置であって、前記プロセッサはメモリアクセス要求を発行する発行手段を備え、前記 I / F は前記発行手段によって発行されたメモリアクセス要求をクロック信号に応答して保持する第 1 保持手段を備え、そして前記メモリ制御回路は前記第 1 保持手段によって保持されたメモリアクセス要求に従うアクセス処理を実行する処理手段を備える、メモリアクセス装置。

**【請求項 2】**

前記メモリ制御回路は前記処理手段の処理状態を参照して第 1 レディ / ビジー信号を出力する第 1 出力手段をさらに備え、

前記 I / F は前記発行手段によって発行されたメモリアクセス要求と前記第 1 出力手段によって出力された第 1 レディ / ビジー信号とに基づいて応答信号を作成する作成手段をさらに備え、そして

前記プロセッサは前記作成手段によって作成された応答信号に基づいて第 2 レディ / ビジー信号を出力する第 2 出力手段をさらに備える、請求項 1 記載のメモリアクセス装置。

**【請求項 3】**

前記 I / F は前記第 2 出力手段によって出力された第 2 レディ / ビジー信号を前記クロック信号に応答して保持する第 2 保持手段をさらに備え、

前記処理手段は前記第 2 保持手段によって保持された第 2 レディ / ビジー信号を参照して前記アクセス処理を実行する、請求項 2 記載のメモリアクセス装置。

**【請求項 4】**

前記作成手段は、前記第 1 保持手段によって保持されたメモリアクセス要求の状態を識別する状態識別信号を作成する第 1 信号作成手段、および前記第 1 信号作成手段によって作成された状態識別信号と前記第 1 出力手段によって出力された第 1 レディ / ビジー信号とに論理積を施して前記応答信号を作成する第 2 信号作成手段を含む、請求項 2 または 3 記載のメモリアクセス装置。

**【請求項 5】**

前記メモリアクセス要求はアクセスデータのワード数が記述されたワード数情報を含み、

前記第 1 信号作成手段は前記ワード数情報に応じて異なる状態識別信号を作成する、請求項 4 記載のメモリアクセス装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

この発明は、メモリアクセス装置に関し、特に、プロセッサによって発行されたメモリアクセス要求に従うアクセス処理をメモリ制御回路と協働して実行する、メモリアクセス装置に関する。

**【背景技術】****【0002】**

この種の装置の一例が、特許文献 1 に開示されている。この背景技術によれば、複数の要求元からそれぞれ発行された複数のリクエストが調停回路によって調停される。メモリアクセス回路は、調停回路によって書き込みリクエストが承認されたとき、 SDRAM に所望のデータを書き込む。メモリアクセス回路はまた、調停回路によって読み出しリクエストが承認されたとき、 SDRAM から所望のデータを読み出す。

**【特許文献 1】特開 2006 - 330806 号公報****【発明の開示】****【発明が解決しようとする課題】****【0003】**

しかし、背景技術では、要求元と調停回路とを結ぶ信号線の品質に起因してリクエスト

10

20

30

40

50

の転送動作に遅延が生じ、これによってメモリアクセス処理の高速化が妨げられるおそれがある。

#### 【0004】

それゆえに、この発明の主たる目的は、メモリアクセス処理の高速化を実現できる、メモリアクセス装置を提供することである。

#### 【課題を解決するための手段】

#### 【0005】

この発明に従うメモリアクセス装置(10：実施例で相当する参照符号。以下同じ)は、プロセッサ(12)とI/F(14)とメモリ制御回路(16)とを備えるメモリアクセス装置(10)であって、プロセッサはメモリアクセス要求を発行する発行手段(12b)を備え、I/Fは発行手段によって発行されたメモリアクセス要求をクロック信号に応答して保持する第1保持手段(24~30)を備え、そしてメモリ制御回路は第1保持手段によって保持されたメモリアクセス要求に従うアクセス処理を実行する処理手段(16a)を備える。

10

#### 【0006】

メモリアクセス装置は、プロセッサとI/Fとメモリ制御回路とを備える。プロセッサはメモリアクセス要求を発行する発行手段を備え、I/Fは発行手段によって発行されたメモリアクセス要求をクロック信号に応答して保持する第1保持手段を備え、そしてメモリ制御回路は第1保持手段によって保持されたメモリアクセス要求に従うアクセス処理を実行する処理手段を備える。

20

#### 【0007】

メモリアクセス要求をクロック信号に応答して保持することで、メモリアクセス要求の転送動作の遅延をクロック信号の周期まで短縮される。これによって、メモリアクセス処理の高速化が図られる。

#### 【0008】

好ましくは、メモリ制御回路は処理手段の処理状態を参照して第1レディ/ビジー信号を出力する第1出力手段(16b)をさらに備え、I/Fは発行手段によって発行されたメモリアクセス要求と第1出力手段によって出力された第1レディ/ビジー信号とに基づいて応答信号を作成する作成手段(34)をさらに備え、そしてプロセッサは作成手段によって作成された応答信号に基づいて第2レディ/ビジー信号を出力する第2出力手段(12c)をさらに備える。

30

#### 【0009】

或る局面では、I/Fは第2出力手段によって出力された第2レディ/ビジー信号をクロック信号に応答して保持する第2保持手段(32)をさらに備え、処理手段は第2保持手段によって保持された第2レディ/ビジー信号を参照してアクセス処理を実行する。

#### 【0010】

他の局面では、作成手段は、第1保持手段によって保持されたメモリアクセス要求の状態を識別する状態識別信号を作成する第1信号作成手段(36, 38)、および第1信号作成手段によって作成された状態識別信号と第1出力手段によって出力された第1レディ/ビジー信号とに論理積を施して応答信号を作成する第2信号作成手段(40)を含む。

40

#### 【0011】

さらに好ましくは、メモリアクセス要求はアクセスデータのワード数が記述されたワード数情報を含み、第1信号作成手段はワード数情報に応じて異なる状態識別信号を作成する。

#### 【発明の効果】

#### 【0012】

この発明によれば、メモリアクセス要求をクロック信号に応答して保持するようにしたため、メモリアクセス要求の転送動作の遅延をクロック信号の周期まで短縮される。これによって、メモリアクセス処理の高速化が図られる。

#### 【0013】

この発明の上述の目的、その他の目的、特徴および利点は、図面を参照して行う以下の

50

実施例の詳細な説明から一層明らかとなろう。

**【発明を実施するための最良の形態】**

**【0014】**

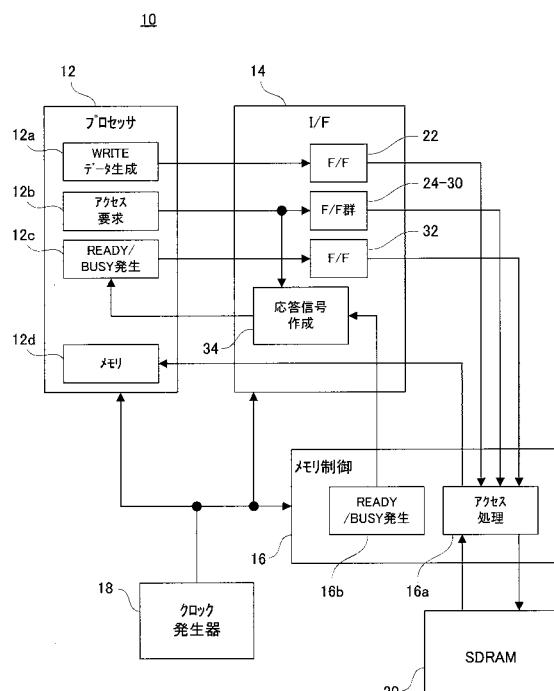

図1を参照して、この実施例のメモリアクセス装置10は、クロック信号を発生するクロック発生器18を含む。クロック発生器20によって発生されたクロック信号は、タイミング制御のためにプロセッサ12、I/F回路14およびメモリ制御回路16に与えられる。

**【0015】**

プロセッサ12に設けられたアクセス要求発生回路12bは、SDRAM20に対するデータ書き込みまたはSDRAM20からのデータ読み出しを実行するとき、I/F回路14に向けてメモリアクセス要求を発行する。発行されたメモリアクセス要求は、I/F回路14に設けられたF/F回路24～30によって一時的に保持され、その後にメモリ制御回路16のアクセス処理回路16aに向けて出力される。アクセス処理回路16aは、I/F回路14から与えられたメモリアクセス要求に従って、所望のデータをSDRAM20に書き込み、或いはSDRAM20に格納された所望のデータを読み出す。10

**【0016】**

データ書き込みの対象となる所望のデータは、プロセッサ12に設けられたWRITEデータ作成回路12aによって作成され、I/F回路14に設けられたF/F回路22を経てアクセス処理回路16aに与えられる。また、アクセス処理回路16aによってSDRAM20から読み出された所望のデータは、I/F回路14を経てプロセッサ12に与えられ、プロセッサ12に設けられたメモリ12dに書き込まれ。20

**【0017】**

メモリ制御回路16に設けられたREADY/BUSY発生回路16bは、アクセス処理回路16aによって実行されるアクセス処理を参照して第1レディ/ビジー信号を作成し、作成された第1レディ/ビジー信号をI/F回路14に向けて出力する。I/F回路14に設けられた応答信号作成回路34は、プロセッサ12から与えられた上述のメモリアクセス要求とREADY/BUSY発生回路16bから与えられた第1レディ/ビジー信号とに基づいて応答信号を作成し、作成された応答信号をプロセッサ12に与える。

**【0018】**

プロセッサ12のREADY/BUSY発生回路12cは、I/F回路14から与えられた応答信号に基づいて第2レディ/ビジー信号を作成する。作成された第2レディ/ビジー信号は、I/F回路14に設けられたF/F回路32を経て、メモリ制御回路16のアクセス処理回路16aに与えられる。アクセス処理回路16aは、与えられた第2レディ/ビジー信号を参照してアクセス処理を実行する。こうしてやり取りされる第1レディ/ビジー信号および第2レディ/ビジー信号によって、プロセッサ12とメモリ制御回路16との間で連携が確保される。30

**【0019】**

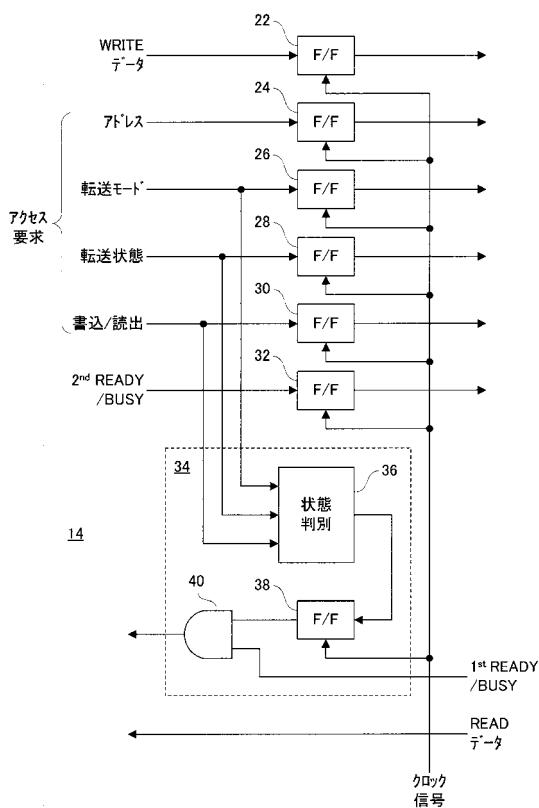

I/F回路14は、図2に示すように構成される。プロセッサ12から与えられるメモリアクセス要求は、アドレス情報、転送モード情報、転送状態情報および書き込み/読み出し情報を含む。アドレス情報には、アクセス先のアドレスが記述される。転送モード情報には、書き込み/読み出しの対象となるデータのワード数が“1ワード”および“2ワード以上”的いずれであるかを識別する情報が記述される。転送状態情報には、現時点の書き込み/読み出しに係るデータが“1ワード目”であるか“2ワード目以降”であるかを識別する情報が記述される。書き込み/読み出し情報には、今回のアクセスが“データ書き込み”および“データ読み出し”的いずれであるかを識別する情報が記述される。40

**【0020】**

アドレス情報は、F/F回路24を経てメモリ制御回路16に出力される。転送モード情報は、F/F回路26を経てメモリ制御回路16に出力される。転送状態情報は、F/F回路28を経てメモリ制御回路16に出力される。書き込み/読み出し情報は、F/F回路30を経てメモリ制御回路16に出力される。なお、転送モード情報、転送状態情報50

および書き込み／読み出し情報は、総括して“各種制御情報”と定義する。

【0021】

各種制御情報はまた、状態判別回路36に与えられる。状態判別回路36は、与えられた各種制御情報に基づいて現在のアクセス要求状態を判別し、状態判別信号を出力する。出力された状態判別信号は、F/F回路38を介してANDゲート40に与えられる。ANDゲートは、F/F回路38から与えられた状態判別信号とメモリ制御回路16から与えられた第1レディ／ビジー信号とに論理積を施して応答信号を作成し、作成された応答信号をプロセッサ12に向けて出力する。

【0022】

なお、上述のように、データ書き込みの対象となるデータはF/F回路22を介してメモリ制御回路16に出力され、第2レディ／ビジー信号はF/F回路32を介してメモリ制御回路16に出力され、そしてSDRAM20から読み出されたデータはそのままプロセッサ12に出力される。また、F/F回路22～32および38は、クロック発生回路18から出力されたクロック信号に同期してF/F動作を実行する。

10

【0023】

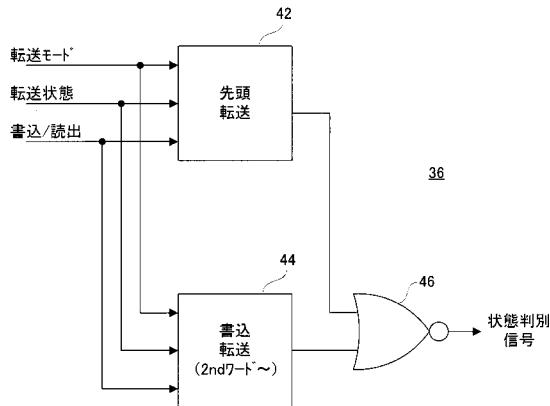

状態判別回路36は、図3に示すように構成される。各種制御情報は、先頭転送回路42および書き込み転送回路44の各々に与えられる。先頭転送回路42および書き込み転送回路44は、表1に示す要領で“0”または“1”を出力する。

【表1】

20

| ①先頭転送 | ②書き込み転送<br>(2ndワード～) | 状態<br>判別信号 |

|-------|----------------------|------------|

| 1     | x                    | 0          |

| x     | 1                    | 0          |

| 0     | 0                    | 1          |

30

【0024】

表1によれば、先頭転送回路42は、データ書き込みおよびデータ読み出しの各々が実行されるとき、1ワード目のメモリアクセス要求に対応して

40

“1”を出力する。また、書き込み転送回路44は、データ書き込みが実行されるとき、2ワード目以降のメモリアクセス要求に対応して“1”を出力する。

【0025】

先頭転送回路42および書き込み転送回路44の出力はEXOR回路46によって排他的論理和処理を施される。演算結果は、状態判別信号としてEXOR回路46から出力される。

【0026】

参考までに、表1において注目される動作をデータ読み出しおよびデータ書き込みの各々に対応して表2に示す。

50

【表2】

| 書込/読出 | 転送長    | 表1の中で注目する動作 |

|-------|--------|-------------|

| 読出    | すべて    | ①           |

| 書込    | 1ワード   | ①           |

| 書込    | 2ワード以上 | ①, ②        |

10

## 【0027】

20

表2によれば、データ読み出しでは、ワード数に関係なく先頭転送回路42の出力動作のみが注目される。一方、データ書き込みでは、ワード数が“1”であるとき先頭転送回路42の出力動作のみが注目され、ワード数が“2以上”であるとき先頭転送回路42および書き込み転送回路44の両方の出力動作が注目される。

## 【0028】

20

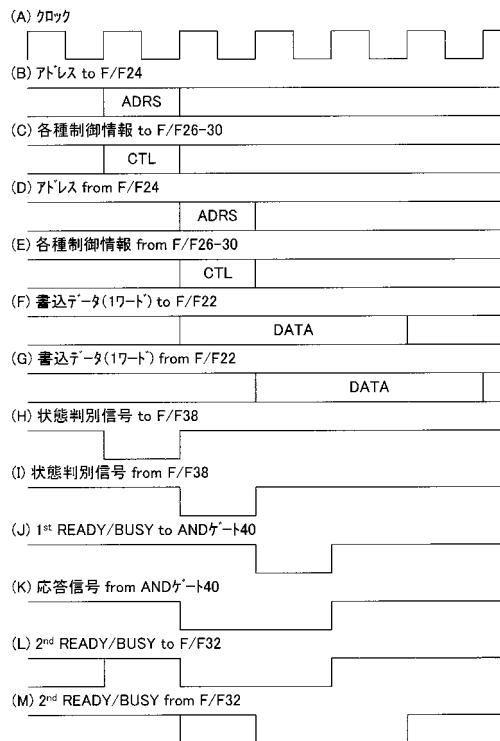

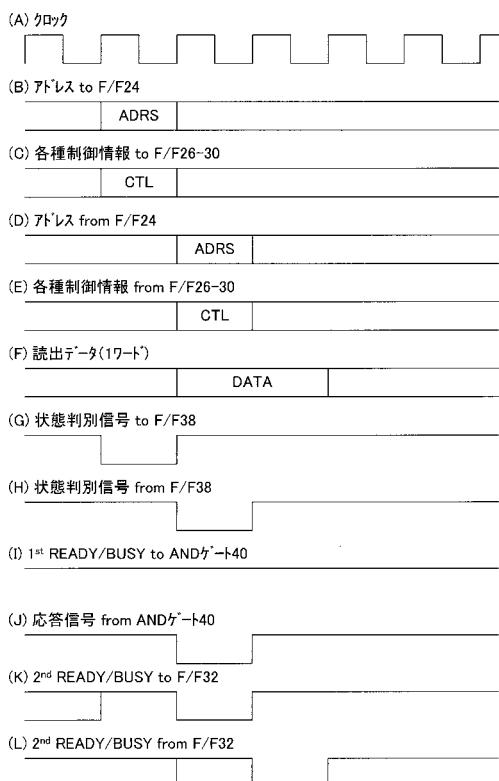

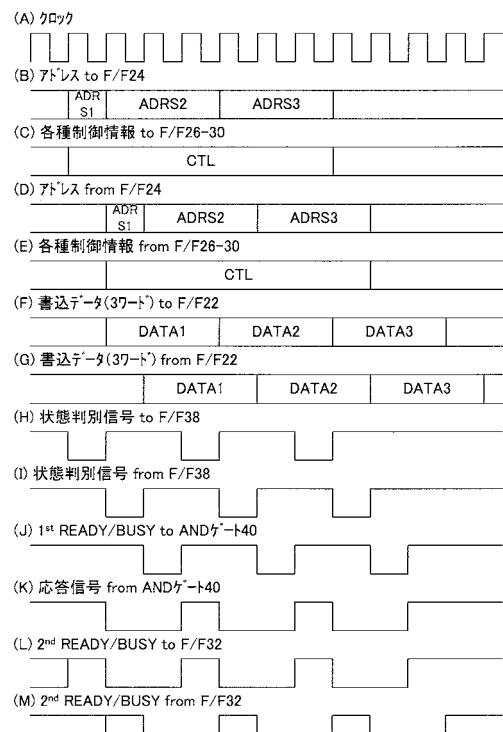

この結果、1ワードのデータ書き込みは図4(A)～図4(M)に示す要領で実行され、1ワードのデータ読み出しは図5(A)～図5(L)に示す要領で実行される。また、3ワードのデータ書き込みは図6(A)～図6(M)に示す要領で実行され、3ワードのデータ読み出しは図7(A)～図7(L)に示す要領で実行される。

## 【0029】

30

図4(A)～図4(M)を参照して、アドレス情報および各種制御情報が図4(B)および図4(C)に示すタイミングでF/F回路24およびF/F回路26～30に与えられ、かつ書き込み対象である1ワードのデータが図4(F)に示すタイミングでF/F回路22に与えられた場合、アドレス情報、各種制御情報および書き込みデータは、図4(A)に示すクロック信号に応答して、図4(D)、図4(E)および図4(G)に示すタイミングでF/F回路24、F/F回路26～30およびF/F回路22から出力される。つまり、プロセッサ12から与えられたアドレス情報、各種制御情報および書き込みデータは、1クロック周期の遅れでI/F14から出力される。

## 【0030】

30

状態判別回路36は、図4(C)に示す各種制御情報に基づいて、図4(H)に示す状態判別信号を作成する。作成された状態判別信号はF/F回路38によって1クロック周期だけ遅延し、F/F回路38からは図4(I)に示すタイミングで状態判別信号が出力される。

40

## 【0031】

メモリ制御回路16は、I/F14から与えられた各種制御情報に基づいて、図4(J)に示す第1レディ/ビジー信号を出力する。ANDゲート40は、図4(I)に示す状態判別信号と図4(J)に示す第1レディ/ビジー信号とに論理積を施し、図4(K)に示す応答信号をプロセッサ12に向けて出力する。

## 【0032】

40

プロセッサ12に設けられたREADY/BUSY発生回路12cは、図4(K)に示す応答信号に基づいて図4(L)に示す第2レディ/ビジー信号を作成する。作成された第2レディ/ビジー信号は、F/F回路32によって1クロック周期だけ遅延される。こ

50

の結果、第2レディ／ビジー信号は、図4(M)に示すタイミングでF/F回路32からメモリ制御回路16に向けて出力される。

#### 【0033】

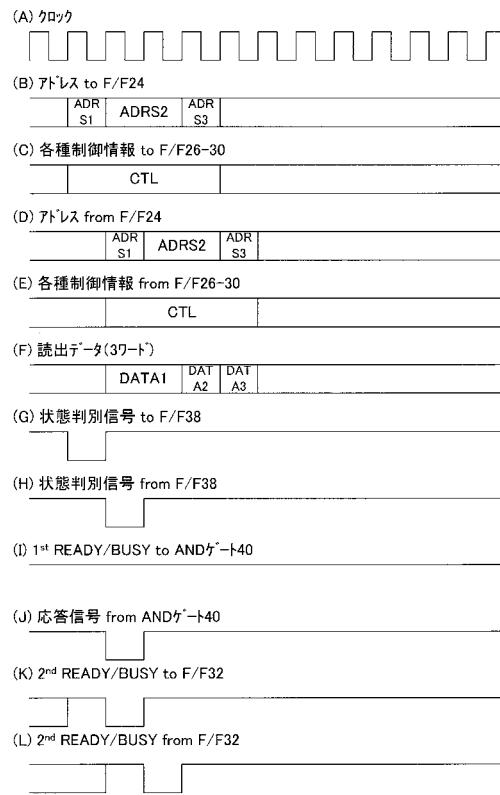

図5(A)～図5(L)を参照して、アドレス情報および各種制御情報が図5(B)および図5(C)に示すタイミングでF/F回路24およびF/F回路26～30に与えられた場合、アドレス情報および各種制御情報は、図5(A)に示すクロック信号に応答して、図5(D)および図5(E)に示すタイミングで(つまり1クロック周期の遅れで)F/F回路24およびF/F回路26～30から出力される。

#### 【0034】

状態判別回路36は、図5(C)に示す各種制御情報に基づいて、図5(G)に示す状態判別信号を作成する。作成された状態判別信号は、F/F回路38によって1クロック周期だけ遅延し、図5(H)に示すタイミングでF/F回路38から出力される。10

#### 【0035】

メモリ制御回路16は、I/F14から与えられた各種制御情報に基づいて、図5(I)に示す第1レディ／ビジー信号を出力する。ANDゲート40は、図5(H)に示す状態判別信号と図5(I)に示す第1レディ／ビジー信号とに論理積を施し、図5(J)に示す応答信号をプロセッサ12に向けて出力する。

#### 【0036】

プロセッサ12のREADY/BUSY発生回路12cは、図5(J)に示す応答信号に基づいて図5(K)に示す第2レディ／ビジー信号を作成する。作成された第2レディ／ビジー信号は、F/F回路32によって1クロック周期だけ遅延され、図5(L)に示すタイミングでメモリ制御回路16に向けて出力される。20

#### 【0037】

図6(A)～図6(M)を参照して、3ワードに対応するアドレス情報および各種制御情報が図6(B)および図6(C)に示すタイミングでF/F回路24およびF/F回路26～30に与えられ、かつ書き込み対象である3ワードのデータが図6(F)に示すタイミングでF/F回路22に与えられた場合、アドレス情報、各種制御情報および書き込みデータは、図6(A)に示すクロック信号に応答して、図6(D), 図6(E)および図6(G)に示すタイミングで(つまり1クロック周期の遅れで)F/F回路24, F/F回路26～30およびF/F回路22から出力される。30

#### 【0038】

状態判別回路36は、図6(C)に示す各種制御情報に基づいて、図6(H)に示すように間欠的に3回立ち下がる状態判別信号を作成する。作成された状態判別信号は、F/F回路38によって1クロック周期だけ遅延し、図6(I)に示すタイミングでF/F回路38から出力される。

#### 【0039】

メモリ制御回路16は、I/F14から与えられた各種制御情報に基づいて、図6(J)に示す第1レディ／ビジー信号を出力する。ANDゲート40は、図6(I)に示す状態判別信号と図6(J)に示す第1レディ／ビジー信号とに論理積を施し、図6(K)に示す応答信号をプロセッサ12に向けて出力する。40

#### 【0040】

READY/BUSY発生回路12cは、図6(K)に示す応答信号に基づいて図6(L)に示す第2レディ／ビジー信号を作成する。作成された第2レディ／ビジー信号は、F/F回路32によって1クロック周期だけ遅延される。この結果、第2レディ／ビジー信号は、図6(M)に示すタイミングでF/F回路32からメモリ制御回路16に向けて出力される。

#### 【0041】

図7(A)～図7(L)を参照して、3ワードに対応するアドレス情報および各種制御情報が図7(B)および図7(C)に示すタイミングでF/F回路24およびF/F回路26～30に与えられた場合、アドレス情報および各種制御情報は、図7(A)に示すク50

ロック信号に応答して、図7(D)および図7(E)に示すタイミングでF/F回路24およびF/F回路26～30から出力される。

#### 【0042】

状態判別回路36は、図7(C)に示す各種制御情報に基づいて、図7(G)に示す状態判別信号を作成する。作成された状態判別信号は、F/F回路38によって1クロック周期だけ遅延し、図7(H)に示すタイミングでF/F回路38から出力される。

#### 【0043】

メモリ制御回路16は、I/F14から与えられた各種制御情報に基づいて、図7(I)に示す第1レディ/ビジー信号を出力する。ANDゲート40は、図7(H)に示す状態判別信号と図7(I)に示す第1レディ/ビジー信号とに論理積を施し、図7(J)に示す応答信号をプロセッサ12に向けて出力する。10

#### 【0044】

READY/BUSY発生回路12cは、図7(J)に示す応答信号に基づいて図7(K)に示す第2レディ/ビジー信号を作成する。作成された第2レディ/ビジー信号は、F/F回路32によって1クロック周期だけ遅延され、図7(L)に示すタイミングでメモリ制御回路16に向けて出力される。

#### 【0045】

以上の説明から分かるように、メモリアクセス装置10は、プロセッサ12とI/F回路14とメモリ制御回路16とを備える。プロセッサ12は、メモリアクセス要求を発行するアクセス要求発生回路12bを備える。I/F回路14は、プロセッサ12から出力されたメモリアクセス要求をクロック信号に応答して保持するF/F回路24～30を備える。メモリ制御回路16は、F/F回路24～30によって保持されたメモリアクセス要求に従うアクセス処理を実行するアクセス処理回路16aを備える。20

#### 【0046】

また、メモリ制御回路16は、アクセス処理回路16aの処理状態を参照して第1レディ/ビジー信号を出力するREADY/BUSY発生回路16bをさらに備える。I/F回路14は、アクセス要求発生回路12bから出力されたメモリアクセス要求とREADY/BUSY発生回路16bから出力された第1レディ/ビジー信号とに基づいて応答信号を作成する応答信号作成回路34をさらに備える。プロセッサ12は応答信号作成回路34によって作成された応答信号に基づいて第2レディ/ビジー信号を出力するREADY/BUSY発生回路12cをさらに備える。30

#### 【0047】

さらに、I/F回路14は、READY/BUSY発生回路から出力された第2レディ/ビジー信号をクロック信号に応答して保持するF/F回路32をさらに備える。アクセス処理回路16aは、F/F回路32によって保持された第2レディ/ビジー信号を参照してアクセス処理を実行する。

#### 【0048】

また、応答信号作成回路34は、F/F回路26～30によって保持されたメモリアクセス要求の状態を判別する状態判別信号を作成する状態判別回路36と、作成された状態判別信号をクロック信号に応答して保持するF/F回路38と、F/F回路38によって保持された状態判別信号とREADY/BUSY発生回路16bから出力された第1レディ/ビジー信号とに論理積を施して応答信号を作成するANDゲート40とを含む。40

#### 【0049】

メモリアクセス要求をクロック信号に応答して保持することで、メモリアクセス要求の転送動作の遅延をクロック信号の周期まで短縮される。これによって、メモリアクセス処理の高速化が図られる。

#### 【0050】

また、メモリアクセス要求と第1レディ/ビジー信号とに基づいて応答信号を作成し、応答信号に基づいて第2レディ/ビジー信号を作成することで、プロセッサ12とメモリ制御回路16との間で連携を確保することができる。50

## 【図面の簡単な説明】

【0051】

【図1】この発明の一実施例の構成を示すブロック図である。

【図2】図1実施例に適用されるI/Fの構成の一例を示すブロック図である。

【図3】図2実施例に適用される状態判別回路の構成の一例を示すブロック図である。

10

【図4】(A)はクロックの出力動作の一例を示すタイミング図であり、(B)はプロセッサからのアドレスの出力動作の一例を示すタイミング図であり、(C)はプロセッサからの各種制御情報の出力動作の一例を示すタイミング図であり、(D)はF/F回路からのアドレスの出力動作の一例を示すタイミング図であり、(E)はF/F回路からの各種制御情報の出力動作の一例を示すタイミング図であり、(F)はプロセッサからの書き込みデータの出力動作の一例を示すタイミング図であり、(G)はF/F回路からの書き込みデータの出力動作の一例を示すタイミング図であり、(H)は状態判別回路からの状態判別信号の出力動作の一例を示すタイミング図であり、(I)はF/F回路からの状態判別信号の出力動作の一例を示すタイミング図であり、(J)はメモリ制御回路からの第1レディ/ビジー信号の出力動作の一例を示すタイミング図であり、(K)はANDゲートからの応答信号の出力動作の一例を示すタイミング図であり、(L)はプロセッサからの第2レディ/ビジー信号の出力動作の一例を示すタイミング図であり、(M)はF/F回路からの第2レディ/ビジー信号の出力動作の一例を示すタイミング図である。

【図5】(A)はクロックの出力動作の一例を示すタイミング図であり、(B)はプロセッサからのアドレスの出力動作の一例を示すタイミング図であり、(C)はプロセッサからの各種制御情報の出力動作の一例を示すタイミング図であり、(D)はF/F回路からのアドレスの出力動作の一例を示すタイミング図であり、(E)はF/F回路からの各種制御情報の出力動作の一例を示すタイミング図であり、(F)はメモリ制御回路からの読み出しデータの出力動作の一例を示すタイミング図であり、(G)は状態判別回路からの状態判別信号の出力動作の一例を示すタイミング図であり、(H)はF/F回路からの状態判別信号の出力動作の一例を示すタイミング図であり、(I)はメモリ制御回路からの第1レディ/ビジー信号の出力動作の一例を示すタイミング図であり、(J)はANDゲートからの応答信号の出力動作の一例を示すタイミング図であり、(K)はプロセッサからの第2レディ/ビジー信号の出力動作の一例を示すタイミング図であり、(L)はF/F回路からの第2レディ/ビジー信号の出力動作の一例を示すタイミング図である。

20

【図6】(A)はクロックの出力動作の他の一例を示すタイミング図であり、(B)はプロセッサからのアドレスの出力動作の他の一例を示すタイミング図であり、(C)はプロセッサからの各種制御情報の出力動作の他の一例を示すタイミング図であり、(D)はF/F回路からのアドレスの出力動作の他の一例を示すタイミング図であり、(E)はF/F回路からの各種制御情報の出力動作の他の一例を示すタイミング図であり、(F)はプロセッサからの書き込みデータの出力動作の他の一例を示すタイミング図であり、(G)はF/F回路からの書き込みデータの出力動作の他の一例を示すタイミング図であり、(H)は状態判別回路からの状態判別信号の出力動作の他の一例を示すタイミング図であり、(I)はF/F回路からの状態判別信号の出力動作の他の一例を示すタイミング図であり、(J)はメモリ制御回路からの第1レディ/ビジー信号の出力動作の他の一例を示すタイミング図であり、(K)はANDゲートからの応答信号の出力動作の他の一例を示すタイミング図であり、(L)はプロセッサからの第2レディ/ビジー信号の出力動作の他の一例を示すタイミング図であり、(M)はF/F回路からの第2レディ/ビジー信号の出力動作の他の一例を示すタイミング図である。

30

【図7】(A)はクロックの出力動作の他の一例を示すタイミング図であり、(B)はプロセッサからのアドレスの出力動作の他の一例を示すタイミング図であり、(C)はプロセッサからの各種制御情報の出力動作の他の一例を示すタイミング図であり、(D)はF/F回路からのアドレスの出力動作の他の一例を示すタイミング図であり、(E)はF/F回路からの各種制御情報の出力動作の他の一例を示すタイミング図であり、(F)はメモリ制御回路からの読み出しデータの出力動作の他の一例を示すタイミング図であり、(

40

50

(G) は状態判別回路からの状態判別信号の出力動作の他の一例を示すタイミング図であり、(H) はF / F回路からの状態判別信号の出力動作の他の一例を示すタイミング図であり、(I) はメモリ制御回路からの第1レディ / ビジー信号の出力動作の他の一例を示すタイミング図であり、(J) はANDゲートからの応答信号の出力動作の他の一例を示すタイミング図であり、(K) はプロセッサからの第2レディ / ビジー信号の出力動作の他の一例を示すタイミング図であり、(L) はF / F回路からの第2レディ / ビジー信号の出力動作の他の一例を示すタイミング図である。

#### 【符号の説明】

##### 【0052】

- 10 ... メモリアクセス装置

- 12 ... プロセッサ

- 14 ... I / F回路

- 16 ... メモリ制御回路

- 18 ... クロック発生器

- 20 ... SDRAM

- 22 ~ 32 ... F / F回路

- 34 ... 応答信号作成回路

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

## 【図7】