(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5725804号

(P5725804)

(45) 発行日 平成27年5月27日(2015.5.27)

(24) 登録日 平成27年4月10日(2015.4.10)

(51) Int.Cl.

H01S 5/183 (2006.01)

F 1

H01S 5/183

請求項の数 8 (全 22 頁)

(21) 出願番号 特願2010-249129 (P2010-249129)

(22) 出願日 平成22年11月5日 (2010.11.5)

(65) 公開番号 特開2012-104522 (P2012-104522A)

(43) 公開日 平成24年5月31日 (2012.5.31)

審査請求日 平成25年10月31日 (2013.10.31)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100094112

弁理士 岡部 譲

(74) 代理人 100096943

弁理士 白井 伸一

(74) 代理人 100101498

弁理士 越智 隆夫

(74) 代理人 100107401

弁理士 高橋 誠一郎

(74) 代理人 100106183

弁理士 吉澤 弘司

(74) 代理人 100128668

弁理士 斎藤 正巳

最終頁に続く

(54) 【発明の名称】面発光レーザ及び面発光レーザアレイ、面発光レーザの製造方法及び面発光レーザアレイの製造方法、面発光レーザアレイを備えた光学機器

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に、下部D B Rと、活性領域と、電流狭窄構造と表面にレリーフ構造とを備えた上部D B Rと、を有し、メサ構造に構成された面発光レーザの製造方法であって、

基板の上に、下部D B Rを形成する工程と、

前記下部D B Rの上に、活性領域を形成する工程と、

前記活性領域の上に、選択酸化層と、前記基板の側から第4の半導体層、第3の半導体層、第2の半導体層の順に積層された層構造と、を有する上部D B Rを形成する工程と、前記上部D B Rの上に第1の半導体層を形成する工程と、

前記第1の半導体層の上に、前記上部D B Rのレリーフ構造の底面となる領域の外周側でかつ、前記第1の半導体層の表面に位置し、電極とのコンタクトを行うためのコンタクト領域を保護する第5の半導体層を形成する工程と、

前記第5の半導体層と前記上部D B Rの表面のレリーフ構造を設ける領域に露出している前記第1の半導体層の上に、前記上部D B Rの表面のレリーフ構造を規定するためのパターンとメサ構造を規定するためのパターンで第1の誘電体膜を形成する工程と、

前記第1の誘電体膜を用い、前記表面のレリーフ構造を規定するためのパターンで前記第1の半導体層をバーニングする工程と、

前記第1の半導体層に形成された前記レリーフ構造を規定するためのパターンに対応した領域の上に、第2の誘電体膜を形成する工程と、

前記第2の誘電体膜の上でかつ、前記レリーフ構造を規定するためのパターンに対応す

10

20

る領域を覆うように、フォトレジストパターンを形成する工程と、

前記フォトレジストパターンを用い、前記メサ構造を規定するためのパターンで前記第5の半導体層と前記第1の半導体層とをドライエッチングし、かつ、前記ドライエッチングにて前記第1の半導体層に形成された前記メサ構造を規定するパターンで前記上部DBRと前記選択酸化層とをドライエッチングして、前記メサ構造を形成する工程と、

前記選択酸化層を選択酸化することにより電流狭窄構造を形成する工程と、

前記第1の誘電体膜及び前記第2の誘電体膜を除去する工程と、

前記レリーフ構造のパターンが形成された前記第1の半導体層をエッティングマスクとし、前記第3の半導体層をエッティングストップ層として、前記第2の半導体層をエッチングし、前記レリーフ構造の底面を露出させる工程と、

10

前記レリーフ構造の底面を露出させる工程の後に、前記第2の半導体層と第3の半導体層をエッティングストップ層として、前記レリーフ構造のパターンが形成された前記第1の半導体層をエッチングし、前記レリーフ構造の上面である前記第2の半導体層の表面を露出させる工程と、

を有し、

前記第5の半導体層が前記第2の半導体層と同一材料で形成され、且つ前記第5の半導体層の厚さが前記第2の半導体層の厚さよりも厚いことを特徴とする面発光レーザの製造方法。

#### 【請求項2】

前記第5の半導体層のエッティングレートをc、層の厚さをvとし、

20

前記第2の半導体層のエッティングレートをd、層の厚さをwとするとき、

$c \times v > d \times w$  の関係を満たすことを特徴とする請求項1に記載の面発光レーザの製造方法。

#### 【請求項3】

前記第4の半導体層の屈折率をn4、前記第3の半導体層の屈折率をn3、前記第2の半導体層の屈折率をn2、前記第1の半導体層の屈折率をn1とするとき、

$n_4 < n_3 < n_2 < n_1$  を満たすことを特徴とする請求項1または2に記載の面発光レーザの製造方法。

#### 【請求項4】

前記レリーフ構造は、凸型の構造であることを特徴とする請求項3に記載の面発光レーザの製造方法。

30

#### 【請求項5】

前記第4の半導体層の屈折率をn4、前記第3の半導体層の屈折率をn3、前記第2の半導体層の屈折率をn2、前記第1の半導体層の屈折率をn1とするとき、

$n_4 > n_3 > n_2 < n_1$  を満たすことを特徴とする請求項1または2に記載の面発光レーザの製造方法。

#### 【請求項6】

前記レリーフ構造は、凹型の構造であることを特徴とする請求項5に記載の面発光レーザの製造方法。

#### 【請求項7】

前記第1の半導体層のエッティングレートをa、層の厚さをxとし、

40

前記第2の半導体層のエッティングレートをb、層の厚さをyとするとき、

$a \times x > b \times y$  の関係を満たすことを特徴とする請求項1乃至6のいずれか1項に記載の面発光レーザの製造方法。

#### 【請求項8】

請求項1乃至7のいずれか1項に記載の面発光レーザの製造方法による面発光レーザを複数個配置して面発光レーザアレイを製造することを特徴とする面発光レーザアレイの製造方法。

#### 【発明の詳細な説明】

#### 【技術分野】

**【0001】**

本発明は、面発光レーザ及び面発光レーザアレイ、面発光レーザの製造方法及び面発光レーザアレイの製造方法、面発光レーザアレイを備えた光学機器に関する。

**【背景技術】****【0002】**

垂直共振器型面発光レーザ(Vertical Cavity Surface Emitting Laser : VCSEL)は、半導体基板の面内方向に対して垂直にレーザ光を出射するものである。

このVCSELは、一般的に基板上に、積層された1対の分布型プラッギ反射鏡(Distributed Bragg Reflector : DBR)に挟まれた領域に活性領域を有する構成となっている。10

この面発光レーザを単一横モードで発振させるために、従来から様々な方法が検討されてきている。

例えば、選択酸化を用いて電流狭窄構造を形成する際に、高次横モードがカットオフとなる大きさまで電流狭窄径を小さくすることで、単一横モードを実現する方法がある。

また、別の例では、VCSELの光出射面に面内に反射率分布を生じさせる構造(以下、表面レリーフ構造と記す。)を設け、高次横モードに対する反射率を低次横モードに対する反射率よりも低くし、高次横モードの発振を抑制する方法がある。

上記表面レリーフ構造を用いる場合、留意すべき事項の一つに、表面レリーフ構造の反射率分布と横モードに関する発振時の光分布との位置を精度よく合わせなければならないという点がある。20

**【0003】**

特許文献1では、このような表面レリーフ構造と光のモードとの位置合わせを簡便な製造プロセスにより実現する提案がなされている。

この特許文献1では、面発光レーザのメサ構造を形成するためのパターンと、表面レリーフ構造を形成するためのパターンとを同一工程で形成している。この方法によれば、メサ構造の中心位置と表面レリーフ構造の中心位置との位置合わせができる。メサ構造の側面から選択酸化することにより電流狭窄構造を形成するため、メサ構造は電流狭窄構造を決定づける。また、電流狭窄構造は横モードの光分布を決定づける。したがって、メサ構造と表面レリーフ構造の位置関係が決まれば、光のモードと表面レリーフ構造の位置関係が決定される。30

また、特許文献1では、表面レリーフ構造の形成を2段階に分けて行い、第2段目のエッチングを行う工程を、電流狭窄構造の形成後に行うことによって、表面レリーフ構造の受けるプロセスダメージを軽減できるようにしている。

これにより、プロセスダメージから表面レリーフ構造の底面の安定形成を実現している。

**【先行技術文献】****【特許文献】****【0004】****【特許文献1】特開2010-40600号公報****【発明の概要】****【発明が解決しようとする課題】****【0005】**

上記のように、特許文献1に記載の製造方法は、十分実用的なプロセスである。

しかしながら、所望の面発光レーザをより精度良く作製するためには、表面レリーフ上面の制御を行う必要がある。

より具体的には、特許文献1では、結晶成長時に形成した最上面が表面レリーフの上面となっている。結晶成長時に形成した最上面は、その後のプロセスにより、表面荒れ、削れ、プラズマダメージ等が生じるため、結晶成長時に形成した面をそのままの状態でデバイス完成時まで保つことが困難であり、設計時とは異なるデバイス特性となるおそれがある。40

特に、この製造工程中に生じるダメージは面内に均一に生じるものではなく、制御することも困難である。

そのため、表面レリーフ上面の状態が素子毎に異なることとなるため、製造したデバイスの特性が面内やウエハ毎にばらついてしまう。

#### 【0006】

そこで、本発明は、上記課題に鑑み、面内やウエハ毎における特性のばらつきを抑制し、単一基本横モードで発振することが可能となる面発光レーザとその製造方法の提供を目的とする。

また、本発明は、上記面発光レーザの製造方法を用いた面発光レーザアレイの製造方法、面発光レーザアレイ、面発光レーザアレイを備えた光学機器の提供を目的とする。 10

#### 【課題を解決するための手段】

#### 【0007】

本発明の面発光レーザの製造方法は、基板上に、下部D B Rと、活性領域と、電流狭窄構造と表面にレリーフ構造とを備えた上部D B Rと、を有し、メサ構造に構成された面発光レーザの製造方法であって、

基板の上に、下部D B Rを形成する工程と、

前記下部D B Rの上に、活性領域を形成する工程と、

前記活性領域の上に、選択酸化層と、前記基板の側から第4の半導体層、第3の半導体層、第2の半導体層の順に積層された層構造と、を有する上部D B Rを形成する工程と、前記上部D B Rの上に第1の半導体層を形成する工程と、 20

前記第1の半導体層の上に、前記上部D B Rのレリーフ構造の底面となる領域の外周側でかつ、前記第1の半導体層の表面に位置し、電極とのコンタクトを行うためのコンタクト領域を保護する第5の半導体層を形成する工程と、

前記第5の半導体層と前記上部D B Rの表面のレリーフ構造を設ける領域に露出している前記第1の半導体層の上に、前記上部D B Rの表面のレリーフ構造を規定するためのパターンとメサ構造を規定するためのパターンで第1の誘電体膜を形成する工程と、

前記第1の誘電体膜を用い、前記表面のレリーフ構造を規定するためのパターンで前記第1の半導体層をパターニングする工程と、

前記第1の半導体層に形成された前記レリーフ構造を規定するためのパターンに対応した領域の上に、第2の誘電体膜を形成する工程と、 30

前記第2の誘電体膜の上でかつ、前記レリーフ構造を規定するためのパターンに対応する領域を覆うように、フォトレジストパターンを形成する工程と、

前記フォトレジストパターンを用い、前記メサ構造を規定するためのパターンで前記第5の半導体層と前記第1の半導体層とをドライエッチングし、かつ、前記ドライエッチングにて前記第1の半導体層に形成された前記メサ構造を規定するパターンで前記上部D B Rと前記選択酸化層とをドライエッチングして、前記メサ構造を形成する工程と、

前記選択酸化層を選択酸化することにより電流狭窄構造を形成する工程と、

前記第1の誘電体膜及び前記第2の誘電体膜を除去する工程と、

前記レリーフ構造のパターンが形成された前記第1の半導体層をエッチングマスクとし、前記第3の半導体層をエッチングストップ層として、前記第2の半導体層をエッチングし、前記レリーフ構造の底面を露出させる工程と、 40

前記レリーフ構造の底面を露出させる工程の後に、前記第2の半導体層と第3の半導体層をエッチングストップ層として、前記レリーフ構造のパターンが形成された前記第1の半導体層をエッチングし、前記レリーフ構造の上面である前記第2の半導体層の表面を露出させる工程と、

を有し、

前記第5の半導体層が前記第2の半導体層と同一材料で形成され、且つ前記第5の半導体層の厚さが前記第2の半導体層の厚さよりも厚いことを特徴とする。

また、本発明の面発光レーザアレイの製造方法は、上記した面発光レーザの製造方法による面発光レーザを複数個配置して面発光レーザアレイを製造することを特徴とする。 50

**【発明の効果】****【0008】**

本発明によれば、面内やウエハ毎における特性のばらつきを抑制し、単一基本横モードで発振することが可能となる面発光レーザとその製造方法の提供を実現する。

また、本発明は、上記面発光レーザの製造方法を用いた面発光レーザアレイの製造方法、面発光レーザアレイ、面発光レーザアレイを備えた光学機器を実現する。

**【図面の簡単な説明】****【0009】**

【図1】本発明の実施例1における面発光レーザの構成を示す断面図。

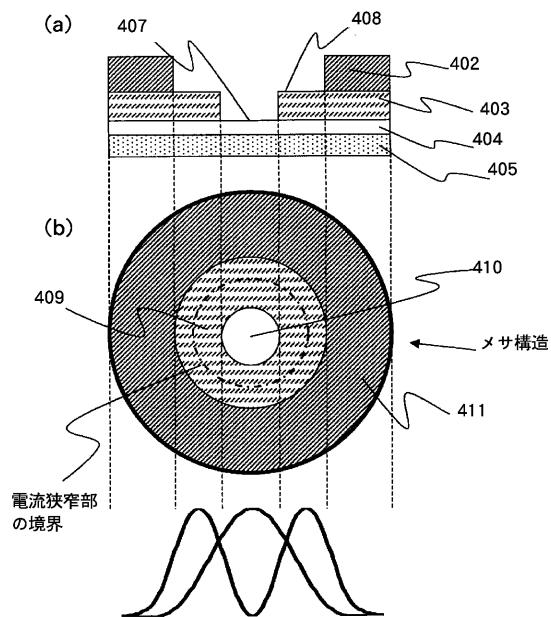

【図2】本発明の実施例1における面発光レーザの表面レリーフ構造を説明する図。 10

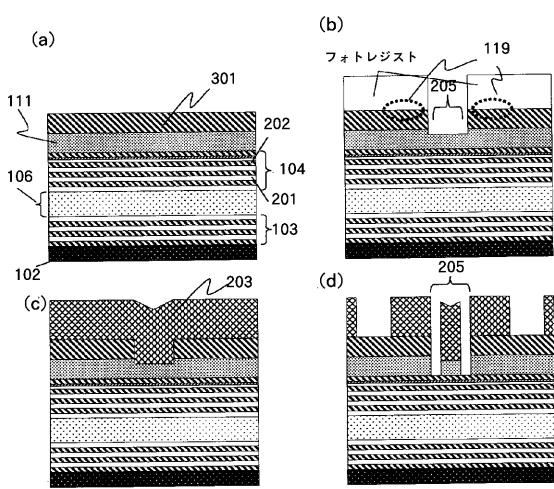

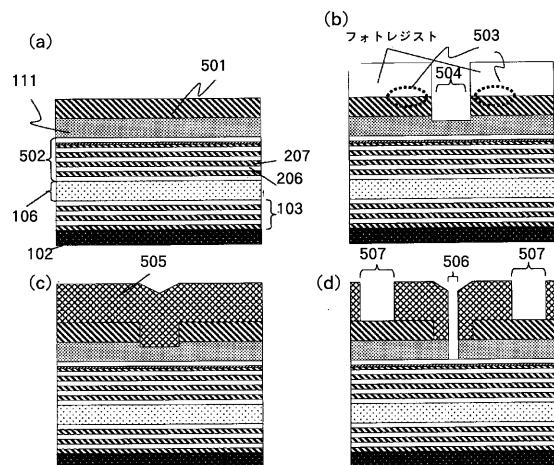

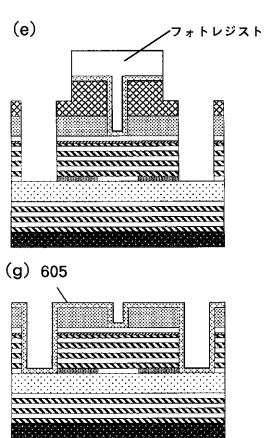

【図3】本発明の実施例1における表面レリーフ構造を有する面発光レーザの製造方法の(a)～(d)の工程を説明する工程図。

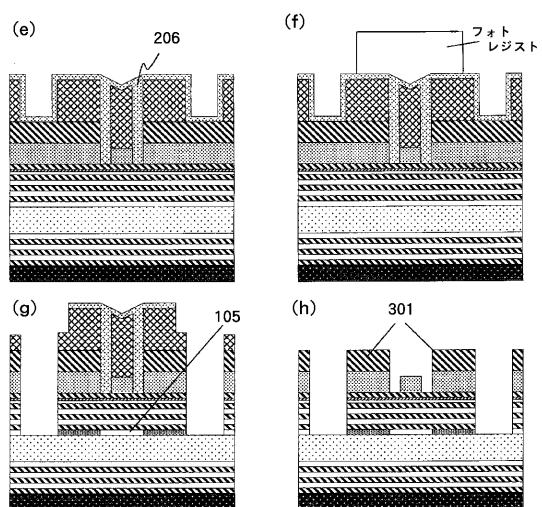

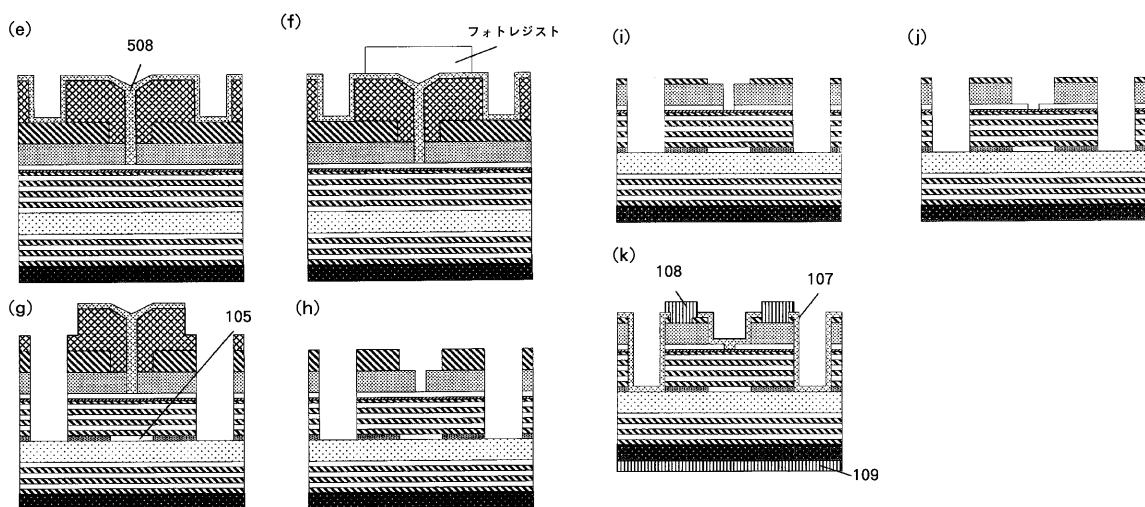

【図4】本発明の実施例1における表面レリーフ構造を有する面発光レーザの製造方法を説明する図3(a)～(d)に続く(e)～(h)の工程を示す工程図。

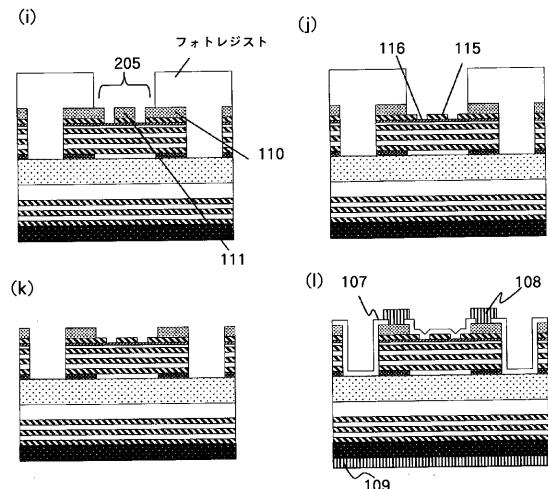

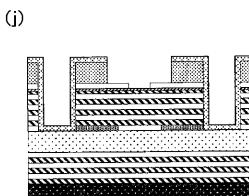

【図5】本発明の実施例1における表面レリーフ構造を有する面発光レーザの製造方法を説明する図4(e)～(h)に続く(i)～(l)の工程を示す工程図。

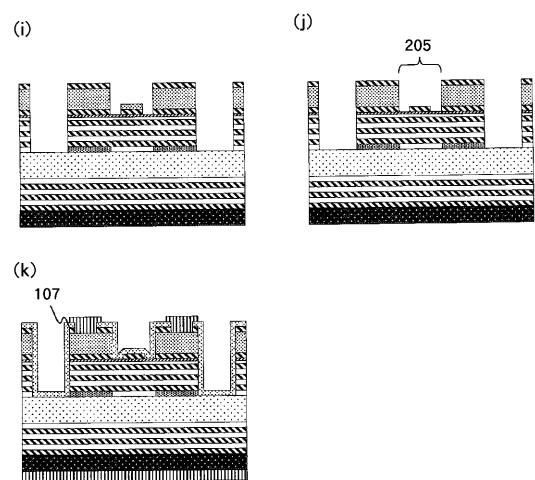

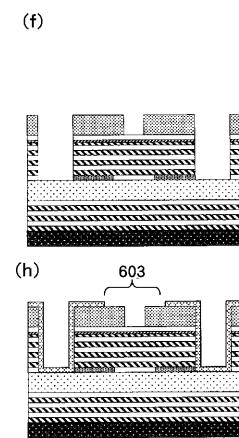

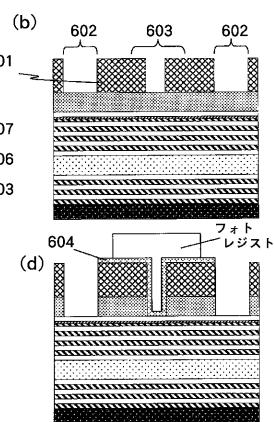

【図6】本発明の実施例2における表面レリーフ構造を有する面発光レーザの製造方法の(a)～(d)の工程を説明する工程図。

【図7】本発明の実施例2における表面レリーフ構造を有する面発光レーザの製造方法を説明する図6(a)～(d)に続く(e)～(h)の工程を示す工程図。 20

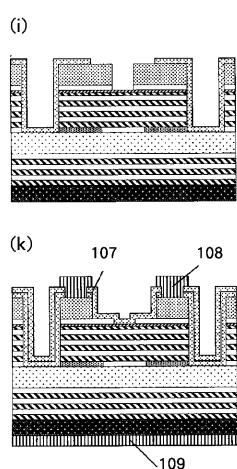

【図8】本発明の実施例2における表面レリーフ構造を有する面発光レーザの製造方法を説明する図7(e)～(h)に続く(i)～(k)の工程を示す工程図。

【図9】本発明の実施例3における面発光レーザの表面レリーフ構造を説明する図。

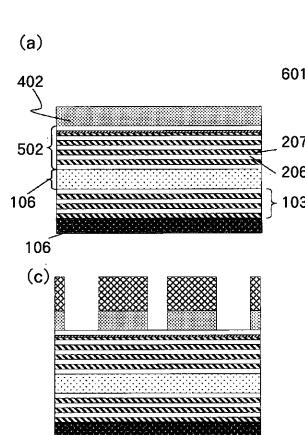

【図10】本発明の実施例3における表面レリーフ構造を有する面発光レーザの製造方法の(a)～(d)の工程を説明する工程図。

【図11】本発明の実施例3における表面レリーフ構造を有する面発光レーザの製造方法を説明する図10(a)～(d)に続く(e)～(h)の工程を示す工程図。

【図12】本発明の実施例3における表面レリーフ構造を有する面発光レーザの製造方法を説明する図11(e)～(h)に続く(i)～(k)の工程を示す工程図。

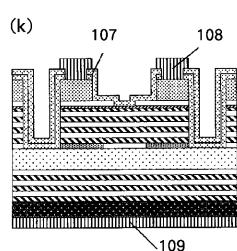

【図13】本発明の実施例4における表面レリーフ構造を有する面発光レーザの製造方法の(a)～(d)の工程を説明する工程図。 30

【図14】本発明の実施例4における表面レリーフ構造を有する面発光レーザの製造方法を説明する図13(a)～(d)に続く(e)～(h)の工程を示す工程図。

【図15】本発明の実施例4における表面レリーフ構造を有する面発光レーザの製造方法を説明する図14(e)～(h)に続く(i)～(k)の工程を示す工程図。

【図16】本発明の実施例5における垂直共振器型面発光レーザアレイを実装した電子写真記録方式の画像形成装置の構造図。

**【発明を実施するための形態】****【0010】**

本発明によれば、面発光レーザの上部DBRの光出射部に反射率分布を制御するために施された段差構造による表面レリーフ構造を作製するに際し、 40

特に、表面レリーフ構造の表面として、結晶成長時に形成した異種材料間の界面を利用し、安定的に形成することが可能となる。

これまで結晶成長時の界面を安定的に形成できなかった理由は、上記したとおりであり、これらの理由から表面レリーフの上面と底面を、ダメージが生じる工程の後に形成する必要がある。

しかし、従来のセルファアラインによる場合には、一連の工程の最初にパターニングを行うことが必要となる。

したがって、このようなセルファアラインによることは、ダメージが生じるプロセスの後に表面レリーフ表面を形成する必要性と相反している。 50

## 【0011】

このようなことから、本発明ではダメージが生じた後に表面レリーフの表面を形成する方法を見出した。

特許文献1のセルフアラインでのV C S E L 製造工程においてダメージが生じる工程としては、主にセルフアラインでの表面レリーフとメサ形成を同時に行うために必要な誘電体膜の成膜、

及び、その除去、メサ形成時に用いるフォトレジストの除去、及び、全工程におけるフォトレジスト除去時のアッシング工程が挙げられる。

さらに、表面レリーフ底面形成時に、表面レリーフ底面の形成時のエッチャントが、表面レリーフ上面へダメージを与える。

これらの工程中に、表面レリーフを構成する界面（上面および底面）を露出させずに終了させることが、本発明における製造方法の特徴である。

具体的には、表面レリーフ上面をコンタクト層を兼ねる第1の半導体層で、表面レリーフ底面を第2の半導体層で保護しながら、ダメージが生じる工程を経た後に選択エッチングにより表面レリーフ上面及び底面を露出させる工程として、上記課題を解決した。

## 【実施例】

## 【0012】

以下に、本発明の実施例について説明する。

## [実施例1]

実施例1として、本発明を適用した凸型の表面レリーフ構造を有する面発光レーザ及びその製造方法について説明する。

本実施例の面発光レーザは、基板上に、下部D B R、活性領域、上部D B R、コンタクト部を含む複数の半導体層が積層され、上部D B Rの光出射部に反射率分布を制御するために施された段差構造による表面レリーフ構造を備え、メサ構造に構成されている。

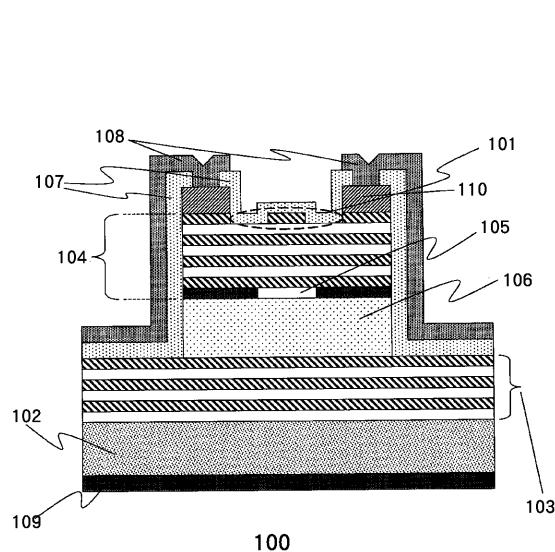

具体的には図1の構造を備える。図1において、100は面発光レーザ、101は表面レリーフ構造、102は基板、103は下部D B R、104は上部D B Rである。

また、105は電流狭窄部、106は活性領域、107は絶縁膜、108は上部電極、109は下部電極である。

この面発光レーザ100は、円柱状のメサ構造となっている。

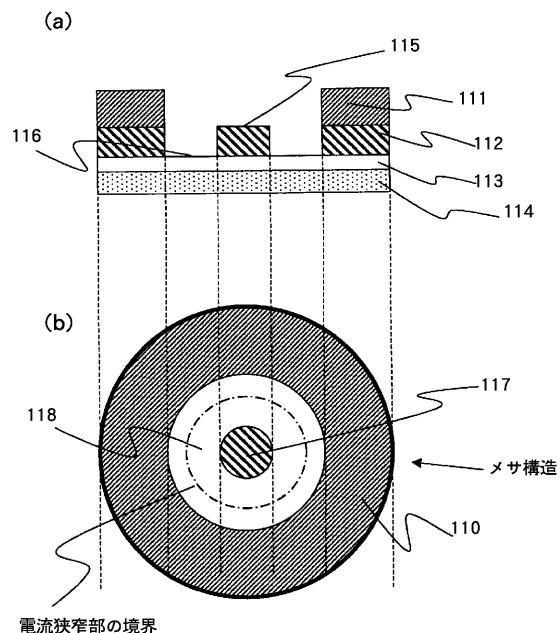

図2(a)、(b)を用いて、表面レリーフ構造101について説明する。

図2(a)は表面レリーフ構造の断面図、図2(b)は上から見た平面図である。

表面レリーフ構造101では、凸型の構造が第2の半導体層112によって形成されている。以後、この凸型構造の表面を表面レリーフ上面115と記す。

また、凸型構造の周囲は、第2の半導体層112が取り除かれ、第3の半導体層113が露出している。以後、この露出している面を表面レリーフ底面116と記す。

本実施例では、表面レリーフ上面115が高い反射率を有する高反射領域117となり、表面レリーフ底面116が低い反射率を有する低反射領域118となるようにウエハが設計されている。

高反射領域117は、電流狭窄部に対して面内の位置が制御されて形成されている。また、表面レリーフ底面116の周囲に、電流を電極から流すために必要な層のコンタクト部110が第1の半導体層111によって形成されている。

## 【0013】

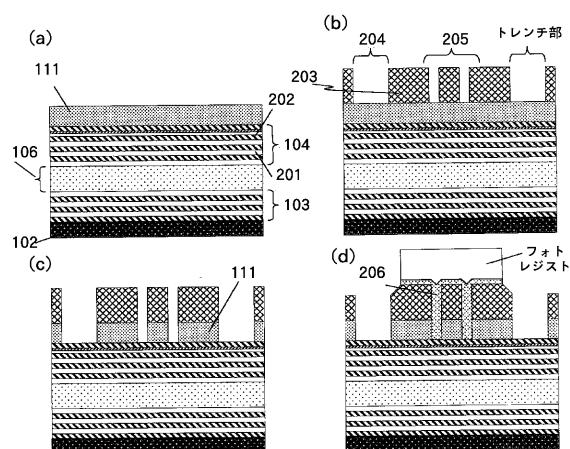

つぎに、本実施例における表面レリーフ構造を有する面発光レーザの製造方法について、図3(a)～図5(1)を用いて説明する。

V C S E L用ウエハとして、基板102上に下部D B R103、活性領域106、上部D B R104、コンタクト層となる第1の半導体層111の順番で積層構造を形成する。

このとき、コンタクト層は上部D B R104の一部とならないように設計する。具体的には、上部D B R104は、V C S E Lの発振波長をλとし、半導体層の屈折率をnとするとき、λ/4nの膜厚で交互に積層された構造体によって構成されている。

以下、このD B Rを構成する層において、屈折率が低い層を低屈折率層201、高い層を

10

20

30

40

50

高屈折率層 202 と記す。

低屈折率層 201 と高屈折率層 201 の 2 層を 1 ペアとし、設計に応じて適した反射率となるように複数ペア積層する。

また、電流狭窄構造を選択酸化によって形成するために、複数の低屈折率層 201 の内、少なくとも 1 層を選択酸化層 207 として選択酸化が可能な Al<sub>x</sub>Ga<sub>1-x</sub>As ( $x > 0.85$ ) と置き換える必要がある。

さらに、選択酸化層は他の DBR の層よりも選択酸化による酸化速度が速い必要がある。本実施例で使用する Al<sub>0.9</sub>Ga<sub>0.1</sub>As / Al<sub>0.5</sub>Ga<sub>0.5</sub>As の DBR に選択酸化層を導入する場合は、Al<sub>0.9</sub>Ga<sub>0.1</sub>As よりも酸化速度の速い材料、例えば、Al<sub>0.98</sub>Ga<sub>0.02</sub>As を用いる必要がある。

10

#### 【0014】

本実施例において、上部 DBR は上記構造体中に、基板側から第 4 の半導体層、第 3 の半導体層、第 2 の半導体層の順に積層されてなる層構造を備える。

そして、前記面発光レーザの発振波長を  $\lambda$  とし、前記各半導体層の屈折率を  $n$  とするとき、第 2 から第 4 の半導体層による層の合計厚さが  $\lambda / 2n$  の整数倍の厚さで形成されている。

また、前記第 4 の半導体層の屈折率を  $n_4$ 、前記第 3 の半導体層の屈折率を  $n_3$ 、前記第 2 の半導体層の屈折率を  $n_2$  とし、後述する第 1 の半導体層の屈折率を  $n_1$  とするとき、屈折率が  $n_4 < n_3 < n_2 < n_1$  を満たす関係とされ、 $n_2$  と  $n_1$  の界面で反射率が最大となるようにされている。

20

具体的には、上部 DBR は最後の 3 層がつぎのように形成されている。

上部 DBR の上にコンタクト層として第 1 の半導体層 111 が形成されるが、このコンタクト層側から上部 DBR の最後の 3 層を、第 2 の半導体層 112、第 3 の半導体層 113、第 4 の半導体層 114 とする。

この第 2 の半導体層 112 は、高屈折率層 207 と同一材料、第 4 の半導体層 114 は低屈折率層 206 と同一材料で構成される。

また、第 3 の半導体層 113 は、第 2 の半導体層 112 をエッティングする際にエッチングストップとして機能する材料で構成され、且つ、第 2 の半導体層 112 と第 4 の半導体層 114 の中間の屈折率を有することが望まれる。

本実施例での上部 DBR は最終の面で最も高い反射率を有するように設計する。そのため、上部 DBR の最終層は高屈折率層で終了していることが望ましい。

30

上部 DBR 最後の 3 層がその下に積層された DBR との整合を保つために、第 2 の半導体層 112、第 3 の半導体層 113、第 4 の半導体層 114 の 3 層の合計膜厚が  $\lambda / 2n$  の厚さとなることが好ましい。

例えば、第 2 の半導体層 112 の厚さを  $\lambda / 4n$  の厚さとすると、第 3 の半導体層 113 と第 4 の半導体層 114 の合計厚さが  $\lambda / 4n$  となる。

このような厚さとすることで、表面レリーフ底面 116 が最も反射率が低く、表面レリーフ上面 115 が最も反射率が高くなり、反射率差が最大となる。

そのため、高次モードを最も強く抑制することが可能となる。ここでは、 $\lambda / 4n$  として説明しているが、 $\lambda / 4n$  の奇数倍の厚さであれば同様の効果を得ることができる。

40

#### 【0015】

また、別の例として、第 2 の半導体層 112 の厚さを  $\lambda / 8n$  とし、第 3、第 4 の半導体層の合計厚さが  $3 \times \lambda / 8n$  の厚さとなるようにしても良い。

この例では、表面レリーフ上面 115 と底面での反射率差が小さくなるが、全体的に反射率が高くなり閾値電流値を低く抑えることができる。

例えば、電流狭窄部の非酸化領域が小さい場合表面レリーフ構造が無い面発光レーザであっても多少基本横モードで発振可能な注入電流領域がある。

このような面発光レーザに表面レリーフ構造を付加すると、高次モードへの抑制効果が小さくても、注入電流領域全体を单一基本横モードで発振可能とすることができる。

さらに、全体的な反射率の低下を抑えることができ、閾値電流値の上昇を抑えることが可

50

能となり、面発光レーザとしては、より好ましい特性を得ることができる。

このように、半導体層の厚さ、つまり表面レリーフ構造の上面から底面までの高さは、面発光レーザの設計によって、好ましい値が変わることがあるため、面発光レーザの設計や用途に応じて決定することができる。

#### 【0016】

面発光レーザに用いる具体的な材料として、本実施例では例えば、活性領域に赤色で発光する材料を設けた場合を考える。

上部及び下部DBRとしては赤色に吸収を持たない材料で構成されることが一般的であり、例えば、Al組成xが0.4より大きいAl<sub>x</sub>Ga<sub>1-x</sub>Asを用いる。

この材料でDBRを構成すると、低屈折率層にはAl<sub>0.9</sub>Ga<sub>0.1</sub>As、高屈折率層にはAl<sub>0.5</sub>Ga<sub>0.5</sub>Asなどが用いられる。

10

ここで挙げた材料は、上部及び下部DBRを構成する材料の一例でありこの材料に限つたものではない。

赤色の面発光レーザにおいても、Al<sub>0.4</sub>Ga<sub>0.6</sub>AsとAl<sub>0.8</sub>Ga<sub>0.2</sub>Asの組合せ等、屈折率が異なる材料の組合せで構成されても良い。これにより、DBRの屈折率差を確保しながら、選択酸化時の選択性が上がる。また赤外の面発光レーザでは、Al<sub>0.1</sub>Ga<sub>0.9</sub>AsとAlAsの組合せのように、より屈折率差が大きい材料の組合せを用いることができ、所望の反射率を得るために積層する層数を少なくすることが可能となる。

また、上部DBRと下部DBRをそれぞれ異なる材料構成としても良い。

#### 【0017】

20

その後、第1の半導体層形成工程において、上部DBR108の各層よりも屈折率の高いコンタクト層として第1の半導体層111を、上部DBR上に成長させる。

第1の半導体層111であるコンタクト層としては、一般に金属との接触抵抗を低く抑えられ、且つ、空気中でも材料の変質の少ないGaAsが用いられる。本実施例においてもGaAsを用いる。

これらの層構成は、GaAs基板上に、MOCVD(Metal-Organic Chemical Vaper Deposition:有機金属化学気相成長法)や、

MBE(Molecular Beam Epitaxy:分子線エピタキシー)などを用いて結晶成長を行い形成する(図3(a))。

次に、第1の誘電体膜形成工程において上記のように結晶成長を行ったウエハ上(第1の半導体層上)に、エッチングマスクとして第1の誘電体膜を形成する。この第1の誘電体膜203に、表面レリーフ構造部205とメサ構造を規定するためのトレンチ部204のエッチングパターンを、同一フォトマスクで一括にフォトリソグラフィーとウェットエッチングによって、第1の誘電体膜203にパターンを形成する。そして、フォトレジストを除去する(図3(b))。

この第1の誘電体膜203は、本実施例ではSiO<sub>2</sub>を用いる。その他にも、SiNやSiONなど通常半導体デバイス製造に用いられる誘電体を用いることができる。

#### 【0018】

この表面レリーフ構造部205は、例えば内径が4μm、外径が9μmの円周状の溝をエッチングすることによって形成できる。

40

このとき4μmの直径を有する第1の誘電体膜203のポストが形成される。また、同一マスクで形成するメサ構造を決定するトレンチ部204は、例えば、内径27μm、外形40μmの溝をエッチングすることによって形成できる。

このとき、27μmの直径を有する第1の誘電体膜203のポストが形成される。

このトレンチ部204を形成したポスト内に同心円状に、前述の表面レリーフ構造のための溝のパターンを形成されることにより、表面レリーフ構造とメサ構造の面内の相対位置が一意に決まる。

ここで挙げた表面レリーフ構造の大きさは、一例であり異なる大きさであっても良い。

この大きさは、電流狭窄部105の大きさとの関係や、上述した表面レリーフ構造の高さから決定される。

50

さらに、高次モードの抑制を強くしたい場合は、第2の半導体層の径は小さく、抑制を弱くしたい場合は径を大きくするなど、面発光レーザに要求される特性からも、表面レリーフ構造の径が決定されることもある。

例えば、電流注入領域の一部を単一横モード化したい要求に対しては、第2の半導体層の径を大きくするなどが考えられる。

第1の誘電体膜203のパターニング後に、ウェットエッティングによって、第1の半導体層111のGaAsをエッティングし、GaAs下の第2の半導体層112が残るようにエッティングを制御する。

このとき、第2の半導体層112がAlを含有したAlGaAsである場合、クエン酸系水溶液のエッチャントを用いれば、 $Al_yGa_{1-y}As$  ( $y > 0$ ) がエッティングストップ層として働く。これにより、第2の半導体層112をエッティングせずにGaAsを取り去ることが可能となる。10

この時のクエン酸系のエッチャントには、例えば、クエン酸1水和物と水を重量比で1:1で混合したものとし、A : 過酸化水素水 : 水 = 2 : 60 : 250 の体積比で混合した水溶液をエッチャントとして用いることができる。

本発明者らの実験によると、このエッチャントはGaAsが2nm/秒以上、 $Al_{0.5}Ga_{0.5}As$ では0.1nm/秒未満のエッティングレートを有していることが確認されている。

両材料でのエッティング選択比が20以上あり、 $Al_{0.5}Ga_{0.5}As$ がエッティングストップとして働き、高屈折率層の $Al_{0.5}Ga_{0.5}As$ が、残ったエッティングが実現できる(図3(c))。20

#### 【0019】

次に、ウエハ全体に更に第2の誘電体膜206を形成する。その後、表面レリーフ部を覆うようにフォトリソグラフィーによりフォトレジストパターンを形成し、ウェットエッティングを行い、トレンチ部204に形成された第2の誘電体膜206を除去する。

このトレンチ部204の第2の誘電体膜206を除去する際に、セルファアラインでパターニングされた第1の誘電体膜203が除去されないように、第1の誘電体膜203の厚さは、第2の誘電体膜206の厚さよりも十分に厚いことが望まれる(図3d))。

第2の誘電体膜206は、第1の誘電体膜203と同じでも異なる材料でも良いが、同一エッチャントでエッティングできる材料であれば、後の誘電体膜除去工程を同一とすることができ工程の減少が期待できる。30

例えば、第1の誘電体膜203にSiO<sub>2</sub>を用いた場合、同じくSiO<sub>2</sub>を用いることもできる。また、SiONやSiNも同様に使用することが可能となる。

これらの材料の場合、エッチャントとしてバッファードフッ酸を用いることができる。

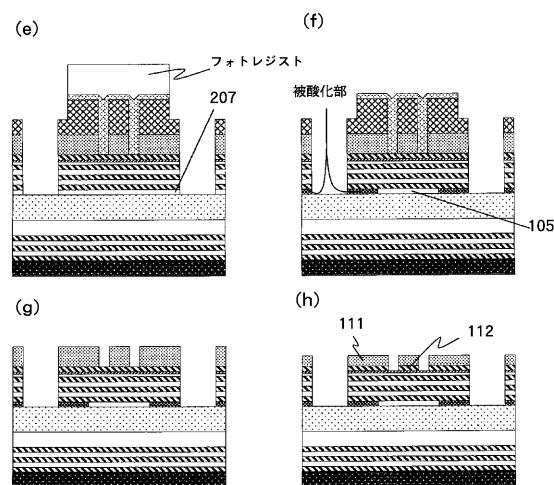

その後、ドライエッティングを行いトレンチ部204の上部DBRを選択酸化層207が露出するまでエッティングし、メサ構造を形成する(図4(e))。

例えば、ドライエッティングではGaAs系材料をエッティングする場合、SiCl<sub>4</sub>とArの混合ガスを用いたリアクティブイオンエッティング(RIE)などを用いることができる。40

#### 【0020】

次に、フォトレジストを酸素プラズマにてアッシングを行い取り除く。

このときに、第2の誘電体があることにより表面レリーフ構造部において露出している第2の半導体層112にダメージが入ることを抑制している。

この第2の誘電体膜206が無くても、酸素プラズマのアッシングの時間や強度によりDBR最上層が取り除かれない場合もあるが、工程の面内分布やマージンを考慮すると第2の誘電体膜206はあったほうが望ましい。

次に、ドライエッティングにより露出した選択酸化層207をメサ側壁から選択酸化することで、電流狭窄部105を形成する(図4(f))。

この選択酸化では、例えば400℃に熱した炉にウエハを配置し、30分間水蒸気を導入することによって行う。50

このような高温化では、G a A s や A l G a A s から砒素原子が抜けることによってダメージが生じることがある。そのため、選択酸化時に誘電体膜で半導体表面を覆っていることは重要である。

この選択酸化の工程において、選択酸化を行う距離を 1 0 . 7 5 μ m とすると、メサ構造が図 3 ( b ) の工程において 2 7 μ m の直径にて形成されているため、電流狭窄部 1 0 5 の径は 5 . 5 μ m となる。

#### 【 0 0 2 1 】

次に、第 1 の誘電体膜 2 0 3 、及び、第 2 の誘電体膜 2 0 6 を除去する（図 4 ( g ) ）。

例えば、誘電体膜が S i O や S i O N , S i N であった場合、バッファードフッ酸をエッチャントとして用いることができる。

10

また、D B R が A l G a A s で構成されている場合、バッファードフッ酸を用いると、D B R 側壁からエッチングされてしまい、メサが崩れることがある。

このような場合は、フォトレジストにて D B R 側壁を保護してから、誘電体膜のエッチングを行っても良い。

次に、コンタクト層である第 1 の半導体層 1 1 1 をエッチングマスクとして D B R 最上層の第 2 の半導体層 1 1 2 をエッチングし、表面レリーフ構造の底面を露出させる（図 4 ( h ) ）。

このとき、コンタクト層と第 2 の半導体層 1 1 2 とでエッチングの選択比が大きく取れるエッチャントでエッチングすることが好ましいが、第 2 の半導体層 1 1 2 をエッチングする時間でコンタクト層が全て取り除かれなければ、それに限ったものではない。

20

例えば、ここではエッチャントにリン酸系水溶液のエッチャントが使用できる。本発明者らの実験によると、リン酸（含量 8 5 % ）：過酸化水素水：水 = 4 : 1 : 9 0 の体積比で混合したリン酸水溶液を用いた場合、G a A s は、0 . 6 n m / 秒、A l <sub>0 . 5</sub> G a <sub>0 . 5</sub> A s は 1 . 1 n m / 秒のエッチングレートであった。

このエッチャントを使用した場合、G a A s と A l G a A s とでは、大きなエッチング選択比を取ることができないが、コンタクト層の G a A s を例えば、2 0 0 n m の厚さで積層する。

また、V C S E L が赤色の 6 8 0 n m で発振し、第 2 の半導体層 1 1 2 の高屈折率層 2 0 7 が A l <sub>0 . 5</sub> G a <sub>0 . 5</sub> A s である場合、第 2 の半導体層 1 1 2 は屈折率が約 3 . 4 6 となり、/ 4 n の厚さが約 4 9 . 1 n m となる。

30

この第 2 の半導体層 1 1 2 を上述のエッチャントでエッチングする場合、4 4 . 6 秒のエッチング時間が必要となるが、G a A s がエッチングされる厚さは 2 6 . 7 n m となる。エッチング及び高屈折率層 2 0 7 の厚さに面内分布があることを想定し、2 0 秒ほど多くエッチングしたとしても、G a A s のエッチングされる厚さは、約 3 9 n m となり G a A s が全て取り除かれることは無い。

このようにコンタクト層の G a A s を厚く積層することで、エッチングの選択比が大きく取れない場合でも、この工程は実現できる。

このとき、第 3 の半導体層 1 1 3 をエッチングストップ層として第 2 の半導体層 1 1 2 のエッチングが止まるエッチャントを使う必要がある。

40

上記エッチャントを使用する場合、エッチングストップ層として第 3 の半導体層 1 1 3 が機能するには、A l G a I n P 、具体的には ( A l <sub>0 . 5</sub> G a <sub>0 . 5</sub> ) <sub>0 . 5</sub> I n <sub>0 . 5</sub> P などの材料が使用できる。

#### 【 0 0 2 2 】

その後、フォトリソグラフィーによりコンタクト部 1 1 0 となる表面レリーフ底面 1 1 6 の外周側（表面レリーフ構造の上面と反対側）にあるコンタクト部を保護し、表面レリーフ構造 2 0 5 が露出するようにフォトレジストパターンを形成する（図 5 ( i ) ）。

次に、このフォトレジストパターンをマスクに表面レリーフ構造のコンタクト部（第 1 の半導体層）をエッチングし、表面レリーフ構造の上面を露出させる（図 5 ( j ) ）。

これらにより、第 2 の半導体層 1 1 2 、及び、第 3 の半導体層 1 1 3 がエッチングストップ層となる（図 5 ( k ) ）。

これにより、第 2 の半導体層 1 1 2 、及び、第 3 の半導体層 1 1 3 がエッチングストップ層となる（図 5 ( k ) ）。

10

20

30

40

50

として機能するエッチャントを用いることで、表面レリーフ構造の上面、底面ともに結晶成長時に規定した界面で形成可能となる。

以上により、表面レリーフ構造の上面・底面ともに結晶成長時に規定した界面で形成でき、製造工程に生じる表面荒れ・削れ・ダメージによる表面レリーフ構造の製造不安定性を排除できる。

なお、本実施例においては、前記第1の半導体層のエッチングレートをa、層の厚さをxとし、前記第2の半導体層のエッチングレートをb、層の厚さをyとするとき、 $a \times x > b \times y$ の関係を満たすことで、第1の半導体がエッチングされない構成を探ることができる。

また、本実施例においては、前記コンタクト部を保護を、表面レリーフ構造の上面を露出させる工程の直前に実施するようにしてもよいし、表面レリーフ構造の底面を露出させる工程の直前に実施しするようにしてもよい。10

#### 【0023】

その後、フォトレジストを除去し(図5(k))、ウエハ全面を絶縁層で覆い、コンタクト部110の一部を電極取り出しのため絶縁膜を取り除き、金属を蒸着し、基板裏面にも金属を蒸着することでデバイスが完成する(図5(l))。この絶縁膜は、表面レリーフ構造も覆うため、面発光レーザの反射率を変化させないために、 $/2n$ (nは材料の屈折率)の厚さで形成することが望ましい。例えば、絶縁膜が屈折率1.54のSiOの場合、680nmの赤色で発振するとき $/2n$ の厚さは、約220nmの厚さとなる。絶縁膜として、その他にもSiO<sub>2</sub>やSiON、SiNなど、通常半導体デバイスに絶縁膜として使用する材料を使用することができる。20

本実施例のSiOを用いる場合は、エッチャントとしてバッファードフッ酸を使用することができる。

#### 【0024】

本実施例において、上部DBRおよびコンタクト層がp型、下部DBR及び基板がn型半導体で形成されている場合、上部電極にはチタンと金の積層構造を、裏面電極には金とゲルマニウムの合金とニッケルと金の積層構造とすることができる。

表面レリーフ構造の上面・底面の形成工程の後には、表面レリーフ部の半導体表面が露出した状態でのエッチング等の工程は存在しないため、表面レリーフの表面にダメージが侵入すること無く、デバイスが完成する。30

以上の工程を用いることにより、結晶成長時に形成した界面を安定的に残した表面レリーフ構造が形成でき、製造ばらつきが抑制された単一基本横モードで発振する面発光レーザが実現できる。

また、本実施例では、単素子の面発光レーザの製造方法について説明したが、この単素子の面発光レーザを複数個配置したアレイにも上述の製造方法を適用することができる。

#### 【0025】

##### 【実施例2】

本発明の実施例2における面発光レーザの製造方法について説明する。

本施例では実施例1と同様に凸型の表面レリーフ構造を有する面発光レーザの製造方法を、図6(a)～図8(k)を用いて説明する。40

本実施例では、実施例1で用いたウエハのコンタクト層の上に、更に第2の半導体層と同一の材料で構成された、第5の半導体層301を形成したウエハを利用する。

この第5の半導体層301は、後述する理由により第2の半導体層112よりも厚いことが望まれる。

始めに上述のウエハにコンタクト部110と表面レリーフ構造部205とを切り分けるフォトリソグラフィーを行う。次にフォトレジストパターンをエッチングマスクに第5の半導体層301をウェットエッチャングによってエッチャングする(図6(b))。

本実施例では、実施例1で使用した第2の半導体層と同一材料であるAl<sub>0.5</sub>Ga<sub>0.5</sub>Asを使用する。

このエッチャングでは、実施例1で用いたリン酸系のエッチャントを使用する。50

この第5の半導体層301の厚さは、後述するように150nmとしているため、エッチングの時間は137秒かかる。

さらに、面内分布を考慮し20秒ほど多くエッチングを行う。これにより、第1の半導体層もエッチングされるが、後述する200nmの厚さであれば全て取り除かれることは無い。

この工程にて、後の工程(図8(j))での第1の半導体層111の除去時に利用するエッチングマスクの面内方向の切り分けが実施される。

#### 【0026】

次に、エッチングマスクとして第1の誘電体膜203を形成する(図6(c))。

その後、実施例1と同様にフォトリソグラフィーとウェットエッチングにより第1の誘電体膜203へパターニング(図6(d))、第2の誘電体膜206及びフォトレジストで表面レリーフ構造部205を保護する(図7(e)、(f))。

そして、ドライエッチングによりメサを形成し、選択酸化を実施し(図7(g))、第1の誘電体膜203および第2の誘電体膜206を取り除く(図7(h))。

#### 【0027】

次に、第5の半導体層301およびコンタクト層である第1の半導体層111をエッチングマスクとしてDBR最上層の第2の半導体層112のエッチングを行う(図8(i))。

このとき、第2の半導体層112と第5の半導体層301は、同一材料で形成されているため第5の半導体層301も同時にエッチングされる。

そのため、第2の半導体層112よりも第5の半導体層301は厚く形成されていることが重要である。

例えば、ここでのエッチングには、リン酸系のエッチャントを使用する。本発明者らの実験では、リン酸(含量85%)：過酸化水素水：水=4:1:90の体積比で混合したリン酸水溶液を用いた場合、

GaAsは、0.6nm/秒、Al<sub>0.5</sub>Ga<sub>0.5</sub>Asは1.1nm/秒のエッチングレートであった。

本実施例では、第5の半導体層301及び、第2の半導体層112にAl<sub>0.5</sub>Ga<sub>0.5</sub>Asを用い、コンタクト層である第1の半導体層111にGaAsを使用したとする。

ここで、第2の半導体層112を/4nとした場合約49.1nmとなり、この第2の半導体層をエッチングするためにかかる時間は、約44.6秒となる。この値から実施例1と同様にGaAsの厚さを200nmの厚さにしておく。

また、第5の半導体層301のAl<sub>0.5</sub>Ga<sub>0.5</sub>Asは49.1nm以上あることが必須であり、且つ後述するエッチングマスクとして使用するため膜の均一性、エッチングの面内分布を考慮して、150nmの厚さにしておく。

実施例1でも記載したが、上述した第2の半導体層の厚さが/4nである場合は、一例であるに過ぎない。面発光レーザに要求される特性によって、厚さを決定できる。

#### 【0028】

第2の半導体層112のエッチングの後、表面レリーフ構造部205の上面に露出しているコンタクト層である第1の半導体層111を取り除く(図8(j))。

ここで、第2の半導体層がエッチングストップとして機能するエッチャントでエッチングすることにより、結晶成長時に形成した界面を表面レリーフ上面に利用することが可能となる。

このとき、図6(b)の工程にてパターニングした形状を保ち、前工程にてエッチングマスクの一つとして利用した第5の半導体層301がコンタクト部119を保護することになる。コンタクト部119の第1の半導体層111がエッチングされず、表面レリーフ上面の第1の半導体層111のみがエッチングされることになる。

また、実施例1と同様に第3の半導体層がエッチングストップ層として機能するように材料を選定することで表面レリーフ底面も結晶成長時の界面を利用することが可能となる。

ここで、第3の半導体層として、実施例1と同様に(A<sub>1</sub><sub>0.5</sub>O<sub>0.5</sub>Ga<sub>0.5</sub>)<sub>0.5</sub>In<sub>0.5</sub>Pを

10

20

30

40

50

用いる。

なお、本実施例においては、第5の半導体層のエッティングレートをc、層の厚さをvとし、第2の半導体層のエッティングレートをd、層の厚さをwとするとき、 $c \times v > d \times w$ の関係を満たす構成を探ることができる。

#### 【0029】

その後、絶縁膜107としてSiNを $/2n$ の厚さで形成し、コンタクト部のみ絶縁膜をエッティングする。

次に、この絶縁膜107をエッティングマスクとし、残留した第5の半導体層301をエッティングし、コンタクト層である第1の半導体層111を露出させ、この箇所に電極となる金属を形成し、基板裏面にも金属膜を形成することで面発光レーザを製造する(図8(k))。

これにより、表面レリーフ構造と電流狭窄構造の位置合わせを行いながら、表面レリーフ構造の上面・底面ともに結晶成長時の結晶界面を有し、安定的に単一基本横モードで発振する面発光レーザを製造することが可能となる。

本実施例では実施例1と異なり、表面レリーフ構造を形成した後に、表面レリーフ構造が露出したままフォトレジストを除去することができなく、より表面レリーフ構造に与えるダメージを少なくすることができる。そのため、より安定的に表面レリーフ構造を形成することができ、単一横モードで発振する面発光レーザの製造歩留まりを向上させることができる。

また、本実施例では、単素子の面発光レーザの製造方法について説明したが、この単素子の面発光レーザを複数個配置したアレイにも上述の製造方法を適用することができる。

#### 【0030】

##### [実施例3]

つぎに、本発明の実施例3における凹型の表面レリーフ構造を有する面発光レーザの製造方法について説明する。

図9(a)、(b)にて実施例1、2と異なる形態の表面レリーフ構造401の詳細な説明を行う。図9(a)は表面レリーフ構造の断面図、(b)は上から見た平面図である。表面レリーフ構造401では、凹型の構造が第2の半導体層403によって形成されている。以後、この凹型構造の表面を表面レリーフ上面408と記載する。また、凹型構造の中心は、第2の半導体層403が取り除かれ、第3の半導体層404が露出している。

以後、この露出している面を表面レリーフ底面407と記載する。本実施例では、表面レリーフ上面408が低い反射率を有する低反射領域409となり、表面レリーフ底面407が高い反射率を有する高反射領域410となるようにウエハが設計されている。

高反射領域410は、電流狭窄部に対して面内の位置が制御されて形成されている。また、表面レリーフ上面408の周囲に、電流を電極から流すために必要な層のコンタクト部が形成されている。

#### 【0031】

本実施例で作製する面発光レーザのウエハ構成は、上部DBR502及びその上に形成する層以外の層構成は、実施例2と同様の構成のウエハ構成となっている。

具体的には、基板上に下部DBR、活性領域、上部DBR502、コンタクト層として第1の半導体層402、第5の半導体層501が順に積層されたウエハ構成である。

この上部DBR502の最後の3層が実施例2と異なっている。また、面発光レーザの構成も表面レリーフ構造部以外は、実施例1及び実施例2と同様の構成となっている。

#### 【0032】

次に、本実施例の面発光レーザの製造方法について説明する。

図10(a)～図12(k)にこの製造方法の工程図を示す。

本実施例の上部DBR502は、高屈折率層207と低屈折率層206が交互に積層されていることは実施例2と変わりはないが、最後の3層の構成が実施例2と異なっている。その他の構成は、実施例2と同様である。

本実施例では、屈折率が $n_4 > n_3 > n_2 < n_1$ を満たす関係とされ、 $n_3$ と $n_2$ の界面

10

20

30

40

50

で反射率が最大となるようにされている。

具体的には、上部 D B R 5 0 2 の最後の 3 層をコンタクト層側から、第 2 の半導体層 4 0 3、第 3 の半導体層 4 0 4、第 4 の半導体層 4 0 5 とする。

この第 4 の半導体層 4 0 5 は高屈折率層と同一材料、第 3 の半導体層 4 0 4 は第 2 の半導体層 4 0 3 をエッティングする際にエッティングストップ層として機能する材料で構成される。

第 2 の半導体層 4 0 3 は、第 4 の半導体層 4 0 5、及び、第 3 の半導体層 4 0 4 よりも屈折率の低い材料で構成されている（また、第 3 の半導体層 4 0 4 は、第 1 及び第 2 の誘電体膜を除去する際にエッティングされない材料である必要がある。）。

また、第 3 の半導体層 4 0 4 は第 4 の半導体層 4 0 5 と第 2 の半導体層 4 0 3 の中間の屈折率となる材料で構成されている。

10

具体的には、高屈折率層 2 0 7 として、 $A l_{0.5}G a_{0.5}A s$  を、

低屈折率層 2 0 6 として、 $A l_{0.9}G a_{0.1}A s$  を、

第 4 の半導体層 4 0 5 として、 $A l_{0.5}G a_{0.5}A s$  を、

第 3 の半導体層 4 0 4 として、 $(A l_{0.5}G a_{0.5})_{0.5}I n_{0.5}P$  を、

第 2 の半導体層 4 0 3 として、 $A l_{0.75}G a_{0.2}A s$  を、それぞれ用いることができる

。

### 【 0 0 3 3 】

本実施例での上部 D B R 5 0 2 は第 3 の半導体層 4 0 4 と第 2 の半導体層 4 0 3 の界面で最も高い反射率を有するように設計される。

20

上部 D B R 5 0 2 最後の 3 層がその下に積層された D B R との整合を保つために、第 2 の半導体層 4 0 3、第 3 の半導体層 4 0 4、第 4 の半導体層 4 0 5 の 3 層の合計膜厚が  $/ 2 n$  ( $n$  は各材料の屈折率) の厚さとなることが好ましい。

上述した上部 D B R 5 0 2 上にコンタクト層として機能する第 1 の半導体層 4 0 2 として G a A s が形成され、さらに上層に第 5 の半導体層 5 0 1 として  $A l_{0.75}G a_{0.3}A s$  が形成されている。

始めにウエハにコンタクト部 5 0 3 と表面レリーフ構造部 5 0 4 とを切り分けるフォトリソグラフィーを行う。

次に、フォトレジストパターンをエッティングマスクに第 5 の半導体層 5 0 1 をウェットエッティングによって直径  $10 \mu m$  の孔状のパターンでエッティングする（図 10 ( b )）。

30

この工程にて、後の工程（図 12 ( j )）でのコンタクト層除去時に利用するエッティングマスクの面内方向の切り分けが実施される。

その後、実施例 1 と同様に第 1 の誘電体膜 5 0 5 を形成し（図 10 ( c )）、フォトリソグラフィーとウェットエッティングによって、表面レリーフ孔 5 0 6 とトレンチ部 5 0 7 を形成する。

### 【 0 0 3 4 】

本実施例では、凹型の表面レリーフ構造であるため、エッティングされる構造は実施例 1 と若干異なっている。

具体的には、例えば表面レリーフ孔 5 0 6 として直径  $4 \mu m$  の孔状のパターンと、トレンチ部 5 0 7 として内径  $27 \mu m$ 、外形  $40 \mu m$  の溝をエッティングする。この両者のパターンが中心を同じくするように、同一マスクで形成することにより表面レリーフ構造とメサ構造の面内の相対位置が一意に決定される。

40

その後は、実施例 2 と同様に第 1 の半導体層 4 0 2 をエッティングし（図 10 ( d )）、第 2 の誘電体膜 5 0 8 及びフォトレジストで表面レリーフを保護する（図 11 ( e )、( f )）。

その後、ドライエッティングによりメサを形成し、選択酸化を実施し（図 11 ( g )）、第 1 の誘電体膜 5 0 5 及び、第 2 の誘電体膜 5 0 8 を除去する（図 11 ( h )）。

そして、第 2 の半導体層 4 0 3 のエッティング（図 12 ( i )）、第 1 の半導体層 4 0 2 のエッティングを行う（図 12 ( j )）。

さらに、絶縁膜形成、第 5 の半導体層 5 0 1 の除去、電極形成を行い、面発光レーザを作

50

製する（図12（k））。

また、本実施例では、実施例2と異なる上部DBR502の構成とすることで、凹型の表面レリーフ構造を形成することができる。

また、本実施例では、単素子の面発光レーザの製造方法について説明したが、この単素子の面発光レーザを複数個配置したアレイにも上述の製造方法を適用することができる。

#### 【0035】

##### [実施例4]

つぎに、本発明の実施例4における凹型の表面レリーフ構造を有する面発光レーザの製造方法について説明する。

本実施例も実施例3と同様の凹型の表面レリーフ構造を有する面発光レーザの製造方法に 10 関するものであることから、使用するウエハ構造は、第5の半導体層501が存在しないこと意外は、実施例3と同様の構成となる。

本実施例の製造方法について図9（a）、（b）及び図13（a）～図15（k）を用いて以下に記す。

第5の半導体層501を形成していない実施例3にて使用したウエハを本実施例では使用する。

具体的には、基板上に下部DBR、活性領域、上部DBR502、コンタクト層として第1の半導体層402の順に積層されたウエハであり、上部DBRの最後の3層の層構成が実施例3と同様な構成である。

このウエハを、実施例3の図10（d）以降の工程と同様に、第1の誘電体膜601を形成しフォトリソグラフィーとウェットエッチングによって、表面レリーフ構造部603とトレンチ部602を形成する（図13（b））。

この時の表面レリーフ構造部及びトレンチ部の構成は、実施例3と同様である。以降の工程も実施例3と同様に、第1の半導体層402をエッチングし（図13（c））、第2の誘電体膜604及びフォトレジストで表面レリーフを保護し（図13（d））、ドライエッチングによりメサを形成し、選択酸化を実施する（図14（e））。

そして、第1及び、第2の誘電体膜の除去を行う（図14（f））。

#### 【0036】

これらに続く、次の工程が本実施例に特有の工程である。

すなわち、コンタクト部保護工程が、選択酸化工程の後であって、且つ表面レリーフ構造の上面を露出させる工程の前に実施され、コンタクト部として機能する第1の半導体層領域の保護が、第3の誘電体膜によって行われる。

具体的には、図14（f）続く工程において、第3の誘電体膜605を形成する（図14（g））。

この誘電体膜は、例えばSiO<sub>2</sub>、SiN、SiONなどが用いられるが、これに限られるものではない。

次に、表面レリーフ構造が露出するようにフォトリソグラフィーとウェットエッチングにより第3の誘電体膜605をパターニングする（図14（h））。

このとき、上述した誘電体膜を用いる場合、エッチャントとしてバッファードフッ酸を用いることができる。

次に、実施例1、2、3と同様に第2の半導体層403をエッチングし、続いて第1の半導体層402をエッチングする。

これらのエッチングの際に用いるエッチャントに対して第3の誘電体膜605が除去されないことが重要である。

本実施例で使用している材料であれば、実施例1で使用しているクエン酸系のエッチャントに対して、第3の誘電体膜605がエッチングされない。

その後、実施例1と同様に絶縁膜を形成し、電極を取り出す部分の絶縁膜を除去し、上部・裏面電極を形成することで面発光レーザを作製できる（図15（i）～（k））。

#### 【0037】

本実施例では、実施例1と異なり表面レリーフ構造を形成した後にフォトレジストを除

10

20

30

40

50

去する工程が無く、より表面レリーフ構造に与えるダメージ類を少なくすることが可能となる。

また、実施例2や実施例3と異なり、電極形成のためにコンタクト部の絶縁膜を取り除く際に、第1の半導体層111をエッティングするためのエッティングマスクが絶縁膜を取り除くエッチャントと同一のものを使用することができる。

そのため、ウェットエッティングの工程が一つ少なくすることができる。

また、本実施例では、単素子の面発光レーザの製造方法について説明したが、この単素子の面発光レーザを複数個配置したアレイにも上述の製造方法を適用することができる。

#### 【0038】

##### [実施例5]

10

実施例5として、図16を用いて本発明を適用した垂直共振器型面発光レーザがアレイ状に配列して構成された面発光レーザアレイを、光源として備えられている光学機器の構成例について説明する。

ここでは、光学機器として、上記面発光レーザによるレーザアレイを用いて構成した画像形成装置の構成例について説明する。

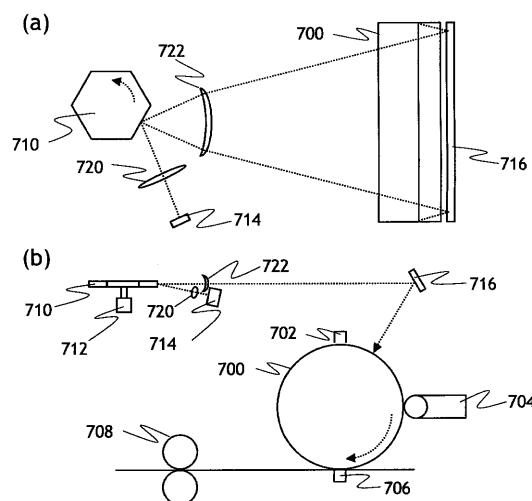

図16に、本発明による垂直共振器型面発光レーザアレイを実装した電子写真記録方式の画像形成装置の構造図を示す。

図16(a)は画像形成装置の平面図であり、図16(b)は同装置の側面図である。

図16において、700は感光ドラム、702は帯電器、704は現像器、706は転写帯電器、708は定着器、710は回転多面鏡、712はモータである。

20

また、714は垂直共振器型面発光レーザアレイ、716は反射鏡、720はコリメータレンズ及び722はf-レンズである。

図16において、モータ712は回転多面鏡710を回転駆動するものである。

#### 【0039】

本実施例における回転多面鏡710は、6つの反射面を備えている。

垂直共振器型面発光レーザアレイ714は、記録用光源となるものであり、レーザドライバ(図示せず)により画像信号に応じて点灯または消灯するように構成されている。

こうして光変調されたレーザ光は、垂直共振器型面発光レーザアレイ714からコリメータレンズ720を介し回転多面鏡710に向けて照射される。

回転多面鏡710は矢印方向に回転していて、垂直共振器型面発光レーザアレイ714から出力されたレーザ光は、回転多面鏡710の回転に伴い、その反射面で連続的に出射角度を変える偏向ビームとして反射される。

30

この反射光は、f-レンズ722により歪曲収差の補正等を受け、反射鏡716を経て感光ドラム700に照射され、感光ドラム700上で主走査方向に走査される。

このとき、回転多面鏡710の1面を介したビーム光の反射により、感光ドラム700の主走査方向に垂直共振器型面発光レーザアレイ714に対応した複数のライン分の画像が形成される。

#### 【0040】

本実施例においては、4×8の垂直共振器型面発光レーザアレイ714を用いており、4ライン分の画像が形成される。

40

感光ドラム700は、予め帯電器702により帯電されており、レーザ光の走査により順次露光され、静電潜像が形成される。

また、感光ドラム700は矢印方向に回転していて、形成された静電潜像は、現像器704により現像され、現像された可視像は転写帯電器706により、転写紙(図示せず)に転写される。

可視像が転写された転写紙は、定着器708に搬送され、定着を行った後に機外に排出される。

なお、感光ドラム700の側部における主走査方向の走査開始位置近傍に、ビーム検出センサ(Beam Detectセンサ:以下BDセンサ)が配置されている(不図示)。

#### 【0041】

50

回転多面鏡 710 の各反射面で反射されたレーザ光は、ライン走査に先立って B D センサにより検出される。

この検出信号は、主走査方向の走査開始基準信号としてタイミングコントローラ（図示せず）に入力され、この信号を規準として各ラインにおける走査方向の書き出し開始位置の同期が取られる。

なお、本実施例では、 $4 \times 8$  垂直共振器型面発光レーザアレイを用いたが、これに限定されるものではなく、 $m \times n$  垂直共振器型面発光レーザアレイ（ $m, n$ ：自然数（0は含まず））であっても良い。

#### 【0042】

以上説明したように、本発明による垂直共振器型面発光レーザアレイを電子写真記録方式の画像形成装置に用いることにより、高速・高精細印刷を可能とする画像形成装置を得ることが可能となる。また、信頼性の高い面発光レーザアレイを用いることにより、画像形成装置自体の信頼性も向上させることが可能となる。

#### 【符号の説明】

#### 【0043】

- 100 : 面発光レーザ

- 101 : 表面レリーフ構造

- 102 : 基板

- 103 : 下部 D B R

- 104 : 上部 D B R

- 105 : 電流狭窄部

- 106 : 活性領域

- 107 : 絶縁膜

- 108 : 上部電極

- 109 : 下部電極

- 110 : コンタクト部

- 111 : 第1の半導体層

- 112 : 第2の半導体層

- 113 : 第3の半導体層

- 114 : 第4の半導体層

- 115 : 表面レリーフ上面

- 116 : 表面レリーフ底面

- 117 : 高反射領域

- 118 : 低反射領域

- 201 : 低屈折率層

- 202 : 高屈折率層

- 203 : 第1の誘電体膜

- 204 : トレンチ部

- 205 : 表面レリーフ構造部

- 206 : 第2の誘電体膜

- 207 : 選択酸化層

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

401

【図11】

【図12】

【図13】

【図15】

【図16】

---

フロントページの続き

(74)代理人 100134393

弁理士 木村 克彦

(74)代理人 100174230

弁理士 田中 尚文

(72)発明者 稲生 耕久

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 内田 達朗

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

(72)発明者 内田 武志

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 百瀬 正之

(56)参考文献 特開2010-040600(JP,A)

特開2007-201398(JP,A)

特開2006-210429(JP,A)

特開2010-251342(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01S 5/00 - 5/50