(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5584474号

(P5584474)

(45) 発行日 平成26年9月3日(2014.9.3)

(24) 登録日 平成26年7月25日(2014.7.25)

(51) Int.Cl.

F 1

|              |           |

|--------------|-----------|

| HO1L 23/12   | (2006.01) |

| HO1L 21/3205 | (2006.01) |

| HO1L 21/768  | (2006.01) |

| HO1L 23/522  | (2006.01) |

|            |      |

|------------|------|

| HO1L 23/12 | 501P |

| HO1L 21/88 | J    |

| HO1L 21/88 | T    |

請求項の数 9 (全 34 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2009-552696 (P2009-552696)  |

| (86) (22) 出願日 | 平成20年2月26日 (2008.2.26)        |

| (65) 公表番号     | 特表2010-520641 (P2010-520641A) |

| (43) 公表日      | 平成22年6月10日 (2010.6.10)        |

| (86) 國際出願番号   | PCT/US2008/002659             |

| (87) 國際公開番号   | W02008/108970                 |

| (87) 國際公開日    | 平成20年9月12日 (2008.9.12)        |

| 審査請求日         | 平成23年2月25日 (2011.2.25)        |

| (31) 優先権主張番号  | 60/905,096                    |

| (32) 優先日      | 平成19年3月5日 (2007.3.5)          |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                           |

|-----------|-------------------------------------------------------------------------------------------|

| (73) 特許権者 | 309034272<br>インヴェンサンス・コーポレイション<br>アメリカ合衆国 カリフォルニア州 95<br>134、サン・ホセ、オーチャード・パー<br>クウェイ 3025 |

| (74) 代理人  | 100099623<br>弁理士 奥山 尚一                                                                    |

| (74) 代理人  | 100096769<br>弁理士 有原 幸一                                                                    |

| (74) 代理人  | 100107319<br>弁理士 松島 鉄男                                                                    |

| (74) 代理人  | 100114591<br>弁理士 河村 英文                                                                    |

| (74) 代理人  | 100125380<br>弁理士 中村 純子                                                                    |

最終頁に続く

(54) 【発明の名称】貫通ビアによって前面接点に接続された後面接点を有するチップ

## (57) 【特許請求の範囲】

## 【請求項 1】

前面と、前記前面から離間した後面とを有する半導体要素であって、前記前面および前記後面は、第1の厚みを有する薄い領域と、前記第1の厚みの少なくとも2倍の第2の厚みを有する厚い領域とを画定しており、前記半導体要素は、前記前面における半導体素子と、前記素子に接続された、前記前面における複数の第1の導電接点を備えており、前記第1の導電接点のそれぞれが、前記各半導体要素の前記前面から離間した表面を有している、半導体要素であって、前記薄い領域は、前記半導体要素の対向する縁の間に直線方向に延在するストライプとして形成され、該ストライプは、平坦であって前記前面から等距離に位置する低くなつた面を有している、半導体要素と、

前記半導体要素の外部に露出している複数の第2の導電接点と、

前記第2の導電接点を導電ビアに接続する複数の導電トレースと

を備えてなり、

前記半導体要素は、前記半導体要素の前記薄い領域を通って、前記半導体要素の前記後面から前記第1の導電接点に延びる複数の前記導電ビアをさらに含み、前記導電ビアは、前記第1の導電接点の表面に接する金属を含んでいる、超小型電子ユニット。

## 【請求項 2】

前記第2の導電接点は、前記後面において、前記厚い領域の上に覆い被さっていることを特徴とする請求項1に記載の超小型電子ユニット。

## 【請求項 3】

前記後面の上に覆い被さっている誘電体層をさらに備えることを特徴とする請求項1に記載の超小型電子ユニット。

【請求項4】

前記第2の導電接点および前記導電トレースは、前記誘電体層の上に覆い被さっていることを特徴とする請求項3に記載の超小型電子ユニット。

【請求項5】

請求項1に記載の超小型電子ユニットを備えるアセンブリであって、前記半導体要素の前記後面の上に覆い被さっているコンプライアント誘電体層をさらに含み、前記アセンブリは、前記第2の導電接点に接続される端子を有する回路パネルをさらに含んでおり、前記誘電体層の弾性係数と前記誘電体層の厚みとの積は、前記超小型電子ユニットと前記回路パネルとの間の熱膨張の不一致を相殺するのに十分なものであることを特徴とするアセンブリ。10

【請求項6】

請求項1に記載の超小型電子ユニットを備えるカメラモジュールであって、前記半導体素子は、撮像領域を備え、前記カメラモジュールは、前記前面の少なくとも一部に覆い被さったカバー要素と、前記撮像領域と位置合わせされて前記カバー要素に取り付けられた光学要素を有する光学要素を有する光学ユニットとをさらに備えていることを特徴とするカメラモジュール。

【請求項7】

前記半導体要素を配置した位置に前記前面の少なくとも一部に覆い被さっているカバー要素をさらに備えていることを特徴とする請求項1に記載の超小型電子ユニット。20

【請求項8】

前記半導体要素は、前記前面から離間した後面を有しており、前記第2の導電接点と前記導電トレースとを形成するのに先だって、前記後面に覆い被さるように誘電体層を電着するステップを含んでおり、前記第2の導電接点と前記導電トレースとは、前記誘電体層に覆い被さるように形成されている、請求項1から4のいずれかに記載の超小型電子ユニットを製造する方法。

【請求項9】

前記第2の厚みと少なくとも実質的に同じ厚みになるように、前記半導体要素を前記後面から薄くするステップを実行した後に、前記半導体要素の一部を前記第1の厚みよりも薄くするステップを実行して前記薄膜領域を形成することを含むことを特徴とする請求項1から4のいずれかに記載の超小型電子ユニット。30

【発明の詳細な説明】

【技術分野】

【0001】

【関連出願の相互参照】

本願は、2007年3月5日に出願された米国仮特許出願第60/905,096号の出願日の利益を主張するものであり、その開示内容は引用することにより本明細書の一部をなすものとする。

【発明の分野】

【0002】

本発明は、超小型電子素子のパッケージング、特に、半導体素子のパッケージングに関するものである。

【背景技術】

【0003】

超小型電子素子および半導体チップの中には、音響変換器、無線周波数エミッタ、または無線周波数検出器のような素子、光電子素子、またはこのような素子の組合せを備えている種類のものがある。このような素子は、典型的には、エネルギー、例えば、音響エネルギー、無線周波数エネルギー、または光波長エネルギーを半導体チップの面に配置された素子に伝達し、またはそれらの素子から伝達させることを可能にするパッケージングを50

必要としている。

#### 【0004】

このような素子は、多くの場合、超小型電子素子の前面に露出しているので、通常、埃、他の粒子、汚染物質、または湿気のような要因から保護する必要がある。この理由から、加工の初期段階において、超小型電子素子を、このような超小型電子素子の前面を覆うリッドまたは他の要素と組み合わせると、有利である。

#### 【0005】

超小型電子システムの種類によっては、極めて小さいパッケージ、すなわち、チップスケールパッケージを有するチップおよびパッケージ化されたチップを回路パネルに取り付けることが望まれている。場合によっては、アセンブリの回路密度を増すために、チップを互いに上下に積層し、相互接続することが望まれている。

10

#### 【0006】

量産チップの種類によっては、パッケージングコストを厳密に管理することも必要とされることがある。このような半導体チップをパッケージングするのに用いられる処理は、ウエハまたはウエハの一部の形態にある互いに結合されたままの多くのチップに対して、同時に用うことができる。このような「ウエハレベル」の処理は、典型的には、ウエハの全体に適用される一連の処理によって行われ、この後、ウエハは、個々のチップにダイシングされることになる。有利には、このウエハレベルのパッケージングプロセスは、元の半導体チップと同一の面積寸法を有するパッケージ化チップを製造するので、回路パネルなどへの相互接続をコンパクトにすることができます。

20

#### 【発明の概要】

#### 【0007】

本発明の一態様によれば、超小型電子ユニットが提供されている。この超小型電子ユニットでは、半導体要素は、前面と、前面から遠く離れた後面とを有している。前面および後面は、第1の厚みを有する薄い領域および第1の厚みの少なくとも約2倍の第2の厚みを有する厚い領域を画定しているとよい。このような超小型電子ユニットでは、半導体要素は、前面における半導体素子、および該素子に接続された、前面における複数の第1の導電接点を備えているとよい。複数の導電ビアが、後面から、半導体要素の薄い領域を通って、第1の導電接点に延在しているとよい。複数の第2の導電接点が、半導体要素の外部に露出され、複数のトレースが、この第2の導電接点を導電ビアに接続するようになっているとよい。

30

#### 【0008】

本発明の他の態様によれば、超小型電子ユニットが提供されている。このような超小型電子では、半導体要素は、前面と、前面における半導体素子と、前面から遠く離れた後面とを有している。第1の導電接点が、前面に設けられているとよい。半導体要素は、後面から部分的に半導体要素を通って前面に向かって延在する第1の深さの第1の孔も有しているとよい。第1の孔から第1の導電接点に延在する第2の孔は、第2の深さを有しているとよい。複数の第1の導電ビアが、第2の孔の壁に沿って延在し、第1の導電接点に接觸しているとよい。複数の導電性相互接続部が、第1の導電ビアに接続されているとよい。一実施形態では、このような導電性相互接続部は、第1の孔の壁に沿って延在しているとよい。複数の第2の導電接点が、導電性相互接続部に接続されているとよい。一例では、第2の接点は、半導体要素の外部に露出しているとよい。

40

#### 【0009】

本発明の一態様によれば、超小型電子ユニットが提供されている。この超小型電子ユニットは、前面と、前面における半導体要素と、該素子に接続された、前面における複数の第1の導電接点とを有する半導体要素を備えているとよい。半導体要素の前面と向き合っている内面と、内面から遠く離れた外面とを有するリッドが設けられているとよい。第1の深さを有する第1の孔が、外面から少なくとも部分的にリッドを通って内面に向かって延在しているとよい。リッドの内面を半導体要素の前面の上方に支持する支持構造体が設けられているとよい。一例では、支持構造体は、第1の孔と一直線に並んだ第2の孔を有

50

している。第2の孔は、支持構造体を通って、第1の導電接点に延在しているとよい。複数の第1の導電ビアが、第2の孔の壁に沿って延在し、第1の導電接点に接触することができる。複数の第2の導電性ビアが、第1の孔の壁に沿って延在しているとよい。複数の第2の導電接点が、リッドの外部に露出しているとよい。一例では、複数の導電トレースが、第2の導電接点を導電ビアに接続するようになっている。

#### 【0010】

本発明の一態様によれば、超小型電子ユニットが提供されている。この超小型電子ユニットは、前面と、前面における半導体素子とを有する半導体要素を備えている。半導体素子に接続された複数の第1の導電接点が、前面に設けられているとよい。超小型電子ユニットは、半導体要素の前面と向き合った内面と、内面から遠く離れた外面とを有するリッドを附加的に備えているとよい。リッドの内面および外面は、第1の厚みを有する薄い領域および第1の厚みの少なくとも約2倍の第2の厚みを有する厚い領域を画定しているとよい。このようなリッドは、外面からリッドの薄い領域を通って第1の導電接点に延在する複数の導電ビアをさらに備えているとよい。このような超小型電子ユニットは、複数の第2の導電接点をさらに備えているとよい。複数の導電トレースが、第2の導電接点を導電ビアに接続するようになっているとよい。

#### 【0011】

本発明の一態様によれば、超小型電子ユニットが提供されている。この超小型電子ユニットは、半導体要素の前面と向き合った内面と、内面から遠く離れた外面と、を有するリッドを備えているとよい。複数の導電ビアが、リッド内を通って、第1の導電接点に接触するようになっているとよい。このような超小型電子ユニットは、リッドの外面の上に覆い被さっている複数の第2の導電接点を附加的に備えているとよい。複数の導電トレースが、第2の導電接点を導電ビアに接続するようになっているとよい。

#### 【0012】

本発明の一態様によれば、超小型電子ユニットが提供されている。この超小型電子ユニットは、前面と、前面における半導体素子と、前面から遠く離れた後面とを有する半導体要素を備えている。前面導電接点が、前面に露出しているとよい。後面導電接点が、後面に露出しているとよい。複数の導電ビアが、前面導電接点に接続されているとよい。導電ビアは、前面から下方に延在しているとよい。開口が、導電ビアの少なくとも1つと位置合わせされて、後面から下方に延在しているとよい。導電トレースが、導電ビアの少なくとも1つから開口の壁に沿って、上方に延在しているとよい。このような導電トレースは、後面導電接点の少なくとも1つに接続されるようになっているとよい。

#### 【0013】

本発明の一態様によれば、超小型電子ユニットが提供されている。この超小型電子ユニットは、前面と、前面における半導体素子と、前面から遠く離れた後面とを有する半導体要素を備えている。後面導電接点が、後面に露出しているとよい。このような超小型電子ユニットでは、複数の導電ビアが、前面から下方に延在しているとよい。開口が、導電ビアの少なくとも1つと位置合わせされて、後面から下方に延在しているとよい。導電バンプを開口内の導電ビアの1つに接合させることができる。このような場合、導電バンプは、導電ビアから、後面によって画定された面の上方の位置まで延在しているとよい。

#### 【0014】

本発明の一態様によれば、超小型電子ユニットが提供されている。この超小型電子ユニットは、前面と、前面における半導体素子と、前面から遠く離れた後面とを有する半導体要素を備えている。後面導電接点が、後面に露出していてもよい。複数の導電ビアが、前面から下方に延在していてもよい。開口が、導電ビアの少なくとも1つと位置合わせされて、後面から下方に延在するようになっていてもよい。導電バンプを前面における導電ビアの1つに接合させることができる。導電バンプは、例えば、前面から上方に延在するようになっていてもよい。

#### 【0015】

本発明の他の態様によれば、超小型電子ユニットを製造する方法が提供されている。こ

10

20

30

40

50

のような方法は、前面と、前面から遠く離れた後面と、前面における半導体素子とを有する半導体要素を設けることを含んでいるとよい。半導体素子に接続された第1の導電接点が、半導体要素の前面に設けられているとよい。複数の導電ビアが、後面から半導体要素を通って第1の導電接点に延在しているとよい。このような方法は、後面の上に覆い被さる複数の第2の導電接点、および複数の導電トレースを形成することをさらに含んでいるとよい。導電トレースは、第2の導電接点を導電ビアに接続するためのものである。

#### 【0016】

本発明の他の態様によれば、超小型電子ユニットを製造する方法が提供されている。このような方法では、前面と、前面における半導体素子とを備える半導体要素が設けられることになる。前面における第1の導電接点が、半導体素子に接続されているとよい。半導体要素は、前面から遠く離れた後面と、後面に露出した半導体材料とをさらに備えているとよい。複数の貫通孔が、後面から半導体要素を通って第1の導電接点に延在しているとよい。後面誘電体層が、後面における露出した半導体材料上または貫通孔の壁に沿って、またはその両方に電着されるとよい。第2の導電接点が、後面の上に覆い被さって形成されるとよい。第1の導電接点と接触する複数の導電ビアが、貫通孔内に形成されるとよい。第2の導電接点を導電ビアに接続する複数の導電トレースが形成されるとよい。

10

#### 【0017】

本発明の他の実施形態によれば、超小型電子ユニットを製造する方法が提供されている。このような方法は、半導体要素を、半導体要素の前面の上に覆い被さるカバー要素と組み合わせ、ユニットを形成することを含んでいるとよい。半導体要素は、半導体素子に接続された、前面における第1の導電接点を有しているとよい。前面から遠く離れた後面が、設けられているとよい。複数の貫通孔が、後面から半導体要素を通って、第1の導電接点に延在しているとよい。一実施形態では、半導体材料が、後面および貫通孔の壁に露出している。

20

#### 【0018】

誘電体層が、後面および貫通孔の壁に沿って、露出した半導体材料の上に覆い被さるよう電着されるとよい。誘電体層は、第1の導電接点に接觸する導電ビアが貫通孔内に形成されるように、誘電体層の全体にわたって電着されてもよい。複数の第2の導電接点が、後面の上に覆い被さって形成され、複数の導電トレースが、導電ビアを第2の導電接点に接続するようになっているとよい。

30

#### 【図面の簡単な説明】

#### 【0019】

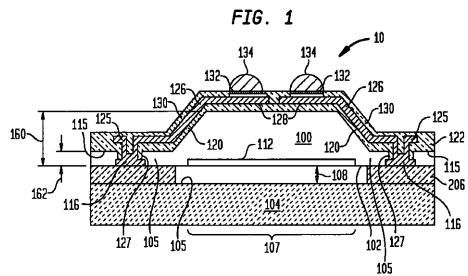

【図1】本発明の実施形態によるパッケージ化された半導体チップを示す断面図である。

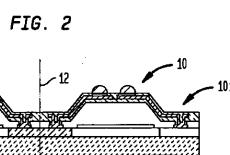

【図2】本発明の実施形態による複数のパッケージ化されたチップを同時に製造する方法の一段階を示す断面図である。

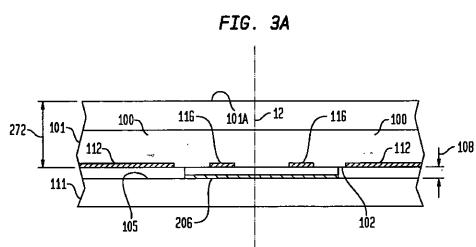

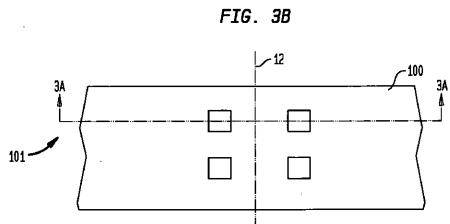

【図3A・3B】本発明の実施形態による製造の一段階を示す断面図および対応する上から見た平面図である。

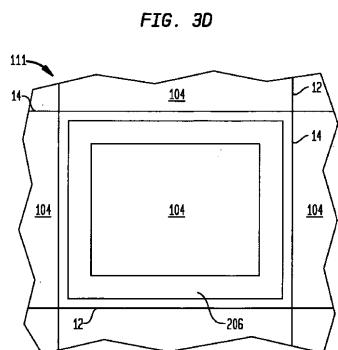

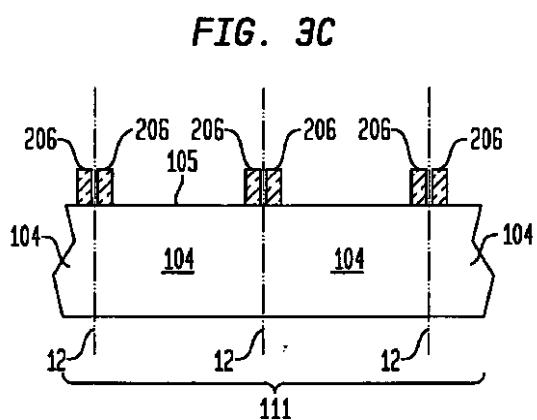

【図3C・3D】本発明の実施形態による製造方法の一段階におけるリッド部材の準備を示す断面図および対応する平面図である。

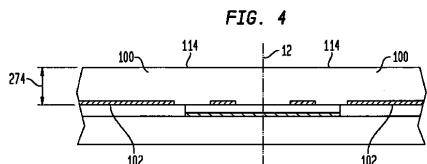

【図4】本発明の実施形態による製造の方法の一段階を示す断面図である。

40

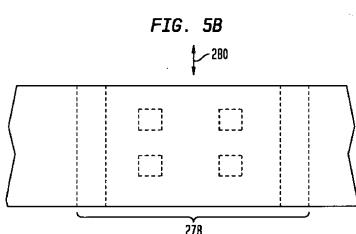

【図5A・5B】本発明の実施形態による製造の一段階を示す断面図および対応する上から見た平面図である。

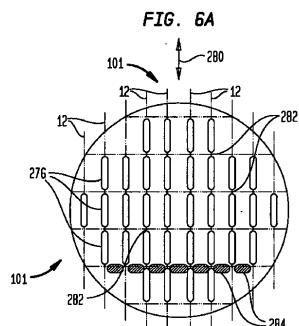

【図6A】本発明の実施形態による製造の一段階を示す平面図である。

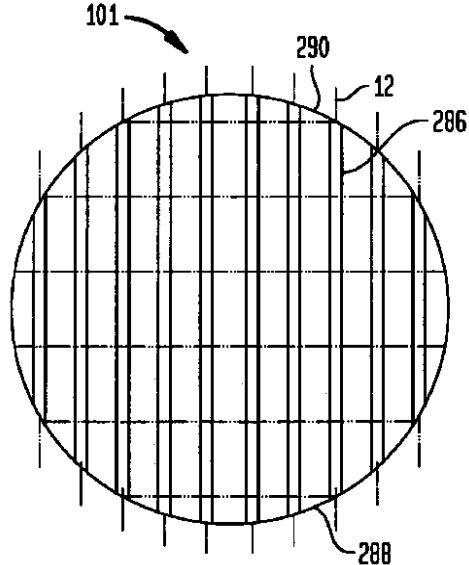

【図6B】本発明の代替的実施形態による製造の一段階を示す平面図である。

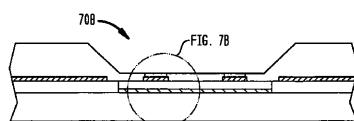

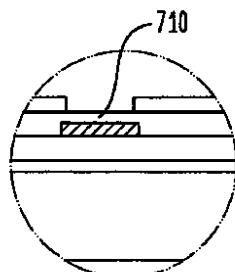

【図7A・7C】本発明の実施形態による製造の一段階を示す断面図、対応する上から見た平面図、および拡大図である。

【図8A・8B】本発明の実施形態による製造の一段階を示す断面図および上から見た平面図である。

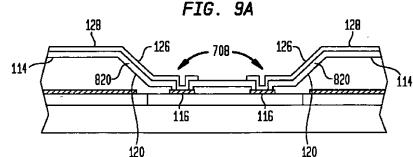

【図9A・9B】本発明の実施形態による製造の一段階を示す断面図および対応する上から見た平面図である。

50

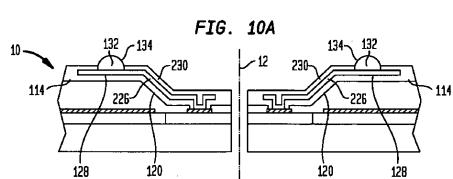

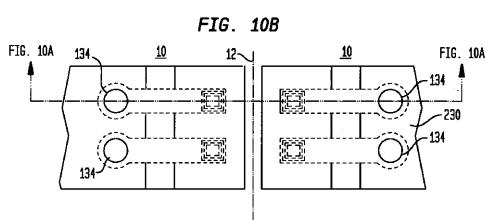

【図10A・10B】本発明の実施形態による製造の一段階を示す断面図および対応する上から見た平面図である。

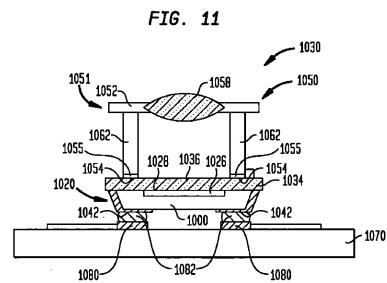

【図11】本発明の実施形態によるカメラモジュールのような光電子素子モジュールを示す断面図である。

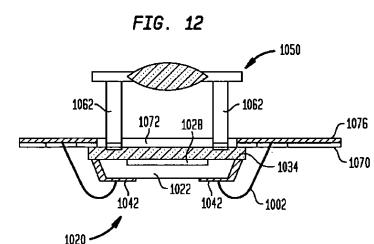

【図12】本発明の実施形態によるカメラモジュールのような代替的な光電子素子モジュールを示す断面図である。

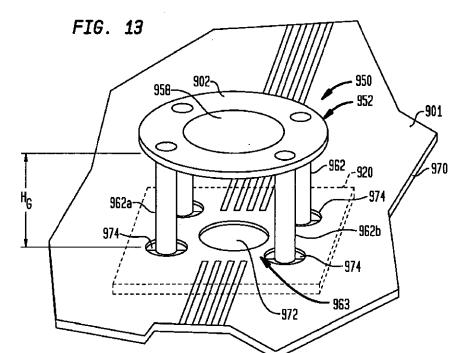

【図13】本発明の実施形態によるカメラモジュールのような代替的な光電子素子モジュールを示す断面図に対応する透視図である。

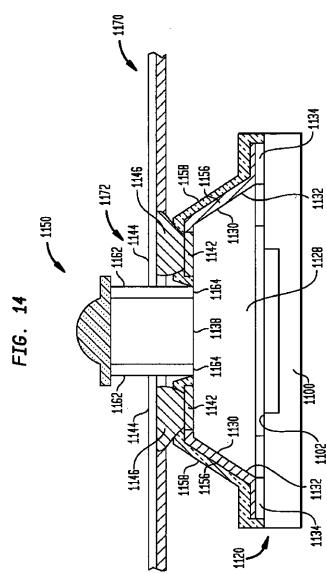

【図14】本発明の実施形態によるカメラモジュールのようなさらに他の代替的な光電子素子モジュールを示す断面図である。

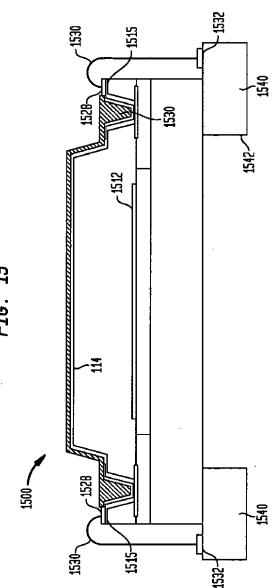

【図15】本発明の実施形態によるパッケージ化された半導体チップを備えるアセンブリを示す断面図である。

【図16A】本発明の他の実施形態によるパッケージ化されたチップを示す断面図である。

【図16B】図16Aに示されているパッケージ化されたチップをさらに示す平面図である。

【図17】本発明の他の実施形態によるパッケージ化されたチップを示す断面図である。

【図18】本発明のさらに他の実施形態によるパッケージ化されたチップを示す断面図である。

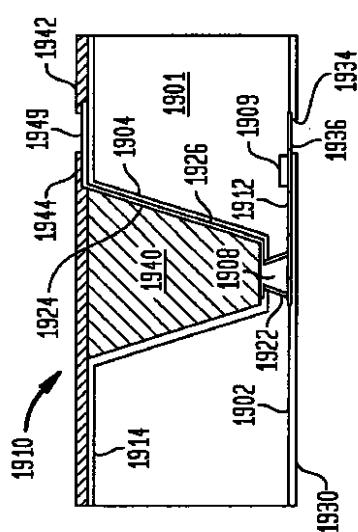

【図19A】本発明のさらに他の実施形態によるパッケージ化されたチップを示す部分断面図である。

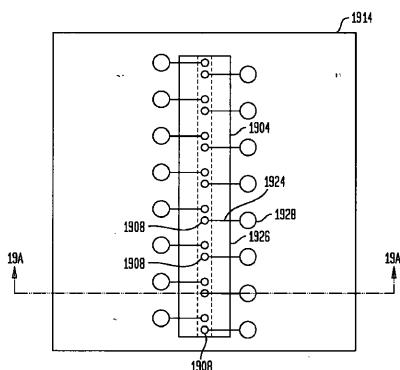

【図19B】図19Aに示されている本発明の実施形態によるパッケージ化されたチップをさらに示す対応する平面図である。

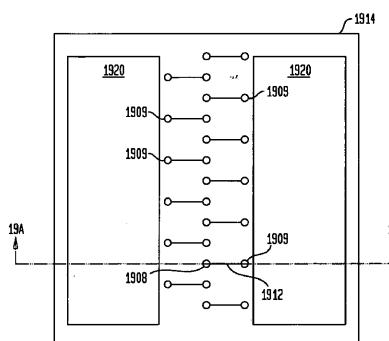

【図19C】図19Aに示されている本発明の実施形態の変更例によるパッケージ化されたチップをさらに示す対応する平面図である。

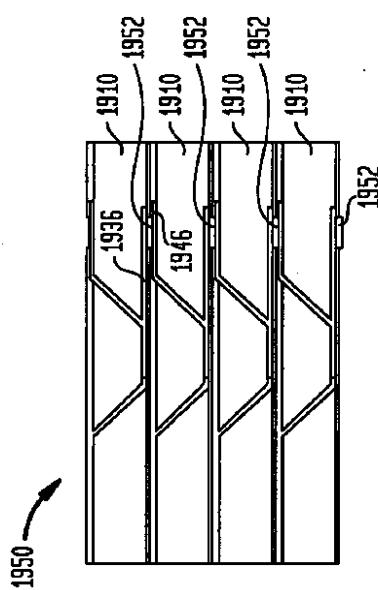

【図19D】図19Aに示されているようなパッケージ化されたチップの複数個を備える積層アセンブリを示す断面図である。

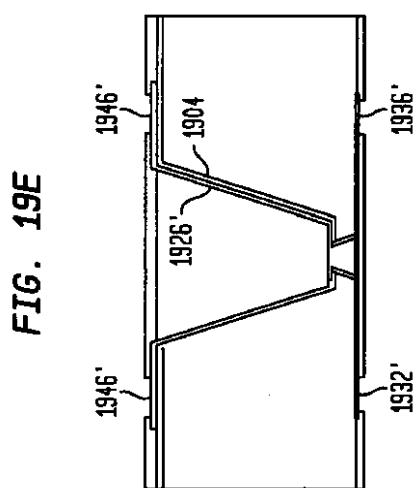

【図19E】図19Aに示される本発明の実施形態の変更例によるパッケージ化されたチップを示す部分断面図である。

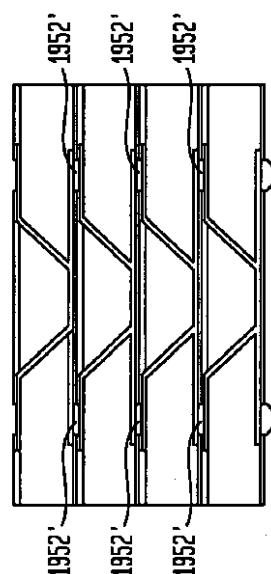

【図19F】図19Eに示されているようなパッケージ化されたチップの複数個を備える積層アセンブリを示す断面図である。

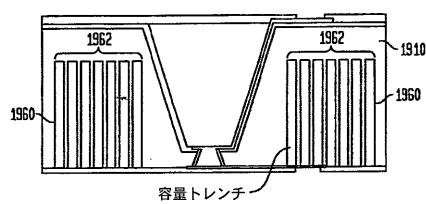

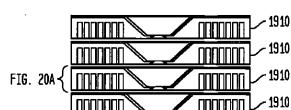

【図20A】図19Aに示されているような実施形態の変更例によるパッケージ化されたチップを示す断面図である。

【図20B】図20Aに示されているようなパッケージ化されたチップの複数個を備える積層アセンブリを示す断面図である。

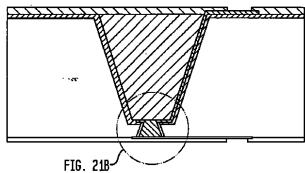

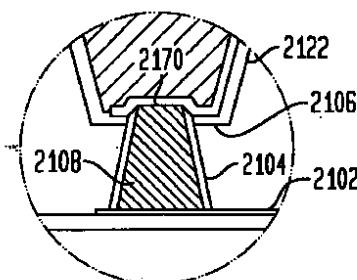

【図21A】本発明の実施形態によるパッケージ化されたチップをさらに示す断面図である。

【図21B】図21Aに示されるパッケージ化されたチップをさらに示す拡大詳細図である。

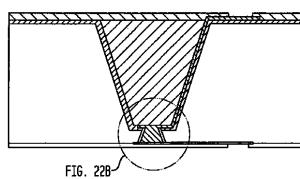

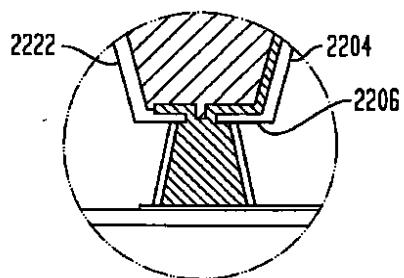

【図22A】本発明の実施形態によるパッケージ化されたチップをさらに示す断面図である。

【図22B】図22Aに示されるパッケージ化されたチップをさらに示す拡大詳細図である。

【図23A-C】本発明の実施形態による変更例を示すパッケージ化されたチップを示す断面図である。

【図23D-F】本発明の実施形態による変更例を示すパッケージ化されたチップを示す断面図である。

【図24A】本発明の実施形態によるパッケージ化されたチップをさらに示す断面図である。

【図24B】図24Aに示されているパッケージ化されたチップをさらに示す拡大詳細図

10

20

30

40

50

である。

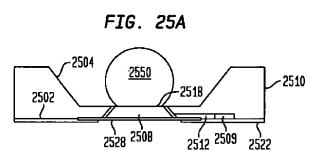

【図25A】本発明の実施形態によるパッケージ化されたチップを示す断面図である。

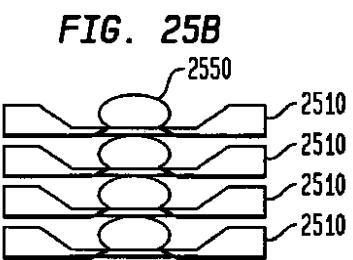

【図25B】図25Aに示されているようなパッケージ化されたチップの複数個を備える積層アセンブリを示す断面図である。

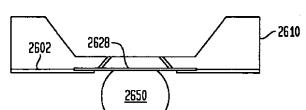

【図26A】本発明の実施形態によるパッケージ化されたチップを示す断面図である。

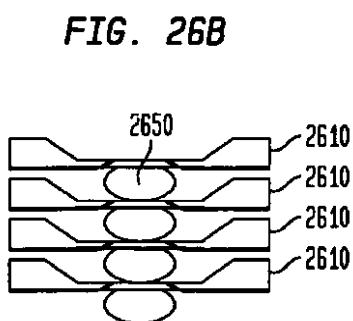

【図26B】図26Aに示されているようなパッケージ化されたチップの複数個を備える積層アセンブリを示す断面図である。

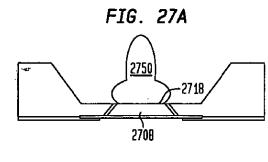

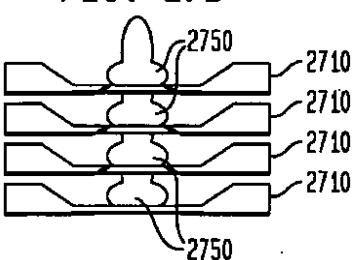

【図27A】本発明の実施形態によるパッケージ化されたチップを示す断面図である。

【図27B】図27Aに示されているようなパッケージ化されたチップの複数個を備える積層アセンブリを示す断面図である。

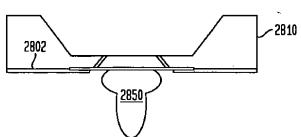

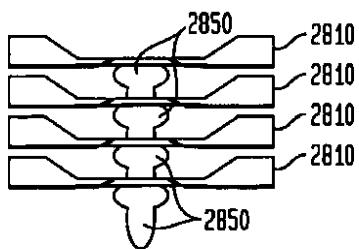

【図28A】本発明の実施形態によるパッケージ化されたチップを示す断面図である。

【図28B】図28Aに示されているようなパッケージ化されたチップの複数個を備える積層アセンブリを示す断面図である。

【発明を実施するための形態】

【0020】

図1は、本発明の実施形態によるパッケージ化された半導体チップ10の断面図である。図1に示されているように、このパッケージ化されたチップは、半導体チップの前面102が下方を向いた方位で示されている。図1に示されているように、このパッケージ化されたチップは、前面102および前面から遠く離れた後面114を有する半導体チップ100を備えている。チップ100の前面は、リッドまたはカバー104によって覆われている。リッド104は、半導体チップ100と組み合わされ、パッケージ化されたチップ10を形成するようになっている。図1に示されているように、半導体チップ100の前面102は、リッド104の上を向いた内面105に向かって、下向きになっている。半導体チップ100は、典型的には、1つ以上の半導体素子112が前面102の下方の素子領域内に配置されている半導体基板を備えている。半導体チップ100は、基板の上に覆い被さっている複数の誘電体層も備え、この誘電体層内に、導電金属配線層およびビア(図示せず)が配置されている。半導体素子112は、チップの前面上および/またはチップの前面と後面との間に配置されている。このパッケージチップは、チップスケールパッケージ(CSP)と呼ばれることもある。何故なら、パッケージ化されたチップ10の(例えば、矢印102の方向における)横寸法が、ベアチップの横寸法と殆ど同じだからである。

【0021】

半導体チップ100は、典型的には、1つ以上の隔離構造体206を介して、リッド104に接続されている。この隔離構造体は、接着剤、無機材料または有機材料、および/または接合金属から構成されているとよい。チップから一定間隔離れてリッドを支持する構造体は、本願の出願人が共有する、2006年1月23日に出願された米国仮出願第60/761,171号および2006年2月21日に出願された米国仮出願第60/775,086号に記載されている。これらの仮出願は、その開示内容を引用することによって本明細書の一部をなすものとする。パッケージ化されたチップは、図1に示されているように、チップの前面102とリッド104の内面105との間に内部空洞106を備えているとよい。代替的に、パッケージ化されたチップ10は、内部空洞を備えずに、構成されていてもよい。空洞が存在する場合、空洞の高さ108および横寸法、例えば、横寸法110は、典型的には、例えば、リッド104を半導体チップ100と組み合わせるために用いられる構造体206の高さおよび横寸法によって決定されることになる。特定の実施形態では、リッド104は、ガラスまたはポリマー材料から本質的に構成され、対象となる電磁周波数スペクトルに対して、少なくとも部分的に透過性を有している。リッド104は、フィルタ機能をもたらすために、部分的に透過性を有していてもよく、または対象となる周波数範囲に対して本質的に透過性を有していてもよい。

【0022】

半導体チップ100内の半導体素子112の例として、典型的には、電磁変換素子、例

10

20

30

40

50

えば、電磁放射線を検出または出力する電磁素子または電気光学素子が挙げられる。半導体素子は、無線周波、および／または赤外線、可視光、および／または紫外線を含む光波長、または高波長スペクトル、例えば、制限されないが、X線波長を放出または受信するように、設計されているとよい。代替的に、半導体素子112は、音響変換素子から構成されてもよい。このような素子は、媒体、例えば、空気および／または他の流体媒体（気体または液体）を介して受信した音圧波を1つ以上の電気信号に変換し、または1つ以上の信号を音圧波に変換するように設計されている。

#### 【0023】

特定の実施形態では、パッケージ化されたチップは、チップ100の半導体素子112が画像を取得する撮像領域107を備えるセンサユニットである。撮像領域107によって取得された画像を表す1つ以上の信号を生成するために、チップ100内の電子回路（図示せず）が、撮像領域107内の半導体素子に接続されている。撮像業界では、この目的を達成するための多くの電子回路がよく知られている。例えば、半導体チップ100は、クロッキング回路および電荷／電圧変換回路のような従来回路を有する一般的に知られている電荷結合素子（CCD）でありうる。

#### 【0024】

図1から分かるように、半導体チップは、この半導体チップ前面に複数の前面接触パッド116を備えている。図1には具体的に示されていないが、素子領域における半導体素子112は、前面接触パッド116に導電的に接続されている。従って、半導体チップ100の1つ以上の誘電体層内にまたはその上方に延在する配線を介して、半導体素子に導電的にアクセス可能である。

#### 【0025】

半導体チップは、後面から角度を付けて配置された表面120を有している。図1に示されているように、表面120は、後面から直角以外の角度で傾斜しているとよい。この勾配は、穏やかな角度、例えば、後面の法線に対して45°未満の角度でもよいし、またはより急峻な角度、例えば、法線に対して45°より大きい角度でもよい。代替的に、表面120は、後面に対して直角であってもよい。表面120は、低くなった後面115で終端している。低くなった後面115は、前面102から離れた方を向き、半導体チップ100の薄い領域105によって、前面102から離間している。

#### 【0026】

導電ビア125が、チップ100の前面102と低くなった後面115との間に延在している。この導電ビアは、前面接触パッド116と、低くなった後面115および表面120の上に覆い被さっている導電トレース126との間を導電的に相互接続している。導電ビア125は、前面と低くなった後面との間に延在する孔127内に配置された誘電体層122の上に覆い被さっている導電層を含んでいる。前面102と低くなった後面との間に、孔127の壁が垂直に、すなわち、前面に対して直角に延在している。代替的に、孔127は、低くなった後面から前面に向かう方向にテープが付されていてもよく、この場合、孔は、低くなった後面から離れるにつれて、細くなる。さらに他の代替例では、孔127は、前面から低くなった後面に向かう方向にテープが付されていてもよく、この場合、孔は、前面から深くなるにつれて、細くなる。以下に示される実施形態の各々は、これらの利用可能な孔形状のいずれか1つを有する孔を備えうる。

#### 【0027】

図1に示されている例では、導電ビア125は、チップの接触パッド116から孔127の壁に沿って上方に延在する導電トレースの形態にあり、これらのトレースは、壁120に沿って上方に延在し、後面114に続いている。代替的に、導電ビア125は、導電材料、例えば、金属で充填された孔127の形態でありうる。このような場合、トレース126を、ビアのそれぞれから壁120に沿って後面114上まで延在させることができる。

#### 【0028】

誘電体層122は、好ましくは、コンフォーマルコーティング（conformal coating）

10

20

30

40

50

された誘電材料から構成されている。好ましくは、コンフォーマルコーティングに裂け目がなく、誘電体層 122 が半導体チップ 100 に対して良好な絶縁分離をもたらすようになつてているとよい。望ましくは、誘電体層 122 は、十分に低い弾性係数および十分な厚みを有して、この弾性係数と厚みとの積によって、追従性 (compliance) をもたらすようなコンプライアント (compliant) 層である。具体的には、このようなコンプライアント層によって、接点 128 および接点に取り付けられたトレース 126 がいくらか曲がることが可能になつてているとよい。このようにして、パッケージ化されたチップ 10 の外部導電バンプ 134 と回路パネル (図示せず) の端子との間の接合は、パッケージ化されたチップ 10 と回路パネル (図示せず) との間の熱膨張係数 (CTE) の不一致による熱歪に良好に耐えることができる。望ましくは、誘電体層 122 の厚みとその弾性係数との積によって得られる追従性の程度は、チップ 100 と回路パネルとの間の熱膨張の不一致によつて導電バンプに作用する歪みを相殺するのに十分なものでありうる。CTE の不一致による熱歪への耐性を高めるために、アンダーフィル (図示せず) が誘電体層 130 の露出面とこのような回路パネルとの間に設けられてもよい。

#### 【0029】

図 1 をさらに参考すると、導電トレース 126 は、導電ビア 125 を、パッケージ化されたチップ 10 の外面の上に覆い被さつてゐる対応するパッケージ接触パッド 128 に導電的に接続している。図 1 に具体的に示されているように、パッケージ接触パッド 128 は、半導体チップ 100 の後面 114 の上に覆い被さつてゐる。導電トレース 126 は、誘電体層 122 の上に覆い被さつて、半導体チップの表面 120 および後面 114 の一部にわたつて延在している。望ましくは、導電トレース 126 は、チップ 100 の個々の前面接触パッド 116 を対応する個々のパッケージ接触パッド 128 に接続している。接触パッド 128 上には、導電バンプ 134 が設けられているとよい。前面と後面との間の超小型電子要素 100 の厚み 160 は、典型的には、 $200 \mu\text{m}$  未満であり、さらに著しく小さくすることができ、例えば、 $130 \text{ nm}$ 、 $70 \text{ nm}$ 、または  $70 \text{ nm}$  未満とすることができます。低くされた面 115 と前面 102 との間の超小型電子要素の厚み 162 は、通常、厚み 160 の半分または半分未満である。望ましくは、低くされた面における超小型電子要素の厚み 162 は、厚み 160 の半分よりも著しく小さくなつてゐるといふ。一例では、厚み 162 は、ほぼ  $10 \mu\text{m}$  である。

#### 【0030】

図 1 にさらに示されているように、第 2 の誘電体層 130 が、導電トレース 126 の上に覆い被さり、導電トレース 126 に対して絶縁分離をもたらしている。この層は、パッケージ 10 の「外部パッシベーション層」 130 と呼ばれることがある。この第 2 の誘電体層は、無機誘電材料、有機誘電材料、またはその両方から構成されているとよい。この第 2 の誘電体は、電着されたコンフォーマルコーティング材、または他の誘電材料、例えば、感光性ポリマー材料、例えば、半田マスク材料から構成されていてもよい。感光性半田マスク材料は、種々の製造業者、特に Shipley 社および Toyo 社から入手可能である。

#### 【0031】

特定の実施形態では、金属層から構成されているかまたは濡れ性金属層を含む複数の金属層の積層から構成されている金属構造 132 が、パッケージ接触パッド 128 の上に覆い被さり、導電バンプ 134 が、この金属構造 132 の上に覆い被さつてゐる。典型的には、導電バンプ 134 は、半田、錫、または複数の金属を含む共晶混合物のような比較的に低融点を有する可融性金属から構成されている。代替的に、バンプ 134 は、濡れ性金属 (例えば、半田または他の可融性金属の融点よりも高い融点を有する銅または他の貴金属または非貴金属) から構成されていてもよい。このような濡れ性金属は、回路パネルのような相互接続要素の対応する特徴部、例えば、可融性金属特徴部に接合され、これによつて、パッケージ化チップ 10 をこのような相互接続要素に外部的に相互接続することができる。他の代替例では、バンプ 134 は、媒体内に散在する導電材料、例えば、導電ペースト、例えば、金属充填ペースト、半田充填ペースト、または等方性導電接着剤、または異方性導電接着剤から構成されている。

10

20

30

40

50

## 【0032】

図2を参照すると、半導体チップ100は、好ましくは、ウエハレベルの処理、すなわち、複数の半導体チップ100が半導体素子ウエハ101の一部または全体として互いに接合されている状態で、これらの半導体チップ100に対して同時に行われる処理によって、同時にパッケージ化されるとよい。図2に示されている製造のこの段階に達した後、リッド104が取り付けられたウエハのアセンブリは、ダイシングレーン12および図2では見えていないダイシングレーンに沿って、個々のパッケージ化された半導体チップに切断されることになる。

## 【0033】

以下、図3A～図10Bを参照して、複数のパッケージ化されたチップ10(図1)を同時に製造する方法について説明する。図3Aに示されているように、半導体素子ウエハまたは複数のチップ100を含む素子ウエハの一部が、素子領域112および前面接点116を有するチップ100の前面102をリッド部材111に向き合わせて、リッド部材111に取り付けられている。望ましくは、リッド部材111は、半導体素子ウエハ101の横方向寸法と同一の横方向寸法(内面105によって画定された面内に延在する方向における寸法)を有している。参考番号12は、個々のチップ100間の境界におけるダイシングレーンの位置を示している。ウエハのダイシングレーン12は、それほど広くなくてもよい。チップ100の接合パッド116の位置は、特定されている必要がなく、通常、接合パッドは、ダイシングレーンから充分に離れている。ダイシングレーンの代表的な幅は、ほぼ40μmである。図3Bの平面図に示されているように、素子ウエハの後面101Aは、チップの前面102の上方に位置している。望ましくは、製造のこの段階では、後面101Aは、素子ウエハの初期厚み272だけ、チップの前面102から均一に離間している。素子ウエハの下部の接合パッド116の位置およびダイシングレーン12の位置が、素子ウエハの後面101Aから見た対応する平面図(図3B)に示されている。

## 【0034】

図3Aにさらに示されているように、隔離構造体206が、素子ウエハ101をリッド部材111の内面105から上方に距離108を隔てて支持している。図3Cは、製造の予備段階を示している。この予備段階において、複数の隔離構造体206が、ダイシングレーン12で互いに結合している個々のリッド要素104を含むリッド部材111の主面から外方に延在して形成されることになる。図3Dからよく分かるように、各隔離構造体206は、典型的には、元のリッド部材111から切断される個々のリッド間の境界に位置する垂直方向を向くダイシングレーン12および水平方向を向くダイシングレーン14の両方に沿った矩形の形状を有している。図3Dに示されているように、隔離構造体206は、「額縁状リング形状」と呼ばれるような形態を有している。前述したように、隔離構造体は、1つ以上の無機誘電材料、有機誘電材料、半導体、1つ以上の金属、金属化合物のような導体、またはこのような材料の組合せをから構成することができる。隔離構造体は、例えば、2004年9月24日に出願された米国特許出願第10/949,674号または米国仮出願第60/761,171号に記載されているように、アディティブな処理またはサブトラクティブな処理、またはこれらの両方によって、製造することができる。なお、これらの開示内容は、引用することにより本明細書の一部をなすものとする。隔離構造体が金属から構成される場合、この隔離構造体は、金属の薄層をスパッタリングするステップ、サブトラクティブなパターンニングを行うステップ、そして、最終金属によって残りの構造体を電気メッキするステップの組合せによって製造することができる。代替的に、隔離構造体は、無電解メッキ、そして、サブトラクティブなパターンニングおよび電気メッキによって形成することもできる。特定の実施形態では、隔離構造体206は、例えば、引用することにより本明細書の一部をなすものとする米国仮出願第60/775,086号に記載されている方法によって、スパッタリングまたはメッキによって形成された既存の導電層上にポリマーを電気泳動堆積することによって形成されている。

## 【0035】

10

20

30

40

50

素子ウエハ 101 を図 3 A に示されているようにリッド要素 111 に接合した後、後面 101 A から、素子ウエハの厚みを薄くすることができる。後面からの研削、ラッピング、あるいは研磨、またはその組合せを用いて、厚みを薄くすることができる。この厚みを薄くさせるプロセス中、半導体チップの前面の上に覆い被さっているリッド要素 104 は、半導体チップを構造的に支持し、半導体チップの剛性を高め、パッケージ化されたチップを必要に応じてより小さい厚みまで薄くするのに役立つことになる。この段階中に、一例として、素子ウエハの厚みを約 700 nm から約 130 nm 以下まで薄くすることができる。

### 【0036】

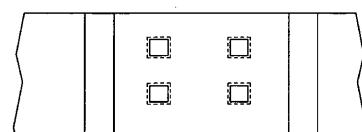

この後、得られた素子ウエハは、図 4 に示されているように、薄くなった厚みを有し、後面 114 は、厚み 274 だけ、各チップ 100 の前面 102 から離れている。次に、図 5 A に示されているように、素子ウエハの後面 114 から前面 102 に向かって下方に延在する凹部 276 が、素子ウエハに形成されることになる。この凹部は、例えば、チップの後面 114 の残すことが望まれる部分にマスク層を形成した後、素子ウエハを選択的にエッチングすることによって形成することができる。例えば、感光層、例えば、フォトレジスト層を堆積させ、後面の一部のみを覆うようにパターン化し、そして、時限式エッチングプロセスを行って、凹部 276 を形成することができる。ダイシングレーン 12 と位置整合して、素子ウエハの全体にわたって直線方向 280 に延在するストライプ 278 として、この凹部を形成することができる。図 6 A から最もよく分かるように、望ましくは、垂直方向に延在するダイシングレーンと位置整合して、素子ウエハの垂直レイアウト方向 280 に延在する多数の細長の凹部 276 が、同時に形成されるとよい。垂直方向に延在する凹部 276 は、それぞれのチップ対のダイシングラインに沿ってのみ延在するように、形成されてもよい。この場合、これらの凹部は、垂直方向ダイシングレーン 12 と素子ウエハの水平方向レイアウト方向に延在する水平方向ダイシングレーン 14 との間の交差点 282 では、チップのコーナ部の上に覆い被さっていなくてもよい。他の例では、水平方向に延在する多数の凹部 284 が、各チップの水平方向ダイシングレーン 14 に隣接する接合パッドの上に覆い被さるように形成されてもよい。垂直方向に延在する凹部 276 と水平方向に延在する凹部 284 の両方が、素子ウエハに形成されてもよい。特定の例では、チップの境界を定めるダイシングレーンの 1 つのみに隣接する接合パッドの上に覆い被さる凹部が形成されてもよい。他の例では、チップの 2 つのダイシングレーンのみの上に覆い被さるかまたはチップの境界を定める 3 つ以上のダイシングレーンのみの上に覆い被さる凹部が形成されてもよい。一例では、凹部は、図 6 A に示されているより小さくなっていてもよい。この場合、これらの凹部は、素子ウエハ 101 のダイシングレーン 12 に隣接している接合パッドの列のいくつかの接合パッドのみの上に覆い被されることになる。図 6 B に示されているさらに他の例では、ダイシングレーン 12 と並んだ凹部 286 が、素子ウエハ 101 のそれぞれの縁 288, 290 間に、ストライプとして延在するようになっていてもよい。

### 【0037】

図 5 A に特に示されているように、各凹部 276 は、望ましくは、低くなった面 502 を有している。この面 502 は、平坦で、前面 102 から等距離に位置している。後面 114 からこの低くなった面に向かって下方に延在する凹部の壁 504 は、傾斜しているとい。すなわち、この壁 504 は、図 5 A に特に示されているように、後面 114 の垂直角度（直角）以外の角度で延在しているとい。湿式エッチングプロセス、例えば、等方性エッチングプロセス、および特にテーパ付きのブレードを用いるソーイング（sawing）を用いて、図 5 A に示されているような傾斜壁 504 を有する凹部を形成することができる。特にレーザダイシング、メカニカルミリングを用いて、傾斜壁を有する凹部を形成することもできる。代替的に、傾斜せずに、これらの壁は、後面 114 から直角に前面 102 に向かって下方に垂直に延在していてもよい。特に、異方性エッチングプロセス、レーザダイシング、レーザドリル加工、機械的な除去プロセス、例えば、ソーイング、ミリング、超音波加工を用いて、本質的に垂直方向の壁を有する凹部を形成してもよい。素子ウ

10

20

30

40

50

エハに凹部を形成した後、フォトレジストのような感光層が、素子ウエハの後部に堆積され、接合パッド 116 と位置整合して低くなった面 502 に重なるマスク開口 506 を形成するようにパターン化されることになる。

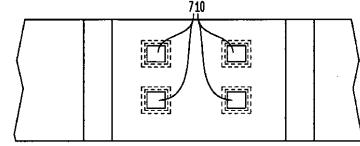

【0038】

そして、図 7A に示されているように、マスク開口の下に位置する半導体材料を除去するため、マスク開口内に露出する低くなった面 502 の部分にエッティングプロセスが施される。その結果、前面接点 116 と接触して、低くなった面内に延在するビア 708 が形成されることになる。このエッティングプロセスは、望ましくは、酸化物材料を残しながら、半導体材料、例えば、シリコンを選択的にエッティングする方法によって行われる。典型的には、チップの前面接点、例えば、チップの接合パッド 116 は、(中間レベルの誘電体層またはチップに絶縁または隔離をもたらす他の目的の層として作用する)酸化物材料またはパッシベーションに用いられる他の誘電材料からなる 1 つ以上の層に重なっている。誘電体を残す選択的な方法によって、半導体材料をエッティングすることによって、必要に応じて、素子ウエハを横切る十分なプロセス窓を維持しながら、素子ウエハの全ての位置において半導体材料の厚みを減じるオーバエッティングを行うことができる。選択的なエッティングプロセスが用いられると、好ましくは、図 7B の部分拡大図に示されているように、ビア 708 を形成した後、誘電体層 710、例えば、酸化物層が適所に残ることになる。代替的に、レーザドリル加工またはメカニカルミリングを用いて、ビア 708 を形成することができるが、この場合、前面接点パッドの表面をビア内に露出させることができる。

10

20

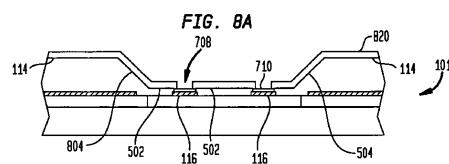

【0039】

そして、図 8A に示されている製造の段階では、誘電体層 820 が、ビアの壁 804、およびチップの壁 504 および後面 114 に形成されることになる。種々の方法を用いて、このような誘電体層を形成することができる。一例では、流動性を有する誘電材料が、チップ 100 を含むウエハ 101 の後面 114 に塗布され、そして、この流動性を有する材料が、「スピンドルコーティング」作業中にウエハの後面の全体により均一に分布され、続いて、乾燥サイクル、例えば、加熱が施されることになる。他の例では、誘電材料からなる熱可塑性膜が素子ウエハ 101 の後面に施されてもよく、そして、ウエハおよびリッド部材を含むアセンブリが加熱され、これによって、この膜を低くなった面 115 上およびビア 708 内に向かって下方に流動させることができる。他の例では、蒸着を用いて、誘電体層を形成してもよい。

30

【0040】

さらに他の例では、リッド要素が取り付けられた素子ウエハを備えるアセンブリが誘電体堆積浴内に浸漬され、誘電体コンフォーマルコーティングまたは層 820 を形成するようになっている。好ましくは、電気泳動堆積技術を利用して、誘電体コンフォーマルコーティングを、アセンブリの露出した導電面および半導電面にのみ堆積されるように、形成するとよい。堆積中、半導体素子ウエハは、所望の電気ポテンシャルに保持され、電極は、異なる所望の電気ポテンシャルに保持された浴内に保持されることになる。そして、アセンブリは、浴内において、適切な条件下で十分な時間にわたって保持され、これによって、素子ウエハの導電性または半導電性の露出面、例えば、制限されないが、後面 114、凹部の壁 504、低くなった面 502、およびビア 708 の壁 804 に沿って、電着された誘電体コンフォーマルコーティング 820 を形成することができる。十分に強力な電場が被覆される表面と浴との間に維持されている限り、電気泳動堆積が生じることになる。電気泳動堆積コーティングは、自己制限的なので、パラメータ、例えば、電圧、堆積の濃度などによって制御されるある厚みに達すると、堆積が停止することになる。電気泳動堆積は、アセンブリの導電性および / または半導電性の外面上に均一なコンフォーマルコーティングを連続的に形成することができる。加えて、電気泳動堆積コーティングは、好ましくは、その誘電(非導電)特性によって、接点 116 を覆って残っている誘電体層 710 には形成されない。換言すれば、電気泳動堆積の特性は、もし誘電材料が十分な厚みを有し、その誘電特性を有しているなら、導体の上に覆い被さっている誘電材料の層上に

40

50

は形成されないことがある。典型的には、電気泳動堆積は、約 10  $\mu\text{m}$  から数 10  $\mu\text{m}$  を超える厚みを有する誘電体層上には生じることがない。

【 0 0 4 1 】

好ましくは、コンフォーマル誘電体層 820 は、陰極エポキシ堆積前駆体から形成されるとよい。代替的に、ポリウレタン堆積前駆体またはアクリル堆積前駆体が用いられてもよい。種々の電気泳動コーティング用前駆体組成物および供給元を以下の表 1 に列挙する。

【 0 0 4 2 】

【表 1】

| Eコートの名称        | POWERCRON 645     | POWERCRON 648    | CATHOGUARD 325 |

|----------------|-------------------|------------------|----------------|

| 製造             |                   |                  |                |

| 製造業者           | PPG 社             | PPG 社            | BASF 社         |

| 種類             | 陰極                | 陰極               | 陰極             |

| ポリマー基          | エポキシ              | エポキシ             | エポキシ           |

| 所在地            | ヒツツバーグ、ペンシルベニア州   | ヒツツバーグ、ペンシルベニア州  | サウスフィールド、ミシガン州 |

| 適用データ          |                   |                  |                |

| Pb/Pf フリー      | Pb フリー            | Pb または Pf フリー    | Pb フリー         |

| HAP, g/L       |                   | 60-84            | 規格準拠           |

| VOC, g/L(マキシム) |                   | 60-84            | <95            |

| 硬化             | 20 分/175°C        | 20 分/175°C       |                |

| 膜特性            |                   |                  |                |

| 色              | 黒                 | 黒                | 黒              |

| 厚み, μm         | 10-35             | 10-38            | 13-36          |

| 鉛筆硬度           |                   | 2H+              | 4H             |

| 浴特性            |                   |                  |                |

| 固形分、重量%        | 20(18-22)         | 20(19-21)        | 17.0-21.0      |

| pH(25°C)       | 5.9(5.8-6.2)      | 5.8(5.6-5.9)     | 5.4-6.0        |

| 導電率(25°C) μS   | 1000-1500         | 1200-1500        | 1000-1700      |

| P/B 比          | 0.12-0.14         | 0.12-0.16        | 0.15-0.20      |

| 稼働温度(°C)       | 30-34             | 34               | 29-35          |

| 時間、秒           | 120-180           | 60-180           | 120+           |

| 陽極             | SS316             | SS316            | SS316          |

| 電圧、ボルト         |                   | 200-400          | >100           |

| Eコートの名称        | ELECTROLAC        | LECTRASEAL DV494 | LECTROBASE 101 |

| 製造             |                   |                  |                |

| 製造業者           | MACDERMID 社       | LVH COATINGS 社   | LVH COATINGS 社 |

| 種類             | 陰極                | 陽極               | 陰極             |

| ポリマー基          | ポリカレタン            | ウレタン             | ウレタン           |

| 所在地            | ウォーターベリー、コネティカット州 | ハーミンガム、英国        | ハーミンガム、英国      |

| 適用データ          |                   |                  |                |

| Pb/Pf フリー      |                   | Pb フリー           | Pb フリー         |

| HAP, g/L       |                   |                  |                |

| VOC, g/L(マキシム) |                   |                  |                |

| 硬化             | 20 分/149°C        | 20 分/175°C       | 20 分/175°C     |

| 膜特性            |                   |                  |                |

| 色              | 透明(+染色)           | 黒                | 黒              |

| 厚み、μm          |                   | 10-35            | 10-35          |

| 鉛筆硬度           | 4H                |                  |                |

| 浴特性            |                   |                  |                |

| 固形分、重量%        | 7.0(6.5-8.0)      | 10-12            | 9-11           |

| pH(25°C)       | 5.5-5.9           | 7-9              | 4.3            |

| 導電率(25°C) μS   | 450-600           | 500-800          | 400-800        |

| P/B 比          |                   |                  |                |

| 稼働温度(°C)       | 27-32             | 23-28            | 23-28          |

| 時間、秒           |                   |                  | 60-120         |

| 陽極             | SS316             | 316SS            | 316SS          |

| 電圧、ボルト         | 40、最大             |                  |                |

## 【0043】

図 8 B は、電気泳動堆積の後、接合パッドの上方のビア 708 が開いた状態にあることを示している。誘電体コンフォーマルコーティングを電気泳動堆積した後、半導体チップの前面接触パッドをパッケージ化されたチップの外側接点に接続する導電トレースを形成

10

20

30

40

50

する処理が開始されることになる。

#### 【0044】

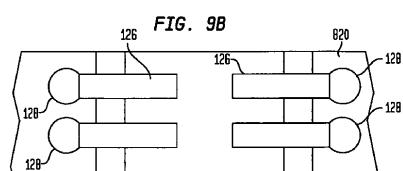

次に、図9A、図9Bを参照すると、基板に対して、導電トレース126およびランド128を形成する処理を行うための準備がなされることになる。もし先の処理によって、誘電体層820がチップの前面接触パッド116を遮っているなら、この段階において、レーザドリル加工、メカニカルミリング、または他の適切な技術を用いて、前面接触パッドに隣接するビアの底を開口することができる。加えて、もしチップの既存の誘電体層710(図8A)の一部が接点116に重なって残っているなら、このような層をこの段階において除去することができる。このような除去は、例えば、レーザドリル加工、メカニカルミリング、または他の適切な技術によって行うことができる。他の有力な除去技術として、種々の選択的エッティングが挙げられるが、これらの選択的エッティングは、事実上、等方性エッティングまたは異方性エッティングでありうる。異方性エッティングプロセスの例として、イオンの流れがエッティングされる表面に向かって導かれる反応性イオンエッティングプロセスが挙げられる。反応性イオンエッティングプロセスは、一般的に、等方性エッティングプロセスよりも選択性が小さく、イオンが高入射角で衝突した表面がイオン流れの方を向いている表面よりも大きくエッティングされることになる。反応性イオンエッティングプロセスが用いられるとき、望ましくは、マスク層が、誘電体コンフォーマルコーティング820の上に覆い被さるように堆積され、ビア708と一直線に並ぶ開口が、このマスク層に形成されるとよい。これによって、エッティングプロセス中に誘電体コーティング820のビア708内に存在する以外の部分が除去されるのを避けることができる。

#### 【0045】

そして、導電トレース126およびランド128が、誘電体コンフォーマルコーティング820の上に覆い被さるように形成されることになる。トレースおよびランドを形成する例示的な方法では、誘電体コンフォーマルコーティング820の上に覆い被さるように、金属層が堆積されるようになっている。代替的に、これらの表面の一部をマスク層によって保護しながら、堆積が行われてもよい。金属層は、好ましくは、主金属層をアセンブリの露出面にスパッタによって堆積させるか、または無電解メッキによって、堆積せるとよい。この段階は、例えば、素子ウエハの後面、壁、および低くなつた面へのプランケット堆積によって行われてもよい。一実施形態では、主金属層は、アルミニウムを含んでいるか、または本質的にアルミニウムから構成されている。他の特定の実施形態では、主金属層は、銅を含んでいるか、または本質的に銅から構成されている。さらに他の実施形態では、主金属層は、チタンを含んでいるか、または本質的にチタンから構成されている。主金属層を形成するプロセスにおいて、1つ以上の他の例示的な金属が用いられてもよい。

#### 【0046】

そして、感光層が主金属層を覆って堆積され、三次元フォトリソグラフィ・パターンニングプロセス、例えば、Badehiに付与された米国特許第5,716,759号に記載されているプロセスを用いて、主金属をパターン化することになる。なおこの特許の開示内容は、引用することにより本明細書の一部をなすものとする。そして、感光層の残りの部分が除去される。その結果、形成されるべき導電トレースの寸法に対応する個々の導電パターンが形成されることになる。主金属を個々のラインにパターン化した後、感光層が素子ウエハから除去され、電気メッキプロセスを用いて、第2の金属層を主金属層上にメッキし、これによって、前面接触パッド116から壁120に沿って半導体チップの後面114上に延在する個々の導電トレース126が形成されることになる。第2の金属の例として、ニッケルまたは他の貴金属が挙げられる。一実施形態では、主金属層上の電気メッキされた第2の金属によって、最終的な導電トレースが得られたことになる。代替的に、耐食性をもたらすために、任意選択的な第3の金属層、例えば、金、プラチナ、またはパラジウムが第2の金属上にメッキされ、これによって、最終的な導電トレースが得られるようになっていてもよい。

#### 【0047】

10

20

30

40

50

続いて、例示的なプロセスでは、付加的な誘電体層 230 が、後面 114 および壁 120 に沿って延在する導電トレース 226 の各々の上に覆い被さるように、堆積されることになる。望ましくは、付加的な誘電体層 230 は、図 8A, 図 8B を参照して前述したような電気泳動堆積プロセスによって、堆積されるとよい。フォトレジスト 酸化物マスク、などを含むパターン化されたマスク層が、接点 128 上に形成される。そして、電気泳動堆積プロセス中、このパターン化されたマスク層によって、得られる誘電体層が接点 128 上に形成されるのを回避することができる。そして、パターン化されたマスク層が除去され、誘電体層 230 の開口内に接点 128 が露出することになる。

#### 【0048】

代替的に、誘電体層 230 を電気泳動堆積法によって堆積する代わりに、誘電体層は、封止材または半田マスク材料のような感光性の誘電体をスピンドルコーティングまたは噴霧コーティングによって素子ウエハの後面 114 および壁 120 に向かって形成し、比較的に均一な厚いコーティングを形成することによって形成されてもよい。そして、フォトリソグラフィプロセスによって、接点 128 と位置整合する開口をコンフォーマルな誘電体層 230 に形成することができる。1つ以上のプロセス、例えば、加熱などによって、誘電体層 230 をこの感光性材料の最初の堆積の後に硬化させるとよい。

#### 【0049】

次に、濡れ性金属層 132、例えば、「バンプ下地金属化」(UBM) が、誘電体層 230 の開口内に、接点 128 の各々と接触して、形成されることになる。1つの例示的なプロセスでは、拡散バリア層、例えば、チタン、タンゲステン、タンタル、または他の同様の金属を含む導電層が、接点 128 と接触して形成される。そして、第1の濡れ性金属を含む層が、バリア層の上に覆い被さるように堆積されてもよい。このような層は、金属、例えば、ニッケル、銅、または他の金属、望ましくは、貴金属から構成されている。耐食性を高めるために、通常は極めて薄い、例えば、0.1 μm の金の層が、濡れ性金属の最終層として堆積されてもよい。濡れ性金属層が形成された後、導電バンプ 134 が、各接点の上方において濡れ性金属層と接触して形成されることになる。半田、錫、共晶組成物のような可融性金属、または導電ペースト、例えば、特に半田充填または銀充填ペーストから構成される導電バンプが形成されるとよい。導電バンプは、1種または複数種の導電材料を含んでいてもよい。特定の例では、導電バンプは、1種または複数種の貴金属、例えば、銅、ニッケルなどを含みうる。一例では、半田、錫、または共晶物のような可融性金属から構成される球状物を濡れ性金属層 132 上に配置し、そして、これらの導電バンプを加熱し、濡れ性金属層 132 に融着させることによって形成されるとよい。

#### 【0050】

最終的に、パッケージ化されたチップは、ソーキングまたは他のダイシング法によって、ダイシングレーン 12 に沿って互いに切断され、図 10A, 図 10B に示されているような個々のパッケージ化されたチップ 10 を形成することになる。パッケージ化されたチップを個々のユニットに切断する種々の例示的なプロセスが、(引用することにより本明細書の一部をなすものとする) 本願の出願人が共有する米国仮出願第 60/761,171 号および第 60/775,986 号に記載されている。パッケージ化されたチップを切断し、図 10A, 図 10B に示されているような個々のパッケージ化チップを形成するために、これらのプロセスのいずれが用いられてもよい。

#### 【0051】

本発明の実施形態によるカメラモジュール 1030 (図 11) は、センサユニット 1020 を備えている。センサユニット 1020 は、センサユニットの後面、すなわち、半導体チップ 1000 の (撮像領域 1026 を支持する前面 1028 と反対側の) 表面に配置された接点 1042 を有している。このセンサユニットは、図 1 を参照して前述したようなものであればよい。同様のセンサユニットおよびカメラモジュールは、本願の出願人が共有する、2005年11月2日に出願された米国特許出願第 11/265,727 号および 2005 年 12 月 30 日に出願された米国特許出願第 11/322,617 号 (これらは、代理人整理番号 TESSERA 3.0 - 381CIP および 3.0 - 464 によつ

10

20

30

40

50

て、さらに特定されている)に記載されている。これらの開示内容は、引用することにより本明細書の一部をなすものとする。センサユニットの接点1042は、半田のような可融導電材料の塊1082によって、回路パネル1070の端子1080に接続されている。

### 【0052】

この構成における光学ユニット1050は、ターレットまたは支持構造1051を備えている。ターレットまたは支持構造1051は、1つ以上のレンズまたは他の光学要素1058を保持するように配置された取付け部1052を有している。支持構造1051は、取付け部1052から後方に突出する細長ポスト1062の形態にある複数の後方要素1062も備えている。これらのポストは、後面1054を有している。後面1054は、センサユニットの基準面に当接するかまたは機械的に係合し、光学ユニットをセンサユニットに対して位置決めするようになっている。図11に示されている例では、後面1054は、撮像領域1026の上に覆い被さっている透明カバー1034の前面に当接している。代替的に、ターレットまたは支持構造は、チップ1000の撮像領域1026に対するターレットの傾斜を制限すると共にチップ1000に対する光学ユニット1050の高さを機械的に設定するために、位置合わせ特徴部、例えば、ポストやピンや凹部などを備えていてもよい。

### 【0053】

ポスト1062の後面と前面1034との間の接続部を水平にし、かつ厚みを均一にすることが望ましい。この目的を達成する他の方法として、金属取付け特徴部およびパッド1055が、カバー1034の外面1036に設けられていてもよい。これらのパッド1055は、例えば、拡散接合によって、ポスト1062の後面1054の金属特徴部に冶金的に接合されるようになっている。代替的に、いくらか薄い接着剤を用いて、ポストの後面をカバーに接合することもできる。

### 【0054】

他の実施形態では、ターレットまたは支持構造1051は、ポストの代わりに、円筒形状または多面形状の空間を囲むまたは実質的に囲む後方要素を備えている。円筒状の壁または多面状(例えば、箱状)の壁を有するこのような後方要素が設けられる場合、後方要素の後面が、カバー1034の外面1036に設けられているセンサユニットの基準面に当接することになる。

### 【0055】

図12に示されている上記実施形態の変更例では、センサユニット1020は、センサユニットの前部、従って、撮像領域1028を回路パネル1070の後面または底面に向かって前方に向けて、取り付けられている。センサユニットの接点1042は、適切なリードまたはワイヤボンド1002によって、回路パネルの導体1076に接続されている。この実施形態では、光学ユニット1050の後方要素1062は、撮像領域1028と一直線に並んだ回路パネルの孔1072内に突出している。換言すると、孔1072は、光学要素から撮像領域への光経路を含むと共に、後方要素1062を収容するのにも十分大きくなっている。同様の構成が、前述したように、前面に接点を有するセンサユニットと共に用いられてもよい。

### 【0056】

本発明のさらに他の実施形態によるカメラモジュール(図13)は、回路パネル970の底側または後側に配置された、破線で描かれている、センサユニット920を備えている。ここでも、センサユニットのチップの撮像領域は、回路パネルの孔972と一直線に並んでいる。この構成における光学ユニット950は、1つ以上のレンズまたは他の光学要素958を保持するように配置された取付け部902を有するターレット(turret)または支持構造952を備えている。支持構造952は、取付け部902から後方に突出する細長ポストの形態にある複数の後方要素962も備えている。これらのポストは、回路パネルの開口974を貫通し、センサユニットと機械的に係合し、前述したように、光学ユニットをセンサユニットに対して位置決めするようになっている。ここでも、ポストは

10

20

30

40

50

、ポスト間の間隙、例えば、ポスト 9 6 2 a , 9 6 2 b 間の間隙 9 6 3 a を画定している。ここでも、回路パネル 9 7 0 は、これらの間隙内に延在しているとよく、従って、センサユニットと光学ユニットとの間に延在しているとよく、これによって、前述したように、センサユニットへの接続を容易にしている。図 1 3 の実施形態では、これらの間隙は、かなりの高さを有している。完成したアセンブリにおける間隙の高さ  $H_G$  は、回路パネル 9 7 0 の前面 9 0 1 の上方の取付け要素 9 0 2 の高さに等しくなっている。高さ  $H_G$  は、望ましくは、約 2 mm 以上、さらに望ましくは、約 5 mm 以上、最も好ましくは、約 1 cm 以上である。各間隙の幅（すなわち、後方要素 9 6 2 a , 9 6 2 b 間の回路パネルに平行の水平距離）も、望ましくは、少なくとも約 2 mm 、さらに望ましくは、少なくとも約 5 mm 、最も望ましくは、少なくとも約 1 cm である。以下にさらに述べるように、このように大きい間隙を設けることによって、完成したアセンブリへの作業を行うために光学要素と孔 9 7 2 との間の領域内にアクセスすることが可能になる。この大きな間隙は、アセンブリの全体の高さを大きくすることなく、設けることができる。レンズ 9 5 8 のような光学要素とセンサユニットとの間の距離は、システムの光学的特性、例えば、レンズ 9 5 8 の焦点距離によって、設定されるものである。従って、レンズは、いずれにしても、回路パネルの前方にかなりの距離を隔てて支持されねばならないからである。10

#### 【 0 0 5 7 】

図 1 3 の実施形態によるモジュールまたはアセンブリは、組立の後、1 つ以上の間隙を介して、望ましくは、回路パネルの貫通孔 9 7 2 も介して、センサユニットへの作業を行うことによって処理することができる。例えば、アセンブリに対して、クリーニング作業を施すことができる。この作業では、クリーニング液、クリーニング用具、またはその両方が、1 つ以上の間隙および貫通孔 9 7 2 内に挿入され、センサモジュールの表面を洗浄するようになっている。例えば、センサモジュールが、回路パネルの後面または底面に向かって前方を向いているカバーを含んでいる場合、（センサチップの撮像領域と一直線に並んだ領域を含む）孔と一直線に並んだカバーの領域を洗浄することができる。完成したアセンブリに対してこのようなクリーニング作業を行う能力は、アセンブリプロセス中の汚染の影響を弱くするものである。これによって、より高い品質のカメラユニットをもたらすことができると共に、組立中の条件をいくらかの汚染が許容されるように緩和することもできる。例えば、「クリーンルーム」環境を不要とすることができ、または代替的に、安価なより低品質のクリーンルームを用いることができる。さらに他の例では、センサユニットは、別体のカバーを組み込む必要がなく、その代りに、撮像領域およびパッシベーション層を有する「ベア」半導体チップのみから構成されていてもよい。なお、パッシベーション層は、組立プロセス中にベアチップを化学的損傷または機械的損傷から保護するのに有効な薄いコーティングの形態にある。このようなベアの撮像チップは、典型的には、1 つ以上の撮像要素の上への埃の堆積を避けるために、取扱い中、極めて厳しい予防策が必要である。カバーを組み込んでいるセンサユニットの場合、これらの要件がいくらか緩和されることになる。しかし、組立後に後クリーニングを行うことによって、カバーを組み込でいないセンサユニットのアセンブリに対しても、これらの要件を緩和させることができる。20

#### 【 0 0 5 8 】

本発明のさらに他の実施形態による方法では、センサユニットは、センサユニットの前面の上に覆い被さる犠牲層、例えば、カバーを備えているセンサユニットにおけるそのカバーの外面の上に覆い被さる犠牲層、またはカバーを備えていないセンサユニットにおけるチップの撮像領域の上に覆い被さる犠牲層を備えているとよい。まず、犠牲層が適所に配置されたアセンブリが製造される。そして、この完成したアセンブリに、犠牲層またはセンサユニットの撮像領域と一直線に並んだ犠牲層の少なくとも一部を、孔 9 7 2 を通してまたは支持構造 9 5 2 の1つ以上の間隙 9 6 3 を通して、除去する作業が施されることになる。例えば、犠牲層は、犠牲層を溶解することによって、または犠牲層に機械的に係合させ、その犠牲層をセンサユニットから外に剥離することによって、除去されるとよい。犠牲層の除去によって、その層上に溜まった汚染物を除去することができる。30

## 【0059】

1つ以上の間隙を通して、他の作業が行われてもよい。例えば、工具を1つ以上の間隙内に挿入し、回路パネルの導体に係合させ、それらの導体をセンサユニットの接点に接合させるようにしてもよい。代替的に、ワイヤボンディング工具を用いて、孔972、または1つ以上の付加的な開口974、またはこの目的のために回路パネルに設けられた他の開口(図示せず)を通して、導体とセンサユニットとの間に延在するワイヤボンドをもたらすようにしてもよい。

## 【0060】

前述したような大きな間隙をもたらすために、ポスト状の後方要素を設けることは、必要不可欠なものではない。例えば、後方要素は、板またはリブの形態であってもよい。また、多数の間隙を設けることは、必要不可欠なものではなく、作業によっては、1つの間隙のみで十分な場合もある。

10

## 【0061】

図14は、本発明の他の実施形態による光学ユニットまたはカメラモジュールを示している。この実施形態では、センサユニット1120は、カバー1128の外面1138の上に覆い被さっている回路パネル1170の端子1144に、例えば、半田塊1146を介して、導電的に接続された接点1142を有している。カバーの壁1130は、好ましくは、壁の縁部1132の半径が穏やかで、好ましくは、チップの前面1102に設けられた一連の第1の接点1134と壁1130との間の滑らかな移行をもたらすように、傾斜している。一連の導電トレース1156が、第1の接点1134から壁1130に沿ってカバー1128の外面1138上に延在し、接点1142に導電的に接続されている。誘電体コティング1158、例えば、好ましくは、電気泳動堆積によって堆積されたエポキシ材料または他のポリマー材料が、導電トレース1156の上に覆い被さり、パッセーション層、例えば、接点1142の上方に露出した開口を有する半田マスクとして利用されることになる。

20

## 【0062】

図12を参照して前述した例におけるように、光学ユニット1150は、一連の後方要素1162を有している。これらの後方要素1162は、光学要素1158を支持する構造から後方に延在している。光学要素1158の例として、例えば、レンズ、または特に屈折要素または回折要素、フィルタ、反射鏡、および散乱体から選択された他の光学要素が挙げられる。ここでも、後方要素の後面1164は、回路パネルの孔1172貫通し、カバー1128の外面1138、またはセンサユニット1120の他の基準面と当接または係合するのに適するようになっている。

30

## 【0063】

前述の実施形態では、回路パネルは、センサユニットの撮像領域と一直線になってパネルを貫通する孔を有している。このような孔は、回路パネルに透明領域を形成することになる。他の実施形態では、回路パネルは、センサユニットの撮像領域と一直線に並んだ固体の透明領域を備えている。例えば、回路パネルは、透明な誘電材料から形成されていてよい。この場合、回路パネルの導体を、透明領域を横切らないように配線することによって、回路パネルの透明領域を簡単に得ることができる。

40

## 【0064】

図15は、パッケージ化されたチップ10(図1)の変更例によるパッケージ化されたチップ1500を示す断面図である。図15に示されているように、チップの外部接点1528は、チップの低くなった面によって画定されたチップの棚1515に露出されている。この場合、外部接点1528は、半導体チップの縁1502に隣接して配置されている。回路パネルのような外部要素への相互接続は、ボンドワイヤ1530の第1の端を外部接点1528に接続させ、ボンドワイヤ1530の第2の端を回路パネル1540の端子1532に接続させることによって、得られることになる。回路パネルは、チップの光電子要素1512、例えば、イメージセンサと位置合わせされた開口1542を有している。代替的に、ボンドワイヤに代わって、導電塊、例えば、半田塊、半田ボールなどを用

50

いて、接点 1528 をチップの後面 114 の上方に配置された外部要素に相互接続するこ

ともできる。

【0065】

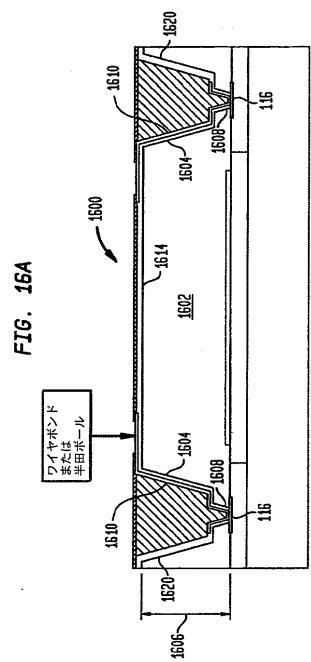

図 16A は、パッケージ化されたチップ 10 (図 1) の変更例によるパッケージ化され

たチップ 1600 を示す断面図である。この実施形態では、チップ 1602 の大きい開口

1604 が、チップの厚み 1606 の大部分にわたって延在し、ビア 1608 が、大きな

開口 1604 内から前面導電接点 116 に延在している。大きな開口 1604 は、ビア 1

608 のそれぞれに重なる孔の形態で設けられてもよいし、または代替的に、図 6A に示

されているように、各チップの接合パッドの 1 つ以上の列にわたって延在する溝の形態で

設けられてもよいし、またはチップを含むウエハの全長にわたって延在する溝 (図 6B)

の形態で設けられてもよい。望ましくは、ウエハの形態にあるときのチップの厚み 160

6 は、図 16A に示されているパッケージ化されたチップを形成するステップを実施する

前に、その元の厚みから薄くされているとよい。例えば、チップを含む素子チップは、素

子ウエハを対応するリッド要素に接合する前に約 200 μm の厚みを有するように、後面

からの研磨またはラッピングによって、薄くすることができる。もしウエハをリッド要素

に接合した後に、研磨が行われるなら、厚みをさらに一層、例えば、50 μm の厚みまで

薄くすることができる。

10

【0066】

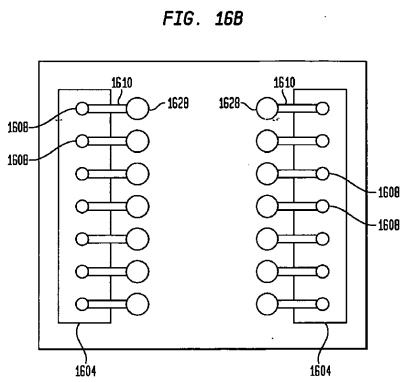

図 16A に示されている例では、導電トレース 1610 が、チップの接合パッド 116

からビア 1608 の壁および開口 1604 の壁に沿って上方に延在している。代替的に、

ビア 1608 を導電材料によって充填することもできる。このような場合、トレース 16

10 は、ビアのそれぞれから、いくつかのビアによって共有されている開口 1604 の壁

に沿って上方に延在することができる (後面からみた平面図 (図 16B) を参照)。トレ

ース 1610 は、チップ 1602 の後面 1614 の上に覆い被さる位置において外部接点

1628 に接続されている。図 1 および図 15 ~ 図 24B は、小さい充填ビア 1908 (例

えば、図 19A) またはビア (例えば、ビア 1608) に沿って延在するトレースを有

する実施形態を示しているが、いずれの場合も、導電性ビアの代替的な構造と互いに取り

換えることができる。

20

【0067】

代替的に、各大きい開口 1604 がその内部に 1 つしかビアを有していないとき、ビア

1608 および大きい開口 1604 が、ビア 1608 の壁および開口 1604 の壁に配置

された誘電体層 1620 の上に覆い被さる導電材料によって充填されてもよい。

30

【0068】

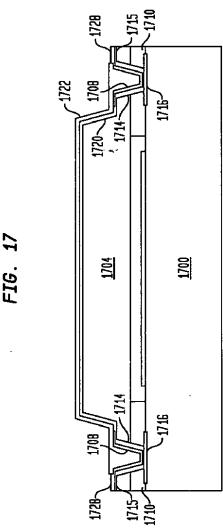

図 17 は、図 15 を参照して前述した実施形態の変更例によるパッケージ化されたチ

ップを示している。この例は、チップではなく、むしろ任意選択的な透過性リッドが、その

縁に隣接する低くなつた面によって画定された棚 1715、および棚上に配置された接点

1728 を有している点において、図 15 に示されている例と異なっている。図 17 は、

1 つ以上の誘電体層 1720, 1722、例えば、スピンドルコートされた誘電体、半田マス

クなどがリッドの上面にわたって延在し得る実施形態を示している。しかし、もしリッド

1704 が一般的に誘電特性を有しているなら、このような誘電体層は、必要ではなく、

大抵の場合、省略されていてもよい。また、図 17 に示されているように、リッドの内面

1706 は、支持構造体 1710 によって、チップの前面 1702 から離間されている。望ましくは、

ビアは、リッドを含むリッドウエハがチップ 1700 を含む素子ウエハに支持構造体 1710

を介在させて接合された後に、形成されるとよい。前述したような種々のエッティングプロセス、

ミリングプロセス、レーザプロセス、または機械的ドリル加工プロセスを用いて、リッド

および支持構造体 1710 に孔 1714 を形成し、接点 1716 を露出させ、そして、ビアが金属化され、

接点 1728 やトレース 1708 などが形成されることになる。

40

【0069】

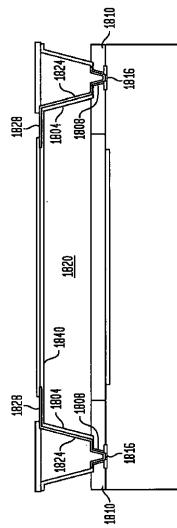

図 18 は、図 17 に示されている実施形態の変更例によるパッケージ化されたチップを

50

示している。この変更例は、図16A、図16Bに示されている実施形態とも類似性を有している。この実施形態では、リッドの大きな開口1804の壁に沿って延在するトレース1824は、第1の端において金属化されたビア1808に接続され、第2の端においてリッド1820の上面1844の上に覆い被さっている外部接点1828に接続されている。ビアは、支持構造体1810を通じて、チップの導電接点1816まで延在している。外部要素への電気的な相互接続は、外部接点1828に取り付けられたボンドワイヤを介して、または半田塊、例えば、半田ボール、バンプ、などによって、得られることになる。

#### 【0070】

図19Aは、本発明の他の実施形態による積層可能なチップスケールのパッケージ化されたチップ1910を示す断面図である。パッケージ化されたチップの例として、ダイナミック・ランダム・アクセス・メモリ(DRAM)のような特定形式の超小型電子素子が挙げられる。パッケージ化されたチップ1910は、チップ1901の前面1902から内方に延在する導電ビア1908が、チップの後面1914の大きな開口の壁に沿って延在するトレース1924と接続している点において、前述のパッケージ化されたチップ1600(図16A)と類似の構造を有している。しかし、パッケージ化されたチップ1910は、前面の上に覆い被さるリッドを備えず、導電ビア1908は、チップ1901の前面に沿って延在する再分配トレース1912を経由して接合パッド1909に接続されている。図19Bは、このパッケージ化されたチップの後面1914から見た対応する平面図である。図19Aは、図19Bの線19A-19A'に沿った断面図である。図19Bに示されているように、トレース1924は、ビア1908から大きな開口1904の壁1926に沿って後面1914上まで上方に延在している。トレース1924は、チップの後面1914の上に覆い被さっている外部接点1946に接続されている。図19Cを参照すると、チップ1901の前面から見た平面図が示されている。このチップの例として、例えば、DRAMが挙げられる。DRAMでは、接合パッド1909は、典型的には、メモリ回路1920間に列をなして設けられている。図19Aは、図19Cの線19A-19A'に沿った断面図である。前面1902の再分配トレース1912は、接合パッド1909を導電ビア1908に接続している。トレースは、図19B、19Cに示されているように配置されることが可能である。すなわち、いくつかのトレースは、導電ビアから第1の方向に延在し、他のトレースは、導電ビアから第2の方向に延在し、第2の方向は、第1の方向と逆になっている。このようにして、導電ビアの左側の接合パッドは、いくつかの導電ビアに接続され、導電ビアの右側の接合パッドは、他の導電ビアに接続されている。

#### 【0071】

図19Aを再び参照すると、導電ビア1908は、チップの前面1902から後面1914に向かう方向に小さくなるように、テーパが付されている。これらの導電ビアは、誘電体層1922によって、チップの半導体材料から絶縁されている。パッシバーション層1930が、導電ビア1908を含むチップの前面1902の上に覆い被さっている。この誘電体層の開口1934から、チップの前面の接点1936が露出している。望ましくは、前面接点1936は、接合パッド1909と位置合わせされていないが、位置合わせされていてもよい。

#### 【0072】

トレース間に電気的隔離をもたらすと共にパッケージ化されたチップ1901に機械的支持をもたらすために、望ましくは、誘電性充填材料1940が、大きな開口1904内のトレース1924の上に覆い被さっている。望ましくは、誘電体層1942、例えば、半田マスクが、トレース1924の上に覆い被さっている。この誘電体層の開口1944から、チップの後面接点1946が露出している。

#### 【0073】

前面接点1936および後面接点1946の両方を設けることによって、いくつかのパッケージ化されたチップを互いに上下に積層し、パッケージ化されたチップの積層アセン

10

20

30

40

50

ブリ 1950 を形成することができる（図 19D）。このような構成では、前面接点は、後面接点と一直線に並んでいる。積層アセンブリ内のパッケージ化されたチップの互いに隣接するものの間の接続は、導電塊を介して行われている。前面の誘電体層 1930 および後面の誘電体層 1942 は、相互接続がなされている箇所を除いて、アセンブリ内の互いに隣接するパッケージ化されたチップ 1910 間に電気的隔離をもたらしている。

#### 【0074】

積層アセンブリ 1950 の利点は、前面接点および後面接点が、パッケージ化されたチップにおける大きい開口 1904 からずれていることがある。従って、パッケージ化されたチップを相互接続するときに積層アセンブリに加えられる圧力は、主に、大きな開口から遠く離れた位置における接点に作用することになる。このような構成は、（大きな開口を形成するために半導体材料を除去したことによって、半導体チップが脆弱になっている可能性がある）パッケージ化されたチップの大きな開口に、圧力が作用するのを回避するのに役立つことになる。

#### 【0075】

開口からずれた接点を有する 1 つの有力な利点は、チップの実際の接合パッドと前面接点および後面接点との間に再分配トレースを設けることができることがある。ある形式のメモリ、例えば、DRAM のチップ選択特徴では、チップのいくつかの接合パッドが、それらの直上に重なっている他のチップの接合パッドに接続されていないことを必要とする。

#### 【0076】

図 19E は、図 19A ~ 図 19C において示されている実施形態の変更例を示す断面図である。この場合、後面接点 1946' は、後面における大きな開口 1904 の左側および右側の両方に露出している。同様に、前面接点 1936' は、前面における開口 1904 の左側および右側の両方に露出している。トレース 1926' が、これらの 2 つの後面接点 1946' を同じ導電ビア 1908 に接続している。図 19F は、これに対応する積層アセンブリを示す断面図である。この積層アセンブリでは、導電塊 1952' が、大きな開口の左側および右側のそれぞれの前面接点を大きな開口の左側および右側のそれぞれの後面接点に接合している。図 19E, 図 19F に示されている構成の他の有力な利益は、パッケージ化されたチップ間のインダクタンスが低減することにある。何故なら、互いに隣接するチップ間に流れる電流は、信号ごとに一組の左右接点内を通過するからである。

#### 【0077】

図 20A は、DRAM 形式の積層可能なパッケージ化されたチップ 1910 の利点を示す断面図である。DRAM 形式の半導体チップは、チップの前面から上方に延在する高アスペクト比トレンチ 1960 の形態にあるキャパシタを備えている。多くの場合、チップの接合パッドは、このようなトレンチキャパシタのアレイ 1962 に近接して配置されている。パッケージ化されたチップ 1910 では、前面接点と後面接点との間の相互接続は、トレンチキャパシタアレイ 1962 からいくらか離れた大きな開口を通して行われるようになっている。図 20B を参照すると、積層体内の互いに隣接するチップ 1910 間の相互接続は、トレンチキャパシタアレイの配置または機能を干渉しないように、チップ内に延在する相互接続部を用いて得られることになる。

#### 【0078】

導体ビアと大きな開口内のトレースとの間の相互接続は、種々の方法によって達成することができる。図 21A は、この相互接続の一例を示している。図 21B の拡大図に示されているように、前面 2102 から上方に延在するように形成された導電ビア 2108 は、金属によって充填されている。例えば、前面から孔をエッチングした後、金属の比較的薄い層をスパッタさせ、孔の壁および底を覆うことができる。そして、電気メッキを用いて、金属充填部を形成することができる。図 21B に示されているように、大きな開口 2104 は、化学エッチング法、例えば、導電ビアを形成している金属を保護しながら半導体材料を選択的にエッチングする方法によって、形成されることになる。開口 2104 をオーバーエッチングする結果として、導電ビアの上面 2170 が十分に露出することになる。

10

20

30

40

50

そして、誘電体層 2122 が形成され、そして、例えば、レーザを用いることによって、開口がビア 2108 の上に覆い被さっている誘電体層に形成されることになる。レーザは、ビアの上面の全体から誘電体層を選択的に除去することができる。何故なら、ビアの上面の誘電体層は、大きな開口の底 2106 の上に覆い被さっている誘電体層の焦点面とは、異なる焦点面にあるからである。続いて、導電トレース 2124 が形成されると、このトレースは、ビア 2108 の上面の全体と接触することになる。

#### 【0079】

図 22A は、相互接続の他の例を示している。図 22B の拡大図に示されているように、大きい開口 2204 は、導電ビアを形成した後、ソーリングによって形成されることになる。そして、誘電体層 2222 が形成された後、レーザを用いることによって、開口が誘電体層内に形成されることになる。この例では、レーザ開口は、誘電体層が開口の底 2206 の半導体材料と接触する箇所における開口の形成を避けるために、寸法が制限されている。

10

#### 【0080】

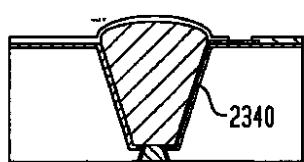

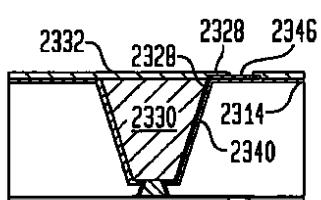

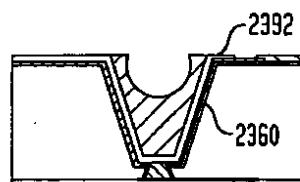

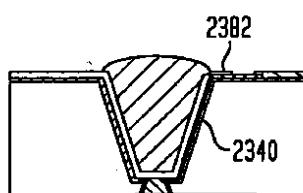

図 23A ~ 図 23F は、チップの大きな開口内に導電トレースを形成した後、大きな開口を充填する種々の代替例を示す断面図である。図 23A に示されているように、導電トレースを形成した後、流動性の誘電性充填材料 2330 が、チップの大きな開口内または後面上に配置または計量供給されることになる。流動性の誘電材料は、例えば、スピニングまたは熱処理によって、開口内に分配され、これによって、充填材料が、開口 2304 を充填し、後面 2314 と略同じ高さの面をもたらすことになる。そして、半田マスク 2332 が、充填材料 2330 およびトレース 2328 の上に覆い被さるように、配置されることになる。この半田マスクの開口から、後面接点 2346 が露出している。図 23B は、代替例を示している。この代替例では、充填材料 2340 は、大きい開口よりも大きい容積を有しているので、後面 2314 の上方に突出することになる。代替的に、充填材料 2340 は、均一に分布されていないとき、後面 2314 の上方に突出することがある。図 23C は、充填材料 2350 の容積が開口 2304 の容積よりも小さいとき、または充填材料 2350 が均一に分布されていないときの他の例を示している。

20

#### 【0081】

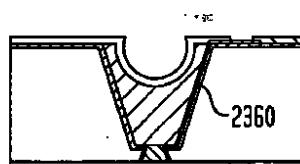

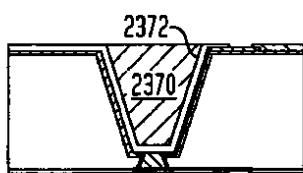

図 23D は、図 23A に示されている例と類似している他の代替例を示している。しかし、この例では、充填材料 2370 が堆積される前に、半田マスク層 2372 が配置されている。図 23E は、図 23B に示されている例と類似している例を示している。しかし、この例では、充填材料 2380 が堆積される前に、半田マスク層 2382 が配置されている。最後に、図 23F は、図 23C に示されている例と類似している例を示している。しかし、この例では、充填材料 2390 が堆積される前に、半田マスク層 2392 が配置されている。

30

#### 【0082】

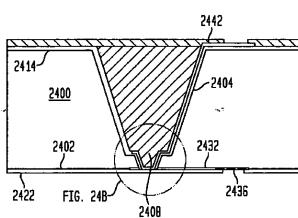

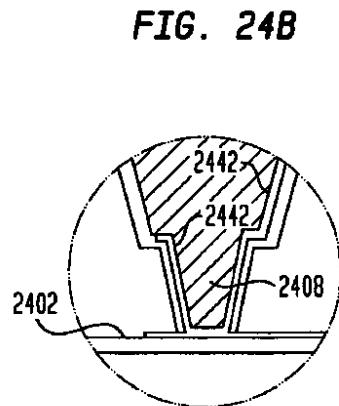

図 24A は、図 19A ~ 図 19C に示されているパッケージ化されたチップの変更例を示す断面図である。図 24B は、図 24A の導電ビア 2408 を示す拡大図である。この変更例では、導電ビア 2408 は、チップの前面 2402 に向かう方向に沿って開口内に施されるプロセスによって、形成されるようになっている。この場合のプロセスは、図 16A, 図 16B を参照して前述したプロセスに類似している。製造中、前面接点 2436、トレース 2432、および誘電体層 2422 を前面に形成した後、チップ 2400 を含む素子ウエハを一時的にキャリアウエハ(図示せず)上に前面を下向きにして取り付けることができる。大きな開口を形成した後、例えば、レーザ穿孔、エッティング、メカニカルミリング、などによって、大きな開口内からビア用の孔を形成することができる。孔が形成されるとき、キャリアウエハは、導電トレース 2402 を孔の底の適所に保持するのを助長する機械的な支持を導電トレース 2402 にもたらすことができる。続いて、ビアおよび大きな開口を同時処理によって金属化し、ビアおよび大きな開口内から後面 2414 上に延在する導電トレース 2442 を形成することができる。

40

#### 【0083】

50

図19A～図19Cを参照して前述したパッケージされたチップ1910の他の変更例として、図25Aは、半田ボール2550の形態にある露出したチップ対チップ相互接続部を有するチップ2510を示している。この実施形態では、半田ボール2550は、大きな開口2504内の導電ビア2508の上面2518に接合されている。導電ビアは、例えば、導電トレースを経由して、チップ2510の前面2502上の接合パッド2509または他の接点に導電的に接続されているとよい。パッシベーション層2522が、導電トレース2512および接合パッド2509の上に覆い被さっている。このパッシベーション層2522は、導電ビア2508と位置合わせされた開口を有している。図25Bは、図25Aに示されている複数のチップ2510を備える積層アセンブリを示している。各チップは、隣接するチップにそれらの間に位置する半田ボール2550を介して相互接続されている。

10

#### 【0084】

図26Aは、図25Aに示されている実施形態の変更例を示している。この変更例では、半田ボール2650が、チップの前面2602の下方に下向きに突出するように、導電ビア2608の底面2628に接続されている。図26Bは、複数のチップ2610を備える積層アセンブリを示している。複数のチップは、互いに隣接するチップ2610間に介在する半田ボール2650を介して互いに導電的に接合されている。

#### 【0085】

図27Aは、図25Aに示されている実施形態の他の変更例を示している。この変更例では、スタッドバンプ2750、例えば、本質的に金または他の金属からなるスタッドバンプが、導電ビア2708の上面に接合されている。図27Bは、これに対応する積層アセンブリを示している。この積層アセンブリでは、スタッドバンプ2750が、チップの互いに隣接するものを導電的に相互接続している。

20

#### 【0086】

図28は、図26Aに示されている実施形態と類似しているさらに他の変形例を示している。この変形例では、スタッドバンプが、チップの前面2802から下方に突出するように、導電ビアの底面に接合されている。図28Bは、これに対応する積層アセンブリを示している。この積層アセンブリでは、図28Aに示されているチップ2810は、スタッドバンプ2850によって導電的に相互接続されている。

#### 【0087】

ここでは本発明を特定の実施形態を参照して説明したが、これらの実施形態は、本発明の原理および用途の単なる例示にすぎないことを理解されたい。従って、例示的な実施形態に対して、多くの修正がなされてもよいし、添付の請求項に記載されているような本発明の精神および範囲から逸脱することなく、他の構成が考案されてもよいことを理解されたい。

30

#### 【0088】

例えば、本発明の特定の実施形態では、導電トレースは、半導体チップの前面の導電特徴部からリッドの縁に沿って、または半導体チップを覆っているリッドに形成された開口の壁に沿って、カバー要素の外面上に延在するようになっていてもよい。

【 図 1 】

【 図 2 】

### 【図3A】

【図3D】

【 図 4 】

### 【図 5 A】

【図3B】

### 【図3C】

【図5B】

### 【図 6 A】

【図 6 B】

FIG. 6B

【図 7 A】

FIG. 7A

【図 7 B】

FIG. 7B

【図 7 C】

FIG. 7C

【図 8 A】

FIG. 8A

【図 9 B】

FIG. 9B

【図 8 B】

FIG. 8B

【図 10 A】

FIG. 10A

【図 9 A】

FIG. 9A

【図 10 B】

FIG. 10B

### 【図11】

## 【図12】

【図14】

【 図 1 3 】

【図15】

【図 16A】

FIG. 16A

【図 16B】

FIG. 16B

【図 17】

FIG. 17

【図 18】

FIG. 18

【図 19A】

FIG. 19A

【図19B】

FIG. 19B

【図 19C】

### 【図19D】

FIG. 19C

FIG. 19D

【図19E】

FIG. 19E

【図19F】

FIG. 19F

【図20A】

FIG. 20A

容量トレンチ

【図20B】

FIG. 20B

【図21A】

FIG. 21A

FIG. 21B

【図21B】

FIG. 21B

【図22A】

FIG. 22A

FIG. 22B

【図 2 2 B】

FIG. 22B

【図 2 3 B】

FIG. 23B

【図 2 3 A】

FIG. 23A

【図 2 3 C】

FIG. 23C

【図 2 3 D】

FIG. 23D

【図 2 3 F】

FIG. 23F

【図 2 3 E】

FIG. 23E

【図 2 4 A】

FIG. 24A

【図 24B】

【図 25A】

【図 26B】

【図 27A】

【図 25B】

【図 26A】

【図 27B】

【図 28A】

【図28B】

FIG. 28B

---

フロントページの続き

(74)代理人 100142996

弁理士 森本 聰二

(74)代理人 100154298

弁理士 角田 恭子

(72)発明者 ハーバ, ベルガセム

アメリカ合衆国カリフォルニア州 95134, サン・ノゼ, オーチャード・パークウェイ 302

5, テッセラ, インコーポレイテッド気付

(72)発明者 ホーナー, ケネス・アレン

アメリカ合衆国カリフォルニア州 95134, サン・ノゼ, オーチャード・パークウェイ 302

5, テッセラ, インコーポレイテッド気付

(72)発明者 タッカーマン, デイヴィッド・ビー

アメリカ合衆国カリフォルニア州 95134, サン・ノゼ, オーチャード・パークウェイ 302

5, テッセラ, インコーポレイテッド気付

(72)発明者 オガネシャン, ヴェイジ

アメリカ合衆国カリフォルニア州 95134, サン・ノゼ, オーチャード・パークウェイ 302

5, テッセラ, インコーポレイテッド気付

審査官 山本 雄一

(56)参考文献 特開2002-217331 (JP, A)

特開2005-101268 (JP, A)

特開平08-213427 (JP, A)

特開2005-216921 (JP, A)

特開2002-016178 (JP, A)

特開2005-209967 (JP, A)

特開2001-085559 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 23/12-23/15

H01L 21/3205

H01L 21/768

H01L 23/522