(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5868545号

(P5868545)

(45) 発行日 平成28年2月24日(2016.2.24)

(24) 登録日 平成28年1月15日(2016.1.15)

|                       |                |

|-----------------------|----------------|

| (51) Int.Cl.          | F 1            |

| HO4N 5/3745 (2011.01) | HO4N 5/335 745 |

| HO4N 5/374 (2011.01)  | HO4N 5/335 740 |

| HO4N 5/369 (2011.01)  | HO4N 5/335 690 |

| HO4N 5/378 (2011.01)  | HO4N 5/335 780 |

請求項の数 21 (全 21 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2015-507211 (P2015-507211)  |

| (86) (22) 出願日 | 平成25年4月19日 (2013.4.19)        |

| (65) 公表番号     | 特表2015-518696 (P2015-518696A) |

| (43) 公表日      | 平成27年7月2日 (2015.7.2)          |

| (86) 国際出願番号   | PCT/US2013/037319             |

| (87) 国際公開番号   | W02013/158965                 |

| (87) 国際公開日    | 平成25年10月24日 (2013.10.24)      |

| 審査請求日         | 平成27年11月19日 (2015.11.19)      |

| (31) 優先権主張番号  | 61/635,751                    |

| (32) 優先日      | 平成24年4月19日 (2012.4.19)        |

| (33) 優先権主張国   | 米国(US)                        |

早期審査対象出願

|           |                                                              |

|-----------|--------------------------------------------------------------|

| (73) 特許権者 | 503455363<br>レイセオン カンパニー                                     |

|           | アメリカ合衆国 マサチューセッツ州 O<br>2451 ウォルサム ウィンター スト<br>リート 870        |

| (74) 代理人  | 100107766<br>弁理士 伊東 忠重                                       |

| (74) 代理人  | 100070150<br>弁理士 伊東 忠彦                                       |

| (74) 代理人  | 100091214<br>弁理士 大貫 進介                                       |

| (72) 発明者  | デナム, マーティン, エス.<br>アメリカ合衆国 オレゴン州 97701<br>ペンド ダックス・ロード 24780 |

最終頁に続く

(54) 【発明の名称】再分配されたデジタルピクセル

## (57) 【特許請求の範囲】

## 【請求項 1】

ピクセルセルのアレイと、

複数のアナログ - デジタル変換器と、

前記ピクセルセルのアレイから物理的に離れて配置され且つ該ピクセルセルのアレイへ結合される複数のデジタルメモリ素子に含まれる対応する複数のデジタルカウンタとを有し、

前記ピクセルセルの夫々は、

光電流を受けるよう構成される入力部と、

前記入力部へ結合され、前記光電流から電荷を蓄積するよう構成される蓄電デバイスと、

前記蓄電デバイスへ結合され、前記電荷をアナログ量子化事象信号へ変換するよう構成される量子化回路と

を有し、

前記複数のアナログ - デジタル変換器の夫々は、入力部及び出力部を備え、前記複数のアナログ - デジタル変換器の夫々は、その入力部を介して前記ピクセルセルのうちの少なくとも1つの前記蓄電デバイスへ結合され、夫々の蓄電デバイスにおける残留電荷をデジタル2進値に変換するよう構成され、

前記デジタルカウンタの夫々は、前記ピクセルセルのうちの夫々1つと関連して該夫々1つと通信し、前記ピクセルセルのうちの前記少なくとも1つから前記アナログ量子化事

10

20

象信号を受信することに応答して、前記ピクセルセルのうちの前記夫々 1 つから前記アナログ量子化事象信号を受信することに応答してデジタルカウンタ値をインクリメントして記憶するよう構成される、

撮像システム。

【請求項 2】

前記ピクセルセルのアレイを含む読出集積回路チップを更に有する

請求項 1 に記載の撮像システム。

【請求項 3】

前記複数のデジタルメモリ素子は、前記読出集積回路チップに隣接して配置される、

請求項 2 に記載の撮像システム。 10

【請求項 4】

前記読出集積回路チップは、前記ピクセルセルのアレイを含む第 1 の部分と、該第 1 の部分とは異なる第 2 の部分とを備え、該第 2 の部分は、前記複数のデジタルメモリ素子を含む、

請求項 2 に記載の撮像システム。

【請求項 5】

前記ピクセルセルの夫々は、衝突する光に応答して前記光電流を生成するよう構成される光検出器を更に有し、

前記デジタルカウンタ値は、前記ピクセルセルのうちの夫々 1 つの前記光検出器に衝突する光の強さに対応する、 20

請求項 2 に記載の撮像システム。

【請求項 6】

前記読出集積回路チップへハイブリッド化される光検出器のアレイを更に有し、

夫々の光検出器は、前記ピクセルセルのアレイのうちの対応するピクセルセルに関連する、

請求項 2 に記載の撮像システム。

【請求項 7】

前記複数のデジタルメモリ素子は、静的ランダムアクセスメモリ及びレジスタファイルのうちの少なくとも 1 つを含む、

請求項 1 に記載の撮像システム。 30

【請求項 8】

複数のストローブラインを更に有し、該複数のストローブラインの夫々は、前記ピクセルセルのうちの少なくとも 1 つの前記量子化回路へ結合され、当該ストローブラインが結合されている前記量子化回路へ周期的な時間インターバルでストローブ信号を送信するよう構成される、

請求項 1 に記載の撮像システム。

【請求項 9】

前記量子化回路は、前記ストローブ信号を受信することに応答して、前記蓄電デバイスにおける前記電荷が所定の閾値を超えるかどうかを決定するよう構成される、

請求項 8 に記載の撮像システム。 40

【請求項 10】

前記量子化回路は更に、前記蓄電デバイスにおける前記電荷が前記所定の閾値を超えると決定することに応答して、前記アナログ量子化事象信号を生成するよう構成される、

請求項 9 に記載の撮像システム。

【請求項 11】

前記蓄電デバイスはキャパシタであり、

前記量子化回路は、前記キャパシタへ結合される電荷除去回路を含む、

請求項 1 に記載の撮像システム。

【請求項 12】

前記複数のアナログ - デジタル変換器のうちの少なくとも 1 つからの前記デジタル 2 進

値と、前記複数のデジタルカウンタのうちの少なくとも1つからの前記デジタルカウンタ値とを出力ビデオフレームの少なくとも1つのピクセルに変換するよう構成されるデジタルフォーマッタを更に有する

請求項1に記載の撮像システム。

**【請求項13】**

ピクセルセルのアレイにおける複数のピクセルの夫々について、当該ピクセルによって生成された電荷を、夫々のピクセルに付随する複数の蓄電デバイスの1つにおいて蓄えるステップと、

夫々の前記蓄電デバイスにおける蓄積された電荷が所定の閾値を超えるかどうかを周期的に決定するステップと、

夫々の前記蓄電デバイスにおける前記蓄積された電荷が前記所定の閾値を超えると決定することに応答して、夫々の前記蓄電デバイスにおいて蓄えられている前記電荷を所定の電荷減少量だけ低減し、デジタルカウンタにおいて蓄えられ且つ夫々のピクセルに関連する複数のデジタルカウンタ値のうちの1つをインクリメントするステップであって、前記デジタルカウンタ値は、前記ピクセルセルのアレイから物理的に離れて配置され且つ該ピクセルセルのアレイへ結合されて前記ピクセルのアレイと通信する複数のデジタルメモリ素子に含まれる、ステップと、

前記複数のピクセルの夫々の前記蓄電デバイスにおける残留電荷をアナログ信号へ周期的に変換するステップと、

夫々のピクセルからの前記アナログ信号を複数のアナログ - デジタル変換器の1つにより夫々のデジタル2進値へ変換するステップであって、前記複数のアナログ - デジタル変換器の夫々は、入力部及び出力部を備え、前記複数のアナログ - デジタル変換器の夫々は、その入力部を介して前記複数のピクセルのうちの対応する1つの夫々の前記蓄電デバイスへ結合される、ステップと

を有する画像検出方法。

**【請求項14】**

夫々の前記デジタルカウンタ値及び夫々の前記デジタル2進値のうちの少なくとも1つを出力ビデオフレームにおける複数のピクセルのうちの1つに変換するステップを更に有する

請求項13に記載の画像検出方法。

**【請求項15】**

前記出力ビデオフレームを符号化するステップを更に有する

請求項14に記載の画像検出方法。

**【請求項16】**

前記ピクセルセルのアレイを含む読出集積回路チップを設けるステップを更に有する

請求項13に記載の画像検出方法。

**【請求項17】**

前記読出集積回路チップから離れたチップ上に前記複数のデジタルメモリ素子を設けるステップを更に有する

請求項16に記載の画像検出方法。

**【請求項18】**

前記読出集積回路チップの第1の部分に前記ピクセルセルのアレイを設けるステップと、

前記第1の部分とは異なる前記読出集積回路チップの第2の部分に前記複数のデジタルメモリ素子を設けるステップと

を更に有する請求項16に記載の画像検出方法。

**【請求項19】**

夫々の前記蓄電デバイスにおける蓄積された電荷が所定の閾値を超えるかどうかを周期的に決定するステップは、複数のクロックサイクルにわたって前記複数のピクセルの夫々について実行される、

請求項 1 3 に記載の画像検出方法。

【請求項 2 0】

夫々のピクセルは、光検出器を有し、

当該方法は、夫々のピクセルについて、前記光検出器に衝突する放射線に応答して前記電荷を生成するステップを有する、

請求項 1 3 に記載の画像検出方法。

【請求項 2 1】

基板上にピクセルセルのアレイを配置するステップと、

前記基板上に、前記ピクセルセルのアレイに隣接して、メモリ素子のアレイを配置するステップと、

前記基板上に、複数のアナログ - デジタル変換回路を配置するステップと

を有し、

夫々のピクセルセルは、光検出器と、該光検出器へ結合されるキャパシタと、該キャパシタへ結合される比較器とを含み、

夫々のメモリ素子は、カウンタと、該カウンタへ結合される蓄積デバイスとを含み、前記複数のアナログ - デジタル変換回路の夫々は、入力部及び出力部を備え、前記複数のアナログ - デジタル変換回路の夫々は、その入力部を介して前記ピクセルセルのうちの少なくとも 1 つの前記キャパシタへ結合され、夫々の前記蓄積デバイスにおける残留電荷をデジタル 2 進値に変換するよう構成される、

読み出集積回路チップの製造方法。

【発明の詳細な説明】

【背景技術】

【0 0 0 1】

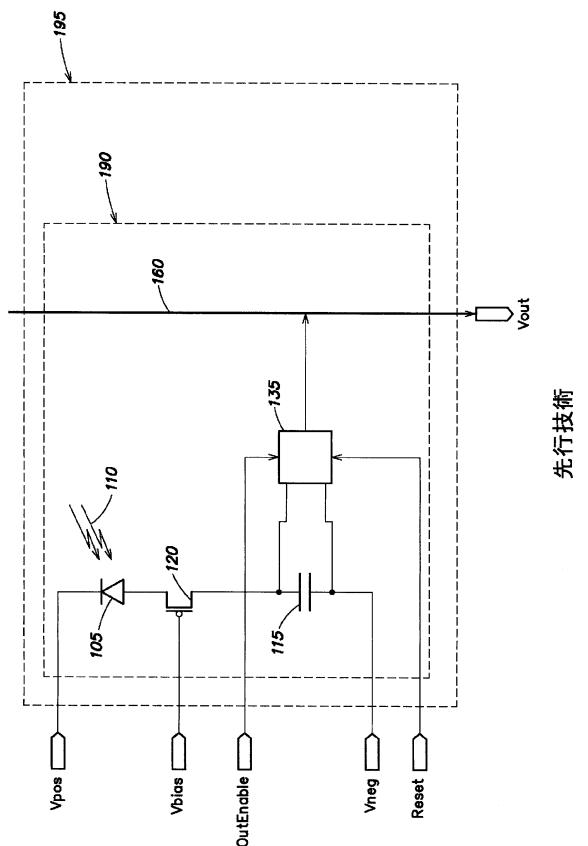

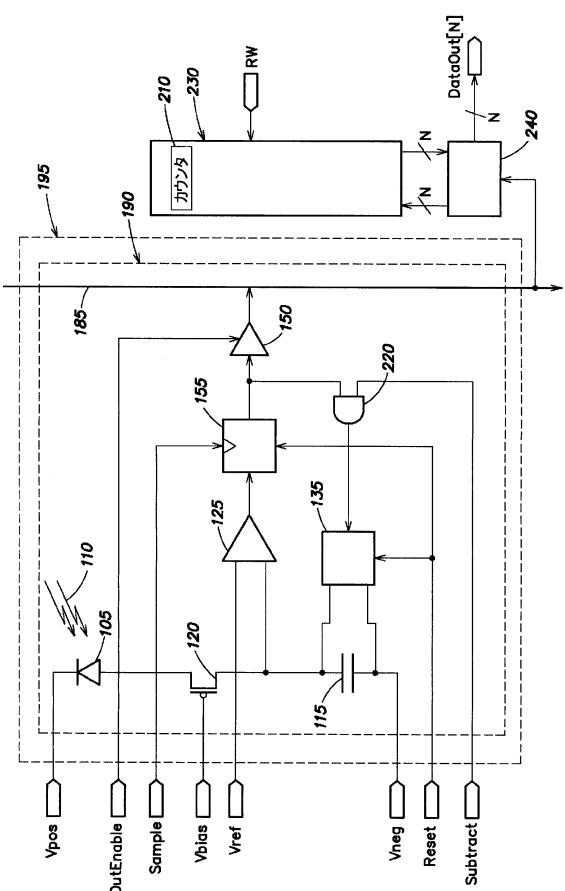

焦点面アレイは、列及び行によって編成されている検出器素子又はピクセルの 2 次元アレイを含む。図 1 は、ピクセル 190 のアレイ 195 の一例のプロック図である。ピクセル 190 内の回路が、様々な波長の光束 110 に対応するフォトダイオード 105 からの電荷を蓄積することができることは、一般的である。しばしば、電荷は、電荷を有効に積分して、積分インターバルと呼ばれる所与の時間インターバルにわたって光束 110 の強さに対応する電圧を生成する容量素子 115 において、蓄積される。図 1 に表される例では、フォトダイオード 105 は、電圧 Vbias によりバイアスをかけられる MOS トランジスタ又は直接注入ゲート 120 を介して容量素子 115 へ結合されている。図 1 において、回路素子 135 は、容量素子 115 の電圧を初期状態へ再設定し直すことができる回路と、アレイ 195 の出力部への伝送のために列（又は行）配線 160 へ電荷又は電圧を運ぶことができる回路とを有する。そのような電圧又は電荷は、焦点面アレイ 195 の各ピクセル 190 について少なくとも 1 つの値である 2 進値をもたらす、焦点面アレイに付随する回路によって、デジタル化され得る。このように、焦点面アレイは、光束の 2 次元パターンをバイナリ値の 2 次元アレイに変換するために使用されてよく、そのような、結果として得られるアレイは、しばしばデジタル画像と呼ばれる。

【0 0 0 2】

積分インターバルにわたってピクセル 190 によって蓄積される電荷の実効量は、デジタルカウンタ回路の負荷によって増大され得る。幾つかの例において、各ピクセルは、固有のデジタルカウンタ回路を与えられる。追加の回路は、所定量の電荷がピクセルの容量素子から除去されることを可能にし、これに対してデジタルカウンタの値を 1 カウントだけ増やすよう、ピクセルへ加えられ得る。このように、積分インターバルの時間の経過期間にわたって、ピクセル 190 の容量素子 115 は光電荷を積分することができ、ピクセル内の回路は所定量の電荷を除去することができ、デジタルカウンタは電荷除去の回数をカウントすることができる。このようにして、積分インターバルにわたってピクセルによって蓄積される電荷の実効量は、デジタルカウンタが容量素子の積分範囲に及ぶので、増大され得る。

【0 0 0 3】

10

20

30

40

50

電荷除去を記録するのに使用されるデジタルカウンタのタイプは、電荷除去をカウントすることができる、2進、グレイコード、線形フィードバックシフトレジスタ（LFSR）、又は何らかの他のデジタルカウント回路を含む如何なる論理変形物であってもよい。加えて、電荷除去の相対符号は、回路接地に対してプラス又はマイナスであることができ、故に、電荷除去は、幾つかの場合において、電荷付加と見なされ得る。

## 【0004】

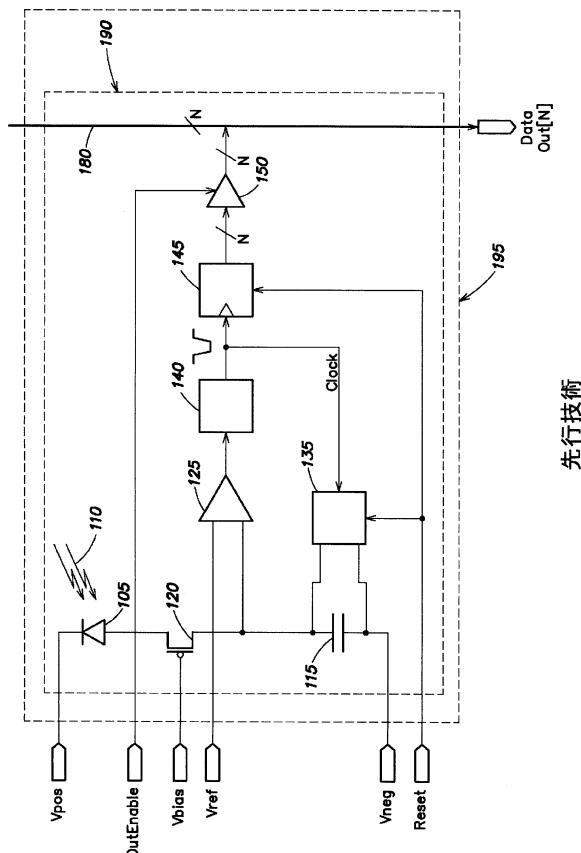

“デジタルピクセル”又は“ピクセル内ADC”と呼ばれるピクセル回路の分類は、図2に表されるように、夫々のピクセル内のデジタルカウンタ回路を特徴付ける。一般的なデジタルピクセル回路は、光電荷を積分して電圧を生成する容量素子115と、電圧がリファレンス電圧を超える場合を検出する比較器125と、所定の固定量の電荷を容量素子115から除去する電荷除去回路135と、ある量の電荷が容量素子から除去される度にインクリメントするデジタルカウンタ回路145とを特徴とする。リセットロジック140は、クロックタイプの信号を電荷除去回路135へ供給して、電荷除去回路に、容量素子の両端電圧がリファレンス電圧を超えていることを示す比較器125からの信号に応答して容量素子115から所定量の電荷を除去させる。夫々の電荷除去ノリセット事象により、デジタルカウンタ145はインクリメントされる。デジタルカウンタ145の値は、図2に示されるように、データ出力ライン180上でトリステートゲート150を介して読み出されてよい。デジタルカウンタ145の値を出力の組へ運ぶ多数の他の手段は、当業者によって認識されるであろうように、トリステートゲート150の代替案として存在する。例えば、値はシフトアウトされてよい。

10

20

## 【0005】

一般的なデジタルピクセル回路において、容量素子のサイズは、しばしば、比較的小さい値（例えば、1.0フェムトファラッド又は10フェムトファラッド）へと低減され、カウンタビットの数は、広範囲のカウント値をもたらす何らかのビット数、例えば、16ビットである。これに対して、容量素子115の電圧範囲は、しばしば、比較的小さく、例えば、250ミリボルトである。この構成において、デジタルカウンタ145は、アナログ-デジタル変換器として動作することができ、アナログ-デジタル変換を実行するピクセルの回路の機能をもたらし、よって、“ピクセル内ADC”回路と呼ばれる。所定量の電荷はまた、電荷“素量”とも呼ばれ得る。容量素子115からの電荷除去は、MOSFETのような簡単なデバイスを用いて第1の電圧へリセットされ直されてよい。電荷除去はまた、容量素子の電圧を1の値から第2の値へ至らせる電荷素量を除去する更に複雑な回路であってもよい。

30

## 【0006】

上記の従来のデジタルピクセルの幾つかの否定的な特質が存在する。特に、デジタルカウンタ回路145は、夫々のピクセル190内で有限な面積を消費する。回路の製造プロセスが比較的低い密度である場合は（例えば、180ナノメートルCMOS）、デジタルカウンタの面積は、容量素子115、比較器125、及び電荷除去回路135のための取るに足りない面積を残しながら、ピクセル内の利用可能な面積のほぼ全てを占有し得る。上述されたように、ピクセル190は、バイアシング回路、例えば、直接注入ゲートMOSFET120を更に含んでよく、やはり、取るに足りない面積が、そのデバイス（1又は複数）のために利用可能であり得る。それら又は他の回路デバイスのための取るに足りない又は十分でない余地がピクセル面積内に存在するそのような場合に、そのような回路の性能は低下し得る。よって、例えば、ノイズが有意に増大し得る。利用可能な面積を制限して、アナログ回路（例えば、容量素子115、比較器125、及び電荷除去回路135）の品質を制限するデジタルカウンタ回路145に加えて、制限された面積はまた、デジタルピクセルの容量を制限する。より具体的に、容量素子115のサイズは、より少ない総電荷蓄積に制限されることがあり、これは、ピクセル190の入力束性能を、場合により、所与のエンドアプリケーションのために必要とされるものよりも少なく制限することがある。

40

## 【0007】

50

反対に、回路の製造プロセスが比較的高い密度である場合は（例えば、65ナノメートルCMOS）、容量素子115、比較器125、電荷除去回路135、及びバイアス回路120のための十分な余地が存在し得る。しかしながら、そのようなプロセスの関連する経常外費用は、そのようなデバイスの一部の消費者にとって高すぎることがある。

【0008】

他の否定的な特質は、デジタルカウンタ回路145が、容量素子115、比較器125、電荷除去回路135、及びバイアシング回路120のようなアナログ回路とともに存在する場合に、デジタルカウンタのスイッチング事象に関連する瞬時電流が供給ラインにおいて及びCMOS基板電位においてノイズ電圧を生成し、アナログ回路の性能の品質低下及びノイズの増大を生じさせ得ることである。

10

【0009】

幾つかの場合に、比較器回路125は、容量素子115での電圧が比較器回路の閾値に達する場合に瞬時にクロック信号をデジタルカウンタ回路145へ送信する。この同じクロック信号はまた、電荷除去回路135に、電荷素量を容量素子から除去させる。そのような回路は、カウント動作のために使用又は必要とされる外部のタイミングストローブが存在しないので、“非同期”デジタルピクセルと呼ばれる。非同期デジタルピクセル回路は、それらが小型であり、比較的簡単であり、タイミングストローブを必要とする同様の回路よりも低い電力を有することができる、望ましい。しかしながら、非同期デジタルピクセルが、ランダムな電源過渡電圧及びランダムな基板電圧変動をもたらし、更にはアナログ回路の品質を低下させ且つノイズを増大させる予測不能のタイミングの瞬間的な電源擾乱を生じさせ得ることは、事実である。加えて、焦点面アレイにおける全体的な入射束110が比較的高い場合に、デジタルピクセルのアレイによって生成される予測不能の電源遷移の積み重なりは、アナログ回路の品質を実質的に低下させる。

20

【0010】

デジタルピクセルにデジタルカウンタを有することの更なる否定的な特質は、デジタルカウンタ145への供給金属ラインが、夫々のピクセル190への金属ラインの利用可能な全体のルーティングの一定割合を消費することである。同様に、カウンタの出力ビットは、焦点面アレイ195のエッジへのルーティングを必要とし、利用可能なルーティング面積を更に消費する。供給配線及び出力ビットルーティング配線の組み合わせは、面積が利用可能であった場合にアナログ供給配線の抵抗を減らして、改善されたアナログ性能をもたらすことができるピクセルのアナログ回路への配線の数及び幅を増大させるのにしばしば必要とされる面積を消費する。この要因とともに、更なるピクセル面積は、カウンタ値が読み出されることを可能にするよう焦点面アレイ195のエッジへ加えられる出力可能回路により消費される。そのような回路は、焦点面アレイ195のエッジへデジタルカウンタ値を伝播するよう構成されるトリステートドライバ150、動的プルダウンマルチプレクサ、シフトレジスタ、又は何らかの他の回路を含んでよい。

30

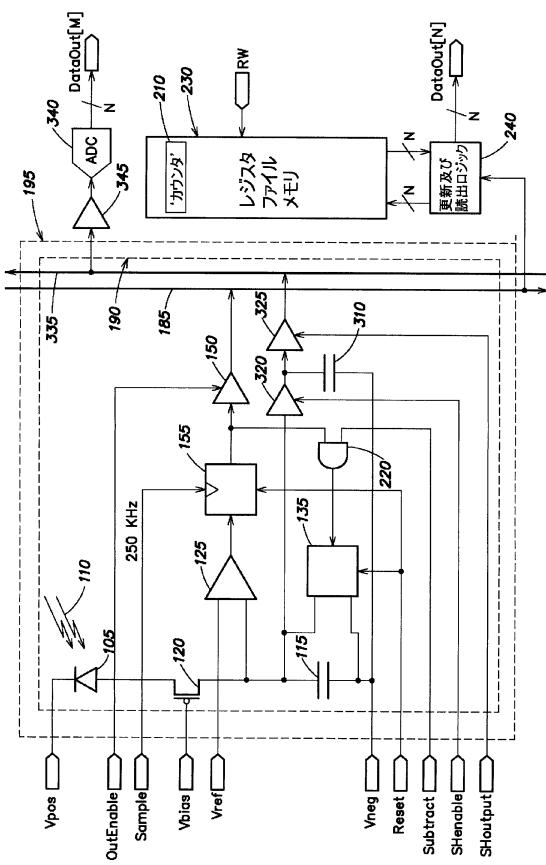

【0011】

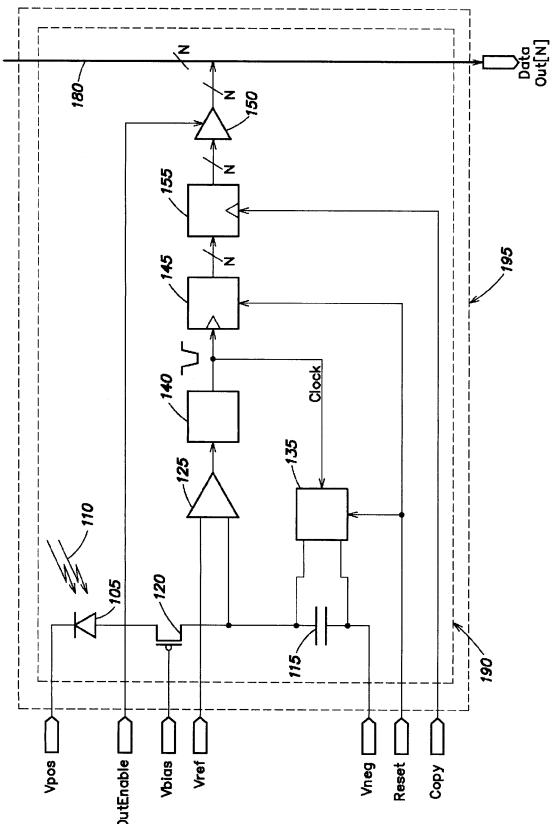

図3を参照すると、他の否定的な特質は、“読み出中積分（integrate-while-read）”機能が必要とされる場合に、デジタル記憶素子（例えば、ラッチ155）の追加の組が更にピクセル190内に組み込まれる必要があり、上述されたような、デジタルピクセルにおいてデジタルカウンタ145を有することに付随する問題を、更に悪化させることである。読み出中積分モードにおいて、積分インターバルの終わりに、デジタルカウンタ145の値は、デジタル記憶素子155にコピーされ、読み出しのための値、例えば、1度に1つの行又は1つの列を保ち、デジタルカウンタ145を、積分された電荷の更なるカウントのために使用されるよう解放する。

40

【0012】

このように、デジタルピクセル回路は、ピクセルの全体的な電荷保持機能を高めることができるデジタルカウンタ回路を含む。同時に、しかしながら、デジタルピクセル回路は、その使用を制限し得る幾つかの否定的な特質を備える。

【発明の概要】

50

## 【発明が解決しようとする課題】

## 【0013】

態様及び実施形態は、概して、焦点面アレイ（FPA）（focal plane array(s)）の読み出集積回路（ROIC）（Read-Out Integrated Circuit(s)）を対象とし、特に、ピクセルごとの平均光電流のアナログ - デジタル変換がROICで起こり且つROICの出力が主にデジタルであるROICの分類を対象とする。様々な実施形態は、夫々のピクセルにおいてアナログ - デジタル変換器（ADC）を含んで、上述されたようにデジタルピクセルとして知られるROICの分類に対する改善を提供することができる。態様及び実施形態によって提供される技術的利点は、従来のアーキテクチャに対して、所与のピクセルサイズ及びプロセス・フォトリソグラフィ・ノードについて、オンチップのADCを備えるROICの改善された実現可能性、ダイナミックレンジ、費用、性能、ノイズ性能、及び電力消費を含んでよい。10

## 【課題を解決するための手段】

## 【0014】

一実施形態に従って、ROIC FPAは、行及び列によって編成されている検出器素子又はピクセルの2次元アレイを含み、そのようなピクセルは、電荷を積分する容量素子、比較器回路、電荷除去回路、及び可能性があるバイアシング回路を含む、従来技術のピクセルの主たるアナログ部品を備える。しかし、従来のデジタルピクセル回路と異なり、特定の実施形態は、更に以下で論じられるように、FPAの面積の外に夫々のピクセルのデジタルカウンタ回路を置く。加えて、特定の実施形態は、FPAの物理面積の外に、カウンタ読み出回路（例えば、トリリストードライバ）、及び読み出中積分のための任意の保持ラッチとともに、カウンタ回路を位置付ける。20

## 【0015】

好ましい実施形態において、ROIC FPAは、FPAと同じ集積回路（IC）上に、デジタルカウンタ、デジタルカウンタ読み出回路、及び任意の保持状態素子を置く。デジタルカウンタ、デジタルカウンタ読み出、及び任意の保持状態素子の物理的、論理的、及び回路態様は、焦点面195又は含まれるピクセル190の物理的な態様の制約によって制限されない。よって、例えば、電荷を積分する容量素子、比較回路、電荷除去回路、及び可能性があるバイアシング回路を有するピクセル回路はピクセルのピッチによって制限され、一方、デジタル回路は、それらの実効密度を増大させ得る他の実効ピッチにおいて配置されてよい。30

## 【0016】

代替の実施形態において、ROIC FPAは、デジタル回路、デジタルカウンタ読み出回路、及び任意の保持状態素子を同じIC上に位置付けないことがあり、代わりに、デジタルカウンタを記憶し且つ変更し且つ読み出すよう構成される同じIC上にない別の回路への通信網回路を設けてよい。同じIC上にないそのような別の回路は、例えば、フィールドプログラマブルゲートアレイ（FPGA）であってよい。

## 【0017】

一実施形態に従って、ROIC FPAは、アナログアレイ（フォトダイオード及び積分キャパシタを含む。）と、アナログアレイと物理的に離れたデジタル回路とを含む。アナログ及びデジタルの各領域に含まれる回路は、従来のデジタルピクセルと略同じ機能を実行するよう構成される（例えば、とりわけ、光電流積分、クロッキング、カウント及び/又は読み出）。デジタル回路をアナログアレイから物理的に離すことによって、デジタル回路がアナログアレイのサイズによって制限されない設計が達成され、これにより、ピクセルサイズが従来のデジタルピクセルのサイズと同じままであるか、又はそのサイズに対して低減されるにもかかわらず、より高密度の部品が利用可能にされ得る。40

## 【0018】

他の実施形態において、撮像システムは、ピクセルセルのアレイと、前記ピクセルセルのアレイから物理的に離れて配置され且つ該ピクセルセルのアレイへ結合される複数のデジタルメモリ素子とを有し、前記ピクセルセルの夫々は、衝突する光に応答して光電流を50

生成するよう構成される光検出器と、該光検出器へ結合され、前記光電流から電荷を蓄積するよう構成される蓄電デバイスと、該蓄電デバイスへ結合され、前記電荷をアナログ量子化事象信号へ変換するよう構成される量子化回路とを有し、前記デジタルメモリ素子の夫々は、前記ピクセルセルのうちの少なくとも1つと電気通信し、前記ピクセルセルのうちの前記少なくとも1つから前記アナログ量子化事象信号を受信することに応答して、前記ピクセルセルのうちの前記少なくとも1つの前記光検出器に衝突する光の強さに対応するデジタル値を記憶するよう構成される。

【0019】

一例において、撮像システムは、前記ピクセルセルのアレイを含む読出集積回路（R O I C）チップを更に有する。他の例において、前記複数のデジタルメモリ素子は、前記R O I Cチップに隣接して配置される。一例において、前記R O I Cチップは、前記ピクセルセルのアレイを含む第1の部分と、該第1の部分とは異なる第2の部分とを備え、該第2の部分は、前記複数のデジタルメモリ素子を含む。他の例において、前記複数のデジタルメモリ素子は、静的ランダムアクセスメモリ（S R A M）及びレジスタファイルのうちの少なくとも1つを含む。撮像システムは、複数のストローブラインを更に有し、該複数のストローブラインの夫々は、前記デジタルメモリ素子のうちの1つへ、及び前記ピクセルセルのうちの少なくとも1つの前記量子化回路へ電気的に結合され、前記複数のストローブラインは、周期的な時間インターバルで前記量子化回路へストローブ信号を送信するよう構成される。一例において、前記量子化回路は、前記ストローブ信号を受信することに応答して、前記蓄電デバイスにおける前記電荷が所定の閾値を超えるかどうかを決定するよう構成される。他の例において、前記量子化回路は更に、前記蓄電デバイスにおける前記電荷が前記所定の閾値を超えると決定することに応答して、前記アナログ量子化事象信号を生成するよう構成される。撮像システムは、複数のアナログ - デジタル変換器を更に有し、該複数のアナログ - デジタル変換器の夫々は、入力部及び出力部を備え、前記複数のアナログ - デジタル変換器の夫々は、前記入力部で前記ピクセルセルのうちの少なくとも1つの前記量子化回路へ結合され、前記出力部で前記複数のデジタルメモリ素子のうちの少なくとも1つへ結合され、前記複数のアナログ - デジタル変換器の夫々は、前記アナログ量子化事象信号を前記デジタル値へ変換するよう構成される。

【0020】

他の実施形態に従って、画像検出方法は、ピクセルセルのアレイにおける複数のピクセルの夫々について、当該ピクセルによって当該ピクセルに衝突する放射線に応答して生成された電荷を、夫々のピクセルに付随する複数の蓄電デバイスの1つにおいて蓄えるステップと、夫々の前記蓄電デバイスにおける蓄積された電荷が所定の閾値を超えるかどうかを周期的に決定するステップと、夫々の前記蓄電デバイスにおける前記蓄積された電荷が前記所定の閾値を超えると決定することに応答して、夫々の前記蓄電デバイスにおいて蓄えられている前記電荷を所定の電荷減少量だけ低減し、前記ピクセルセルのアレイから物理的に離れて配置され且つ該ピクセルセルのアレイへ結合されて前記ピクセルのアレイと電気通信する複数のデジタルメモリ素子に含まれるデジタルカウンタにおいて蓄えられ且つ夫々のピクセルに関連する複数のデジタルカウンタ値のうちの1つをインクリメントするステップとを有する。

【0021】

一例において、画像検出方法は、夫々の前記蓄電デバイスにおける残留電荷をアナログ信号へ周期的に変換するステップを更に有する。他の例において、画像検出方法は、前記アナログ信号を、夫々のピクセルに付随する複数のアナログ - デジタル変換器の1つにより夫々のデジタルカウンタ値へ変換するステップを更に有する。他の例において、画像検出方法は、前記夫々のデジタルカウンタ値及び夫々のデジタル2進値のうちの少なくとも1つを出力ビデオフレームにおける複数のピクセルのうちの1つに変換するステップを更に有する。他の例において、画像検出方法は、前記出力ビデオフレームを符号化するステップを更に有する。画像検出方法は、前記ピクセルセルのアレイを含む読出集積回路（R O I C）チップを設けるステップを更に有してよい。画像検出方法は、前記R O I Cチップ

10

20

30

40

50

プから離れたチップ上に前記複数のデジタルメモリ素子を設けるステップを更に有してよい。他の例において、画像検出方法は、前記R O I Cチップの第1の部分に前記ピクセルセルのアレイを設けるステップと、前記第1の部分とは異なる前記R O I Cチップの第2の部分に前記複数のデジタルメモリ素子を設けるステップとを更に有する。他の例において、夫々の前記蓄電デバイスにおける蓄積された電荷が所定の閾値を超えるかどうかを周期的に決定するステップは、複数のクロックサイクルにわたって前記複数のピクセルの夫々について実行される。

【0022】

他の実施形態に従って、読出集積回路(R O I C)チップの製造方法は、基板上にピクセルセルのアレイを配置するステップと、前記基板上に、前記ピクセルセルのアレイに隣接して、メモリ素子のアレイを配置するステップとを有し、夫々のピクセルセルは、光検出器と、該光検出器へ結合されるキャパシタと、該キャパシタへ結合される比較器とを含み、夫々のメモリ素子は、カウンタと、該カウンタへ結合される蓄積デバイスとを含む。

10

【0023】

一例において、前記R O I Cチップの製造方法は、前記基板上に、前記ピクセルセルのアレイと前記メモリ素子のアレイとの間に有する複数のアナログ-デジタル変換(A D C)回路を配置するステップを更に有し、該A D C回路の夫々は、少なくも1つのピクセルセル及び少なくとも1つのメモリ素子へ結合される。

【図面の簡単な説明】

【0024】

20

【図1】1以上のピクセルを含む焦点面アレイの一例のブロック図である。

【図2】デジタルピクセルを含む焦点面アレイの一例のブロック図である。

【図3】デジタルピクセルを含む焦点面アレイの他の例のブロック図である。

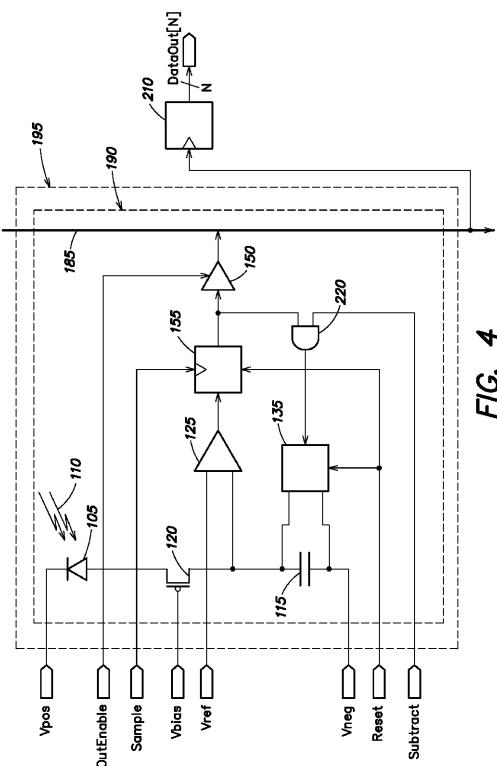

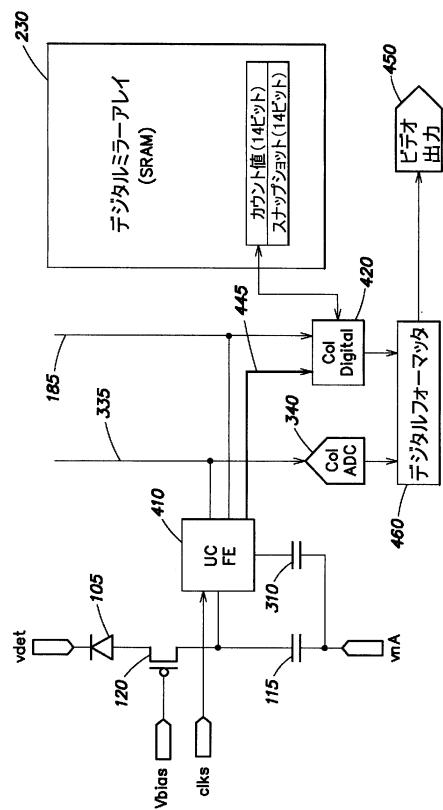

【図4】本発明の態様に従う再分配された読出集積回路焦点面アレイ及び関連するデジタル回路の一例のブロック図である。

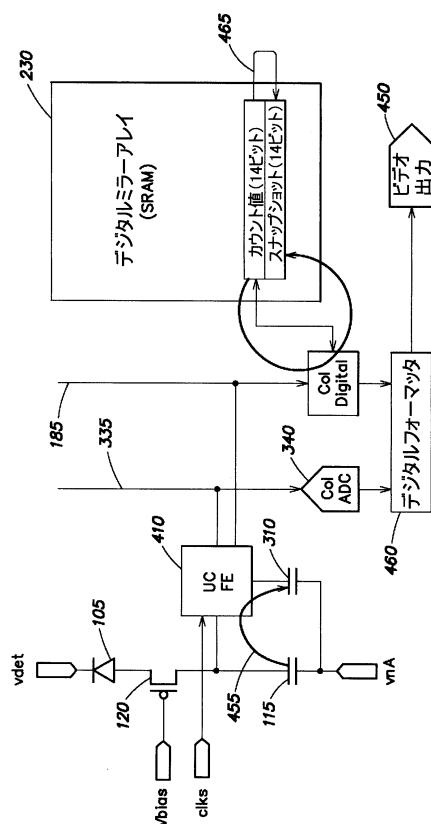

【図5】本発明の態様に従う再分配された読出集積回路焦点面アレイ及び関連するデジタル回路の他の例のブロック図である。

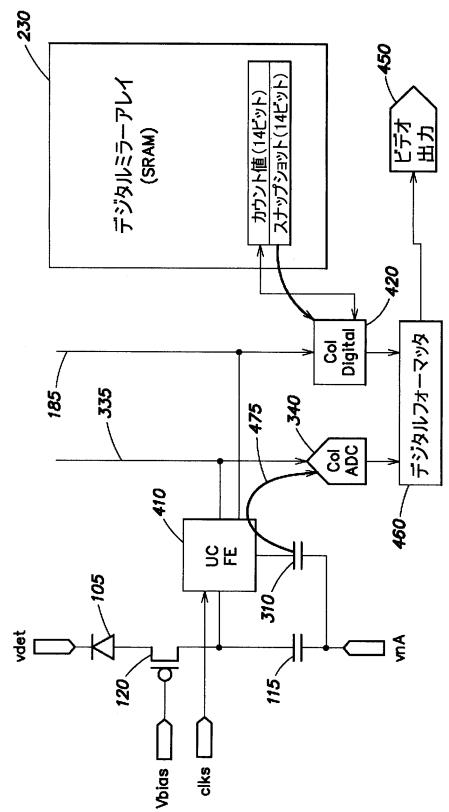

【図6】本発明の態様に従う再分配された読出集積回路焦点面アレイ及び関連するデジタル回路の他の例のブロック図である。

【図7】本発明の態様に従う、積分及び電荷減算を含む再分配されたデジタルピクセルの例の動作を説明するブロック図である。

30

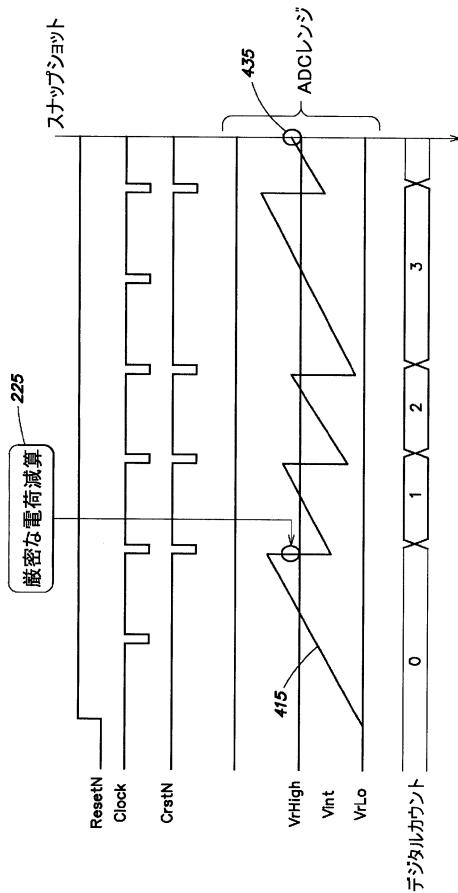

【図8】本発明の態様に従う図7、図9、図10及び図11の再分配されたデジタルピクセルの動作の例に対応するタイミング図である。

【図9】本発明の態様に従う、S R A M内のカウンタをインクリメントすることを含む再分配されたデジタルピクセルの例の動作を更に説明するブロック図及びタイミング図である。

【図10】本発明の態様に従う、スナップショット事象を含む再分配されたデジタルピクセルの例の動作を更に説明するブロック図である。

【図11】本発明の態様に従う再分配されたデジタルピクセル、読出及び列に基づくアナログ-デジタル変換器の例の動作を更に説明するブロック図である。

40

【発明を実施するための形態】

【0025】

少なくとも1つの様々な態様は、添付の図を参照して以下で論じられる。図は、実寸であるよう意図されない。図は、様々な態様及び実施形態の説明及び更なる理解を提供するよう意図され、本明細書に組み込まれてその部分を構成するが、本発明の限定の定義として意図されない。図中、様々な図中に表される夫々の同じ又はほぼ同じ構成要素は、同じ参照符号によって表される。明りょうさのために、あらゆる構成要素があらゆる図において符号を付されなくてよい。

【0026】

態様及び実施形態は、上述されたもののようなデジタルピクセルを含む、焦点面アレイ

50

のための読出集積回路 (R O I C) に関する。特定の態様及び実施形態は、単一のデジタルピクセル焦点面アレイを、物理的に共在することができるがそうである必要はない 2 つの別個の構成要素に再分配することに向けられる。一実施形態に従って、例えば、何らかのバイアシング回路 120、閾値比較器 125、容量素子 (ここでは積分キャパシタと呼ばれる。) 115、及び電荷除去回路 135 を含むピクセルの “フロントエンド” 回路は、夫々のピクセルに付随するバックエンド又はデジタル回路 (例えば、デジタルカウンタ、読出回路及び任意に保持又は “スナップショット” レジスタを含む。) から空間的且つ概念的に分離され移転されてよい。アナログアレイは、従来の焦点面アレイの同じピクセル次元並びに行及び列編成を保ってよく、一方、デジタル回路は、何らかの態様において、例えば、S R A M 又はレジスタファイルを用いて、編成され構成されてよい。仮想の ( 又は “論理的な ” ) デジタルカウンタ及びスナップショット又は保持レジスタは、S R A M 又はレジスタファイルにおいてビットによって表示されてよく、デジタルプロセッシング回路は、夫々のピクセルについて必要に応じて、カウンタ及びスナップショットレジスタを有効に生成するよう、S R A M 又はレジスタファイルから読み出し、変更し、それらに書き込むことができる。加えて、デジタルプロセッシング回路は、R O I C へ値及び機能を加えるよう、概念的デジタルカウンタへプロセッシング機能を付加してよい。

### 【 0 0 2 7 】

従来の R O I C F P A の物理的な回路レイアウトは、比較的小さく、必然的にアレイにおいて光検出器と同じピッチを有する。よって、例えば、長波長赤外線 (L W I R) F P A のピクセルが 30 マイクロメートル (ミクロン又は  $\mu$  m) ピッチを有する場合は、デジタルピクセル回路のレイアウトも辺ごとに 30  $\mu$  m よりも大きくてはならない。よって、ピクセルのサイズが小さくなるにつれて、回路面積も然るべく縮小する。結果として、従来のアナログピクセルの光電荷保持容量は、ピクセル内のアナログ部品が同じ面積を占有する傾向があるので、ピクセルサイズとともに指数的に減少する。また、従来のアナログピクセルの光電荷保持容量は、オーバーヘッド面積が特定の固定回路のために必要とされ且つレイアウト間隔規則が圧縮可能でないことがあるために、関連する光束よりも高い割合で偏って減少する。反対に、顧客需要の結果として、撮像性能を改善するよう、ピクセルごとの光電荷保持容量を、低減するのではなく、増大させることができ望ましい。デジタルカウンタ 145 は、N がカウンタビットの数であるとして、 $2^N$  のウェルキャパシティ乗算器を備える。しかしながら、デジタルピクセルのストレージのデジタル保持容量 (すなわち、ビット数) はまた、ピクセルサイズが縮小するにつれて達成するのがより困難になり、より厳しいリソグラフィを使用する要件をもたらし、設計の費用、マスク及びシリコンウェハにおいて指数関数的増大を引き起こす。よって、先に論じられたように、たとえ積分キャパシタよりも  $2^N$  倍多い量子化電荷を記憶することができる保持レジスタ及びデジタルカウンタが夫々のデジタルピクセルにおいて形成され得るとしても、そのような構成は、N の所望値を達成するために極めて密な回路レイアウトを要し、設計及び製造するのに費用がかかる。加えて、デジタルピクセルは、上述されたように、ピクセル内 A D C カウンタに付随する効果に起因したノイズの増大 (又は信号対ノイズ比の低下) のような、幾つかの他の欠点に苦しむ。カウンタ (電荷ダンプの回数を測定する。) の 2 進値とノイズの量との間には極めて強い相関が存在し得る。例えば、リファレンス電圧においてノイズが存在する場合に、デジタルカウンタは、そのノイズにカウントの数を乗じる。加えて、カウンタ自身が、それらのスイッチング遷移電流のために、電源において “ノイズ” を生成することがある。このデジタル誘発過渡ノイズは、リファレンス電源によって拾得され、先と同じくカウント数を乗じられ得る。非同期ピクセルはまた、隣接するピクセルにおける無関係のスイッチング事象の分布のおかげで、付加的なノイズを積み重ねことがある。よって、例えば、リセット “ゲート” が積分キャパシタにおいて閉じている場合に、隣接セルにおけるリセット開始 (beginning-of-reset) 事象は、リファレンス信号において d i / d t 電流を引き起こし、リセット終了 (end-of-reset) 電圧をオフさせ得る。また、電荷共有として知られている現象は、リセット回路を駆動するゲートの供給ラインにおける A C 及び D C 電圧に起因して、変動リセット回路にノイズ電子を容量素子 1

10

20

30

40

50

15に投入させ得る。

【0028】

このように、たとえピクセル内デジタルカウンタの使用がウェルキャパシタンス制限に対処することができるとしても、デジタルピクセルは、望まないノイズを導入することができ、更には、カウンタを実装するために高度な製造プロセスを使用する必要があり得るために、厳しい経常外(NRE)及び製造費用に苦しむこととなり得る。従って、回路の全体のサイズを低減しながらピクセルピッチが低減され得るようにピクセルを構成することが望ましい。

【0029】

上述されたように、一実施形態に従って、ROIC FPAは、第1及び第2の物理構造に物理的に分割される。第1の物理構造は、アナログフロントエンド部品(例えば、アナログ量子化器回路)のみを含むピクセルのアレイを含む。第1のアレイのピクセル次元は、従来のFPAアレイにおいて見られるのと同じ又は略同じであってよい。幾つかの実施形態において、第2の物理構造は、SRAM又はレジスタファイルに基づくストレージ及び関連するデジタルプロセッシングロジックを含む。第2のアレイのアスペクト比及びサイズは、厳しく制限されず、従来のデジタルピクセルの光電荷保持容量を低減したサイズ制約を軽減又は排除することができる最良の密度のために最適化されてよい。特に、一実施形態において、デジタルカウンタ145は、ピクセル(すなわち、アナログアレイ又は第1の物理構造)から“除去”され、サイズ及びレイアウトが光検出器アレイによって制限されない第2の物理構造において実装される。結果として、以下で更に論じられるように、有益な面積がデジタルカウンタによって利用されないので、積分キャパシタはより大きくされ得、あるいは、ピクセル全体は(例えば)より小さくされ得る。

【0030】

幾つかの実施形態において、プレスケーラ又は“プレカウンタ”がピクセル内に含まれてよい。しかしながら、カウンタ機能の大部分は、やはり以下で更に論じられるように、依然として第2の物理構造において実装される。他の実施形態において、ROIC FPAは、サンプル・アンド・ホールドキャパシタ及び転送回路がFPAのアナログピクセルに加えられる場合に残留積分電圧値を更にデジタル化することができるADCの列に関連したブロックを含む。ここで記載される実施形態の少なくとも1つにおいて、ROIC FPAは、従来のROIC FPAに対して、改善された感度、ノイズ等価温度差(NE 30 DT)(noise equivalent differential temperature)、及び信号対ノイズ比(SNR)を有する。

【0031】

態様及び実施形態は、それらの適用において、以下の記載において説明されるか又は図面において表される構成要素の配置及び構成の詳細に制限されない。本発明の実施形態は、他の実施形態の能力を有し、様々な方法において実施又は実行可能である。また、ここで使用される表現及び用語は、記載のためであり、限定と見なされるべきではない。本願における“含む”、“有する”、又は“備える”、“包含する”、“伴う”及びそれらの変形の使用は、以降で挙げられている項目及びそれらの等価物並びに付加的な項目を包含するよう意図される。

【0032】

図4は、ピクセル190のアレイを含むFPA195を含む撮像システムの一例のプロック図である。上述されたようにデジタルカウンタ及び関連するデジタル回路がピクセル内に包含される従来のデジタルピクセルと異なり、特定の実施形態に従って、夫々のピクセル190に関連するデジタルカウンタ210は、図4に示されるように、FPA195から離れて位置付けられている。夫々のピクセル190は、上述されたように、光検出器105と、積分容量素子115と、関連するデジタル回路とを含み、積分容量素子115から除去される電荷の量に対応する信号をトリミングゲート150を介して読出ライン185上で周期的に供給する。そのような信号は、上述されたように、電荷除去事象をカウントするデジタルカウンタ210へ供給され、Nビットのデジタル出力信号をData 40 50

Out ライン上で供給する。Data Out 値は、上述されたように、ピクセルのアナログ - デジタル変換である。ピクセル 190 のアレイ及びそれらの関連するアナログ且つ電荷除去回路をデジタルカウンタ及び関連するデジタル回路から物理的に離すこのような編成は、ピクセルサイズが小さいままであることを可能にしながら、より大きい積分容量素子 115 のために夫々のピクセル 190 において更なる空間を生み出す。一実施形態において、撮像システム ROI C のサイズは、例えば、約 31 ミリメートル × 25 ミリメートルであってよい。更に、デジタルカウンタ及び部品を別個の空間に分離することは、より密なメモリ素子の使用、例えば、及び / 又は、撮像システムの改善された分解能及び性能のためのピクセルごとの更なるビットを可能にする。

## 【0033】

10

依然として図 4 を参照して、夫々のデジタルピクセル 190 に関連する積分容量素子 115、電荷除去回路 135 等のようなフロントエンドアナログ回路は、撮像システムの大部分はアナログの FPA アレイ 195 において配置される。図 4 に表される例では、上記のピクセル 190 の回路部品に加えて、ピクセルは、ラッチ 155 と電荷除去回路 135 との間に結合される AND ゲート 220 を含む。AND ゲート 220 は、図示されるように、その入力部で、積分容量素子 115 における電荷が、上述されたように比較器 125 によって定義される閾値を超えていることを示すラッチ 155 からの信号と、外部の減算信号 (Subtract) とを受け入れる。AND ゲート 220 の出力は、電荷除去回路 135 へ供給され、電荷除去回路に積分容量素子 115 から電荷素量を取り出させる。電荷除去事象を示す信号は、上述されたように、ライン 185 上で供給される。

20

## 【0034】

一実施形態において、FPA 195 のフロントエンド回路は、赤外線検出器アレイへハイブリッド化されてよく、よって、ピクセルピッチは、検出器ピッチと同じであってよい。ハイブリッド化は、例えば、焦点面アレイセンサのようなデバイスの ROI C 部分と光検出器 105 とを結合するプロセスを指す。よって、FPA 195 は、従来の FPA と同じピクセル次元並びに列及び行編成（例えば、1920 × 1080, 12 ミクロンピッチ）を有してよく、これは、撮像システムの幾つかの実施形態をハイブリッド化に適したものとする。デジタルカウンタ 210 のような、夫々のデジタルピクセル 190 に関連するバックエンド回路（又はデジタル素子）は、物理的に別個の構造（先に第 2 の物理構造と呼ばれた。）において位置付けられる。この構造は、アレイフォーマットを有しても有さなくてよい。例えば、第 2 の物理構造は、ROI C のフットプリント面積を低減するようピクセルアレイの近くで、ROI C の異なるシリコン領域において空間的に位置付けられてよく、あるいは、第 2 の物理構造は、特定のニーズ又はダイサイズに適するよう ROI C の利用可能な面積領域を満たしてよい。他の実施形態において、第 2 の物理構造は、FPA アレイ 195 の ROI C へ通信上結合される別個の IC に配置されてよい。第 2 の物理構造は必ずしも検出器アレイへハイブリッド化されないので、ビット、レジスタ、及び他の部品のアスペクト比は柔軟であり、多数の異なる方法において実施されてよい。概念を例証すると、デジタルカウンタ 210 の下位ビットは FPA の同じ ROI C に配置されてよく、一方、上位ビットは隣接する IC 又は他の回路に位置付けられてよい。そのような配置は、出力帯域幅を低減し且つダイサイズ制約を満足することができる。

30

## 【0035】

40

図 4 のトリーステートゲート 150 及びラッチ 155 は、図 3 のトリーステートゲート 150 及びラッチ 155 と機能及び回路組成が類似する一方、動作においては重要な相違が存在する点が留意されるべきである。それらのゲートのタイミング及び機能は異なっており、それら 2 つの異なるピクセル設計の間で首尾一貫している。より重要なことには、図 4 において存在するトリーステートゲート 150 及びラッチ 155 のインスタンスは、より少なく、ROI C 上でピクセル内の十分な面積節約及び改善された効率をもたらす。好ましい実施形態において、図 4 においては唯 1 つのトリーステートゲート 150 及びラッチ 155 が存在し、有意により多くのピクセル面積がフロントエンドアナログ回路に利用可能であるという本発明の利点をもたらす。

50

## 【0036】

図5を参照すると、一実施形態において、夫々のピクセル190に関連するデジタルカウンタ210を含む第2の物理構造は、如何なる方法によっても編成可能であり、上述されたように、S R A M及び／又はレジスタファイルのようなデジタルメモリ230を用いて実装されてよい。このように、デジタル回路は、例えば、F P Aアレイ195と同じ論理構成（例えば、 $1920 \times 1080$ 個の記憶素子）、又は異なる論理構成を有してよい。そのような代替の構成は、修理及び収率向上のために余分のものを含んでよい。S R A M又はレジスタファイルは、異なるレイアウトパターンにおいて編成されてよい。これは、デジタルカウンタ210及び保持レジスタを形成する回路の面積効率が、従来のデジタルピクセルにおいて可能であるよりも、レイアウトアスペクト比及び全体密度の両方について、従来設計に対して改善されることを可能にする。10

## 【0037】

一実施形態において、リセットロジック140は、デジタルメモリ230のS R A M又はレジスタファイルに関連する更新及び読出回路に組み込まれてよい。

## 【0038】

少なくとも一実施形態において、デジタルメモリ230は、読出／書込コマンド（R W）に応答してビットをS R A M又はレジスタファイルから読み出すこと又はそれらへ書き込むことを可能にするよう構成される。デジタルメモリ230及び／又は更新及び読出回路240は、以下の機能のうちの幾つか又は全てを実行するよう構成されてよい：

- 1) デジタルカウンタ210を表すNビットのワードを夫々の回路から読み出し、ワードをインクリメント及び／又はデクリメントし、列読出ライン185上で信号により伝えられる情報に基づきワードをデジタルカウンタ210に書き戻す；20

- 2) スナップショット事象の間、Nビットのワードをデジタルカウンタ210から読み出し、ワードをスナップショット値として隣接するメモリ位置へ書き込む；

- 3) 他のデジタル信号プロセッシング事象を実行する；且つ／あるいは

- 4) スナップショットレジスタの値を読み出し、値をR O I Cに関連する出力部へ転送する（すなわち、ピクセル値を読み出す）。

## 【0039】

上記のステップは、読出中積分アーキテクチャを実施する。読出中積分アーキテクチャにおいて、夫々のピクセルについて、メモリ位置、すなわち、デジタルカウンタ210を記憶する第1の位置及びスナップショット値を記憶する第2の位置の2つの組が存在する。代替的に、積分後読出（integrate-then-read）アーキテクチャにおいて、デジタルカウンタ210の値を交互のメモリ位置へ転送するのではなく、デジタルカウンタ値は、R O I Cに関連する出力部へ転送されてよい。そのような配置は、唯1つの記憶位置が夫々のピクセルのデジタルカウンタ210に必要とされるので、全体のメモリサイズをおおよそ半分に低減する。30

## 【0040】

一実施形態に従って、デジタルピクセルのデジタルカウンタ210（及び任意に他のデジタルアスペクト又は回路）をアナログアレイから除去し分離し、代わりにデジタルカウンタ210を別個のデジタル構造において実装することによって、上述されたように、多数の異なるレイアウトを適応させることができるS R A M又はレジスタファイルを用いて、面積効率及び費用における有意な改善が達成され得る。例えば、デジタルカウンタ210及びレジスタを形成する回路の面積効率は、レイアウトアスペクト比及び全体密度の両方について、大いに増大し得る。このような密度における大いなる増大は、より古く且つより安価な技術がR O I Cを形成するのに使用されることを可能にする。例えば、密度の改善は、実効ピクセルサイズが改善され、同時に、より古い技術が使用され得るほど十分であり得る。よって、例えば、180 nm技術は、12ミクロンのピクセルピッチを形成するために使用されてよく、180 nm技術が、（例えば）32 nm技術を用いて形成されたデジタルピクセルと直接に張り合うことを可能にする。そのような場合に、N R E費用優位は飛躍的であり、例えば、8倍又は16倍であり得る。40

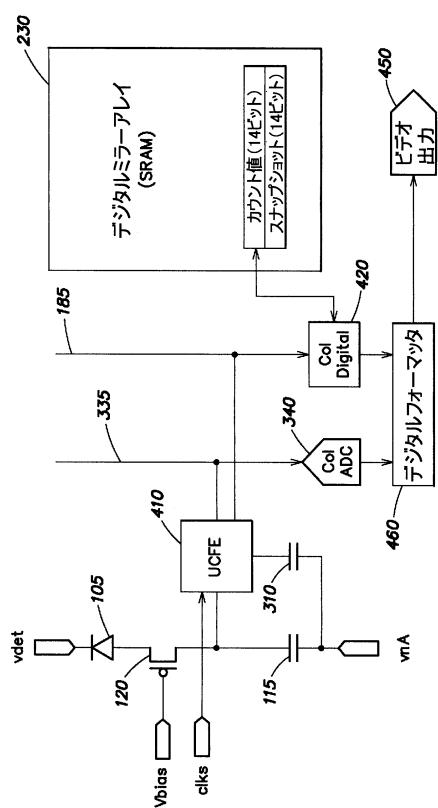

## 【0041】

図6を参照すると、一実施形態において、撮像システムは、複数の、列又は行に基づくアナログ-デジタル変換器(ADC)340を更に含む。ADC340は、夫々のフレームの終わりに夫々のデジタルピクセル190の積分容量素子115に残されている残留電圧をデジタル化するために使用されてよい。残留電圧がサンプル・アンド・ホールドキャパシタ310へ転送される場合は、次いで、ラインごとに、サンプル・アンド・ホールドキャパシタ電圧は、列読出ライン335上に、そして、アナログ信号からデジタル値(図示されるように、Data Out[M]における出力)への変換のためにADC340のうちの1つに駆動され得る。電圧転送回路320は、サンプル・アンド・ホールドインペル信号(SHenable)に応答して電圧をサンプル・アンド・ホールドキャパシタ310に転送するために使用されてよい。第2の電圧転送回路325は、サンプル・アンド・ホールド出力信号(SHoutput)に応答して電圧をサンプル・アンド・ホールドキャパシタ310から列読出ライン335上に出力するために使用されてよい。バッファ345は、図6に示されるように、列読出ライン335とADC340との間に結合されてよい。図6の回路は、読出中積分アーキテクチャを作り出す。撮像装置設計の技術において通常の知識を有する者(つまり、当業者)によって認識されるであろうように、本開示の利点を鑑み、読出後積分アーキテクチャは、電圧転送回路320及びサンプル・アンド・ホールドキャパシタ310を除去し、容量素子115における残留電圧を電圧転送回路325を介して列転送ライン335へ直接に運ぶことによって、達成され得る。同じく当業者によって認識されるであろうように、上記の場合において、電圧転送は、電荷転送により置換されてよく、そのような転換は、本発明の全体の機能又は動作に実質的に影響を及ぼさない。

## 【0042】

上述されたように、アナログアレイにおけるピクセルは、列及び行において配置されてよい。一例において、ピクセルの各列は、対応する、列に基づくADC340へ結合され、このADC340が残留電圧をデジタル化する。なお、異なる回路トポロジが上記の機能を実行するために使用されてよいこと、更には、ADC340が異なる列の間で時分割方式により使用されてよい(例えば、ADC340の1つが、複数の異なるピクセル列又は行に使用されてよい。)ことが理解されるであろう。一実施形態において、ADC340はROICに位置付けられる。

## 【0043】

図7乃至11は、再分配されたデジタルピクセルの様々な態様及び例の動作を更に例示及び説明するブロック及びタイミング図である。

## 【0044】

図7は、左側にある単一のアナログピクセルの構成要素(光検出器105、直接注入ゲート120、積分容量素子115、サンプル・アンド・ホールドキャパシタ310、及びユニットセルフロントエンド(UCFE)(Unit Cell Front End)回路410を含む。)と、中央にある列ADC回路(Col ADC)340及び列デジタル(Col Digital)420と、右側にあるデジタルミラーアレイ230(例えば、集合SRAMであってよい。)とを表す。積分容量素子115における電圧は、図8に表されるように、光検出器105からの光電流に応答して増大する(トレース415は、積分容量素子115における電圧Vintを表す。)。この構成は、例えば、長波長赤外線(LWIR)束及びHgCdTe検出器にうまく適する点が留意されるべきである。なお、他の波長について、他の配置がより最適であり得る。例えば、異なる検出器アレイは、反対の配置においてバイアスをかけられてよく、積分容量素子115における積分電圧へ、仮想接地に対して減少し、次いで増大する。

## 【0045】

周期的に、クロック信号は、ピクセル単位で、行単位で、列単位で、又はそれらの何らかの組み合わせごとに、UCFE回路410を呼び出す。積分容量素子115における電圧が閾値を超える場合は、2つの事象が起こってよい。最初に、厳密な電荷減算のよう

、電荷除去事象 225 が U C F E 410 によって引き起こされ、上述されたように、電荷素量を積分容量素子 115 から除去する。加えて、U C F E 410 の出力は、電荷除去事象 225 が起こったことを列デジタル回路 420 に知らせるよう列サンプルライン 185 上で論理値をアサートするためにクロックによって（適切な時点で）有効にされる。フレーム期間の終わりに、残留電圧は、図 8 における波形の右手側において 435 で指定されるように、積分容量素子 115 に残存してよい。

#### 【0046】

図 9 を参照すると、電荷除去事象 225 が起こり、そのような事象が起きたことが列デジタル回路 420 に知らされる場合に、列デジタル回路 420（一実施形態において分散される。）は、上述されたように S R A M 又はレジスタファイルにおいてビットとして記憶されたカウンタ値を読み出し、値を“1”だけインクリメントし、その値を矢印 445 によって示されるように S R A M 又はレジスタファイルに書き戻してよい。他の例において、グレイコード又は線形フィードバックシフトレジスタ（L F S R）符号化のような代替のカウントシーケンスが実施されてよい。加えて、処理において、他の動作が実行されてよく、例えば、“ピクセル内”デジタルプロセッシングを実行するメカニズムとしてデクリメント又は（他の仮想ピクセル位置へ）シフトする。

#### 【0047】

図 10 を参照すると、読み出中積分を達成する一実施形態において、フレーム期間の終わりに、ストローブ又はクロックは、夫々のピクセル U C F E 410 に、積分容量素子 115 からの値をサンプル・アンド・ホールドキャパシタ 310 にコピー又は転送させて、積分容量素子の残留電圧を保持する。同時に、又は略同時に、列デジタル回路 420 は、矢印 465 によって示されるように、カウンタ値（S R A M 又はレジスタファイルに含まれる。）をスナップショット位置（同じく S R A M 又はレジスタファイルにある。）にコピーする。幾つかの実施において、全ての S R A M 又はレジスタファイルのカウンタ位置をそれらの対応するスナップショット位置に同時にコピーしようと試みることは、好ましくないことがあり、そのような動作は、追加の回路及び面積を必要とすることがあり、デジタルメモリ 230 の使用の価値を低下させ得る。然るに、一実施形態において、S R A M 又はレジスタファイルのビットは、例えば、16 といった何らかの適当な数量においてクラスタ化される。加えて、コピー又は転送の動作は、転送が順次に実行されるように、同数、例えば、16 のクロックサイクルを必要としてよい。一実施形態において、それらの 16 のサイクルは、スナップショット事象の存続期間を可能な限り短いまとめるように、可能な限り直ぐ近くにある。以下で更に論じられるように、このように S R A M 又はレジスタファイル（又は他のストレージ）をクラスタ化することには、多くの他の利点が存在し得る。

#### 【0048】

図 11 を参照すると、一実施形態において、サンプル・アンド・ホールドキャパシタ 310 の値及びスナップショットデジタル値は、出力ビデオストリーム 450 を形成するよう、ライン単位で、次いで列単位で読み出される。サンプル・アンド・ホールドキャパシタ 310 の値がライン 335 上で読み出されると（矢印 475 によって表される。）、列に基づく A D C 340 は、残留電圧を 2 進値に変換する。その後に、A D C の値及び記憶されているスナップショット値は、例えば、ピクセルごとに、結合され、ビデオ出力チャネル 450 において送信され、そして、デジタルフォーマッタ 460 によって符号化形式においてフォーマットされてよい（例えば、8 b 10 b）。

#### 【0049】

デジタルカウンタ 210 及びスナップショットレジスタのための S R A M 又はレジスタファイルストレージ、並びに撮像システムのデジタルプロセッシング回路を構成するために使用され得る多くの回路トポロジが存在する。S R A M 又はレジスタファイルは、F P A アレイ 195 におけるピクセルの 1 つの行及び少なくとも 1 つの列に付随してよい。一実施形態において、回路は、16 論理列幅による N ビット深の配置を含む。S R A M ワードライン高さは、代替的に、6 論理列に 2 ワード（例えば、デジタルカウンタのための 1

10

20

30

40

50

ワード及びスナップショットレジスタのための 1 ワード ) を乗じた結果である 32 ワードであってよい。デジタル回路を実施するために使用される回路は、デジタルカウンタ及びスナップショットレジスタを含むデジタルストレージの 1 行 × 16 列の配置を含んでよい。例えば、デジタルカウンタ及びスナップショットレジスタは、9 ビット幅 ( すなわち、 $N = 9$  ビット ) のブロックに配置される。ブロックは、16 列を単位として、何らかの所望の数の行を構成するようスタックされてよく、ブロックは、クロック及び他のデータ信号が自由にそれらを行き来することを可能にするようアライメントされてよい。あらゆる数のブロックが、所望の数の列を達成するよう互いに隣接して置かれてよい。他の行及び列サイズ配置が可能であり、且つ、行及び列の機能は入れ替えられてよいことが理解されるであろう。

10

#### 【 0050 】

上述されたように、SRAM 又はレジスタファイルの配置は、ハイブリッド化されたピクセルを適合させるために物理的に制限されない。更に、より大きいデジタルワード ( 例えば、13 ビット ) が、SRAM のために ROIC においてより広い面積を用いることによって形成され得る。一実施形態において、撮像システム ROIC のサイズは、例えば、およそ 31 ミリメートル × 25 ミリメートルであってよい。

#### 【 0051 】

撮像システムのデジタル回路の少なくとも一部を実施するための、SRAM 及び / 又はレジスタファイルのようなデジタルメモリの使用の更なる利点は、デジタルメモリにおける点欠陥を補償又は解消して、撮像システムのロバスト性を改善するために使用され得る様々なメカニズムが存在することである。SRAM における欠陥を補償する技術の一例は、2012 年 5 月 5 日付で出願された、 “Repair Device and Method for Integrated Circuit Structured Arrays” と題された自己の同時係属米国特許出願第 13/411967 号において記載されている。

20

#### 【 0052 】

このように、態様及び実施形態は、ピクセル内回路が 2 つの構造、例えば、アナログアレイ及びデジタルメモリに再分配される、デジタルピクセル能力を実施するアーキテクチャを提供する。デジタルメモリは、ROIC 上にあってもなくてもよい。アナログアレイは、上述されたように、ピクセルごとに、入力された光電流を量子化する。列に基づくストローブラインは、上述されたように、関連するデジタルカウンタ 210 をインクリメントするよう、量子化事象をデジタルアレイへ運ぶ。一実施形態において、サンプル・アンド・ホールドキャバシタ 310 がアナログアレイに加えられてよく、更なる列に基づくアナログ - デジタル変換器 340 は、システムのダイナミックレンジを広げるために使用されてよい。上記の実施形態は、スナップショット及び “ 読出中積分 ” 動作を実施する。しかしながら、他のモードの動作及び構成も実施されてよい。対象及び実施形態は、デジタルカウンタ 210 のようなデジタル機能を隣接する又はチップ外の領域に移動させることによって実効回路密度を増大させることを含め、上述されたように、多数の利点を提供することができる。一実施形態において、全体のデジタルカウンタ機能は、上述されたように、ピクセルのアナログ区域から除去され、デジタルアレイにおいて実装される。他の実施形態において、 “ サブカウンタ ” が、 “ プレスケーラ ” を提供するよう、比較的少ないフィットを含んでピクセル内で実装されてよい。サブカウンタは、例えば、1 ビット、2 ビット又は 3 ビットといった小さいビットのカウンタであるから、ピクセル内で多くの面積を使い尽くさず、一方、より大きい ( 例えば、12 ビット又は 16 ビット ) デジタルカウンタ 210 は、ピクセル外に移動され、上述されたように、デジタルメモリ 230 を用いて実施される。然るに、サブカウンタを含む実施形態でさえ、従来のデジタルピクセルに対する有意なサイズ及び / 又は密度の改善を達成することができる。

30

#### 【 0053 】

本発明の少なくとも一実施形態の幾つかの態様を先に記載してきたが、当然に、様々な代替、変更及び改善が当業者に容易に想到可能であろう。そのような代替、変更及び改善は、本開示の部分であるよう意図され、本発明の適用範囲内にあるよう意図される。然る

40

50

に、先の記載及び図面は、単に、一例である。

【図1】

【図2】

【図3】

【図4】

FIG. 4

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

### 【図 1 1】

---

フロントページの続き

(72)発明者 ボエムラー, クリスチャン, エム.

アメリカ合衆国 カリフォルニア州 93436 ロンポク コマース・ストリート 433

審査官 鈴木 肇

(56)参考文献 米国特許出願公開第2010/0194956(US, A1)

米国特許出願公開第2010/0140732(US, A1)

米国特許出願公開第2011/0215222(US, A1)

米国特許出願公開第2014/0061442(US, A1)

特表2006-523074(JP, A)

米国特許第6977601(US, B1)

特表2009-543454(JP, A)

特開2011-071958(JP, A)

米国特許出願公開第2008/0158400(US, A1)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 - 5/378

H01L 21/339

H01L 27/14 - 27/148

H01L 29/762