# ${\bf (19)}\ World\ Intellectual\ Property\ Organization$

International Bureau

(43) International Publication Date 30 August 2007 (30.08.2007) (10) International Publication Number WO 2007/098167 A2

- (51) International Patent Classification: *G01R 31/28* (2006.01) *G06F 11/00* (2006.01)

- (21) International Application Number:

PCT/US2007/004422

(22) International Filing Date:

19 February 2007 (19.02.2007)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

60/774,431

17 February 2006 (17.02.2006)

US

60/832,466

22 July 2006 (22.07.2006)

US

60/853,055

20 October 2006 (20.10.2006)

US

- (71) Applicant (for all designated States except US): MENTOR GRAPHICS CORPORATION [US/US]; 8005 Sw Boeckman Road, Wilsonville, OR 97070-7777 (US).

- (72) Inventors; and

- (75) Inventors/Applicants (for US only): MRUGAL-SKI, Grzegorz [PL/US]; 7114 Sw Bouchaine Street, Wilsonville, OR 97070 (US). RAJSKI, Janusz [CA/US]; 6502 Horton Rd., West Linn, OR 97068 (US). TYSZER, Jerzy [PL/PL]; Os. Stare Zegrze 89c/2, PL-61-249 Poznan (PL). CHENG, Wu-tung [US/US]; 19030 Sw 35th Place, Lake Oswego, OR 97034 (US). MUKHERJEE, Nilanjan [IN/US]; 298028 Sw Flynn Street, Wilsonville, OR 97070 (US). KASSAB, Mark [CA/US]; 28911 Sw Cascade Loop, Wilsonville, OR 97070 (US).

- (74) Agent: BIBLE, Patrick, M.; Klarquist Sparkman, Llp, One World Trade Center, Suite 1600, 121 Sw Salmon Street, Portland, OR 97204 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LV, LY, MA, MD, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RS, RU, SC, SD, SE, SG, SK, SL, SM, SV, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, LV, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

#### Published:

without international search report and to be republished upon receipt of that report

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

(57) Abstract: Disclosed herein are exemplary embodiments of a so-called "X-press" test response compactor. Certain embodiments of the disclosed compactor comprise an overdrive section and scan chain selection logic. Certain embodiments of the disclosed technology offer compaction ratios on the order of 100Ox. Exemplary embodiments of the disclosed compactor can maintain about the same coverage and about the same diagnostic resolution as that of conventional scan-based test scenarios. Some embodiments of a scan chain selection scheme can significantly reduce or entirely eliminate unknown states occurring in test responses that enter the compactor. Also disclosed herein are embodiments of on-chip comparator circuits and methods for generating control circuitry for masking selection circuits.

#### MULTI-STAGE TEST RESPONSE COMPACTORS

#### CROSS REFERENCE TO RELATED APPLICATIONS

This application claims the benefit of U.S. Provisional Patent Application No. 60/774,431, titled "Multi-Stage Test Response Compactors," filed February 17, 2006; U.S. Provisional Patent Application No. 60/832,466, titled "Multi-Stage Test Response Compactors," filed July 22, 2006; and U.S. Provisional Patent Application No. 60/853,055, titled "Multi-Stage Test Response Compactors," filed October 20, 2006. Each of these applications is incorporated herein by reference.

10

5

#### **FIELD**

The disclosed technologies relate to testing electronic circuits, particularly using compression hardware.

15

20

#### **BACKGROUND**

Testing an electronic circuit for possible defects can result in a significant amount of test data (for example, test responses), particularly if the circuit is large and/or complicated. Test responses stored by scan chains in a circuit can be compressed, for example, to allow for the responses to be analyzed using fewer test resources (for example, test pins), possibly by automated testing equipment (ATE) external to the circuit. Test response compactors exist, but the compaction ratio of these devices is often limited to the ratio of the number of scan chains to the number of compactor outputs. Accordingly, there is a need for compaction schemes providing potentially higher compaction ratios.

25

30

#### **SUMMARY**

Disclosed herein are exemplary embodiments of improved test response compactors, methods of operation and designing such compactors, and systems using such compactors. Certain embodiments of such compactors are referred to herein as "X-(su)press" or "X-press" test response compactors and comprise a first compaction section, a second compaction section (sometimes referred to herein as

the "overdrive section"), and scan chain selection logic for selectively masking one or more test response bits. Certain embodiments of the disclosed technology offer compaction ratios on the order of 1000x. Exemplary embodiments of the disclosed compactor can maintain about the same coverage and about the same diagnostic resolution as that of conventional scan-based test scenarios. Some embodiments of a scan chain selection scheme can significantly reduce or entirely eliminate unknown states occurring in test responses that enter the compactor.

5

10

15

20

25

30

Various aspects and features of the disclosed technology (which can be realized alone or in combination with one another) can include the following: (1) an architecture of a multi-stage test response compactor that works with multiple scan chains, generally preserves the benefits of spatial compaction, and offers comparatively higher compression ratios; (2) a multi-level scan chain selection logic that can be integrated with the compactor; and (3) a methodology for determining per-pattern scan chain selection masks employed to suppress unknown ("X") states based on a ranking of scan chains.

In some embodiments of the disclosed technologies, two-stage test response compactors with scan chain selection logic (for example, for selectively masking one or more test response bits) are provided. Embodiments of the compactor are capable of handling a wide range of X state profiles, offer compaction ratios higher than the ratio of scan chains to compactor outputs, and/or provide high diagnostic resolution. In addition, and in certain embodiments, on-chip comparator and registration circuitry records fail log information. This can result in a significant reduction of test time. Furthermore, embodiments of the multi-stage compactors described herein can be useful for legacy cores where higher compression ratios can only be achieved by external solutions, as their scan chain configurations generally cannot be changed.

Also described herein are exemplary methods for synthesizing selection logic for masking one or more test response bits. These techniques can reduce the data required to operate the selection logic. Moreover, exemplary selection techniques for determining mask bits (also referred to herein as "masking instructions" or "masking instruction bits") for the selection logic are disclosed.

One exemplary embodiment disclosed herein is an apparatus for compacting test responses of a circuit-under-test. The apparatus includes, for example, a first spatial compactor comprising a plurality of first-compactor inputs and a firstcompactor output; a register comprising a register input coupled to the firstcompactor output and a plurality of register outputs; and a second spatial compactor comprising a plurality of second-compactor inputs coupled to the plurality of register outputs and a second-compactor output. In certain implementations of these embodiments, the register is operable to load test response bits through the register input and to output the test response bits in parallel through the plurality of register outputs. In some embodiments the first spatial compactor and the second spatial compactor are feedback free. In certain embodiments, the first spatial compactor and the second spatial compactor comprise respective networks of XOR or XNOR gates. In some embodiments, at least one of the first spatial compactor and second spatial compactor is a pipelined spatial compactor. The register can comprise two or more sequential elements coupled in series. The register can also be operable to serially load the test response bits. In certain embodiments, the first spatial compactor comprises a plurality of first-compactor outputs, and in some embodiments the second spatial compactor comprises a plurality of secondcompactor outputs.

5

10

15

20

25

30

In additional embodiments, the apparatus can further comprise a first set of masking logic coupled to the plurality of first-compactor inputs and a second set of masking logic coupled between the plurality of register outputs and the plurality of second-compactor inputs. In some embodiments, the apparatus further comprises selection logic having one or more selection-logic inputs and a plurality of selection-logic outputs, the plurality of selection-logic outputs being coupled to respective inputs of the first set of masking logic and respective inputs of the second set of masking logic, the selection logic being operable to selectively control the first set of masking logic and the second set of masking logic in response to one or more masking instruction bits received at the one or more selection-logic inputs. In certain embodiments, the selection logic comprises a network of digital logic gates (for example, XOR or XNOR gates) configured according to polynomials (for

example, polynomials describing respective relationships between at least one selection logic input and at least one selection logic output). In some embodiments, the register is a first register, the selection logic comprises a plurality of selection-logic inputs, and the apparatus further comprises a second register having a second-register input and a plurality of second-register outputs, the plurality of second-register outputs being coupled to the plurality of selection-logic inputs. In certain embodiments of the apparatus, the masking instruction bits are uncompressed bits received from, for example, an external tester, an on-chip memory, or an on-chip decompressor.

5

10

15

20

25

30

Another exemplary embodiment disclosed herein is a method for compacting test responses of a circuit-under-test. In this exemplary embodiment, a plurality of uncompressed test response bits is compressed, thereby producing a first set of compressed test response bits. The first set of compressed test response bits are loaded into a plurality of sequential elements. The first set of compressed test response bits are unloaded in parallel from the plurality of sequential elements, and the first set of compressed test response bits are further compressed. In some embodiments, the loading occurs in a first period of two or more clock cycles, and the unloading occurs in a second period of one clock cycle. In certain embodiments, one or more of the uncompressed test response bits are selectively masked before the uncompressed test response bits are compressed and/or further compressed. In some embodiments, masking instruction bits for controlling the selective masking are loaded as the uncompressed test response bits are being compressed and/or as the compressed test response bits are being further compressed. Circuits for compressing test responses that are configured to perform these methods are also disclosed.

Another exemplary embodiment disclosed herein is an apparatus for compacting test responses of a circuit-under-test. The apparatus of this embodiment includes two or more sequential elements having respective inputs and outputs. The sequential elements are operable to input a group of two or more uncompressed test response bits through the inputs of the sequential elements and are further operable to output in parallel the group of uncompressed test response bits through the

5

10

15

20

25

30

outputs of the sequential elements. The apparatus further includes a first spatial compactor comprising a plurality of first-compactor inputs and a first-compactor output. The first-compactor inputs are coupled to the outputs of the sequential elements. In some embodiments, the apparatus further includes a second spatial compactor comprising a plurality of second-compactor inputs and a secondcompactor output. In these embodiments, one of the plurality of second-compactor inputs is coupled to the first-compactor output. In certain embodiments, the two or more sequential elements are scan cells in a scan chain of the circuit-under-test. In some embodiments, the two or more sequential elements form a register coupled to an output of a scan chain of the circuit-under-test. In certain embodiments, the first spatial compactor and the second spatial compactor are feedback free. In some embodiments, the first spatial compactor and the second spatial compactor comprise respective networks of XOR or XNOR gates. In certain embodiments, the secondcompactor inputs are coupled to outputs of multiple additional spatial compactors. In these embodiments, each additional spatial compactor is configured to input additional uncompressed test response bits received in parallel from additional respective sequential elements. Some embodiments further comprise a first set of masking logic coupled to the plurality of first-compactor inputs, and a second set of masking logic coupled to the plurality of second-compactor inputs. In certain embodiments, the apparatus further comprises selection logic having one or more selection-logic inputs and a plurality of selection-logic outputs. In these embodiments, the plurality of selection-logic outputs is coupled to respective inputs of the first set of masking logic and respective inputs of the second set of masking logic. Furthermore, the selection logic can be operable to selectively control the first set of masking logic and the second set of masking logic in response to one or more masking instruction bits received at the one or more selection-logic inputs. The selection logic can comprise, for example, a network of XOR or XNOR gates configured according to polynomials. In certain embodiments, the apparatus further comprises a register having a register input and a plurality of register outputs. In these embodiments, the plurality of register outputs is coupled to the plurality of selection-logic inputs.

Another exemplary embodiment disclosed herein is a method of testing a circuit-under-test. In this exemplary embodiment, test pattern data is provided to inputs of a circuit-under-test during a first interval. Masking instructions for a masking circuit are provided to the inputs of the circuit-under-test during a second interval. In certain embodiments, the first interval precedes the second interval. In other embodiments, the second interval precedes the first interval. In some embodiments, the first interval comprises a third and a fourth interval and the second interval comprises a fifth and sixth interval, and the third and fourth intervals are interspersed with the fifth and sixth intervals. In certain embodiments, the masking instructions are applied to a masking circuit as a test response to a test pattern generated from the test pattern data is being unloaded from the circuit-under-test. In some embodiments, the masking instructions are applied to a masking circuit as a test response to a test pattern generated from other test pattern data is being unloaded from the circuit-under-test. The method can further comprise masking one or more test response bits according to the masking instructions. Circuits for performing these exemplary methods are also disclosed.

5

10

15

20

25

30

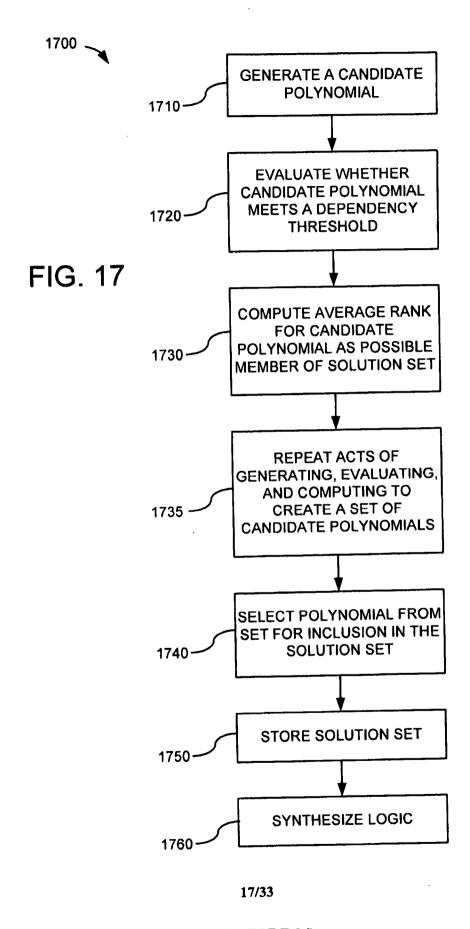

Another exemplary embodiment described herein is a method of generating selection logic for a selection circuit used to control the masking of unknown states during test response compaction. In this embodiment, a candidate polynomial for possible inclusion in a set of accepted polynomials is generated (for example, randomly). The candidate polynomial and the accepted polynomials describe connections of two or more inputs of the selection logic to a respective output of the selection circuit. One or more test sets of polynomials are selected. The test sets respectively comprise at least the candidate polynomial and one or more polynomials from the set of accepted polynomials. Rank values for the test sets are computed. The candidate polynomial is selected for inclusion in the set of accepted polynomials based at least in part on the rank values. The set of accepted polynomials (with the candidate polynomial) is stored on one or more computer-readable media. In certain embodiments, the method further includes generating a circuit description of the selection logic and storing the circuit description of the selection logic on one or more computer-readable media. In these embodiments, the

selection logic implements polynomials from the set of accepted polynomials. In some embodiments, the method further includes determining whether the candidate polynomial shares more than a fixed number of terms with one or more of the polynomials in the set of accepted polynomials, and generating a new candidate polynomial if the candidate polynomial does share more than the fixed number of terms with one or more of the polynomials in the set of accepted polynomials. In certain embodiments, the act of computing the rank values further comprises averaging the rank values for the two or more test sets of polynomials, and the act of selecting the candidate polynomial is based at least in part on the average rank value. In some embodiments, the acts of generating, selecting, and computing are repeated for a plurality of additional candidate polynomials. In certain embodiments, the act of selecting the candidate polynomial for inclusion in the accepted set of polynomials is further based on comparing the average rank value of the candidate polynomial with respective average rank values of the additional candidate polynomials. In some embodiments, the act of computing the rank values for the two or more sets of polynomials comprises determining reduced-row echelon forms of the two or more test sets of polynomials.

5

10

15

20

25

30

Another exemplary embodiment disclosed herein is a method of generating masking instructions for a selection circuit operable to mask test response bits during testing of a circuit-under-test. In this embodiment, a test pattern being applied to the circuit-under-test is simulated to produce a test response. One or more unknown states are identified in the test response. One or more test response bits are selected for masking based at least in part on the one or more identified unknown states. One or more indications of the selected test response bits are stored on one or more computer-readable media. In certain embodiments, masking instructions for a selection circuit are encoded based at least in part on the selected one or more test response bits. In some embodiments, one or more fault observation sites in the test response are identified, and the selection of the one or more test response bits for masking is further based at least in part on the one or more identified fault observation sites. In certain embodiments, the act of selecting one or more test response bits for masking comprises assigning weights to one or more scan cells of a

selected scan chain of the circuit-under-test based at least in part on the one or more identified unknown states, the one or more identified fault observation sites, or both the one or more identified unknown states and the one or more identified fault observation sites. The method can further include aggregating the weights for one or more groups of scan cells within the selected scan chain, computing one or more scores for the selected scan chain based at least in part on the aggregated weights, and determining whether to mask test response bits from the selected scan chain based at least in part on the scores. In some embodiments, the weights represent a type of value stored in the scan cells after the simulation of the test pattern being applied. In certain embodiments, one of the scores computed for the selected scan chain is proportional to an estimated number of errors that will be preserved if the selected scan chain is masked and/or one of the scores computed for the selected scan chain is proportional to an estimated number of errors that will be preserved if the selected scan chain is not masked.

5

10

15

20

25

30

Another exemplary embodiment disclosed herein is a method of generating masking instructions for a selection circuit operable to mask test response bits during testing of a circuit. According to this embodiment, weights are assigned to one or more scan cells of a selected scan chain. The weights are aggregated for one or more groups of scan cells within the selected scan chain. One or more scores are computed for the selected scan chain based at least in part on the aggregated weights. A determination is made whether to mask test response bits from the selected scan chain based at least in part on the scores. The determination is stored on one or more computer-readable media. In certain embodiments, masking instructions for the selection circuit are encoded based at least in part on the determination, and the masking instructions are stored on one or more computerreadable media. In some embodiments, the weights represent a type of value stored in the scan cells after a test pattern is applied to a circuit-under-test. In certain embodiments, the act of assigning weights comprises assigning a first weight to a first respective scan cell in the selected scan chain that captures an unknown value. In some embodiments, the act of assigning weights comprises assigning a second weight to a second respective scan cell in the selected scan chain that captures a

value indicative of a targeted fault. In certain embodiments, the second weight is greater than the first weight. In some embodiments, the act of assigning weights further comprises assigning a third weight to a third respective scan cell in the selected scan chain that capture a value that is neither unknown nor indicative of a targeted fault. In certain embodiments, the second weight is greater than both the first weight and the third weight, and the third weight is greater than the first weight. In some embodiments, one of the scores computed for the selected scan chain is proportional to an estimated number of errors that will be preserved if the selected scan chain is not masked and/or one of the scores computed for the selected scan chain is proportional to an estimated number of errors that will be preserved if the selected scan chain is masked. In certain embodiments, the acts of assigning, aggregating, and computing are repeated for one or more additional scan chains, thereby computing one or more scores for each of the one or more additional scan chain. In some embodiments, the act of determining whether to mask test response bits from the selected scan chain further comprises comparing the one or more scores of the selected scan chain with the one or more scores for each respective additional scan chain.

5

10

15

20

25

30

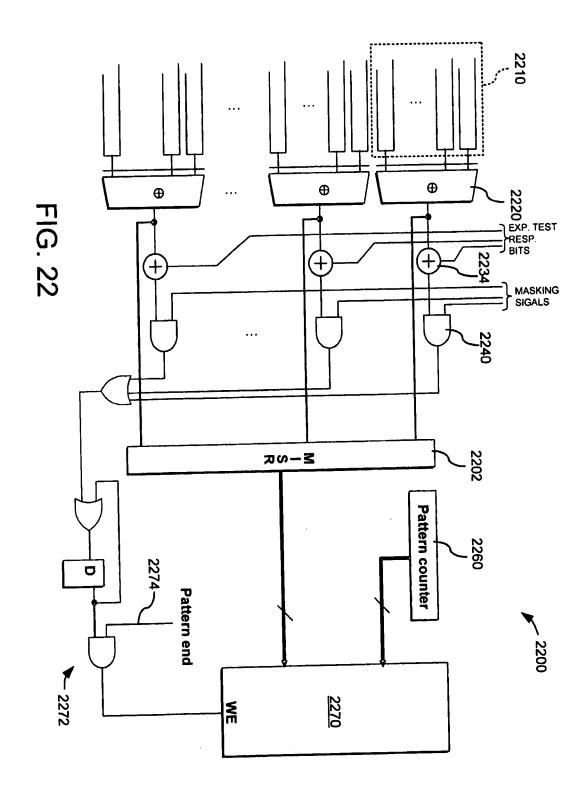

Another exemplary embodiment disclosed herein comprises a method of testing a plurality of circuits in a testing system. At a first input of one of the plurality of circuits, masking data for controlling a masking circuit is received. At a second input of the one of the plurality of circuits, expected test response data for evaluating test responses generated during testing of the one of the plurality of circuits is received. In this exemplary embodiment, the masking data and the expected test response data are received simultaneously at the first and second inputs. In some embodiments, the test responses are compacted test responses. In certain embodiments, the test responses are loaded into a multiple-input shift register (MISR), one or more compactor signatures are produced in the MISR, and the one or more compactor signatures are stored in one or more computer-readable media. In some embodiments, a list of candidate fault locations is generated according to the one or more compactor signatures, and the list of candidate fault locations is stored on one or more computer-readable media. In certain

embodiments, one or more error vectors are generated based at least in part on the test responses and the expected test response data. In these embodiments, the error vectors can be compacted in a multiple-input shift register to produce one or more compactor signatures, and the one or more compactor signatures can be stored in one or more computer-readable media. The multiple-input shift register can produce a compactor signature from multiple error vectors input over a plurality of shift cycles. For example, the multiple-input shift register can produce one compactor signature per test pattern. In certain embodiments, an error vector is generated based at least in part on the test responses and the expected test response data (for example, for a single shift cycle), and the error vector is stored on one or more computer-readable media. In some embodiments, the test responses are loaded into a priority encoder circuit. In these embodiments, the test responses comprise test response values from three or more compactor outputs, and the priority encoder circuit is configured to detect three or more errors in the test responses input in a single shift cycle.

5

10

15

20

25

30

Another exemplary embodiment disclosed herein is an apparatus comprising a plurality of scan chain groups, each scan chain group of the plurality comprising one or more scan chains and one or more corresponding scan chain group outputs. The apparatus further comprises a plurality of comparator circuits, each comparator circuit of the plurality comprising a comparator input and a comparator output. The apparatus also includes a multiple-input shift register (MISR) comprising MISR inputs and a MISR output. The apparatus additionally includes a plurality of compactors, each compactor of the plurality comprising one or more compactor inputs coupled to the scan chain group outputs of a respective one of the plurality of scan chain groups and further comprising a compactor output coupled directly to a respective one of the MISR inputs and also coupled to the comparator input of a respective comparator. In some embodiments, the apparatus further includes a memory with a first input coupled to the MISR output and a second input coupled to a pattern counter. In certain embodiments, the apparatus further comprises a plurality of masking gates, each masking gate being coupled between the compactor output of a respective one of the comparators and a respective input of the MISR.

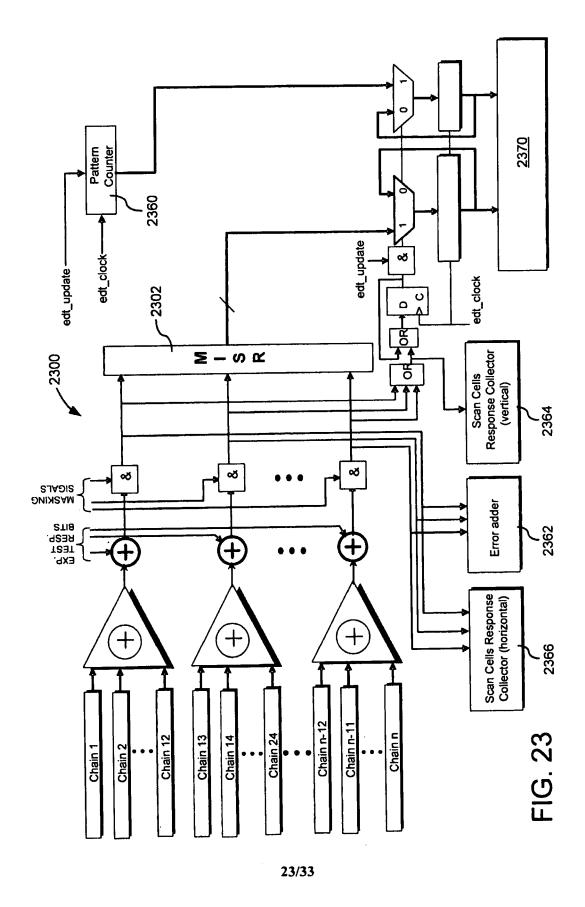

Another exemplary embodiment disclosed herein is an apparatus comprising a plurality of scan chain groups, each scan chain group of the plurality comprising one or more scan chains and one or more corresponding scan chain group outputs. The apparatus of this embodiment further comprises a plurality of comparator circuits, each comparator circuit of the plurality comprising a comparator input and a comparator output. The apparatus also comprises a multiple-input shift register (MISR) comprising MISR inputs coupled to the comparator outputs of respective comparators and a MISR output. The apparatus further comprises a plurality of compactors, each compactor of the plurality comprising one or more compactor inputs coupled to the scan chain group outputs of a respective one of the plurality of scan chain groups and further comprising a compactor output coupled to the comparator input of a respective comparator. The apparatus further includes a first collector circuit coupled to one or more of the comparator outputs. The first collector circuit can be configured to record which one or more of the plurality of compactors produces one or more error outputs during testing. The apparatus also includes a second collector circuit coupled to one or more comparator outputs. The second collector circuit can be configured to record one or more time indicators for the one or more error outputs. In certain embodiments, the second collector circuit is coupled to two or more of the comparator outputs through an OR gate. Some embodiments further include a memory having an input coupled to the MISR output. Certain embodiments further include a plurality of masking circuits, each masking circuit having a masking circuit input coupled to the comparator output of a respective comparator and a masking circuit output coupled to a respective MISR input of the MISR.

25

30

5

10

15

20

Another exemplary embodiment disclosed herein is an apparatus for testing a plurality of electronic circuits. The apparatus includes a plurality of scan chain groups, each scan chain group of the plurality comprising one or more scan chains and one or more corresponding scan chain group outputs. The apparatus also includes a plurality of comparator circuits, each comparator circuit of the plurality comprising a comparator input and a comparator output. The apparatus further includes an encoder circuit comprising a plurality of encoder inputs and an encoder

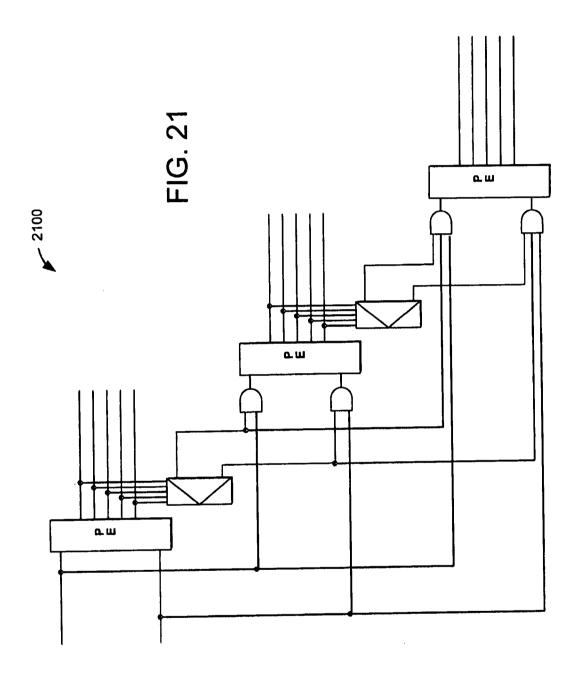

output. The encoder inputs are coupled to respective comparator outputs. The apparatus also includes a plurality of compactors, each compactor comprising one or more compactor inputs coupled to the scan chain group outputs of a respective one of the scan chain groups and further comprising a compactor output coupled to the comparator input of a respective comparator. The encoder of this embodiment is configured to detect more than two error values output from the compactor outputs (for example, during a single shift cycle). The encoder can additionally be configured to detect two or fewer error values output from the compactor outputs. Some embodiments further include a plurality of masking circuits, each masking circuit having a masking circuit input coupled to the comparator output of a respective compactor and a masking output coupled to respective encoder inputs. Certain embodiments also comprise a memory coupled to the encoder output.

5

10

15

20

25

30

Any of the disclosed methods can be implemented as computer-readable media comprising computer-executable instructions for causing a computer to perform the methods. Further, computer-readable media storing signatures produced by any of the disclosed compactors, storing lists of fault candidates or faulty scan cell candidates identified by any of the disclosed methods, storing circuit descriptions for implementing any of the disclosed compactor embodiments, or storing final or intermediate results for any of the described methods are also disclosed.

The foregoing and other objects, features, and advantages of the invention will become more apparent from the following detailed description, which proceeds with reference to the accompanying figures.

#### **BRIEF DESCRIPTION OF THE DRAWINGS**

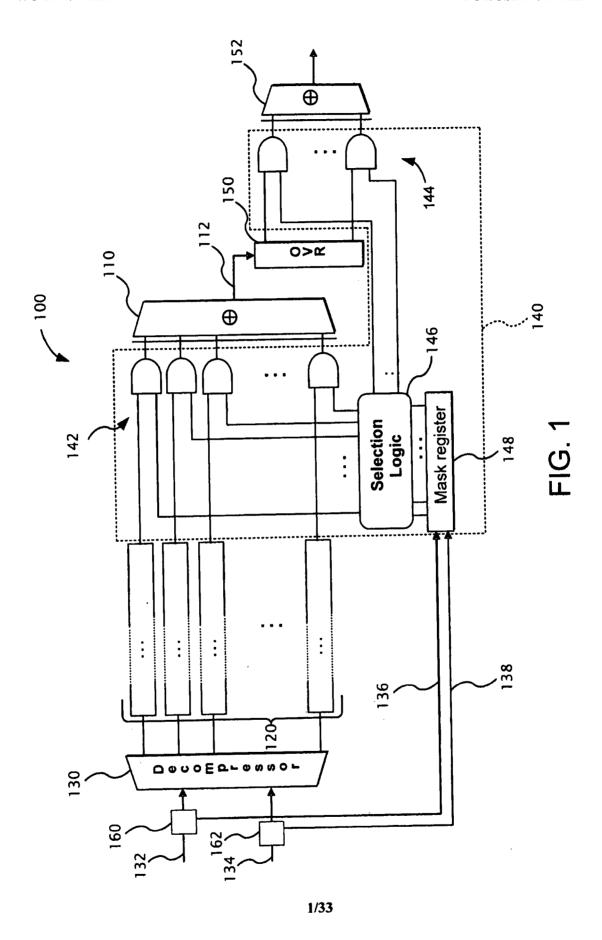

- FIG. 1 shows an exemplary embodiment of a test response compactor architecture.

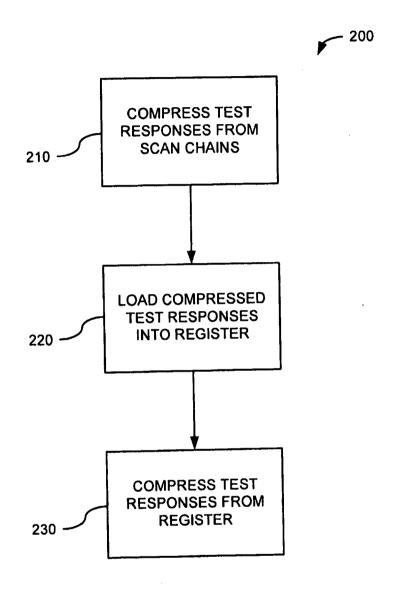

- FIG. 2 shows a block diagram of one embodiment of a method for compressing test responses.

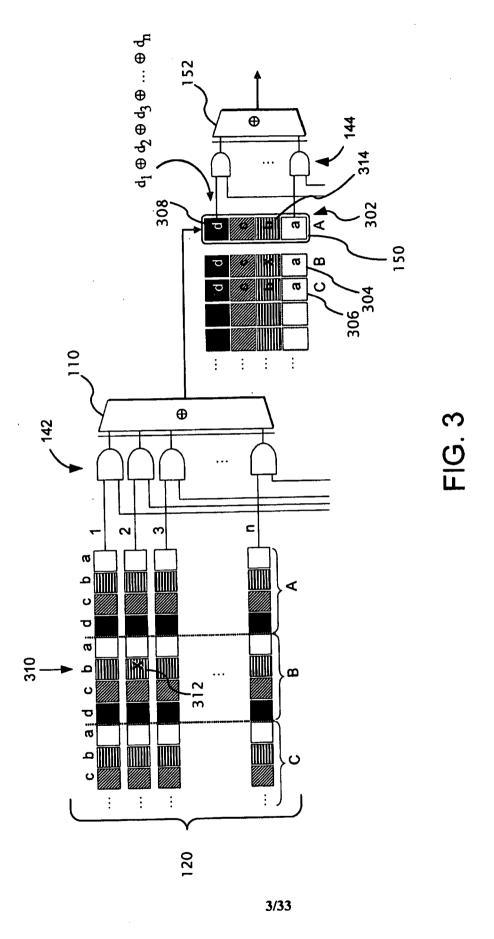

- FIG. 3 illustrates one example of how a selector circuit can be used to handle X states that can appear in scan chains of a circuit-under-test.

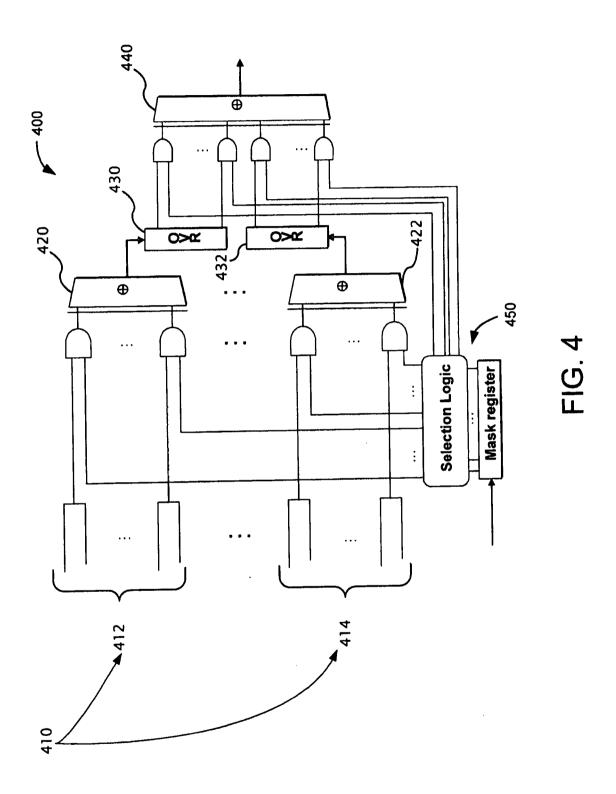

FIG. 4 shows a block diagram of an additional embodiment of a test response compactor architecture.

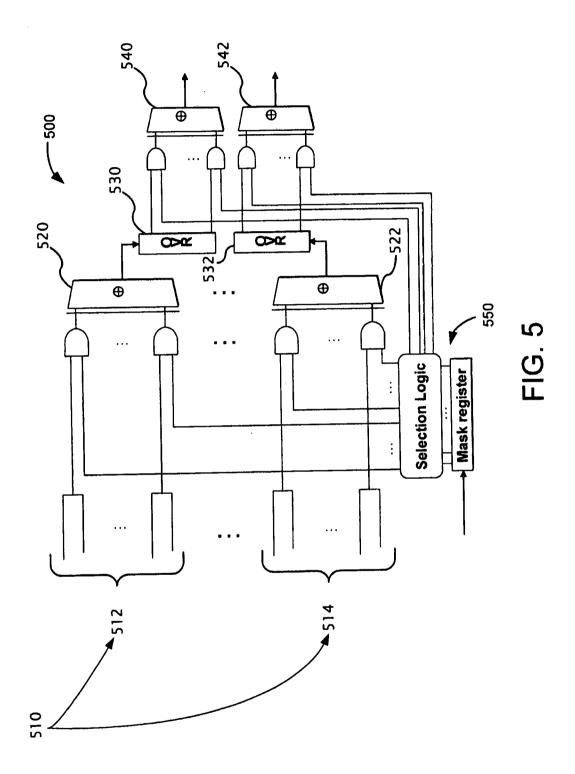

- FIG. 5 shows a block diagram of an additional embodiment of a test response compactor architecture.

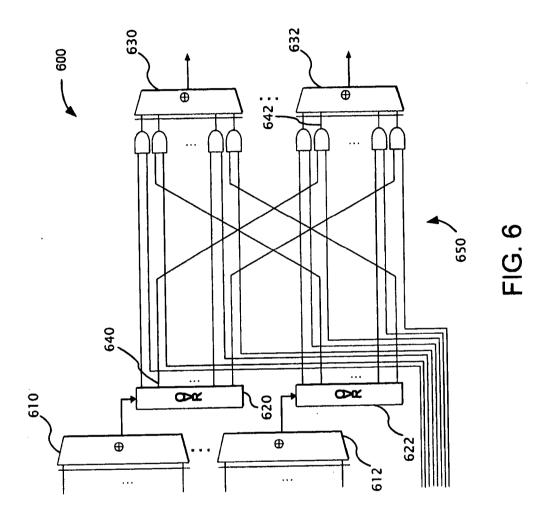

- FIG. 6 shows a block diagram of an additional embodiment of a test response compactor architecture.

5

20

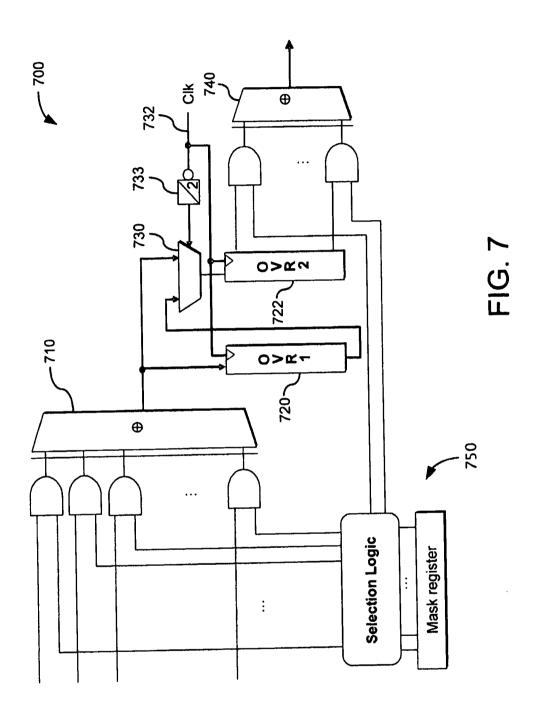

- FIG. 7 shows a block diagram of an additional embodiment of a test response compactor architecture.

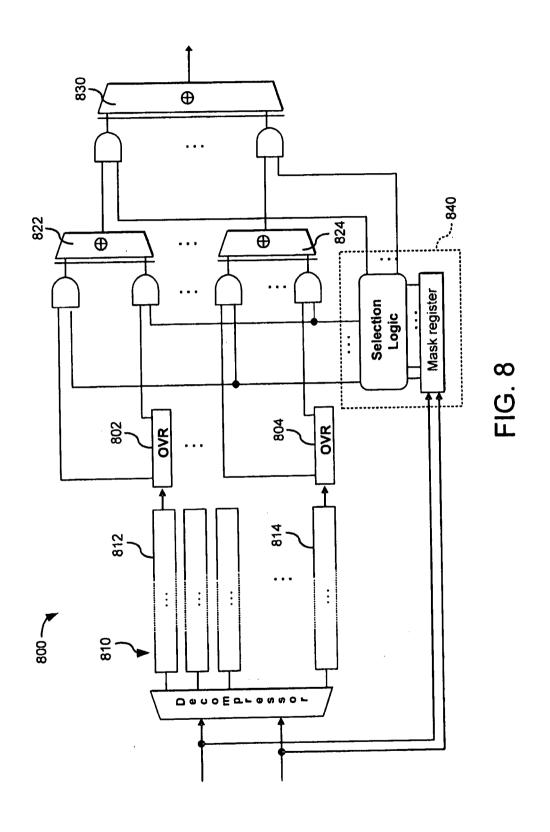

- FIG. 8 shows a block diagram of an additional embodiment of a test response compactor architecture.

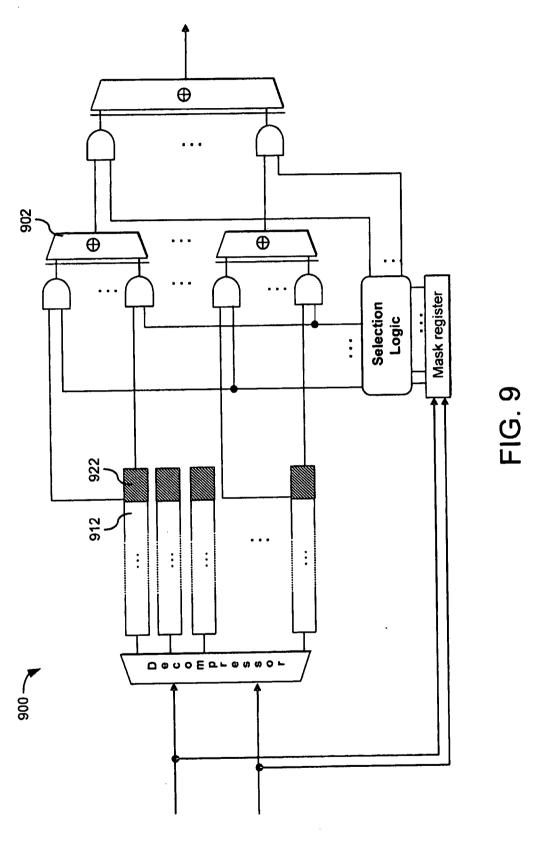

- FIG. 9 shows a block diagram of an additional embodiment of a test response compactor architecture.

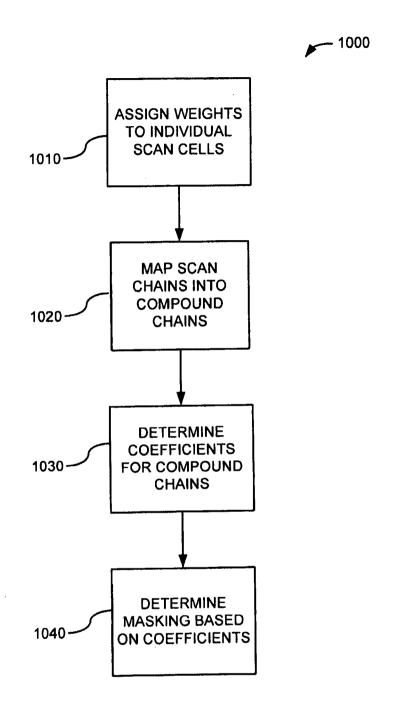

- FIG. 10 shows a block diagram of one embodiment of a method for determining masking signals for use with a selector circuit.

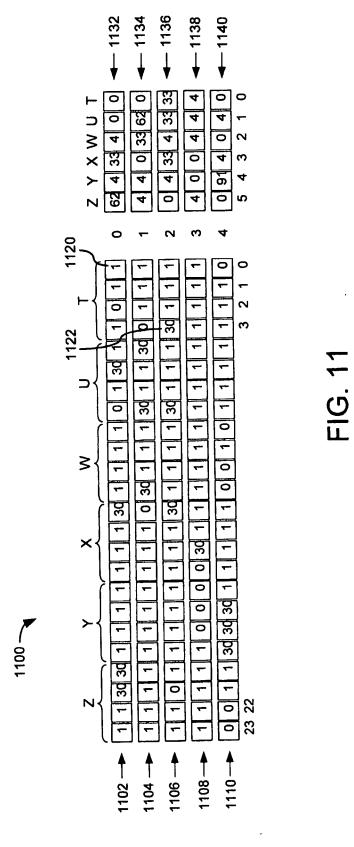

- FIG. 11 shows one embodiment of a representation of scan chains.

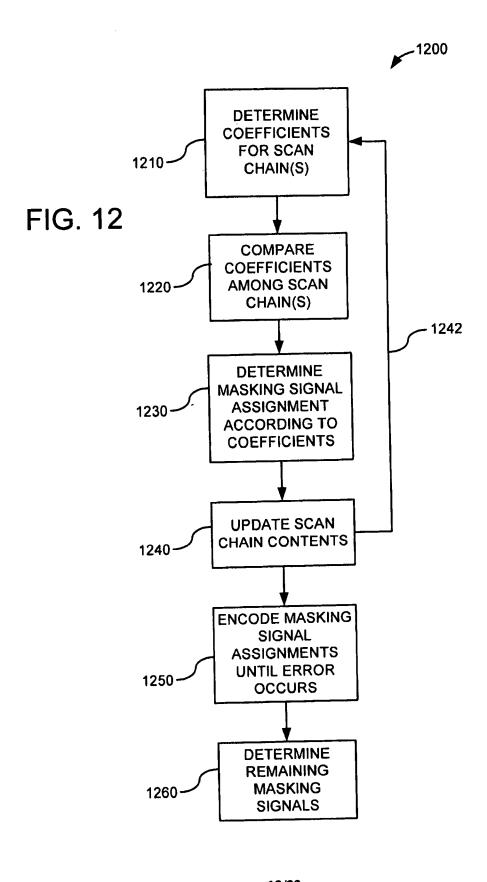

- FIG. 12 shows a block diagram of one embodiment of a method for selecting scan chains to mask.

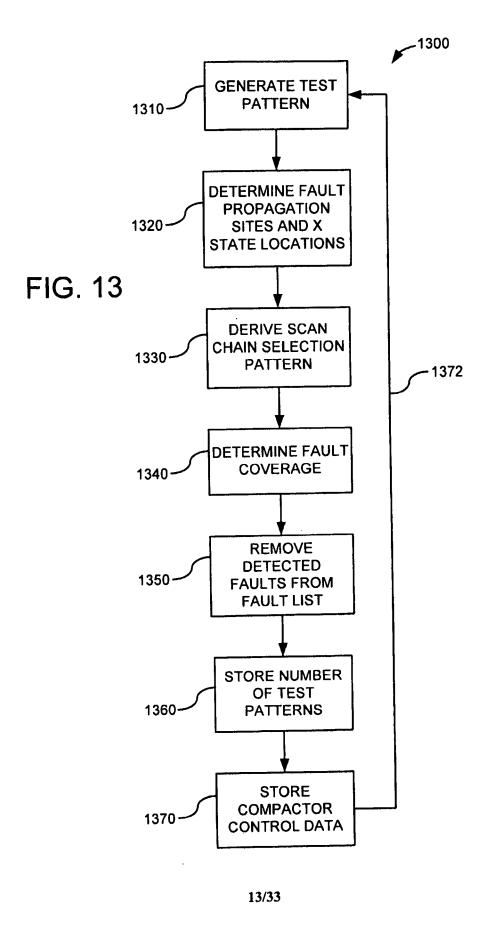

- FIG. 13 show a block diagram of one embodiment of a method for using test patterns in the presence of a selective compactor.

- FIGS. 14 and 15 show tables describing experimental results of using methods and apparatus described herein.

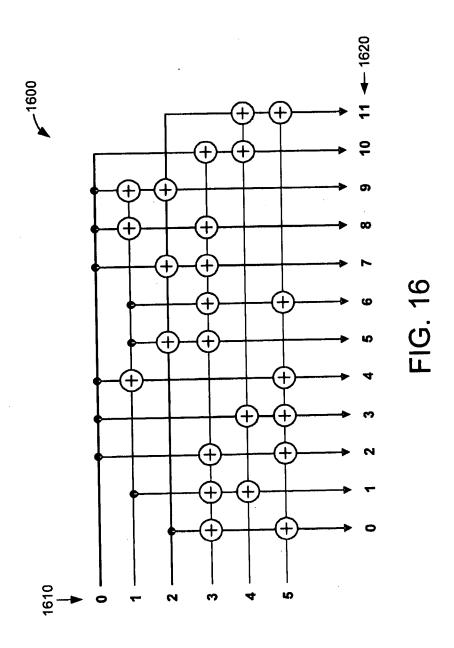

- FIG. 16 shows one embodiment of a selection logic circuit.

- FIG. 17 shows a block diagram of one embodiment of a method for generating control logic for a selection circuit.

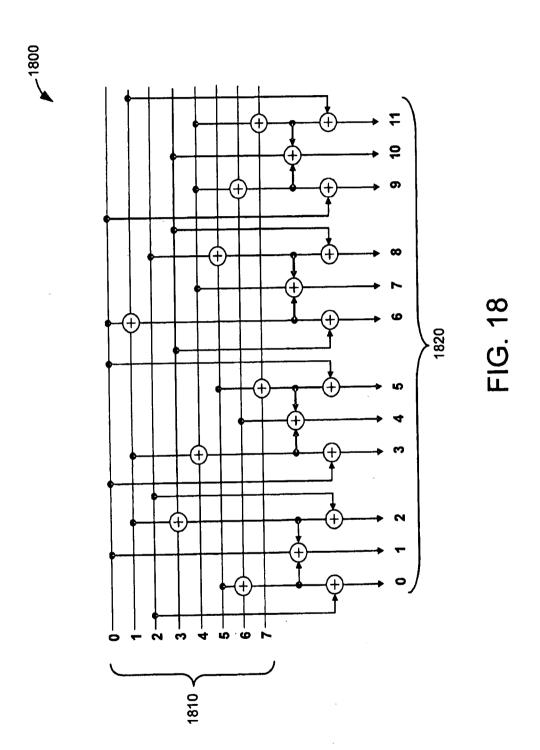

- FIG. 18 shows one embodiment of a selection logic circuit.

- FIG. 19 shows a block diagram of one embodiment of a method of finding top-up stimuli for a test response compactor architecture.

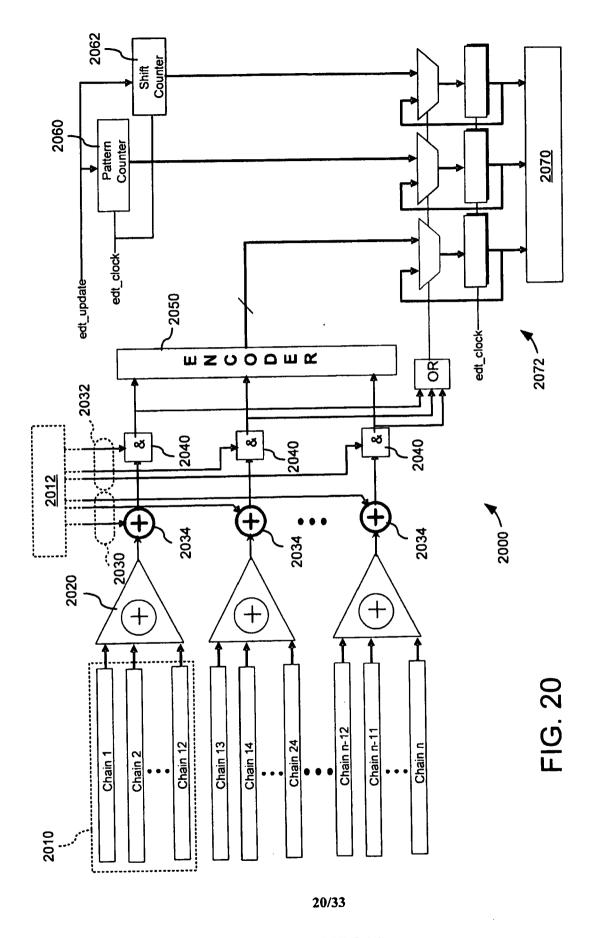

- FIG. 20 shows a block diagram of one embodiment of an exemplary on-chip testing architecture.

- FIG. 21 shows a block diagram of one embodiment of a priority encoder.

FIG. 22 shows a block diagram of a further embodiment of an exemplary onchip testing architecture.

FIG. 23 shows a block diagram of an additional embodiment of an exemplary on-chip testing architecture.

5

15

30

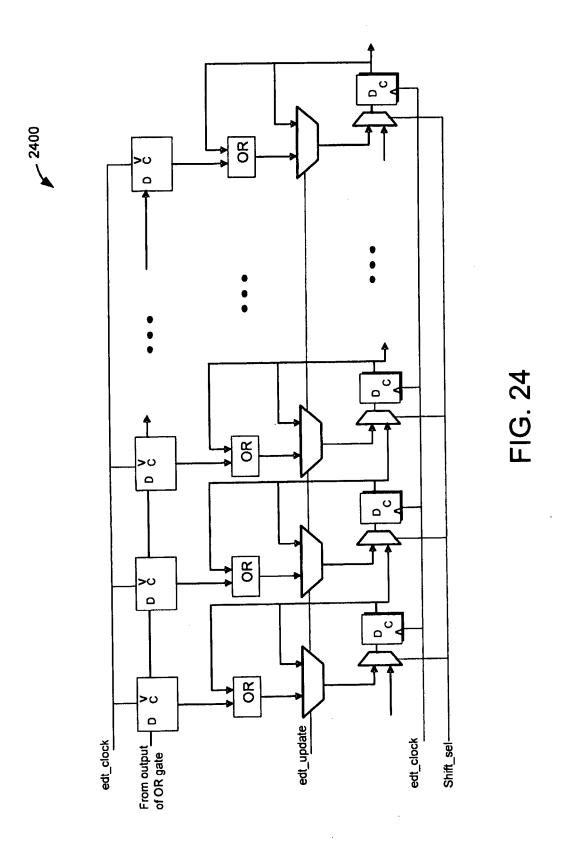

- FIG. 24 shows a block diagram of one embodiment of a vertical collector circuit for use with the on-chip testing architecture of FIG. 23.

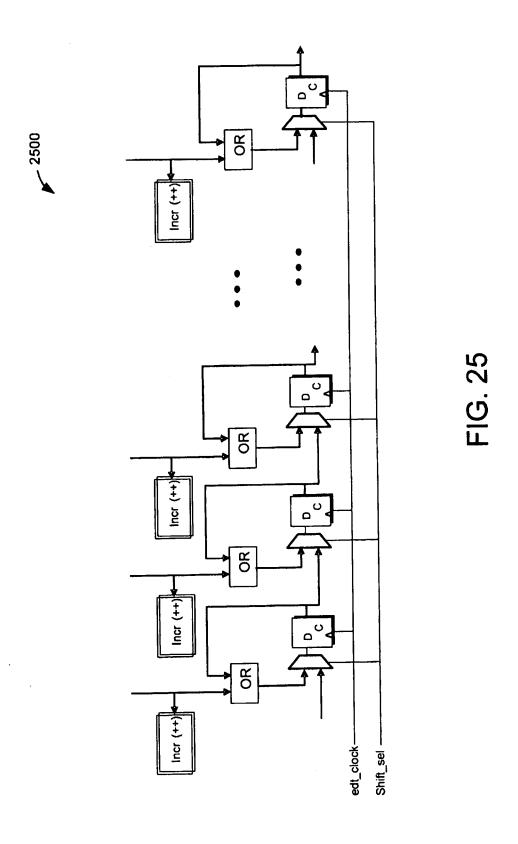

- FIG. 25 shows a block diagram of one embodiment of a horizontal collector circuit for use with the on-chip testing circuit compactor architecture of FIG. 23.

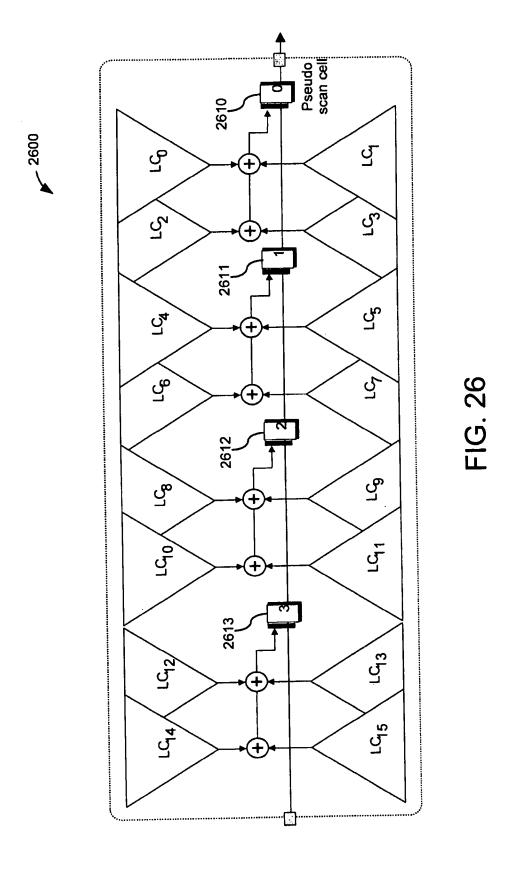

- FIG. 26 illustrates a block diagram of a transformed circuit for diagnosis.

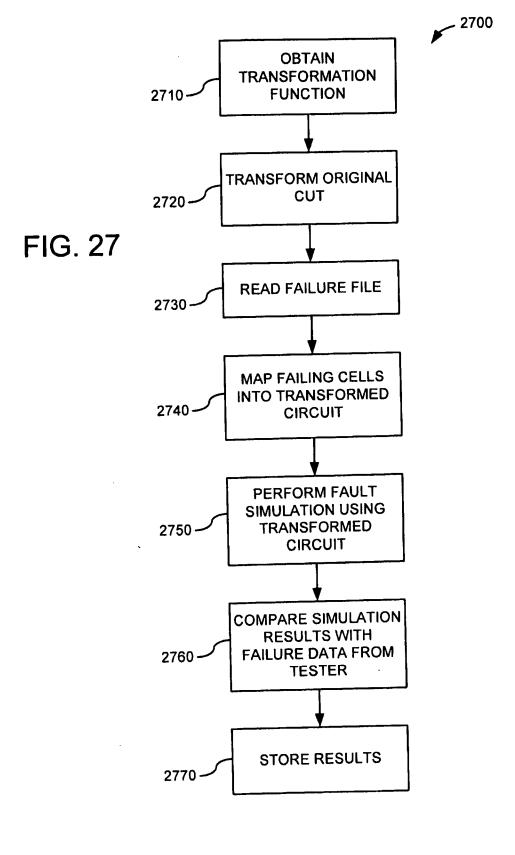

- FIG. 27 shows a block diagram of one exemplary method of performing fault diagnosis of a tested circuit.

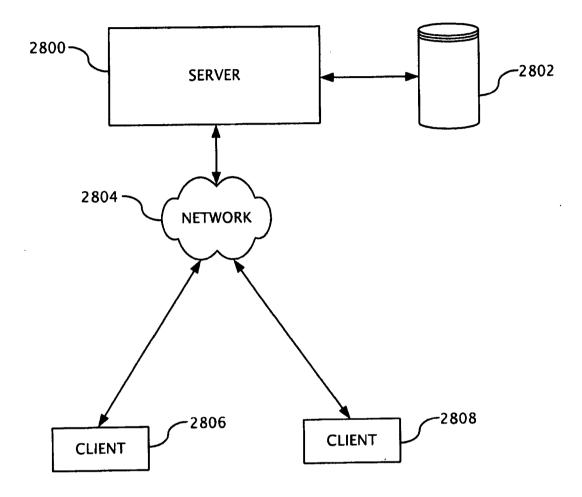

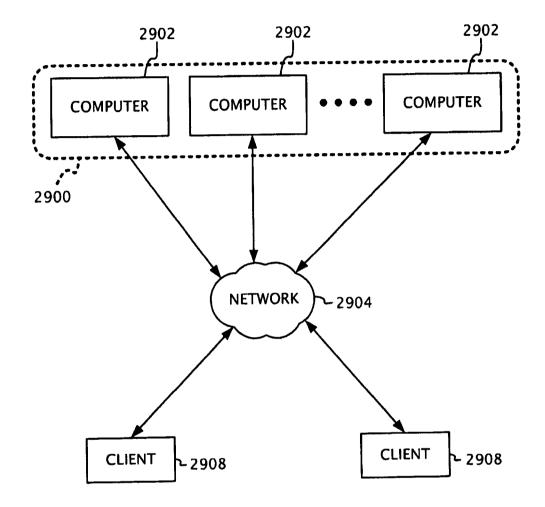

- FIG. 28 is a schematic block diagram of a network as may be used to perform any of the disclosed methods or to generate any of the disclosed compactor embodiments.

- FIG. 29 is a schematic block diagram of a distributed computing network as may be used to perform any of the disclosed methods or to generate any of the disclosed compactor embodiments.

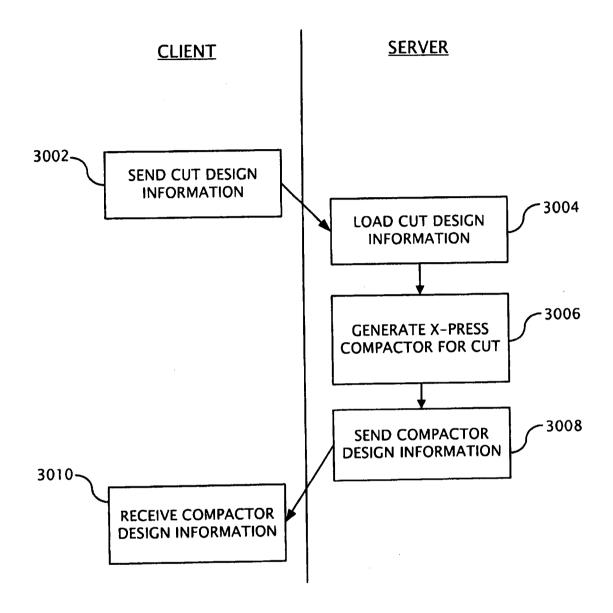

- FIG. 30 is a flowchart illustrating how an embodiment of the disclosed compactor can be generated in the network of FIG. 28 or FIG. 29.

- FIG. 31 shows a block diagram of an additional embodiment of a test response compactor architecture.

- FIG. 32 shows a block diagram of an additional embodiment of a test response compactor architecture.

- FIG. 33 shows a block diagram of an additional embodiment of a test response compactor architecture.

#### **DETAILED DESCRIPTION**

Disclosed below are representative embodiments of electronic circuit testing techniques and associated apparatus that should not be construed as limiting in any way. Instead, the present disclosure is directed toward all novel and nonobvious features and aspects of the various disclosed methods, apparatus, and equivalents

thereof, alone and in various combinations and subcombinations with one another. The disclosed technology is not limited to any specific aspect or feature, or combination thereof, nor do the disclosed methods and apparatus require that any one or more specific advantages be present or problems be solved.

5

10

15

20

25

30

As used in this application and in the claims, the singular forms "a," "an" and "the" include the plural forms unless the context clearly dictates otherwise.

Additionally, the term "includes" means "comprises." Moreover, unless the context dictates otherwise, the term "coupled" means electrically or electromagnetically connected or linked and includes both direct connections or direct links and indirect connections or indirect links through one or more intermediate elements not affecting the intended operation of the circuit.

Although the operations of some of the disclosed methods and apparatus are described in a particular, sequential order for convenient presentation, it should be understood that this manner of description encompasses rearrangement, unless a particular ordering is required by specific language set forth below. For example, operations described sequentially may in some cases be rearranged or performed concurrently. Moreover, for the sake of simplicity, the attached figures may not show the various ways in which the disclosed methods and apparatus can be used in conjunction with other methods and apparatus. Additionally, the description sometimes uses terms like "determine" and "select" to describe the disclosed methods. These terms are high-level abstractions of the actual operations that are performed. The actual operations that correspond to these terms will vary depending on the particular implementation and are readily discernible by one of ordinary skill in the art.

The disclosed embodiments can be implemented in, for example, a wide variety of integrated circuits that utilize scan-based or partially scan-based testing (for example, application-specific integrated circuits (ASICs) (including mixed-signals ASICs), systems-on-a-chip (SoCs), or programmable logic devices (PLDs) such as field programmable gate arrays (FPGAs)). Such integrated circuits can be used in a vast assortment of electronic devices, ranging from portable electronics (such as cell phones, media players, and the like) to larger-scale items (such as

computers, control systems, airplanes, automobiles, and the like). All such items comprising integrated circuits with embodiments of the disclosed technology or equivalents are considered to be within the scope of this disclosure.

5

10

15

20

25

30

Any of the apparatus described herein can be designed, verified, and/or simulated using software that comprises computer-executable instructions stored on one or more computer-readable media. Such software can comprise, for example, an electronic design automation (EDA) software tool, such as a design, verification, or simulation tool. Similarly, any of the methods described herein can be performed or simulated (at least in part) using software comprising computer-executable instructions stored on one or more computer-readable media. Furthermore, any intermediate or final results of the disclosed methods can be stored on one or more computer-readable media. For example, a software tool can be used to determine and store one or more control signals (for example, mask bits) used to control any of the disclosed apparatus. Any such software can be executed on a single computer or on a networked computer (for example, via the Internet, a wide-area network, a local-area network, a client-server network, or other such network). For clarity, only certain selected aspects of the software-based implementations are described. Other details that are well known in the art are omitted. For the same reason, computer hardware is not described in further detail. It should be understood that the disclosed technology is not limited to any specific computer language, program, or computer. For instance, a wide variety of commercially available computer languages, programs, and computers can be used.

Further, any of the disclosed apparatus can be stored as circuit design information on one or more computer-readable media. For example, one or more data structures containing design information (for example, a netlist, HDL file, or GDSII file) can be created (or updated) and stored to include design information for any of the disclosed apparatus. Such data structures can be created (or updated) and stored at a local computer or over a network (for example, by a server computer). Similarly, compressed test responses produced by any of the disclosed apparatus or control signals used to operate any of the disclosed apparatus (for example, mask bits) can be stored on one or more computer-readable media (for example, in one or

more data structures). Such computer-readable media are considered to be within the scope of the disclosed technologies.

Moreover, any of the disclosed methods can be used in a computer simulation, ATPG, or other EDA environment, wherein test patterns, test responses, and compressed test responses are determined by or otherwise analyzed using representations of circuits, which are stored on one or more computer-readable media. For presentation purposes, however, the present disclosure sometimes refers to a circuit or its circuit components by their physical counterpart (for example, scan cells, spatial compactors, registers, selection logic, logic gates, and other such terms). It should be understood, however, that any reference in the disclosure or the claims to a physical component includes representations of such circuit components as are used in simulation, ATPG, or other such EDA environments.

### Introduction and Overview of Disclosed Technologies

5

10

15

20

25

30

Test response compaction, in conjunction with stimuli compression, can play an important role in handling the growth of test data volume. Although the development of various compaction schemes reflects the needs of various application domains, a test response compactor desirably preserves the observability of any scan cell for a wide range of unknown-state profiles, while maintaining high compaction ratios, providing the ability to detect a variety of failures found in real silicon, and/or achieving design simplicity. It can also be desirable to control compactor operations with a minimal amount of additional information, so that this data will have little or no negative impact on the effective test data volume compression.

In some cases, unknown states (also referred to herein as "X states") can render tests useless when employing test response compaction. In many scan-based designs, X states, once captured in scan cells, are subsequently injected into a compactor. Hence, they can affect a resultant signature, especially if a time compactor is used, where X states can quickly multiply (due to a feedback fan-out) and stay in the compactor until a read out operation. Multiplication of unknown

states can be prevented in some compactor architectures, such as modular time compactors which use simple binomials in the feedback. In some cases, such an arrangement can significantly reduce the negative impact of X states.

Combinational compactors can flush out X states, but in order to avoid masking inputs from the scan chains and to allow diagnosis, such compactors typically have to observe each scan chain on two or more outputs. Finite memory compactors can flush out X states in a number of scan shift cycles. However, even if a test response compactor is designed to tolerate a pre-specified amount of X states, its ability to handle a wide range of X state profiles typically requires a scan chain selection (masking) mechanism. *See, e.g.*, U.S. Pat. Nos. 6,557,129 and 6,829,740, which are incorporated herein by reference. Otherwise, certain combinations of X states that cannot be eliminated by automatic test pattern generation (ATPG) can prevent observability of some scan cells and cause a significant fault coverage drop.

#### 15 Exemplary Test Circuit Compactor Architectures

5

10

20

25

30

Fig. 1 shows an exemplary embodiment 100 of a compactor architecture (an X-Press compactor architecture) comprising a first test response compactor 110 and a second test response compactor 152 in an embedded deterministic test environment having *n* scan chains 120. Compressed test stimuli can be provided to the scan chains 120 via a decompressor 130 through one or more input channels (or input paths) 132, 134. In some embodiments, these channels can also be used in conjunction with input channels 136, 138 to deliver mask bits (masking instructions) to a selector circuit 140 via components 160, 162. In particular embodiments, the components 160, 162 are pipeline registers, while in other embodiments they are demultiplexers. In further embodiments, there is not necessarily a data dependency between the compressed test stimuli and the mask bits, as is discussed more fully below. The compactor 110 can be a space compactor (or spatial compactor) comprising an XOR or XNOR tree and can be coupled to the scan chains 120 via the selector circuit 140. An output 112 of the first compactor 110 can be coupled to a *v*-bit overdrive register 150. In some embodiments the overdrive register 150 can be

implemented as a sequentially loading register, for example, a shift register. The overdrive register 150 can comprise one or more sequential elements, such as flip-flops or latches, coupled in series. The overdrive register 150 can be configured to receive compressed test responses from the first compactor 110 and provide them to the second compactor 152. The second compactor 152 can be a space compactor (or spatial compactor) comprising an XOR or XNOR tree. In particular embodiments, the first compactor 110 and/or the second compactor 152 comprise feedback free compactors. In further embodiments, the first compactor 110 and/or the second compactor 152 comprise pipelined spatial compactors.

5

10

15

20

25

30

Fig. 2 shows a block diagram of one exemplary embodiment of a method 200 for compressing test responses using a test response compactor architecture such as the embodiment 100 of Fig. 1. In method act 210, test response bits from the scan chains 120 are compressed by the compactor 110. In method act 220 the compressed test response bits are loaded into the v-bit overdrive register 150. In exemplary embodiments, the compressed test response bits are serially loaded into the register. This loading can occur, for example, over a period of two or more clock cycles. In method act 230, the compressed test response bits are further compressed by the second compactor 152. In exemplary embodiments, the contents of the overdrive register are unloaded in parallel (possibly over a period of one clock cycle) into the second compactor 152 and compressed every  $\nu$  scan shift cycles. The unloading of the overdrive register 150 and compression in the second compactor 152 can occur during the same clock cycle as the last shift cycle from the v scan shift. In certain embodiments, the compressed test response bits are unloaded and compressed into the second compactor 152 during every clock cycle, but are only recorded every  $\nu$  scan shift cycles.

The compression ratio of scan chain inputs to compactor outputs that can potentially be achieved using a two-stage compaction scheme, such as that described in Fig. 2, can go beyond a limit determined approximately by the ratio between the number of scan chains n and the number of compactor outputs w. In some embodiments, for instance, the compression ratio can be increased by about a factor of v (for example, the ratio can be approximately  $n \times v : w$ ).

For example, one embodiment of a test response compactor architecture according to the architecture of Fig. 1 comprises two tester input channels (for example, channels 132, 134), one compactor output channel (w = 1), one hundred internal scan chains (n = 100), and an overdrive register ten bits (v = 10). With conventional technologies the ratio of scan chains to tester input channels sets the maximum compression level (for example, 50x). Using the disclosed technologies, however, the test data compression ratio is approximately  $100 \times 10 / 1 = 1000x$ .

5

10

15

20

25

30

Returning to Fig. 1, the selector circuit 140 can comprise a first group of logic gates 142 and second group of logic gates 144. One or more groups of such logic gates are sometimes referred to herein as "masking logic." In the depicted embodiment, these gates are shown as being AND gates, but in further embodiments other logic gates (including multiple types of logic gates) can be used. The selector circuit 140 can further comprise a selection logic circuit 146 configured to apply signals to at least some of the first and second groups of logic gates 142, 144. In some embodiments the selector circuit 140 can act in response to mask bits received (for example, through the input paths 136, 138). In further embodiments, at least some of the mask bits are provided to the selection logic 146 via a mask register 148. Design and implementation of the selection logic circuit 146 is described in more detail below.

In some embodiments, the selector circuit 140 can block or "mask" one or more selected inputs to the first compactor 110 and/or the second compactor 152. The selected inputs can carry, for example, unknown states and/or unwanted responses from the scan chains 120 and/or the overdrive register 150. Inputs to the groups of logic gates 142, 144 can be provided such that the unknown states and/or unwanted responses do not reach the compactors 110, 152, and are instead replaced by known values (for example, a "0" or "1").

In some embodiments, the following signals can be provided to one or more gates in the groups of logic gates 142, 144. To block a selected scan chain output or a selected overdrive register output (for example, to suppress an X state), a "0" value can be provided to one or more of the gates. A "1" value can be provided to one or more of the gates to cause the selector circuit 140 to pass values (for example,

values indicative of a targeted or untargeted fault) to a compactor. For scan chain outputs or overdrive outputs whose content is not considered critical (for example, are not associated with a scan cell whose value is indicative of a targeted or untargeted fault), a "don't care" value of either "0" or "1" can be assigned to logic gates for those outputs. These values can vary depending on the implementation.

5

10

15

20

25

30

In this application and in the claims, "first compactor stage" generally refers to the first compactor 110 and the group of logic gates 142, while "second compactor stage" generally refers to the second compactor 152, the group of logic gates 144 and the overdrive register 150.

Fig. 3 is a schematic block diagram illustrating one example of how the selector circuit 140 can be used to handle X states that can appear in the scan chains 120. In the depiction of Fig. 3, the overdrive register 150 is a 4-bit shift register. Accordingly, in the left half of Fig. 3 the data cycles in the scan chains 120 are shown as being grouped into blocks of four cycles, as indicated by the capital letters "A," "B" and "C." Individual cycles in each block are respectively labeled with lower-case letters "a," "b," "c" and "d." In the right half of Fig. 3, compressed test response bits 302 of block A are shown loaded into the overdrive register 150. (Although the left and right halves of Fig. 3 show events that do not happen simultaneously, they are shown in one figure for ease of reference.) Block A in the right half of Fig. 3 comprises bits that are the result of compressing uncompressed test response bits from multiple scan chains. For example, a compressed test response bits 108 is the XORed value of uncompressed test response bits 1 to n from the d cycle of the A block. Compressed test response bits 304, 306 of blocks B and C, respectively, can be loaded in succession into the overdrive register 150.

As shown on the left-hand side of Fig. 3, scan chain cycle 310 (i.e., cycle b of block B) contains an X state in cell 312 of scan chain 2. This X state can hide errors captured in the same scan-out cycle (i.e., in cycle b of block B in the other scan chains). Subsequently, this X state can invalidate test results in the block B as a whole (for example, after block B is compressed by the compactor 152). This is because, in the depicted embodiment and in the absence of any masking, the compressed content of the cells comprising block B are loaded into the overdrive

register 150 in such a way that data for cycles a, b, c and d of a block are processed simultaneously by the second compactor 152. In some embodiments, the X state can be masked by the one of the logic gates 142 such that the X state is not passed to the first compactor 110. In some embodiments, mask signals are provided to the logic gates on a per-pattern basis, though in other embodiments masking signals are applied in other intervals (for example, on a multiple-pattern basis, a cycle-by-cycle basis, or a multiple-cycle basis). Accordingly, using the logic gates 142 to mask one cell in the scan chains 120 results in masking values for the entire scan chain, which can prevent test response bits indicative of targeted faults (error values) from being observed from the masked scan chain. An alternative approach is to allow the cycle 310 to be compressed by the first compactor 110. The second-stage logic gates 144 can then be used to mask the compressed b cycle containing the unknown state. If mask signals are provided to the second-stage logic gates 144 on a per-pattern basis, masking at this stage can potentially eliminate not only errors occurring in every  $\nu$ -th cell in the scan chain, but also unknown states captured in those cells.

5

10

15

20

25

30

Additional embodiments of test circuit compactor architectures appear in Figs. 4-7. Fig. 4 shows one embodiment of a test response compactor architecture 400 where the scan chains 410 are partitioned into groups 412 and 414. Data from each scan chain group is compressed by a separate compactor 420, 422 and fed into respective separate overdrive registers 430, 432. Values in the overdrive registers 430, 432 can be compressed by another compactor 440. Inputs to the compactors 420, 422, 440 can be masked using one or more selector circuits 450, as is similarly described above. In the embodiment of Fig. 4, a bit in one overdrive register can be masked while bits in the other overdrive register remain unmasked. Thus, the impact of an X state in one of the scan chain groups 412, 414 on results obtained from the other scan chain group can be reduced. Although only two first-stage compactors and overdrive registers are shown in Fig. 4, it is to be understood that multiple additional compactors and registers could be used in the illustrated architecture.

Fig. 5 shows another embodiment of a test response compactor architecture 500 configured to provide multiple outputs. Similar to the test circuit compactor

architecture 400 of Fig. 4, architecture 500 comprises scan chains 510 partitioned into groups 512, 514, the groups providing test response data that is compressed by compactors 520, 522. These compactors 520, 522 feed data into respective overdrive registers 530, 532. In the architecture 500, the overdrive registers 530, 532 feed compacted responses into separate respective compactors 540, 542 instead of the same compactor. This can isolate a first scan chain group from the effects of an X state in a second scan chain group with or without masking one or more inputs to the compactors 520, 540, 542. In embodiments where masking can be used, the architecture can further comprise one or more selector circuits 550. Although only two first-stage compactors, overdrive registers, and second-stage compactors are shown in Fig. 5, it is to be understood that multiple additional compactors and registers could be used in the illustrated architecture.

5

10

15

20

25

30

Fig. 6 depicts an additional embodiment of a test response compactor architecture 600 configured to provide multiple outputs. In this embodiment, compactors 610, 612 compress outputs from multiple respective scan chain groups (not shown) and provide the compressed outputs to respective overdrive registers 620, 622. The overdrive registers 620, 622 provide inputs to two compactors 630, 632. In this embodiment, non-consecutive bits from the overdrive registers can be provided to the compactors 630, 632 to reduce the impact of burst errors. For example, an output 640 from the overdrive register 620 can be routed to an input 642 on the compactor 632, rather than to an input on the compactor 630. Other routing configurations can also be used. The test circuit compactor architecture can further comprise one or more selector circuits 650. Although only two first-stage compactors, overdrive registers, and second-stage compactors are shown in Fig. 6, it is to be understood that multiple additional compactors and registers could be used in the illustrated architecture.

An additional embodiment of a test response compactor architecture 700 appears in Fig. 7. The depicted embodiment is configured to reduce the effect of burst errors while providing a single output. Compressed outputs from a compactor 710 are provided to a first overdrive register 720 and to a multiplexer (MUX) 730. The overdrive register 720 also feeds into the MUX 730, which is in turn coupled to

a second overdrive register 722. The overdrive registers 720, 722 are clocked by a clock signal 732, and a divided version of the clock signal (produced by clock divider 733) is provided to the MUX 730. This arrangement can allow the overdrive register 722 to provide a non-consecutive group of outputs to a compactor 740. The architecture 700 can further comprise one or more selector circuits 750. Although only one first-stage compactors, two overdrive registers, and one second-stage compactors are shown in Fig. 7, it is to be understood that multiple additional compactors and registers could be used in the illustrated architecture.

5

10

15

20

25

30

Fig. 8 shows a block diagram of another embodiment of a test response compactor architecture 800. In this embodiment, one or more overdrive registers 802, 804 are placed in the first stage of the compactor architecture 800. More particularly, the overdrive registers 802, 804 receive inputs from one or more scan chains. For example, overdrive register 802 receives inputs from scan chain 812. Although Fig. 8 shows only two overdrive registers, it is to be understood that, in this embodiment, one overdrive register is coupled to each of the scan chains 810. In other embodiments, other numbers of registers are coupled to the scan chains. The overdrive registers 802, 804 are configured to load inputs from their respective scan chains into a first stage of compactors. For example, overdrive registers 802, 804 load values received from scan chains 812, 814 into first-stage compactors 822, 824, respectively. Generally, values are loaded in parallel from the overdrive registers 802, 804 into the first-stage compactors 822, 824. Outputs from the firststage compactors 822, 824 can be subsequently compacted by a second-stage compactor 830. The compactor architecture 800 can further comprise a selector circuit 840 for masking one or more inputs to the compactors 822, 824, 830. The selector circuit 840 can be similar to the selector circuits of other compactor architectures described above. Although only two first-stage compactors and overdrive registers are shown in Fig.8, it is to be understood that multiple additional compactors and registers could be used in the illustrated architecture.

Fig. 9 shows a block diagram of a further embodiment of a test response compactor architecture 900. In this embodiment, instead of providing inputs to a first stage compactor 902 from an overdrive register, inputs can be loaded in parallel

directly from v scan cells in a scan chain (usually, the last v cells of the chain) every v clock cycles. For example, in Fig. 9, scan chain 912 provides inputs to a compactor 902 from v scan cells 922 at the end of the chain 912. (In Fig. 9, in order to aid clarity, the individual cells are not shown.)

5

10

15

20

25

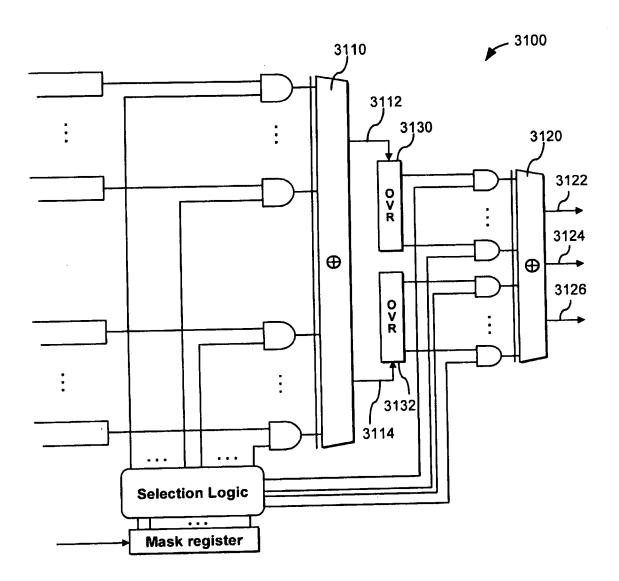

Fig. 31 shows a block diagram of a further embodiment of a test response compactor architecture 3100 comprised of a compactor 3110 in a first-stage and a compactor 3120 in a second stage. The compactor 3110 comprises multiple outputs 3112, 3114 coupled to respective overdrive registers 3130, 3132. The compactor 3120 comprises multiple outputs 3122, 3124, 3126. Generally, test compactor architectures described herein can be adapted to embodiments comprising one or more compactors with multiple outputs.

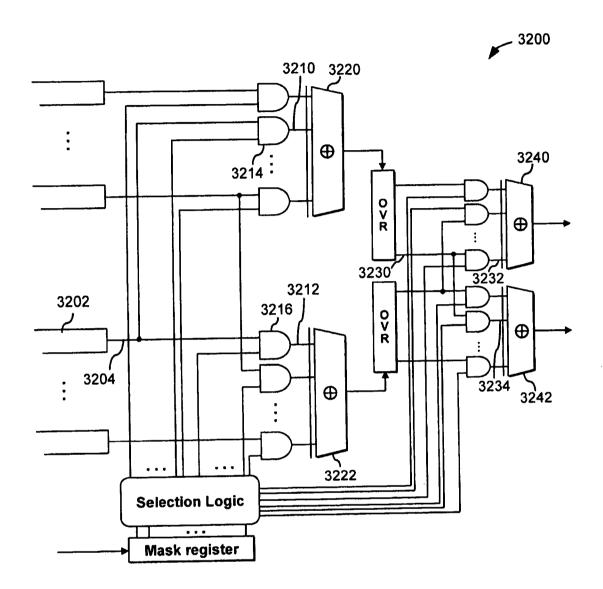

Fig. 32 shows a block diagram of another embodiment of a test response compactor architecture 3200 where one or more scan chain outputs and/or overdrive register outputs can each drive multiple compactor inputs (for example, the outputs can have fan-out). For example, in the depicted embodiment a scan chain 3202 has a scan chain output 3204 that is coupled to compactor inputs 3210, 3212 through respective masking gates 3214, 3216. Thus the scan chain output 3204 can drive two compactors 3220, 3222. An overdrive register output 3230 similarly drives inputs 3232, 3234 of two second-stage compactors 3240, 3242, respectively.

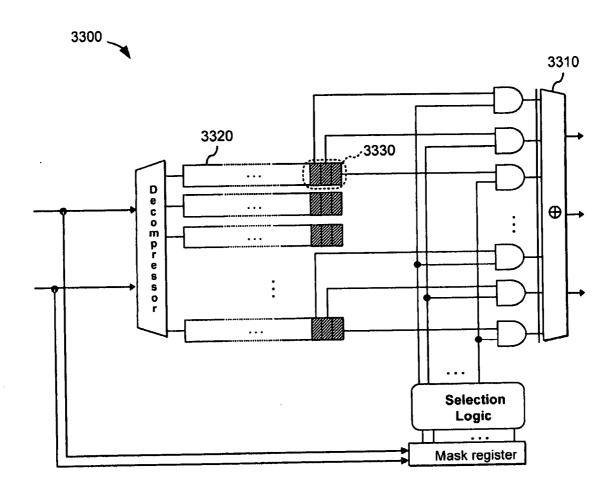

Fig. 33 shows a block diagram of an additional embodiment of a test response compactor architecture 3300. This embodiment is similar to the architecture 900 of Fig. 9 in that inputs to a compactor 3310 can be loaded in parallel from  $\nu$  cells in a scan chain. For example, a scan chain 3320 provides inputs to the compactor 3310 from the scan cells 3330 of the scan chain 3320. In the depicted embodiment, the compactor 3310 comprises multiple outputs, and the architecture 3300 is a single-stage compactor architecture. In further embodiments, compactor inputs can be loaded from one or more overdrive registers instead of directly from the scan chains themselves, similar to the architecture 800 of Fig. 8.

## Masking Signal Selection Methods

5

10

15

20

25

30

The selection of masking signals for selector circuits (for example, in selector circuit 140 of Fig. 1, the mask signals provided by the selection logic 146 to the groups of logic gates 142, 144) can have a significant impact on test quality. Masking signals can be chosen using different methods. In some embodiments, for a given test pattern applied to a circuit design, scan chains are ranked according to one or more factors (for example, potential coverage gains or losses in detecting possible faults that can result from masking or not masking the chain). For purposes of this discussion, a single scan cell is chosen as a primary fault propagation site. This approach allows faults to be handled in a uniform manner. Otherwise, faults with a small number of propagation sites might be difficult to detect due to a dominant position of faults with a large number of observation points.

Fig. 10 shows a block diagram of one embodiment of a general method 1000 for determining masking signals for use with a selector circuit, such as selector circuit 140. The disclosed embodiment can be performed, for example, for each test pattern of a test set to be applied during testing and can use simulation results (for example, from a simulation of the test pattern being applied to the circuit-under-test) to determine the respective weights to be assigned. The method 1000 can also be used with a variety of compactor architectures (for example, XOR, X-compact, Icompact, and others). In method act 1010, weights are assigned to a plurality of individual scan cells in one or more scan chains. For example, assuming that a given cell is observed, the cell's weight can indicate the cell's contribution to the total error coverage. In some embodiments, weights can be assigned as follows: scan cells that capture unknown states can be assigned a weight of "0"; scan cells that capture don't care states can be assigned a value of "1"; and scan cells which are likely to be affected by faults (termed herein "primary" cells) can be assigned a weight "C." By assigning a weight of 1 to cells capturing don't care states, those cells can be included in analyses that lead to masking decisions. Since faults often propagate to more than one scan cell, it can be beneficial to have such cells observed (for example, if the primary cell is masked). To retain priority among scan cells, however, the weight C associated with primary cells is desirably large enough so

that the combined effect of having many or all cells with don't care values observed does not significantly reduce the visibility of one or more primary cells.

Fig. 11 shows one embodiment of a representation 1100 of five scan chains 1102, 1104, 1106, 1108, 1110 each comprised of 24 scan cells. The scan cells have been assigned a weight of 0, 1, or 30 (the value of C in this embodiment) according to method act 1010. For example, a scan cell 1120 has been assigned a weight of 1, indicating that it captured a don't care value, whereas scan cell 1122 has been assigned a weight of 30, indicating that it captured a value indicative of the presence of a fault.

5

10

15

20

25

30

Returning to Fig. 10, in method act 1020, the weights for a plurality of the scan cells within one or more of the scan chains are aggregated. The weights are desirably aggregated according to how the scan cells will be compacted during the next compaction stage. For example, in certain exemplary embodiments, the scan chain representation 1100 is mapped to a representation referred to herein as a "compound chain." A compound chain can be created from the weights assigned to a scan chain by representing several scan cells from a chain in a single compound cell. In some embodiments  $\nu$  consecutive scan cells in a chain can be represented by one compound cell. A weight can be assigned to a compound cell based at least in part on values in one or more original scan cells that the compound cell represents. In some embodiments, a compound cell weight is the sum of the weights of the

original cells. Additionally, a compound cell can be assigned a weight of "0" if one of the original cells to be included as part of the compound cell has a weight of "0" (for example, if one of the original cells captures an X state). In particular embodiments, this can anticipate, to some extent, possible results of compaction of data provided by an overdrive register. As explained above, an X state that is not suppressed before a first compaction stage can potentially render lots of error data useless, either due to X-masking or due to the second stage gating. In some embodiments, blocking certain X states earlier in a compaction process can help prevent a significant coverage drop.

Fig. 11 shows exemplary embodiments of the scan chains 1102, 1104, 1106, 1108, 1110 mapped into compound chains 1132, 1134, 1136, 1138, 1140,

respectively. For ease of reference, in Fig. 11 the scan chains 1102, 1104, 1106, 1108, 1110 are shown divided into 4-cell groups T, U, W, X, Y and Z. The columns of the compound chains (sometimes referred to herein as "time frames") are labeled to indicate which 4-cell group a compound cell represents. For example, the compound cell in the T column of compound chain 1136 has a weight of 33, which is the sum of the scan cells in group T of scan chain 1106. The compound cell in column T of compound chain 1132 has a value of 0, since one cell in group T of scan chain 1106 has a weight of 0.

5

10

15

20

25

In certain embodiments, mask selection can be based on the weights of the original scan chains instead of the weights of the compound scan chains. This can be used if, for example, no cell or few cells in the compound chains have a weight at least equal to C.

In method act 1030 of method 1000, coefficients (sometimes referred to herein as "scores") can be determined based, for example, on the aggregated weights in one or more compound scan chains. In some embodiments, coefficients  $S_i$  and  $M_i$  are computed for the compound scan chains. In such exemplary embodiments,  $S_i$  is proportional to the estimated number of errors that will be preserved provided scan chain i is selected, and coefficient  $M_i$  is proportional to the estimated number of errors that will be preserved if the scan chain i is masked.

Let X(i) be the set of zero-weight cells hosted by the compound scan chain i. Furthermore, for a given c-th cell of all compound scan chains, let  $E_c$  and  $X_c$  represent the sum of weights over these cells and the number of cells that have weight zero, respectively. Coefficient  $S_i$  can then be given by exemplary equation 1:

$$S_{i} = \sum_{c} w_{i,c} 2^{-X_{c}} - \sum_{c \in X(i)} E_{c} / X_{c}$$

(1)

where  $w_{i,c}$  is the weight of cell c in the compound scan chain i.  $S_i$  in equation 1 is equal to the total weight over all cells occurring in a given compound scan chain and scaled by the probability that X states occurring in the corresponding time frames will be masked (it is assumed that a single scan chain is masked with probability 0.5).  $S_i$  is affected in equation 1 by the weights  $E_c$  associated with the same time frames as those of X states hosted by a given scan chain.  $E_c$  is scaled by the number

of corresponding X states, in order to avoid double counting. As can be seen, the second component can account for errors which can be X-masked if the scan chain itself is not masked.

As an example, the above quantities for the compound scan chains shown in Fig. 11 can be determined where i = 1 (i.e., compound scan chain 1134). In this example, C = 30 and  $X(1) = \{0, 3\}$  (i.e., cells 0 and 3 of compound scan chain 1 have weights of 0). Also,  $E_0 = 37$ ,  $E_3 = 70$ ,  $X_0 = 3$ ,  $X_3 = 2$ . Hence,  $S_1$  is computed as:

$$S_1 = 62 \times 0.5 + 33 \times 0.5 + 4 \times 0.5 + 4 \times 0.25 - 37/3 - 70/2 = 3.2$$

(2)

In some embodiments, the quantity  $M_i$  can be determined as:

5

10

15

20

25

$$M_{I} = \sum_{c \in X(I)} E_{c} 2^{-(X_{c}-1)} - \sum_{c} w_{I,c} (X_{c}+1)^{-1}$$

(3)

In this exemplary equation, the first term is equal to the sum over weights  $E_c$  corresponding to the same time frames as those of X states (now masked) hosted by a given scan chain, assuming that they are not masked by other unknown states from the same shift cycles. The second term reduces the first by weights of cells occurring in the masked scan chain, calibrated by X's from other scan chains, and including the masked chain itself. In various embodiments, either  $S_i$  or  $M_i$  can be negative, thus indicating a possible coverage drop when either selecting or gating a given scan chain.

Returning to Fig. 10, in method act 1040, a decision whether to mask a given chain can be made based at least in part on the coefficients (for example, the values of  $S_i$  and/or  $M_i$  for the chain).

Fig. 12 shows one embodiment of a method 1200 for selecting scan chains to mask, given a test pattern, one or more detected faults, and corresponding locations of failing scan cells and unknown states. Method 1200 can be integrated with the general method 1000 introduced above.

In method act 1210, coefficients (for example,  $S_i$  and/or  $M_i$ ) for one or more scan chains are determined. In method act 1220, coefficients for two or more scan chains are compared. In method act 1230, one or more chains can be chosen for selection or masking based at least in part on the coefficients. For example, in some embodiments a scan chain having a large or the largest value of  $S_i$  can be assigned a

masking bit value of 1, indicating that values from that chain should be passed to a compactor. A scan chain having a large or the largest value of  $M_i$  can be assigned a masking bit value of 0, indicating that values from the scan chain should be masked.

In method act 1240, a representation of the contents of the scan chains can be updated based on decisions (which can be preliminary) in method act 1230. For example, in the representation (such as representation 1100), errors and/or X states can be deleted from scan chains that have been assigned a masking value of 0. One or more of the foregoing method acts can be repeated, as indicated by arrow 1242, such that masking bit values can be iteratively assigned to one or more other scan chains.

5

10

15

20

25

30

In method act 1250, the mask bit assignments are encoded. For example, in certain embodiments, this procedure involves assigning the masking signals to the scan chains of the circuit-under-test and determining the necessary mask bits to be input into the selection circuit to achieve the desired masking. In particular embodiments, the masking signals are assigned according to values of  $S_i$  or  $M_i$  and are considered sequentially in the order in which the scan chains were considered in the above method acts. In certain embodiments, this confirmation procedure involves solving linear equations to determine whether and how the desired masking signals are to be generated in the selection circuit. In the illustrated embodiment, the process proceeds until the first encoding error occurs (for example, the first scan chain is considered that cannot have the masking signals preliminarily assigned to it). Furthermore, in one particular embodiment, regardless of the order determined by coefficients  $S_i$  and  $M_i$ , the encoding process starts with a scan chain whose mask signal is 1. This modification can be implemented to prevent all masking bits from being set to 0 by encoding, at the very beginning of the procedure, masking signals for a large group of scan chains that should be masked. Such an approach would potentially make all scan chains unobservable.

In method act 1260, the remaining unencoded masking signals that were not the subject of encoding are evaluated and encoded, if possible, in view of the selector architecture.

In additional embodiments, the selection method described above can be

applied to the second stage of compaction as well. In such embodiments, masking signals can be determined with respect to values in compressed cycles, such as the compressed cycles 302, 304, 306 of Fig. 3. Weights can be assigned to the values in the compressed cycles. A weight can be related to, for example, an error count indicating how many of the scan cells (in unmasked chains) from which the compressed value was produced are fault propagation sites. In some embodiments, if a given scan cell captures an X and the cell's scan chain is not masked, a certain weight (for example, 0) can be assigned to a compressed value produced from the cell.

10

15

20

25

30

5

### **Exemplary Experimental Compaction Results**

An exemplary embodiment of the test circuit compactor architecture illustrated in Fig. 1 was tested on several industrial designs. In the reported experiments the mask register was loaded once per pattern. Such an approach contributed a relatively small amount of data to the total volume of test data and consequently did not compromise the overall compression ratio. Generally, the presence of X states and the use of selection logic can cause several test escapes when applying original test patterns. Therefore, top-up patterns were used to restore the complete fault coverage. The corresponding increase in pattern count and the effective compression can be used as basic figures of merit to assess the performance of the compaction scheme.

Fig. 13 shows a block diagram of a method 1300 for using test patterns with a selective compactor (for example, the compactor architecture 100 of Fig. 1). The method 1300 was used for obtaining experimental results described below. Starting with an original fault list, in method act 1310 a test pattern was generated, and in method act 1320 fault propagation sites and X state locations were determined for one or more scan chains in the test circuit architecture. For example, the application of the test pattern to the circuit-under-test and the circuit-under-test's response to the test pattern (the test response) can be simulated. In method act 1330 values for masking or selecting scan chains and/or overdrive register values were determined (using method 1200 described above). In method act 1340, fault coverage was

examined in view of the determined masking values. In method act 1350, detected faults were removed from the original fault list. In method act 1360, the number of test patterns used to arrive at a given level of fault coverage was recorded, and in method act 1370 the mask bits for controlling the compactor were also stored. The method 1300 was repeated until the faults on the original fault list were detected, as indicated by arrow 1372.

5

10

15

20

25

30

The results of the experiments are summarized in Table 1 (appearing in Fig. 14) and in Table 2 (appearing in Fig. 15). For each circuit the following information is provided: name, scan architecture, and the total number of faults; the total number of error bits (the number of scan cells that capture erroneous signals); the number of test patterns which contribute to the fault coverage ("FC") assuming that there is no compaction; the sequential depth of deployed test patterns; the X-fill rate computed as a ratio of the total number of captured X states to the number of scan cells multiplied by the number of test patterns; the size m of the mask register; the size v of the overdrive register; the total number of patterns and the corresponding increase in pattern count represented as absolute values (in the columns labeled "IPC"), and as a percentage of the original number of tests (in the columns labeled "%"); and the effective compaction ratio C. In Tables 1 and 2, C = AsL / T (L/v + c), where A is the number of original patterns, T is the total number of test patterns, T is the number of scan chains, T is the amount of X-Press compactor control data (for example, the number of mask bits).