(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4916658号

(P4916658)

(45) 発行日 平成24年4月18日(2012.4.18)

(24) 登録日 平成24年2月3日(2012.2.3)

|                       |            |         |  |

|-----------------------|------------|---------|--|

| (51) Int.Cl.          | F 1        |         |  |

| GO6K 19/07 (2006.01)  | GO6K 19/00 | H       |  |

| HO1L 27/04 (2006.01)  | HO1L 27/04 | U       |  |

| HO1L 21/822 (2006.01) | HO1L 29/78 | 6 1 3 Z |  |

| HO1L 29/786 (2006.01) | GO6K 19/00 | K       |  |

| GO6K 19/077 (2006.01) | HO1Q 1/24  | C       |  |

請求項の数 6 (全 30 頁) 最終頁に続く

|              |                               |                 |           |

|--------------|-------------------------------|-----------------|-----------|

| (21) 出願番号    | 特願2004-363424 (P2004-363424)  | (73) 特許権者       | 000153878 |

| (22) 出願日     | 平成16年12月15日 (2004.12.15)      | 株式会社半導体エネルギー研究所 |           |

| (65) 公開番号    | 特開2005-202943 (P2005-202943A) | 神奈川県厚木市長谷398番地  |           |

| (43) 公開日     | 平成17年7月28日 (2005.7.28)        | (72) 発明者        | 小山 潤      |

| 審査請求日        | 平成19年12月14日 (2007.12.14)      | 神奈川県厚木市長谷398番地  | 株式会社      |

| (31) 優先権主張番号 | 特願2003-423861 (P2003-423861)  | 半導体エネルギー研究所内    |           |

| (32) 優先日     | 平成15年12月19日 (2003.12.19)      | (72) 発明者        | 齋藤 利彦     |

| (33) 優先権主張国  | 日本国 (JP)                      | 神奈川県厚木市長谷398番地  | 株式会社      |

|              |                               | 半導体エネルギー研究所内    |           |

前置審査

審査官 神田 太郎

最終頁に続く

(54) 【発明の名称】半導体装置

(57) 【特許請求の範囲】

## 【請求項 1】

アンテナ回路と、

前記アンテナ回路からの信号が入力される電源回路と、

前記アンテナ回路からの信号を增幅するアンプと、

前記增幅された信号を分周する分周回路と、

前記電源回路からの信号、及び前記分周された信号が入力されるチャージポンプと、

前記チャージポンプからの信号が入力される不揮発性メモリと、を有し、

前記チャージポンプは、前記分周された信号をクロック信号として用いることにより、

前記電源回路からの信号を昇圧して前記不揮発性メモリに供給し、

前記昇圧された信号が供給される表示部を有することを特徴とする半導体装置。

## 【請求項 2】

請求項 1 において、

前記電源回路、前記チャージポンプ、前記アンプ、又は前記分周回路の少なくとも一つは、基板上に設けられた薄膜トランジスタを有することを特徴とする半導体装置。

## 【請求項 3】

請求項 1 又は 2 において、

前記チャージポンプは、

前記電源回路と電気的に接続されたアノードと、前記不揮発性メモリと電気的に接続されたカソードと、を備えたダイオードと、

10

20

前記アノードに電気的に接続された第1の容量と、

前記カソードに電気的に接続された第2の容量と、

前記第2の容量に電気的に接続された入力端子と、前記第1の容量に電気的に接続された出力端子と、を備えたインバータと、を有することを特徴とする半導体装置。

【請求項4】

請求項1又は2において、

前記チャージポンプは、

容量と、

前記電源回路と電気的に接続された第1の電極と、前記容量に電気的に接続された第2の電極と、を備えた第1のトランジスタと、

基準電源に電気的に接続された第3の電極と、前記容量に電気的に接続された第4の電極と、を備えた第2のトランジスタと、

前記容量及び前記第4の電極に接続された第5の電極と、前記第1の電極に電気的に接続された第6の電極と、を備えた第3のトランジスタと、

前記第2の電極及び前記容量に電気的に接続された第7の電極と、前記不揮発性メモリと電気的に接続された第8の電極を有する第4のトランジスタと、を有することを特徴とする半導体装置。

【請求項5】

請求項1乃至4のいずれか一項において、

前記不揮発性メモリは、EEPROMであることを特徴とする半導体装置。

【請求項6】

請求項1乃至5のいずれか一項に記載された半導体装置は、ICカード、IDタグ、無線タグ、またはIDチップであることを特徴とする半導体装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、IDチップとして用いる半導体装置に関する。特に、ガラス、プラスチックなどの絶縁基板上に形成されたIDチップとして用いる半導体装置に関する。

本明細書中において、IDチップとは個体認識に用いる半導体チップのことであり、ICタグ、無線タグ、RFID、ICカードなどに使用されるものとする。

【背景技術】

【0002】

コンピュータ技術の発展や、画像認識技術の向上によって、バーコードなどの媒体を用いた情報認識が広く普及し、商品データの認識などに用いられている。今後はさらに多量の情報認識が実施されると予想される。その一方、バーコードによる情報読み取りなどでは、読み取りのためにはバーコードリーダーがバーコードとの接触を必要とする、またバーコードに記録される情報量があまり多くできないという欠点があり、非接触の情報認識および媒体の記憶容量増大が望まれている。

【0003】

このような要望から、近年ICを用いたIDチップが開発されている。IDチップとはICチップ内のメモリ回路に必要な情報を記憶し、非接触手段、一般的には無線手段を用いて内部の情報を読み取るものである。このようなIDチップの実用化によって、商品流通などの簡素化、低コスト化が可能になるものと期待されている。

【0004】

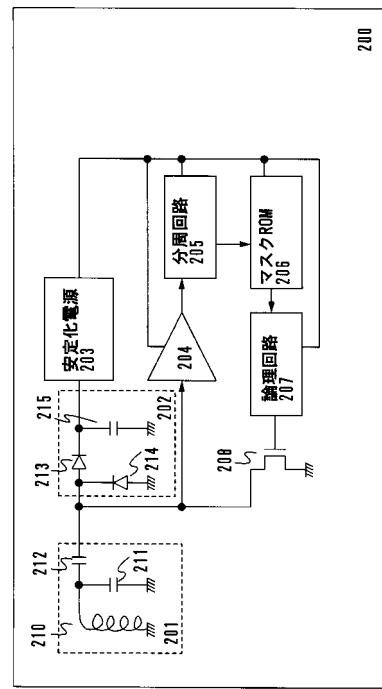

このようなIDチップの技術としては例えば図2に示すようなものがある。ICチップ200はアンテナ回路201、整流回路202、安定化電源203、アンプ204、分周回路205、マスクROM206、論理回路207、スイッチ用トランジスタ208によって構成されている。また、アンテナ回路201はアンテナコイル210、同調容量211、カップリング容量212によって構成される。整流回路202はダイオード213、214、平滑容量215によって構成される。

10

20

30

40

50

## 【0005】

このような I C タグの動作を以下に説明する。アンテナ回路 201 で受信した交流信号はダイオード 213、214 によって半波整流され、平滑容量 215 によって平滑される。この平滑された電圧は多数のリップルを含んでいるため、安定化電源 203 で安定化され、安定化された後の電圧をアンプ 204、分周回路 205、マスク ROM 206、論理回路 207 に供給する。なお、リップルとは、電源電圧の最も高い電圧と、最も低い電圧との差に相当する。一方、アンテナ回路 201 で受信された交流信号はアンプ 204 を通して分周回路 205 に入力され、分周がおこなわれる。アンテナに受信される信号が 13.56MHz の場合 8 分周、16 分周がおこなわれる。そして、分周後の信号を用いて、マスク ROM 206 に記憶されているデータを呼び出す。つぎにマスク ROM 206 のデータを論理回路 207 で加工し、その出力でスイッチトランジスタ 208 を動作させる。 10

## 【0006】

スイッチトランジスタ 208 がオンするとアンテナ回路の出力が GND に接地されるため、アンテナのインピーダンスが変化する。これによって、ID チップのアンテナで反射される質問器の信号に変化が生じる。この変化を質問器が読み取ることによって ID チップのマスク ROM に記憶されたデータを知ることが可能になる。なお、ID チップにアンテナを内蔵しているものを無線チップと呼ぶ。

## 【0007】

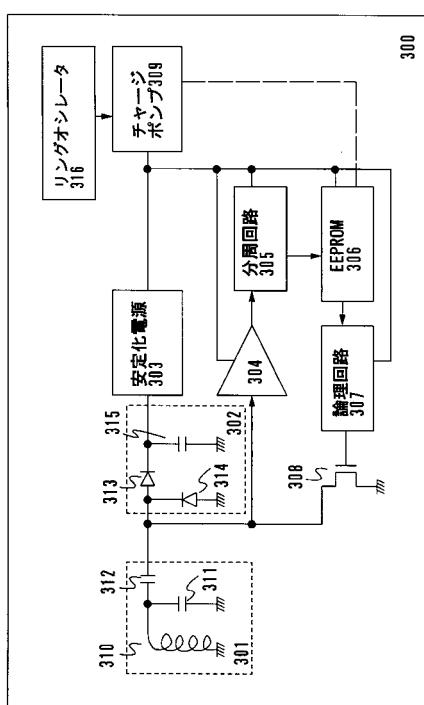

また、上記の例では ROM として、マスク ROM を用いたが書き換え可能な EEPROM のような ROM を載せたものも開発されている。図 3 は EEPROM を登載した ID チップの例である。図 3 に示す ID チップ 300 はアンテナ回路 301、整流回路 302、安定化電源 303、アンプ 304、分周回路 305、EEPROM 306、論理回路 307、スイッチ用トランジスタ 308 によって構成されている。また、アンテナ回路 301 はアンテナコイル 310、同調容量 311、カップリング容量 312 によって構成される。整流回路 302 はダイオード 313、314、平滑容量 315 によって構成される。 20

## 【0008】

このような ID チップ 300 の動作を以下に説明する。アンテナ回路 301 で受信した交流信号はダイオード 313、314 によって半波整流され、平滑容量 315 によって平滑される。この平滑された電圧は多数のリップルを含んでいるため、安定化電源 303 で安定化され、安定化された後の電圧をアンプ 304、分周回路 305、EEPROM 306、論理回路 307 に供給する。一方、アンテナ回路 301 で受信された交流信号はアンプ 304 を通して分周回路 305 に入力され、分周がおこなわれる。アンテナに受信される信号が 13.56MHz の場合 8 分周、16 分周がおこなわれる。そして、分周後の信号を用いて、EEPROM 306 に記憶されているデータを呼び出す。つぎに EEPROM 306 のデータを論理回路 307 で加工し、その出力でスイッチトランジスタ 308 を動作させる。 30

## 【0009】

スイッチトランジスタ 308 がオンするとアンテナ回路 301 の出力が GND に接地されるため、アンテナのインピーダンスが変化する。これによって、ID チップのアンテナで反射される質問器の信号に変化が生じる。この変化を質問器が読み取ることによって ID チップの EEPROM に記憶されたデータを知ることが可能になる。 40

## 【0010】

EEPROM にデータを書き込むときは通常の動作電圧より高い電圧が必要となる。図 3 の例ではリングオシレータ（リング発振器）316 を用いて、交流信号を発生させ、その交流信号を用いて、チャージポンプ 309 を動作させ、安定化電源 303 の出力を昇圧し EEPROM で使用している。

## 【0011】

このような ID チップの例として例えば特許文献 1 などがある。

【特許文献 1】特開 2001-250393 号公報

【発明の開示】

**【発明が解決しようとする課題】****【0012】**

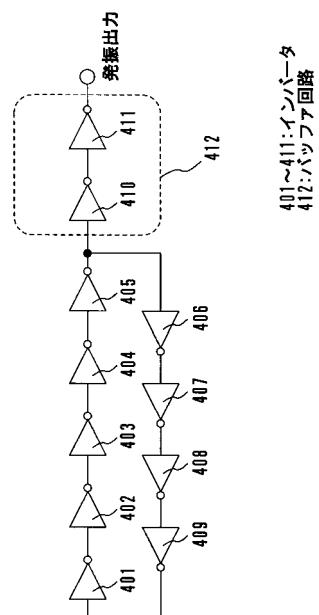

以上に述べたような従来のIDチップ用半導体装置では、以下のような課題があった。リングオシレータは一般に図4に示すように、奇数個のインバータ401～409をリング状に接続し、その出力をインバータ410、411からなるバッファ回路412を介して取り出したものである。

**【0013】**

図3に示したリングオシレータを用いたチャージポンプ回路では、リングオシレータの発振周波数がそれを構成するトランジスタの特性（例えばしきい値電圧など）のばらつきによって変動してしまう。また、周囲温度などでもトランジスタ特性は変動するため、周囲温度の変化によっても発振周波数が変動していた。このように発振周波数が変動することによって、チャージポンプ回路が動作する周期が変わるために、チャージポンプ回路の出力電圧が変動してしまうことがあった。このような変動はEEPROMなどの電源変動となり、それらの安定動作の妨げとなっていた。

**【0014】**

そこで本発明は、IDチップに用いる半導体装置において、EEPROMなどに用いる高電圧の電源を安定化させることを課題とする。

**【課題を解決するための手段】****【0015】**

前述の課題を解決するために、本発明では次のような手段を用いた。

チャージポンプ回路に用いるクロック信号を、リングオシレータから生成するのではなく、アンテナ回路から入力される交流信号を使用して生成する。

**【0016】**

このような構成にすることにより、本発明は、電源回路と、送受信回路と、論理回路と、メモリと、チャージポンプと、アンテナ回路とを有し、前記電源回路および前記送受信回路は、アンテナ回路と電気的に接続され、前記送受信回路は、前記メモリ、前記論理回路と電気的に接続され、前記電源回路は、前記送受信回路と、前記メモリと、前記論理回路と、前記チャージポンプと電気的に接続され、前記アンテナ回路で受信した交流信号は、前記電源回路で整流化された後、前記チャージポンプで昇圧された信号が、前記メモリに入力されることを特徴とする半導体装置である。

**【0017】**

また、電源回路と、送受信回路と、論理回路と、メモリと、チャージポンプと、アンテナ回路とを有し、前記電源回路および前記送受信回路は、アンテナ回路と電気的に接続され、

前記送受信回路は、前記メモリ、前記論理回路と電気的に接続され、前記電源回路は、前記送受信回路と、前記メモリと、前記論理回路と、前記チャージポンプと電気的に接続され、

前記アンテナ回路で受信した後前記電源回路で整流化された第1の信号と、前記アンテナ回路で受信した後前記送受信回路で処理された第2の信号とを用いて、前記チャージポンプで昇圧された第3の信号が、前記メモリに入力されることを特徴とする半導体装置である。

**【0018】**

また、電源回路と、送受信回路と、論理回路と、メモリと、チャージポンプと、表示装置と、アンテナ回路とを有し、前記電源回路および前記送受信回路は、アンテナ回路と電気的に接続され、前記送受信回路は、前記メモリ、前記論理回路と電気的に接続され、前記電源回路は、前記送受信回路と、前記メモリと、前記論理回路と、前記チャージポンプと電気的に接続され、前記アンテナ回路で受信した交流信号は、前記電源回路で整流化された後、前記チャージポンプで昇圧された信号が、前記メモリ及び前記表示装置に入力されることを特徴とする半導体装置である。

**【0019】**

10

20

30

40

50

また、本発明は、電源回路と、送受信回路と、論理回路と、メモリと、チャージポンプと、表示装置と、アンテナ回路とを有し、前記電源回路および前記送受信回路は、アンテナ回路と電気的に接続され、前記送受信回路は、前記メモリ、前記論理回路と電気的に接続され、前記電源回路は、前記送受信回路と、前記メモリと、前記論理回路と、前記チャージポンプと電気的に接続され、前記アンテナ回路で受信した後前記電源回路で整流化された第1の信号と、前記アンテナ回路で受信した後前記送受信回路で処理された第2の信号とを用いて、前記チャージポンプで昇圧された第3の信号が、前記メモリ及び前記表示装置に入力されることを特徴とする半導体装置である。

【0020】

なお、前記表示装置は液晶、発光素子、又は電気泳動素子を用いている。

10

【0021】

また、前記アンテナ回路で受信した交流信号を前記送受信回路で処理した第4の信号が、前記メモリに入力される。

【0022】

また、前記メモリはEEPROMである。

【0023】

また、前記チャージポンプは直列に接続した複数のダイオード、複数の容量手段、インバータから構成され、前記複数のダイオードそれぞれに前記容量手段が電気的に接続され、前記チャージポンプに入力された信号、および前記インバータによって反転された前記信号の反転信号が、前記容量手段の前記ダイオードに接続されていない一端に入力されることによって、昇圧される。

20

【0024】

また、前記チャージポンプは第1乃至第4のトランジスタ、及び容量素子で構成され、入力端子は前記第1のトランジスタおよび前記第3のトランジスタと電気的に接続され、前記第1のトランジスタは前記容量素子および前記第4のトランジスタと電気的に接続され、前記第2のトランジスタは一端が接地され、他端は前記第3のトランジスタおよび前記容量素子と電気的に接続され、前記第4のトランジスタは出力端子に接続され、前記チャージポンプに入力された複数の信号を前記第1乃至第4のトランジスタに入力することにより、前記入力端子に入力された信号は昇圧される。

【0025】

30

また、前記電源回路、前記送受信回路、前記論理回路、前記メモリ、又は前記チャージポンプの少なくとも一つは、薄膜トランジスタで構成されている。

【0026】

また、前記アンテナ回路および前記電源回路と、前記送受信回路と、前記論理回路と、前記メモリと、前記チャージポンプとが、それぞれ同一の絶縁基板上に一体形成されている。

【0027】

また、前記電源回路と、前記送受信回路と、前記論理回路と、前記メモリと、前記チャージポンプとが、それぞれ同一の第1の絶縁基板上に一体形成され、前記アンテナ回路は第2の絶縁基板上に形成されている。

40

【0028】

また、前記絶縁基板はガラス、プラスチック、又はフィルム状の絶縁体である。

【0029】

また、前記アンテナ回路は、前記電源回路、前記送受信回路、前記論理回路、前記メモリ、前記チャージポンプの少なくとも一つと重畳している。

【0030】

また、前記アンテナ回路に入る信号は無線信号である。

【0031】

また、本発明ではこれらの特徴を有する、ICカード、IDタグもしくはIDチップが提供される。

50

## 【0032】

なお、本明細書中で「電源回路」とは交流信号を整流して直流電圧に変換する整流回路、および整流回路から出力される電源の安定化を図る安定化電源回路を指す。また、「送受信回路」とは増幅器や分周回路、アンテナ回路の出力信号を変化させるトランジスタ素子等を指す。また、「表示装置」とは液晶、有機EL、電気泳動素子等を用いた表示部およびその駆動回路を合わせたものを指す。

## 【発明の効果】

## 【0033】

本発明の半導体装置は、チャージポンプ回路に用いるクロック信号を、アンテナ回路から入力される交流信号を使用して生成することによって、トランジスタ素子のばらつきの影響を受けない安定な昇圧をおこなうことができる。また、周囲温度の影響を受けない安定な昇圧をおこなうことができる。10

## 【発明を実施するための最良の形態】

## 【0034】

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従つて、本発明は本実施の形態の記載内容に限定して解釈されるものではない。また、実施形態において同じ部分は同じ符号を付して詳しい説明を省略する。20

## 【0035】

本発明の半導体装置について説明する。

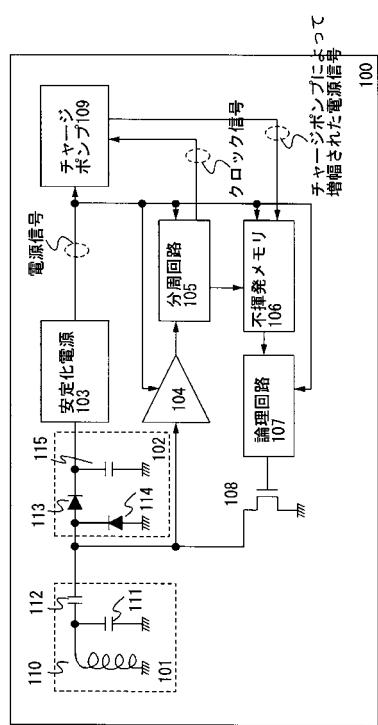

図1において、IDチップに用いる半導体装置100はアンテナ回路101、整流回路102、安定化電源103、アンプ104、分周回路105、不揮発性メモリ106、論理回路107、スイッチ用トランジスタ108、チャージポンプ109によって構成されている。また、アンテナ回路101はアンテナコイル110、同調容量111、カップリング容量112によって構成される。整流回路102はダイオード113、114、平滑容量115によって構成される。図1に示す実施形態において、アンテナ回路は半導体装置上に構成されているが、これに限定されずアンテナ回路を半導体装置の外部に接続しても良い。

## 【0036】

この回路で用いるダイオードは一例として、TFT素子をダイオード接続したものを用いることができる。また、容量507～512は基板上に直接構成してもよいし、外付けにすることもできる。外付けにする容量はどのような形状でも構わないが、IDチップに用いる回路規模の観点からチップコンデンサを用いるとより好ましい。なお、この図で挙げた例は一例であって、回路構成、ダイオード及び容量の材質及び個数はこれに限定されるものではない事を付記する。30

## 【0037】

このような半導体装置の動作を以下に説明する。アンテナ回路101で受信した交流信号はダイオード113、114によって半波整流され、容量115によって平滑される。この平滑された電圧は多数のリップルを含んでいるため、安定化電源103で安定化され、安定化された後の電圧をアンプ104、分周回路105、不揮発性メモリ106、論理回路107に供給する。一方、アンテナ回路で受信された交流信号はアンプ104を通して分周回路105に入力され、分周がおこなわれる。アンテナに受信される信号が13.56MHzの場合8分周、16分周がおこなわれる。そして、分周後の信号を用いて、不揮発性メモリ106に記憶されているデータを呼び出す。つぎに不揮発性メモリ106のデータを論理回路107で加工し、その出力でスイッチトランジスタ108を動作させる。40

## 【0038】

スイッチ用トランジスタ108がオンするとアンテナ回路101の出力がGNDに接続されるため、アンテナのインピーダンスが変化する。これによって、IDチップのアンテ50

ナで反射される質問器の信号に変化が生じる。この変化を質問器が読み取ることによって I D チップの不揮発性メモリ 106 に記憶されたデータを知ることが可能になる。

【0039】

一般的に不揮発性メモリへの書き込みは読み出しに比べて高い電圧を必要とする。従って、読み出しが安定化電源 103 で安定された電圧でおこなえば良いが、書き込みをおこなう場合には、チャージポンプ 109 によって、安定化電源 103 の出力電圧を昇圧し、その電圧を用いて書き込みをおこなう必要がある。また、ここでは図示していないが液晶などを用いた表示装置を用いる場合、駆動するために高い電圧が必要となるため、やはりチャージポンプ 109 で昇圧した電源を用いる。

【0040】

不揮発性メモリに書き込みをおこなう場合は、チャージポンプ 109 によって、安定化電源 103 の出力電圧を昇圧し、その電圧を用いて書き込みをおこなう。チャージポンプを駆動するためのクロック信号は従来例に示したようなリングオシレータではなく、アンテナから入力された交流信号を用いて生成する。図 1 では交流信号を分周してチャージポンプにクロックとして入力しているが、直接入力するまたは、ロジック回路を介して入力してもかまわない。

【0041】

アンテナから入力される交流信号は規格によって周波数が固定されているため、従来例のようにトランジスタ素子のバラツキによって、周波数が変動することではなく、または周囲温度によって周波数が変動することはない。このようにして、安定した昇圧が可能となり、その結果として、安定な書き込みが可能となる。

【実施例 1】

【0042】

以下に本発明の実施例について記述する。

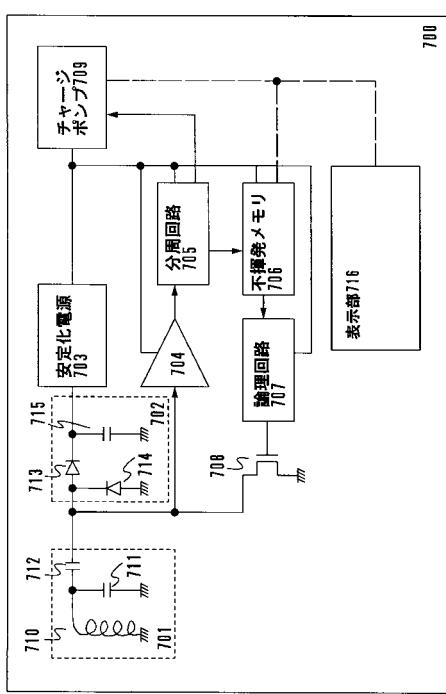

図 7 において、I D チップに用いる半導体装置 700 はアンテナ回路 701、整流回路 702、安定化電源 703、アンプ 704、分周回路 705、不揮発性メモリ 706、論理回路 707、スイッチ用トランジスタ 708、チャージポンプ 709、表示部 716 によって構成されている。また、アンテナ回路 701 はアンテナコイル 710、同調容量 711、カップリング容量 712 によって構成される。整流回路 702 はダイオード 713、714、平滑容量 715 によって構成される。図 7 に示す実施例において、アンテナ回路は半導体装置上に構成されているが、これに限定されずアンテナ回路を半導体装置の外部に接続しても良い。

【0043】

表示部 716 は液晶を用いた表示部、有機 E L などの発光素子をもちいた表示部、電気泳動素子を用いた表示部などがあるが、これ以外のものであっても良い。これらの表示部を構成する表示材料は一般的に駆動電圧が L S I の駆動電圧より高く、10V 以上であることが多い。従って、表示部の動作においても昇圧が必要となる。

表示内容は不揮発性メモリに記憶された内容を表示して良いし、質問器から送られた情報を表示しても良い。

【0044】

このような I D チップの動作を以下に説明する。アンテナ回路 701 で受信した交流信号はダイオード 713、714 によって半波整流され、平滑容量 715 によって平滑される。この平滑された電圧は多数のリップルを含んでいるため、安定化電源 703 で安定化され、安定化された後の電圧をアンプ 704、分周回路 705、不揮発性メモリ 706、論理回路 707 に供給する。一方、アンテナ回路で受信された交流信号はアンプ 704 を通して分周回路 705 に入力され、分周がおこなわれる。アンテナに受信される信号が 13.56MHz の場合 8 分周、16 分周がおこなわれる。そして、分周後の信号を用いて、不揮発性メモリ 706 に記憶されているデータを呼び出す。つぎに不揮発性メモリ 706 のデータを論理回路 707 で加工し、その出力でスイッチ用トランジスタ 708 を動作させる。

10

20

30

40

50

## 【0045】

スイッチ用トランジスタ708がオンするとアンテナ回路701の出力がGNDに接続されるため、アンテナのインピーダンスが変化する。これによって、IDチップのアンテナで反射される質問器の信号に変化が生じる。この変化を質問器が読み取ることによってIDチップの不揮発性メモリ706に記憶されたデータを知ることが可能になる。

## 【0046】

表示部に表示をおこなう場合は、チャージポンプ709によって、安定化電源703の出力電圧を昇圧し、その電圧を用いて表示をおこなう。チャージポンプを駆動するためのクロック信号は従来例に示したようなリングオシレータではなく、アンテナから入力された交流信号を用いて生成する。図7では交流信号を分周してチャージポンプにクロックとして入力しているが、直接入力するまたは、ロジック回路を介して入力してもかまわない。

10

## 【0047】

アンテナから入力される交流信号は規格によって周波数が固定されているため、従来例のようにトランジスタ素子のバラツキによって、周波数が変動する、または周囲温度によって周波数が変動することはない。このようにして、安定した昇圧が可能となり、その結果として、安定な書き込みが可能となる。

## 【0048】

また、本実施例は実施形態との組み合わせからなる構成を用いても実現することができる。

20

## 【実施例2】

## 【0049】

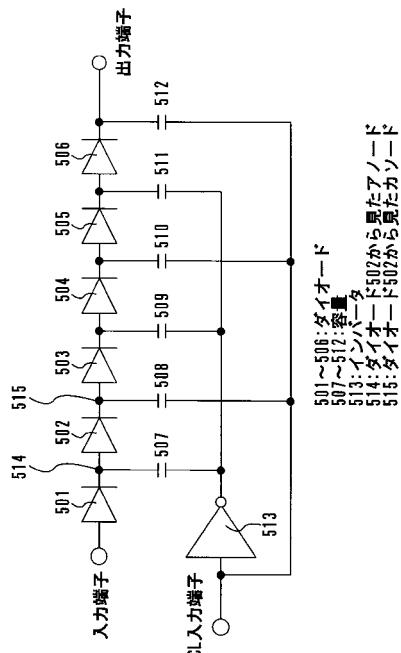

図5はチャージポンプ回路の実施例である。

## 【0050】

ここに示すチャージポンプ回路は6個のダイオード501～506と容量507～512、インバータ513から構成され、クロック信号を入力することにより、入力電圧をVIN、ダイオードの順方向電圧をVFとしたときに出力には(VIN - VF) × 6の電圧を得ることができるというものである。

## 【0051】

ここで、クロック信号は図1のアンテナ回路101で受信した信号、またはアンテナ回路101で受信した信号をアンプ104で増幅して分周回路105に入力し、分周回路105によって分周がおこなわれたものを用いることができる。

30

## 【0052】

図5を用いて動作の概略を説明する。クロック信号はCL入力端子を通して、容量508、510、512の一端へ、インバータ513によって反転させた信号を容量507、509、511の一端へ入力される。

## 【0053】

ダイオード502から見たアノードを514、カソードを515とする。クロック信号およびその反転信号によりアノード514およびカソード515にそれぞれ電荷が供給される。そして、アノード514とカソード515の電位差がダイオードの順方向電圧VFを超えたときに電流が流れ、カソード側を昇圧する。このとき上昇する電圧は(VIN - VF)となる。

40

## 【0054】

回路が直列に複数接続されている場合、一段進むたびに出力の電圧が(VIN - VF)分だけ上昇する。図5の場合は6段直列に接続されているため出力は(VIN - VF) × 6分上昇することになる。このようにして図5の回路はチャージポンプとして働く。

## 【0055】

この回路で用いるダイオードは一例として、TFT素子をダイオード接続したもの用いることができる。また、容量507～512は基板上に直接構成してもよいし、外付けにすることもできる。外付けにする容量はどのような形状でも構わないが、RFIDチッ

50

プに用いる回路規模の観点からチップコンデンサを用いるとより好ましい。なお、この図で挙げた例は一例であって、回路構成、ダイオード及び容量の材質及び個数はこれに限定されるものではない事を付記する。

【0056】

また、本実施例は実施形態、および実施例1のどのような組み合わせからなる構成を用いても実現することができる。

【実施例3】

【0057】

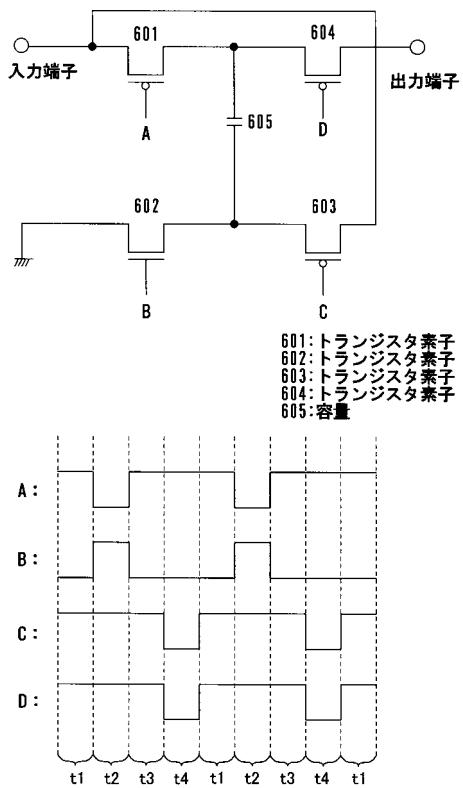

図6は実施例2と異なるチャージポンプ回路の例である。

【0058】

ここに示すチャージポンプ回路は図6(A)に示すように4個のトランジスタ素子601～604と容量605から構成され、P型トランジスタ601のゲート電極には信号Aが、N型トランジスタ602のゲート電極には信号Bが、P型トランジスタ603のゲート電極には信号Cが、P型トランジスタ604のゲート電極には信号Dがそれぞれ入力される。図6(B)に示すような信号A～Dを入力することにより、入力信号よりも高い出力信号を得ることができるものである。

【0059】

信号A～Dは図1のアンテナ回路101で受信した信号、またはアンテナ回路101で受信した信号をアンプ104で増幅して分周回路105に入力し、分周回路105によって分周がおこなわれたものを用いることができる。

【0060】

図6を用いて動作の概略を説明する。動作期間を信号A～Dの入力パターンによってt1～t4に分ける。まずt1の期間においては信号AはHi、信号BはLo、信号CはHi、信号DはHiがそれぞれトランジスタ素子601～604に入力される。よってトランジスタ素子601～604はオフした状態であり、従って容量605や出力は浮遊状態のまま変化しない。

【0061】

t2の期間においてはLoである信号AとHiである信号Bによってトランジスタ素子601および602がオンすることによって、容量605は一端は接地され、もう一端には入力端子からの信号に応じた電荷が蓄電される。信号Cおよび信号DはHiのままでトランジスタ素子603および604はオフのままである。

【0062】

t3の期間においては信号AはHiに、信号BはLoに変わるために再びトランジスタ素子601および602はオフして容量605と入力端子との接続は遮断される。信号Cおよび信号Dはこの期間でもHiであるためトランジスタ素子603および604はオフのままである。

【0063】

t4においては信号AはHi、信号BはLoのままでトランジスタ素子601および602はオフのままである。しかし信号Cおよび信号DはLoになるためトランジスタ素子603およびトランジスタ素子604がオンする。このことにより、接地されていた容量605の一方の端子の電位が入力端子の電位まで持ち上がるため、容量結合により容量605の電位が持ち上がり出力端子から出力される。

【0064】

再び期間t1に戻り、信号A～Dによりトランジスタ素子601～604はオフされ、以降動作を繰り返す。このようにして図6の回路はチャージポンプとして働く。

【0065】

この回路で用いる容量605は基板上に直接構成してもよいし、外付けにすることもできる。外付けにする容量はどのような形状でも構わないが、RFIDチップに用いる回路規模の観点からチップコンデンサを用いるとより好ましい。なお、この図で挙げた例は一例であって、回路構成、容量の材質及び個数はこれに限定されるものではない事を付記す

10

20

30

40

50

る。

【0066】

また、本実施例は実施形態、および実施例1のどのような組み合わせからなる構成を用いても実現することができる。

【実施例4】

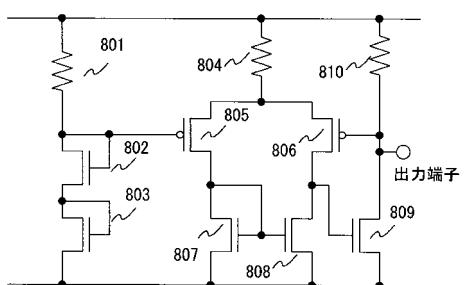

【0067】

図8は安定化電源の例である。図8の安定化電源回路は基準電圧回路とバッファアンプで構成される。基準電圧回路は抵抗801、ダイオード接続のトランジスタ802、803によって構成され、トランジスタのVGS2つ分の基準電圧を発生させる。

【0068】

バッファアンプはトランジスタ805、806で構成される差動回路、トランジスタ807、808によって構成されるカレントミラー回路、電流供給用抵抗804、トランジスタ809、抵抗810によって構成されるソース接地アンプよりなる。

【0069】

出力端子より流れる電流が大きいときはトランジスタ809に流れる電流が少なくなり、また、出力より流れる電流が小さいときはトランジスタ809に流れる電流が多くなり、抵抗810に流れる電流はほぼ一定となるように動作する。

【0070】

また出力端子の電位は基準電圧回路とほぼ同じ値となる。ここでは基準電圧回路とバッファアンプよりなる安定化電源回路を示しているが、本発明に用いる安定化電源回路は上記にこだわらず、他の形式の回路であっても良い。

【0071】

また、本実施例は実施形態、および実施例1～3のどのような組み合わせからなる構成を用いても実現することができる。

【実施例5】

【0072】

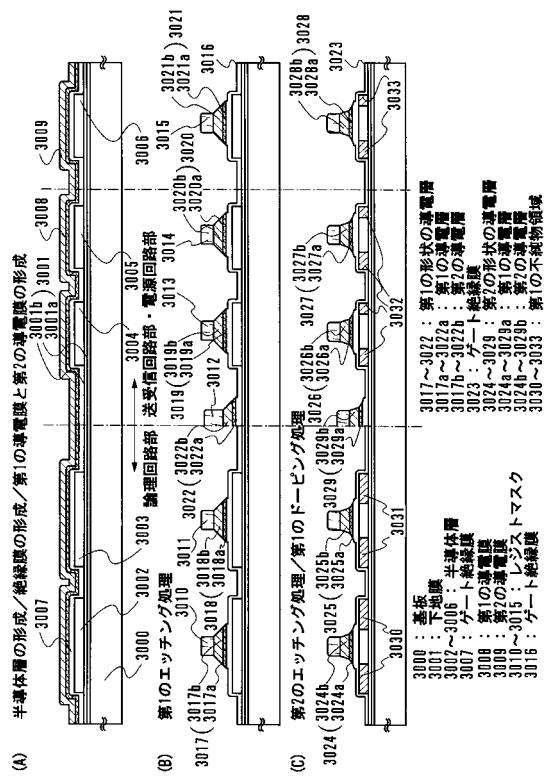

本実施例においては、同一の絶縁基板上に実施形態で示したスイッチ用トランジスタ及び容量手段などに用いるTFT (Thin Film Transistor; 薄膜トランジスタ)を同時に作製する方法について図9乃至図11を用いて説明する。この方法によりN型TFT、P型TFTを有する論理回路部(論理回路・メモリなど)と、N型TFT、P型TFT、容量手段を有する送受信回路部(アンプ・分周回路など)、電源回路部(整流回路・安定化電源など)とを同一の基板上に形成することができる。

【0073】

なお、本実施例では半導体素子としてNチャネル型TFT、Pチャネル型TFTを例に挙げて示すが、本発明においてIDチップに含まれる半導体素子はこれに限定されるものではなく、有機薄膜トランジスタ、ダイオード、MIM素子などを適宜用いることができる。また、この作製方法は一例であって、絶縁基板上での作製方法を限定するものではなく、単結晶基板を用いたMOSトランジスタ、バイポーラトランジスタ、インダクタ等を適宜用いることができる。

【0074】

まず、図9(A)に示すように、コーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラス、またはアルミニオホウケイ酸ガラスなどのガラスから成る、もしくは耐熱性プラスチックからなる基板3000上に酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜から成る下地膜3001を形成する。例えば、プラズマCVD法でSiH<sub>4</sub>、NH<sub>3</sub>、N<sub>2</sub>Oから作製される酸化窒化シリコン膜3001aを10～200nm(好ましくは50～100nm)形成し、同様にSiH<sub>4</sub>、N<sub>2</sub>Oから作製される酸化窒化水素化シリコン膜3001bを50～200nm(好ましくは100～150nm)の厚さに積層形成する。本実施例では下地膜3001を2層構造として示したが、前記絶縁膜の単層膜または2層以上積層させた構造として形成しても良い。

10

20

30

40

50

## 【0075】

島状半導体層3002～3006は、非晶質構造を有する半導体膜をレーザ結晶化法や公知の熱結晶化法を用いて作製した結晶質半導体膜で形成する。この島状半導体層3002～3006の厚さは25～80nm(好ましくは30～60nm)の厚さで形成する。結晶質半導体膜の材料に限定はないが、好ましくはシリコンまたはシリコンゲルマニウム(SiGe)合金などで形成すると良い。

## 【0076】

レーザ結晶化法で結晶質半導体膜を作製するには、パルス発振型または連続発光型のエキシマレーザやYAGレーザ、YVO<sub>4</sub>レーザを用いる。これらのレーザを用いる場合には、レーザ発振器から放射されたレーザ光を光学系で線状に集光し半導体膜に照射する方法を用いると良い。結晶化の条件は実施者が適宣選択するものであるが、エキシマレーザを用いる場合はパルス発振周波数30Hzとし、レーザーエネルギー密度を100～400mJ/cm<sup>2</sup>(代表的には200～300mJ/cm<sup>2</sup>)とする。また、YAGレーザを用いる場合にはその第2高調波を用いパルス発振周波数1～10kHzとし、レーザーエネルギー密度を300～600mJ/cm<sup>2</sup>(代表的には350～500mJ/cm<sup>2</sup>)とすると良い。そして幅100～1000μm、例えば400μmで線状に集光したレーザ光を基板全面に渡って照射し、この時の線状レーザ光の重ね合わせ率(オーバーラップ率)を80～98%として行う。

## 【0077】

次いで、島状半導体層3002～3006を覆うゲート絶縁膜3007を形成する。ゲート絶縁膜3007はプラズマCVD法またはスパッタ法を用い、厚さを40～150nmとしてシリコンを含む絶縁膜で形成する。本実施例では、120nmの厚さの酸化窒化シリコン膜で形成する。勿論、ゲート絶縁膜はこのような酸化窒化シリコン膜に限定されるものでなく、他のシリコンを含む絶縁膜を単層または積層構造として用いても良い。例えば、酸化シリコン膜を用いる場合には、プラズマCVD法でTEOS(Tetraethyl Orthosilicate)とO<sub>2</sub>とを混合し、反応圧力40Pa、基板温度300～400とし、高周波(13.56MHz)、電力密度0.5～0.8W/cm<sup>2</sup>で放電させて形成することができる。このようにして作製される酸化シリコン膜は、その後400～500の熱アニールによりゲート絶縁膜として良好な特性を得ることができる。

## 【0078】

そして、ゲート絶縁膜3007上にゲート電極を形成するための第1の導電膜3008と第2の導電膜3009とを形成する。本実施例では、第1の導電膜3008をTaで50～100nmの厚さに形成し、第2の導電膜3009をWで100～300nmの厚さに形成する。

## 【0079】

Ta膜はスパッタ法で、TaのターゲットをArでスパッタすることにより形成する。この場合、Arに適量のXeやKrを加えると、Ta膜の内部応力を緩和して膜の剥離を防止することができる。また、相のTa膜の抵抗率は20μcm程度でありゲート電極に使用することができるが、相のTa膜の抵抗率は180μcm程度でありゲート電極とするには不向きである。相のTa膜を形成するために、Taの相に近い結晶構造をもつ窒化タンタルを10～50nm程度の厚さでTaの下地に形成しておくと相のTa膜を容易に得ることができる。

## 【0080】

W膜を形成する場合には、Wをターゲットとしたスパッタ法で形成する。その他に6フッ化タンゲステン(WF<sub>6</sub>)を用いる熱CVD法で形成することもできる。いずれにしてもゲート電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は20μcm以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図ることができるが、W中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。このことより、スパッタ法による場合、純度99.9999%のWターゲットを用い

10

20

30

40

50

、さらに成膜時に気相中からの不純物の混入がないように十分配慮してW膜を形成することにより、抵抗率9~20 $\mu$  cmを実現することができる。

#### 【0081】

なお、本実施例では、第1の導電膜3008をTa、第2の導電膜3009をWとしたが、特に限定されず、いずれもTa、W、Ti、Mo、Al、Cuなどから選ばれた元素、または前記元素を主成分とする合金材料もしくは化合物材料で形成しても良い。また、リン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜を用いても良い。本実施例以外の組み合わせの一例で望ましいものとしては、第1の導電膜3008を窒化タンタル(TaN)で形成し、第2の導電膜3009をWとする組み合わせ、第1の導電膜3008を窒化タンタル(TaN)で形成し、第2の導電膜3009をAlとする組み合わせ、第1の導電膜3008を窒化タンタル(TaN)で形成し、第2の導電膜3009をCuとする組み合わせ等が挙げられる。

10

#### 【0082】

また、LDDを小さくして済むような場合は、W単層などの構成にしても良いし、構成は同じでも、テーパー角を立てることによって、LDDの長さを小さくすることができる。

#### 【0083】

次に、レジストによるマスク3010~3015を形成し、電極及び配線を形成するための第1のエッティング処理を行う。本実施例ではICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッティング法を用い、エッティング用ガスにCF<sub>4</sub>とCl<sub>2</sub>を混合し、1Paの圧力でコイル型の電極に500WのRF(13.56MHz)電力を投入してプラズマを生成して行う。基板側(試料ステージ)にも100WのRF(13.56MHz)電力を投入し、実質的に負の自己バイアス電圧を印加する。CF<sub>4</sub>とCl<sub>2</sub>を混合した場合にはW膜及びTa膜とも同程度にエッティングされる。

20

#### 【0084】

上記エッティング条件では、レジストによるマスクの形状を適したものとすることにより、基板側に印加するバイアス電圧の効果により第1の導電層及び第2の導電層の端部がテーパー形状となる。テーパー部の角度は15~45°となる。ゲート絶縁膜上に残渣を残すことなくエッティングするためには、10~20%程度の割合でエッティング時間を増加させると良い。W膜に対する酸化窒化シリコン膜の選択比は2~4(代表的には3)であるので、オーバーエッティング処理により、酸化窒化シリコン膜が露出した面は20~50nm程度エッティングされることになる。こうして、第1のエッティング処理により第1の導電層と第2の導電層から成る第1の形状の導電層3017~3022(第1の導電層3017a~3022aと第2の導電層3017b~3022b)を形成する。このとき、ゲート絶縁膜3007においては、第1の形状の導電層3017~3022で覆われない領域は20~50nm程度エッティングされ薄くなった領域3016が形成される。(図9(B))

30

#### 【0085】

続いて、図9(C)に示すように、レジストマスク3010~3015は除去しないまま、第2のエッティング処理を行う。エッティングガスにCF<sub>4</sub>とCl<sub>2</sub>とO<sub>2</sub>とを用い、W膜を選択的にエッティングする。この時、第2のエッティング処理により第2の形状の導電層3024~3029(第1の導電層3024a~3029aと第2の導電層3024b~3029b)を形成する。このとき、ゲート絶縁膜3007においては、第2の形状の導電層3024~3029で覆われない領域はさらに20~50nm程度エッティングされ薄くなった領域3023が形成される。

40

#### 【0086】

W膜やTa膜のCF<sub>4</sub>とCl<sub>2</sub>の混合ガスによるエッティング反応は、生成されるラジカルまたはイオン種と反応生成物の蒸気圧から推測することができる。WとTaのフッ化物と塩化物の蒸気圧を比較すると、Wのフッ化物であるWF<sub>6</sub>が極端に高く、その他のWC<sub>1.5</sub>、TaF<sub>5</sub>、TaC<sub>1.5</sub>は同程度である。従って、CF<sub>4</sub>とCl<sub>2</sub>の混合ガスではW膜及びT

50

a 膜共にエッティングされる。しかし、この混合ガスに適量の  $O_2$  を添加すると  $CF_4$  と  $O_2$  が反応して  $CO$  と  $F$  になり、 $F$  ラジカルまたは  $F$  イオンが多量に発生する。その結果、フッ化物の蒸気圧が高い  $W$  膜のエッティング速度が増大する。一方、Ta は  $F$  が増大しても相対的にエッティング速度の増加は少ない。また、Ta は  $W$  に比較して酸化されやすいので、 $O_2$  を添加することで Ta の表面が酸化される。Ta の酸化物はフッ素や塩素と反応しないためさらに Ta 膜のエッティング速度は低下する。従って、 $W$  膜と Ta 膜とのエッティング速度に差を作ることが可能となり  $W$  膜のエッティング速度を Ta 膜よりも大きくすることが可能となる。

#### 【0087】

そして第1のドーピング処理を行い、N型を付与する不純物元素を添加する。ドーピングの方法はイオンドープ法もしくはイオン注入法で行えば良い。イオンドープ法の条件はドーズ量を  $1 \times 10^{13} \sim 5 \times 10^{14}$  atoms /  $cm^2$  とし、加速電圧を  $60 \sim 100$  keV として行う。N型を付与する不純物元素として15族に属する元素、典型的にはリン(P)または砒素(As)を用いるが、ここではリン(P)を用いる。この場合、導電層 3024 ~ 3029 が N型を付与する不純物元素に対するマスクとなり、自己整合的に第1の不純物領域 3030 ~ 3033 が形成される。第1の不純物領域 3030 ~ 3033 には  $1 \times 10^{20} \sim 1 \times 10^{21}$  atoms /  $cm^3$  濃度範囲で N型を付与する不純物元素を添加する。(図9(C))。

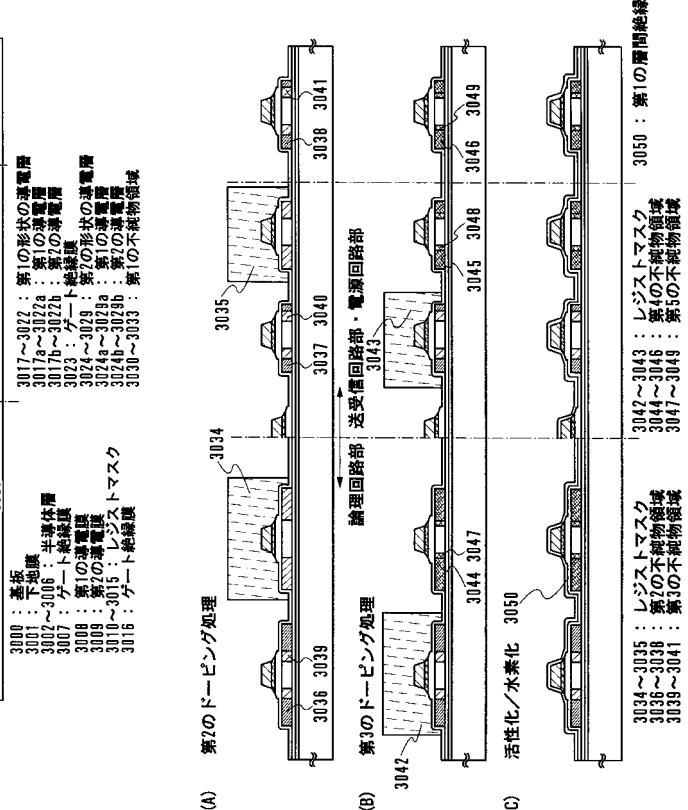

#### 【0088】

そして、図10(A)に示すように P型 TFT になる部分をレジストマスク 3034、3035 で覆った上で第2のドーピング処理を行う。このとき、画素部 TFT は全てレジストマスクで覆わずに外側を開けてドーピングを行う。第2のドーピング処理は、第1のドーピング処理よりもドーズ量を下げて高い加速電圧の条件として N型を付与する不純物元素をドーピングする。例えば、加速電圧を  $70 \sim 120$  keV とし、 $1 \times 10^{13}$  atoms /  $cm^2$  のドーズ量で行い、図9(C)で島状半導体層に形成された第1の不純物領域 3030 ~ 3033 内に新たな不純物領域 3036、3037、3038 を形成する。ドーピングは、第2の形状の導電層 3024、3026、3028 を不純物元素に対するマスクとして用い、レジストマスクで覆われていないところの第1の導電層 3024a、3026a、3028a の下側の領域の半導体層にも不純物元素が添加されるようにドーピングする。こうして、第3の不純物領域 3039、3040、3041 が形成される。この第3の不純物領域 3039、3040、3041 に添加されたリン(P)の濃度は、第1の導電層 3024a、3026a、3028a のテープ部の膜厚に従って緩やかな濃度勾配を有している。なお、第1の導電層 3024a、3026a、3028a のテープ部と重なる半導体層において、第1の導電層 3024a、3026a、3028a のテープ部の端部から内側に向かって若干、不純物濃度が低くなっているものの、ほぼ同程度の濃度である。

#### 【0089】

そして、図10(B)に示すように、P型 TFT を形成する島状半導体層 3003、3005 と容量手段を形成する島状半導体層 3006 に、第1の導電型とは逆の導電型の第4の不純物領域 3044、3045、3046 を形成する。第2の形状の導電層 3025b、3027b、3028b を不純物元素に対するマスクとして用い、自己整合的に不純物領域を形成する。このとき、N型 TFT を形成する島状半導体層 3002、および 3004 はレジストマスク 3042、3043 で全面を被覆しておく。ドーピングは、第2の形状の導電層 3025、3027、3028 を不純物元素に対するマスクとして用い、レジストマスクで覆われていないところの第1の導電層 3025a、3027a、3028a の下側の領域の半導体層にも不純物元素が添加されるようにドーピングする。こうして、第5の不純物領域 3047、3048、3049 が形成される。不純物領域 3044 と 3045、3046 にはそれぞれ異なる濃度でリンが添加されているが、ジボラン( $B_2H_6$ )を用いたイオンドープ法で形成し、そのいずれの領域においても不純物濃度が  $2 \times 10^{20} \sim 2 \times 10^{21}$  atoms /  $cm^3$  なるようにする。

10

20

30

40

50

## 【0090】

以上までの工程でそれぞれの島状半導体層に不純物領域が形成される。島状半導体層と重なる第3の形状の導電層3024～3027がゲート電極として機能する。また、3029は島状のソース信号線として機能する。3028は容量配線として機能する。

## 【0091】

レジストマスク3042、3043を除去した後、導電型の制御を目的として、それぞれの島状半導体層に添加された不純物元素を活性化する工程を行う。この工程はファーネスアニール炉を用いる熱アニール法で行う。その他に、レーザアニール法、またはラピッドサーマルアニール法(RTA法)を適用することができる。熱アニール法では酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400～700、代表的には500～600で行うものであり、本実施例では500で4時間の熱処理を行う。ただし、第2の形状の導電層3024～3029に用いた配線材料が熱に弱い場合には、配線等を保護するため層間絶縁膜3050(シリコンを主成分とする)を形成した後で活性化を行うことが好ましい。

## 【0092】

さらに、3～100%の水素を含む雰囲気中で、300～450で1～12時間の熱処理を行い、島状半導体層を水素化する工程を行う。この工程は熱的に励起された水素により半導体層のダンギングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行っても良い(図10(C))。

## 【0093】

次いで、第1の層間絶縁膜3050は酸化窒化シリコン膜から100～200nmの厚さで形成する。その上にアクリルなどの有機絶縁物材料から成る第2の層間絶縁膜3051を形成する。また、第2の層間絶縁膜3051として有機絶縁物材料の代わりに無機材料を用いることもできる。無機材料としては無機SiO<sub>2</sub>やプラズマCVD法で作製したSiO<sub>2</sub>(PCVD SiO<sub>2</sub>)、SOG(Spin on Glass; 塗布珪素酸化膜)等が用いられる。2つの層間絶縁膜を形成した後にコンタクトホールを形成するためのエッティング工程を行う。

## 【0094】

そして、論理回路部において島状半導体層のソース領域とコンタクトを形成するソース配線3052、3053、ドレイン領域とコンタクトを形成するドレイン配線3056、を形成する。また、入出力回路部、電源回路部においても同様に、ソース電極3054、3055、ドレイン電極3057、接続電極3058を形成する(図11)。

## 【0095】

以上のようにして、N型TFT、P型TFTを有する論理回路部と、N型TFT、P型TFT、容量手段を有する入出力回路部、電源回路部とを同一の基板上に形成することができる。

## 【0096】

この実施例は実施形態および実施例1～4のどのような組み合わせからなる構成を用いても実現することができる。

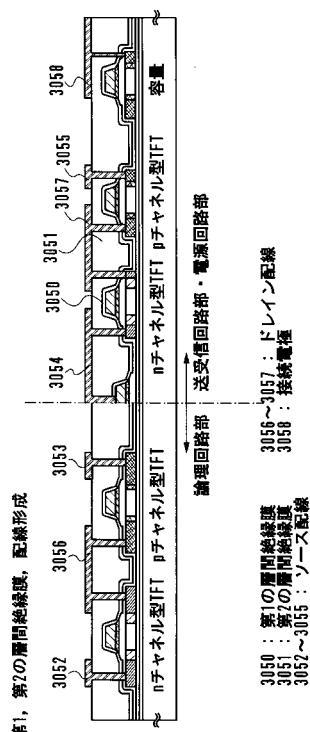

## 【実施例6】

## 【0097】

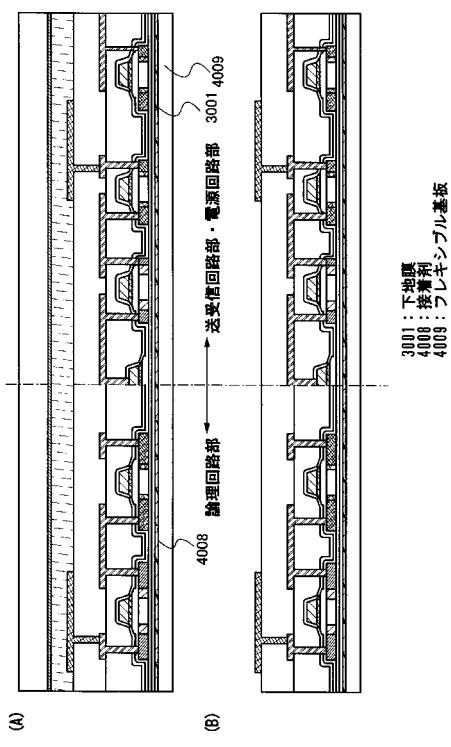

本実施例では、IDチップを形成し、フレキシブル基板へ転写するまでの作製方法について図12乃至図13を用いて説明する。なお、本実施例では半導体素子としてNチャネル型TFT、Pチャネル型TFTを例に挙げて示すが、本発明においてIDチップに含まれる半導体素子はこれに限定されない。また、この作製方法は一例であって、絶縁基板上での作製方法を限定するものではない。

## 【0098】

絶縁基板3000上に金属酸化膜4000を形成する。酸化金属膜は例えば酸化タンゲステンなどを用いることができる。

10

20

30

40

50

## 【0099】

実施例5に示した作業工程に従い、図11に示すように、第1および第2の層間絶縁膜までを形成する。

## 【0100】

次に、パッド4001、4002を形成し、第2の層間絶縁膜3051及びパッド4001、4002上に保護層4003を形成する。次いで、両面テープ4004、4005を用い、保護層4003に第2の基板4006を貼り付け、基板3000に第3の基板4007を貼り付ける(図12(A))。第3の基板4007は、後の剥離工程で基板3000が破損することを防ぐ。

## 【0101】

そして、そして、基板3000と金属酸化膜4000を物理的に引き剥がす。剥離後の状態を図12(B)に示す。その後、接着剤4008でフレキシブル基板4009と、下地膜3001とを接着する(図13(A))。

## 【0102】

次に図13(B)に示すように、保護層4003から両面テープ4004と第2の基板4006を剥がし、保護層4003を除去する事で、フレキシブル基板への転写を行うことができる。

## 【0103】

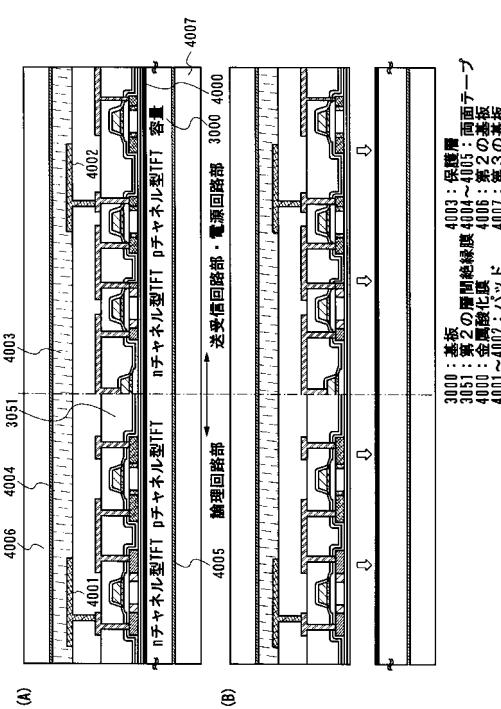

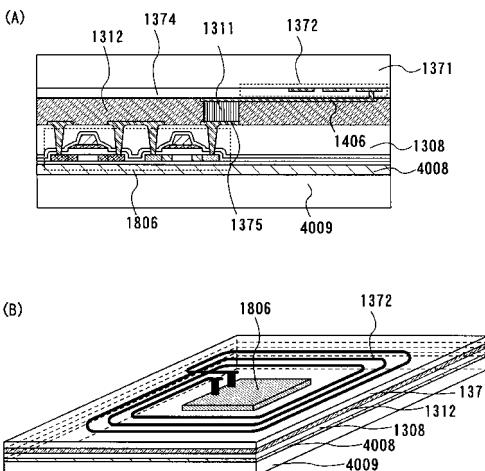

また、本実施例において、アンテナが形成されている第2の基板を用いて作製した半導体装置について図20を用いて説明する。

## 【0104】

図20(A)は、送受信回路又は電源回路の一部とアンテナとの接続部を示す断面図である。第1のフレキシブル基板4009上に接着剤4008を用いてTFT1806が設けられている。一方、第2のフレキシブル基板1371にはアンテナ1372及びパッド1406が絶縁膜1374を介して形成されている。TFT1806のソース電極又はドレイン電極1375とパッド1406とが導電層1311で接続されている。また第1のフレキシブル基板1818と第2のフレキシブル基板1371とは、アンテナ1372及びTFT1806が向かい合った状態で接着剤1312によって、貼り付けられている。

## 【0105】

図20(B)は、図20(A)の半導体装置の斜視図である。第1のフレキシブル基板4009と第2のフレキシブル基板1371との間にはTFT1806で形成された半導体集積回路及びそれに電気的に接続されるアンテナ1372が設けられている。

## 【0106】

この実施例は実施形態および実施例1～5のどのような組み合わせからなる構成を用いても実現することができる。

## 【実施例7】

## 【0107】

実施例6の剥離工程の代わりに、耐熱性の高い基板とTFTの間に水素を含む非晶質珪素膜を設け、レーザ光の照射またはエッティングにより該非晶質珪素膜を除去することで基板とTFTとを剥離し、TFTをフレキシブル基板へ貼り合わせることできる。また、TFTが形成された耐熱性の高い基板を機械的に削除または溶液やガスによるエッティングで除去することでTFTを基板から切り離し、フレキシブル基板へ貼り合わせることができる。

## 【0108】

なお、TFTが形成された耐熱性の高い基板を、溶液やガスによるエッティングで除去することでTFTを基板から切り離す方法としては、基板上に、シリコン膜からなる剥離層、及び絶縁膜を積層した後、TFT及びTFTを保護する絶縁膜を形成した後、ハロゲン化フッ素を含む気体または液体中に晒して、剥離層の除去を行う方法がある。

## 【0109】

この場合、ステンレスなどの金属、または半導体基板などの表面に酸化シリコンや窒化

10

20

30

40

50

シリコンなどの絶縁膜を形成した基板なども用いることができる。例えば、Siウェハを覆って、酸化珪素膜を形成し、これを基板として使用することができる。

【0110】

またはSiウェハ上に酸化珪素膜等を形成したものを基板として使用してもよい。この場合、SiウェハをClF<sub>3</sub>(三フッ化塩素)等のハロゲン化フッ素によりエッチングし、Siウェハを除去する。また酸化珪素膜等上には、単結晶シリコンを形成し、単結晶シリコンを有するトランジスタを形成することができる。

【0111】

このようにSiウェハを用いる場合、その他の基板上に半導体集積回路を形成する場合と比較して、微細化を達成することができる。

10

【実施例8】

【0112】

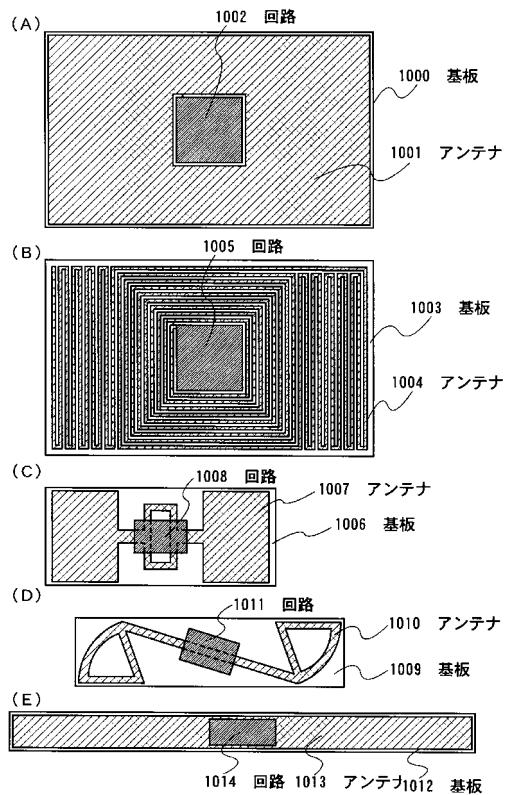

本実施例では本発明を用いた回路に外付けのアンテナをつけた例を図14、図15、図18及び図19を用いて説明する。

【0113】

図14(A)は回路の周りを一面のアンテナで覆ったものである。基板1000上にアンテナ1001を構成し、本発明を用いた回路1002を接続する。図面では回路1002の周りをアンテナ1001で覆う構成になっているが、全面をアンテナで覆い、その上に電極を構成した回路1002を貼り付けるような構造を取っても良い。

【0114】

20

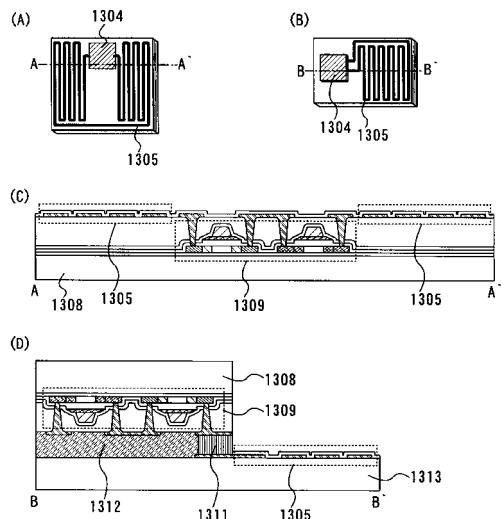

図18(A)及び図18(C)は、同一基板上に半導体集積回路1304とアンテナ1305が形成された半導体装置であり、図18(A)は上面図、図18(C)は図18(A)のA-A'における断面図である。アンテナ1305は、半導体集積回路1304を構成するTFT1309のソース電極びドレイン電極と同時に形成されている。

【0115】

図18(B)及び図18(D)は、アンテナ1305を含む基板1313上に、半導体集積回路1304を実装した半導体装置であり、図18(B)は上面図、図18(D)は図18(B)のB-B'における断面図である。半導体集積回路1304を構成するTFT1309とアンテナは、導電層1331を介して電気的に接続されている。

【0116】

30

図14(B)は細いアンテナを回路の周りを回るように配置したものである。基板1003上にアンテナ1004を構成し、本発明を用いた回路1005を接続する。なお、アンテナの配線は一例であってこれに限定するものではない。

【0117】

図14(C)は高周波数のアンテナである。基板1006上にアンテナ1007を構成し、本発明を用いた回路1008を接続する。

【0118】

図14(D)は180度無指向性(どの方向からでも同じく受信可能)なアンテナである。基板1009上にアンテナ1010を構成し、本発明を用いた回路1011を接続する。

40

【0119】

図14(E)は棒状に長く伸ばしたアンテナである。基板1012上にアンテナ1013を構成し、本発明を用いた回路1014を接続する。

【0120】

本発明を用いた回路とこれらのアンテナへの接続は公知の方法で行うことができる。例えばアンテナと回路をワイヤボンディング接続やバンプ接続を用いて接続する、あるいはチップ化した回路の一面を電極にしてアンテナに貼り付けるという方法を取ってもよい。この方式ではACF(anisotropic conductive film; 異方性導電性フィルム)を用いて貼り付けることができる。

【0121】

50

アンテナに必要な長さは受信に用いる周波数によって適正な長さが異なる。一般には波長の整数分の1の長さにすると良いとされる。例えば周波数が2.45GHzの場合は約60mm(1/2波長)、約30mm(1/4波長)とすれば良い。

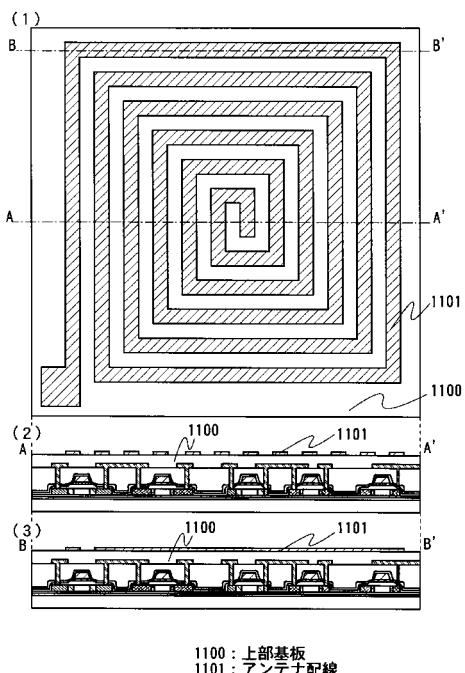

【0122】

また、本発明の回路を有する基板上に別の基板(上部基板)を取りつけ、さらにその上にアンテナを形成してもよい。図15にその一例として回路上に基板を取りつけ、らせん状のアンテナを配置したものの上面図および断面図を示す。図15(1)は、アンテナを配置した半導体装置の上面図を示し、図15(2)は、図15(1)の(A)-(A')の断面図、図15(3)は、図15(1)の(B)-(B')における断面図を示す。基板1102上に本発明の回路が形成され、該回路の上に上部基板1100が設けられ、上部基板にはアンテナ配線1101が形成されている。

10

【0123】

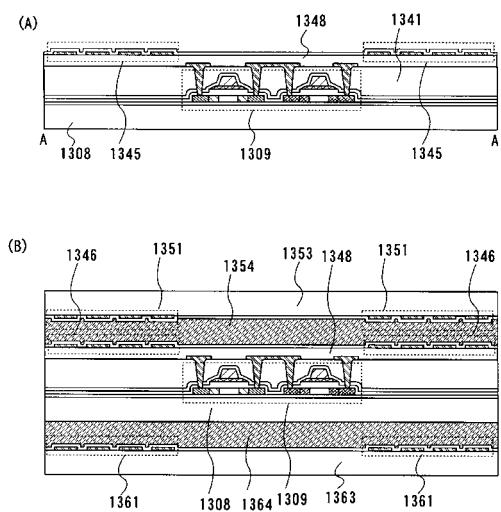

また、図19(A)に示すように、TFT1309が形成されている層間絶縁膜1341上に第2の層間絶縁膜1348を形成し、第2の層間絶縁膜1348上にアンテナ1345を形成しても良い。この場合、TFT1309上にもアンテナを形成することができるため、任意の距離のアンテナを形成することができる。

【0124】

また、図19(B)に示すように、図19(B)に示すアンテナを有する半導体集積回路をアンテナが形成された基板で挟持することができる。TFT1309が形成されている基板1308とアンテナ1361が形成されている基板(第2の基板)1363とが、第1の接着剤1364で貼付られている。また、TFT1309上に第2の層間絶縁膜1348を介して形成されたアンテナ1346とアンテナ1351が形成されている基板(第3の基板)1353とが、第2の接着剤1354で貼付られている。

20

【0125】

なお、図19(B)においては、第2の基板1363と第3の基板1353のように異なる基板で、TFT1309及びアンテナ1346を有する基板を挟持したが、この構造に限定されるものではない。例えば、第2の基板を折りたたんでTFT1309及びアンテナ1346を有する基板を挟持してもよい。また、アンテナ1346を有さないTFT1309をひとつ又は複数の基板で挟持してもよい。

【0126】

30

これらの場合、図19(A)の半導体装置よりもさらにアンテナを長く形成することができる。

【0127】

なお、本実施例に示した例はごく一例であり、アンテナの形状を限定するものではない。あらゆる形状のアンテナについて本発明は実施することが可能である。

【0128】

この実施例は実施形態および実施例1~6のどのような組み合わせからなる構成を用いても実現することができる。

【実施例9】

【0129】

40

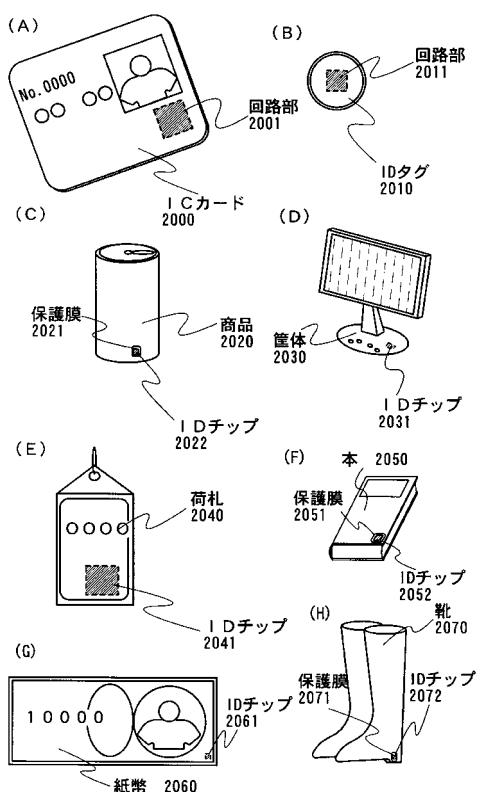

本実施例では本発明を用いた、ICカード、IDタグおよびIDチップなどの例を図16および図17を用いて説明する。

【0130】

図16(A)はICカードであり、個人の識別用のほかに内蔵された回路のメモリが書き換え可能であることをを利用して現金を使わずに代金の決済が可能なクレジットカード、あるいは電子マネーといったような使い方もできる。ICカード2000の中に本発明を用いた回路2001を組み込んでいる。

【0131】

図16(B)はIDタグであり、個人の識別用のほかに、小型化可能であることから特定の場所での入場管理などに用いることができる。IDタグ2010の中に本発明を用い

50

た回路 2011 を組み込んでいる。

【0132】

図 16 (C) はスーパーマーケットなどの小売店で商品を扱う際の商品管理を行うための ID チップ 2022 を商品に貼付した例である。本発明は ID チップ 2022 内の回路に適用される。このように ID チップを用いることにより、在庫管理が容易になるだけではなく、万引きなどの被害を防ぐことも可能である。図面では ID チップ 2022 が剥がれ落ちてしまうことを防ぐために接着を兼ねた保護膜 2021 を用いているが、ID チップ 2022 を接着剤を用いて直接貼付するような構造を取っていてもよい。また、商品に貼付する構造上、実施例 2 で挙げたフレキシブル基板を用いて作製すると好ましい。

【0133】

図 16 (D) は商品製造時に識別用の ID チップを組み込んだ例である。図面では例としてディスプレイの筐体 2030 に ID チップ 2031 を組み込まれている。本発明は ID チップ 2031 内の回路に適用される。このような構造を取ることにより製造メーカーの識別、商品の流通管理などを容易に行うことができる。なお、図面ではディスプレイの筐体を例として取り上げているが、本発明はこれに限定されることはなく、さまざまな物品に対して適用することが可能である。

【0134】

図 16 (E) は物品搬送用の荷札である。図面では荷札 2040 内に ID チップ 2041 が組み込まれている。本発明は ID チップ 2041 内の回路に適用される。このような構造を取ることにより搬送先の選別や商品の流通管理などを容易に行うことができる。なお、図面では物品を縛るひも状のものにくくりつけるような構造を取っているが、本発明はこれに限定されることはなく、シール材のようなものを用いて物品に直接貼付するような構造を取ってもよい。

【0135】

図 16 (F) は本 2050 に ID チップ 2052 が組み込まれたものである。本発明は ID チップ 2052 内の回路に適用される。このような構造を取ることにより書店における流通管理や図書館などの貸し出し処理などを容易に行うことができる。図面では ID チップ 2052 が剥がれ落ちてしまうことを防ぐために接着を兼ねた保護膜 2051 を用いているが、ID チップ 2052 を接着剤を用いて直接貼付するような構造を取る、または本 2050 の表紙に埋め込む構造を取っていてもよい。

【0136】

図 16 (G) は紙幣 2060 に RFID チップ 2061 が組み込まれたものである。本発明は ID チップ 2061 内の回路に適用される。このような構造を取ることにより偽札の流通を阻止することが容易に行える。なお、紙幣の性質上 ID チップ 2061 が剥がれ落ちるのを防ぐために紙幣 2060 に埋め込むような構造を取るとより好ましい。

【0137】

図 16 (H) は靴 2070 に ID チップ 2072 が組み込まれたものである。本発明は RFID チップ 2072 内の回路に適用される。このような構造を取ることにより製造メーカーの識別、商品の流通管理などを容易に行うことができる。図面では ID チップ 2072 が剥がれ落ちてしまうことを防ぐために接着を兼ねた保護膜 2071 を用いているが、ID チップ 2072 を接着剤を用いて直接貼付するような構造を取る、または靴 2070 に埋め込む構造を取っていてもよい。

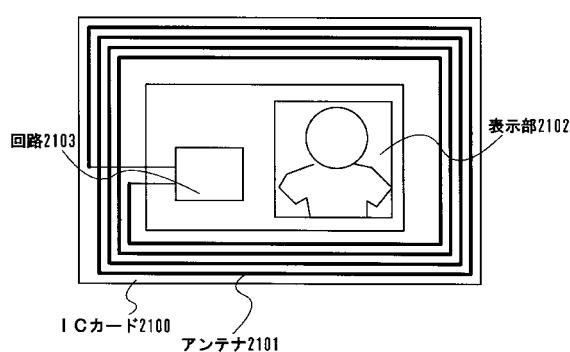

【0138】

図 17 は本発明の回路の周りに外付けのアンテナ 2101 を円周状に張り巡らせ、表示部 2102 を取りつけた IC カードである。表示部 2102 は表示に必要な駆動回路などが具備され、回路内のメモリ、あるいは外部からの入力信号を利用して画像の表示、書き換えが可能である。IC カード 2100 の中に本発明を用いた回路 2103 を組み込んでいる。アンテナの形状はカードの形状の合わせて円周状に配置したが、これはアンテナの形状を限定するものではなく、自由に形状を定めることができる。また、アンテナは外付けであることに限定されず、回路内部にアンテナを内蔵してもよい。

10

20

30

40

50

## 【0139】

なお、本実施例に示した例はごく一例であり、これらの用途に限定するものではないことを付記する。

## 【0140】

以上の様に、本発明の適用範囲は極めて広く、あらゆる物品の固体認識用のチップとして適用することが可能である。また、本実施例は実施形態、実施例1～7のどのような組み合わせからなる構成を用いても実現することができる。

## 【図面の簡単な説明】

## 【0141】

【図1】本発明の半導体装置の構成を示すブロック図。

10

【図2】従来の半導体装置の構成を示すブロック図。

【図3】従来の半導体装置の構成を示すブロック図。

【図4】リングオシレータの回路構成を示す図。

【図5】チャージポンプの回路構成を示す図。

【図6】チャージポンプの回路構成を示す図。

【図7】本発明の半導体装置の構成を示すブロック図。

【図8】安定化電源の回路構成を示す図。

【図9】本発明の半導体装置の製造プロセスを示す図。

【図10】本発明の半導体装置の製造プロセスを示す図。

20

【図11】本発明の半導体装置の製造プロセスを示す図。

【図12】本発明の半導体装置の製造プロセスを示す図。

【図13】本発明の半導体装置の製造プロセスを示す図。

【図14】本発明の半導体装置を使用したアンテナの一例を示す図。

【図15】本発明の半導体装置を使用したアンテナの一例を示す図。

【図16】本発明の半導体装置を使用した応用例を示す図。

【図17】本発明の半導体装置を使用した表示装置付きICカードの例を示す図。

【図18】本発明の半導体装置を示す図。

【図19】本発明の半導体装置を示す図。

【図20】本発明の半導体装置を示す図。

## 【符号の説明】

30

## 【0142】

100 半導体装置

101 アンテナ回路

102 整流回路

103 安定化電源

104 アンプ

105 分周回路

106 不揮発性メモリ

107 論理回路

108 スイッチ用トランジスタ

40

109 チャージポンプ

110 アンテナコイル

111 同調容量

112 カップリング容量

113 ダイオード

114 ダイオード

115 平滑容量

200 ICチップ

201 アンテナ回路

202 整流回路

50

|       |                  |    |

|-------|------------------|----|

| 2 0 3 | 安定化電源            |    |

| 2 0 4 | アンプ              |    |

| 2 0 5 | 分周回路             |    |

| 2 0 6 | マスクROM           |    |

| 2 0 7 | 論理回路             |    |

| 2 0 8 | スイッチ用トランジスタ      |    |

| 2 1 0 | アンテナコイル          |    |

| 2 1 1 | 同調容量             |    |

| 2 1 2 | カッピング容量          |    |

| 2 1 3 | ダイオード            | 10 |

| 2 1 4 | ダイオード            |    |

| 2 1 5 | 平滑容量             |    |

| 3 0 0 | IDチップ            |    |

| 3 0 1 | アンテナ回路           |    |

| 3 0 2 | 整流回路             |    |

| 3 0 3 | 安定化電源            |    |

| 3 0 4 | アンプ              |    |

| 3 0 5 | 分周回路             |    |

| 3 0 6 | EEPROM           |    |

| 3 0 7 | 論理回路             | 20 |

| 3 0 8 | スイッチ用トランジスタ      |    |

| 3 0 9 | チャージポンプ          |    |

| 3 1 0 | アンテナコイル          |    |

| 3 1 1 | 同調容量             |    |

| 3 1 2 | カッピング容量          |    |

| 3 1 3 | ダイオード            |    |

| 3 1 4 | ダイオード            |    |

| 3 1 5 | 平滑容量             |    |

| 3 1 6 | リングオシレータ(リング発振器) |    |

| 4 0 1 | インバータ            | 30 |

| 4 0 2 | インバータ            |    |

| 4 0 3 | インバータ            |    |

| 4 0 4 | インバータ            |    |

| 4 0 5 | インバータ            |    |

| 4 0 6 | インバータ            |    |

| 4 0 7 | インバータ            |    |

| 4 0 8 | インバータ            |    |

| 4 0 9 | インバータ            |    |

| 4 1 0 | インバータ            |    |

| 4 1 1 | インバータ            | 40 |

| 4 1 2 | バッファ回路           |    |

| 5 0 1 | ダイオード            |    |

| 5 0 2 | ダイオード            |    |

| 5 0 3 | ダイオード            |    |

| 5 0 4 | ダイオード            |    |

| 5 0 5 | ダイオード            |    |

| 5 0 6 | ダイオード            |    |

| 5 0 7 | 容量               |    |

| 5 0 8 | 容量               |    |

| 5 0 9 | 容量               | 50 |

|         |                   |    |

|---------|-------------------|----|

| 5 1 0   | 容量                |    |

| 5 1 1   | 容量                |    |

| 5 1 2   | 容量                |    |

| 5 1 3   | インバー <sup>タ</sup> |    |

| 5 1 4   | アノード              |    |

| 5 1 5   | カソード              |    |

| 6 0 1   | トランジスタ素子          | 10 |

| 6 0 2   | トランジスタ素子          |    |

| 6 0 3   | トランジスタ素子          |    |

| 6 0 4   | トランジスタ素子          |    |

| 6 0 5   | 容量                |    |

| 7 0 0   | 半導体装置             |    |

| 7 0 1   | アンテナ回路            |    |

| 7 0 2   | 整流回路              |    |

| 7 0 3   | 安定化電源             |    |

| 7 0 4   | アンプ               |    |

| 7 0 5   | 分周回路              |    |

| 7 0 6   | 不揮発性メモリ           |    |

| 7 0 7   | 論理回路              |    |

| 7 0 8   | スイッチ用トランジスタ       | 20 |

| 7 0 9   | チャージポンプ           |    |

| 7 1 0   | アンテナコイル           |    |

| 7 1 1   | 同調容量              |    |

| 7 1 2   | カップリング容量          |    |

| 7 1 3   | ダイオード             |    |

| 7 1 4   | ダイオード             |    |

| 7 1 5   | 平滑容量              |    |

| 7 1 6   | 表示部               |    |

| 8 0 1   | 抵抗                |    |

| 8 0 2   | トランジスタ            | 30 |

| 8 0 3   | トランジスタ            |    |

| 8 0 4   | 電流供給用抵抗           |    |

| 8 0 5   | トランジスタ            |    |

| 8 0 6   | トランジスタ            |    |

| 8 0 7   | トランジスタ            |    |

| 8 0 8   | トランジスタ            |    |

| 8 0 9   | トランジスタ            |    |

| 8 1 0   | 抵抗                |    |

| 1 0 0 0 | 基板                |    |

| 1 0 0 1 | アンテナ              | 40 |

| 1 0 0 2 | 回路                |    |

| 1 0 0 3 | 基板                |    |

| 1 0 0 4 | アンテナ              |    |

| 1 0 0 5 | 回路                |    |

| 1 0 0 6 | 基板                |    |

| 1 0 0 7 | アンテナ              |    |

| 1 0 0 8 | 回路                |    |

| 1 0 0 9 | 基板                |    |

| 1 0 1 0 | アンテナ              |    |

| 1 0 1 1 | 回路                | 50 |

|         |          |    |

|---------|----------|----|

| 1 0 1 2 | 基板       |    |

| 1 0 1 3 | アンテナ     |    |

| 1 0 1 4 | 回路       |    |

| 1 1 0 0 | 上部基板     |    |

| 1 1 0 1 | アンテナ配線   |    |

| 1 1 0 2 | 基板       |    |

| 1 3 0 4 | 半導体集積回路  |    |

| 1 3 0 5 | アンテナ     |    |

| 1 3 0 8 | 基板       |    |

| 1 3 0 9 | TFT      | 10 |

| 1 3 1 1 | 導電層      |    |

| 1 3 1 2 | 接着剤      |    |

| 1 3 1 3 | 基板       |    |

| 1 3 3 1 | 導電層      |    |

| 1 3 4 1 | 層間絶縁膜    |    |

| 1 3 4 5 | アンテナ     |    |

| 1 3 4 6 | アンテナ     |    |

| 1 3 4 8 | 層間絶縁膜    |    |

| 1 3 5 1 | アンテナ     |    |

| 1 3 5 3 | 基板       | 20 |

| 1 3 5 4 | 接着剤      |    |

| 1 3 6 1 | アンテナ     |    |

| 1 3 6 3 | 基板       |    |

| 1 3 6 4 | 接着剤      |    |

| 1 3 7 1 | フレキシブル基板 |    |

| 1 3 7 2 | アンテナ     |    |

| 1 3 7 4 | 絶縁膜      |    |

| 1 3 7 5 | ドレイン電極   |    |

| 1 4 0 6 | パッド      |    |

| 1 8 0 6 | TFT      | 30 |

| 1 8 1 8 | フレキシブル基板 |    |

| 2 0 0 0 | ICカード    |    |

| 2 0 0 1 | 回路       |    |

| 2 0 1 0 | IDタグ     |    |

| 2 0 1 1 | 回路       |    |

| 2 0 2 1 | 保護膜      |    |

| 2 0 2 2 | IDチップ    |    |

| 2 0 3 0 | 筐体       |    |

| 2 0 3 1 | IDチップ    |    |

| 2 0 4 0 | 荷札       | 40 |

| 2 0 4 1 | IDチップ    |    |

| 2 0 5 0 | 本        |    |

| 2 0 5 1 | 保護膜      |    |

| 2 0 5 2 | IDチップ    |    |

| 2 0 6 0 | 紙幣       |    |

| 2 0 6 1 | IDチップ    |    |

| 2 0 7 0 | 靴        |    |

| 2 0 7 1 | 保護膜      |    |

| 2 0 7 2 | IDチップ    |    |

| 2 1 0 0 | ICカード    | 50 |

|         |         |    |

|---------|---------|----|

| 2 1 0 1 | アンテナ    |    |

| 2 1 0 2 | 表示部     |    |

| 2 1 0 3 | 回路      |    |

| 3 0 0 0 | 基板      |    |

| 3 0 0 1 | 下地膜     |    |

| 3 0 0 2 | 島状半導体層  |    |

| 3 0 0 3 | 島状半導体層  |    |

| 3 0 0 4 | 島状半導体層  |    |

| 3 0 0 5 | 島状半導体層  |    |

| 3 0 0 6 | 島状半導体層  | 10 |

| 3 0 0 7 | ゲート絶縁膜  |    |

| 3 0 0 8 | 導電膜     |    |

| 3 0 0 9 | 導電膜     |    |

| 3 0 1 0 | レジストマスク |    |

| 3 0 1 1 | レジストマスク |    |

| 3 0 1 2 | レジストマスク |    |

| 3 0 1 3 | レジストマスク |    |

| 3 0 1 4 | レジストマスク |    |

| 3 0 1 5 | レジストマスク |    |

| 3 0 1 6 | 領域      | 20 |

| 3 0 1 7 | 導電層     |    |

| 3 0 1 8 | 導電層     |    |

| 3 0 1 9 | 導電層     |    |

| 3 0 2 0 | 導電層     |    |

| 3 0 2 1 | 導電層     |    |

| 3 0 2 2 | 導電層     |    |

| 3 0 2 3 | 領域      |    |

| 3 0 2 4 | 導電層     |    |

| 3 0 2 5 | 導電層     |    |

| 3 0 2 6 | 導電層     | 30 |

| 3 0 2 7 | 導電層     |    |

| 3 0 2 8 | 導電層     |    |

| 3 0 2 9 | 導電層     |    |

| 3 0 3 0 | 不純物領域   |    |

| 3 0 3 1 | 不純物領域   |    |

| 3 0 3 2 | 不純物領域   |    |

| 3 0 3 3 | 不純物領域   |    |

| 3 0 3 4 | レジストマスク |    |

| 3 0 3 5 | レジストマスク |    |

| 3 0 3 6 | 不純物領域   | 40 |

| 3 0 3 7 | 不純物領域   |    |

| 3 0 3 8 | 不純物領域   |    |

| 3 0 3 9 | 不純物領域   |    |

| 3 0 4 0 | 不純物領域   |    |

| 3 0 4 1 | 不純物領域   |    |

| 3 0 4 2 | レジストマスク |    |

| 3 0 4 3 | レジストマスク |    |

| 3 0 4 4 | 不純物領域   |    |

| 3 0 4 5 | 不純物領域   |    |

| 3 0 4 6 | 不純物領域   | 50 |

|           |              |    |

|-----------|--------------|----|

| 3 0 4 7   | 不純物領域        |    |

| 3 0 4 8   | 不純物領域        |    |

| 3 0 4 9   | 不純物領域        |    |

| 3 0 5 0   | 層間絶縁膜        |    |

| 3 0 5 1   | 層間絶縁膜        |    |

| 3 0 5 2   | ソース配線        |    |

| 3 0 5 3   | ソース配線        |    |

| 3 0 5 4   | ソース電極        |    |

| 3 0 5 5   | ソース電極        |    |

| 3 0 5 6   | ドレイン配線       | 10 |

| 3 0 5 7   | ドレイン電極       |    |

| 3 0 5 8   | 接続電極         |    |

| 4 0 0 0   | 金属酸化膜        |    |

| 4 0 0 1   | パッド          |    |

| 4 0 0 2   | パッド          |    |

| 4 0 0 3   | 保護層          |    |

| 4 0 0 4   | 両面テープ        |    |

| 4 0 0 5   | 両面テープ        |    |

| 4 0 0 6   | 基板           |    |

| 4 0 0 7   | 基板           | 20 |

| 4 0 0 8   | 接着剤          |    |

| 4 0 0 9   | フレキシブル基板     |    |

| 3 0 0 1 a | 酸化窒化シリコン膜    |    |

| 3 0 0 1 b | 酸化窒化水素化シリコン膜 |    |

| 3 0 1 7 a | 導電層          |    |

| 3 0 1 7 b | 導電層          |    |

| 3 0 1 8 a | 導電層          |    |

| 3 0 1 8 b | 導電層          |    |

| 3 0 1 9 a | 導電層          |    |

| 3 0 1 9 b | 導電層          | 30 |

| 3 0 2 0 a | 導電層          |    |

| 3 0 2 0 b | 導電層          |    |

| 3 0 2 1 a | 導電層          |    |

| 3 0 2 1 b | 導電層          |    |

| 3 0 2 2 a | 導電層          |    |

| 3 0 2 2 b | 導電層          |    |

| 3 0 2 4 a | 導電層          |    |

| 3 0 2 4 b | 導電層          |    |

| 3 0 2 5 a | 導電層          |    |

| 3 0 2 5 b | 導電層          | 40 |

| 3 0 2 6 a | 導電層          |    |

| 3 0 2 6 b | 導電層          |    |

| 3 0 2 7 a | 導電層          |    |

| 3 0 2 7 b | 導電層          |    |

| 3 0 2 8 a | 導電層          |    |

| 3 0 2 8 b | 導電層          |    |

| 3 0 2 9 a | 導電層          |    |

| 3 0 2 9 b | 導電層          |    |

【 図 1 】

【図2】

【図3】

【 四 4 】

【図5】

【 四 6 】

【 四 7 】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

---

フロントページの続き

(51)Int.Cl. F I

H 01Q 1/24 (2006.01)

(56)参考文献 特開2000-242754 (JP, A)

特開平05-122108 (JP, A)

特開2000-020665 (JP, A)

特開2003-202840 (JP, A)

国際公開第98/029261 (WO, A1)

特開2003-339156 (JP, A)

特開2002-150250 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 K 19/00

G 06 K 17/00