(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6088253号

(P6088253)

(45) 発行日 平成29年3月1日(2017.3.1)

(24) 登録日 平成29年2月10日(2017.2.10)

(51) Int.Cl.

F 1

|                     |                  |      |       |         |

|---------------------|------------------|------|-------|---------|

| <b>H01L 27/105</b>  | <b>(2006.01)</b> | H01L | 27/10 | 4 4 1   |

| <b>H01L 21/8242</b> | <b>(2006.01)</b> | H01L | 27/10 | 6 2 1 Z |

| <b>H01L 27/108</b>  | <b>(2006.01)</b> | H01L | 29/78 | 6 1 3 B |

| <b>H01L 29/786</b>  | <b>(2006.01)</b> | H01L | 29/78 | 6 1 8 B |

| <b>H01L 27/10</b>   | <b>(2006.01)</b> | H01L | 27/10 | 6 7 1 Z |

請求項の数 3 (全 23 頁) 最終頁に続く

(21) 出願番号

特願2013-5091 (P2013-5091)

(22) 出願日

平成25年1月16日(2013.1.16)

(65) 公開番号

特開2013-175708 (P2013-175708A)

(43) 公開日

平成25年9月5日(2013.9.5)

審査請求日 平成27年12月21日(2015.12.21)

(31) 優先権主張番号

特願2012-11147 (P2012-11147)

(32) 優先日

平成24年1月23日(2012.1.23)

(33) 優先権主張国

日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 王丸 拓郎

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 塙野入 豊

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 小山 満

最終頁に続く

(54) 【発明の名称】 半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1のトランジスタを有する揮発性回路部と、

第2のトランジスタと容量素子とを有する不揮発性記憶部と、を有し、

前記第1のトランジスタは、半導体層にシリコンを有し、

前記第2のトランジスタは、半導体層に酸化物半導体を有し、

前記容量素子は、前記第2のトランジスタのソース電極またはドレイン電極の一方に電

気的に接続され、

前記第2のトランジスタのソース電極またはドレイン電極の他方は、前記揮発性回路部

内のデータの保持及び出力が行われるノードに電気的に接続され、

前記第2のトランジスタ及び前記容量素子は、前記第1のトランジスタの上方に、絶縁

層を介して位置し、

前記第2のトランジスタは、複数の前記第1のトランジスタと重畠し、

前記第2のトランジスタのチャネル長は、前記第1のトランジスタのチャネル長の3倍

以上200倍以下である半導体装置。

## 【請求項 2】

第1のトランジスタを有する揮発性回路部と、

第2のトランジスタと容量素子とを有する不揮発性記憶部と、を有し、

前記第1のトランジスタは、半導体層にシリコンを有し、

前記第2のトランジスタは、半導体層に酸化物半導体を有し、

10

20

前記容量素子は、前記第2のトランジスタのソース電極またはドレイン電極の一方に電気的に接続され、

前記第2のトランジスタのソース電極またはドレイン電極の他方は、前記揮発性回路部内のデータの保持及び出力が行われるノードに電気的に接続され、

前記第2のトランジスタ及び前記容量素子は、前記第1のトランジスタの上方に、絶縁層を介して位置し、

前記第2のトランジスタは、複数の前記第1のトランジスタと重畠し、

前記容量素子は、複数の前記第1のトランジスタと重畠し、

前記第2のトランジスタのチャネル長は、前記第1のトランジスタのチャネル長の3倍以上200倍以下である半導体装置。 10

### 【請求項3】

請求項1又は請求項2において、

前記第2のトランジスタは、ゲート絶縁層を介して前記酸化物半導体と重なるゲート電極を有し、

前記容量素子は、前記第2のトランジスタの前記ゲート電極と同層の第1の配線層と、前記ゲート絶縁層と同層の絶縁層と、前記第2のトランジスタの前記ソース電極または前記ドレイン電極と同層の第2の配線層とを有する半導体装置。

### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

20

本発明は、演算装置に用いることが可能な、データを一時的に保持する半導体装置に関する。

#### 【背景技術】

#### 【0002】

中央演算装置(Central Processing Unit:CPU)などの半導体装置は、一般的に、データや命令を記憶するための記憶装置の他に、高速でデータの書き込みと読み出しができ、データの一時的な保持が可能なレジスタが設けられている。

#### 【0003】

通常、レジスタとしては、フリップフロップが用いられる。フリップフロップは、電源の供給が継続的に行われている間は、データの保持を行うことができる。そのため、データを保持するための電源の供給が必要であり、その分の消費電力が増加する。近年では、データに一時的な保持に用いるレジスタを有する半導体装置として、電源の供給がなくてもデータの保持が可能な素子を追加し、低消費電力化が図られた構成が提案されている。 30

#### 【0004】

例えば特許文献1では、フリップフロップに、リーク電流の極めて小さい酸化物半導体で構成されるメモリを追加して用いる構成が提案されている。

#### 【先行技術文献】

#### 【特許文献】

#### 【0005】

#### 【特許文献1】特開2011-151796号公報

40

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0006】

特許文献1に記載のレジスタを構成する回路は、微細化して設けられることが求められる。一方で、リーク電流の極めて小さい酸化物半導体をチャネル領域に具備するトランジスタは、微細化が進むにつれて、電気的な特性が変化する。具体的にはトランジスタのチャネル長が短くなるにつれて、閾値電圧がマイナス側にシフトしてしまう。そして、閾値電圧がマイナス側にシフトすると、十分小さいリーク電流となるトランジスタとして用いることが難しくなってしまう。そのため、半導体装置の微細化が進むに従って、データを一時的に保持することが難しくなってしまうといった問題が生じる。 50

**【0007】**

本発明の一態様は、フリップフロップに、リーク電流の極めて小さい酸化物半導体で構成されるメモリを追加して用いる構成において、リーク電流の極めて小さい酸化物半導体をチャネル領域に具備するトランジスタの電気的特性が大きく変化することなく、データの一時的な保持が可能な半導体装置を提供することを課題の一とする。

**【課題を解決するための手段】****【0008】**

上記課題を解決するために本発明の一態様では、シリコンをチャネル領域に具備するトランジスタと酸化物半導体をチャネル領域に具備するトランジスタとを積層して設けられる不揮発性のレジスタにおいて、酸化物半導体をチャネル領域に具備するトランジスタのチャネル長を、シリコンをチャネル領域に具備するトランジスタのチャネル長より大きくし、チャネル長が同じ場合よりも閾値電圧のマイナス側へのシフトを抑制する構成とする。具体的には、シリコンをチャネル領域に具備するトランジスタのチャネル長を  $L_s$ 、酸化物半導体をチャネル領域に具備するトランジスタのチャネル長を  $L_o$ 、とすると、 $L_s / L_o$  比を 1 / 6 以下（例えば、0.5 μm / 3 μm）、好ましくは 1 / 20（例えば、0.5 μm / 10 μm）以下、とする。当該構成とすることで、不揮発性のレジスタを微細化する際、酸化物半導体をチャネル領域に具備するトランジスタのチャネル長を大きくすることができ、十分小さいリーク電流となるトランジスタとすることができます。そして、半導体装置への電源の供給が停止しても、不揮発性のレジスタ内のデータの保持を行うことができる。

10

**【0009】**

本発明の一態様は、チャネル領域がシリコンで形成された第1のトランジスタが複数設けられて構成される揮発性記憶回路部と、チャネル領域が酸化物半導体で形成された第2のトランジスタと、第2のトランジスタのソースまたはドレインの一方に電気的に接続された容量素子と、で構成される不揮発性記憶部と、を有し、第2のトランジスタは、絶縁層を介した第1のトランジスタ上に重畳して設けられており、第2のトランジスタのチャネル長は、第1のトランジスタのチャネル長の3倍以上200倍以下である半導体装置である。

20

**【0010】**

本発明の一態様は、チャネル領域がシリコンで形成された第1のトランジスタが複数設けられて構成される揮発性記憶回路部と、チャネル領域が酸化物半導体で形成された第2のトランジスタと、第2のトランジスタのソースまたはドレインの一方に電気的に接続された容量素子と、で構成される不揮発性記憶部と、を有し、第2のトランジスタは、絶縁層を介した第1のトランジスタ上に重畳して設けられており、第2のトランジスタのチャネル長は、第1のトランジスタのチャネル長の3倍以上200倍以下であり、第2のトランジスタに重畳する第1のトランジスタの個数は、6個以上である半導体装置である。

30

**【0011】**

本発明の一態様において、第1のトランジスタと第2のトランジスタとを接続するための導電層が設けられるための開口部の直径は、0.5 μm 以下である半導体装置が好ましい。

40

**【0012】**

本発明の一態様において、複数の第1のトランジスタ間を電気的に接続するための配線層が、第1のトランジスタ上の複数の層にわたって設けられており、第2のトランジスタは、配線層の間に設けられている半導体装置が好ましい。

**【0013】**

本発明の一態様において、第2のトランジスタのチャネル長は、第1のトランジスタのチャネル長の6倍以上20倍以下である半導体装置が好ましい。

**【発明の効果】****【0014】**

本発明の一態様により、フリップフロップに、リーク電流の極めて小さい酸化物半導体で

50

構成されるメモリを追加して用いる構成において、リーク電流の極めて小さい酸化物半導体をチャネル領域に具備するトランジスタの電気的特性が大きく変化することなく、データの一時的な保持が可能な半導体装置を提供することができる。

【図面の簡単な説明】

【0015】

【図1】半導体装置の構成を示す回路図及び断面図。

【図2】半導体装置の構成を示す回路図。

【図3】半導体装置の構成を説明するための回路図。

【図4】半導体装置の動作を説明するためのタイミングチャート図。

【図5】半導体装置の構成を示す回路図。

【図6】半導体装置の構成を示すレイアウト図。

【図7】半導体装置の構成を示すレイアウト図。

【図8】半導体装置の構成を示す断面図。

【図9】半導体装置の構成を示す断面図。

【図10】半導体装置の構成を示すブロック図。

【発明を実施するための形態】

【0016】

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従つて実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する発明の構成において、同じ物を指し示す符号は異なる図面間において共通とする。

【0017】

なお、各実施の形態の図面等において示す各構成の大きさ、層の厚さ、信号波形は、明瞭化のために誇張されて表記している場合がある。よって、必ずしもそのスケールに限定されない。

【0018】

また、トランジスタの「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」の用語は、入れ替えて用いることができるものとする。

【0019】

また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって形成されている場合なども含む。

【0020】

なお、本発明は、マイクロプロセッサ、画像処理回路、D S P ( D i g i t a l S i g n a l P r o c e s s o r )、マイクロコントローラなどの集積回路や、R F タグ、半導体表示装置等、記憶装置を用いることができる半導体装置を、その範疇に含む。半導体表示装置には、液晶表示装置、有機発光素子( O L E D )に代表される発光素子を各画素に備えた発光装置、電子ペーパー、D M D ( D i g i t a l M i c r o m i r r o r D e v i c e )、P D P ( P l a s m a D i s p l a y P a n e l )、F E D ( F i e l d E m i s s i o n D i s p l a y )等や、記憶装置を駆動回路または制御回路に有しているその他の半導体表示装置が、その範疇に含まれる。

【0021】

(実施の形態1)

半導体装置は、シリコンをチャネル領域に具備するトランジスタで構成されるフリップフロップと、酸化物半導体をチャネル領域に具備するトランジスタで構成される不揮発性の記憶部とを一組として不揮発性フリップフロップを構成している。当該不揮発性フリップ

10

20

30

40

50

フロップを単数または複数設けることで1ビットまたは複数ビットのデータを記憶することができる。本実施の形態では、まずは、nビット（nは自然数）のデータを保持する半導体装置として説明を行い、次いで1ビットのデータを保持する不揮発性フリップフロップの詳細な構成について説明していく。

#### 【0022】

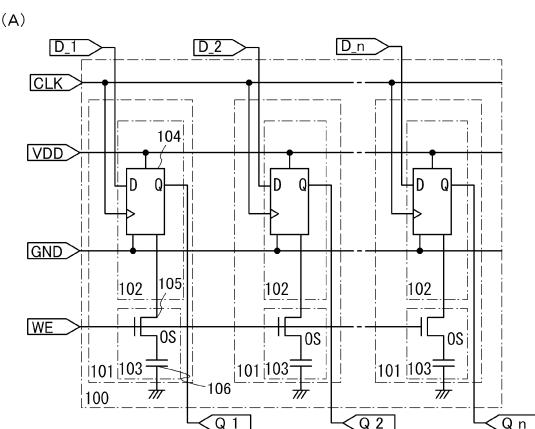

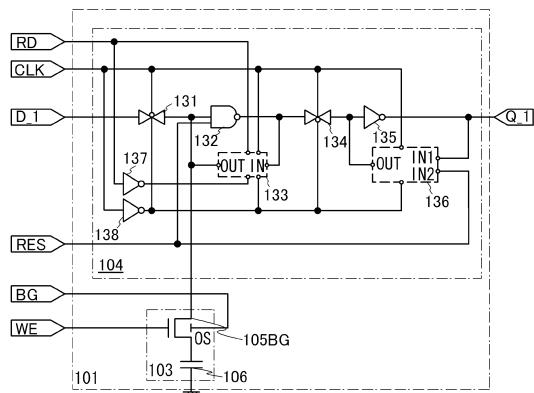

図1(A)に、nビットのデータを保持できる半導体装置のブロック図の一例を示す。図1(A)に示す半導体装置100は、n個の不揮発性フリップフロップ101を有する。

#### 【0023】

不揮発性フリップフロップ101は、揮発性記憶部102及び不揮発性記憶部103を有する。

10

#### 【0024】

揮発性記憶部102は、フリップフロップ104を有する。図1(A)では、フリップフロップの一例としてD-フリップフロップを示している。揮発性記憶部102のフリップフロップ104は、高電源電位VDD及び低電源電位GNDによる電源の供給、クロック信号CLK、及びデータD\_1乃至D\_nが入力される。他にも、フリップフロップの回路構成に応じて、制御を行うための信号を入力する構成としてもよい。フリップフロップ104の端子Dに入力されるデータD\_1乃至D\_nは、クロック信号に同期してデータの保持及び出力端子Q\_1乃至Q\_nからの出力を行う構成となる。

#### 【0025】

なお、フリップフロップ104を構成するトランジスタは、シリコンをチャネル領域に具備する複数のトランジスタで構成される。フリップフロップ104を構成するトランジスタは、データを高速で読み出しありは書き込みを行うために、微細化されたトランジスタを用いる。フリップフロップ104を構成するトランジスタは、チャネル長が0.5μm以下とすることが好適である。なおフリップフロップ104を構成するトランジスタのチャネル長の下限を示していないが、微細化による加工が可能であれば、より小さい寸法のチャネル長とすることが可能である。

20

#### 【0026】

なお微細化されたトランジスタのチャネル長は、最小の加工寸法で設計されたものであり、シリコンをチャネル領域に具備するトランジスタに設けられる開口部の直径に言い換えることも可能である。前述のチャネル長の場合、開口部の直径は、0.5μm以下と言い換えることができる。

30

#### 【0027】

不揮発性記憶部103は、酸化物半導体をチャネル領域に具備するトランジスタ105及び容量素子106を有する。図1(A)に示す不揮発性記憶部103は、制御信号WEによりトランジスタ105を導通状態にすることで、容量素子106での電荷の充放電を行うことができる、また図1(A)に示す不揮発性記憶部103は、制御信号WEによりトランジスタ105を非導通状態にすることで、容量素子106に保持された電荷の保持を行う。当該容量素子106での電荷の保持は、トランジスタ105のリーク電流が極めて小さいことを利用して、電源の供給がなくてもデータの論理状態に応じて電荷の保持を行うことができる。すなわち、トランジスタのソースまたはドレインの一方の端子と容量素子の一方の電極との間のノードで電荷を保持し、入力されたデータの論理状態の保持を行う。

40

#### 【0028】

トランジスタ105は、酸化物半導体をチャネル領域に具備するトランジスタである。なお図面において、トランジスタ105は酸化物半導体をチャネル領域に具備するトランジスタであることを示すために、OSの符号を付している。

#### 【0029】

酸化物半導体をチャネル領域に具備するトランジスタ105は、シリコンをチャネル領域に具備するトランジスタと同様に微細化すると、微細化によりトランジスタのチャネル長が短くなるにつれて、閾値電圧がマイナス側にシフトしてしまう。閾値電圧がマイナス側

50

にシフトすると、十分小さいリーク電流となるトランジスタとして用いることが難しくなり、データを一時的に保持する不揮発性記憶部として用いることが難しくなってしまう。そのため本実施の形態の構成において、酸化物半導体をチャネル領域に具備するトランジスタ105のチャネル長は、フリップフロップ104を構成するシリコンをチャネル領域に具備するトランジスタのチャネル長よりも大きくする。具体的には、酸化物半導体をチャネル領域に具備するトランジスタ105のチャネル長は、フリップフロップ104を構成するシリコンをチャネル領域に具備するトランジスタのチャネル長の3倍以上200倍以下、好ましくは6倍以上20倍以下とする。すなわち酸化物半導体をチャネル領域に具備するトランジスタ105のチャネル長は、チャネル長が $1.5\mu m$ 以上 $100\mu m$ 以下、好ましくは $3\mu m$ 以上 $10\mu m$ 以下とする構成とする。当該構成とすることで、リーク電流の極めて小さい酸化物半導体をチャネル領域に具備するトランジスタの電気的特性が大きく変化することなく、データの一時的な保持ができる不揮発性記憶部103とすることができます。10

#### 【0030】

酸化物半導体をチャネル領域に具備するトランジスタのチャネル長を前述の範囲とすると、閾値電圧の変動幅を安定させることができることについては、本出願人による特開2011-192958号公報、特開2011-228679号公報等に詳細に記載されているので参考にすればよい。

#### 【0031】

なお、チャネル長とは、キャリアが流れる方向に対して平行な方向についてのチャネル領域の長さであり、言い換えれば、ソース電極とドレイン電極間の距離である。またチャネル長は、半導体層に重畳するゲート電極の幅ということも可能である。20

#### 【0032】

一方で、フリップフロップ104を構成するシリコンをチャネル領域に具備するトランジスタのチャネル長に対して、酸化物半導体をチャネル領域に具備するトランジスタ105のチャネル長を大きくとると、半導体装置の大型化が懸念される。そこで本発明の一態様では、フリップフロップ104を構成するシリコンをチャネル領域に具備するトランジスタと、酸化物半導体をチャネル領域に具備するトランジスタ105とを積層して配置する構成とする。当該構成とすることで、酸化物半導体をチャネル領域に具備するトランジスタ105のチャネル長を大きくしても、半導体装置の大型化を抑制することができる。30

#### 【0033】

加えて本実施の形態の構成では、フリップフロップ104を構成するシリコンをチャネル領域に具備するトランジスタのうちの複数のトランジスタと、酸化物半導体をチャネル領域に具備するトランジスタ105と、を重畳するように設ける構成とする。フリップフロップ104を構成するトランジスタ数は、インバータ回路、スイッチ等を構成するトランジスタをカウントすると、10個以上となる。従ってフリップフロップ104を構成するシリコンをチャネル領域に具備するトランジスタのいずれか複数を、酸化物半導体をチャネル領域に具備するトランジスタ105に重畳するように設ける構成とすることができる。当該構成とすることで、半導体装置を構成するフリップフロップ104及びトランジスタ105を単位面積あたりで効率的に配置することができる。具体的にトランジスタ105と重畳する、フリップフロップ104を構成するシリコンをチャネル領域に具備するトランジスタの個数は、6個以上とすることが好適である。40

#### 【0034】

また本実施の形態の構成は、酸化物半導体をチャネル領域に具備するトランジスタ105のみならず、容量素子106が占める面積を大きくして設けることができる。そして、容量素子106は、トランジスタ105と同様に、フリップフロップ104を構成するシリコンをチャネル領域に具備するトランジスタと積層して配置する構成とする。当該構成とすることで、容量素子106が占める面積を大きくしても、半導体装置の大型化を抑制することができる。

#### 【0035】

50

加えて本実施の形態の構成では、フリップフロップ 104 を構成するシリコンをチャネル領域に具備するトランジスタのうちの複数のトランジスタと、容量素子 106 と、を重畠するように設ける構成とする。フリップフロップ 104 を構成するトランジスタ数は、インバータ回路、スイッチ等を構成するトランジスタをカウントすると、10 個以上となる。従ってフリップフロップ 104 を構成するシリコンをチャネル領域に具備するトランジスタのいずれか複数を、容量素子 106 に重畠するように設ける構成とすることができる。当該構成とすることで、半導体装置を構成するフリップフロップ 104 及び容量素子 106 を単位面積あたりで効率的に配置することができる。

#### 【0036】

次いで、不揮発性フリップフロップ 101 を構成する、シリコンをチャネル領域に具備するトランジスタ及び酸化物半導体をチャネル領域に具備するトランジスタ 105 を積層して設けた模式的な断面図について図 1 (B) に示す。

10

#### 【0037】

図 1 (B) では、積層して設けられる、シリコンをチャネル領域に具備するトランジスタが設けられる素子層 111、酸化物半導体をチャネル領域に具備するトランジスタが設けられる素子層 112、素子層 111 と素子層 112 との電気的接続を図るための配線層 113、及び素子層 112 の上方で別の配線層と電気的接続を図るための配線層 114 を示している。

#### 【0038】

素子層 111 には、素子分離層 120 を挟んで、シリコンをチャネル領域に具備するトランジスタ 121 が複数設けられている。トランジスタ 121 は、シリコンで形成される半導体層 122、ゲート電極として機能する導電層 123、並びにトランジスタ 121 のソース電極またはドレイン電極として機能する導電層 124 及び導電層 125 を有する。

20

#### 【0039】

なお、導電層 124 及び導電層 125 は、素子層 111、素子層 112、配線層 113、及び配線層 114 の配線として用いることができる。導電層 124 及び導電層 125 は、ダマシン法によって層間絶縁層の溝に銅などの導電層を埋め込んで、径の異なる導電層 124 及び導電層 125 を形成すればよい。なおトランジスタを有する素子層及び各層を電気的に接続する配線層は、C M P ( C h e m c a l M e c h a n i c a l P o l i s h i n g ) 技術を用いて平坦化した後、形成することが望ましい。

30

#### 【0040】

配線層 113 には、層間絶縁層の間に、他の素子層のトランジスタ間や配線間の電気的接続を図るための導電層 124 及び導電層 125 が設けられている。

#### 【0041】

素子層 112 には、酸化物半導体をチャネル領域に具備するトランジスタ 126 及び容量素子 127 が設けられている。トランジスタ 126 は、酸化物半導体で形成される半導体層 128、ソース電極またはドレイン電極として機能する導電層 129、ゲート電極として機能する導電層 130 を有する。容量素子 127 は、一方の電極として機能する導電層 129、及び他方の電極として機能する導電層 130 を有する。

40

#### 【0042】

配線層 114 には、層間絶縁層の間に、他の素子層のトランジスタ間や配線間の電気的接続を図るための導電層 124 及び導電層 125 が設けられている。

#### 【0043】

なお素子層 112 は、配線層 113 と配線層 114 との間に設けられている。当該構成とすることで、素子層 111 のレイアウトを変更することなく、素子層 112 を設けることができる。

#### 【0044】

なおトランジスタ 121 は、トップゲート型のトランジスタとして説明するが、微細化が可能なトランジスタであれば、Fin 型トランジスタ等の他の構造であってもよい。またチャネル領域が形成される半導体層は、単結晶シリコン基板上に直接トランジスタを形成

50

して用いる構成であってもよいし、SOI (Silicon on Insulator) 基板上のシリコン層を用いる構成であってもよいし、または単結晶シリコン膜を別の基板に貼り合わせて得られる半導体層を用いる構成であってもよい。また素子分離層は、LOCOS (Local Oxidation of Silicon) 技術や、STI (Shallow Trench Isolation) を用いて作製すればよい。

#### 【0045】

なおトランジスタ126は、トップゲート型のトランジスタとして説明するが、ボトムゲート型のトランジスタであってもよい。また、トランジスタ126は、スタガー型またはコプレナー型のトランジスタの構成を取ることができる。なお、チャネル領域を挟んで、トランジスタ126の閾値電圧を制御するためのバックゲート電極を設ける構成としてもよい。

10

#### 【0046】

ここで、トランジスタ126の半導体層に用いる酸化物半導体について詳述する。

#### 【0047】

トランジスタの半導体層中のチャネル領域に用いる酸化物半導体としては、少なくともインジウム (In) または亜鉛 (Zn) を含むことが好ましい。特にIn及びZnを含むことが好ましい。また、それらに加えて、酸素を強く結びつけるスタビライザーを有することが好ましい。スタビライザーとしては、ガリウム (Ga)、スズ (Sn)、ジルコニウム (Zr)、ハフニウム (Hf) 及びアルミニウム (Al) の少なくともいずれかを有すればよい。

20

#### 【0048】

また、他のスタビライザーとして、ランタノイドである、ランタン (La)、セリウム (Ce)、プラセオジム (Pr)、ネオジム (Nd)、サマリウム (Sm)、ユウロピウム (Eu)、ガドリニウム (Gd)、テルビウム (Tb)、ジスプロシウム (Dy)、ホルミウム (Ho)、エルビウム (Er)、ツリウム (Tm)、イッテルビウム (Yb)、ルテチウム (Lu) のいずれか一種または複数種を有してもよい。

#### 【0049】

例えば、四元系金属の酸化物であるIn - Sn - Ga - Zn系酸化物や、三元系金属の酸化物であるIn - Ga - Zn系酸化物、In - Sn - Zn系酸化物、In - Zr - Zn系酸化物、In - Al - Zn系酸化物、Sn - Ga - Zn系酸化物、Al - Ga - Zn系酸化物、Sn - Al - Zn系酸化物や、In - Hf - Zn系酸化物、In - La - Zn系酸化物、In - Ce - Zn系酸化物、In - Pr - Zn系酸化物、In - Nd - Zn系酸化物、In - Sm - Zn系酸化物、In - Eu - Zn系酸化物、In - Gd - Zn系酸化物、In - Tb - Zn系酸化物、In - Dy - Zn系酸化物、In - Ho - Zn系酸化物、In - Er - Zn系酸化物、In - Tm - Zn系酸化物、In - Yb - Zn系酸化物、In - Lu - Zn系酸化物や、二元系金属の酸化物であるIn - Zn系酸化物、Sn - Zn系酸化物、Al - Zn系酸化物、Zn - Mg系酸化物、Sn - Mg系酸化物、In - Mg系酸化物や、In - Ga系の材料、一元系金属の酸化物であるIn系酸化物、Sn系酸化物、Zn系酸化物などを用いることができる。

30

#### 【0050】

なお、ここで、例えば、In - Ga - Zn系酸化物とは、In、Ga及びZnを主成分として有する酸化物という意味であり、In、Ga及びZnの比率は問わない。

40

#### 【0051】

また、酸化物半導体として、 $InM_0_3 (ZnO)_m$  ( $m > 0$ ) で表記される材料を用いてもよい。なお、Mは、Ga、Fe、Mn及びCoから選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、 $In_2SnO_5 (ZnO)_n$  ( $n > 0$ ) で表記される材料を用いてもよい。

#### 【0052】

例えば、 $In : Ga : Zn = 3 : 1 : 2$ 、 $In : Ga : Zn = 1 : 1 : 1$  または  $In : Ga : Zn = 2 : 2 : 1$  の原子数比のIn - Ga - Zn系酸化物やその組成の近傍の酸化物

50

を用いることができる。または、In : Sn : Zn = 1 : 1 : 1、In : Sn : Zn = 2 : 1 : 3 または In : Sn : Zn = 2 : 1 : 5 の原子数比の In - Sn - Zn 系酸化物やその組成の近傍の酸化物を用いるとよい。

#### 【0053】

なお、例えば、In、Ga、Zn の原子数比が In : Ga : Zn = a : b : c ( a + b + c = 1 ) である酸化物が、原子数比が In : Ga : Zn = A : B : C ( A + B + C = 1 ) の酸化物の r だけ近傍であるとは、a、b、c が、式(1)を満たすことをいう。

#### 【0054】

$$(a \cdot A)^2 + (b \cdot B)^2 + (c \cdot C)^2 = r^2 \quad (1)$$

#### 【0055】

r としては、例えば、0.05 とすればよい。他の酸化物でも同様である。

10

#### 【0056】

しかし、これらに限らず、必要とする半導体特性（電界効果移動度、しきい値電圧等）に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

#### 【0057】

また、酸化物半導体を半導体層中のチャネル形成領域に用いたトランジスタは、酸化物半導体を高純度化することにより、オフ電流（ここでは、オフ状態のとき、たとえばソース電位を基準としたときのゲート電位との電位差がしきい値電圧以下のときのドレイン電流とする）を十分に低くすることが可能である。例えば、加熱成膜により水素や水酸基を酸化物半導体中に含ませないようにし、または成膜後の加熱により膜中から除去し、高純度化を図ることができる。高純度化されることにより、チャネル形成領域に In - Ga - Zn 系酸化物を用いたトランジスタで、チャネル長が 10 μm、半導体膜の膜厚が 30 nm、ドレイン電圧が 1 V ~ 10 V 程度の範囲である場合、オフ電流を、 $1 \times 10^{-13} \text{ A}$  以下とすることが可能である。またチャネル幅あたりのオフ電流（オフ電流をトランジスタのチャネル幅で除した値）を  $1 \times 10^{-23} \text{ A} / \mu\text{m}$  ( $10 \text{ yA} / \mu\text{m}$ ) から  $1 \times 10^{-22} \text{ A} / \mu\text{m}$  ( $100 \text{ yA} / \mu\text{m}$ ) 程度とすることが可能である。

20

#### 【0058】

また、成膜される酸化物半導体膜は、単結晶、多結晶（ポリクリスタルともいう。）または非晶質などの状態をとる。

30

#### 【0059】

好ましくは、酸化物半導体膜は、C AAC - OS ( C Axis Aligned Crystalline Oxide Semiconductor ) 膜とする。

#### 【0060】

C AAC - OS 膜は、完全な単結晶ではなく、完全な非晶質でもない。C AAC - OS 膜は、非晶質相に結晶部及び非晶質部を有する結晶 - 非晶質混相構造の酸化物半導体膜である。なお、当該結晶部は、一辺が 100 nm 未満の立方体内に収まる大きさが多い。また、透過型電子顕微鏡 ( TEM : Transmission Electron Microscope ) による観察像では、C AAC - OS 膜に含まれる非晶質部と結晶部との境界は明確ではない。また、TEM によって C AAC - OS 膜には粒界（グレインバウンダリーともいう。）は確認できない。そのため、C AAC - OS 膜は、粒界に起因する電子移動度の低下が抑制される。

40

#### 【0061】

C AAC - OS 膜に含まれる結晶部は、c 軸が C AAC - OS 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃い、かつ a b 面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c 軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、異なる結晶部間で、それぞれ a 軸及び b 軸の向きが異なっていてもよい。本明細書において、単に垂直と記載する場合、85° 以上 95° 以下の範囲も含まれることとする。また、単に平行と記載する場合、-5°

50

以上 5° 以下の範囲も含まれることとする。

#### 【 0 0 6 2 】

なお、 C A A C - O S 膜において、結晶部の分布が一様でなくてもよい。例えば、 C A A C - O S 膜の形成過程において、酸化物半導体膜の表面側から結晶成長させる場合、被形成面の近傍に対し表面の近傍では結晶部の占める割合が高くなることがある。また、 C A A C - O S 膜へ不純物を添加することにより、当該不純物添加領域において結晶部が非晶質化することもある。

#### 【 0 0 6 3 】

C A A C - O S 膜に含まれる結晶部の c 軸は、 C A A C - O S 膜の被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向に揃うため、 C A A C - O S 膜の形状（被形成面の断面形状または表面の断面形状）によっては互いに異なる方向を向くことがある。なお、結晶部の c 軸の方向は、 C A A C - O S 膜が形成されたときの被形成面の法線ベクトルまたは表面の法線ベクトルに平行な方向となる。結晶部は、成膜することにより、または成膜後に加熱処理などの結晶化処理を行うことにより形成される。

10

#### 【 0 0 6 4 】

C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

#### 【 0 0 6 5 】

以上がトランジスタ 126 の半導体層に用いる酸化物半導体についての説明である。

20

#### 【 0 0 6 6 】

図 1 (A) でも説明したように本実施の形態の構成では、図 1 (B) のトランジスタ 121 のチャネル長を L<sub>s</sub>、トランジスタ 126 のチャネル長を L<sub>o</sub>、とすると、 L<sub>s</sub> / L<sub>o</sub> 比を 1 / 3 以上 1 / 200 以下、好ましくは 1 / 6 乃至 1 / 20、とする。当該構成とすることで、トランジスタ 121 のチャネル長を微細化しても、トランジスタ 126 のチャネル長を大きくすることが可能な面積を確保することができる。そのためトランジスタ 126 は、十分小さいリーク電流となるトランジスタとすることができます。そして、半導体装置への電源の供給が停止しても、不揮発性記憶部内のデータの保持を行うことができる。

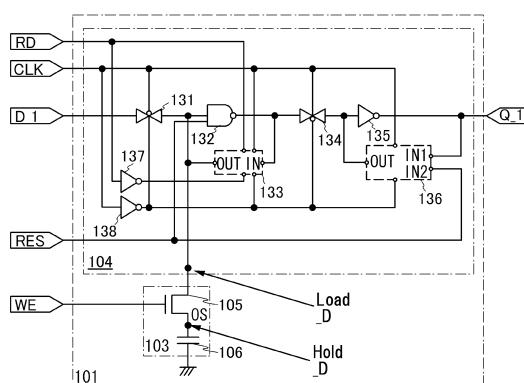

#### 【 0 0 6 7 】

次いで、図 1 (A) で示した揮発性記憶部 102 が具備するフリップフロップ 104 の具体的な回路構成について、図 2 に一例を示す。図 2 に示す例は、一段目のフリップフロップ 104 の回路構成とすることにより、電源の供給の停止及び復帰の際に、不揮発性記憶部 103 に保持したデータを誤動作なく、書き込み及び読み出しの制御を行うことができる。

30

#### 【 0 0 6 8 】

図 2 に示すフリップフロップ 104 は、アナログスイッチ 131、NAND 回路 132、論理回路 133、アナログスイッチ 134、インバータ回路 135、論理回路 136 で構成される。なお、図 2 に示すインバータ回路 137 及びインバータ回路 138 は、それぞれクロック信号 C L K 及び制御信号 R D の反転信号を生成するために設けられる回路であり、各段のフリップフロップ 104 に設けることを省略することも可能である。

40

#### 【 0 0 6 9 】

アナログスイッチ 131 は、データ D\_1 をフリップフロップ 104 に保持するために、クロック信号 C L K に同期してオンまたはオフが制御される回路である。アナログスイッチ 131 は、シリコンをチャネル領域に具備する p チャネル型トランジスタと、シリコンをチャネル領域に具備する n チャネル型トランジスタと、を組み合わせて構成すればよい。

#### 【 0 0 7 0 】

NAND 回路 132 は、リセット信号 R E S と、データ D\_1 または不揮発性記憶部に保持された信号または論理回路 133 より出力される信号との否定論理積を出力するための回路である。NAND 回路 132 は、シリコンをチャネル領域に具備する p チャネル型ト

50

ランジスタと、シリコンをチャネル領域に具備する n チャネル型トランジスタと、を組み合わせて構成すればよい。

【 0 0 7 1 】

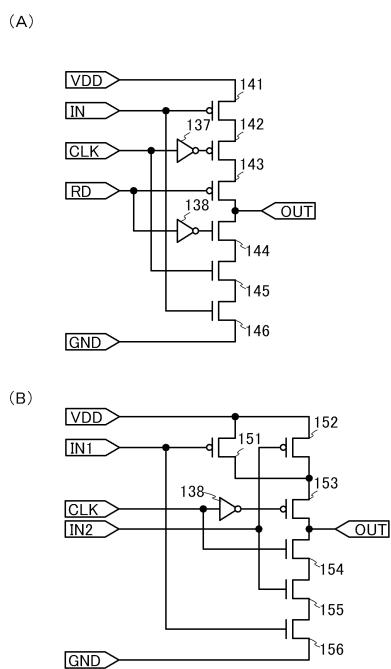

論理回路 133 は、NAND 回路 132 の出力信号が入力され、クロック信号 CLK 及び制御信号 RD に同期して反転信号を出力するための回路である。論理回路 133 の具体的な回路構成について図 3 ( A ) に示す。

【 0 0 7 2 】

図 3 ( A ) に示す論理回路 133 は、シリコンをチャネル領域に具備する p チャネル型トランジスタ 141、p チャネル型トランジスタ 142、及び p チャネル型トランジスタ 143、並びにシリコンをチャネル領域に具備する n チャネル型トランジスタ 144、n チャネル型トランジスタ 145、及び n チャネル型トランジスタ 146 を有する。10 論理回路 133 は、クロック信号 CLK が H レベル、制御信号 RD が L レベルの信号のとき、論理回路 133 はインバータ回路として機能する。また論理回路 133 は、クロック信号 CLK 及び制御信号 RD が共に H レベルまたは L レベルの信号のとき、またはクロック信号 CLK が L レベル、制御信号 RD が H レベルの信号のとき、ハイインピーダンスの状態となり、出力端子は電気的に浮遊状態となる。

【 0 0 7 3 】

アナログスイッチ 134 は、フリップフロップ 104 に保持されたデータを出力するために、クロック信号 CLK に同期してオンまたはオフが制御される回路である。20 なおアナログスイッチ 134 は、アナログスイッチ 131 と同時にオンしないように、クロック信号 CLK が入力される。アナログスイッチ 134 は、シリコンをチャネル領域に具備する p チャネル型トランジスタと、シリコンをチャネル領域に具備する n チャネル型トランジスタと、を組み合わせて構成すればよい。

【 0 0 7 4 】

インバータ回路 135 は、フリップフロップ 104 に保持された際に反転したデータ Data を再度反転して出力するための回路である。インバータ回路 135 は、シリコンをチャネル領域に具備する p チャネル型トランジスタと、シリコンをチャネル領域に具備する n チャネル型トランジスタと、を組み合わせて構成すればよい。

【 0 0 7 5 】

論理回路 136 は、インバータ回路 135 の出力信号と、リセット信号 RES との否定論理積を出力するための回路である。30 論理回路 136 の具体的な回路構成について図 3 ( B ) に示す。

【 0 0 7 6 】

図 3 ( B ) に示す論理回路 136 は、シリコンをチャネル領域に具備する p チャネル型トランジスタ 151、p チャネル型トランジスタ 152、及び p チャネル型トランジスタ 153、並びにシリコンをチャネル領域に具備する n チャネル型トランジスタ 154、n チャネル型トランジスタ 155、及び n チャネル型トランジスタ 156 を有する。40 論理回路 136 は、クロック信号 CLK が H レベルの信号のとき、論理回路 136 は NAND 回路として機能し、クロック信号 CLK が L レベルの信号のとき、ハイインピーダンスの状態となり、出力端子は電気的に浮遊状態となる。

【 0 0 7 7 】

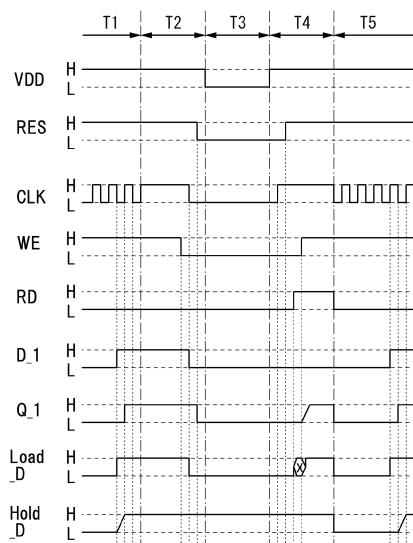

次いで、データ Data の保持時に電源の供給を停止して再び電源を供給する、図 2 で示した不揮発性フリップフロップ 101 の回路の駆動方法を説明する。図 4 は、電源停止前の通常動作 (期間 T1)、データバックアップ動作 (期間 T2)、電源停止時 (期間 T3)、データリカバリー動作 (期間 T4)、電源停止後の通常動作 (期間 T5) の各動作に分けて示したタイミングチャート図である。

【 0 0 7 8 】

なお図 4 のタイミングチャート図において、「Load\_D」は図 2 に示す不揮発性記憶部 103 に接続され、データの保持及び出力が行われる揮発性記憶部 102 内のノードである。また、「Hold\_D」は図 2 に示す不揮発性記憶部 103 内でデータの保持を行50

うノードである。

**【0079】**

なお各信号及びノードの電位は、高電源電位VDDに基づくHレベル(図中、Hで表記)の電位及び低電源電位GNDに基づくLレベル(図中、Lで表記)の電位で表すことができる。

**【0080】**

まず図4中の期間T1での動作について説明する。期間T1は、クロック信号CLKのトグル動作に応じて、データD\_1を不揮発性フリップフロップ101内のノードLoad\_Dに保持し、及び出力端子Q\_1より出力する。具体的に期間T1では、クロック信号CLKの立ち下がりに同期してノードLoad\_D及びノードHold\_DにデータD\_1を保持し、クロック信号CLKの立ち上がりに同期して出力端子Q\_1よりデータD\_1を出力する。また、期間T1では、高電源電位VDD側の電位をHレベルにして、不揮発性フリップフロップ101への電源の供給を行う。また期間T1では、リセット信号RESをHレベル、制御信号WEをHレベル、制御信号RDをLレベルにして各動作が行われる。

10

**【0081】**

期間T1では、制御信号WEを常にHレベルにしておき、トランジスタ105を常に導通状態としておく。当該構成とすることで、ノードHold\_Dの電位がデータD\_1に応じて切り替えることができ、データアッカアップ時におけるデータD\_1の保持をより確実に行うことができる。

20

**【0082】**

次いで図4中の期間T2の動作について説明する。期間T2は、ノードHold\_Dに保持したデータD\_1を保持しながら、各信号及び電源の供給を停止するデータバックアップ動作の期間である。期間T2では、クロック信号CLK、制御信号WE及びリセット信号RESをHレベル、制御信号RDをLレベルとする。そして、各信号の電位を順にLレベルにして、電源の供給を停止する。

**【0083】**

まず期間T2では、クロック信号をHレベルに固定した状態で、制御信号WEをLレベルに切り替える。そしてノードHold\_Dに保持されたデータD\_1の電位を固定する。次いで、データD\_1及びクロック信号をLレベルに切り替える。そしてノードLoad\_Dの電位をLレベルにする。次いで、リセット信号RESをLレベルに切り替える。そして出力端子Q\_1の電位をLレベルにする。最後に高電源電位VDDが供給される配線の電位をLレベルにして電源の供給を停止する。

30

**【0084】**

次いで図4中の期間T3について説明する。期間T3は、電源の供給を停止する期間である。期間T3では、各信号の電位はLレベルとすることができます。このとき、ノードHold\_Dに保持されたデータD\_1(図4ではHレベルの電位)が保持される。データD\_1の保持については、上述したように、酸化物半導体をチャネル領域に具備するトランジスタ105が、リーク電流が極めて小さいことを利用して実現することができる。

40

**【0085】**

次いで図4中の期間T4の動作について説明する。期間T4は、電源の供給を再開し、ノードHold\_Dに保持されたデータD\_1を揮発性記憶部102のフリップフロップ104に復帰させるデータリカバリー動作の期間である。期間T2では、電源の供給を復帰した後、クロック信号CLK、次いでリセット信号RES、次いで制御信号RDをHレベルにする。そしてノードLoad\_Dを電気的に浮遊状態(図4中、「X」で表記)とする。この浮遊状態にした後、制御信号WEをHレベルとし、ノードHold\_Dに保持されたデータD\_1をノードLoad\_Dに復帰させる。

**【0086】**

次いで図4中の期間T5の動作について説明する。期間T5は、電源停止後の通常動作をする期間である。具体的には、クロック信号CLKのトグル動作を再開させ、期間T1と

50

同様に、データD\_1を不揮発性フリップフロップ101内のノードL o a d \_ Dに保持、及び出力端子Q\_1より出力する。

#### 【0087】

以上が、図2で示した不揮発性フリップフロップ101の回路の駆動方法の説明である。

#### 【0088】

本実施の形態で示した半導体装置は、記憶回路に電源電圧が供給されない間は、揮発性記憶部に記憶されていたデータを、不揮発性記憶部に設けられた記憶ノードによって保持する構成とすることができます。特に本発明の半導体装置は、該構成において、シリコンをチャネル領域に具備するトランジスタと、酸化物半導体をチャネル領域に具備するトランジスタとを積層し、酸化物半導体をチャネル領域に具備するトランジスタのチャネル長は、シリコンをチャネル領域に具備するトランジスタのチャネル長よりも大きくする構成とすることを特徴とするものである。当該構成とすることで、リーク電流の極めて小さい酸化物半導体をチャネル領域に具備するトランジスタの電気的特性が大きく変化することなく、データの保持ができる不揮発性記憶部103とすることができます。

#### 【0089】

(実施の形態2)

本実施の形態では、実施の形態1で説明した半導体装置を構成する不揮発性記憶部103のトランジスタ105の構成について、別の構成を示し、説明する。

#### 【0090】

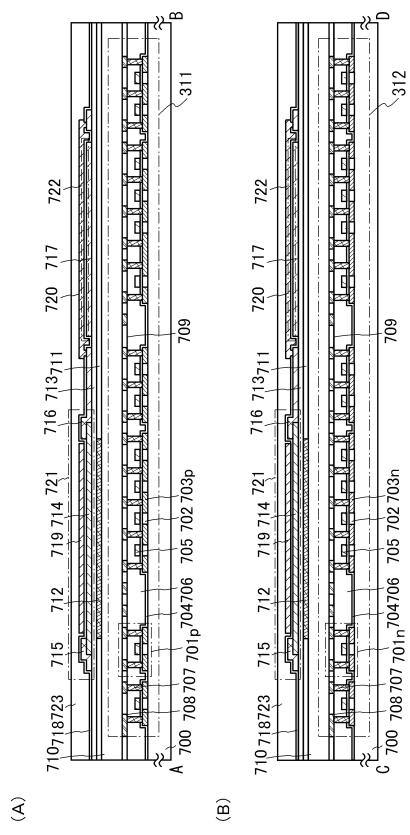

図5は、図2で示した回路図におけるトランジスタ105を、バックゲートを設けたトランジスタ105BGとし、当該トランジスタ105BGのバックゲートに、閾値電圧を制御するためのバックゲート電圧BGを入力する構成としたものである。

#### 【0091】

バックゲート電圧BGの電位を制御してトランジスタ105BGの閾値電圧を制御する構成とすることで、図5に示す不揮発性記憶部103は、制御信号WEによるトランジスタ105を非導通状態とする動作を、より確実に行うことができる。したがって本実施の形態の構成では、制御信号WEによるトランジスタ105BGを非導通状態にする動作により、トランジスタ105のリーク電流が極めて小さい状態であることを確保し、電源の供給がなくてもデータの論理状態に応じて電荷の保持を行うことができる。

#### 【0092】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

#### 【0093】

(実施の形態3)

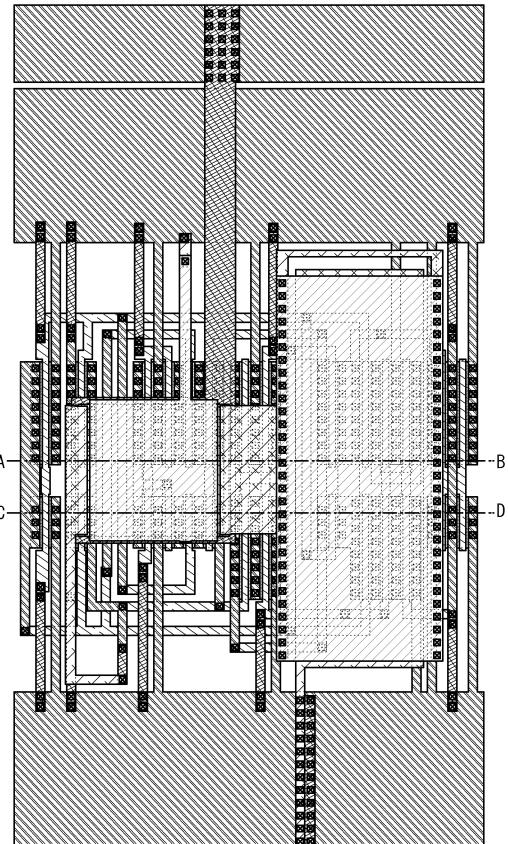

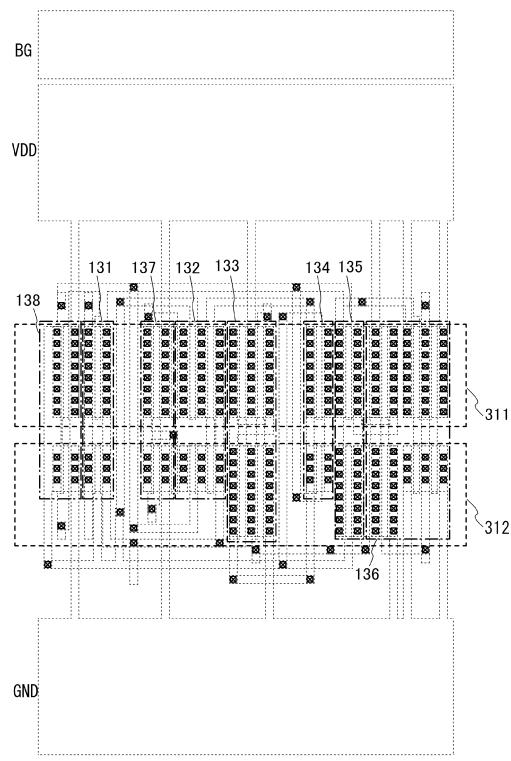

本実施の形態では、上記実施の形態2で説明した半導体装置を構成する揮発性記憶部102及び不揮発性記憶部103の各トランジスタを配置したレイアウト図について、具体的な例を示し、説明する。

#### 【0094】

図6は、図5で説明した回路図における各トランジスタを積層して配置した上面からのレイアウト図である。また図7では、揮発性記憶部102のフリップフロップ104を構成するシリコンをチャネル領域に具備する複数のトランジスタに着目し、図5における各回路との対応関係についてのみ図示したレイアウト図である。また図8(A)に示す断面図は、図6で示したレイアウト図における一点鎖線A-Bの断面図であり、図8(B)に示す断面図は、図6で示したレイアウト図における一点鎖線C-Dの断面図である。

#### 【0095】

なお図6及び図7では、主要な配線、シリコンで形成される半導体層、及び酸化物半導体で形成される半導体層のみを示し、絶縁膜等は省略してある。

#### 【0096】

図6では、シリコンで形成される半導体層301、配線層302、配線層303、開口部304、配線層305、酸化物半導体で形成される半導体層306、配線層307及び配

10

20

30

40

50

線層 308 のレイアウトを示している。なお配線層 302 は、図 2 におけるフリップフロップ 104 のトランジスタにおけるゲート電極層を含む配線層として機能する。なお配線層 303 は、図 2 におけるフリップフロップ 104 のトランジスタにおけるソース電極及びドレイン電極を含む配線層として機能する。なお開口部 304 は、積層して設けられた上層と下層の配線層または半導体層を電気的に接続するものとして示している。なお配線層 305 は、図 2 におけるトランジスタ 105BG におけるバックゲート電極を含む配線層として機能する。なお配線層 307 は、図 2 におけるトランジスタ 105BG におけるソース電極及びドレイン電極を含む配線層として機能する。なお配線層 308 は、図 5 におけるトランジスタ 105BG におけるゲート電極を含む配線層として機能する。

## 【0097】

10

図 7 では、図 6 で示した半導体層 301、配線層 302、配線層 303、開口部 304 を点線で表し、図 5 における各回路と対応関係にある領域に対し同じ符号を付している。また図 7 中、配線層に供給される電位として、VDD、GND 及びバックゲート電圧 BG を示しており、VDD 及びバックゲート電圧 BG が供給される配線側に、揮発性記憶部 102 のフリップフロップ 104 を構成する p チャネル型トランジスタ（図 7 中、領域 311）が並んで設けられ、GND が供給される配線側に、揮発性記憶部 102 のフリップフロップ 104 を構成する n チャネル型トランジスタ（図 7 中、領域 312）が並んで設けられている。

## 【0098】

20

また、図 8 (A) に示す断面図では、領域 311 に複数の p チャネル型トランジスタ 701p が設けられる様子を示している。また、図 8 (A) に示す断面図では、p チャネル型トランジスタ 701p の上層に、酸化物半導体をチャネル領域に具備するトランジスタ 721 及び容量素子 722 が設けられる様子を示している。

## 【0099】

ここで p チャネル型トランジスタ 701p の構成について説明する。p チャネル型トランジスタ 701p は、基板 700 上に p 型不純物領域 703p を含むシリコンで形成された島状の半導体層 702 と、ゲート絶縁層 704 と、ゲート電極 705 と、層間絶縁層 706 に形成された開口部に埋め込まれた配線層 707 と、絶縁層 709 に形成された開口部に埋め込まれた配線層 708 を有する。

## 【0100】

30

また酸化物半導体をチャネル領域に具備するトランジスタ 721 及び容量素子 722 の構成について説明する。なおトランジスタ 721 及び容量素子 722 は層間絶縁層 723 に覆われて設けられており、当該層間絶縁層に形成される配線層を介して、さらに上層の配線層に接続される構成を取り得るが、ここでは説明を省略する。

## 【0101】

トランジスタ 721 は、p チャネル型トランジスタ 701p 上の絶縁層 710 を含む配線層（配線となる導電層は図示せず）上に、絶縁層 711 に形成された開口部に埋め込まれたバックゲート電極 712 と、絶縁膜 713 と、絶縁膜 713 上に形成された酸化物半導体を具備する半導体層 714 と、半導体層 714 の両端に形成されたソース電極またはドレイン電極として機能する配線層 715 及び配線層 716 と、ゲート絶縁層 718 と、ゲート電極 719 と、を有する。

40

## 【0102】

容量素子 722 は、配線層 715 及び配線層 716 と同層に形成される、一方の電極として機能する配線層 717 と、ゲート絶縁層 718 と、ゲート電極 719 と同層に形成される、他方の電極として機能する配線層 720 と、を有する。

## 【0103】

また、図 8 (B) に示す断面図では、領域 312 に複数の n チャネル型トランジスタ 701n が設けられる様子を示している。また、図 8 (B) に示す断面図では、n チャネル型トランジスタ 701n の上層に、酸化物半導体をチャネル領域に具備するトランジスタ 721 及び容量素子 722 が設けられる様子を示している。

50

**【 0 1 0 4 】**

図 8 ( B ) に示す断面図が図 8 ( A ) と異なる点は、基板 7 0 0 上の島状の半導体層 7 0 2 が有する不純物領域が n 型不純物領域 7 0 3 n に変わった点のみであり、そのほかの構成については、図 8 ( A ) での構成と同様である。

**【 0 1 0 5 】**

図 6 乃至図 8 から、揮発性記憶部 1 0 2 のフリップフロップ 1 0 4 を構成するトランジスタは、高速に動作させる必要があるためチャネル長が小さいことがわかる。加えて図 6 乃至図 8 から、フリップフロップ等の機能を実現するためのトランジスタ数が多いことがわかる。

**【 0 1 0 6 】**

一方で不揮発性記憶部 1 0 3 を構成する、不揮発性記憶部 1 0 3 のトランジスタ 1 0 5 及び容量素子 1 0 6 は、上記実施の形態 1 でも説明したように、各素子の占有面積を大きくして設けることができる。具体的には、トランジスタ 1 0 5 ではチャネル長の大きいトランジスタとし、容量素子 1 0 6 では、対向する電極の面積を大きくとることができる。そのため、リーク電流の極めて小さい酸化物半導体をチャネル領域に具備するトランジスタの電気的特性が大きく変化することなく、データの一時的な保持ができる不揮発性記憶部 1 0 3 とすることができます。

**【 0 1 0 7 】**

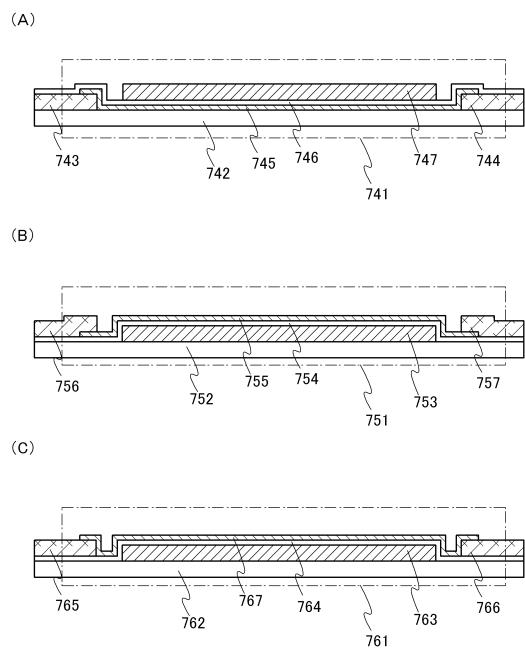

また、本実施の形態の構成において、図 8 に示す、酸化物半導体をチャネル領域に具備するトランジスタ 7 2 1 の各構成の積層順序は、他の構成とすることもできる。例えば、図 9 ( A ) に示すトランジスタ 7 4 1 のような積層順序としても良い。トランジスタ 7 4 1 は、絶縁膜 7 4 2 上に設けられたソース電極およびドレイン電極として機能する配線層 7 4 3 及び配線層 7 4 4 と、配線層 7 4 3 及び配線層 7 4 4 の上面および側面と接するように設けられた半導体層 7 4 5 と、半導体層 7 4 5 上に設けられたゲート絶縁層 7 4 6 と、半導体層 7 4 5 と重畠してゲート絶縁層 7 4 6 上に設けられたゲート電極 7 4 7 と、有する。つまり、トランジスタ 7 4 1 は、半導体層 7 4 5 が配線層 7 4 3 及び配線層 7 4 4 の上面および側面と接するように設けられている点において、トランジスタ 7 2 1 と異なる。

**【 0 1 0 8 】**

また、図 9 ( B ) に示すトランジスタ 7 5 1 のような積層順序としても良い。トランジスタ 7 5 1 は、絶縁膜 7 5 2 上に設けられたゲート電極 7 5 3 と、ゲート電極 7 5 3 上に設けられたゲート絶縁層 7 5 4 と、ゲート絶縁層 7 5 4 上に設けられた半導体層 7 5 5 と、半導体層 7 5 5 の上面および側面と接するように設けられたソース電極およびドレイン電極として機能する配線層 7 5 6 及び配線層 7 5 7 と、を有する。つまり、トランジスタ 7 5 1 は、ゲート電極 7 5 3 とゲート絶縁層 7 5 4 が半導体層 7 5 5 の下に設けられた、ボトムゲート構造である点において、トランジスタ 7 2 1 と異なる。

**【 0 1 0 9 】**

また、図 9 ( C ) に示すトランジスタ 7 6 1 のような積層順序としても良い。トランジスタ 7 6 1 は、絶縁膜 7 6 2 上に設けられたゲート電極 7 6 3 と、ゲート電極 7 6 3 上に設けられたゲート絶縁層 7 6 4 と、ゲート絶縁層 7 6 4 上に設けられたソース電極およびドレイン電極として機能する配線層 7 6 5 及び配線層 7 6 6 と、配線層 7 6 5 及び配線層 7 6 6 の上面および側面と接するように設けられた半導体層 7 6 7 と、を有する。つまり、トランジスタ 7 6 1 は、ゲート電極 7 6 3 とゲート絶縁層 7 6 4 が半導体層 7 6 7 の下に設けられた、ボトムゲート構造である点において、トランジスタ 7 2 1 と異なる。

**【 0 1 1 0 】**

以上説明したように、本実施の形態における、酸化物半導体をチャネル領域に具備するトランジスタは、様々な積層順序のトランジスタの構成をとることができます。

**【 0 1 1 1 】**

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

**【 0 1 1 2 】**

10

20

30

40

50

(実施の形態 4 )

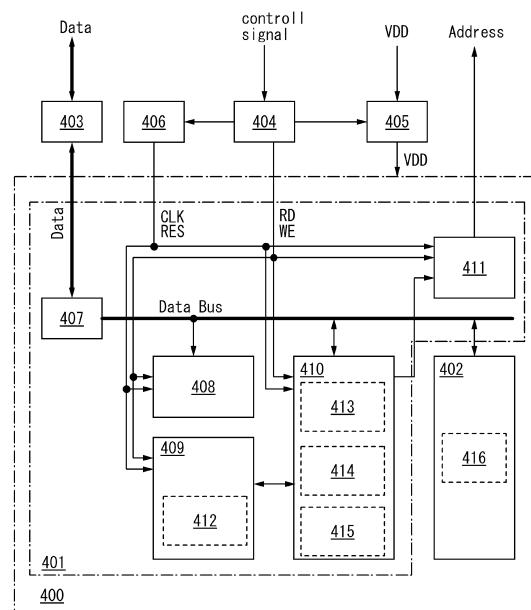

上記実施の形態で説明した半導体装置を C P U として機能させる場合の、具体的な一形態について説明する。図 10 には、C P U 及びその周辺回路のブロック図の一例を示す。

【 0 1 1 3 】

C P U 4 0 0 は、制御装置部 4 0 1 と、演算装置部 4 0 2 を有する。また図 10 では、C P U 4 0 0 の周辺回路として、データバッファ回路 4 0 3 、電源制御回路 4 0 4 、電源切り替え回路 4 0 5 、及び内部制御信号生成回路 4 0 6 を示している。

【 0 1 1 4 】

制御装置部 4 0 1 は、データラッチ回路 4 0 7 、命令レジスタ回路 4 0 8 、コントロール回路 4 0 9 、レジスタ群 4 1 0 、及びアドレスバッファ回路 4 1 1 を有する。コントロール回路 4 0 9 は、ステートマシーン 4 1 2 を有する。またレジスタ群 4 1 0 は、プログラムカウンタ 4 1 3 、汎用レジスタ回路 4 1 4 、及び演算レジスタ回路 4 1 5 を有する。また演算装置部 4 0 2 は、A L U 4 1 6 ( A r i t h m e t i c l o g i c u n i t ) を有する。

【 0 1 1 5 】

C P U 及びその周辺回路の各回路は、データバスの他、アドレスバス、コントロールバスを介して、データ、アドレス、制御信号の入出力を行う。なお図 10 ではデータバスを太線、コントロールバスを細線で表し、アドレスバスを省略して示している。

【 0 1 1 6 】

データバッファ回路 4 0 3 は、制御装置部 4 0 1 に入出力される命令（プログラム）を含むデータを一時的に記憶しておく緩衝記憶回路である。電源制御回路 4 0 4 は、外部より入力される制御信号に応じて電源切り替え回路 4 0 5 における電源の供給の制御を行い、且つ制御装置部 4 0 1 の各回路が具備する不揮発性フリップフロップで構成されるレジスタ回路を制御するための制御信号 R D 及び制御信号 W E を出力する回路である。電源切り替え回路 4 0 5 は、外部より入力される電源を電源制御回路 4 0 4 の制御に応じて供給するか否か切り替える回路である。内部制御信号生成回路 4 0 6 は、電源制御回路 4 0 4 の制御に応じて制御装置部 4 0 1 の各回路が具備する不揮発性フリップフロップで構成されるレジスタ回路を制御するためのクロック信号 C L K 及びリセット信号 R E S を出力する回路である。

【 0 1 1 7 】

データラッチ回路 4 0 7 は、制御装置部 4 0 1 に入出力される命令（プログラム）を含むデータを一時的に記憶して、データバスを介して、選択的に制御装置部 4 0 1 の各回路に供給する回路である。命令レジスタ回路 4 0 8 は、制御装置部 4 0 1 に送られる命令のデータを一時的に記憶しておく回路である。コントロール回路 4 0 9 は、入力された命令をデコードし、制御装置部 4 0 1 の各回路に実行させる機能を有する。またコントロール回路 4 0 9 のステートマシーン 4 1 2 は、制御装置部 4 0 1 の状態を一時的に記憶しておく回路である。レジスタ群 4 1 0 のプログラムカウンタ 4 1 3 は、次に実行する命令のアドレスを記憶する回路である。レジスタ群 4 1 0 の汎用レジスタ回路 4 1 4 は、外部の主記憶装置から読み出されたデータを一時的に記憶しておく回路である。レジスタ群 4 1 0 の演算レジスタ回路 4 1 5 は、A L U 4 1 6 の演算処理の途中で得られたデータを一時的に記憶しておく回路である。アドレスバッファ回路 4 1 1 は、次に実行する命令のアドレスを一時的に記憶しておく、外部の主記憶装置に出力する回路である。演算装置部 4 0 2 の A L U 4 1 6 は、四則演算、論理演算などの各種演算処理を行う機能を有する。

【 0 1 1 8 】

次いで、C P U 4 0 0 の動作について説明する。

【 0 1 1 9 】

C P U 4 0 0 は、プログラムカウンタ 4 1 3 の複数のスタックのうち、実行する命令のアドレスに従い、主記憶装置の対応するアドレスにアドレスバッファ回路 4 1 1 を介してアクセスする。そして外部の主記憶装置から命令を読み出し、命令レジスタ回路 4 0 8 に記憶させる。

10

20

30

40

50

## 【0120】

CPU400は、命令レジスタ回路408に記憶されている命令をデコードし、命令を実行する。具体的には、デコードされた命令が演算処理を行う命令であれば、コントロール回路409が、デコードされた命令に従ってALU416の動作を制御するための各種信号を生成する。ALU416は、汎用レジスタ回路414に記憶されたデータを用いて演算処理を行い、演算処理で得られたデータを汎用レジスタ回路414または演算レジスタ回路415に一時的に記憶する。デコードされた命令が、データの格納や読み出しの場合には、外部の主記憶装置やレジスタ群410の各回路へ適宜アクセスする。

## 【0121】

なお、図10に示すCPU400では、制御装置部401の命令レジスタ回路408、コントロール回路409、レジスタ群410、及びアドレスバッファ回路411のデータを一時的に記憶する回路内に、上記実施の形態で説明した不揮発性フリップフロップで構成されるレジスタ回路を有する。すなわち、制御装置部401の命令レジスタ回路408、コントロール回路409、レジスタ群410、及びアドレスバッファ回路411のデータは、電源の供給が停止しても消去されず、再度電源を供給した際にデータを復元した状態に戻すことができる。そのため、CPU400内でのデータの再度の読み出しが、電源の供給が必要ない場合の消費電力の低減を図ることができる。10

## 【0122】

特に、上記実施の形態で説明した不揮発性フリップフロップでは、リーク電流の極めて小さい酸化物半導体をチャネル領域に具備するトランジスタの電気的特性が大きく変化することなく、データの一時的な保持が可能なCPUとすることができる。20

## 【0123】

本実施の形態は、上記実施の形態と適宜組み合わせて実施することが可能である。

## 【符号の説明】

## 【0124】

|           |              |    |

|-----------|--------------|----|

| T 1       | 期間           | 30 |

| T 2       | 期間           |    |

| T 3       | 期間           |    |

| T 4       | 期間           |    |

| T 5       | 期間           |    |

| 1 0 0     | 半導体装置        | 40 |

| 1 0 1     | 不揮発性フリップフロップ |    |

| 1 0 2     | 揮発性記憶部       |    |

| 1 0 3     | 不揮発性記憶部      |    |

| 1 0 4     | フリップフロップ     |    |

| 1 0 5     | トランジスタ       |    |

| 1 0 5 B G | トランジスタ       |    |

| 1 0 6     | 容量素子         |    |

| 1 1 1     | 素子層          |    |

| 1 1 2     | 素子層          |    |

| 1 1 3     | 配線層          | 50 |

| 1 1 4     | 配線層          |    |

| 1 2 0     | 素子分離層        |    |

| 1 2 1     | トランジスタ       |    |

| 1 2 2     | 半導体層         |    |

| 1 2 3     | 導電層          |    |

| 1 2 4     | 導電層          |    |

| 1 2 5     | 導電層          |    |

| 1 2 6     | トランジスタ       |    |

| 1 2 7     | 容量素子         |    |

|       |               |    |

|-------|---------------|----|

| 1 2 8 | 半導体層          |    |

| 1 2 9 | 導電層           |    |

| 1 3 0 | 導電層           |    |

| 1 3 1 | アナログスイッチ      |    |

| 1 3 2 | N A N D 回路    |    |

| 1 3 3 | 論理回路          |    |

| 1 3 4 | アナログスイッチ      |    |

| 1 3 5 | インバータ回路       |    |

| 1 3 6 | 論理回路          |    |

| 1 3 7 | インバータ回路       | 10 |

| 1 3 8 | インバータ回路       |    |

| 1 4 1 | p チャネル型トランジスタ |    |

| 1 4 2 | p チャネル型トランジスタ |    |

| 1 4 3 | p チャネル型トランジスタ |    |

| 1 4 4 | n チャネル型トランジスタ |    |

| 1 4 5 | n チャネル型トランジスタ |    |

| 1 4 6 | n チャネル型トランジスタ |    |

| 1 5 1 | p チャネル型トランジスタ |    |

| 1 5 2 | p チャネル型トランジスタ |    |

| 1 5 3 | p チャネル型トランジスタ | 20 |

| 1 5 4 | n チャネル型トランジスタ |    |

| 1 5 5 | n チャネル型トランジスタ |    |

| 1 5 6 | n チャネル型トランジスタ |    |

| 3 0 1 | 半導体層          |    |

| 3 0 2 | 配線層           |    |

| 3 0 3 | 配線層           |    |

| 3 0 4 | 開口部           |    |

| 3 0 5 | 配線層           |    |

| 3 0 6 | 半導体層          |    |

| 3 0 7 | 配線層           | 30 |

| 3 0 8 | 配線層           |    |

| 3 1 1 | 領域            |    |

| 3 1 2 | 領域            |    |

| 4 0 0 | C P U         |    |

| 4 0 1 | 制御装置部         |    |

| 4 0 2 | 演算装置部         |    |

| 4 0 3 | データバッファ回路     |    |

| 4 0 4 | 電源制御回路        |    |

| 4 0 5 | 回路            |    |

| 4 0 6 | 内部制御信号生成回路    | 40 |

| 4 0 7 | データラッチ回路      |    |

| 4 0 8 | 命令レジスタ回路      |    |

| 4 0 9 | コントロール回路      |    |

| 4 1 0 | レジスタ群         |    |

| 4 1 1 | アドレスバッファ回路    |    |

| 4 1 2 | ステートマシーン      |    |

| 4 1 3 | プログラムカウンタ     |    |

| 4 1 4 | 汎用レジスタ回路      |    |

| 4 1 5 | 演算レジスタ回路      |    |

| 4 1 6 | A L U         | 50 |

|         |               |    |

|---------|---------------|----|

| 7 0 0   | 基板            |    |

| 7 0 1 n | n チャネル型トランジスタ |    |

| 7 0 1 p | p チャネル型トランジスタ |    |

| 7 0 2   | 半導体層          |    |

| 7 0 3 n | n 型不純物領域      |    |

| 7 0 3 p | p 型不純物領域      |    |

| 7 0 4   | ゲート絶縁層        |    |

| 7 0 5   | ゲート電極         |    |

| 7 0 6   | 層間絶縁層         |    |

| 7 0 7   | 配線層           | 10 |

| 7 0 8   | 配線層           |    |

| 7 0 9   | 絶縁層           |    |

| 7 1 0   | 絶縁層           |    |

| 7 1 1   | 絶縁層           |    |

| 7 1 2   | バックゲート電極      |    |

| 7 1 3   | 絶縁膜           |    |

| 7 1 4   | 半導体層          |    |

| 7 1 5   | 配線層           |    |

| 7 1 6   | 配線層           |    |

| 7 1 7   | 配線層           | 20 |

| 7 1 8   | ゲート絶縁層        |    |

| 7 1 9   | ゲート電極         |    |

| 7 2 0   | 配線層           |    |

| 7 2 1   | トランジスタ        |    |

| 7 2 2   | 容量素子          |    |

| 7 2 3   | 層間絶縁層         |    |

| 7 4 1   | トランジスタ        |    |

| 7 4 2   | 絶縁膜           |    |

| 7 4 3   | 配線層           |    |

| 7 4 4   | 配線層           | 30 |

| 7 4 5   | 半導体層          |    |

| 7 4 6   | ゲート絶縁層        |    |

| 7 4 7   | ゲート電極         |    |

| 7 5 1   | トランジスタ        |    |

| 7 5 2   | 絶縁膜           |    |

| 7 5 3   | ゲート電極         |    |

| 7 5 4   | ゲート絶縁層        |    |

| 7 5 5   | 半導体層          |    |

| 7 5 6   | 配線層           |    |

| 7 5 7   | 配線層           | 40 |

| 7 6 1   | トランジスタ        |    |

| 7 6 2   | 絶縁膜           |    |

| 7 6 3   | ゲート電極         |    |

| 7 6 4   | ゲート絶縁層        |    |

| 7 6 5   | 配線層           |    |

| 7 6 6   | 配線層           |    |

| 7 6 7   | 半導体層          |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

■~301 □~302 □~303 ■~304 ■~305 □~306 □~307 □~308

【図7】

【図8】

【図9】

【図10】

---

フロントページの続き

| (51)Int.Cl.             | F I                              |

|-------------------------|----------------------------------|

| H 01 L 21/822 (2006.01) | H 01 L 27/10 6 8 1 F             |

| H 01 L 27/04 (2006.01)  | H 01 L 27/10 4 6 1               |

| H 03 K 3/356 (2006.01)  | H 01 L 27/04 C<br>H 03 K 3/356 D |

(56)参考文献 特開2011-171723(JP,A)

特開2010-141230(JP,A)

特開2009-135350(JP,A)

特開2011-228679(JP,A)

米国特許出願公開第2011/0176357(US,A1)

国際公開第2011/089847(WO,A1)

米国特許出願公開第2010/0148171(US,A1)

特開2011-192958(JP,A)

特開2011-211185(JP,A)

## (58)調査した分野(Int.Cl., DB名)

H 01 L 27 / 105

H 01 L 21 / 822

H 01 L 21 / 8242

H 01 L 27 / 04

H 01 L 27 / 10

H 01 L 27 / 108

H 01 L 29 / 786

H 03 K 3 / 356