(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5955323号

(P5955323)

(45) 発行日 平成28年7月20日(2016.7.20)

(24) 登録日 平成28年6月24日(2016.6.24)

(51) Int.Cl.

G06F 12/00 (2006.01)

F 1

G 06 F 12/00 5 6 4 C

請求項の数 20 (全 23 頁)

(21) 出願番号 特願2013-529258 (P2013-529258)

(86) (22) 出願日 平成23年9月13日 (2011.9.13)

(65) 公表番号 特表2013-543612 (P2013-543612A)

(43) 公表日 平成25年12月5日 (2013.12.5)

(86) 國際出願番号 PCT/US2011/051345

(87) 國際公開番号 WO2012/037086

(87) 國際公開日 平成24年3月22日 (2012.3.22)

審査請求日 平成26年8月19日 (2014.8.19)

(31) 優先権主張番号 12/910,412

(32) 優先日 平成22年10月22日 (2010.10.22)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 61/382,089

(32) 優先日 平成22年9月13日 (2010.9.13)

(33) 優先権主張国 米国(US)

(73) 特許権者 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVICES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンディベール、ビイ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・プレイス、メイル・ストップ

・68 (番地なし)

(74) 代理人 100108833

弁理士 早川 裕司

(74) 代理人 100111615

弁理士 佐野 良太

最終頁に続く

(54) 【発明の名称】構成可能な電力状態をもつダイナミックRAMPHYインターフェース

## (57) 【特許請求の範囲】

## 【請求項1】

メモリデバイスのための物理メモリインターフェースを制御するための方法であって、

第1および第2の電力コンテキストを格納することと、

前記メモリデバイスからのデータ読み取りおよび前記メモリデバイスへのデータ書き込みの

ためにタイミング遅延を提供するように構成された複数の調整可能な遅延素子を提供する

ことであって、各調整可能な遅延素子が、前記第1および第2の電力コンテキストのうち

の選択された1つに応答する遅延時間を有する、複数の調整可能な遅延素子を提供すること、

電力コンテキスト変更要求を受信することと、

前記電力コンテキスト変更要求に基づいて、前記第1および第2の電力コンテキストの

うちの1つを選択することと

を含む方法。

## 【請求項2】

前記第1および第2の電力コンテキストのうちの1つを選択する前に、前記メモリデバ

イスに関連したセルフリフレッシュモードを選択するように構成されたセルフリフレッシュ

出力を生成することをさらに含む、請求項1に記載の方法。

## 【請求項3】

前記第1の電力コンテキストを格納するように構成された第1のセットのレジスタを提

供することと、

前記第2の電力コンテキストを格納するように構成された第2のセットのレジスタを提供することと、

前記電力コンテキスト変更要求に応答して、前記第1および前記第2のセットのレジスタのうちの1つを選択することと

をさらに含む、請求項1に記載の方法。

【請求項4】

前記電力コンテキスト変更要求に応答して、前記物理インターフェースの少なくとも1つのドライバに対する選択可能なドライブ強度を調整することをさらに含む、請求項1に記載の方法。

【請求項5】

前記電力コンテキスト変更要求に応答して、前記物理インターフェースの少なくとも1つの受信器に対する選択可能な終端インピーダンスを調整することをさらに含む、請求項1に記載の方法。

【請求項6】

第1のメモリトレーニング段階を経て前記第1の電力コンテキストを生成することと、

第2のメモリトレーニング段階を経て前記第2の電力コンテキストを生成することとを

さらに含む、請求項1に記載の方法。

【請求項7】

電力制御インターフェース(ACPI)S3電力状態から復帰すると、前記第1および第2の電力コンテキストのうちの少なくとも1つを復元することをさらに含む、請求項1に記載の方法。

【請求項8】

前記第1および第2の電力コンテキストをサウスブリッジ上のメモリ位置から取り出す

ことをさらに含む、請求項1に記載の方法。

【請求項9】

前記第1および第2の電力コンテキストをノースブリッジ上のメモリ位置から取り出す

ことをさらに含む、請求項1に記載の方法。

【請求項10】

メモリデバイスのための物理メモリインターフェースであって、

第1の電力コンテキストおよび第2の電力コンテキストを受信するように構成された複

数のレジスタと、

前記第1および第2の電力コンテキストのうちの1つを選択するように構成された選択

回路と、

前記メモリデバイスからのデータ読み取りおよび前記メモリデバイスへのデータ書き込みの

ためにタイミング遅延を提供するように構成された複数の調整可能な遅延素子であって、

各調整可能な遅延素子が、前記第1および第2の電力コンテキストのうちの前記選択され

た1つに応答する遅延時間を有する、複数の調整可能な遅延素子と

を含む、物理メモリインターフェース。

【請求項11】

前記選択回路が、前記第1および第2の電力コンテキストのうちの前記選択された1つ

をメモリ位置から取り出す、請求項10に記載の物理メモリインターフェース。

【請求項12】

前記第1の電力コンテキストを格納するように構成された第1のセットのレジスタと、

前記第2の電力コンテキストを格納するように構成された第2のセットのレジスタとを

さらに含み、

前記選択回路が前記第1と第2のセットのレジスタとの間で選択するように構成されて

いる、請求項10に記載の物理メモリインターフェース。

【請求項13】

各々が、前記第1および第2の電力コンテキストのうちの前記選択された1つに応答して

選択可能なドライブ強度を有する、複数のドライバをさらに含む、請求項10に記載の

10

20

30

40

50

物理メモリインタフェース。

【請求項 14】

各々が前記第1および第2の電力コンテキストのうちの前記選択された1つに応答して選択可能な終端インピーダンスを有する複数の受信器をさらに含む、請求項10に記載の物理メモリインタフェース。

【請求項 15】

前記第1の電力コンテキストが第1のメモリトレーニング段階を経て決定され、かつ、前記第2の電力コンテキストが第2のメモリトレーニング段階を経て決定される、請求項10に記載の物理メモリインタフェース。

【請求項 16】

物理メモリデバイスの複数のチャネルのためのインタフェースをさらに含む、請求項10に記載の物理メモリインタフェース。

10

【請求項 17】

前記物理メモリインタフェースが、中央処理装置(CPU)のダイ上に配置されている、請求項10に記載の物理メモリインタフェース。

【請求項 18】

電力制御インタフェース(ACPI)S3電力状態から復帰すると、前記第1および第2の電力コンテキストのうちの少なくとも1つを取り出すように構成されたメモリインタフェースをさらに含む、請求項10に記載の物理メモリインタフェース。

【請求項 19】

前記第1および第2の電力コンテキストをメモリ位置からロードするように構成されたメモリインタフェースをさらに含む、請求項10に記載の物理メモリインタフェース。

20

【請求項 20】

前記物理メモリインタフェースに結合されたメモリデバイスをさらに含み、前記メモリデバイスが、前記第1および第2の電力コンテキストのうちの前記選択された1つに関連する前記タイミング遅延を用いて、データの読み取りおよび書き込みのために構成されている、請求項10に記載の物理メモリインタフェース。

【発明の詳細な説明】

【技術分野】

【0001】

30

本発明は、ダイナミックランダムアクセスメモリ(DRAM)デバイスと直接インタフェースをとる物理層を含むメモリサブシステムに関する。

【0002】

〔関連出願の相互参照〕

本願は、2010年9月13日に出願された、米国仮出願第61/382,089号、および2010年10月22日に出願された、米国非仮出願第12/910,412号の利益を主張し、それらは、本明細書中に完全に明記されているかのように、参照により組み込まれる。

【背景技術】

【0003】

40

典型的なメモリシステムは、メモリコントローラとメモリデバイスとの間でデータを伝送するために、非同期クロック方式または同期クロック方式のいずれかを使用する。同期クロックは、メモリデバイスが、制御入力に応答する前にクロック信号を待ち、従って、コンピュータのシステムバスと同期されることを意味する。同期ダイナミックランダムアクセスメモリ(SDRAM)は、通常非同期メモリデバイスよりも高いクロック速度をサポートするので、幅広く使用される。

【0004】

ダブルデータレート(DDR)SDRAMは、クロック信号の立ち上がりエッジおよび立ち下がりエッジの両方でデータを伝送する。かかるメモリデバイスは、より低いクロック周波数を使用するが、電気データおよびクロック信号のタイミングの厳格な制御を必要

50

とする。かかるデバイスの第1のバージョン(DDR1)は、同じクロック周波数で動作するシングルデータレート(SDR)SDRAMの帯域幅のほぼ2倍を達成した。DDR2およびDDR3 SDRAMデバイスは、DDR1デバイスに関する後続の改善である。どのタイプのDDRメモリが使用されているか(DDR1/DDR2/DDR3)に関わらず、物理インターフェース(Phy)が、メモリコントローラとDDR SDRAMデバイスとの間に直接結合される。Phyインターフェースは、一般に、DDR SDRAMデータストローブのタイミング要件を処理するための回路機構を含む。典型的なPhyインターフェースの実装は、メモリ性能レベルまたは要求される電力を迅速に調整するための機構を提供しない。

【発明の概要】

10

【課題を解決するための手段】

【0005】

物理メモリインターフェース(Phy)が提供される。Phyは、メモリコントローラと物理メモリデバイスとの間のインターフェースをとる。Phyインターフェースは、第1の電力コンテキストおよび第2の電力コンテキストを受信するように構成されたコマンドおよび状態レジスタ(CSR)を含む。選択回路が提供される。選択回路は、第1と第2の電力コンテキストの間で切り替えるように構成される。Phyインターフェースは、複数の調整可能な遅延素子を含み、各々が、選択された電力コンテキストに応答する遅延時間有する。電力コンテキスト間での切替えは、1つまたは複数の調整可能な遅延素子の調整という結果になる。

20

【0006】

別の実施形態では、Phyインターフェースは、第1の電力コンテキストを格納するように構成された第1のセットのCSRおよび第2の電力コンテキストを格納するように構成された第2のセットのCSRを含む。Phyインターフェースは、各々が、選択された電力コンテキストに応答する選択可能なドライブ強度を有する複数のドライバも含む。Phyインターフェースは、各々が、選択された電力コンテキストに応答する選択可能な終端インピーダンスを有する複数の受信器も含む。電力コンテキスト間での切替えは、1つまたは複数のドライバ/受信器のドライブ強度および/または終端インピーダンスの調整という結果になり得る。

【0007】

30

第1および第2の電力コンテキストは、BIOSトレーニング手順を経て決定され得る。かかる手順は、複数の段階をもち得る。例えば、第1の電力コンテキストは、第1のメモリトレーニング段階を経て決定され得、第2の電力コンテキストは、第2のメモリトレーニング段階を経て決定され得る。

【0008】

Phyインターフェースは、CSRへの読み取り/書き込みアクセスを可能にするように構成されている構成バスを含み得る。Phyインターフェースは、物理メモリデバイスの複数のチャネルをサポートするようにも構成され得る。Phyインターフェースは、中央処理装置(CPU)のダイ上を含め、様々な場所に配置され得る。

【図面の簡単な説明】

40

【0009】

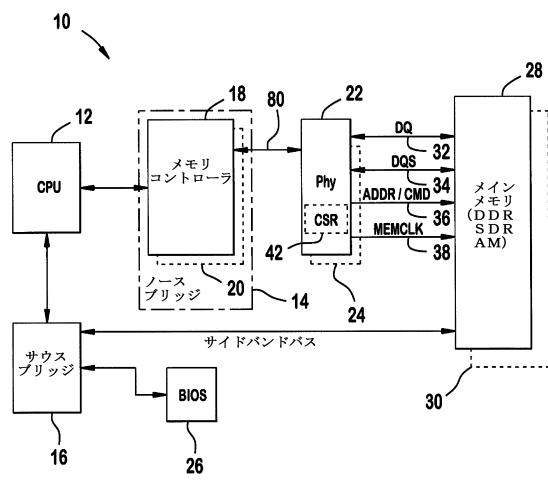

【図1】典型的なコンピュータシステムの一部を示す。

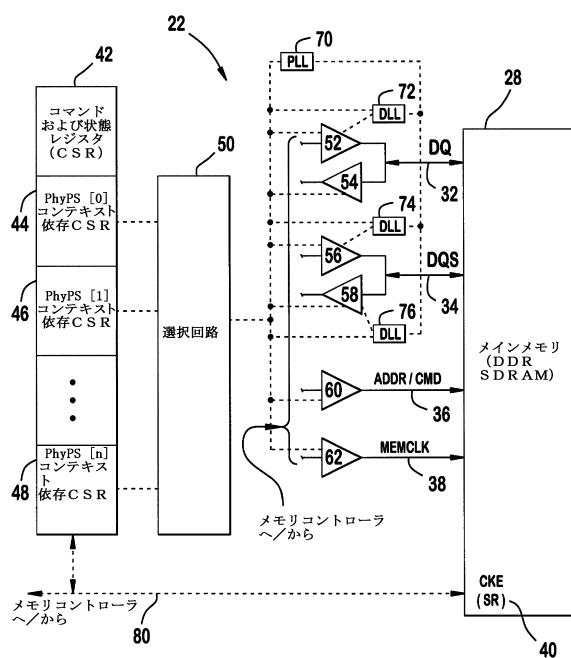

【図2】Phyの高レベルアーキテクチャを示す。

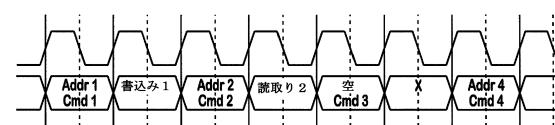

【図3】Phyインターフェース構成バス上のアドレス、コマンド(例えば、読み取り、書き込み)、およびデータを示すタイミング図である。

【図4】CSRアドレス指定の内訳を示す。

【発明を実施するための形態】

【0010】

図1は、中央処理装置(CPU)12、コア理論チップセット14、16およびメインメモリ28へのメモリインターフェース18を含む、コンピュータシステム10の一部を示

50

す。コア理論チップセットは、ノースブリッジ 14（または統合メモリコントローラ）とサウスブリッジ（または入出力コントローラハブ）16との間で分割され得る。メモリコントローラ 18 は、しばしばノースブリッジ 14 に配置される。かかる回路機構は、単一チップまたは C P U 内など、様々な場所に物理的に配置され得ることを理解すべきである。メモリコントローラ 18 は、通常、メインメモリ 30 との間を行き来するデータの論理的な流れを管理する。ダイナミックランダムアクセスメモリは、様々なメモリ記憶セル内のチャージを保持するために定期的なリフレッシュ信号も必要とし得る。メモリコントローラ 18 は、一般に、これらのリフレッシュ操作を管理する。C P U アーキテクチャおよび / またはオペレーティングシステムに応じて、メインメモリ 30 は、データを 32 ビットまたは 64 ビットデータ単位で伝送し得る。他のサイズのデータ単位がサポートされ得ることを理解すべきである。いくつかのメモリシステムは、ブロック 20、24、および 30 で示される、複数のチャネル（例えば、2 つ以上の独立したメモリコントローラ）を含む。明確にするために、本明細書に含まれる例は、単一のメモリチャネルのみを示し得る。本開示の範囲から逸脱することなく、複数のチャネルが使用され得ることを理解すべきである。10

#### 【 0 0 1 1 】

P h y インタフェース 22 は、メモリコントローラ 18 と物理メモリデバイスとの間に存在する。P h y インタフェースは、一般に、中央処理装置内に配置されるが、他の場所に配置され得る。明確にするために、P h y インタフェース 22 は、図 1 では別個のブロックとして示す。P h y インタフェースは、通常、メインメモリデータストローブのタイミング要件を処理するための回路機構を含む。本開示では、ダブルデータレート ( D D R ) という用語は、D D R 1 / D D R 2 / D D R 3 および / またはかかるメモリデバイスの次の世代を包含する。D D R メモリデバイスは、一般に、電子デバイス技術合同協議会 ( J E D E C : J o i n t E l e c t r o n D e v i c e s E n g i n e e r i n g C o u n c i l s ) 規格に準拠する。これらの規格は、D D R メモリデータがどのようにアクセスされ（読み取られ）、格納される（書き込まれる）のかを定義する。P h y インタフェースは、他のメモリタイプおよび / または他のメモリ規格と共に動作するように構築され得ることを理解すべきである。典型的な D D R S D R A M メモリデバイスへのインターフェースは、主として 2 つの信号クラス、D Q ( データ ) 32 および D Q S ( データストローブ ) 34 を通して達成される。他の信号は、メモリクロック ( M E M C L K ) 38 、ならびにアドレスおよびコマンド信号（通常、A D D R / C M D 36 として示す）を含む。典型的なメモリデバイスは、図に示されていない、追加の信号を使用し得ることを理解すべきである。かかる信号は、明確さのみのために省略されている。例えば、電力および接地信号は示されていない。かかる信号は、典型的な実施態様に含まれるであろうことを理解すべきである。20

#### 【 0 0 1 2 】

読み取り操作中、D D R S D R A M は、D Q および D Q S を、一般に「エッジアライン ( e d g e a l i g n e d ) 」と呼ばれる方法で、同時に発行する。メモリコントローラが、D D R S D R A M から送信されているデータを正しく取得するため、P h y インタフェース 22 は、遅延ロックループ ( D L L ) などの遅延回路を利用して、有効なデータウインドウまたは「データアイ ( d a t a e y e ) 」の間に、D Q 信号を正しくラッチするために D Q S 信号が使用され得るように、D Q S 信号を遅延させる。同様に、P h y インタフェース 22 は、データの D D R D R A M への書き込みをサポートするためにも遅延回路を利用し得る。データ読み取りのため、D Q S 34 を遅延させる必要がある。データ書き込みのため、D Q S および D Q 34 、32 を遅延させる必要がある。P h y は、D Q S 34 を、エッジアラインよりむしろ、D Q 32 データアイの中央に合わせる。D Q S 34 は、書き込み平準化 ( w r i t e l e v e l i n g ) のために遅延されて、データアイの中央要件を満足する。他の遅延も使用され得る（例えば、データバスの 3 状態制御の読み取り / 書込みのため）。P h y インタフェース 22 は、以下でさらに詳述する、遅延タイミング、ドライブ強度、および様々な他のパラメータを制御するために利用さ304050

れる複数のコマンドおよび状態レジスタ (CSR) 42を含む。かかる回路機構は、チャネルベース毎でも重複され得ることを理解すべきである。

【0013】

Phyインターフェースは、また、送信器のドライブ強度および受信器の終端インピーダンスの調整または選択も行い得る。固定のタイミング遅延、送信器ドライブ強度および受信器終端インピーダンスを使用するよりも、これらのパラメータは、コンピュータシステムが作動されるたびに調整され得る。これは、通常、トレーニングプログラムの支援を受けて達成される。トレーニングプログラムは、通常、基本入出力システム (BIOS) メモリデバイス 26 に格納されるが、装置ハードウェア内にも実装され得る。トレーニングプログラムは、パワーオンセルフテスト (POST) 中にアルゴリズムを実行し、それが、多数のメモリインターフェース信号に関連した、適切なタイミング遅延、ドライブ強度および終端インピーダンスを決定する。これらのパラメータは、Phyへの、および Phy からの様々な信号経路の全体的なタイミングを定義する複数のレジスタで Phyインターフェース内に保存される。別 の方法では、これらのパラメータは、別の場所 (例えば、ノースブリッジ 14 またはサウスブリッジ 16 内) に格納され得る。

10

【0014】

図 2 は、Phyインターフェース 22 の高レベルアーキテクチャを示す。Phyインターフェースは、通常、クロックソース (例えば、PLL 70) およびコマンドおよび状態レジスタ (CSR) 42 を含む制御インターフェースを含む。Phyインターフェース 20 は、DQ 32、DQS 34、アドレス / コマンド線 36 およびクロック入力 38 を含め、デュアルインラインメモリモジュール (DIMM) などの典型的なメモリデバイス上の 大多数のピンに対して物理接続を提供する。

20

【0015】

典型的なメモリデバイスは、クロック可能 (セルフリフレッシュ) 入力 40 も備え得る。クロック可能入力 40 は、メモリデバイスをセルフリフレッシュモードにするために使用される。このモードでは、メモリデバイスは、必要に応じて内部のリフレッシュサイクルを生成するために、オンチップタイマーを使用する。外部クロックもこの間、停止され得る。この入力は、メインメモリデータを失うことなくメモリコントローラを無効にできるので、通常、電源ダウンモードに関連して使用される。

30

【0016】

図 2 に示すように、DQ 32 (データ) および DQS 34 (ストローブ) 線は双方向である。各 DIMM は、複数の DQ 線 (例えば、64 データビット) および複数の DQS 線を有することを理解すべきである。これらの線の各々は、Phyインターフェース 22 内に、関連するドライバ 52、56 および受信器 54、58 を有する。図 2 では、明確にするために、単一のドライバ / 受信器の対を示す。各ドライバは、選択可能または調整可能なドライブ出力を有する。同様に、各受信器は、選択可能または調整可能な終端インピーダンス (例えば、オンダイ終端 (on die termination)) を有する。DQ および DQS 線 32、34 は、遅延ロックループ (DLL) 72、74、76 などの遅延素子にも関連する。遅延素子 (例えば、70 ~ 76)、ドライブ強度または終端インピーダンス値に対する調整は、以下でさらに詳細に説明するように、適切な値を、関連する CSR 42 の適切なフィールド内にプログラミングすることによって達成される。CSR 間の論理結合および遅延素子、ドライブ強度または終端インピーダンスにおける調整は、一般に、点線で示される。

40

【0017】

この例では、ドライバ 52 および 56 は、DLL 72 および 74 とそれぞれ関連する。受信器 58 は、DLL 76 と関連する。前述のように、DLL は、読み取りおよび書き込み操作のために、適切なタイミング遅延を提供するように調整される。Phyインターフェースは、平準化の有無にかかわらず、読み取りおよび書き込み操作を実行するようにも構成され得る。平準化を行う DDR3 DIMMS へのメモリ書き込み操作中に、Phyインターフェースは、各 DRAM チップにおいて、DQS がメモリクロック 58 と合体する (co

50

alesce) のが見られるように、DIMMに進む各DQSの開始を遅延させる。平準化を行う読み取り操作中、Phyインターフェースは、フライバイワットポロジによって取り込まれた遅延の補償も行い得る。

#### 【0018】

より高いデータレートでの操作の信号品位の問題に起因して、Phyインターフェースは、DLL設定をバーストごと(またはトランザクション)のベースで動的に変更し得る。Phyインターフェースは、システム内の各DIMMに対してDQおよびDQSに対する遅延設定の最適な組(tupple)を格納し得る。アクセスされているDIMMに応じて、Phyインターフェースは、適切なDLL設定を取り出し、それらを適用する。

#### 【0019】

Phyインターフェースは、所望の性能レベルに基づき、その要求される電力を調整し得る。電力コンテキストをいつ変更すべきかの決定は、様々な情報源に由来し得ることを理解すべきである。例えば、オペレーティングシステムは、コンテキスト変更が要求されることを(例えば、アイドル時間の設定期間後、ユーザーコマンド、時間スケジュールまたは同様のものによって)判断し得る。別の方では、コンテキスト変更がいつ要求されるかを判断するためにハードウェアが使用され得る。コンテキスト変更は、異なる電力状態に関連する、異なるセットのPhyインターフェースパラメータ間で切り替えることにより達成される。例えば、高電力状態(例えば、より高いメモリ速度)および低電力状態(例えば、より低いメモリ速度)。各電力状態は、Phyインターフェースパラメータまたはコンテキストの関連するセット(つまり、各信号線に対する遅延素子設定、ドライブ強度および終端インピーダンス)を有する。以降で詳述するように、電力状態間の切替えは、いくつかの方法で達成され得る。本明細書で開示するように、複数の電力状態間の切替えは、任意のメモリタイプに適用でき、以下の例で使用されるように、DDRメモリとの使用に限定されないことを理解すべきである。

#### 【0020】

この例では、メモリコントローラ18は、32ビットの、時間インターリーブされた、一方向の構成バス80を介して、CSR42にアクセスし得る。アドレスおよびコマンド(例えば、読み取り、書き込み、何もしない)は、図3に示すように、第1のパイプステージ内に送信され、その後、第2のパイプステップ内のデータが続く。CSRは、他の通信リンクを介してアクセスできることを理解すべきである。

#### 【0021】

この例では、CSRアドレス空間は16ビット幅で、65,536の一意の16ビットレジスタの空間を可能にする。かかる大空間を可能にする代わりに、アドレスは、次の機能を可能にするためにマッピングされる: すなわち、チップレット識別、イントラチップレットブロードキャスト(intra-chiplet broadcast)、補償ブロードキャスト(compensation broadcast)、チップレットインスタンス識別(D3DBYTE、D3CLK、およびD3CMPは、2回以上配置されるチップレットである)。図4は、CSRアドレス指定に対する内訳を示す。

#### 【0022】

CSRの一部のみが所与の電力状態に関連する値を含む。電力状態間での低遅延の切替えを容易にするため、各電力状態に対して電力コンテキスト依存のCSRのセットが提供される。図2に戻ると、CSRの第1のセットが第1の電力コンテキストと関連するPhyPS[0] 44。CSRの別のセットが第2の電力コンテキストと関連するPhyPS[1] 46。PhyPS[n] 48によって示されるように、3つ以上の電力コンテキストをサポートするために、CSRの追加のセットが提供され得ることを理解すべきである。CSRの異なるセット間で選択するために、マルチプレクサまたは選択回路50が提供される。Phyインターフェースは、電力コンテキスト依存でないCSRも含む。かかるCSRは、全ての電力状態で適用可能である。

#### 【0023】

各PhyPS内の各CSRに対するプログラム可能フィールドの要約を以下の表1に示す。

10

20

30

40

50

す。

【表1】

| 番号 | 説明                                                                        |

|----|---------------------------------------------------------------------------|

| 1  | D D R P L L レート；                                                          |

| 2  | D L L (遅延ロックループ) 周波数固有のプログラミング；                                           |

| 3  | D Q S (ストローブビット) ドライブ強度 (D S)；                                            |

| 4  | D Q (データビット) D S                                                          |

| 5  | M e m C l k D S                                                           |

| 6  | アドレス&コマンド (A d d r, バンク, R A S, C A S, W E, A d d r P a r i t y) D S      |

| 7  | チップ選択 (C s) & オンダイ終了 (O d t) D S                                          |

| 8  | クロック可能 (C k e) D S                                                        |

| 9  | P r o c O d t 強度                                                          |

| 10 | P r o c O d t O f f                                                       |

| 11 | バイトごとのD I MMごとのチャネルごとのT x D q s D 1 1 制御                                  |

| 12 | バイトごとのD I MMごとのチャネルごとのT x D q D 1 1 制御                                    |

| 13 | バイトごとのD I MMごとのチャネルごとのR x E n D 1 1 制御                                    |

| 14 | ニブルごとD I MMごとチャネルごとのR x D q s L D 1 1 制御<br>(x 4 およびx 8 のD I MMタイプで使用される) |

| 15 | ニブルごとD I MMごとチャネルごとのR x D q s U D 1 1 制御<br>(x 4 のD I MMタイプで使用される)        |

| 16 | チャネルごとのA d d r C m d D 1 1 制御                                             |

| 17 | チャネルごとのC s O d t D 1 1 制御                                                 |

| 18 | チャネルごとのC k e D 1 1 制御                                                     |

| 19 | D I MM対ごとのチャネルごとのM e m C l k D 1 1 制御                                     |

#### 【0024】

この例では、P h y インタフェースの関連するフィールドのプログラミングは、構成バス80を介して、コマンドを発行するか、またはC S R内の個々のフィールドをプログラミングすることによって達成される。例えば、1つのP h y P Sから別への変更は、D D R P h y インタフェース間接レジスタ空間に発行された単一のコマンドで達成され得る。P h y P S コンテキスト依存C S Rのプログラミングは、適切なP h y P S コンテキストを設定し、次いで、正常な間接C S R書込みまたは読み取りを行うことによって達成され得る。あるいは、直接C S R書込みまたは読み取りは、P h y P S コンテキストを考慮することなく、任意のC S Rに達し得る。

#### 【0025】

P h y インタフェースは、M a s t e r \_ 0 x 0 8 [ 1 2 ] - P h y P S、M a s t e r \_ 0 x 0 8 [ 8 ] - P s t a t e T o A c c e s s およびM a s t e r \_ 0 x 1 8 [ 8 ] - P h y P S M a s t e r C h a n n e l を含む、一連のコマンドで制御され得る。用語体系 [ 1 2 ]、[ 8 ] および同様のものは、コマンド内のビット位置を指す。M a s t

10

20

30

40

50

`er_0x08[12]` コマンドは、現在の Phy インタフェース P 状態 (0 または 1) に対応する。このコマンドは、電力コンテキスト (例えば、CSR のどのセットが現在アクティブであるか) を制御する。`Master_0x08[8]` コマンドは、CSR アクセス中に、どの P 状態の読み取りまたは書き込みを行うかを選択する。BIOS は、実際の P 状態変更を行う必要なく、どの P 状態を書き込むかを制御するために、この方法を使用し得る。3つ以上の電力コンテキストをサポートするために、追加のビットが使用され得ることを理解すべきである。`Master_0x18[8]` コマンドはマスター・チャネルを選択する。この実施形態では、このビットによって指定されたチャネル (マスター・チャネル) のみが、`0x0B[PhyPS変更]` コマンドの発行を許可される。他のチャネルから発行されたどの `0x0B[PhyPS変更]` コマンドも無視されるであろう。3つ以上のチャネルをサポートするために、追加のビットが追加され得ることを理解すべきである。この実施形態では、以下の `0x0B` コマンドが定義される：

【表 2】

| 番号 | 説明                                       |

|----|------------------------------------------|

| 1  | PhyPS を変更する                              |

| 2  | PhySR (セルフリフレッシュ) に入って、出る                |

| 3  | DDR レート変更 (すなわち、DDR PLL 周波数を変更する)        |

| 4  | 他の Phy インタフェース sub モードを (sub コマンドで) 更新する |

| 5  | ~PowerOk の既定の設定                          |

### 【0026】

完全な `0x0B` データパケットを以下の表 3 に示す。

【表3】

| ビット位置 | 説明                                                                                                                                                                             |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | PhySRRquest (セルフリフレッシュ)                                                                                                                                                        |

| 30    | PhyPSRequest                                                                                                                                                                   |

| 29~27 | 予約済み                                                                                                                                                                           |

| 26    | PhyPS = <所望のPhyインターフェース電力状態><br>PhyPS 0 または 1 の低電力または高電力モードとの<br>関連 (それぞれ低DDRレートまたは高DDRレート) は、<br>Phy の観点から見れば任意である。この例では、Phy<br>PS 1 は低電力状態として、また PhyPS 0 は高電力状<br>態として定義される。 |

| 25~24 | PhySR P11制御                                                                                                                                                                    |

| 23    | PhySR                                                                                                                                                                          |

| 22~18 | 予約済み                                                                                                                                                                           |

| 17~16 | DdrRate                                                                                                                                                                        |

| 15~4  | 予約済み                                                                                                                                                                           |

| 3     | DdrRateRequest                                                                                                                                                                 |

| 2~0   | DdrRate                                                                                                                                                                        |

## 【0027】

この例では、電力コンテキストが単一ビット ( すなわち、PhyPS [ 0 ] および PhyPS [ 1 ] ビット位置 26 ) で選択される。3つ以上のコンテキストをサポートするために、追加のビットが追加され得ることを理解すべきである。PhyPSRequest ビット ( ビット位置 30 ) は、コマンドがコンテキスト変更を含むことを示すために使用される。電力コンテキストは、通常、以下のように変更され得る。コンテキスト変更要求を受信すると、各アクティブなチャネルがセルフリフレッシュ ( SR ) モード (  $0 \times 0 B$  [ PhySR = 1 ] ) にされる。この「セーフモード」では、メモリデバイスは、必要に応じて内部のリフレッシュサイクルを生成するために、オンチップタイマーを使用する。選択した SR モードに応じて、外部クロックもこの間、停止され得る。SR モードに入るには、異なる時に起こり得るが、全てのチャネルは、コンテキスト変更の前に SR モードでなければならない。電力コンテキスト変更が開始される (  $0 \times 0 B$  [ PhyPS = X ] 、 [ PhyPSRequest = 1 ] ) 。アクティブなチャネルの各々は、SR モードから正常モード (  $0 \times 0 B$  [ PhySR = 0 ] ) に切り替えられる。

## 【0028】

コンテキスト変更コマンドを受信すると、Phyインターフェースは、PhyPS コンテキストを変更し、DDR PLL 乗算器およびドライバが更新され、そして、PLL が再ロックされる。これが全て完了すると、CfgDone が設定される。その後、SR モードから出ると、DLL が再ロックする。PhyPS 変更が生じている間、メモリコントローラは、Phyインターフェースへの全ての入力に対する制御 ( 具体的には、CKE、MemReset、ReadPending、WritePending、他の3状態制御の全て ) を維持する。

## 【0029】

意図は、PhyPS を可能な限り迅速に変更することにあるので、PhyPS 変更は P

10

20

30

40

50

LLを電源の入ったままにすることが一般に予期される。従って、PhyPSの変更は、直ちにPLL再ロック（および再ロックの待機）をトリガーし、SRから出た後にDLL再ロックが生じる。しかし、PLL（VCOまたは調整器のいずれか）の電源を落としているSRモード中にあり、かつ、このSRモードにある間にPhyPSを変更することは可能である。この場合、Phyインターフェースはまだ、PhyPS変更の直後にPLL再ロック時間を待機するが、後にSRから出ると、Phyインターフェースは、PLL再ロック（PLLが電源を入れ戻す過程にあるので）およびDLL再ロックの両方を待機するであろう。

### 【0030】

Phyインターフェースセルフリフレッシュ（PhySR）に入って出る0x0Bコマンドは、チャネル0または1のいずれかで発行され得；1つのDRAMチャネルをSRモードにするが、他はそうではないことを可能にする。Phy内のPCLKグローバルグリッドの電源を完全に落とすために、チャネル0および1の両方がPhySRにある必要がある。PhySRを変更する0x0Bを、以下の表4に示す：

【表4】

| ビット位置 | 説明                               |

|-------|----------------------------------|

| 31    | PhySRRquest（セルフリフレッシュ）           |

| 30    | PhyPSRrequest = 0                |

| 29~27 | 該当なし                             |

| 26    | PhyPS = <所望のPhyインターフェース電力状態> = X |

| 25~24 | PhySR P11制御 {調整器PD, VCO PD}      |

| 23    | PhySRに入るにはPhySR = 1、出るには0        |

| 22~0  | 該当なし                             |

### 【0031】

0x0B[23 = PhySR]とともに0x0B[31 = PhySRRquest]を設定すると、Phyインターフェースがセルフリフレッシュに入るか、または出るようになる。0x0B[25:24]は、SRにある間、PLLの動作を制御する。SRモードに入るのは非常に迅速であり、0x0Bコマンドの受信からCf Doneがアサートされる時間まで~300nsかかる。メモリコントローラが可能な限り迅速に前進できるようになるため、メモリコントローラは、Cf Doneが1から0へ遷移するのをモニタし得る。これは、Phyインターフェースがメモリコントローラからの入力を遮断して、すべてのCKEを低下させ、MemResetを適切にドライブし、残りの全てのDDRバスピンを3状態にすることを示す。この時点で、メモリコントローラが狂うのは安全である。Cf DoneがアサートされるまでVddrレールをドロップして、必要なCSRトランザクションの全てが完了していることを示すことは安全ではない。

### 【0032】

PhySRから出ることは、はるかに潜在的であり、Phyインターフェースクロックグリッド（PCLK）がオンに戻され、DLLが再ロックされることを必要とする。PLLは、SRの間、オンのままにされるか、またはオフにされ得る。この実施形態では、PhySR変更の実行中、0x0B[30 = PhyPSRequest]は0でなければならない。0x0B[31 = PhySRRquest]または0x0B[30 = PhyPSRequest]のいずれかを設定すると、0x0B[22:0]を無効にし、それは、DDRレートフィールドを更新するために0x0B[3 = DdrRateRequest]を設定することはできなことを意味する。PhyインターフェースPLL乗算器およびドライバを含むCSRをロードするために、DDRレートを第1に設定する。0x0B[P

10

20

30

40

50

**h y P S 変更**] を送信すると、DDR PLL 乗算器およびドライバをロードする。他の実施形態では、複数の高レベル  $0 \times 0$  B コマンドを同時に実行することが可能であり得る。 $0 \times 0$  B [ 31 = Phy S R Request ] = 1 かつ  $0 \times 0$  B [ 23 = Phy S R ] が結果的に Phy S R 状態に対して変更を行わない場合、Cfg Done をアサートする前に、DLL ロック時間がまだ従われる。

#### 【0033】

この実施形態では、DDR バス上のDRAM データレートに対する  $0 \times 0$  B コマンドは、チャネル 0 においてのみ BIOS によって設定される。チャネル 1 におけるDRAM データレートを設定するために  $0 \times 0$  B コマンドを送信しても、効果がない。他の実施形態は、各チャネル上で独自の DDR データレートをサポートし得ることを理解すべきである。

10  $0 \times 0$  B DDR レートコマンドを以下の表 5 に示す：

【表 5】

| ビット位置 | 説明                                 |

|-------|------------------------------------|

| 31    | Phy S R Request = 0                |

| 30    | Phy P S Request = 0                |

| 29~27 | 予約済み                               |

| 26    | Phy PS = <所望の Phy インタフェース電力状態> = X |

| 25~24 | Phy S R P11 制御 = X                 |

| 23    | Phy S R = X                        |

| 22~18 | 予約済み                               |

| 17~16 | Ddr Rate [4:3]                     |

| 15~4  | 予約済み                               |

| 3     | Ddr Rate Request = 1               |

| 2~0   | Ddr Rate [2:0] = 所望のレートに設定         |

10

20

30

#### 【0034】

この  $0 \times 0$  B [ Ddr Rate ] コマンドを介して実際の DDR レートおよび PLL 周波数を変更することは、レガシーバIOSのために含まれている。Phy インタフェース P 状態を理解する BIOS は、代わりに、直接 CSR\_Master\_0x00 [ Ddr Rate ] および Master\_0x40 [ Ddr Rate ] を通じて Phy インタフェース P 状態の両方に対して DDR レートをプログラムすべきである。これらの（直接 CSR を通じた）レート変更は、以降の  $0 \times 0$  B [ Phy PS 変更 ] の後にのみ影響を及ぼすであろう。

#### 【0035】

この実施形態では、DDR レートに対する更新を実行する場合、 $0 \times 0$  B [ 31 = Phy S R Request ] および  $0 \times 0$  B [ 30 = Phy P S Request ] は両方とも 0 でなければならない。実施形態は、複数の高レベル  $0 \times 0$  B コマンドを同時にサポートし得ることを理解すべきである。

40

#### 【0036】

コールドリセット、ウォームリセット後の Phy PS 状態、または高度構造及び電力制御インターフェース (ACPI) 電力状態 S3 (一般に、RAM に対するスタンバイ (Standby)、スリープ (Sleep)、またはサスPEND (Suspend) と呼ばれる) を以下の表 6 に示す。全ての状態は、ウォームリセットを通して持続する。それ故、以下のウォームリセットの項目では、値は、ウォームリセットの前のままである。

【表6】

| チャネル実装  | イベント                   | 両方のPhyPSがサポートされる場合の規定値                                                    | 1つだけのPhyPSがサポートされる場合の規定値                                                  |

|---------|------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|

| チャネル0のみ | コールドリセット               | PhyPS=0<br>PStateToAccess=0<br>PhyPSMasterChannel=0<br>PhySR=0 (すべてのチャネル) | PhyPS=0<br>PStateToAccess=0<br>PhyPSMasterChannel=0<br>PhySR=0 (すべてのチャネル) |

|         | ウォームリセット               | PhyPS=0または1<br>PStateToAccess=0または1<br>PhyPSMasterChannel=0               | PhyPS=0<br>PStateToAccess=0<br>PhyPSMasterChannel=0                       |

|         | S3                     | PhySR=0または1<br>(チャネル0)                                                    | PhySR=0または1<br>(チャネル0)                                                    |

|         | PhySR=1<br>(チャネル1)     | PhySR=1<br>(チャネル1)                                                        |                                                                           |

|         | PhySR=0 (すべてのチャネル)     | PhySR=0 (すべてのチャネル)                                                        |                                                                           |

|         | ウォームリセット               | PhyPS=0または1<br>PStateToAccess=0または1<br>PhyPSMasterChannel=0               | PhyPS=0<br>PStateToAccess=0<br>PhyPSMasterChannel=0                       |

|         | S3                     | コールドリセットと同じ                                                               | コールドリセットと同じ                                                               |

|         | PhySR=1<br>(チャネル0)     | PhySR=1<br>(チャネル0)                                                        |                                                                           |

|         | PhySR=0または1<br>(チャネル0) | PhySR=0または1<br>(チャネル0)                                                    |                                                                           |

|         | PhySR=0 (すべてのチャネル)     | PhySR=0 (すべてのチャネル)                                                        |                                                                           |

| チャネル1のみ | コールドリセット               | PhyPS=0<br>PStateToAccess=0<br>PhyPSMasterChannel=0<br>PhySR=0 (すべてのチャネル) | PhyPS=0<br>PStateToAccess=0<br>PhyPSMasterChannel=0<br>PhySR=0 (すべてのチャネル) |

|         | ウォームリセット               | PhyPS=0または1<br>PStateToAccess=0または1<br>PhyPSMasterChannel=0               | PhyPS=0<br>PStateToAccess=0<br>PhyPSMasterChannel=0                       |

|         | S3                     | コールドリセットと同じ                                                               | コールドリセットと同じ                                                               |

|         | PhySR=1<br>(チャネル0)     | PhySR=1<br>(チャネル0)                                                        |                                                                           |

|         | PhySR=0または1<br>(チャネル0) | PhySR=0または1<br>(チャネル0)                                                    |                                                                           |

|         | PhySR=0 (すべてのチャネル)     | PhySR=0 (すべてのチャネル)                                                        |                                                                           |

|         | ウォームリセット               | PhyPS=0または1<br>PStateToAccess=0または1<br>PhyPSMasterChannel=0               | PhyPS=0<br>PStateToAccess=0<br>PhyPSMasterChannel=0                       |

|         | S3                     | コールドリセットと同じ                                                               | コールドリセットと同じ                                                               |

|         | PhySR=1<br>(チャネル0)     | PhySR=1<br>(チャネル0)                                                        |                                                                           |

|         | PhySR=0または1<br>(チャネル0) | PhySR=0または1<br>(チャネル0)                                                    |                                                                           |

| 両方のチャネル | コールドリセット               | PhyPS=0<br>PStateToAccess=0<br>PhyPSMasterChannel=0<br>PhySR=0 (すべてのチャネル) | PhyPS=0<br>PStateToAccess=0<br>PhyPSMasterChannel=0<br>PhySR=0 (すべてのチャネル) |

|         | ウォームリセット               | PhyPS=0または1<br>PStateToAccess=0または1<br>PhyPSMasterChannel=0               | PhyPS=0<br>PStateToAccess=0<br>PhyPSMasterChannel=0                       |

|         | S3                     | コールドリセットと同じ                                                               | コールドリセットと同じ                                                               |

|         | PhySR=1<br>(チャネル0)     | PhySR=1<br>(チャネル0)                                                        |                                                                           |

|         | PhySR=0または1<br>(チャネル0) | PhySR=0または1<br>(チャネル0)                                                    |                                                                           |

|         | PhySR=0 (すべてのチャネル)     | PhySR=0 (すべてのチャネル)                                                        |                                                                           |

|         | ウォームリセット               | PhyPS=0または1<br>PStateToAccess=0または1<br>PhyPSMasterChannel=0               | PhyPS=0<br>PStateToAccess=0<br>PhyPSMasterChannel=0                       |

|         | S3                     | コールドリセットと同じ                                                               | コールドリセットと同じ                                                               |

|         | PhySR=1<br>(チャネル1)     | PhySR=1<br>(チャネル1)                                                        |                                                                           |

|         | PhySR=0 (すべてのチャネル)     | PhySR=0 (すべてのチャネル)                                                        |                                                                           |

## 【0037】

典型的なコンピュータ電力供給が最初に通電される場合、様々な電圧が安定するのに時間がかかる。電圧が安定する前に、コンピュータを起動しようとすることが許可された場合、予測できない結果が生じ得る。コンピュータが時期尚早に起動するのを防ぐため、電力供給が使える状態であれば、電力供給はPowerOK信号を出力する。この信号が送信されるまで、マザーボードはコンピュータを起動するのを拒否する。

## 【0038】

コールドブート (~PowerOKがアサートされ、同様にResetがアサートされる) 時には、PhyPSが自動的に0に設定され、PhyインターフェースはPhySRではないであろう(全てのDLLの電源が入れられる)。ウォームブート(PowerOKは継続的にアサートされ、Resetのみがアサートされる) 時には、PhyPSおよびPhySR状態が、ウォームリセットの直前の状態によって決定される。ウォームリセットからの復帰は、BIOSが適切なPhyPSおよびPhySR状態を設定することを必要とする(時間最適化ソリューションは、これらの状態の直接CSR読み取りを実行し、次いで必要

10

20

30

40

50

であれば、書き込みを実行することである）。B IOS は、ウォームリセットの後、Phy インタフェースが、SR モードにないことを確実にすべきである。

【0039】

DDR3 は、書き込み平準化 (WL) および  $R \times E_n$  の曖昧でない収束を有するために、2つのバスのトレーニング手順を必要とするので、より高出力の P 状態に対するトレーニングの過程の一部として低周波数 P 状態に対してトレーニングすることが可能である。その手順は、BIOS は既に、ウォームリセットまたは S3 からの退出とは対照的に、これはコールドリセット（従って、トレーニングを必要とする）である判断しているとも仮定する。

【0040】

メモリトレーニングの第1のバスは、以下の表7に示すような曖昧でないトレーニングに対して必要な初期の DDR レートを使用する。以下の表の全てで設定されるステップの特定の順番は、本開示の範囲から逸脱することなく、変更し得ることを理解すべきである。

【表7】

|   | 説明                                                                 |

|---|--------------------------------------------------------------------|

| 1 | メモリを備えたチャネルに対して以下の手順を実行する。メモリのないどのチャネルも SR にし、これらのチャネルに対して他に何もしない。 |

| 2 | 関連するメモリコントローラレジスタ空間を構成する。                                          |

| 3 | 全てのアクティブなチャネルを SR にする（随意）。                                         |

| 4 | DDR レートを目標レートにプログラムする。                                             |

| 5 | 全てのアクティブなチャネルを正常モードに設定する（すなわち、チャネルを SR から出す）。DLL が再ロックされる。         |

10

20

30

【0041】

この時点で、DDR PLL および DLL が、使用するために適切に構成されている。Phy PS コンテキストは Phy PS0 である。メモリが存在する場合、両方のチャネルがトレーニングを開始する準備ができている。トレーニングは、表8に大まかに示すように、AMD Generic Encapsulated Software Architecture (AGESA) ブートストラッププロトコルなどの、周知のプロトコルに従う：

【表 8】

|    | 説明                                                                                    |

|----|---------------------------------------------------------------------------------------|

| 6  | 全てのドライブ強度フィールドを設定する。                                                                  |

| 7  | N B _ T x C h n C 1 k E n を設定し、ハードウェアベースのフェンス (fence) トレーニングを実行し、最終的なフェンス値を書き留めて設定する。 |

| 8  | アドレス／バンク／R A S／C A S／W E／M e m C 1 k D 1 1 起動遅延を設定する。                                 |

| 9  | C s & O d t D 1 1 起動遅延を設定する。                                                          |

| 10 | C k e D 1 1 起動遅延を設定する。                                                                |

| 11 | D R A M i n i t を実行する。                                                                |

| 12 | 既定値定数を使用して、ハードウェアベースのW L トレーニングを実行する。                                                 |

| 13 | 既定値定数を使用して、ハードウェアベースのR x E n トレーニングを実行する。                                             |

| 14 | T x D q / R x D q s 書込み／読み取りトレーニングを実行する。                                              |

| 15 | M R L トレーニングがここで起こり得るか、または後で起こり得る。N C L K は、このD D R レートに対する最終的な目標速度で実行する必要がある。        |

10

20

30

## 【0042】

この時点で、曖昧でないトレーニングに対する初期D D R レートのトレーニングおよびプログラミングが完了する。この初期トレーニングプロトコル中に確立されたこのD D R レートおよび他のパラメータが、第1の電力コンテキスト（例えば、より低速度 P h y P S [ 1 ]）として使用され得る。P h y P S [ 1 ]は、別のD D R レートに基づき設定され得る（すなわち、この周波数に対してステップ4～15を繰り返す）ことを理解すべきである。次の段階は、より高い（P h y P S [ 0 ]）D D R レートに対してトレーニングする。前述したバスは、書き込み平準化およびR x E n ハードウェアのトレーニングアルゴリズムにおけるエイリアシングを解決した。書き込み平準化およびR x E n トレーニング値は、M e m C 1 k データレート比P h y P S 0 / P h y P S 1によってスケーリングされ、P h y P S [ 0 ]におけるトレーニングの第2の段階に対するシードとして使用される。手順は、表9に示すように開始される。

40

【表 9】

|     | 説明                                                             |

|-----|----------------------------------------------------------------|

| 1 6 | 全てのアクティブなチャネルを S R にする (随意)。                                   |

| 1 7 | D D R レートを所望の P h y P S [ 0 ] D D R レートにプログラミングする。             |

| 1 8 | 全てのアクティブなチャネルを正常モードに設定する (すなわち、チャネルを S R から出す)。D L L が再ロックされる。 |

10

【0043】

この時点で、D D R P L L および D L L が、使用するために適切に構成される。P h y P S コンテキストはまだ P h y P S [ 0 ] であり、P h y インタフェースは P h y P S [ 0 ] D D R レートで実行する。両方のチャネルは、メモリが存在する場合、表 8 に大まかに示すように、トレーニングの次の段階を開始する準備ができている：

【表 10】

|     | 説明                                                                             |

|-----|--------------------------------------------------------------------------------|

| 1 9 | 全てのドライブ強度フィールドを設定する。                                                           |

| 2 0 | N B _ T x C h n C l k E n を設定し、ハードウェアベースのフェンストレーニングを実行し、最終的なフェンス値を書き留めて設定する。   |

| 2 1 | アドレス／バンク／R A S／C A S／W E／M e m C l k D L L 起動遅延を設定する。                          |

| 2 2 | C s & O d t D l l 起動遅延を設定する。                                                   |

| 2 3 | C k e D l l 起動遅延を設定する。                                                         |

| 2 4 | D R A M i n i t を実行する。                                                         |

| 2 5 | 既定値定数を使用して、ハードウェアベースのW L トレーニングを実行する。                                          |

| 2 6 | 既定値定数を使用して、ハードウェアベースのR x E n トレーニングを実行する。                                      |

| 2 7 | T x D q / R x D q s 書込み／読み取りトレーニングを実行する。                                       |

| 2 8 | M R L トレーニングがここで起こり得るか、または後で起こり得る。N C L K は、このD D R レートに対する最終的な目標速度で実行する必要がある。 |

20

30

40

【0044】

これで、電力コンテキスト P h y P S [ 0 ] の第 2 の段階のトレーニングおよびプログラミングが完了する。この時点で、両方の P h y P S 空間にに対するレートがトレーニングされ、トレーニングされた値が、トレーニングの一部として P h y インタフェース P h y P S [ 0 ] C S R に対して既に書き込まれている。P h y インタフェースは、現在、

50

`PhyPS[0]` コンテキスト内である。`PhyPS[1]` トレーニング値はトレーニングされているが、`PhyPS[1]` CSR にまだ書き込まれていない。`PhyPS[0]` CSR は、表 11 に大まかに示すように更新される：

【表 11】

|    | 説明                                                                       |

|----|--------------------------------------------------------------------------|

| 29 | 1を <code>Master_0x08[PStateToAccess]</code> に書き込む— <code>PhyPS[1]</code> |

| 30 | 格納された <code>PhyPS1</code> トレーニング値を <code>PhyPS1</code> CSR に書き込む         |

| 31 | 0を <code>Master_0x08[PStateToAccess]</code> に書き込む— <code>PhyPS[0]</code> |

10

【0045】

1つの`PhyPS`のみが必要とされる場合には、`BIOS`がどの`PhyPS`コンテキストを使用すべきかを選択し得る。歴史的な意味を維持するため、`BIOS`は`PhyPS[0]`に対して`Phy`インターフェースを構成し得る。

20

【0046】

`S3`からの復帰は、いかなる`DRAM`トレーニングも伴わず、不揮発性状態（通常、サウスブリッジにおける）からのトレーニング値の復元のみである。`S3`からの復帰は、一般に、（`~PwrOk`のために）`PhyPS`コンテキストが`PhyPS0`であり、`Master_0x08[PStateToAccess]`が0であること、両方のチャネルが`PhySR`から出ていること、およびマスターチャネルがチャネル0である（たとえ、メモリがチャネル0上に存在しなくても）ことを保証する。`S3`からの復帰に対する手順を大まかに表 12 に示す：

【表 1 2】

|   | 説明                                                                                                                                                                                                                 |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | 全てのアクティブなチャネルをSRにする。                                                                                                                                                                                               |

| 2 | チャネル0上にメモリがない場合、アクティブなDCTのみによってチャネル1上で発行されているPhyPS変更が影響を与えることを確実にするため、Master_0x18[PhyPSMasterChannel] (3.7を参照) を設定する。メモがチャネル1上に存在しない場合には、Master_18[PhyPSMasterChannel] はチャネル0の既定値のままにされるべきであるので、動作は必要とされないことに留意する。 |

| 3 | S3中に発行されている～PwrOkのためにPhyインターフェースがPhyPS0内にあると、PhyPS0トレーニング値および導出値の全てを復元する。                                                                                                                                          |

| 4 | DDRレートをPhyPS0レートで更新する。                                                                                                                                                                                             |

| 5 | 1をマスターチャネル内のMaster_0x08[PSstateToAccess]に書き込む。これは、全てのPCIアクセスがここでPhyPS=1で向けられることを意味する。                                                                                                                              |

| 6 | 全てのPhyPS1トレーニング値および導出値を復元する。                                                                                                                                                                                       |

| 7 | DDRレートをPhyPS1レートで更新する。ここで、PhyPS_CSRの両方のセットが復元され、準備ができている。                                                                                                                                                          |

| 8 | 0x0B[PhyPSの所望のPhyPSへの変更]をマスターチャネル内で発行する。これは、DDRPLLを所望のPhyPSレートに更新する。CfgDoneがアサートされるのを待機する。                                                                                                                         |

| 9 | 全てのアクティブなチャネルをSRから出す。未実装のチャネルはSRに残す。DLLが再ロックされる。PhyインターフェースはここでいずれかのPhyPSで動作する準備ができ、現在は要求されたPhyPS内である。                                                                                                             |

【0047】

ウォームリセットの復帰は、S3からの復帰とほぼ同一である。S3からの復帰は、～PwrOkで、PhyPSコンテキストをPhyPS0に設定し、PhyPS変更を伝達するためにチャネル0をマスターチャネルとして指定し、両方のチャネルでPhyインターフェースをPhySRから出す。対照的に、ウォームリセットは、PhyPSおよびPh

10

20

30

40

50

y S R をマスター・チャネルと同様に未知の状態のままにしておく。ウォームリセットの復帰には構造上の穴が存在することにさらに留意すべきである。システムがコールドブートし、メモリトレーニングを完了し、全てのトレーニング値を不揮発性メモリに格納し得る前にウォームリセット復帰が発行されると、復帰は失敗するであろう。この問題を回避するため、BIOSは、トレーニング値が計算され、うまく格納されているか否かを示すために（コールドリセット時にリセットされるが、ウォームリセットを通じて持続する）フラグを使用すべきであり、ウォームリセット中に、BIOSがこのフラグが設定されているのを見ると、トレーニングされた状態を復元することによって復帰し得る。トレーニングされた状態は、Master\_0x18 [PhyPSMasterChannel] も含み、同様に、どの未実装のチャネルも SR モードのままにされる。このフラグが設定されていなければ、BIOSは Phy を（再）トレーニングする必要がある。以下の開示では、このフラグが設定されていて、トレーニング値が格納されていると仮定する。従って、ウォームリセット復帰はいかなるDRAMトレーニングも伴わず、（通常、サウスブリッジ内の）不揮発性状態からトレーニング値を復元するだけである。ウォームリセット復帰を実行するための手順を大まかに表13に示す：

【表13】

|    | 説明                                                                                                                                      |

|----|-----------------------------------------------------------------------------------------------------------------------------------------|

| 1  | 全てのアクティブなチャネルを SR にする。                                                                                                                  |

| 2  | BIOSが、どのチャネルが PhyPS 変更を受け入れるマスター・チャネルであるかを決定する。BIOSによるMaster_0x08 [PStateToAccess] または0x0B [PhyPS] コマンドへの以後のアクセスは、マスター・チャネルへ向けられるべきである。 |

| 3  | PhyPS [0] を選択する (Master_0x08 [PStateToAccess] = 0)                                                                                      |

| 4  | 全ての PhyPS 0 のトレーニング値および導出値を復元する。                                                                                                        |

| 5  | DDR レートを PhyPS [0] レートに更新する。                                                                                                            |

| 6  | PhyPS [1] を選択する (Master_0x08 [PStateToAccess] = 1)                                                                                      |

| 7  | 全ての PhyPS 1 のトレーニング値および導出値を復元する。                                                                                                        |

| 8  | DDR レートを PhyPS 1 レートに更新する。                                                                                                              |

| 9  | 0x0B [PhyPS の所望の PhyPS への変更] をマスター・チャネル内で発行する。これは、DDR PLL を所望の PhyPS レートに更新する。CfgDone がアサートするのを待機する。                                    |

| 10 | 全てのアクティブなチャネルを SR から出す。これにより DLL を再ロックする。                                                                                               |

【0048】

表14は、各電力コンテキストに対して重複されている全ての PhyPS CSR のリストを示す。

【表 1 4】

|    |                                                                                       |    |

|----|---------------------------------------------------------------------------------------|----|

|    | 説明                                                                                    |    |

| 1  | PhyPS0のためのMaster_0x00 [Config 0]                                                      |    |

| 2  | PhyPS1のためのMaster_0x40 [Config 0]                                                      |    |

| 3  | PhyPS0のためのMaster_0x01 [Config 1]                                                      |    |

| 4  | PhyPS1のためのMaster_0x41 [Config 1]                                                      |    |

| 5  | PhyPS0のためのMaster_0x02 [AddrCmdCke]                                                    |    |

| 6  | PhyPS1のためのMaster_0x42 [AddrCmdCke]                                                    |    |

| 7  | Master_0x03 [P11Div, P11Mul, P11Div2Bypass, P11Update] は現在、PhyPS0 PLL制御用である           | 10 |

| 8  | Master_0x43 [P11Div, P11Mul, P11Div2Bypass, P11Update] は現在、PhyPS1 PLL制御用である           |    |

| 9  | 8:0. DByte_0x {00, 04, 08} はPhyPS0 DSおよびPOD制御である                                      |    |

| 10 | 8:0. DByte_0x {40, 44, 48} はPhyPS1 DSおよびPOD制御である                                      |    |

| 11 | 8:0. DByte_0x0CはPhyPS0 D11&Pre Configである                                              |    |

| 12 | 8:0. DByte_0x0CはPhyPS1 D11&Pre Configである                                              |    |

| 13 | 8:0. DByte_0x {10, 11} はPhyPS0 D11電力管理である                                             |    |

| 14 | 8:0. DByte_0x {50, 51} はPhyPS1 D11電力管理である                                             |    |

| 15 | 8:0. DByte_0x13はPhyPS0 D11 DByte Configである                                            |    |

| 16 | 8:0. DByte_0x53はPhyPS1 D11 DByte Configである                                            |    |

| 17 | PhyPS0のための8:0. DByte_0x {14, 15, 16, 17} [RxDQS初期/後期選択]                               |    |

| 18 | PhyPS1のための8:0. DByte_0x {54, 55, 56, 57} [RxDQS初期/後期選択]                               |    |

| 19 | PhyPS0のための8:0. DByte_0x {18, 19, 1A, 1B} [RxDQS初期選択]                                  |    |

| 20 | PhyPS1のための20:8:0. DByte_0x {58, 59, 5A, 5B} [RxDQS初期選択]                               |    |

| 21 | PhyPS0のための8:0. DByte_0x1E [バイアス制御]                                                    | 20 |

| 22 | PhyPS1のための8:0. DByte_0x5E [バイアス制御]                                                    |    |

| 23 | PhyPS0のための8:0. DByte_0x1F [受信器制御]                                                     |    |

| 24 | PhyPS1のための8:0. DByte_0x5F [受信器制御]                                                     |    |

| 25 | PhyPS0のためのRxDqs後期選延 {0, 1, 2, 3} に対する8:0. DByte_0x {20, 21, 22, 23}                   |    |

| 26 | PhyPS1のためのRxDqs後期選延 {0, 1, 2, 3} に対する8:0. DByte_0x {60, 61, 62, 63}                   |    |

| 27 | PhyPS0のためのD11TxDqsに対する8:0. DByte_0x {24, 25}                                          |    |

| 28 | PhyPS1のためのD11TxDqsに対する8:0. DByte_0x {64, 65}                                          |    |

| 29 | PhyPS0のためのD11RxEnに対する8:0. DByte_0x {26, 27}                                           |    |

| 30 | PhyPS1のためのD11RxEnに対する8:0. DByte_0x {66, 67}                                           |    |

| 31 | PhyPS0のためのD11TxDqに対する8:0. DByte_0x {28, 29}                                           |    |

| 32 | PhyPS1のためのD11TxDqに対する8:0. DByte_0x {68, 69}                                           |    |

| 33 | PhyPS0のためのD11TxDQSに対する8:0. DByte_0x {2A, 2B}                                          |    |

| 34 | PhyPS1のためのD11TxDQSに対する8:0. DByte_0x {6A, 6B}                                          |    |

| 35 | PhyPS0のためのD11TxDQに対する8:0. DByte_0x {2C, 2D}                                           | 30 |

| 36 | PhyPS1のためのD11TxDQに対する8:0. DByte_0x {6C, 6D}                                           |    |

| 37 | 3:0. MemCk_0x00 [TX Config/DS] はPhyPS0 DSである                                          |    |

| 38 | 3:0. MemCk_0x40 [TX Config/DS] はPhyPS1 DSである                                          |    |

| 39 | 3:0. MemCk_0x1E [バイアス制御] はPhyPS0 DSである                                                |    |

| 40 | 3:0. MemCk_0x5E [バイアス制御] はPhyPS1 DSである                                                |    |

| 41 | PhyPS0のための3:0. MemCk_0x20 [D11選延/コンフィグ]                                               |    |

| 42 | PhyPS1のための3:0. MemCk_0x60 [D11選延/コンフィグ]                                               |    |

| 43 | 0:1. CsOdt_0x {00, 04, 08} [OdtCfg, CsCf0145, CsCf2367] はPhyPS0 DSである                 |    |

| 44 | 0:1. CsOdt_0x {40, 44, 48} [OdtCfg, CsCf0145, CsCf2367] はPhyPS1 DSである                 |    |

| 45 | PhyPS0のための0:1. CsOdt_0x1E [バイアス制御]                                                    |    |

| 46 | PhyPS1のための0:1. CsOdt_0x5E [バイアス制御]                                                    | 40 |

| 47 | PhyPS0のための0:1. CsOdt_0x {20, 21} [D11選延/コンフィグ]                                        |    |

| 48 | PhyPS1のための0:1. CsOdt_0x {60, 61} [D11選延/コンフィグ]                                        |    |

| 49 | A2Byt_0x {00, 04, 08, 0C, 10} [A2Cf0189, A2Cf23AB, A2Cf45CD, A2Cf67E F] はPhyPS0 DSである |    |

| 50 | A2Byt_0x {40, 44, 48, 4C, 50} [A2Cf0189, A2Cf23AB, A2Cf45CD, A2Cf67E F] はPhyPS1 DSである |    |

| 51 | PhyPS0のためのA2Byt_0x1E [バイアス制御]                                                         |    |

| 52 | PhyPS1のためのA2Byt_0x5E [バイアス制御]                                                         |    |

| 53 | PhyPS0のためのA2Byt_0x {20, 21} [D11選延/コンフィグ]                                             |    |

| 54 | PhyPS1のためのA2Byt_0x {60, 61} [D11選延/コンフィグ]                                             |    |

| 55 | PhyPS0のためのD3Cmp_0x02 [プレドライバスルーレート]                                                   |    |

本明細書の開示に基づいて、多数の変形形態が可能であることを理解すべきである。例えば、複数の電力コンテキストが他のメモリ位置（例えば、ノースブリッジ 14 またはサウスブリッジ 16 内）に格納できる。このシナリオでは、標準的な Ph y インタフェースは、コンテキスト依存 C S R の専用セットを必要とせずに、電力コンテキストを切り替え得る。かかるシナリオは、C S R の複数のセットに対する必要性を取り除き得るが、コンテキスト変更に対する待機時間を増加させる。

#### 【 0 0 5 0 】

特徴および要素は特定の組合せで前述されているが、各特徴または要素は、他の特徴および要素なしで単独で、または他の特徴および要素の有無に関わらず様々な組合せで使用され得る。本明細書で提供する方法または流れ図は、汎用コンピュータまたはプロセッサによる実行のために、コンピュータ可読記憶媒体内に組み込まれた、コンピュータプログラム、ソフトウェア、またはファームウェアで実装され得る。コンピュータ可読記憶媒体の例には、読み取り専用メモリ（R O M）、ランダムアクセスメモリ（R A M）、レジスタ、キャッシュメモリ、半導体メモリデバイス、内蔵されたハードディスクおよび取り外し可能ディスクなどの磁気媒体、光磁気媒体、ならびにC D - R O Mディスク、およびデジタル多用途ディスク（D V D）などの光媒体を含む。

#### 【 0 0 5 1 】

適切なプロセッサには、例として、汎用プロセッサ、専用プロセッサ、従来型のプロセッサ、デジタル信号プロセッサ（D S P）、複数のマイクロプロセッサ、D S Pコアと関連した1つまたは複数のマイクロプロセッサ、コントローラ、マイクロコントローラ、特定用途向け集積回路（A S I C）、フィールドプログラマブルゲートアレイ（F P G A）回路、任意の他のタイプの集積回路（I C）、および／または状態マシンを含む。かかるプロセッサは、処理されたハードウェア記述言語（H D L）命令（コンピュータ可読媒体上に格納可能なかかる命令）の結果を用いて、製造プロセスを構成することにより製造され得る。かかる処理の結果は、本発明の態様を実施するプロセッサを製造するために、その後、半導体製造プロセスで使用されるマスクワークであり得る。

10

20

【図1】

【図2】

【図3】

【図4】

| アドレス    | 値         | 機能                                                                                                                                         |

|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| [15:13] | 000       | チップレットタイプ: D3Dbyte (9インスタンス)                                                                                                               |

|         | 001       | チップレットタイプ: D3C1k (4インスタンス)                                                                                                                 |

|         | 010       | チップレットタイプ: D3Cmp (3インスタンス)                                                                                                                 |

|         | 011       | チップレットタイプ: D3MemRef (2インスタンス)                                                                                                              |

|         | 100       | チップレットタイプ: D3Cs0dt (1インスタンス)                                                                                                               |

|         | 101       | チップレットタイプ: D3AByte1 (1インスタンス)                                                                                                              |

|         | 110       | チップレットタイプ: D3AByte (1インスタンス)                                                                                                               |

| [12]    | 0/1       | 1の場合は、アドレスビット[5:1, 0]に一致するチップレット内の全てのレジスタを更新する: 0の場合は、全てのアドレスビット[5:0]を復号する                                                                 |

| [11:8]  | 1011-0000 | チップレットタイプのインスタンス数。最大12のインスタンスが許可される                                                                                                        |

|         | 1100      | [7:6]に一致するすべてのODT補償レジスタへのブロードキャスト                                                                                                          |

|         | 1101      | [7:6]に一致するすべてのドライバ補償レジスタへのブロードキャスト                                                                                                         |

|         | 1110      | [7:6]に一致するすべてのブレドライバ補償レジスタへのブロードキャスト                                                                                                       |

|         | 1111      | タイプフィールド[15:13]に一致するすべてのチップレットへのブロードキャスト                                                                                                   |

| [7:6]   | 11-00     | 補償情報がブロードキャストする([11:8])場合に、情報源を識別する最大4つのコード。各チップレットは、それに関連するD3CMPブロックを識別する2ビットのメタルストラップコードを有する。補償ブロードキャストが生じる場合、[7:6]は、データが供給されたD3CMPを識別する |

| [5:0]   | 1x xxxx   | DLLレジスタ                                                                                                                                    |

|         | 0x_xx00   | ドライバ強度レジスタ                                                                                                                                 |

|         | 0x_xx01   | ドライバ補償レジスタ                                                                                                                                 |

|         | 0x_xx10   | ブレドライバ補償レジスタ                                                                                                                               |

|         | 0x_xx11   | ODT補償レジスタ (D3DBYTEのみ)                                                                                                                      |

---

フロントページの続き

(74)代理人 100162156

弁理士 村雨 圭介

(72)発明者 ショーン サールズ

アメリカ合衆国 78737 テキサス州、オースティン、トワイライト メサ ドライブ 69

12

(72)発明者 ニコラス ティー. ハンフリーズ

アメリカ合衆国 78757 テキサス州、オースティン、ピエモント アベニュー 1717

(72)発明者 ブライアン ダブリュ. アミック

アメリカ合衆国 01730 マサチューセッツ州、ベドフォード、ヒルクレスト ロード 4

(72)発明者 リチャード ダブリュ. リーブス

アメリカ合衆国 01581 マサチューセッツ州、ウェストボロー、ベルクナップ ストリート

9

(72)発明者 ハンター チョウ

アメリカ合衆国 01720 マサチューセッツ州、アクトン、フォークナー ヒル ロード 3

8

(72)発明者 ロナルド エル. ペティジョン

アメリカ合衆国 01742 マサチューセッツ州、コンコード、ミニステリアル ドライブ 1

43

審査官 滝谷 亮一

(56)参考文献 特開2007-249738 (JP, A)

特開2010-160724 (JP, A)

特開2007-241799 (JP, A)

特表2004-528613 (JP, A)

米国特許出願公開第2003/0237056 (US, A1)

米国特許第06618791 (US, B1)

(58)調査した分野(Int.Cl. , DB名)

G 06 F 12 / 00